4h−SiC半導体素子及び半導体装置

【課題】 4h-SiC半導体素子のオン状態の抵抗低減とスイッチング速度向上実現する。

【解決手段】 (0001)面4h-SiC半導体素子のチャネル領域周囲に対してトレンチ溝を設け、シリコン酸化膜を埋め込む。トレンチ溝の酸化膜を、c軸方向へは引っ張り応力が加わり、c軸に垂直な平面上の二つ以上の軸からの圧縮応力が加わるように、平面レイアウトする。例えば、酸化膜で埋め込まれたトレンチ溝を、チャネルを囲む多角形としたり、離散的に配置する場合、チャネルを中心に対称的に配置するレイアウトでもよい。

【解決手段】 (0001)面4h-SiC半導体素子のチャネル領域周囲に対してトレンチ溝を設け、シリコン酸化膜を埋め込む。トレンチ溝の酸化膜を、c軸方向へは引っ張り応力が加わり、c軸に垂直な平面上の二つ以上の軸からの圧縮応力が加わるように、平面レイアウトする。例えば、酸化膜で埋め込まれたトレンチ溝を、チャネルを囲む多角形としたり、離散的に配置する場合、チャネルを中心に対称的に配置するレイアウトでもよい。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、4h-SiC半導体素子の構造および製造方法に関し、特に素子の半導体に4h-SiCを用いたトレンチ型パワーMOSFETに関する。

【背景技術】

【0002】

炭化けい素 (SiC)はバンドギャップがシリコンよりも大きく、絶縁破壊電界強度がシリコンよりも10倍程度高いために、パワー半導体を中心とした半導体素子への様々な応用がなされている。このSiCには3C-SiC、4h-SiC、6h-SiCなどを中心に200種類程度の結晶が知られているが、なかでも4h-SiCはバンドギャップが約3.2eVと大きく、また基板の作製が他の構造より相対的に作りやすいため、広く用いられている。4h-SiCは半導体素子としては主に電力用途のダイオードやパワーMOSFET(Metal Oxide Field Effect Transistor)に用いられる。このうちSiCパワーMOSFETは、Siの IGBTと比較すると、ユニポーラデバイスである分スイッチング速度が速く、またSiパワーMOSFETと比較すると、絶縁破壊電界強度が高い分基板を薄くでき、オン抵抗と呼ばれる動作時の抵抗を小さくすることができる。

【0003】

図2に代表的なパワーMOSFETの断面図を示す。4h-SiCでは基板表面の面方位は多くの場合基板作製が容易なc軸が基板と垂直になる(0001)面が用いられる。基板の裏面側ドレイン領域2aは、接触抵抗を下げるため、1018 (cm-3)程度の高い濃度でドレイン電極1aと接している。また、このドレイン領域2aと低濃度のn-ドリフト領域3aとは、ドレイン領域からのエピタキシャル成長で作り分けられる。ベース領域4aはp型不純物の層で、ゲート電極6aがオンのときにはゲート酸化膜7a直下にn型の反転層が形成され、ソース領域5aと導通する。

【0004】

パワーMOSFETには図3に示されるようなトレンチ型のものもある。この構造は、平面型パワーMOSFETに比べてトレンチ形成に必要な工程が増えるが、チャネルが基板と垂直方向に形成されるので微細化が容易になり、チャネル密度を向上させることによって低オン抵抗化やチップ面積の低減が可能となる。また、微細化した平面型パワーMOSFETで問題となる、図2のゲート酸化膜7aの直下でのドリフト層3aとその両脇のp型不純物層4aの接合間での空乏層によるJFET(Junction Field Effect Transistor)抵抗も生じない。さらには、 4h-SiCの電子の移動度はc軸と水平な方向が最も大きいので、基板表面が(0001)面のトレンチ型パワーMOSFETは、チャネル移動度が大きくなりチャネル抵抗も低減する。

【0005】

ところで、SiCパワーMOSFETのチャネル抵抗が全体のオン抵抗に占める割合は、設計耐圧が高いほど小さくなるが、一般にSiパワーMOSFETやSi-IGBTと比較すると大きい。これは、SiCは耐圧が高いのでドリフト層をSi素子と比較して1/10程度に薄くできるためドリフト層抵抗は小さい一方で、チャネル移動度がバルクの移動度より低下する割合が、Si素子の低下する割合よりも大きくなるためである。

【0006】

従って、SiCパワーMOSFETのオン抵抗の低減にはチャネル抵抗を小さくすることが必要である。

【0007】

この課題に対し、特許文献1には、一軸方向に引っ張り応力を印加してバンド質量を変えることでキャリアの有効質量を小さくし、チャネル移動度を向上させる方法が記載されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2005-244180号

【発明の概要】

【発明が解決しようとする課題】

【0009】

特許文献1に記載のチャネル移動度を向上させる方法は、一軸方向の応力印加方法のみが記載されている。しかし、特許文献1に記載の方法では、チャネル移動度を十分上げることができない。

【0010】

本発明は、上記に鑑みてなされたものであり、(0001)面4h-SiC半導体素子のチャネル移動度を向上させることを目的とする。

【課題を解決するための手段】

【0011】

ここで本発明の代表的な手段を説明する。

【0012】

代表的な手段の一つに、基板表面に対して垂直方向にc軸をもつ第1導電型の4h-SiC基板の表面に形成された第一導電型ドリフト領域と、前記ドリフト領域に接した4h-SiC第二導電型ベース領域と、前記ベース領域に接した4h-SiC第一導電型ソース領域と、前記ソース領域にしたソース電極と、前記ベース領域及びソース領域に隣接するトレンチ状のゲート電極と、前記ゲート電極と4h-SiCの境界に形成されたゲート絶縁膜と、前記4h-SiC基板の裏面に接した第一導電型ドレイン領域と、前記ドレイン領域に接したドレイン電極とを有する4h-SiC半導体素子であり、前記ベース領域及びソース領域に隣接するトレンチ状の埋め込み酸化膜層によってc軸に対して垂直な平面上の二軸以上の方向に圧縮応力が、c軸方向に引っ張り応力がチャネル領域に印加されることを特徴とする4h-SiC半導体素子がある。

【発明の効果】

【0013】

本発明によれば、チャネル移動度が高いトレンチ型4h-SiC半導体素子及び半導体装置を提供し得る。

【図面の簡単な説明】

【0014】

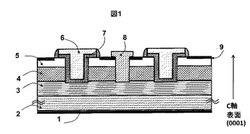

【図1】第1、第2、第3、第4、第5の実施例の4h-SiC半導体素子の要部断面図である。

【図2】平面型トランジスタ構造をもつSiCパワーMOSFETの要部断面図である。

【図3】トレンチ型トランジスタ構造をもつSiCパワーMOSFETの要部断面図である。

【図4】4h-SiCの結晶方位を説明するための概念図である。

【図5】4h-SiCに様々な応力を加えたもとでの伝導帯バンド変位を示す第1原理計算結果の図である。

【図6】4h-SiCに様々な応力を加えたもとでの伝導帯バンド変位を示す第1原理計算結果の図である。

【図7】4h-SiC半導体素子の埋め込み酸化膜層を形成するプロセスフローの1例を示す要部断面図である。

【図8】4h-SiC半導体素子の埋め込み酸化膜層を形成するプロセスフローの1例を示す要部断面図である。

【図9】埋め込み酸化膜層がトレンチ型ゲート電極よりも浅い、4h-SiC半導体素子の一例を示す要部断面図である。

【図10】埋め込み酸化膜層がトレンチ型ゲート電極よりも深い、4h-SiC半導体素子の一例を示す要部断面図である。

【図11】第1の実施例の4h-SiC半導体素子の等方圧縮応力が印加される様子を説明する概念図である。

【図12】第1の実施例の4h-SiC半導体素子にa、 b軸方向に等方圧縮応力が印加されると同時にc軸方向に引っ張り応力が印加される様子を説明する概念図である。

【図13】第1の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図14】第1の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図15】第1の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図16】第1の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図17】第1の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた全体図とその一部拡大図である。

【図18】第2の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図である。

【図19】第2の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図20】第3の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図21】第3の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図22】第4の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部部分図の一例である。

【図23】第4の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図24】第4の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図25】第5の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図26】第6の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた全体図とその一部拡大図の一例である。

【発明を実施するための形態】

【0015】

まず、4h-SiCに応力を印加したときのバンドの変位とバンド質量変位について第一原理計算で得られた詳しい解析結果を説明する。

【0016】

4h-SiCはc軸を対称軸とした6回対称の結晶構造をもつ。図4に示すように、4h-SiCの単位格子は、c軸、c軸に垂直な(0001)面上のa軸、a軸と60度の角度をなすb軸からなる基本並進ベクトルで表される。

【0017】

図5と図6に第一原理によるバンド計算で得られた4h-SiCに様々な応力印加したときの伝導帯のバンド変位を示す。このうち図5(a)が応力の印加のないときのバンド図である。SiCは間接遷移型半導体なので、価電子帯の上端はΓ点を中心に位置している一方で伝導帯の下端はM点に位置している。この伝導帯のバンドのエネルギーE(k)の波数k依存性は近似的に(式1)で表される。

【0018】

【数1】

(式1)においてk0はM点の波数であり、ΔEは伝導体下端のエネルギーを表すものとする。またαはバンド曲線の傾きを示すパラメータとする。このとき有効質量mは(式2)で表される。

【0019】

【数2】

(式2)に示されるようにαの値が大きいほど、バンド質量は小さい。従ってバンド曲線の傾きが大きいほどバンド質量は小さくなる。

【0020】

図5及び図6の(b)-(h)は、実線で表される(a)のバンド図に、点線で表される応力を印加したときの伝導帯下端のバンド図を重ね合わせて示したものである。なおこの図では4h-SiCの結晶格子を10%変位させるだけの応力を加えている。

【0021】

まず(b)、(c)にc軸方向への応力印加のもとでのバンド変位を示す。 (b)に示すように、c軸方向の引っ張り応力を印加すると、M点の下端でバンド曲線の傾きが大きくなり、バンド質量が小さくなる。これは特許文献1(特開2005-244180号公報)の結果と一致する。

【0022】

次に、(d)、(e)にb軸方向のみに応力を加えたときのバンド変位を示す。このときは、バンド曲線の傾きの大きな変位はない。次に、(f)、(g)にa、b軸方向に対して結晶格子を一様に変位させる応力、つまりc軸と垂直な平面に対する等方的な応力を印加したときのバンド変位を示す。このとき、(g)に示されるように、a、b軸方向への等方圧縮によりバンド曲線の傾きが大きくなる。以上の結果は、c軸方向に引っ張り応力、a、b軸方向に等方圧縮応力を印加すると伝導帯のバンド質量が小さくなることを示している。ここで、(h)にc軸方向に引っ張り応力を印加すると同時にa、b軸方向に等方圧縮応力を印加したときのバンド変位を示す。(h)に示されるように、バンド曲線の傾きはこのとき最も大きくなる。これらの結果は、4h-SiCの電子のバンド質量を小さくし、移動度を増加させるためには、c軸方向への引っ張り応力と同時にa、b軸方向に等方的に圧縮応力を印加することが最も効果的であることを示している。このような応力を印加する素子構造を以下の実施例で説明する。

【実施例1】

【0023】

図1は第1の実施例による4h-SiCトレンチ型パワーMOSFETの断面構造を示す概念図である。図1において、本実施例による4h-SiCトレンチ型パワーMOSFETは、ドレイン電極1とドレイン領域2とドリフト領域3とベース領域4とソース領域5とゲート電極6とゲート絶縁膜7と埋め込み酸化膜層8とソース電極9から構成される。

【0024】

ドレイン電極1は、c軸に垂直な(0001)面が露出し、接触抵抗を下げるためのシリサイド形成や、Alスパッタリングによるメタル層形成などがされている。

ドレイン領域2はドレイン電極面との接触面には接触抵抗を下げるためにn型不純物(例えばN:窒素やP:リン)注入などのされたn型4h-SiC基板である。

【0025】

ドリフト領域3はドレイン領域2上に面方位がドレイン領域と同じ4h-SiCをエピタキシャル成長で形成したn型半導体領域である。

【0026】

ベース領域4はドリフト領域3上に位置し、トランジスタのn型チャネル領域形成のために4h-SiCにp型不純物(例えばAl:アルミニウムやB:ボロン)などの注入をして形成したp型半導体領域である。

【0027】

ソース領域5はベース領域の上にn型不純物(例えばN:窒素やP:リン)を注入して形成したn型半導体領域である。

【0028】

ゲート電極6は、上述したベース領域4、ソース領域5上にドライエッチングなどでc軸に平行にトレンチ形成し、ゲート絶縁膜形成の後、ポリシリコンのCVD (Chemical Vapor Deposition) またはアモルファスシリコンのCVD後、熱処理でポリシリコンに変性させるなどで形成した電極領域である。

【0029】

ゲート絶縁膜7は、上述した4h-SiCのトレンチ状のゲート電極6と、ベース領域4ならびにソース領域5に挟まれた位置に形成され、ゲート電極加工時のトレンチ形成の後、ウェット酸化、ドライ酸化あるいはSiO2酸化膜CVDなどによって形成される。

【0030】

埋め込み酸化膜層8は、ゲート電極間に位置し、ゲート電極と同様のトレンチエッチングに後にポリシリコンまたは、アモルファスシリコンをCVDによって堆積し、その後熱酸化により酸化膜にするか、あるいはSiO2を直接CVDで堆積させて形成する。

【0031】

ソース電極9は上述した、ソース領域5の上にシリサイド、あるいはメタルスパッタリングなどをすることで、SiCとの接触抵抗を下げるように形成する。

【0032】

図7及び図8に、以上で説明した本発明の4h-SiCのトレンチ型パワーMOSFETの埋め込み酸化膜層形成時の形成プロセスフローの一例を示す。図7(1)に示されるように、まず4h-SiC基板上にエピタキシャル成長で形成したn型のドリフト層3上に不純物注入によってp型のベース領域4とn型のソース領域5を形成する。

【0033】

次に、図7(2)に示されるように、ドライエッチングなどの方法によってソース領域5ならびにベース領域4を加工してトレンチ形成を行なう。このとき、ゲート電極用のトレンチエッチングと埋め込み酸化膜用のトレンチエッチングは同時に行なうか、あるいは別々に行なう。

【0034】

この次に、図7 (3)に示されるように、ポリシリコン、あるいはアモルファスシリコンのCVDなどの方法によりトレンチの穴を塞ぐ。

【0035】

さらに、図8(4)に示されるように、堆積したシリコン層を700度から1000度未満程度の温度の熱酸化でSiO2にした後で、埋め込み酸化膜層8以外をドライエッチング、あるいはドライエッチングとウェットエッチングの組み合わせにより取り去る。この酸化時に、Siの結晶格子間隔が約0.5nmでSiO2の平均格子間隔も同じく0.5nm程度なので酸化時に酸素原子が加わる分だけSi→SiO2の組成変化で体積が膨張する。この体積膨張により、4h-SiCのベース領域4とソース領域5に応力が加わる。

【0036】

また、図7 (3)、図8(4)での埋め込み酸化膜層形成では、直接酸化膜をCVDなどにより堆積させて、後にゲート電極部分はエッチングで取り去っても良い。このときには、非晶質化している埋め込み酸化膜層8は、この後の通常のプロセスで700度から1000度未満程度の熱負荷によって部分的な組成が変化することで膨張し、4h-SiCのベース領域4とソース領域5に応力が加わる。

【0037】

埋め込み酸化膜8の深さについては、図8(4)のように、ゲート電極6と同じ深さにすることにより、両者を同一工程で作ることができるが、もし別工程で形成するときは、図9のようにゲート電極6よりも浅くしてもよい。これにより、埋め込み酸化膜層8のトレンチ形成時間を短くし、製造に必要な時間とコストを下げることができる。また、図10に示されるようにゲート電極よりも深くしてもよい。これにより応力がかかり電子の移動度の向上する領域が、ゲート電圧印加によりチャネルが形成されるソース領域とベース領域のみでなく、ドリフト層領域も入ることによりオン抵抗をさらに下げることができる。

【0038】

図8(4)の後は、前述のプロセスによって、ゲート絶縁膜7、ゲート電極6、保護膜などが形成されトレンチ型パワーMOSFETは形成される。

【実施例2】

【0039】

第2の実施例では、六角形の単位構造をもつ埋め込み酸化膜層によりチャネル領域に等方的な圧縮応力をかける。図11に第2の実施例をソース電極側から見たときの概念図を示す。図11の5bがソース領域、6bがゲート電極、8bが埋め込み酸化膜層を示している。第2の実施例では、ゲート電極6bと埋め込み酸化膜層8bが中空の六角形の構造を持ち、埋め込み酸化膜層8bが図12に記載された矢印のようにソース領域5bのc軸に対して垂直方向に圧縮応力を印加し、同時にc軸方向に引っ張り応力を印加する。具体的には、SiO2のヤング率は約130GPaで、一方SiCのヤング率は約430GPaなので埋め込み酸化膜層8のSiO2が周囲にSiCに取り囲まれていることで受ける圧縮率の約3割分だけ4h-SiCも等方的に圧縮する。またSiCのポアソン比は約0.14〜0.17程度なのでa、b軸方向に結晶格子の圧縮率の14〜17%程度分c軸方向の結晶定数は増加する。

【0040】

図13に図11の半導体素子の半導体装置中への配列の一例を示す。図11の素子の単位構造は六角形であるために、図13に示されるように、配列のずれによる隙間を生じることなく配置することができる。なお、図11と図13では、ゲート電極6bの内側はソース領域5bのみとなっているが、図14のように、ここにさらに埋め込み酸化膜層5bを設けて六角形の内外からチャネル領域に圧縮応力をかけてもよい。これにより、応力の等方性は弱くなるが、圧縮応力自体をより効果的にかけられるようになる。なお、図13、 図14ではそれぞれの六角形内部のゲート電極6bは互いに分離しているが、さらにこの後の製造工程ではこの上に配線層を配置するなど行って、各ゲート電極を電気的に導通させて、一箇所のゲート電極パッドで電圧を印加できるようにする。これに対して、図15、 図16のように上に配線層を設けず、各ゲート電極6bを直接つなげて、図17にあるように一箇所のゲート電極パッド11で電圧を印加できるようにしてもよい。これにより、応力の等方性は弱くなるが、配線層を一層分なくすことにより製造コストを下げることが可能となる。なお各六角形の単位構造同士の、ゲート電極6bの接続方法は図15、図16のように一方向に各列毎接続するのでなく、他の列に接続したり、異なる方向にある素子のゲート電極と接続してもよい。

【実施例3】

【0041】

第3の実施例は、第2の実施例と異なり、ゲート電極6dと埋め込み酸化膜層8dが中空の三角形の単位構造を持つ。第3の実施例は、三角形の単位構造をもつ埋め込み酸化膜層によりチャネル領域に等方的な圧縮応力をかける。第3の実施例は、第2の実施例と比べて埋め込み酸化膜層面積のソース領域面積に対する比率を大きくすることができるため、より大きな圧縮応力を印加することができる。この三角形の形状は、より等方的な応力を印加するために正三角形の形状に近づけることが望ましい。なお図18では、三角形の内側部分には埋め込み酸化膜8dは存在しないが、埋め込み酸化膜層8dをゲート電極6dの内部に配置してもよい。また図18ではそれぞれの三角形内部のゲート電極6dは互いに分離しているが、さらにこの後の製造工程でこの上に金属層を配置するなどして各ゲート電極を全て電気的に導通させて、一箇所のゲート電極パッドで電圧を印加できるようにする。これに対して、例えば図19のように上に配線層を設けず、各ゲート電極6eを直接つなげて、第2の実施例の図17にあるような方法で一箇所のゲート電極パッド11で電圧を印加できるようにしてもよい。なお、各三角形の単位構造同士のゲート電極6eの接続方法は、図19のように一方向に各列毎接続するのでなく、他の列に接続したり、異なる方向にある素子のゲート電極と接続してもよい。

【実施例4】

【0042】

第4の実施例は、第2、第3の実施例と異なり、ゲート電極6fと埋め込み酸化膜層8fが中空の円形の単位構造を持つ。第4の実施例は、円形の単位構造をもつ埋め込み酸化膜層8fによりチャネル領域に等方的な圧縮応力をかける。第4の実施例は第2、第3の実施例と比べてより等方的に圧縮応力を印加し、電子の移動度を向上させることができる。なお、図20では、円の内側部分には埋め込み酸化膜8dは存在しないが、埋め込み酸化膜層8fをゲート電極6f内部に配置してもよい。また図20ではそれぞれの円形内部のゲート電極6fは互いに分離しているが、さらにこの後の製造工程でこの上に金属層を配置するなどして各ゲート電極6fを全て電気的に導通させて、一箇所のゲート電極パッドで電圧を印加できるようにする。これに対して、例えば、図21のように上に配線層を設けず、各ゲート電極6gを直接つなげて、第2の実施例の図17にあるような方法で一箇所のゲート電極パッド11で電圧を印加できるようにしてもよい。なお各円の単位構造同士の、ゲート電極の接続方法は図21のように一方向に各列毎接続するのでなく、他の列に接続したり、異なる方向にある素子のゲート電極と接続してもよい。

【実施例5】

【0043】

第5の実施例は、第2、第3、第4の実施例と異なり、ゲート電極6hと埋め込み酸化膜層8hが中空の四角形の単位構造を持つ。第5の実施例は、四角形の単位構造を持つ埋め込み酸化膜層8hによりチャネル領域に等方的な圧縮応力をかける。第5の実施例は、第2、第3、第4の実施例と異なり、互いに90度で交わる2方向のみの加工で形成できるため、チップ端の配置や加工が容易になる。なお、この四角形は、より等方的な応力を印加するため正方形に近い形にすることが望ましい。なお、図22では、正方形の内側部分には埋め込み酸化膜層8hは存在しないが、埋め込み酸化膜層8hをゲート電極6h内部に配置してもよい。また図22ではそれぞれの四角形内部のゲート電極6hは互いに分離しているが、さらにこの後の製造工程でこの上に金属層を配置するなどして各ゲート電極6hを全て電気的に導通させて、一箇所のゲート電極パッドで電圧を印加できるようにする。これに対して、例えば図23、図24のように上に配線層を設けず、各ゲート電極を直接つなげて、第2の実施例の図17にあるような方法で一箇所のゲート電極パッド11で電圧を印加できるようにしてもよい。なお各四角形の単位構造同士の、ゲート電極の接続方法は図23、図24のように一方向に各列毎接続するのでなく、他の列に接続したり、異なる方向にある素子のゲート電極と接続してもよい。

【実施例6】

【0044】

第6の実施例では、図25のようにゲート電極6kと埋め込み酸化膜層8kは交互に縞状に配置され、埋め込み酸化膜層8kは両側に分岐構造を複数有する形状をもつ。第6の実施例では、埋め込み酸化膜層の分岐構造8kがチャネル領域を四方から囲むため、チャネル領域に等方的な圧縮応力を印加することができる。

【0045】

また、第6の実施例では、ゲート電極6kは一端で1つにまとめられて、チップ上のゲートパッドに接続されている。これにより、第6の実施例は、第2、第3、 第4、第5の実施例と比べて、従来の構造からのプロセス変更が少なくて済む。

【0046】

なお、本発明で囲む形態について示したがというのは、連続的に囲む必要はなく、二軸以上の方向に分断させた状態で離散的に存在しても囲むように応力がかかれば代替可能である。

【実施例7】

【0047】

第7の実施例の半導体装置では、図26に一例を示すように、半導体装置のチップ端にゲートパット11に導通させない模擬(ダミー)ゲート電極12を1列、もしくは数列配置する。チップ端のトランジスタは、埋め込み酸化膜層から有効な応力が印加されない部分があるが、チップ端のトランジスタを導通させないことで、有効な応力が印加されているトランジスタのみを動作させ、素子の耐圧を向上させることができる。また、素子の(0001)面上、ソース電極やゲート電極のある面の構造は、第1、第2、 第3、第4、第5、第6のいずれの実施例の構造でもよい。

【符号の説明】

【0048】

1、1aドレイン電極

2、2a ドレイン領域

3、3a ドリフト領域

4、4a ベース領域

5、5a、5b、5c、5d、5e、5f、5g、5h、5i、5j、5k ソース領域

6、6a、6b、6c、6d、6e、6f、6g、6h、6i、6j、6k ゲート電極

7、7a ゲート絶縁膜

8、8a、8b、8c、8d、8e、8f、8g、8h、8i、8j、8k埋め込み酸化膜層

9、9a ソース電極

10 ゲート側壁

11 ゲートパッド

12 模擬ゲート電極

【技術分野】

【0001】

本発明は、4h-SiC半導体素子の構造および製造方法に関し、特に素子の半導体に4h-SiCを用いたトレンチ型パワーMOSFETに関する。

【背景技術】

【0002】

炭化けい素 (SiC)はバンドギャップがシリコンよりも大きく、絶縁破壊電界強度がシリコンよりも10倍程度高いために、パワー半導体を中心とした半導体素子への様々な応用がなされている。このSiCには3C-SiC、4h-SiC、6h-SiCなどを中心に200種類程度の結晶が知られているが、なかでも4h-SiCはバンドギャップが約3.2eVと大きく、また基板の作製が他の構造より相対的に作りやすいため、広く用いられている。4h-SiCは半導体素子としては主に電力用途のダイオードやパワーMOSFET(Metal Oxide Field Effect Transistor)に用いられる。このうちSiCパワーMOSFETは、Siの IGBTと比較すると、ユニポーラデバイスである分スイッチング速度が速く、またSiパワーMOSFETと比較すると、絶縁破壊電界強度が高い分基板を薄くでき、オン抵抗と呼ばれる動作時の抵抗を小さくすることができる。

【0003】

図2に代表的なパワーMOSFETの断面図を示す。4h-SiCでは基板表面の面方位は多くの場合基板作製が容易なc軸が基板と垂直になる(0001)面が用いられる。基板の裏面側ドレイン領域2aは、接触抵抗を下げるため、1018 (cm-3)程度の高い濃度でドレイン電極1aと接している。また、このドレイン領域2aと低濃度のn-ドリフト領域3aとは、ドレイン領域からのエピタキシャル成長で作り分けられる。ベース領域4aはp型不純物の層で、ゲート電極6aがオンのときにはゲート酸化膜7a直下にn型の反転層が形成され、ソース領域5aと導通する。

【0004】

パワーMOSFETには図3に示されるようなトレンチ型のものもある。この構造は、平面型パワーMOSFETに比べてトレンチ形成に必要な工程が増えるが、チャネルが基板と垂直方向に形成されるので微細化が容易になり、チャネル密度を向上させることによって低オン抵抗化やチップ面積の低減が可能となる。また、微細化した平面型パワーMOSFETで問題となる、図2のゲート酸化膜7aの直下でのドリフト層3aとその両脇のp型不純物層4aの接合間での空乏層によるJFET(Junction Field Effect Transistor)抵抗も生じない。さらには、 4h-SiCの電子の移動度はc軸と水平な方向が最も大きいので、基板表面が(0001)面のトレンチ型パワーMOSFETは、チャネル移動度が大きくなりチャネル抵抗も低減する。

【0005】

ところで、SiCパワーMOSFETのチャネル抵抗が全体のオン抵抗に占める割合は、設計耐圧が高いほど小さくなるが、一般にSiパワーMOSFETやSi-IGBTと比較すると大きい。これは、SiCは耐圧が高いのでドリフト層をSi素子と比較して1/10程度に薄くできるためドリフト層抵抗は小さい一方で、チャネル移動度がバルクの移動度より低下する割合が、Si素子の低下する割合よりも大きくなるためである。

【0006】

従って、SiCパワーMOSFETのオン抵抗の低減にはチャネル抵抗を小さくすることが必要である。

【0007】

この課題に対し、特許文献1には、一軸方向に引っ張り応力を印加してバンド質量を変えることでキャリアの有効質量を小さくし、チャネル移動度を向上させる方法が記載されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2005-244180号

【発明の概要】

【発明が解決しようとする課題】

【0009】

特許文献1に記載のチャネル移動度を向上させる方法は、一軸方向の応力印加方法のみが記載されている。しかし、特許文献1に記載の方法では、チャネル移動度を十分上げることができない。

【0010】

本発明は、上記に鑑みてなされたものであり、(0001)面4h-SiC半導体素子のチャネル移動度を向上させることを目的とする。

【課題を解決するための手段】

【0011】

ここで本発明の代表的な手段を説明する。

【0012】

代表的な手段の一つに、基板表面に対して垂直方向にc軸をもつ第1導電型の4h-SiC基板の表面に形成された第一導電型ドリフト領域と、前記ドリフト領域に接した4h-SiC第二導電型ベース領域と、前記ベース領域に接した4h-SiC第一導電型ソース領域と、前記ソース領域にしたソース電極と、前記ベース領域及びソース領域に隣接するトレンチ状のゲート電極と、前記ゲート電極と4h-SiCの境界に形成されたゲート絶縁膜と、前記4h-SiC基板の裏面に接した第一導電型ドレイン領域と、前記ドレイン領域に接したドレイン電極とを有する4h-SiC半導体素子であり、前記ベース領域及びソース領域に隣接するトレンチ状の埋め込み酸化膜層によってc軸に対して垂直な平面上の二軸以上の方向に圧縮応力が、c軸方向に引っ張り応力がチャネル領域に印加されることを特徴とする4h-SiC半導体素子がある。

【発明の効果】

【0013】

本発明によれば、チャネル移動度が高いトレンチ型4h-SiC半導体素子及び半導体装置を提供し得る。

【図面の簡単な説明】

【0014】

【図1】第1、第2、第3、第4、第5の実施例の4h-SiC半導体素子の要部断面図である。

【図2】平面型トランジスタ構造をもつSiCパワーMOSFETの要部断面図である。

【図3】トレンチ型トランジスタ構造をもつSiCパワーMOSFETの要部断面図である。

【図4】4h-SiCの結晶方位を説明するための概念図である。

【図5】4h-SiCに様々な応力を加えたもとでの伝導帯バンド変位を示す第1原理計算結果の図である。

【図6】4h-SiCに様々な応力を加えたもとでの伝導帯バンド変位を示す第1原理計算結果の図である。

【図7】4h-SiC半導体素子の埋め込み酸化膜層を形成するプロセスフローの1例を示す要部断面図である。

【図8】4h-SiC半導体素子の埋め込み酸化膜層を形成するプロセスフローの1例を示す要部断面図である。

【図9】埋め込み酸化膜層がトレンチ型ゲート電極よりも浅い、4h-SiC半導体素子の一例を示す要部断面図である。

【図10】埋め込み酸化膜層がトレンチ型ゲート電極よりも深い、4h-SiC半導体素子の一例を示す要部断面図である。

【図11】第1の実施例の4h-SiC半導体素子の等方圧縮応力が印加される様子を説明する概念図である。

【図12】第1の実施例の4h-SiC半導体素子にa、 b軸方向に等方圧縮応力が印加されると同時にc軸方向に引っ張り応力が印加される様子を説明する概念図である。

【図13】第1の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図14】第1の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図15】第1の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図16】第1の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図17】第1の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた全体図とその一部拡大図である。

【図18】第2の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図である。

【図19】第2の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図20】第3の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図21】第3の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図22】第4の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部部分図の一例である。

【図23】第4の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図24】第4の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図25】第5の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた要部断面図の一例である。

【図26】第6の実施例の4h-SiC半導体素子の(0001)面上、ソース領域側からみた全体図とその一部拡大図の一例である。

【発明を実施するための形態】

【0015】

まず、4h-SiCに応力を印加したときのバンドの変位とバンド質量変位について第一原理計算で得られた詳しい解析結果を説明する。

【0016】

4h-SiCはc軸を対称軸とした6回対称の結晶構造をもつ。図4に示すように、4h-SiCの単位格子は、c軸、c軸に垂直な(0001)面上のa軸、a軸と60度の角度をなすb軸からなる基本並進ベクトルで表される。

【0017】

図5と図6に第一原理によるバンド計算で得られた4h-SiCに様々な応力印加したときの伝導帯のバンド変位を示す。このうち図5(a)が応力の印加のないときのバンド図である。SiCは間接遷移型半導体なので、価電子帯の上端はΓ点を中心に位置している一方で伝導帯の下端はM点に位置している。この伝導帯のバンドのエネルギーE(k)の波数k依存性は近似的に(式1)で表される。

【0018】

【数1】

(式1)においてk0はM点の波数であり、ΔEは伝導体下端のエネルギーを表すものとする。またαはバンド曲線の傾きを示すパラメータとする。このとき有効質量mは(式2)で表される。

【0019】

【数2】

(式2)に示されるようにαの値が大きいほど、バンド質量は小さい。従ってバンド曲線の傾きが大きいほどバンド質量は小さくなる。

【0020】

図5及び図6の(b)-(h)は、実線で表される(a)のバンド図に、点線で表される応力を印加したときの伝導帯下端のバンド図を重ね合わせて示したものである。なおこの図では4h-SiCの結晶格子を10%変位させるだけの応力を加えている。

【0021】

まず(b)、(c)にc軸方向への応力印加のもとでのバンド変位を示す。 (b)に示すように、c軸方向の引っ張り応力を印加すると、M点の下端でバンド曲線の傾きが大きくなり、バンド質量が小さくなる。これは特許文献1(特開2005-244180号公報)の結果と一致する。

【0022】

次に、(d)、(e)にb軸方向のみに応力を加えたときのバンド変位を示す。このときは、バンド曲線の傾きの大きな変位はない。次に、(f)、(g)にa、b軸方向に対して結晶格子を一様に変位させる応力、つまりc軸と垂直な平面に対する等方的な応力を印加したときのバンド変位を示す。このとき、(g)に示されるように、a、b軸方向への等方圧縮によりバンド曲線の傾きが大きくなる。以上の結果は、c軸方向に引っ張り応力、a、b軸方向に等方圧縮応力を印加すると伝導帯のバンド質量が小さくなることを示している。ここで、(h)にc軸方向に引っ張り応力を印加すると同時にa、b軸方向に等方圧縮応力を印加したときのバンド変位を示す。(h)に示されるように、バンド曲線の傾きはこのとき最も大きくなる。これらの結果は、4h-SiCの電子のバンド質量を小さくし、移動度を増加させるためには、c軸方向への引っ張り応力と同時にa、b軸方向に等方的に圧縮応力を印加することが最も効果的であることを示している。このような応力を印加する素子構造を以下の実施例で説明する。

【実施例1】

【0023】

図1は第1の実施例による4h-SiCトレンチ型パワーMOSFETの断面構造を示す概念図である。図1において、本実施例による4h-SiCトレンチ型パワーMOSFETは、ドレイン電極1とドレイン領域2とドリフト領域3とベース領域4とソース領域5とゲート電極6とゲート絶縁膜7と埋め込み酸化膜層8とソース電極9から構成される。

【0024】

ドレイン電極1は、c軸に垂直な(0001)面が露出し、接触抵抗を下げるためのシリサイド形成や、Alスパッタリングによるメタル層形成などがされている。

ドレイン領域2はドレイン電極面との接触面には接触抵抗を下げるためにn型不純物(例えばN:窒素やP:リン)注入などのされたn型4h-SiC基板である。

【0025】

ドリフト領域3はドレイン領域2上に面方位がドレイン領域と同じ4h-SiCをエピタキシャル成長で形成したn型半導体領域である。

【0026】

ベース領域4はドリフト領域3上に位置し、トランジスタのn型チャネル領域形成のために4h-SiCにp型不純物(例えばAl:アルミニウムやB:ボロン)などの注入をして形成したp型半導体領域である。

【0027】

ソース領域5はベース領域の上にn型不純物(例えばN:窒素やP:リン)を注入して形成したn型半導体領域である。

【0028】

ゲート電極6は、上述したベース領域4、ソース領域5上にドライエッチングなどでc軸に平行にトレンチ形成し、ゲート絶縁膜形成の後、ポリシリコンのCVD (Chemical Vapor Deposition) またはアモルファスシリコンのCVD後、熱処理でポリシリコンに変性させるなどで形成した電極領域である。

【0029】

ゲート絶縁膜7は、上述した4h-SiCのトレンチ状のゲート電極6と、ベース領域4ならびにソース領域5に挟まれた位置に形成され、ゲート電極加工時のトレンチ形成の後、ウェット酸化、ドライ酸化あるいはSiO2酸化膜CVDなどによって形成される。

【0030】

埋め込み酸化膜層8は、ゲート電極間に位置し、ゲート電極と同様のトレンチエッチングに後にポリシリコンまたは、アモルファスシリコンをCVDによって堆積し、その後熱酸化により酸化膜にするか、あるいはSiO2を直接CVDで堆積させて形成する。

【0031】

ソース電極9は上述した、ソース領域5の上にシリサイド、あるいはメタルスパッタリングなどをすることで、SiCとの接触抵抗を下げるように形成する。

【0032】

図7及び図8に、以上で説明した本発明の4h-SiCのトレンチ型パワーMOSFETの埋め込み酸化膜層形成時の形成プロセスフローの一例を示す。図7(1)に示されるように、まず4h-SiC基板上にエピタキシャル成長で形成したn型のドリフト層3上に不純物注入によってp型のベース領域4とn型のソース領域5を形成する。

【0033】

次に、図7(2)に示されるように、ドライエッチングなどの方法によってソース領域5ならびにベース領域4を加工してトレンチ形成を行なう。このとき、ゲート電極用のトレンチエッチングと埋め込み酸化膜用のトレンチエッチングは同時に行なうか、あるいは別々に行なう。

【0034】

この次に、図7 (3)に示されるように、ポリシリコン、あるいはアモルファスシリコンのCVDなどの方法によりトレンチの穴を塞ぐ。

【0035】

さらに、図8(4)に示されるように、堆積したシリコン層を700度から1000度未満程度の温度の熱酸化でSiO2にした後で、埋め込み酸化膜層8以外をドライエッチング、あるいはドライエッチングとウェットエッチングの組み合わせにより取り去る。この酸化時に、Siの結晶格子間隔が約0.5nmでSiO2の平均格子間隔も同じく0.5nm程度なので酸化時に酸素原子が加わる分だけSi→SiO2の組成変化で体積が膨張する。この体積膨張により、4h-SiCのベース領域4とソース領域5に応力が加わる。

【0036】

また、図7 (3)、図8(4)での埋め込み酸化膜層形成では、直接酸化膜をCVDなどにより堆積させて、後にゲート電極部分はエッチングで取り去っても良い。このときには、非晶質化している埋め込み酸化膜層8は、この後の通常のプロセスで700度から1000度未満程度の熱負荷によって部分的な組成が変化することで膨張し、4h-SiCのベース領域4とソース領域5に応力が加わる。

【0037】

埋め込み酸化膜8の深さについては、図8(4)のように、ゲート電極6と同じ深さにすることにより、両者を同一工程で作ることができるが、もし別工程で形成するときは、図9のようにゲート電極6よりも浅くしてもよい。これにより、埋め込み酸化膜層8のトレンチ形成時間を短くし、製造に必要な時間とコストを下げることができる。また、図10に示されるようにゲート電極よりも深くしてもよい。これにより応力がかかり電子の移動度の向上する領域が、ゲート電圧印加によりチャネルが形成されるソース領域とベース領域のみでなく、ドリフト層領域も入ることによりオン抵抗をさらに下げることができる。

【0038】

図8(4)の後は、前述のプロセスによって、ゲート絶縁膜7、ゲート電極6、保護膜などが形成されトレンチ型パワーMOSFETは形成される。

【実施例2】

【0039】

第2の実施例では、六角形の単位構造をもつ埋め込み酸化膜層によりチャネル領域に等方的な圧縮応力をかける。図11に第2の実施例をソース電極側から見たときの概念図を示す。図11の5bがソース領域、6bがゲート電極、8bが埋め込み酸化膜層を示している。第2の実施例では、ゲート電極6bと埋め込み酸化膜層8bが中空の六角形の構造を持ち、埋め込み酸化膜層8bが図12に記載された矢印のようにソース領域5bのc軸に対して垂直方向に圧縮応力を印加し、同時にc軸方向に引っ張り応力を印加する。具体的には、SiO2のヤング率は約130GPaで、一方SiCのヤング率は約430GPaなので埋め込み酸化膜層8のSiO2が周囲にSiCに取り囲まれていることで受ける圧縮率の約3割分だけ4h-SiCも等方的に圧縮する。またSiCのポアソン比は約0.14〜0.17程度なのでa、b軸方向に結晶格子の圧縮率の14〜17%程度分c軸方向の結晶定数は増加する。

【0040】

図13に図11の半導体素子の半導体装置中への配列の一例を示す。図11の素子の単位構造は六角形であるために、図13に示されるように、配列のずれによる隙間を生じることなく配置することができる。なお、図11と図13では、ゲート電極6bの内側はソース領域5bのみとなっているが、図14のように、ここにさらに埋め込み酸化膜層5bを設けて六角形の内外からチャネル領域に圧縮応力をかけてもよい。これにより、応力の等方性は弱くなるが、圧縮応力自体をより効果的にかけられるようになる。なお、図13、 図14ではそれぞれの六角形内部のゲート電極6bは互いに分離しているが、さらにこの後の製造工程ではこの上に配線層を配置するなど行って、各ゲート電極を電気的に導通させて、一箇所のゲート電極パッドで電圧を印加できるようにする。これに対して、図15、 図16のように上に配線層を設けず、各ゲート電極6bを直接つなげて、図17にあるように一箇所のゲート電極パッド11で電圧を印加できるようにしてもよい。これにより、応力の等方性は弱くなるが、配線層を一層分なくすことにより製造コストを下げることが可能となる。なお各六角形の単位構造同士の、ゲート電極6bの接続方法は図15、図16のように一方向に各列毎接続するのでなく、他の列に接続したり、異なる方向にある素子のゲート電極と接続してもよい。

【実施例3】

【0041】

第3の実施例は、第2の実施例と異なり、ゲート電極6dと埋め込み酸化膜層8dが中空の三角形の単位構造を持つ。第3の実施例は、三角形の単位構造をもつ埋め込み酸化膜層によりチャネル領域に等方的な圧縮応力をかける。第3の実施例は、第2の実施例と比べて埋め込み酸化膜層面積のソース領域面積に対する比率を大きくすることができるため、より大きな圧縮応力を印加することができる。この三角形の形状は、より等方的な応力を印加するために正三角形の形状に近づけることが望ましい。なお図18では、三角形の内側部分には埋め込み酸化膜8dは存在しないが、埋め込み酸化膜層8dをゲート電極6dの内部に配置してもよい。また図18ではそれぞれの三角形内部のゲート電極6dは互いに分離しているが、さらにこの後の製造工程でこの上に金属層を配置するなどして各ゲート電極を全て電気的に導通させて、一箇所のゲート電極パッドで電圧を印加できるようにする。これに対して、例えば図19のように上に配線層を設けず、各ゲート電極6eを直接つなげて、第2の実施例の図17にあるような方法で一箇所のゲート電極パッド11で電圧を印加できるようにしてもよい。なお、各三角形の単位構造同士のゲート電極6eの接続方法は、図19のように一方向に各列毎接続するのでなく、他の列に接続したり、異なる方向にある素子のゲート電極と接続してもよい。

【実施例4】

【0042】

第4の実施例は、第2、第3の実施例と異なり、ゲート電極6fと埋め込み酸化膜層8fが中空の円形の単位構造を持つ。第4の実施例は、円形の単位構造をもつ埋め込み酸化膜層8fによりチャネル領域に等方的な圧縮応力をかける。第4の実施例は第2、第3の実施例と比べてより等方的に圧縮応力を印加し、電子の移動度を向上させることができる。なお、図20では、円の内側部分には埋め込み酸化膜8dは存在しないが、埋め込み酸化膜層8fをゲート電極6f内部に配置してもよい。また図20ではそれぞれの円形内部のゲート電極6fは互いに分離しているが、さらにこの後の製造工程でこの上に金属層を配置するなどして各ゲート電極6fを全て電気的に導通させて、一箇所のゲート電極パッドで電圧を印加できるようにする。これに対して、例えば、図21のように上に配線層を設けず、各ゲート電極6gを直接つなげて、第2の実施例の図17にあるような方法で一箇所のゲート電極パッド11で電圧を印加できるようにしてもよい。なお各円の単位構造同士の、ゲート電極の接続方法は図21のように一方向に各列毎接続するのでなく、他の列に接続したり、異なる方向にある素子のゲート電極と接続してもよい。

【実施例5】

【0043】

第5の実施例は、第2、第3、第4の実施例と異なり、ゲート電極6hと埋め込み酸化膜層8hが中空の四角形の単位構造を持つ。第5の実施例は、四角形の単位構造を持つ埋め込み酸化膜層8hによりチャネル領域に等方的な圧縮応力をかける。第5の実施例は、第2、第3、第4の実施例と異なり、互いに90度で交わる2方向のみの加工で形成できるため、チップ端の配置や加工が容易になる。なお、この四角形は、より等方的な応力を印加するため正方形に近い形にすることが望ましい。なお、図22では、正方形の内側部分には埋め込み酸化膜層8hは存在しないが、埋め込み酸化膜層8hをゲート電極6h内部に配置してもよい。また図22ではそれぞれの四角形内部のゲート電極6hは互いに分離しているが、さらにこの後の製造工程でこの上に金属層を配置するなどして各ゲート電極6hを全て電気的に導通させて、一箇所のゲート電極パッドで電圧を印加できるようにする。これに対して、例えば図23、図24のように上に配線層を設けず、各ゲート電極を直接つなげて、第2の実施例の図17にあるような方法で一箇所のゲート電極パッド11で電圧を印加できるようにしてもよい。なお各四角形の単位構造同士の、ゲート電極の接続方法は図23、図24のように一方向に各列毎接続するのでなく、他の列に接続したり、異なる方向にある素子のゲート電極と接続してもよい。

【実施例6】

【0044】

第6の実施例では、図25のようにゲート電極6kと埋め込み酸化膜層8kは交互に縞状に配置され、埋め込み酸化膜層8kは両側に分岐構造を複数有する形状をもつ。第6の実施例では、埋め込み酸化膜層の分岐構造8kがチャネル領域を四方から囲むため、チャネル領域に等方的な圧縮応力を印加することができる。

【0045】

また、第6の実施例では、ゲート電極6kは一端で1つにまとめられて、チップ上のゲートパッドに接続されている。これにより、第6の実施例は、第2、第3、 第4、第5の実施例と比べて、従来の構造からのプロセス変更が少なくて済む。

【0046】

なお、本発明で囲む形態について示したがというのは、連続的に囲む必要はなく、二軸以上の方向に分断させた状態で離散的に存在しても囲むように応力がかかれば代替可能である。

【実施例7】

【0047】

第7の実施例の半導体装置では、図26に一例を示すように、半導体装置のチップ端にゲートパット11に導通させない模擬(ダミー)ゲート電極12を1列、もしくは数列配置する。チップ端のトランジスタは、埋め込み酸化膜層から有効な応力が印加されない部分があるが、チップ端のトランジスタを導通させないことで、有効な応力が印加されているトランジスタのみを動作させ、素子の耐圧を向上させることができる。また、素子の(0001)面上、ソース電極やゲート電極のある面の構造は、第1、第2、 第3、第4、第5、第6のいずれの実施例の構造でもよい。

【符号の説明】

【0048】

1、1aドレイン電極

2、2a ドレイン領域

3、3a ドリフト領域

4、4a ベース領域

5、5a、5b、5c、5d、5e、5f、5g、5h、5i、5j、5k ソース領域

6、6a、6b、6c、6d、6e、6f、6g、6h、6i、6j、6k ゲート電極

7、7a ゲート絶縁膜

8、8a、8b、8c、8d、8e、8f、8g、8h、8i、8j、8k埋め込み酸化膜層

9、9a ソース電極

10 ゲート側壁

11 ゲートパッド

12 模擬ゲート電極

【特許請求の範囲】

【請求項1】

4h-SiC基板と、

前記基板表面に対して垂直方向にc軸をもち、4h-SiCを用いて前記基板の表側に形成されたドリフト領域と、

4h-SiCを用いて前記ドリフト領域の表側に形成されたベース領域と、

4h-SiCを用いて前記ベース領域の表側に形成されたソース領域と、

4h-SiCを用いて前記ソース領域の表側に形成されたソース電極と、

前記ベース領域のチャネル領域を覆うトレンチ状のゲート電極と、

前記ゲート電極と前記チャネル領域の境界に形成されたゲート絶縁膜と、

4h-SiCを用いて前記4h-SiC基板の裏側に形成されたドレイン領域と、

前記ドレイン領域の裏側に形成されたドレイン電極と、

前記チャネル領域のc軸に対して垂直な平面上の二軸以上の方向に圧縮応力を印加し、c軸方向に引っ張り応力を印加するトレンチ状の埋め込み酸化膜層とを有することを特徴とする4h-SiC半導体素子。

【請求項2】

請求項1記載の4h-SiC半導体素子において、前記トレンチ状の埋め込み酸化膜層は、前記トレンチ状のゲート電極と同じ深さまで形成されることを特徴とする4h-SiC半導体素子。

【請求項3】

請求項1記載の4h-SiC半導体素子において、前記トレンチ状の埋め込み酸化膜層は、前記トレンチ状のゲート電極の深さよりも浅く形成されることを特徴とする4h-SiC半導体素子。

【請求項4】

請求項1記載の4h-SiC半導体素子において、前記トレンチ状の埋め込み酸化膜層は、前記トレンチ状のゲート電極の深さよりも深く形成されることを特徴とする4h-SiC半導体素子。

【請求項5】

請求項1記載の4h-SiC半導体素子において、前記トレンチ状の埋め込み酸化膜層がc軸に対して垂直な平面上において前記ゲート電極の周囲を囲むように形成されることを特徴とする4h-SiC半導体素子。

【請求項6】

請求項5記載の4h-SiC半導体素子において、前記トレンチ状の埋め込み酸化膜層が中空の六角形または三角形または円または四角形の形状を有し、前記ゲート電極を囲むように形成されることを特徴とする4h-SiC半導体素子。

【請求項7】

請求項1記載の4h-SiC半導体素子において、前記トレンチ状のゲート電極が中空の六角形または三角形または円または四角形の形状を有し、前記ゲート電極の中空層に前記トレンチ状の埋め込み酸化膜層が形成されることを特徴とする4h-SiC半導体素子。

【請求項8】

請求項7記載の4h-SiC半導体素子において、前記トレンチ状の埋め込み酸化膜層が六角形または三角形または円または四角形の形状を有することを特徴とする4h-SiC半導体素子。

【請求項9】

請求項1記載の4h-SiC半導体素子において、前記トレンチ状の埋め込み酸化膜層と前記ゲート電極が交互に縞状に形成され、

前記埋め込み酸化膜層は両側に分岐構造を複数有し、前記複数の分岐構造が前記ゲート電極の周囲を囲む形状を有することを特徴とする4h-SiC半導体素子。

【請求項10】

請求項1に記載の半導体素子が配列された半導体装置において、

ゲート電極パットを有し、

複数の半導体素子のゲート電極がゲート電極パットに配線を介して電気的に導通されていることを特徴とする半導体装置。

【請求項11】

請求項1記載の4h-SiC半導体素子において、

トレンチ状の埋め込み酸化膜層は、熱酸化膜であることを特徴とする4h-SiC半導体素子。

【請求項1】

4h-SiC基板と、

前記基板表面に対して垂直方向にc軸をもち、4h-SiCを用いて前記基板の表側に形成されたドリフト領域と、

4h-SiCを用いて前記ドリフト領域の表側に形成されたベース領域と、

4h-SiCを用いて前記ベース領域の表側に形成されたソース領域と、

4h-SiCを用いて前記ソース領域の表側に形成されたソース電極と、

前記ベース領域のチャネル領域を覆うトレンチ状のゲート電極と、

前記ゲート電極と前記チャネル領域の境界に形成されたゲート絶縁膜と、

4h-SiCを用いて前記4h-SiC基板の裏側に形成されたドレイン領域と、

前記ドレイン領域の裏側に形成されたドレイン電極と、

前記チャネル領域のc軸に対して垂直な平面上の二軸以上の方向に圧縮応力を印加し、c軸方向に引っ張り応力を印加するトレンチ状の埋め込み酸化膜層とを有することを特徴とする4h-SiC半導体素子。

【請求項2】

請求項1記載の4h-SiC半導体素子において、前記トレンチ状の埋め込み酸化膜層は、前記トレンチ状のゲート電極と同じ深さまで形成されることを特徴とする4h-SiC半導体素子。

【請求項3】

請求項1記載の4h-SiC半導体素子において、前記トレンチ状の埋め込み酸化膜層は、前記トレンチ状のゲート電極の深さよりも浅く形成されることを特徴とする4h-SiC半導体素子。

【請求項4】

請求項1記載の4h-SiC半導体素子において、前記トレンチ状の埋め込み酸化膜層は、前記トレンチ状のゲート電極の深さよりも深く形成されることを特徴とする4h-SiC半導体素子。

【請求項5】

請求項1記載の4h-SiC半導体素子において、前記トレンチ状の埋め込み酸化膜層がc軸に対して垂直な平面上において前記ゲート電極の周囲を囲むように形成されることを特徴とする4h-SiC半導体素子。

【請求項6】

請求項5記載の4h-SiC半導体素子において、前記トレンチ状の埋め込み酸化膜層が中空の六角形または三角形または円または四角形の形状を有し、前記ゲート電極を囲むように形成されることを特徴とする4h-SiC半導体素子。

【請求項7】

請求項1記載の4h-SiC半導体素子において、前記トレンチ状のゲート電極が中空の六角形または三角形または円または四角形の形状を有し、前記ゲート電極の中空層に前記トレンチ状の埋め込み酸化膜層が形成されることを特徴とする4h-SiC半導体素子。

【請求項8】

請求項7記載の4h-SiC半導体素子において、前記トレンチ状の埋め込み酸化膜層が六角形または三角形または円または四角形の形状を有することを特徴とする4h-SiC半導体素子。

【請求項9】

請求項1記載の4h-SiC半導体素子において、前記トレンチ状の埋め込み酸化膜層と前記ゲート電極が交互に縞状に形成され、

前記埋め込み酸化膜層は両側に分岐構造を複数有し、前記複数の分岐構造が前記ゲート電極の周囲を囲む形状を有することを特徴とする4h-SiC半導体素子。

【請求項10】

請求項1に記載の半導体素子が配列された半導体装置において、

ゲート電極パットを有し、

複数の半導体素子のゲート電極がゲート電極パットに配線を介して電気的に導通されていることを特徴とする半導体装置。

【請求項11】

請求項1記載の4h-SiC半導体素子において、

トレンチ状の埋め込み酸化膜層は、熱酸化膜であることを特徴とする4h-SiC半導体素子。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図17】

【図26】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図17】

【図26】

【公開番号】特開2013−115158(P2013−115158A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−258432(P2011−258432)

【出願日】平成23年11月28日(2011.11.28)

【出願人】(000005108)株式会社日立製作所 (27,607)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月28日(2011.11.28)

【出願人】(000005108)株式会社日立製作所 (27,607)

[ Back to top ]