A面の伝導性チャネルおよびトレンチ保護用井戸領域を有するトランジスタ

【課題】本発明は、半導体結晶構造のトレンチ内に絶縁された制御コンタクトを有するトランジスタを提供する。

【解決手段】半導体結晶構造のトレンチ内に絶縁された制御コンタクトを有するトランジスタであって、該トランジスタは、該トレンチを画定する一対の半導体メサであって、それぞれは少なくとも1つのp−n接合を備える、メサと、該半導体メサの上面部分に延在し、該トレンチの壁を少なくとも部分的に被覆する埋め込みチャネル層であって、該半導体結晶構造のA面にわたって導電性パスを提供する、埋め込みチャネル層と、該半導体メサと該トレンチの底部の下方との間に延在して、該デバイス内の接合型電界効果抵抗を減少させる電流拡散層と、該メサのうちの少なくとも1つから、該トレンチの深さよりも大きい深さまで該電流拡散層内に延在するドープ型井戸とを備える、トランジスタ。

【解決手段】半導体結晶構造のトレンチ内に絶縁された制御コンタクトを有するトランジスタであって、該トランジスタは、該トレンチを画定する一対の半導体メサであって、それぞれは少なくとも1つのp−n接合を備える、メサと、該半導体メサの上面部分に延在し、該トレンチの壁を少なくとも部分的に被覆する埋め込みチャネル層であって、該半導体結晶構造のA面にわたって導電性パスを提供する、埋め込みチャネル層と、該半導体メサと該トレンチの底部の下方との間に延在して、該デバイス内の接合型電界効果抵抗を減少させる電流拡散層と、該メサのうちの少なくとも1つから、該トレンチの深さよりも大きい深さまで該電流拡散層内に延在するドープ型井戸とを備える、トランジスタ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、特に、伝導性チャネルが半導体のA面で形成される、MOSFETに有用なトランジスタ構造に関する。本発明が取り組む課題には、(i)最適な電流出力のために、オン状態でチャネル抵抗を減少させること、および(ii)デバイス内の逆電圧阻止(reverse voltage blocking)能力を最大化するために、電界集中(field crowding)効果を最小化することが含まれる。

【背景技術】

【0002】

過去20年にわたって、トランジスタ設計は、オン状態で制御された電流フローを達成すると同時に、オフ状態で特定の電圧を阻止する能力を有するように最適化されてきた。炭化ケイ素とIII族窒化物とを含む、よりよい半導体材料の開発は、オン状態(例えば、より高い電流出力)とオフ状態(より少ないリーク電流を有する、より高い電圧阻止)との両方において、トランジスタ性能のより大きな制御を可能にする、トランジスタ設計の驚くべき進歩をもたらしてきた。炭化ケイ素は、様々な結晶構造におけるその電気特性により、特に高い関心が持たれてきた。

【0003】

炭化ケイ素の結晶構造は、使用される層の要素構成により説明される場合が多い。炭化ケイ素基板の断面は、シリコン原子の層の上に直接、炭素原子の層、もしくはその逆を示す。シリコン層は、その上にデバイスを形成するために研磨および使用される場合が多く、それは、シリコン面として知られる。炭素層が曝露される場合は、それは炭素面として知られる。非特許文献1を参照されたい。

【0004】

炭化ケイ素結晶の配列の軸はまた、半導体デバイスを形成するための配向の選択において重要な役割を果たす。従来、六方晶系構造に対して、a1、a2、a3、およびcの4つの主軸が、一般的に使用される。aベクトルのすべては、同一の平面(「a平面」)にあり、cベクトルは、a平面に垂直であるc平面にある。同非特許文献1。

【0005】

以前の研究者たちは、得られたデバイスにおける様々な性能特性を実現するために、炭化ケイ素結晶の異なる平面または面を使用しようと試みてきた。例えば、Yanoらは、c面上に形成されるMOSFETのチャネル移動度特性と、4H−SiC基板のa面上の反転層移動度に関する改善された結果とを開示している。Yano、Kimoto、Matsunami、Asano、およびSugawara「High Channel Mobility in Inversion Layers of 4H−SiC MOSFETs by Utilizing

【0006】

【数1】

Face」、IEEE Electron Device Letters、Vol.20、No.12(1999年12月)、p.611−613を参照されたい。

【0007】

Yanoらは、同一の基板上で互いに垂直の電流を有する、2種類のMOSFETを形成した。

【0008】

【数2】

面上に形成されるMOSFETに対するドレイン電流は、実質的に改善され、炭化ケイ素のa面

【0009】

【数3】

を使用することにより、チャネル移動度の著しい増加を示した。しかしながら、Yanoのデバイスは、比較的低い臨界電界強度を有し、所望よりも低いゲート電圧において逆バイアスの下で伝導を行うことから、Yanoの設計は、垂直型パワーデバイスにおいては好ましくない。そのうえ調整される付加パラメータなしで、a面上のMOSFETを改良する唯一の技術は、パワーMOSFETにおける性能の最適化において、最適な解決策であることを証明していない。

【0010】

チャネル抵抗が、特に低電圧(<2kV)の炭化ケイ素MOSFETに対して、MOSFETの全オン抵抗のかなりの部分を作り出すことから、パワーMOSFET内の電流フローを最大化するためのこれまでの努力は、炭化ケイ素デバイスのチャネル抵抗に焦点を当ててきた。チャネル抵抗を減少させる方法は、(1)チャネル移動度を改善すること、(2)デバイスセルピッチを減少すること、および(3)チャネル長さを減少することに集中してきた。研究努力は、これらの方法を広範囲に研究してきたが、従来技術のDMOSFET(二重拡散型金属酸化物半導体FET)と、UMOSFET(トレンチゲート型金属酸化物半導体FET)とは、チャネル移動度の望ましい増加の実現において、わずかな改善のみを示してきた。例えば、既知のUMOSFETは、伝導性チャネルにおけるキャリア密度の増加を示すが、これらの同一のデバイスは、逆バイアスの下で、トレンチゲートの角部における電界集中の損害をこうむる。

【0011】

図1および図4は、従来技術のDMOSFET(5)と従来技術のUMOSFET(28)とをそれぞれ示す。従来のDMOSFET(5)は、半導体(18)上に配設される、ソースと、ゲートと、ドレインコンタクト(10、11、12)とを含み、ゲートコンタクト(11)は、ゲート領域を絶縁する酸化物層(15)の上にある。DMOSFET(5)は、約0.5ミクロンの深さまで半導体内に注入され、約1e20cm−3までドープされる、p+型井戸(19)を含む。約1e20cm−3までドープされるn+ソース領域(20)は、p+井戸(19)に隣接し、p+井戸(19)と埋め込みチャネル(21)との間に配設される。埋め込みチャネル(21)は、ソース(20)と、p+井戸(19)と、活性領域、すなわちJFET領域(23)の間の半導体(18)との部分に延在する。DMOSFET(5)の埋め込みチャネル(21)、JFET領域(23)および支持ドリフト領域(24)は、約1e16cm−3までドープされる。典型的な従来技術のDMOSFETでは、製造プロセスが、層の成長中にドーピングの変わりにイオン注入を使用することによって、チャネル表面を制御する。DMOSFETにおいて、イオン注入を正確に実現することは困難であり、得られたデバイスは、チャネル移動度が制限される。

【0012】

図1のDMOSFET(5)のチャネル抵抗は、図2の順方向電圧対電流曲線に説明される。そこに示すように、図1のDMOSFET(5)は、40cm2/Vsのチャネル移動度と、約4.62mΩ・cm2の特定のオン抵抗とを実現する。それに応じて、図3は、図1の従来技術のDMOSFET(5)の順方向電流分布を示す。これらの値は、約25から50cm2/Vsの典型的なチャネル移動度を達成する、既知のDMOSFETの範囲内である。図3に示すように、デバイスのドリフト領域(24)内の電流分布は、ゲートにより近い上部(23)内の最適な電流よりもはるかに少ない。図3は、電流が、デバイスを介するドレイン(12)への最大フローに対して所望されるようには、拡散していないことを示す。

【0013】

図4の従来技術のUMOSFET(28)は、同様の電流制限を経験している。図面に説明するように、UMOSFET(28)は、スタンダードソース(30)と、ゲート(31)と、ドレイン(32)とを含み、トレンチ(36)の内側をおおう酸化物層(33)の上にあるゲート(31)を有する。UMOSFET(28)の埋め込みチャネル(38)は、埋め込みチャネル(38)が、p−n接合のエピタキシャル層(40、41)と、酸化物層(33)との間にあるように、ソース(30)とトレンチ(36)の下方とにわたって延在する。従来技術のUMOSFETに関する問題は、トレンチ角部(42)が、トレンチ角部における電界の顕著な集中を示し、ドリフト領域(43)と基板(44)とを介する、ドレイン(32)への下方の電流フローを阻止することである。電界集中はまた、逆バイアス動作の間、より低い持続(sustained)ゲート電圧をもたらす。

【0014】

図4のUMOSFETはまた、適切なゲートの配置および動作のために、2ミクロンよりも大きいトレンチを必要とする。反応性イオンエッチングが、UMOSFET内でトレンチを形成するための最適な方法である場合が多いと仮定すると、トレンチ壁は、製造プロセスにおいて、伝導性チャネルが圧迫される非常に重大な損傷を受ける。炭化ケイ素を反応性イオンエッチングにさらす場合に、一定の結果を得ることは困難であり、得られたデバイスは信頼性がない。エッチングに起因する損傷は、絶縁目的でその上に形成される酸化物の質を劣化させる。これらの要因は、従来技術のUMOSFET内で結合して、順方向の伝導に対して最大30ボルトまでのオン電圧を要求する。

【0015】

図1および図4の従来技術のDMOSFETとUMOSFETデバイスとは、逆バイアス動作において入射電圧(incident voltage)を阻止する能力とともに、オン状態における最大電流フローを増加させるトランジスタ設計への修正に対する共通の必要性を図示する。

【0016】

特許文献1(Miyajima 1999年)は、デバイスに対する閾値電圧と阻止特性とを制御すると同時に、チャネル内の電流を増加させることを目的に改良された、従来の炭化ケイ素MOSFETの別の実施例を示す。Miyajimaの特許文献1の特許は、チャネル層のために、ゲートトレンチ壁に沿って炭化ケイ素の垂直な層を利用する。垂直チャネル層は、非常に薄く、約1000から5000オングストロームである。しかしながら、Miyajimaの特許文献1の設計は、トレンチの縁部での電流集中の問題をなおも経験している。さらに、Miyajimaは、チャネル移動度を増大させるための、炭化ケイ素結晶のa面の使用については一切言及していない。

【0017】

特許文献2(Baliga 2002年)は、同時に大きい電圧を支持し、電流飽和モードで動作することに関わる同じ問題のいくつかに取り組んでいる。Baligaの特許文献2の特許出願は、深い井戸の拡張(P+注入)を使用し、トレンチ角部での電流集中をほぼ間違いなく軽減し得る。しかしながら、これらの井戸拡張の以前の研究は、深い井戸が、典型的に高いJFET抵抗をもたらし、それによって、より深いトレンチを必要とすることを示した。Baligaは、実際に、井戸に隣接する領域を空乏化するために、深いP+井戸を使用することにより、JFET効果を促進している。次に、Baligaは、ドレイン領域が電流飽和モードである間に、電界効果トランジスタとしてデバイスの空乏領域を操作するために、JFET効果を使用している。ドレインへの電流フローを抑制するJFET領域の問題は、Baligaのデバイスにおいて、なおも明白である。

【先行技術文献】

【特許文献】

【0018】

【特許文献1】米国特許第5,976,936号明細書

【特許文献2】米国特許出願公開第2002/0185679号明細書

【非特許文献】

【0019】

【非特許文献1】Zetterling、Carl−Mikael、「Process Technology for Silicon Carbide Devices」、Institute of Electrical Engineers(2002年)、p.3

【発明の概要】

【発明が解決しようとする課題】

【0020】

オン状態における高電流出力と、逆バイアスの下でのゲートトレンチにおける低減された電流集中とを有するパワートランジスタを実現するための従来の努力は、概して不成功であった。従来技術は、ゲートトレンチ側壁に沿ったチャネル抵抗を減少させることと、逆バイアスの下で半導体デバイスにわたって電界を拡散するためにデバイスの容量を増加させることとの、競合する要因に取り組むことに失敗してきた。

【課題を解決するための手段】

【0021】

(本発明の簡単な概要)

本発明は、オン状態での順方向に伝導中、ドリフト領域(55)内のJFET効果を最小化すると同時に、炭化ケイ素体(65)のA面に沿った電流を最適化する、新しいトランジスタ構造(50)である。本発明は、トレンチゲート型デバイス内のゲート角部領域(80)を保護する、高濃度ドープ型井戸領域(77)の追加により、高電圧阻止能力をさらに示す。

【0022】

ゲートコンタクト(61)のための、半導体内のエッチングされたトレンチ(56)を利用するトランジスタデバイスに対して、トレンチ側壁に沿った伝導は、半導体、好ましくは炭化ケイ素のA面にわたって導電性パス(72)を提供することにより、増大され得る。本発明によると、トランジスタは、トレンチ(56)を画定する半導体メサ(65)の一部に延在する、埋め込みチャネル層(72)に加えて、トレンチ側壁に沿ったA面の伝導を効果的に使用する。ドープ型井戸(77)は、メサの少なくとも1つから、トレンチ(56)の深さよりも大きい、電流拡散層すなわちドリフト領域(55)内の深さまで延在する。電流拡散ドリフト層(55)は、オン状態で接合抵抗を減少させるために、トレンチ(56)の底部の下にある半導体メサ(65)間に延在する。

【0023】

別の実施形態では、半導体メサ(65)は、その間にトレンチ(56)を画定し、各メサ(65)は、それぞれのメサにおけるp−n接合の幅を画定する。埋め込みチャネル層(72)は、デバイスの上面に隣接し、炭化ケイ素のA面に沿った伝導を利用する、AMOSFET(50)を形成する。埋め込みチャネル層(72)は、トレンチ壁にわたって下方に延在する。例えば、P+伝導性までドープされる深い井戸領域(77)は、AMOSFET(50)の頂部から、トレンチ(56)よりも大きい深さまで、下方に延在する。深いP+井戸(77)は、逆バイアス動作の間、トレンチ角部(80)を保護し、デバイスが、より高い阻止電圧を実現することを可能にする。ドープされた緩衝層(73)は、各垂直トレンチ壁から深い井戸領域に向かって、デバイスの本体にわたって延在する。

【0024】

本発明は、ゲートコンタクト(61)を介して伝導を制御するために、炭化ケイ素のA面を利用する。炭化ケイ素のA面は、半導体にわたって相互コンダクタンスを増加させることにより、チャネル伝導性を増大させる。反対の導電型の緩衝領域(73)に近接する深い井戸領域(77)は、逆バイアス動作の間、トレンチ角部(80)を保護し、それによりデバイスが、より高いゲート阻止電圧に耐えることを可能にする。

【0025】

本明細書において、本発明に従ったAMOSFETを形成するための方法は、半導体(65)内に第1の導電型のドープ型井戸領域(77)を注入するステップと、次に、第1のエピタキシャル層(68)が、ドープ型井戸領域(77)の少なくとも一部を被覆するように、半導体上で、第1の導電型の第1のエピタキシャル層(68)を成長させるステップを含む。次に、本発明は、第1のエピタキシャル層(68)上に、第2の導電型の第2のエピタキシャル層(69)を成長させ、次に、一対のメサを形成するために、エピタキシャル層と該半導体とをエッチングすることにより、pn接合を形成するステップを含む。メサは、その間にトレンチ(56)を画定し、トレンチは、該ドープ型井戸領域(77)の深さよりも小さい、半導体への深さを有する。該第2のエピタキシャル層(68)またはソース領域の一部にわたって、埋め込みチャネル層(72)を成長させ、該メサ間のトレンチへと埋め込みチャネル層(72)を延在させることにより、方法は、改善された性能特性を有するAMOSFETを実現する。

【0026】

エピタキシャル層(68、69)を個々に成長させる代わりに、方法の異なる実施形態では、該方法は、イオン注入による異なる導電型領域の形成を含む。

【0027】

例えば、本発明は、以下の項目を提供する。

(項目1a)

半導体結晶構造のトレンチ内に絶縁された制御コンタクトを有するトランジスタであって、該トランジスタは、

該トレンチを画定する一対の半導体メサであって、それぞれは少なくとも1つのp−n接合を備える、メサと、

該半導体メサの上面部分に延在し、該トレンチの壁を少なくとも部分的に被覆する埋め込みチャネル層であって、該半導体結晶構造のA面にわたって導電性パスを提供する、埋め込みチャネル層と、

該半導体メサと該トレンチの下方との間に延在して、該トランジスタ内の接合型電界効果抵抗を減少させる電流拡散層と、

該メサのうちの少なくとも1つから、該トレンチの深さよりも大きい深さまで該電流拡散層内に延在するドープ型井戸と

を備える、トランジスタ。

(項目2a)

上記トランジスタは、AMOSFETである、項目1aに記載のトランジスタ。

(項目3a)

上記トランジスタは、絶縁ゲート型バイポーラトランジスタである、項目1aに記載のトランジスタ。

(項目4a)

上記トランジスタは、金属酸化物半導体制御型サイリスタである、項目1aに記載のトランジスタ。

(項目5a)

上記ドープ型井戸は、約1×1019cm−3までドープされるP+型井戸である、項目1aに記載のトランジスタ。

(項目6a)

上記メサ内の上記p−n接合のうちの1つは、

上記埋め込みチャネル層の下および上記トレンチと上記P+井戸との間に配設されるP+型半導体エピタキシャル層と、

該トレンチと該P+井戸との間の該P+エピタキシャル層の上にあるN+型ソース領域と

を備える、項目5aに記載のトランジスタ。

(項目7a)

上記P+エピタキシャル層は、約5×1017cm−3までドープされ、上記N+ソース領域は、約1×1020cm−3までドープされる、項目6aに記載のトランジスタ。

(項目8a)

上記ドープ型井戸から上記トレンチまで延在するエピタキシャル緩衝層をさらに備える、項目6aに記載のトランジスタ。

(項目9a)

上記P+型エピタキシャル層と上記緩衝層と上記P+型井戸との間の上記p−n接合は、結合するように十分にドープされ、それによってオフ状態で上記トレンチの角部を保護する、項目8aに記載のトランジスタ。

(項目10a)

第1および第2の半導体メサ間の、ゲートコンタクトを組み込むためのトレンチの壁を画定するAMOSFETであって、該トレンチは、半導体のA面を曝露させ、該AMOSFETは、

該トレンチに隣接する第1の導電型の第1の半導体エピタキシャル層と、

該第1の半導体エピタキシャル層上にある第2の導電型の第2の半導体エピタキシャル層と、

該AMOSFETの第1の表面に隣接する埋め込みチャネル層であって、該第2の半導体エピタキシャル層の上部に延在し、トレンチ壁に沿って続く、埋め込みチャネル層と、

該第1のエピタキシャル層から該半導体へと下方に、該トレンチよりも大きい深さまで延在する該第1の導電型の井戸領域と

を備える、AMOSFET。

(項目11a)

上記第1の導電型は、P+であり、上記第2の導電型は、N+である、項目10aに記載のAMOSFET。

(項目12a)

上記半導体は、炭化ケイ素を含む、項目10aに記載のAMOSFET。

(項目13a)

上記埋め込みチャネル層は、上記第1のメサのN+ソース領域から上記第2のメサ内のN+ソース領域まで延在し、それによって上記トレンチ壁を被覆する、項目10aに記載のAMOSFET。

(項目14a)

上記井戸領域と上記トレンチとの間にN+型緩衝層をさらに備える、項目13aに記載のAMOSFET。

(項目15a)

半導体内のゲートトレンチの壁を画定する第1および第2の半導体メサ内で電気伝導を制御するためのMOSFETであって、該MOSFETは、

該トレンチに隣接するP+型半導体エピタキシャル層と、

該P+エピタキシャル層上にあるN+型ソース領域と、

該MOSFETの第1の表面に隣接する埋め込みチャネル層であって、該N+型ソース領域の上部に延在し、該トレンチ壁に沿って続く、埋め込みチャネル層と、

該P+エピタキシャル層から該半導体へと下方に、該ゲートトレンチよりも大きい深さまで延在するP+型井戸と

を備え、

該MOSFETは、該半導体のA面に沿って該埋め込みチャネル層内で電気伝導を制御する、

MOSFET。

(項目16a)

上記半導体は、炭化ケイ素を含む、項目15aに記載のMOSFET。

(項目17a)

上記埋め込みチャネル層は、上記第1のメサ内のN+ソース領域から上記第2のメサ内のN+ソース領域まで延在し、それにより上記トレンチ壁を被覆する、項目15aに記載のMOSFET。

(項目18a)

上記P+型井戸と上記ゲートトレンチとの間にN+型緩衝層をさらに備える、項目15aに記載のMOSFET。

(項目19a)

上記N+型緩衝層は、上記埋め込みチャネル層の深さと略等しい深さまで延在する、項目18aに記載のMOSFET。

(項目20a)

上記ゲートトレンチと隣接する上記P+型井戸との下に、N+型ドリフト層をさらに備え、該ドリフト層は、上記第1の表面の反対側にある上記MOSFETの表面に向かって延在する、項目15aに記載のMOSFET。

(項目21a)

上記N+型ドリフト層は、該ドリフト層の最高濃度ドープ領域が上記P+井戸に隣接するように、上記反対側のMOSFET表面から上記第1のMOSFET表面に向かって増加するドーピング濃度を備える、項目20aに記載のMOSFET。

(項目22a)

上記P+井戸の反対側にある上記ドリフト層に隣接する半導体基板を備える、項目20aに記載のMOSFET。

(項目23a)

上記ゲートトレンチは、深さが約2ミクロン未満である、項目15aに記載のMOSFET。

(項目24a)

上記ゲートトレンチは、深さが約1ミクロン未満である、項目15aに記載のMOSFET。

(項目25a)

上記ゲートトレンチは、深さが約0.8ミクロンであり、上記P+井戸は、深さが約1.3ミクロンである、項目15aに記載のMOSFET。

(項目26a)

上記N+ソース領域と上記P+エピタキシャル層とは、略同一固定電位にある、項目15aに記載のMOSFET。

(項目27a)

トランジスタを形成する方法であって、

半導体内に第1の導電型のドープ型井戸領域を注入するステップと、

該半導体上に該第1の導電型の第1のエピタキシャル層を成長させることにより、該第1のエピタキシャル層は、該ドープ型井戸領域の少なくとも一部分を被覆するステップと、

該第1のエピタキシャル層上に第2の導電型の第2のエピタキシャル層を成長させるステップと、

該半導体内に一対のメサを形成するために、該エピタキシャル層と該半導体とをエッチングするステップであって、該メサは、その間にトレンチを画定し、該トレンチは、該ドープ型井戸領域の深さよりも小さい該半導体への深さを有する、ステップと、

該第2のエピタキシャル層の一部分にわたって埋め込みチャネル層を成長させ、該メサ間の該トレンチ内に該埋め込みチャネル層を延在させるステップと

を包含する、方法。

(項目28a)

上記チャネル層は、炭化ケイ素から形成され、該炭化ケイ素のA面は、ソースからドレインに伝導性パスを提供する、項目27aに記載の方法。

(項目29a)

上記エッチングするステップの前に上記半導体上にN+型緩衝層を成長させ、次いで上記エピタキシャル層のすべてと、下にある該半導体の一部分とをエッチングするステップをさらに包含する、項目27aに記載の方法。

(項目30a)

トランジスタを形成するステップであって、

半導体内に第1の導電型のドープ型井戸領域を注入するステップと、

該半導体上に該第1の導電型の第1のエピタキシャル層を成長させることにより、該第1のエピタキシャル層は、該ドープ型井戸領域の少なくとも一部分を被覆するステップと、

該第1のエピタキシャル層の上部領域を第2の導電型に変換するステップと、

該半導体内に一対のメサを形成するために、該エピタキシャル層と該半導体とをエッチングするステップであって、該メサは、その間にトレンチを画定し、該トレンチは、該ドープ型井戸領域の深さよりも小さい該半導体への深さを有する、ステップと、

該エピタキシャル層の一部分にわたって埋め込みチャネル層を成長させ、該メサ間の該トレンチ内に該埋め込みチャネル層を延在させるステップと

を包含する、方法。

(項目1b)

半導体結晶構造のトレンチ内に絶縁された制御コンタクトを有するトランジスタであって、該トランジスタは、

該トレンチを画定する一対の半導体メサであって、それぞれは少なくとも1つのp−n接合を備える、メサと、

該半導体メサの上面部分に延在し、該トレンチの壁を少なくとも部分的に被覆する埋め込みチャネル層であって、該半導体結晶構造のA面にわたって導電性パスを提供する、埋め込みチャネル層と、

該半導体メサと該トレンチの底部の下方との間に延在して、該デバイス内の接合型電界効果抵抗を減少させる電流拡散層と、

該メサのうちの少なくとも1つから、該トレンチの深さよりも大きい深さまで該電流拡散層内に延在するドープ型井戸と

を備える、トランジスタ。

(項目2b)

上記トランジスタは、AMOSFETである、項目1bに記載のトランジスタ。

(項目3b)

上記トランジスタは、絶縁ゲート型バイポーラトランジスタである、項目1bに記載のトランジスタ。

(項目4b)

上記トランジスタは、金属酸化物半導体制御型サイリスタである、項目1bに記載のトランジスタ。

(項目5b)

上記ドープ型井戸は、約1×1019cm−3までドープされるP+型井戸である、項目1bに記載のトランジスタ。

(項目6b)

上記メサ内の上記p−n接合のうちの1つは、

上記埋め込みチャネルの下および上記トレンチと上記P+井戸との間に配設されるP+型半導体エピタキシャル層と、

該トレンチと該P+井戸との間の該P+エピタキシャル層の上にあるN+型ソース領域と

を備える、項目1bに記載のトランジスタ。

(項目7b)

上記P+エピタキシャル層は、約5e17cm−3までドープされ、上記N+ソース領域は、約1e20cm−3までドープされる、項目6bに記載のトランジスタ。

(項目8b)

上記ドープ型井戸から上記トレンチまで延在するエピタキシャル緩衝層をさらに備える、項目1bに記載のトランジスタ。

(項目9b)

上記P+型エピタキシャル層と上記N型緩衝層と上記P+型井戸との間の上記p−n接合は、結合するように十分にドープされ、それによってオフ状態で上記トレンチの角部を保護する、項目1bに記載のトランジスタ。

(項目10b)

半導体メサ間のトレンチを画定するAMOSFETであって、該トレンチは、半導体のA面を曝露させ、該AMOSFETは、

該トレンチに隣接する第1の導電型の第1の半導体エピタキシャル層と、

該第1の半導体エピタキシャル層上にある第2の導電型の第2の半導体エピタキシャル層と、

該AMOSFETの第1の表面に隣接する埋め込みチャネル層であって、該第2の半導体エピタキシャル層の上部に延在し、該トレンチの壁に沿って続く、埋め込みチャネル層と、

該第1のエピタキシャル層から該半導体へと下方に、該ゲートトレンチよりも大きい深さまで延在する該第1の導電型の井戸領域と

を備える、AMOSFET。

(項目11b)

上記第1の導電型は、P+であり、上記第2の導電型は、N+である、項目10bに記載のAMOSFET。

(項目12b)

上記半導体は、炭化ケイ素を含む、項目10bに記載のAMOSFET。

(項目13b)

上記埋め込みチャネル層は、1つのメサのN+ソース領域から隣接するメサのN+ソース領域まで延在し、それによって上記トレンチの壁を被覆する、項目10bに記載のAMOSFET。

(項目14b)

上記P+型井戸と上記ゲートトレンチとの間にN+型緩衝層をさらに備える、項目13bに記載のAMOSFET。

(項目15b)

半導体内のゲートトレンチを画定する一対の半導体メサ内で電気伝導を制御するためのMOSFETであって、該MOSFETは、

該トレンチに隣接するP+型半導体エピタキシャル層と、

該P+エピタキシャル層上にあるN+型ソース領域と、

該MOSFETの第1の表面に隣接する埋め込みチャネル層であって、該N+型ソース領域の上部に延在し、該トレンチの壁に沿って続く、埋め込みチャネル層と、

該P+エピタキシャル層から該半導体へと下方に、該ゲートトレンチよりも大きい深さまで延在するP+型井戸と

を備え、

該MOSFETは、該半導体のA面に沿って該埋め込みチャネル内で電気伝導を制御する、

MOSFET。

(項目16b)

上記半導体は、炭化ケイ素を含む、項目15bに記載のMOSFET。

(項目17b)

上記埋め込みチャネル層は、1つのメサの上記N+ソース領域から隣接するメサの上記N+ソース領域まで延在し、それにより上記トレンチの壁を被覆する、項目15bに記載のMOSFET。

(項目18b)

上記P+型井戸と上記ゲートトレンチとの間にN+型緩衝層をさらに備える、項目15bに記載のMOSFET。

(項目19b)

上記N+型緩衝層は、上記埋め込みチャネル層の深さと略等しい深さまで延在する、項目18bに記載のMOSFET。

(項目20b)

上記ゲートトレンチと隣接する上記P+型井戸との下に、N+型ドリフト層をさらに備え、該ドリフト層は、上記第1の表面の反対側にある上記MOSFETの表面に向かって延在する、項目15bに記載のMOSFET。

(項目21b)

上記N+型ドリフト層は、該ドリフト層の最高濃度ドープ領域が上記P+井戸に隣接するように、上記反対側のMOSFET表面から上記第1のMOSFET表面に向かって増加するドーピング濃度を備える、項目20bに記載のMOSFET。

(項目22b)

上記P+井戸の反対側にある上記ドリフト層に隣接する半導体基板を備える、項目20bに記載のMOSFET。

(項目23b)

上記ゲートトレンチは、深さが約2ミクロン未満である、項目15bに記載のMOSFET。

(項目24b)

上記ゲートトレンチは、深さが約1ミクロン未満である、項目15bに記載のMOSFET。

(項目25b)

上記ゲートトレンチは、深さが約0.8ミクロンであり、上記P+井戸は、深さが約1.3ミクロンである、項目15bに記載のMOSFET。

(項目26b)

上記N+ソース領域と上記P+エピタキシャル層とは、略同一固定電位にある、項目15bに記載のMOSFET。

(項目27b)

トランジスタを形成する方法であって、

半導体内に第1の導電型のドープ型井戸領域を注入するステップと、

該半導体上に該第1の導電型の第1のエピタキシャル層を成長させることにより、該第1のエピタキシャル層は、該ドープ型井戸領域の少なくとも一部分を被覆するステップと、

該第1のエピタキシャル層上に第2の導電型の第2のエピタキシャル層を成長させるステップと、

該半導体内に一対のメサを形成するために、該エピタキシャル層と該半導体とをエッチングするステップであって、該メサは、その間にトレンチを画定し、該トレンチは、該ドープ型井戸領域の深さよりも小さい該半導体への深さを有する、ステップと、

該第2のエピタキシャル層の一部分にわたって埋め込みチャネル層を成長させ、該メサ間の該トレンチ内に該埋め込みチャネル層を延在させるステップと

を包含する、方法。

(項目28b)

上記チャネル層は、炭化ケイ素から形成され、該炭化ケイ素のa面は、ソースからドレインに伝導性パスを提供する、項目27bに記載の方法。

(項目29b)

上記エッチングするステップの前に上記半導体上にN+型緩衝層を成長させ、次いで上記エピタキシャル層のすべてと、下にある該半導体の一部分とをエッチングするステップをさらに包含する、項目27bに記載の方法。

(項目30b)

トランジスタを形成するステップであって、

半導体内に第1の導電型のドープ型井戸領域を注入するステップと、

該半導体上に該第1の導電型の第1のエピタキシャル層を成長させることにより、該第1のエピタキシャル層は、該ドープ型井戸領域の少なくとも一部分を被覆するステップと、

該第1のエピタキシャル層の上部領域を第2の導電型に変換するステップと、

該半導体内に一対のメサを形成するために、該エピタキシャル層と該半導体とをエッチングするステップであって、該メサは、その間にトレンチを画定し、該トレンチは、該ドープ型井戸領域の深さよりも小さい該半導体への深さを有する、ステップと、

該エピタキシャル層の一部分にわたって埋め込みチャネル層を成長させ、該メサ間の該トレンチ内に該埋め込みチャネル層を延在させるステップと

を包含する、方法。

【0028】

(摘要)

トランジスタ構造は、オン状態での順方向に伝導中、ドリフト領域内のJFET効果を最小化するAMOSFETを形成するために、炭化ケイ素体のA面に沿って電流を最適化する。該AMOSFETは、トレンチゲート型デバイス内のゲート角部領域を保護する高濃度ドープ型井戸領域の追加により、高電圧阻止能力をさらに示す。該AMOSFETは、該トレンチを画定する半導体メサの一部に延在する埋め込みチャネル層に加えて、トレンチ側壁に沿って該A面の伝導を使用する。ドープ型井戸は、該メサの少なくとも1つから、該トレンチの深さよりも大きい深さまでの電流拡散層内に延在する。電流拡散層は、オン状態で接合抵抗を減少させるために、該トレンチの底部の下にある該半導体メサ間に延在する。該トレンチと該深い井戸との間の緩衝層は、該トレンチ角部における電界集中からの保護を提供する。

【図面の簡単な説明】

【0029】

【図1】図1は、埋め込みチャネルを有する、従来技術の二重拡散型電界効果トランジスタ(DMOSFET)である。

【図2】図2は、図1の従来技術のDMOSFETに関する、順方向IV曲線のグラフ表示である。

【図3】図3は、図1の従来技術のDMOSFETの、順方向電流分布のグラフ表示である。

【図4】図4は、垂直トレンチ壁に沿って伝導性チャネルを有する、従来技術のトレンチゲート型電界効果トランジスタ(UMOSFET)である。

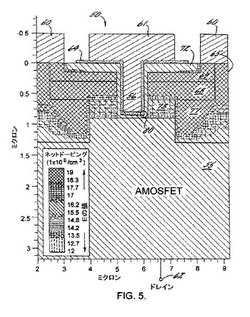

【図5】図5は、本発明に従った、炭化ケイ素結晶構造のa面上に形成される、金属酸化物半導体(MOSFET)である。

【図6】図6は、本発明に従った、炭化ケイ素のa面上に形成される、MOSFETに関する順方向電流分布のグラフ図である。

【図7】図7は、本発明に従った、炭化ケイ素のa面上に形成される、MOSFETに関する順方向電流対電圧曲線のグラフ図である。

【図8a】図8aは、1200Vの阻止電圧での、DMOSFETの電界強度分布を示すグラフである。

【図8b】図8bは、1200Vの阻止電圧での、UMOSFETの電界強度分布を示すグラフである。

【図8c】図8cは、1200Vの阻止電圧での、本発明に従ったAMOSFETの電界強度分布を示すグラフである。

【図9a】図9aは、従来技術のDMOSFETの酸化物層内の、電界強度の最大深さを示すグラフである。

【図9b】図9bは、従来技術のUMOSFETの酸化物層内の、電界強度の最大深さを示すグラフである。

【図9c】図9cは、本発明に従ったAMOSFETの酸化物層内の、電界強度の最大深さを示すグラフである。

【発明を実施するための形態】

【0030】

(詳細な説明)

本発明のMOSFETは、チャネル移動度の増加(例えば、従来技術のDMOSFETに対して、100cm2/Vs以下になるが、AMOSFETに対しては、最大200cm2/Vsになる)のために、炭化ケイ素結晶エピタキシャル層のA面上に、伝導性チャネルを含む。図5は、新しいAMOSFET(50)の構造を説明する。ドリフト領域(55)すなわち電流拡散層は、ソース領域(60)からドリフト領域(55)を通じてドレイン(62)まで流動する電流を有する、AMOSFET(50)の活性領域を形成するエピタキシャル層を支持する。概して、AMOSFET(50)は、半導体結晶構造(58)のトレンチ(56)内に、絶縁ゲート(61)、すなわち制御コンタクトを有するトランジスタである。トレンチ(56)は、一対の半導体メサ(65)を画定し、それぞれは、その中にpn接合を形成するp+型層(68)とn+型層(69)とを含む。p+型層(68)は、埋め込みチャネル(72)の下、およびトレンチ(56)とp+ドープ型井戸(77)との間に配設される、エピタキシャル層である。n+型層(69)は、伝導目的のためのソース領域である。n+層(69)は、p+層(68)の頂部と、埋め込みチャネル(72)の下に隣接して位置する。ドリフト領域(55)は、AMOSFETの上述の活性領域を支持する。好ましい実施形態では、ドリフト領域(55)は、基板上にあるN+エピタキシャル層であり、トレンチの底部と、ゲートコンタクトの反対側にあるAMOSFETの表面との間に延在する。AMOSFETは、ドレイン(62)に近接する底部MOSFET表面から、ソース領域(69)に近接する上部MOSFET表面に向かって増加する、ドリフト領域(55)内のドーピング濃度を利用する等、より高度なドーピング技術を含み得る。本実施形態では、ドリフト層の最高濃度ドープ領域は、該P+井戸(77)に隣接する。

【0031】

ドレインコンタクト(62)は、デバイスの底部に取り付けられ、ソースからドレインへの、ドリフト領域(55)をわたった伝導を可能にする。この伝導は、トレンチ(56)内のゲート(61)上の電圧により制御される。チャネル領域(72)が、適切な抵抗とチャネル長さを有する限り、ある特定閾値以上のゲート上の正電圧は、ソースからドレインへの制御された伝導を可能にする。

【0032】

本発明に従ったAMOSFETは、ソースと、ゲートと、ドレインコンタクト(60、61、62)とを含む、機能的なトランジスタ特性を含み、ゲートコンタクト(61)は、トレンチ(56)内の絶縁酸化物層(64)の上に形成される。ソースコンタクト(60)は、AMOSFET(50)の第1の表面上に位置し、p+ドープ型井戸(77)とn+ソース領域(69)との上部に延在する。

【0033】

好ましい実施形態では、緩衝層(73)は、p+井戸領域(77)から、トレンチ(56)の底部に向かって延在し、酸化物層(64)とゲートコンタクト(61)とは、トレンチ(56)内にある。緩衝層(73)が、トレンチ角部(80)に隣接して適切に配設されると、p+エピタキシャル層(68)と、n型緩衝層(73)と、p+型ドープ型井戸(77)との間のp−n接合は、結合するように十分にドープされ、それにより、オフまたは非伝導状態でトレンチ角部を保護する。これは、AMOSFET(50)が、ドレイン(62)へのリーク電流、またはデバイスの完全な破壊さえもなく、ゲート(61)上のより高い電圧に耐えることを可能にする。好ましい実施形態では、N+型緩衝層(73)は、埋め込みチャネル層(72)とほぼ同じ深さまで延在する。

【0034】

一実施形態では、各層内のドーピングは十分であり、その上に幅広い電圧レベルを有するゲート(61)により制御される、オン状態での最適な電流を提供する。例えば、図5の実施例では、p+エピタキシャル層(68)は、約5e17cm−3までドープされ、n+ソース領域は、約1e20cm−3までドープされる。

【0035】

本発明のAMOSFET(50)は、ゲート(61)電圧に応じて、ソース(60)からドレイン(62)までの高い電流処理能力を提供するために特に好適な、チャネル層(72)を有する。埋め込みチャネル層(72)が、エピタキシャルp−n接合層(68、69)を形成する半導体結晶構造のA面、

【0036】

【数4】

面にわたって、導電性パスを提供するように、埋め込みチャネル層(72)は、半導体メサ(65)の上面の一部に延在し、底壁を含むトレンチ(56)の外壁を少なくとも部分的に被覆する。

【0037】

ドリフトまたは電流拡散層(55)は、デバイス内の接合型電界効果抵抗を減少させるために、トレンチ(56)の底部の下にある半導体メサ(65)間に延在する。好ましい一実施形態では、ドリフト層(55)は、半導体メサ(65)とゲートトレンチ(61)との幅にわたって延在する。ドリフト層(55)は、ドレインコンタクト(62)が取り付けられた半導体基板上に設置され得る。少なくとも1つのドープ型井戸(77)は、メサ(65)の少なくとも1つ内に、トレンチ(56)の深さよりも大きいドリフト領域(55)内の深さまで延在する。

【0038】

図5のデバイスのドーピングレベルは、図面内の陰影により図示される。本発明のAMOSFETが、あらゆる領域に対するあらゆる特定のドーピングレベルに制限されない一方で、ドーピング範囲は、性能、特にソースからドレインへの電流フローに影響を与える。図5のデバイスにより図示される一実施例では、ドープ型井戸(77)は、約1e19cm−3のドーピングレベルを有するp+型井戸である。n+ソース領域(69)は、約1e20cm−3までドープされ、p+エピタキシャル層(68)は、約5e17cm−3までドープされる。本実施形態の望ましい特性を達成するために、埋め込みチャネル層(72)は、約2e16cm−3のドーピングレベルを有し、n+緩衝層は、約1e16cm−3にあり、ドリフト層は、約5e15cm−3までドープされる。任意選択で、チャネル特性の強化のために、n+ソース領域(69)とp+エピタキシャル層とは、略同一固定電位にある。

【0039】

AMOSFETは、トレンチが半導体のA面

【0040】

【数5】

を曝露するように、半導体メサ間にトレンチを画定する。各メサは、ソースからドレインへの電流フローを制御するための、pn接合を含む。それに応じて、メサ(65)は、メサにわたって延在し、トレンチ(56)に隣接する、第1の導電型(例えば、P+)の第1の半導体エピタキシャル層(68)を有する。pn接合を達成するために、メサ(65)は、第1の半導体エピ層(68)上に、第2の導電型(例えば、N+)の第2の半導体エピタキシャル層(69)を含む。図5の実施形態では、N+層(69)は、ソース領域である。

【0041】

埋め込みチャネル(72)は、1つのメサ(65)頂部から、ソースコンタクト(60)の少なくとも一部の下の部分から、半導体のA面に沿ったトレンチ壁を下って、トレンチ底部にわたって、トレンチの反対側の壁に上がって、第2のメサ(65)の表面に延在する。つまり、埋め込みチャネル層(72)は、1つのメサのN+ソース領域から、反対側のメサのN+ソース領域に延在し、それによりトレンチ壁を被覆する。次に、埋め込みチャネル(72)は、ゲートコンタクト(61)と埋め込みチャネル(72)との間に絶縁層(例えば、二酸化ケイ素)(64)を有する、ゲートコンタクト(61)に近接して配設される。その趣旨で、埋め込みチャネル(72)の少なくとも一部は、各メサのソース領域と、ゲートコンタクトの下の絶縁層との間にある。全体的に、AMOSFET(50)は、半導体のA面に沿って、埋め込みチャネル(72)内の電気伝導を制御する。

【0042】

トレンチチャネルの角部(80)を保護し、その領域内の電流集中効果を軽減するために、AMOSFETは、第1のエピタキシャル層(68)から、半導体メサへと下方に延在する、第1の導電型(例えば、P+)を有する井戸領域(77)を含む。本発明のAMOSFET(50)は、ソース領域(60)と同一の導電型(例えば、N+)を有し、トレンチ(56)壁と井戸(77)との間の、各メサ(65)内の底部領域の少なくとも一部に延在する、緩衝層(73)をさらに利用する。緩衝層(73)は、さらなる伝導制御のために、AMOSFET(50)の井戸領域(77)とのpn接合を形成する。好ましい実施形態では、緩衝層(73)は、埋め込みチャネル(72)の外壁から、井戸(77)の外壁に延在する。

【0043】

本発明に従った炭化ケイ素結晶構造のA面

【0044】

【数6】

を利用する一利点は、従来技術のゲートトレンチよりも浅いゲートトレンチによって望ましい性能を達成することである。UMOSFETにおける従来技術のトレンチは、2ミクロンを超える。本明細書中の本発明の一実施形態において、ゲートトレンチ(56)は、約2ミクロン未満の深さであり、好適な実施形態においては、ゲートトレンチ(56)は、約1ミクロン未満の深さである。さらに好適な実施形態は、約0.8ミクロンの深さのゲートトレンチ(56)を利用する。

【0045】

図5のAMOSFETの別の特性は、P+井戸(77)の深さである。井戸(77)は、緩衝層(73)よりも大きい深さまで、かつトレンチ(56)または埋め込みチャネル(72)のいずれかよりもさらに深く延在する。深いP+井戸(77)は、ゲートと半導体との結合により生成される電界を遮断することにより、トレンチ角部(80)を保護する。好ましい実施形態では、P+井戸(77)は、図5に示すように、深さが約1.3ミクロンである。

【0046】

図6に示すように、順方向電流分布は、P+井戸(77)の追加の深さ、および図5に示すような緩衝層(73)の使用により、ドリフト領域(55)のより大きい部分にわたって非常に増大される。電流密度分布が、図6のAMOSFETの主要部分、特にドリフト領域(55)内で、300A/cm2に達することの意義は大きい。比較すると、図3のDMOSFETは、ドリフト領域の著しく小さい領域内で、300A/cm2の範囲の電流密度を達成する。図3でテストされたDMOSFETのドリフト領域の大部分は、200〜225A/cm2の範囲の電流密度を達成した。

【0047】

図7は、図5のAMOSFETデバイスに印加される様々なゲート電圧に対する、電流出力を図示する。2.84mohms・cm2の特定のオン抵抗は、図2に示すような従来技術のDMOSFETに対する、4.62のオン抵抗に比べて著しい改善である。本発明に従ったAMOSFET内の炭化ケイ素A面の使用は、チャネル内の抵抗の著しい減少をもたらす。

【0048】

本明細書に記載されるAMOSFETは、高いチャネル移動度、短いチャネル長さ、半導体内のJFET抵抗の減少、および高いチャネル密度により、より低いオン抵抗を有する。高いチャネル移動度は、A面

【0049】

【数7】

に沿って、埋め込みチャネル(72)を通じて、より高い相互コンダクタンスを示す。チャネル集中の軽減は、A面に沿ったより高い電流処理能力を達成するのに役立つ。これらの質は、約1ミクロン未満までの浅いトレンチエッチングを含む製造プロセスにおいて、達成される。本発明の他の実施形態は、従来技術のデバイスのトレンチ深さよりも著しく小さい、約1ミクロンから2ミクロンのトレンチ深さを利用する。これらの改善をMOSFET設計に組み込むことにより、AMOSFETは、順方向の伝導に対して、約3ボルト未満、および好ましくは約2ボルトの閾値電圧Vtを達成する。

【0050】

図8および図9は、炭化ケイ素のA面上に伝導性チャネルを有する、本発明に従い形成されるトランジスタの、有利な電気的応答を示す。図は、従来の従来技術のDMOSFET(図8a、図9a)とUMOSFET(図8b、図9b)トランジスタとを、本明細書に開示されるAMOSFET(図8c、図9c)と比較する。

【0051】

図8は、それぞれの上の1200Vの阻止電圧の印加後の、3つのデバイス(DMOS、UMOS、AMOS)に関する電界強度分布の略図である。図8aでは、従来技術のDMOSFETは、酸化物絶縁層(15)に沿った高い電界強度を示し、それにより、デバイスがその領域内で破壊する前に、耐えることができる逆バイアスを最小化する。図8bの従来技術のUMOSFETは、トレンチのゲートコンタクトと半導体壁との交差点で、同様の電界集中を示す。図8bにおけるトレンチ角部での電界集中は、デバイスが、完全な電圧阻止特性を達成することを回避する。その一方、本発明に従って形成され、図8cに示すAMOSFETは、トレンチ角部を、トレンチ内のより高い電界から保護する緩衝層(73)と深い井戸(77)とを含む。図8cに示すように、本発明のAMOSFETのトレンチ角部は、約1.26e6ボルト/cm未満の電界強度に曝露され、同一の阻止電圧で約5e6V/cmの電界強度に曝露される、図8bのUMOSFETのトレンチに比べて改善されている。これらの結果に基づき、本発明のAMOSFETは、深いp+井戸(77)とn型緩衝層(73)とを含む改善された設計により、より高い逆阻止電圧に耐えることが可能である。

【0052】

図9は、図8からの各デバイスの酸化物層内の電界強度を図示する(それぞれDMOS、UMOS、およびAMOS)。図9bに示す従来のUMOSFETでは、トレンチ角部での電界は、AMOSFETの酸化物層(図9c)内の最大電界強度よりも50パーセント大きい。AMOSFET(図9c)はまた、図9bのUMOSFETの急激な減少とは対照的に、炭化ケイ素全体により均一に電界を拡散する。UMOSFETに関する電界応答は、適切な動作を妨害する、トレンチ角部での電界集中の予想されたパターンを示す。本明細書に開示されるAMOSFETは、その上のより高い阻止電圧を可能にするために、デバイス本体全体に均一に、適切に電界強度を拡散する。

【0053】

本明細書に開示されるAMOSFETを形成する方法は、従来技術のDMOSFETに効果的に使用されてきた技術を強化する。しかしながら、従来の方法は、AMOSFETが、炭化ケイ素エピ層のA面に伝導性チャネルを含むという事実を説明するために、変更される。上述のように、本発明に従ったMOSFETは、既知の手段により形成される炭化ケイ素基板を任意選択で含む。4H−SiCのドリフト領域(55)層は、基板上でエピタキシャルに成長し、次に、本発明の強化された実施形態で、典型的にn型にドープされる炭化ケイ素の緩衝層(73)が、ドリフト領域(55)上に形成される。方法は、第1の導電型、好ましくはP+の、少なくとも1つのドープ型井戸領域(77)を形成するステップを含む。井戸領域(77)は、あらゆる一般的な技術により形成され得るが、好ましくは、ドーパントを、デバイスの頂部から1ミクロンよりも大きい深さまで、半導体に注入することにより形成される。デバイス本体内にpn接合を形成するために、方法は、第1のエピタキシャル層(68)が、ドープ型井戸領域(77)の少なくとも一部を被覆するように、ドリフト領域(55)上に、第1の導電型の第1のエピタキシャル層(68)を成長させるステップを含む。第2の導電型の第2のエピタキシャル層(69)は、第1のエピタキシャル層(68)上に形成される。この段階でのAMOSFET(50)の本体は、頂部から底部への電気伝導を制御するために、好ましくは炭化ケイ素の半導体層を含む。

【0054】

本発明の方法の次のステップは、半導体層内にトレンチを形成し、それにより一対の半導体メサ(65)を形成するために、エピタキシャル層、特に緩衝層(73)、ならびに第1および第2のエピタキシャル層(68、69)をエッチングするステップである。トレンチ(56)は、好ましくは、ドープ型井戸領域(77)の深さよりも小さい深さまで延在する。埋め込みチャネル層(72)は、第2のエピタキシャル層(69)の少なくとも一部にわたって形成される。埋め込みチャネル層(72)は、トレンチ(56)へとトレンチ底部にわたって延在し、反対側のトレンチ壁と、第1の反対側にある第2のメサの少なくとも一部を被覆するように続く。その後、トレンチ壁は、ゲートコンタクト(61)がトレンチ内に形成される、二酸化ケイ素等のゲート絶縁(64)層により被覆される。これらの種類のトランジスタに共通のソースとドレインコンタクトとが、本明細書のAMOSFET(50)を完成する。

【0055】

上述のドーピング方法は、AMOSFET(50)が、オン状態で高い電流出力を達成するように、他の変形型において修正され得ることに留意することが重要である。例えば、半導体のA面に沿ったチャネル領域を有するトランジスタを形成する方法は、半導体(55)内に第1の導電型のドープ型井戸領域(77)を注入するステップと、次に、井戸層(77)の少なくとも一部分の上に、第1の導電型のエピタキシャル層(68)を成長させるステップとを含む。本発明の本実施形態では、第1のエピタキシャル層(68)の上部は、当該分野で既知の注入技術により、反対の導電型に変換され得る。第2の導電型のこの上部は、次に、トランジスタ(50)内にpn接合を形成するために、第2のエピタキシャル層(69)となる。エピタキシャル層のエッチングは、伝導を制御するゲートコンタクト(61)を形成するために、望ましいトレンチを形成する。

【0056】

本明細書に記載される方法は、半導体層のA面上の高伝導性チャネルから利益を得る、他のトランジスタを形成するためにも使用され得る。したがって、本発明は、MOSFETに限定されず、絶縁ゲート型バイポーラトランジスタと金属酸化物半導体制御型サイリスタとにも、同様に適用できる。これらのデバイスのすべてを形成するために使用される半導体材料は、好ましくは炭化ケイ素であるが、本発明は、そのようなものに限定されない。

【0057】

当業者は、本発明が、多くの異なる種類のトランジスタのデバイス構造において、具現化され得ることを認識するであろう。したがって、本発明は、本明細書に図示される特定の構造に限定されない。例えば、トランジスタは、構成に応じてp型またはn型チャネルを含み得る。本明細書に記載されるあらゆる層またはトランジスタ領域も、本文書に使用される説明が、一例に過ぎないため、反対のドーピングタイプを有し得る。

【0058】

図面および明細書において、本発明の好ましい実施形態が説明されており、特定の用語が用いられてきたが、それらは、一般的かつ説明的意味でのみ使用され、制限目的のために使用されず、本発明の範囲は、特許請求の範囲において規定される。

【技術分野】

【0001】

本発明は、特に、伝導性チャネルが半導体のA面で形成される、MOSFETに有用なトランジスタ構造に関する。本発明が取り組む課題には、(i)最適な電流出力のために、オン状態でチャネル抵抗を減少させること、および(ii)デバイス内の逆電圧阻止(reverse voltage blocking)能力を最大化するために、電界集中(field crowding)効果を最小化することが含まれる。

【背景技術】

【0002】

過去20年にわたって、トランジスタ設計は、オン状態で制御された電流フローを達成すると同時に、オフ状態で特定の電圧を阻止する能力を有するように最適化されてきた。炭化ケイ素とIII族窒化物とを含む、よりよい半導体材料の開発は、オン状態(例えば、より高い電流出力)とオフ状態(より少ないリーク電流を有する、より高い電圧阻止)との両方において、トランジスタ性能のより大きな制御を可能にする、トランジスタ設計の驚くべき進歩をもたらしてきた。炭化ケイ素は、様々な結晶構造におけるその電気特性により、特に高い関心が持たれてきた。

【0003】

炭化ケイ素の結晶構造は、使用される層の要素構成により説明される場合が多い。炭化ケイ素基板の断面は、シリコン原子の層の上に直接、炭素原子の層、もしくはその逆を示す。シリコン層は、その上にデバイスを形成するために研磨および使用される場合が多く、それは、シリコン面として知られる。炭素層が曝露される場合は、それは炭素面として知られる。非特許文献1を参照されたい。

【0004】

炭化ケイ素結晶の配列の軸はまた、半導体デバイスを形成するための配向の選択において重要な役割を果たす。従来、六方晶系構造に対して、a1、a2、a3、およびcの4つの主軸が、一般的に使用される。aベクトルのすべては、同一の平面(「a平面」)にあり、cベクトルは、a平面に垂直であるc平面にある。同非特許文献1。

【0005】

以前の研究者たちは、得られたデバイスにおける様々な性能特性を実現するために、炭化ケイ素結晶の異なる平面または面を使用しようと試みてきた。例えば、Yanoらは、c面上に形成されるMOSFETのチャネル移動度特性と、4H−SiC基板のa面上の反転層移動度に関する改善された結果とを開示している。Yano、Kimoto、Matsunami、Asano、およびSugawara「High Channel Mobility in Inversion Layers of 4H−SiC MOSFETs by Utilizing

【0006】

【数1】

Face」、IEEE Electron Device Letters、Vol.20、No.12(1999年12月)、p.611−613を参照されたい。

【0007】

Yanoらは、同一の基板上で互いに垂直の電流を有する、2種類のMOSFETを形成した。

【0008】

【数2】

面上に形成されるMOSFETに対するドレイン電流は、実質的に改善され、炭化ケイ素のa面

【0009】

【数3】

を使用することにより、チャネル移動度の著しい増加を示した。しかしながら、Yanoのデバイスは、比較的低い臨界電界強度を有し、所望よりも低いゲート電圧において逆バイアスの下で伝導を行うことから、Yanoの設計は、垂直型パワーデバイスにおいては好ましくない。そのうえ調整される付加パラメータなしで、a面上のMOSFETを改良する唯一の技術は、パワーMOSFETにおける性能の最適化において、最適な解決策であることを証明していない。

【0010】

チャネル抵抗が、特に低電圧(<2kV)の炭化ケイ素MOSFETに対して、MOSFETの全オン抵抗のかなりの部分を作り出すことから、パワーMOSFET内の電流フローを最大化するためのこれまでの努力は、炭化ケイ素デバイスのチャネル抵抗に焦点を当ててきた。チャネル抵抗を減少させる方法は、(1)チャネル移動度を改善すること、(2)デバイスセルピッチを減少すること、および(3)チャネル長さを減少することに集中してきた。研究努力は、これらの方法を広範囲に研究してきたが、従来技術のDMOSFET(二重拡散型金属酸化物半導体FET)と、UMOSFET(トレンチゲート型金属酸化物半導体FET)とは、チャネル移動度の望ましい増加の実現において、わずかな改善のみを示してきた。例えば、既知のUMOSFETは、伝導性チャネルにおけるキャリア密度の増加を示すが、これらの同一のデバイスは、逆バイアスの下で、トレンチゲートの角部における電界集中の損害をこうむる。

【0011】

図1および図4は、従来技術のDMOSFET(5)と従来技術のUMOSFET(28)とをそれぞれ示す。従来のDMOSFET(5)は、半導体(18)上に配設される、ソースと、ゲートと、ドレインコンタクト(10、11、12)とを含み、ゲートコンタクト(11)は、ゲート領域を絶縁する酸化物層(15)の上にある。DMOSFET(5)は、約0.5ミクロンの深さまで半導体内に注入され、約1e20cm−3までドープされる、p+型井戸(19)を含む。約1e20cm−3までドープされるn+ソース領域(20)は、p+井戸(19)に隣接し、p+井戸(19)と埋め込みチャネル(21)との間に配設される。埋め込みチャネル(21)は、ソース(20)と、p+井戸(19)と、活性領域、すなわちJFET領域(23)の間の半導体(18)との部分に延在する。DMOSFET(5)の埋め込みチャネル(21)、JFET領域(23)および支持ドリフト領域(24)は、約1e16cm−3までドープされる。典型的な従来技術のDMOSFETでは、製造プロセスが、層の成長中にドーピングの変わりにイオン注入を使用することによって、チャネル表面を制御する。DMOSFETにおいて、イオン注入を正確に実現することは困難であり、得られたデバイスは、チャネル移動度が制限される。

【0012】

図1のDMOSFET(5)のチャネル抵抗は、図2の順方向電圧対電流曲線に説明される。そこに示すように、図1のDMOSFET(5)は、40cm2/Vsのチャネル移動度と、約4.62mΩ・cm2の特定のオン抵抗とを実現する。それに応じて、図3は、図1の従来技術のDMOSFET(5)の順方向電流分布を示す。これらの値は、約25から50cm2/Vsの典型的なチャネル移動度を達成する、既知のDMOSFETの範囲内である。図3に示すように、デバイスのドリフト領域(24)内の電流分布は、ゲートにより近い上部(23)内の最適な電流よりもはるかに少ない。図3は、電流が、デバイスを介するドレイン(12)への最大フローに対して所望されるようには、拡散していないことを示す。

【0013】

図4の従来技術のUMOSFET(28)は、同様の電流制限を経験している。図面に説明するように、UMOSFET(28)は、スタンダードソース(30)と、ゲート(31)と、ドレイン(32)とを含み、トレンチ(36)の内側をおおう酸化物層(33)の上にあるゲート(31)を有する。UMOSFET(28)の埋め込みチャネル(38)は、埋め込みチャネル(38)が、p−n接合のエピタキシャル層(40、41)と、酸化物層(33)との間にあるように、ソース(30)とトレンチ(36)の下方とにわたって延在する。従来技術のUMOSFETに関する問題は、トレンチ角部(42)が、トレンチ角部における電界の顕著な集中を示し、ドリフト領域(43)と基板(44)とを介する、ドレイン(32)への下方の電流フローを阻止することである。電界集中はまた、逆バイアス動作の間、より低い持続(sustained)ゲート電圧をもたらす。

【0014】

図4のUMOSFETはまた、適切なゲートの配置および動作のために、2ミクロンよりも大きいトレンチを必要とする。反応性イオンエッチングが、UMOSFET内でトレンチを形成するための最適な方法である場合が多いと仮定すると、トレンチ壁は、製造プロセスにおいて、伝導性チャネルが圧迫される非常に重大な損傷を受ける。炭化ケイ素を反応性イオンエッチングにさらす場合に、一定の結果を得ることは困難であり、得られたデバイスは信頼性がない。エッチングに起因する損傷は、絶縁目的でその上に形成される酸化物の質を劣化させる。これらの要因は、従来技術のUMOSFET内で結合して、順方向の伝導に対して最大30ボルトまでのオン電圧を要求する。

【0015】

図1および図4の従来技術のDMOSFETとUMOSFETデバイスとは、逆バイアス動作において入射電圧(incident voltage)を阻止する能力とともに、オン状態における最大電流フローを増加させるトランジスタ設計への修正に対する共通の必要性を図示する。

【0016】

特許文献1(Miyajima 1999年)は、デバイスに対する閾値電圧と阻止特性とを制御すると同時に、チャネル内の電流を増加させることを目的に改良された、従来の炭化ケイ素MOSFETの別の実施例を示す。Miyajimaの特許文献1の特許は、チャネル層のために、ゲートトレンチ壁に沿って炭化ケイ素の垂直な層を利用する。垂直チャネル層は、非常に薄く、約1000から5000オングストロームである。しかしながら、Miyajimaの特許文献1の設計は、トレンチの縁部での電流集中の問題をなおも経験している。さらに、Miyajimaは、チャネル移動度を増大させるための、炭化ケイ素結晶のa面の使用については一切言及していない。

【0017】

特許文献2(Baliga 2002年)は、同時に大きい電圧を支持し、電流飽和モードで動作することに関わる同じ問題のいくつかに取り組んでいる。Baligaの特許文献2の特許出願は、深い井戸の拡張(P+注入)を使用し、トレンチ角部での電流集中をほぼ間違いなく軽減し得る。しかしながら、これらの井戸拡張の以前の研究は、深い井戸が、典型的に高いJFET抵抗をもたらし、それによって、より深いトレンチを必要とすることを示した。Baligaは、実際に、井戸に隣接する領域を空乏化するために、深いP+井戸を使用することにより、JFET効果を促進している。次に、Baligaは、ドレイン領域が電流飽和モードである間に、電界効果トランジスタとしてデバイスの空乏領域を操作するために、JFET効果を使用している。ドレインへの電流フローを抑制するJFET領域の問題は、Baligaのデバイスにおいて、なおも明白である。

【先行技術文献】

【特許文献】

【0018】

【特許文献1】米国特許第5,976,936号明細書

【特許文献2】米国特許出願公開第2002/0185679号明細書

【非特許文献】

【0019】

【非特許文献1】Zetterling、Carl−Mikael、「Process Technology for Silicon Carbide Devices」、Institute of Electrical Engineers(2002年)、p.3

【発明の概要】

【発明が解決しようとする課題】

【0020】

オン状態における高電流出力と、逆バイアスの下でのゲートトレンチにおける低減された電流集中とを有するパワートランジスタを実現するための従来の努力は、概して不成功であった。従来技術は、ゲートトレンチ側壁に沿ったチャネル抵抗を減少させることと、逆バイアスの下で半導体デバイスにわたって電界を拡散するためにデバイスの容量を増加させることとの、競合する要因に取り組むことに失敗してきた。

【課題を解決するための手段】

【0021】

(本発明の簡単な概要)

本発明は、オン状態での順方向に伝導中、ドリフト領域(55)内のJFET効果を最小化すると同時に、炭化ケイ素体(65)のA面に沿った電流を最適化する、新しいトランジスタ構造(50)である。本発明は、トレンチゲート型デバイス内のゲート角部領域(80)を保護する、高濃度ドープ型井戸領域(77)の追加により、高電圧阻止能力をさらに示す。

【0022】

ゲートコンタクト(61)のための、半導体内のエッチングされたトレンチ(56)を利用するトランジスタデバイスに対して、トレンチ側壁に沿った伝導は、半導体、好ましくは炭化ケイ素のA面にわたって導電性パス(72)を提供することにより、増大され得る。本発明によると、トランジスタは、トレンチ(56)を画定する半導体メサ(65)の一部に延在する、埋め込みチャネル層(72)に加えて、トレンチ側壁に沿ったA面の伝導を効果的に使用する。ドープ型井戸(77)は、メサの少なくとも1つから、トレンチ(56)の深さよりも大きい、電流拡散層すなわちドリフト領域(55)内の深さまで延在する。電流拡散ドリフト層(55)は、オン状態で接合抵抗を減少させるために、トレンチ(56)の底部の下にある半導体メサ(65)間に延在する。

【0023】

別の実施形態では、半導体メサ(65)は、その間にトレンチ(56)を画定し、各メサ(65)は、それぞれのメサにおけるp−n接合の幅を画定する。埋め込みチャネル層(72)は、デバイスの上面に隣接し、炭化ケイ素のA面に沿った伝導を利用する、AMOSFET(50)を形成する。埋め込みチャネル層(72)は、トレンチ壁にわたって下方に延在する。例えば、P+伝導性までドープされる深い井戸領域(77)は、AMOSFET(50)の頂部から、トレンチ(56)よりも大きい深さまで、下方に延在する。深いP+井戸(77)は、逆バイアス動作の間、トレンチ角部(80)を保護し、デバイスが、より高い阻止電圧を実現することを可能にする。ドープされた緩衝層(73)は、各垂直トレンチ壁から深い井戸領域に向かって、デバイスの本体にわたって延在する。

【0024】

本発明は、ゲートコンタクト(61)を介して伝導を制御するために、炭化ケイ素のA面を利用する。炭化ケイ素のA面は、半導体にわたって相互コンダクタンスを増加させることにより、チャネル伝導性を増大させる。反対の導電型の緩衝領域(73)に近接する深い井戸領域(77)は、逆バイアス動作の間、トレンチ角部(80)を保護し、それによりデバイスが、より高いゲート阻止電圧に耐えることを可能にする。

【0025】

本明細書において、本発明に従ったAMOSFETを形成するための方法は、半導体(65)内に第1の導電型のドープ型井戸領域(77)を注入するステップと、次に、第1のエピタキシャル層(68)が、ドープ型井戸領域(77)の少なくとも一部を被覆するように、半導体上で、第1の導電型の第1のエピタキシャル層(68)を成長させるステップを含む。次に、本発明は、第1のエピタキシャル層(68)上に、第2の導電型の第2のエピタキシャル層(69)を成長させ、次に、一対のメサを形成するために、エピタキシャル層と該半導体とをエッチングすることにより、pn接合を形成するステップを含む。メサは、その間にトレンチ(56)を画定し、トレンチは、該ドープ型井戸領域(77)の深さよりも小さい、半導体への深さを有する。該第2のエピタキシャル層(68)またはソース領域の一部にわたって、埋め込みチャネル層(72)を成長させ、該メサ間のトレンチへと埋め込みチャネル層(72)を延在させることにより、方法は、改善された性能特性を有するAMOSFETを実現する。

【0026】

エピタキシャル層(68、69)を個々に成長させる代わりに、方法の異なる実施形態では、該方法は、イオン注入による異なる導電型領域の形成を含む。

【0027】

例えば、本発明は、以下の項目を提供する。

(項目1a)

半導体結晶構造のトレンチ内に絶縁された制御コンタクトを有するトランジスタであって、該トランジスタは、

該トレンチを画定する一対の半導体メサであって、それぞれは少なくとも1つのp−n接合を備える、メサと、

該半導体メサの上面部分に延在し、該トレンチの壁を少なくとも部分的に被覆する埋め込みチャネル層であって、該半導体結晶構造のA面にわたって導電性パスを提供する、埋め込みチャネル層と、

該半導体メサと該トレンチの下方との間に延在して、該トランジスタ内の接合型電界効果抵抗を減少させる電流拡散層と、

該メサのうちの少なくとも1つから、該トレンチの深さよりも大きい深さまで該電流拡散層内に延在するドープ型井戸と

を備える、トランジスタ。

(項目2a)

上記トランジスタは、AMOSFETである、項目1aに記載のトランジスタ。

(項目3a)

上記トランジスタは、絶縁ゲート型バイポーラトランジスタである、項目1aに記載のトランジスタ。

(項目4a)

上記トランジスタは、金属酸化物半導体制御型サイリスタである、項目1aに記載のトランジスタ。

(項目5a)

上記ドープ型井戸は、約1×1019cm−3までドープされるP+型井戸である、項目1aに記載のトランジスタ。

(項目6a)

上記メサ内の上記p−n接合のうちの1つは、

上記埋め込みチャネル層の下および上記トレンチと上記P+井戸との間に配設されるP+型半導体エピタキシャル層と、

該トレンチと該P+井戸との間の該P+エピタキシャル層の上にあるN+型ソース領域と

を備える、項目5aに記載のトランジスタ。

(項目7a)

上記P+エピタキシャル層は、約5×1017cm−3までドープされ、上記N+ソース領域は、約1×1020cm−3までドープされる、項目6aに記載のトランジスタ。

(項目8a)

上記ドープ型井戸から上記トレンチまで延在するエピタキシャル緩衝層をさらに備える、項目6aに記載のトランジスタ。

(項目9a)

上記P+型エピタキシャル層と上記緩衝層と上記P+型井戸との間の上記p−n接合は、結合するように十分にドープされ、それによってオフ状態で上記トレンチの角部を保護する、項目8aに記載のトランジスタ。

(項目10a)

第1および第2の半導体メサ間の、ゲートコンタクトを組み込むためのトレンチの壁を画定するAMOSFETであって、該トレンチは、半導体のA面を曝露させ、該AMOSFETは、

該トレンチに隣接する第1の導電型の第1の半導体エピタキシャル層と、

該第1の半導体エピタキシャル層上にある第2の導電型の第2の半導体エピタキシャル層と、

該AMOSFETの第1の表面に隣接する埋め込みチャネル層であって、該第2の半導体エピタキシャル層の上部に延在し、トレンチ壁に沿って続く、埋め込みチャネル層と、

該第1のエピタキシャル層から該半導体へと下方に、該トレンチよりも大きい深さまで延在する該第1の導電型の井戸領域と

を備える、AMOSFET。

(項目11a)

上記第1の導電型は、P+であり、上記第2の導電型は、N+である、項目10aに記載のAMOSFET。

(項目12a)

上記半導体は、炭化ケイ素を含む、項目10aに記載のAMOSFET。

(項目13a)

上記埋め込みチャネル層は、上記第1のメサのN+ソース領域から上記第2のメサ内のN+ソース領域まで延在し、それによって上記トレンチ壁を被覆する、項目10aに記載のAMOSFET。

(項目14a)

上記井戸領域と上記トレンチとの間にN+型緩衝層をさらに備える、項目13aに記載のAMOSFET。

(項目15a)

半導体内のゲートトレンチの壁を画定する第1および第2の半導体メサ内で電気伝導を制御するためのMOSFETであって、該MOSFETは、

該トレンチに隣接するP+型半導体エピタキシャル層と、

該P+エピタキシャル層上にあるN+型ソース領域と、

該MOSFETの第1の表面に隣接する埋め込みチャネル層であって、該N+型ソース領域の上部に延在し、該トレンチ壁に沿って続く、埋め込みチャネル層と、

該P+エピタキシャル層から該半導体へと下方に、該ゲートトレンチよりも大きい深さまで延在するP+型井戸と

を備え、

該MOSFETは、該半導体のA面に沿って該埋め込みチャネル層内で電気伝導を制御する、

MOSFET。

(項目16a)

上記半導体は、炭化ケイ素を含む、項目15aに記載のMOSFET。

(項目17a)

上記埋め込みチャネル層は、上記第1のメサ内のN+ソース領域から上記第2のメサ内のN+ソース領域まで延在し、それにより上記トレンチ壁を被覆する、項目15aに記載のMOSFET。

(項目18a)

上記P+型井戸と上記ゲートトレンチとの間にN+型緩衝層をさらに備える、項目15aに記載のMOSFET。

(項目19a)

上記N+型緩衝層は、上記埋め込みチャネル層の深さと略等しい深さまで延在する、項目18aに記載のMOSFET。

(項目20a)

上記ゲートトレンチと隣接する上記P+型井戸との下に、N+型ドリフト層をさらに備え、該ドリフト層は、上記第1の表面の反対側にある上記MOSFETの表面に向かって延在する、項目15aに記載のMOSFET。

(項目21a)

上記N+型ドリフト層は、該ドリフト層の最高濃度ドープ領域が上記P+井戸に隣接するように、上記反対側のMOSFET表面から上記第1のMOSFET表面に向かって増加するドーピング濃度を備える、項目20aに記載のMOSFET。

(項目22a)

上記P+井戸の反対側にある上記ドリフト層に隣接する半導体基板を備える、項目20aに記載のMOSFET。

(項目23a)

上記ゲートトレンチは、深さが約2ミクロン未満である、項目15aに記載のMOSFET。

(項目24a)

上記ゲートトレンチは、深さが約1ミクロン未満である、項目15aに記載のMOSFET。

(項目25a)

上記ゲートトレンチは、深さが約0.8ミクロンであり、上記P+井戸は、深さが約1.3ミクロンである、項目15aに記載のMOSFET。

(項目26a)

上記N+ソース領域と上記P+エピタキシャル層とは、略同一固定電位にある、項目15aに記載のMOSFET。

(項目27a)

トランジスタを形成する方法であって、

半導体内に第1の導電型のドープ型井戸領域を注入するステップと、

該半導体上に該第1の導電型の第1のエピタキシャル層を成長させることにより、該第1のエピタキシャル層は、該ドープ型井戸領域の少なくとも一部分を被覆するステップと、

該第1のエピタキシャル層上に第2の導電型の第2のエピタキシャル層を成長させるステップと、

該半導体内に一対のメサを形成するために、該エピタキシャル層と該半導体とをエッチングするステップであって、該メサは、その間にトレンチを画定し、該トレンチは、該ドープ型井戸領域の深さよりも小さい該半導体への深さを有する、ステップと、

該第2のエピタキシャル層の一部分にわたって埋め込みチャネル層を成長させ、該メサ間の該トレンチ内に該埋め込みチャネル層を延在させるステップと

を包含する、方法。

(項目28a)

上記チャネル層は、炭化ケイ素から形成され、該炭化ケイ素のA面は、ソースからドレインに伝導性パスを提供する、項目27aに記載の方法。

(項目29a)

上記エッチングするステップの前に上記半導体上にN+型緩衝層を成長させ、次いで上記エピタキシャル層のすべてと、下にある該半導体の一部分とをエッチングするステップをさらに包含する、項目27aに記載の方法。

(項目30a)

トランジスタを形成するステップであって、

半導体内に第1の導電型のドープ型井戸領域を注入するステップと、

該半導体上に該第1の導電型の第1のエピタキシャル層を成長させることにより、該第1のエピタキシャル層は、該ドープ型井戸領域の少なくとも一部分を被覆するステップと、

該第1のエピタキシャル層の上部領域を第2の導電型に変換するステップと、

該半導体内に一対のメサを形成するために、該エピタキシャル層と該半導体とをエッチングするステップであって、該メサは、その間にトレンチを画定し、該トレンチは、該ドープ型井戸領域の深さよりも小さい該半導体への深さを有する、ステップと、

該エピタキシャル層の一部分にわたって埋め込みチャネル層を成長させ、該メサ間の該トレンチ内に該埋め込みチャネル層を延在させるステップと

を包含する、方法。

(項目1b)

半導体結晶構造のトレンチ内に絶縁された制御コンタクトを有するトランジスタであって、該トランジスタは、

該トレンチを画定する一対の半導体メサであって、それぞれは少なくとも1つのp−n接合を備える、メサと、

該半導体メサの上面部分に延在し、該トレンチの壁を少なくとも部分的に被覆する埋め込みチャネル層であって、該半導体結晶構造のA面にわたって導電性パスを提供する、埋め込みチャネル層と、

該半導体メサと該トレンチの底部の下方との間に延在して、該デバイス内の接合型電界効果抵抗を減少させる電流拡散層と、

該メサのうちの少なくとも1つから、該トレンチの深さよりも大きい深さまで該電流拡散層内に延在するドープ型井戸と

を備える、トランジスタ。

(項目2b)

上記トランジスタは、AMOSFETである、項目1bに記載のトランジスタ。

(項目3b)

上記トランジスタは、絶縁ゲート型バイポーラトランジスタである、項目1bに記載のトランジスタ。

(項目4b)

上記トランジスタは、金属酸化物半導体制御型サイリスタである、項目1bに記載のトランジスタ。

(項目5b)

上記ドープ型井戸は、約1×1019cm−3までドープされるP+型井戸である、項目1bに記載のトランジスタ。

(項目6b)

上記メサ内の上記p−n接合のうちの1つは、

上記埋め込みチャネルの下および上記トレンチと上記P+井戸との間に配設されるP+型半導体エピタキシャル層と、

該トレンチと該P+井戸との間の該P+エピタキシャル層の上にあるN+型ソース領域と

を備える、項目1bに記載のトランジスタ。

(項目7b)

上記P+エピタキシャル層は、約5e17cm−3までドープされ、上記N+ソース領域は、約1e20cm−3までドープされる、項目6bに記載のトランジスタ。

(項目8b)

上記ドープ型井戸から上記トレンチまで延在するエピタキシャル緩衝層をさらに備える、項目1bに記載のトランジスタ。

(項目9b)

上記P+型エピタキシャル層と上記N型緩衝層と上記P+型井戸との間の上記p−n接合は、結合するように十分にドープされ、それによってオフ状態で上記トレンチの角部を保護する、項目1bに記載のトランジスタ。

(項目10b)

半導体メサ間のトレンチを画定するAMOSFETであって、該トレンチは、半導体のA面を曝露させ、該AMOSFETは、

該トレンチに隣接する第1の導電型の第1の半導体エピタキシャル層と、

該第1の半導体エピタキシャル層上にある第2の導電型の第2の半導体エピタキシャル層と、

該AMOSFETの第1の表面に隣接する埋め込みチャネル層であって、該第2の半導体エピタキシャル層の上部に延在し、該トレンチの壁に沿って続く、埋め込みチャネル層と、

該第1のエピタキシャル層から該半導体へと下方に、該ゲートトレンチよりも大きい深さまで延在する該第1の導電型の井戸領域と

を備える、AMOSFET。

(項目11b)

上記第1の導電型は、P+であり、上記第2の導電型は、N+である、項目10bに記載のAMOSFET。

(項目12b)

上記半導体は、炭化ケイ素を含む、項目10bに記載のAMOSFET。

(項目13b)

上記埋め込みチャネル層は、1つのメサのN+ソース領域から隣接するメサのN+ソース領域まで延在し、それによって上記トレンチの壁を被覆する、項目10bに記載のAMOSFET。

(項目14b)

上記P+型井戸と上記ゲートトレンチとの間にN+型緩衝層をさらに備える、項目13bに記載のAMOSFET。

(項目15b)

半導体内のゲートトレンチを画定する一対の半導体メサ内で電気伝導を制御するためのMOSFETであって、該MOSFETは、

該トレンチに隣接するP+型半導体エピタキシャル層と、

該P+エピタキシャル層上にあるN+型ソース領域と、

該MOSFETの第1の表面に隣接する埋め込みチャネル層であって、該N+型ソース領域の上部に延在し、該トレンチの壁に沿って続く、埋め込みチャネル層と、

該P+エピタキシャル層から該半導体へと下方に、該ゲートトレンチよりも大きい深さまで延在するP+型井戸と

を備え、

該MOSFETは、該半導体のA面に沿って該埋め込みチャネル内で電気伝導を制御する、

MOSFET。

(項目16b)

上記半導体は、炭化ケイ素を含む、項目15bに記載のMOSFET。

(項目17b)

上記埋め込みチャネル層は、1つのメサの上記N+ソース領域から隣接するメサの上記N+ソース領域まで延在し、それにより上記トレンチの壁を被覆する、項目15bに記載のMOSFET。

(項目18b)

上記P+型井戸と上記ゲートトレンチとの間にN+型緩衝層をさらに備える、項目15bに記載のMOSFET。

(項目19b)

上記N+型緩衝層は、上記埋め込みチャネル層の深さと略等しい深さまで延在する、項目18bに記載のMOSFET。

(項目20b)

上記ゲートトレンチと隣接する上記P+型井戸との下に、N+型ドリフト層をさらに備え、該ドリフト層は、上記第1の表面の反対側にある上記MOSFETの表面に向かって延在する、項目15bに記載のMOSFET。

(項目21b)

上記N+型ドリフト層は、該ドリフト層の最高濃度ドープ領域が上記P+井戸に隣接するように、上記反対側のMOSFET表面から上記第1のMOSFET表面に向かって増加するドーピング濃度を備える、項目20bに記載のMOSFET。

(項目22b)

上記P+井戸の反対側にある上記ドリフト層に隣接する半導体基板を備える、項目20bに記載のMOSFET。

(項目23b)

上記ゲートトレンチは、深さが約2ミクロン未満である、項目15bに記載のMOSFET。

(項目24b)

上記ゲートトレンチは、深さが約1ミクロン未満である、項目15bに記載のMOSFET。

(項目25b)

上記ゲートトレンチは、深さが約0.8ミクロンであり、上記P+井戸は、深さが約1.3ミクロンである、項目15bに記載のMOSFET。

(項目26b)

上記N+ソース領域と上記P+エピタキシャル層とは、略同一固定電位にある、項目15bに記載のMOSFET。

(項目27b)

トランジスタを形成する方法であって、

半導体内に第1の導電型のドープ型井戸領域を注入するステップと、

該半導体上に該第1の導電型の第1のエピタキシャル層を成長させることにより、該第1のエピタキシャル層は、該ドープ型井戸領域の少なくとも一部分を被覆するステップと、

該第1のエピタキシャル層上に第2の導電型の第2のエピタキシャル層を成長させるステップと、

該半導体内に一対のメサを形成するために、該エピタキシャル層と該半導体とをエッチングするステップであって、該メサは、その間にトレンチを画定し、該トレンチは、該ドープ型井戸領域の深さよりも小さい該半導体への深さを有する、ステップと、

該第2のエピタキシャル層の一部分にわたって埋め込みチャネル層を成長させ、該メサ間の該トレンチ内に該埋め込みチャネル層を延在させるステップと

を包含する、方法。

(項目28b)

上記チャネル層は、炭化ケイ素から形成され、該炭化ケイ素のa面は、ソースからドレインに伝導性パスを提供する、項目27bに記載の方法。

(項目29b)

上記エッチングするステップの前に上記半導体上にN+型緩衝層を成長させ、次いで上記エピタキシャル層のすべてと、下にある該半導体の一部分とをエッチングするステップをさらに包含する、項目27bに記載の方法。

(項目30b)

トランジスタを形成するステップであって、

半導体内に第1の導電型のドープ型井戸領域を注入するステップと、

該半導体上に該第1の導電型の第1のエピタキシャル層を成長させることにより、該第1のエピタキシャル層は、該ドープ型井戸領域の少なくとも一部分を被覆するステップと、

該第1のエピタキシャル層の上部領域を第2の導電型に変換するステップと、

該半導体内に一対のメサを形成するために、該エピタキシャル層と該半導体とをエッチングするステップであって、該メサは、その間にトレンチを画定し、該トレンチは、該ドープ型井戸領域の深さよりも小さい該半導体への深さを有する、ステップと、

該エピタキシャル層の一部分にわたって埋め込みチャネル層を成長させ、該メサ間の該トレンチ内に該埋め込みチャネル層を延在させるステップと

を包含する、方法。

【0028】

(摘要)

トランジスタ構造は、オン状態での順方向に伝導中、ドリフト領域内のJFET効果を最小化するAMOSFETを形成するために、炭化ケイ素体のA面に沿って電流を最適化する。該AMOSFETは、トレンチゲート型デバイス内のゲート角部領域を保護する高濃度ドープ型井戸領域の追加により、高電圧阻止能力をさらに示す。該AMOSFETは、該トレンチを画定する半導体メサの一部に延在する埋め込みチャネル層に加えて、トレンチ側壁に沿って該A面の伝導を使用する。ドープ型井戸は、該メサの少なくとも1つから、該トレンチの深さよりも大きい深さまでの電流拡散層内に延在する。電流拡散層は、オン状態で接合抵抗を減少させるために、該トレンチの底部の下にある該半導体メサ間に延在する。該トレンチと該深い井戸との間の緩衝層は、該トレンチ角部における電界集中からの保護を提供する。

【図面の簡単な説明】

【0029】

【図1】図1は、埋め込みチャネルを有する、従来技術の二重拡散型電界効果トランジスタ(DMOSFET)である。

【図2】図2は、図1の従来技術のDMOSFETに関する、順方向IV曲線のグラフ表示である。

【図3】図3は、図1の従来技術のDMOSFETの、順方向電流分布のグラフ表示である。

【図4】図4は、垂直トレンチ壁に沿って伝導性チャネルを有する、従来技術のトレンチゲート型電界効果トランジスタ(UMOSFET)である。

【図5】図5は、本発明に従った、炭化ケイ素結晶構造のa面上に形成される、金属酸化物半導体(MOSFET)である。

【図6】図6は、本発明に従った、炭化ケイ素のa面上に形成される、MOSFETに関する順方向電流分布のグラフ図である。

【図7】図7は、本発明に従った、炭化ケイ素のa面上に形成される、MOSFETに関する順方向電流対電圧曲線のグラフ図である。

【図8a】図8aは、1200Vの阻止電圧での、DMOSFETの電界強度分布を示すグラフである。

【図8b】図8bは、1200Vの阻止電圧での、UMOSFETの電界強度分布を示すグラフである。

【図8c】図8cは、1200Vの阻止電圧での、本発明に従ったAMOSFETの電界強度分布を示すグラフである。

【図9a】図9aは、従来技術のDMOSFETの酸化物層内の、電界強度の最大深さを示すグラフである。

【図9b】図9bは、従来技術のUMOSFETの酸化物層内の、電界強度の最大深さを示すグラフである。

【図9c】図9cは、本発明に従ったAMOSFETの酸化物層内の、電界強度の最大深さを示すグラフである。

【発明を実施するための形態】

【0030】

(詳細な説明)

本発明のMOSFETは、チャネル移動度の増加(例えば、従来技術のDMOSFETに対して、100cm2/Vs以下になるが、AMOSFETに対しては、最大200cm2/Vsになる)のために、炭化ケイ素結晶エピタキシャル層のA面上に、伝導性チャネルを含む。図5は、新しいAMOSFET(50)の構造を説明する。ドリフト領域(55)すなわち電流拡散層は、ソース領域(60)からドリフト領域(55)を通じてドレイン(62)まで流動する電流を有する、AMOSFET(50)の活性領域を形成するエピタキシャル層を支持する。概して、AMOSFET(50)は、半導体結晶構造(58)のトレンチ(56)内に、絶縁ゲート(61)、すなわち制御コンタクトを有するトランジスタである。トレンチ(56)は、一対の半導体メサ(65)を画定し、それぞれは、その中にpn接合を形成するp+型層(68)とn+型層(69)とを含む。p+型層(68)は、埋め込みチャネル(72)の下、およびトレンチ(56)とp+ドープ型井戸(77)との間に配設される、エピタキシャル層である。n+型層(69)は、伝導目的のためのソース領域である。n+層(69)は、p+層(68)の頂部と、埋め込みチャネル(72)の下に隣接して位置する。ドリフト領域(55)は、AMOSFETの上述の活性領域を支持する。好ましい実施形態では、ドリフト領域(55)は、基板上にあるN+エピタキシャル層であり、トレンチの底部と、ゲートコンタクトの反対側にあるAMOSFETの表面との間に延在する。AMOSFETは、ドレイン(62)に近接する底部MOSFET表面から、ソース領域(69)に近接する上部MOSFET表面に向かって増加する、ドリフト領域(55)内のドーピング濃度を利用する等、より高度なドーピング技術を含み得る。本実施形態では、ドリフト層の最高濃度ドープ領域は、該P+井戸(77)に隣接する。

【0031】

ドレインコンタクト(62)は、デバイスの底部に取り付けられ、ソースからドレインへの、ドリフト領域(55)をわたった伝導を可能にする。この伝導は、トレンチ(56)内のゲート(61)上の電圧により制御される。チャネル領域(72)が、適切な抵抗とチャネル長さを有する限り、ある特定閾値以上のゲート上の正電圧は、ソースからドレインへの制御された伝導を可能にする。

【0032】

本発明に従ったAMOSFETは、ソースと、ゲートと、ドレインコンタクト(60、61、62)とを含む、機能的なトランジスタ特性を含み、ゲートコンタクト(61)は、トレンチ(56)内の絶縁酸化物層(64)の上に形成される。ソースコンタクト(60)は、AMOSFET(50)の第1の表面上に位置し、p+ドープ型井戸(77)とn+ソース領域(69)との上部に延在する。

【0033】

好ましい実施形態では、緩衝層(73)は、p+井戸領域(77)から、トレンチ(56)の底部に向かって延在し、酸化物層(64)とゲートコンタクト(61)とは、トレンチ(56)内にある。緩衝層(73)が、トレンチ角部(80)に隣接して適切に配設されると、p+エピタキシャル層(68)と、n型緩衝層(73)と、p+型ドープ型井戸(77)との間のp−n接合は、結合するように十分にドープされ、それにより、オフまたは非伝導状態でトレンチ角部を保護する。これは、AMOSFET(50)が、ドレイン(62)へのリーク電流、またはデバイスの完全な破壊さえもなく、ゲート(61)上のより高い電圧に耐えることを可能にする。好ましい実施形態では、N+型緩衝層(73)は、埋め込みチャネル層(72)とほぼ同じ深さまで延在する。

【0034】

一実施形態では、各層内のドーピングは十分であり、その上に幅広い電圧レベルを有するゲート(61)により制御される、オン状態での最適な電流を提供する。例えば、図5の実施例では、p+エピタキシャル層(68)は、約5e17cm−3までドープされ、n+ソース領域は、約1e20cm−3までドープされる。

【0035】

本発明のAMOSFET(50)は、ゲート(61)電圧に応じて、ソース(60)からドレイン(62)までの高い電流処理能力を提供するために特に好適な、チャネル層(72)を有する。埋め込みチャネル層(72)が、エピタキシャルp−n接合層(68、69)を形成する半導体結晶構造のA面、

【0036】

【数4】

面にわたって、導電性パスを提供するように、埋め込みチャネル層(72)は、半導体メサ(65)の上面の一部に延在し、底壁を含むトレンチ(56)の外壁を少なくとも部分的に被覆する。

【0037】

ドリフトまたは電流拡散層(55)は、デバイス内の接合型電界効果抵抗を減少させるために、トレンチ(56)の底部の下にある半導体メサ(65)間に延在する。好ましい一実施形態では、ドリフト層(55)は、半導体メサ(65)とゲートトレンチ(61)との幅にわたって延在する。ドリフト層(55)は、ドレインコンタクト(62)が取り付けられた半導体基板上に設置され得る。少なくとも1つのドープ型井戸(77)は、メサ(65)の少なくとも1つ内に、トレンチ(56)の深さよりも大きいドリフト領域(55)内の深さまで延在する。

【0038】

図5のデバイスのドーピングレベルは、図面内の陰影により図示される。本発明のAMOSFETが、あらゆる領域に対するあらゆる特定のドーピングレベルに制限されない一方で、ドーピング範囲は、性能、特にソースからドレインへの電流フローに影響を与える。図5のデバイスにより図示される一実施例では、ドープ型井戸(77)は、約1e19cm−3のドーピングレベルを有するp+型井戸である。n+ソース領域(69)は、約1e20cm−3までドープされ、p+エピタキシャル層(68)は、約5e17cm−3までドープされる。本実施形態の望ましい特性を達成するために、埋め込みチャネル層(72)は、約2e16cm−3のドーピングレベルを有し、n+緩衝層は、約1e16cm−3にあり、ドリフト層は、約5e15cm−3までドープされる。任意選択で、チャネル特性の強化のために、n+ソース領域(69)とp+エピタキシャル層とは、略同一固定電位にある。

【0039】

AMOSFETは、トレンチが半導体のA面

【0040】

【数5】

を曝露するように、半導体メサ間にトレンチを画定する。各メサは、ソースからドレインへの電流フローを制御するための、pn接合を含む。それに応じて、メサ(65)は、メサにわたって延在し、トレンチ(56)に隣接する、第1の導電型(例えば、P+)の第1の半導体エピタキシャル層(68)を有する。pn接合を達成するために、メサ(65)は、第1の半導体エピ層(68)上に、第2の導電型(例えば、N+)の第2の半導体エピタキシャル層(69)を含む。図5の実施形態では、N+層(69)は、ソース領域である。

【0041】

埋め込みチャネル(72)は、1つのメサ(65)頂部から、ソースコンタクト(60)の少なくとも一部の下の部分から、半導体のA面に沿ったトレンチ壁を下って、トレンチ底部にわたって、トレンチの反対側の壁に上がって、第2のメサ(65)の表面に延在する。つまり、埋め込みチャネル層(72)は、1つのメサのN+ソース領域から、反対側のメサのN+ソース領域に延在し、それによりトレンチ壁を被覆する。次に、埋め込みチャネル(72)は、ゲートコンタクト(61)と埋め込みチャネル(72)との間に絶縁層(例えば、二酸化ケイ素)(64)を有する、ゲートコンタクト(61)に近接して配設される。その趣旨で、埋め込みチャネル(72)の少なくとも一部は、各メサのソース領域と、ゲートコンタクトの下の絶縁層との間にある。全体的に、AMOSFET(50)は、半導体のA面に沿って、埋め込みチャネル(72)内の電気伝導を制御する。

【0042】

トレンチチャネルの角部(80)を保護し、その領域内の電流集中効果を軽減するために、AMOSFETは、第1のエピタキシャル層(68)から、半導体メサへと下方に延在する、第1の導電型(例えば、P+)を有する井戸領域(77)を含む。本発明のAMOSFET(50)は、ソース領域(60)と同一の導電型(例えば、N+)を有し、トレンチ(56)壁と井戸(77)との間の、各メサ(65)内の底部領域の少なくとも一部に延在する、緩衝層(73)をさらに利用する。緩衝層(73)は、さらなる伝導制御のために、AMOSFET(50)の井戸領域(77)とのpn接合を形成する。好ましい実施形態では、緩衝層(73)は、埋め込みチャネル(72)の外壁から、井戸(77)の外壁に延在する。

【0043】

本発明に従った炭化ケイ素結晶構造のA面

【0044】

【数6】

を利用する一利点は、従来技術のゲートトレンチよりも浅いゲートトレンチによって望ましい性能を達成することである。UMOSFETにおける従来技術のトレンチは、2ミクロンを超える。本明細書中の本発明の一実施形態において、ゲートトレンチ(56)は、約2ミクロン未満の深さであり、好適な実施形態においては、ゲートトレンチ(56)は、約1ミクロン未満の深さである。さらに好適な実施形態は、約0.8ミクロンの深さのゲートトレンチ(56)を利用する。

【0045】

図5のAMOSFETの別の特性は、P+井戸(77)の深さである。井戸(77)は、緩衝層(73)よりも大きい深さまで、かつトレンチ(56)または埋め込みチャネル(72)のいずれかよりもさらに深く延在する。深いP+井戸(77)は、ゲートと半導体との結合により生成される電界を遮断することにより、トレンチ角部(80)を保護する。好ましい実施形態では、P+井戸(77)は、図5に示すように、深さが約1.3ミクロンである。

【0046】

図6に示すように、順方向電流分布は、P+井戸(77)の追加の深さ、および図5に示すような緩衝層(73)の使用により、ドリフト領域(55)のより大きい部分にわたって非常に増大される。電流密度分布が、図6のAMOSFETの主要部分、特にドリフト領域(55)内で、300A/cm2に達することの意義は大きい。比較すると、図3のDMOSFETは、ドリフト領域の著しく小さい領域内で、300A/cm2の範囲の電流密度を達成する。図3でテストされたDMOSFETのドリフト領域の大部分は、200〜225A/cm2の範囲の電流密度を達成した。

【0047】

図7は、図5のAMOSFETデバイスに印加される様々なゲート電圧に対する、電流出力を図示する。2.84mohms・cm2の特定のオン抵抗は、図2に示すような従来技術のDMOSFETに対する、4.62のオン抵抗に比べて著しい改善である。本発明に従ったAMOSFET内の炭化ケイ素A面の使用は、チャネル内の抵抗の著しい減少をもたらす。

【0048】

本明細書に記載されるAMOSFETは、高いチャネル移動度、短いチャネル長さ、半導体内のJFET抵抗の減少、および高いチャネル密度により、より低いオン抵抗を有する。高いチャネル移動度は、A面

【0049】

【数7】

に沿って、埋め込みチャネル(72)を通じて、より高い相互コンダクタンスを示す。チャネル集中の軽減は、A面に沿ったより高い電流処理能力を達成するのに役立つ。これらの質は、約1ミクロン未満までの浅いトレンチエッチングを含む製造プロセスにおいて、達成される。本発明の他の実施形態は、従来技術のデバイスのトレンチ深さよりも著しく小さい、約1ミクロンから2ミクロンのトレンチ深さを利用する。これらの改善をMOSFET設計に組み込むことにより、AMOSFETは、順方向の伝導に対して、約3ボルト未満、および好ましくは約2ボルトの閾値電圧Vtを達成する。

【0050】

図8および図9は、炭化ケイ素のA面上に伝導性チャネルを有する、本発明に従い形成されるトランジスタの、有利な電気的応答を示す。図は、従来の従来技術のDMOSFET(図8a、図9a)とUMOSFET(図8b、図9b)トランジスタとを、本明細書に開示されるAMOSFET(図8c、図9c)と比較する。

【0051】

図8は、それぞれの上の1200Vの阻止電圧の印加後の、3つのデバイス(DMOS、UMOS、AMOS)に関する電界強度分布の略図である。図8aでは、従来技術のDMOSFETは、酸化物絶縁層(15)に沿った高い電界強度を示し、それにより、デバイスがその領域内で破壊する前に、耐えることができる逆バイアスを最小化する。図8bの従来技術のUMOSFETは、トレンチのゲートコンタクトと半導体壁との交差点で、同様の電界集中を示す。図8bにおけるトレンチ角部での電界集中は、デバイスが、完全な電圧阻止特性を達成することを回避する。その一方、本発明に従って形成され、図8cに示すAMOSFETは、トレンチ角部を、トレンチ内のより高い電界から保護する緩衝層(73)と深い井戸(77)とを含む。図8cに示すように、本発明のAMOSFETのトレンチ角部は、約1.26e6ボルト/cm未満の電界強度に曝露され、同一の阻止電圧で約5e6V/cmの電界強度に曝露される、図8bのUMOSFETのトレンチに比べて改善されている。これらの結果に基づき、本発明のAMOSFETは、深いp+井戸(77)とn型緩衝層(73)とを含む改善された設計により、より高い逆阻止電圧に耐えることが可能である。

【0052】

図9は、図8からの各デバイスの酸化物層内の電界強度を図示する(それぞれDMOS、UMOS、およびAMOS)。図9bに示す従来のUMOSFETでは、トレンチ角部での電界は、AMOSFETの酸化物層(図9c)内の最大電界強度よりも50パーセント大きい。AMOSFET(図9c)はまた、図9bのUMOSFETの急激な減少とは対照的に、炭化ケイ素全体により均一に電界を拡散する。UMOSFETに関する電界応答は、適切な動作を妨害する、トレンチ角部での電界集中の予想されたパターンを示す。本明細書に開示されるAMOSFETは、その上のより高い阻止電圧を可能にするために、デバイス本体全体に均一に、適切に電界強度を拡散する。

【0053】

本明細書に開示されるAMOSFETを形成する方法は、従来技術のDMOSFETに効果的に使用されてきた技術を強化する。しかしながら、従来の方法は、AMOSFETが、炭化ケイ素エピ層のA面に伝導性チャネルを含むという事実を説明するために、変更される。上述のように、本発明に従ったMOSFETは、既知の手段により形成される炭化ケイ素基板を任意選択で含む。4H−SiCのドリフト領域(55)層は、基板上でエピタキシャルに成長し、次に、本発明の強化された実施形態で、典型的にn型にドープされる炭化ケイ素の緩衝層(73)が、ドリフト領域(55)上に形成される。方法は、第1の導電型、好ましくはP+の、少なくとも1つのドープ型井戸領域(77)を形成するステップを含む。井戸領域(77)は、あらゆる一般的な技術により形成され得るが、好ましくは、ドーパントを、デバイスの頂部から1ミクロンよりも大きい深さまで、半導体に注入することにより形成される。デバイス本体内にpn接合を形成するために、方法は、第1のエピタキシャル層(68)が、ドープ型井戸領域(77)の少なくとも一部を被覆するように、ドリフト領域(55)上に、第1の導電型の第1のエピタキシャル層(68)を成長させるステップを含む。第2の導電型の第2のエピタキシャル層(69)は、第1のエピタキシャル層(68)上に形成される。この段階でのAMOSFET(50)の本体は、頂部から底部への電気伝導を制御するために、好ましくは炭化ケイ素の半導体層を含む。

【0054】

本発明の方法の次のステップは、半導体層内にトレンチを形成し、それにより一対の半導体メサ(65)を形成するために、エピタキシャル層、特に緩衝層(73)、ならびに第1および第2のエピタキシャル層(68、69)をエッチングするステップである。トレンチ(56)は、好ましくは、ドープ型井戸領域(77)の深さよりも小さい深さまで延在する。埋め込みチャネル層(72)は、第2のエピタキシャル層(69)の少なくとも一部にわたって形成される。埋め込みチャネル層(72)は、トレンチ(56)へとトレンチ底部にわたって延在し、反対側のトレンチ壁と、第1の反対側にある第2のメサの少なくとも一部を被覆するように続く。その後、トレンチ壁は、ゲートコンタクト(61)がトレンチ内に形成される、二酸化ケイ素等のゲート絶縁(64)層により被覆される。これらの種類のトランジスタに共通のソースとドレインコンタクトとが、本明細書のAMOSFET(50)を完成する。

【0055】

上述のドーピング方法は、AMOSFET(50)が、オン状態で高い電流出力を達成するように、他の変形型において修正され得ることに留意することが重要である。例えば、半導体のA面に沿ったチャネル領域を有するトランジスタを形成する方法は、半導体(55)内に第1の導電型のドープ型井戸領域(77)を注入するステップと、次に、井戸層(77)の少なくとも一部分の上に、第1の導電型のエピタキシャル層(68)を成長させるステップとを含む。本発明の本実施形態では、第1のエピタキシャル層(68)の上部は、当該分野で既知の注入技術により、反対の導電型に変換され得る。第2の導電型のこの上部は、次に、トランジスタ(50)内にpn接合を形成するために、第2のエピタキシャル層(69)となる。エピタキシャル層のエッチングは、伝導を制御するゲートコンタクト(61)を形成するために、望ましいトレンチを形成する。

【0056】

本明細書に記載される方法は、半導体層のA面上の高伝導性チャネルから利益を得る、他のトランジスタを形成するためにも使用され得る。したがって、本発明は、MOSFETに限定されず、絶縁ゲート型バイポーラトランジスタと金属酸化物半導体制御型サイリスタとにも、同様に適用できる。これらのデバイスのすべてを形成するために使用される半導体材料は、好ましくは炭化ケイ素であるが、本発明は、そのようなものに限定されない。

【0057】

当業者は、本発明が、多くの異なる種類のトランジスタのデバイス構造において、具現化され得ることを認識するであろう。したがって、本発明は、本明細書に図示される特定の構造に限定されない。例えば、トランジスタは、構成に応じてp型またはn型チャネルを含み得る。本明細書に記載されるあらゆる層またはトランジスタ領域も、本文書に使用される説明が、一例に過ぎないため、反対のドーピングタイプを有し得る。

【0058】

図面および明細書において、本発明の好ましい実施形態が説明されており、特定の用語が用いられてきたが、それらは、一般的かつ説明的意味でのみ使用され、制限目的のために使用されず、本発明の範囲は、特許請求の範囲において規定される。

【特許請求の範囲】

【請求項1】

半導体結晶構造のトレンチ内に絶縁された制御コンタクトを有するトランジスタであって、該トランジスタは、

該トレンチを画定する一対の半導体メサであって、それぞれは少なくとも1つのp−n接合を備える、メサと、

該半導体メサの上面部分に延在し、該トレンチの壁を少なくとも部分的に被覆する埋め込みチャネル層であって、該半導体結晶構造のA面にわたって導電性パスを提供する、埋め込みチャネル層と、

該半導体メサと該トレンチの下方との間に延在して、該トランジスタ内の接合型電界効果抵抗を減少させる電流拡散層と、

該メサのうちの少なくとも1つから、該トレンチの深さよりも大きい深さまで該電流拡散層内に延在するドープ型井戸と

を備える、トランジスタ。

【請求項2】

前記トランジスタは、AMOSFETである、請求項1に記載のトランジスタ。

【請求項3】

前記トランジスタは、絶縁ゲート型バイポーラトランジスタである、請求項1に記載のトランジスタ。

【請求項4】

前記トランジスタは、金属酸化物半導体制御型サイリスタである、請求項1に記載のトランジスタ。

【請求項5】

前記ドープ型井戸は、約1×1019cm−3までドープされるP+型井戸である、請求項1に記載のトランジスタ。

【請求項6】

前記メサ内の前記p−n接合のうちの1つは、

前記埋め込みチャネル層の下および前記トレンチと前記P+井戸との間に配設されるP+型半導体エピタキシャル層と、

該トレンチと該P+井戸との間の該P+エピタキシャル層の上にあるN+型ソース領域と

を備える、請求項5に記載のトランジスタ。

【請求項7】

前記P+エピタキシャル層は、約5×1017cm−3までドープされ、前記N+ソース領域は、約1×1020cm−3までドープされる、請求項6に記載のトランジスタ。

【請求項8】

前記ドープ型井戸から前記トレンチまで延在するエピタキシャル緩衝層をさらに備える、請求項6に記載のトランジスタ。

【請求項9】

前記P+型エピタキシャル層と前記緩衝層と前記P+型井戸との間の前記p−n接合は、結合するように十分にドープされ、それによってオフ状態で前記トレンチの角部を保護する、請求項8に記載のトランジスタ。

【請求項10】

第1および第2の半導体メサ間の、ゲートコンタクトを組み込むためのトレンチの壁を画定するAMOSFETであって、該トレンチは、半導体のA面を曝露させ、該AMOSFETは、

該トレンチに隣接する第1の導電型の第1の半導体エピタキシャル層と、

該第1の半導体エピタキシャル層上にある第2の導電型の第2の半導体エピタキシャル層と、

該AMOSFETの第1の表面に隣接する埋め込みチャネル層であって、該第2の半導体エピタキシャル層の上部に延在し、トレンチ壁に沿って続く、埋め込みチャネル層と、

該第1のエピタキシャル層から該半導体へと下方に、該トレンチよりも大きい深さまで延在する該第1の導電型の井戸領域と

を備える、AMOSFET。

【請求項11】

前記第1の導電型は、P+であり、前記第2の導電型は、N+である、請求項10に記載のAMOSFET。

【請求項12】

前記半導体は、炭化ケイ素を含む、請求項10に記載のAMOSFET。

【請求項13】

前記埋め込みチャネル層は、前記第1のメサのN+ソース領域から前記第2のメサ内のN+ソース領域まで延在し、それによって前記トレンチ壁を被覆する、請求項10に記載のAMOSFET。

【請求項14】

前記井戸領域と前記トレンチとの間にN+型緩衝層をさらに備える、請求項13に記載のAMOSFET。

【請求項15】

半導体内のゲートトレンチの壁を画定する第1および第2の半導体メサ内で電気伝導を制御するためのMOSFETであって、該MOSFETは、

該トレンチに隣接するP+型半導体エピタキシャル層と、

該P+エピタキシャル層上にあるN+型ソース領域と、

該MOSFETの第1の表面に隣接する埋め込みチャネル層であって、該N+型ソース領域の上部に延在し、該トレンチ壁に沿って続く、埋め込みチャネル層と、

該P+エピタキシャル層から該半導体へと下方に、該ゲートトレンチよりも大きい深さまで延在するP+型井戸と

を備え、

該MOSFETは、該半導体のA面に沿って該埋め込みチャネル層内で電気伝導を制御する、

MOSFET。

【請求項16】

前記半導体は、炭化ケイ素を含む、請求項15に記載のMOSFET。

【請求項17】

前記埋め込みチャネル層は、前記第1のメサ内のN+ソース領域から前記第2のメサ内のN+ソース領域まで延在し、それにより前記トレンチ壁を被覆する、請求項15に記載のMOSFET。

【請求項18】

前記P+型井戸と前記ゲートトレンチとの間にN+型緩衝層をさらに備える、請求項15に記載のMOSFET。

【請求項19】

前記N+型緩衝層は、前記埋め込みチャネル層の深さと略等しい深さまで延在する、請求項18に記載のMOSFET。

【請求項20】

前記ゲートトレンチと隣接する前記P+型井戸との下に、N+型ドリフト層をさらに備え、該ドリフト層は、前記第1の表面の反対側にある前記MOSFETの表面に向かって延在する、請求項15に記載のMOSFET。

【請求項21】

前記N+型ドリフト層は、該ドリフト層の最高濃度ドープ領域が前記P+井戸に隣接するように、前記反対側のMOSFET表面から前記第1のMOSFET表面に向かって増加するドーピング濃度を備える、請求項20に記載のMOSFET。

【請求項22】

前記P+井戸の反対側にある前記ドリフト層に隣接する半導体基板を備える、請求項20に記載のMOSFET。

【請求項23】

前記ゲートトレンチは、深さが約2ミクロン未満である、請求項15に記載のMOSFET。

【請求項24】

前記ゲートトレンチは、深さが約1ミクロン未満である、請求項15に記載のMOSFET。

【請求項25】

前記ゲートトレンチは、深さが約0.8ミクロンであり、前記P+井戸は、深さが約1.3ミクロンである、請求項15に記載のMOSFET。

【請求項26】

前記N+ソース領域と前記P+エピタキシャル層とは、略同一固定電位にある、請求項15に記載のMOSFET。

【請求項27】

トランジスタを形成する方法であって、

半導体内に第1の導電型のドープ型井戸領域を注入するステップと、

該半導体上に該第1の導電型の第1のエピタキシャル層を成長させることにより、該第1のエピタキシャル層は、該ドープ型井戸領域の少なくとも一部分を被覆するステップと、

該第1のエピタキシャル層上に第2の導電型の第2のエピタキシャル層を成長させるステップと、

該半導体内に一対のメサを形成するために、該エピタキシャル層と該半導体とをエッチングするステップであって、該メサは、その間にトレンチを画定し、該トレンチは、該ドープ型井戸領域の深さよりも小さい該半導体への深さを有する、ステップと、

該第2のエピタキシャル層の一部分にわたって埋め込みチャネル層を成長させ、該メサ間の該トレンチ内に該埋め込みチャネル層を延在させるステップと

を包含する、方法。

【請求項28】

前記チャネル層は、炭化ケイ素から形成され、該炭化ケイ素のA面は、ソースからドレインに伝導性パスを提供する、請求項27に記載の方法。

【請求項29】

前記エッチングするステップの前に前記半導体上にN+型緩衝層を成長させ、次いで前記エピタキシャル層のすべてと、下にある該半導体の一部分とをエッチングするステップをさらに包含する、請求項27に記載の方法。

【請求項30】

トランジスタを形成するステップであって、

半導体内に第1の導電型のドープ型井戸領域を注入するステップと、

該半導体上に該第1の導電型の第1のエピタキシャル層を成長させることにより、該第1のエピタキシャル層は、該ドープ型井戸領域の少なくとも一部分を被覆するステップと、

該第1のエピタキシャル層の上部領域を第2の導電型に変換するステップと、

該半導体内に一対のメサを形成するために、該エピタキシャル層と該半導体とをエッチングするステップであって、該メサは、その間にトレンチを画定し、該トレンチは、該ドープ型井戸領域の深さよりも小さい該半導体への深さを有する、ステップと、

該エピタキシャル層の一部分にわたって埋め込みチャネル層を成長させ、該メサ間の該トレンチ内に該埋め込みチャネル層を延在させるステップと

を包含する、方法。

【請求項1】

半導体結晶構造のトレンチ内に絶縁された制御コンタクトを有するトランジスタであって、該トランジスタは、

該トレンチを画定する一対の半導体メサであって、それぞれは少なくとも1つのp−n接合を備える、メサと、

該半導体メサの上面部分に延在し、該トレンチの壁を少なくとも部分的に被覆する埋め込みチャネル層であって、該半導体結晶構造のA面にわたって導電性パスを提供する、埋め込みチャネル層と、

該半導体メサと該トレンチの下方との間に延在して、該トランジスタ内の接合型電界効果抵抗を減少させる電流拡散層と、

該メサのうちの少なくとも1つから、該トレンチの深さよりも大きい深さまで該電流拡散層内に延在するドープ型井戸と

を備える、トランジスタ。

【請求項2】

前記トランジスタは、AMOSFETである、請求項1に記載のトランジスタ。

【請求項3】

前記トランジスタは、絶縁ゲート型バイポーラトランジスタである、請求項1に記載のトランジスタ。

【請求項4】

前記トランジスタは、金属酸化物半導体制御型サイリスタである、請求項1に記載のトランジスタ。

【請求項5】

前記ドープ型井戸は、約1×1019cm−3までドープされるP+型井戸である、請求項1に記載のトランジスタ。

【請求項6】

前記メサ内の前記p−n接合のうちの1つは、

前記埋め込みチャネル層の下および前記トレンチと前記P+井戸との間に配設されるP+型半導体エピタキシャル層と、

該トレンチと該P+井戸との間の該P+エピタキシャル層の上にあるN+型ソース領域と

を備える、請求項5に記載のトランジスタ。

【請求項7】

前記P+エピタキシャル層は、約5×1017cm−3までドープされ、前記N+ソース領域は、約1×1020cm−3までドープされる、請求項6に記載のトランジスタ。

【請求項8】

前記ドープ型井戸から前記トレンチまで延在するエピタキシャル緩衝層をさらに備える、請求項6に記載のトランジスタ。

【請求項9】

前記P+型エピタキシャル層と前記緩衝層と前記P+型井戸との間の前記p−n接合は、結合するように十分にドープされ、それによってオフ状態で前記トレンチの角部を保護する、請求項8に記載のトランジスタ。

【請求項10】

第1および第2の半導体メサ間の、ゲートコンタクトを組み込むためのトレンチの壁を画定するAMOSFETであって、該トレンチは、半導体のA面を曝露させ、該AMOSFETは、

該トレンチに隣接する第1の導電型の第1の半導体エピタキシャル層と、

該第1の半導体エピタキシャル層上にある第2の導電型の第2の半導体エピタキシャル層と、

該AMOSFETの第1の表面に隣接する埋め込みチャネル層であって、該第2の半導体エピタキシャル層の上部に延在し、トレンチ壁に沿って続く、埋め込みチャネル層と、

該第1のエピタキシャル層から該半導体へと下方に、該トレンチよりも大きい深さまで延在する該第1の導電型の井戸領域と

を備える、AMOSFET。

【請求項11】

前記第1の導電型は、P+であり、前記第2の導電型は、N+である、請求項10に記載のAMOSFET。

【請求項12】

前記半導体は、炭化ケイ素を含む、請求項10に記載のAMOSFET。

【請求項13】

前記埋め込みチャネル層は、前記第1のメサのN+ソース領域から前記第2のメサ内のN+ソース領域まで延在し、それによって前記トレンチ壁を被覆する、請求項10に記載のAMOSFET。

【請求項14】

前記井戸領域と前記トレンチとの間にN+型緩衝層をさらに備える、請求項13に記載のAMOSFET。

【請求項15】

半導体内のゲートトレンチの壁を画定する第1および第2の半導体メサ内で電気伝導を制御するためのMOSFETであって、該MOSFETは、

該トレンチに隣接するP+型半導体エピタキシャル層と、

該P+エピタキシャル層上にあるN+型ソース領域と、

該MOSFETの第1の表面に隣接する埋め込みチャネル層であって、該N+型ソース領域の上部に延在し、該トレンチ壁に沿って続く、埋め込みチャネル層と、

該P+エピタキシャル層から該半導体へと下方に、該ゲートトレンチよりも大きい深さまで延在するP+型井戸と

を備え、

該MOSFETは、該半導体のA面に沿って該埋め込みチャネル層内で電気伝導を制御する、

MOSFET。

【請求項16】

前記半導体は、炭化ケイ素を含む、請求項15に記載のMOSFET。

【請求項17】

前記埋め込みチャネル層は、前記第1のメサ内のN+ソース領域から前記第2のメサ内のN+ソース領域まで延在し、それにより前記トレンチ壁を被覆する、請求項15に記載のMOSFET。

【請求項18】

前記P+型井戸と前記ゲートトレンチとの間にN+型緩衝層をさらに備える、請求項15に記載のMOSFET。

【請求項19】

前記N+型緩衝層は、前記埋め込みチャネル層の深さと略等しい深さまで延在する、請求項18に記載のMOSFET。

【請求項20】

前記ゲートトレンチと隣接する前記P+型井戸との下に、N+型ドリフト層をさらに備え、該ドリフト層は、前記第1の表面の反対側にある前記MOSFETの表面に向かって延在する、請求項15に記載のMOSFET。

【請求項21】

前記N+型ドリフト層は、該ドリフト層の最高濃度ドープ領域が前記P+井戸に隣接するように、前記反対側のMOSFET表面から前記第1のMOSFET表面に向かって増加するドーピング濃度を備える、請求項20に記載のMOSFET。

【請求項22】

前記P+井戸の反対側にある前記ドリフト層に隣接する半導体基板を備える、請求項20に記載のMOSFET。

【請求項23】

前記ゲートトレンチは、深さが約2ミクロン未満である、請求項15に記載のMOSFET。

【請求項24】

前記ゲートトレンチは、深さが約1ミクロン未満である、請求項15に記載のMOSFET。

【請求項25】

前記ゲートトレンチは、深さが約0.8ミクロンであり、前記P+井戸は、深さが約1.3ミクロンである、請求項15に記載のMOSFET。

【請求項26】

前記N+ソース領域と前記P+エピタキシャル層とは、略同一固定電位にある、請求項15に記載のMOSFET。

【請求項27】

トランジスタを形成する方法であって、

半導体内に第1の導電型のドープ型井戸領域を注入するステップと、

該半導体上に該第1の導電型の第1のエピタキシャル層を成長させることにより、該第1のエピタキシャル層は、該ドープ型井戸領域の少なくとも一部分を被覆するステップと、

該第1のエピタキシャル層上に第2の導電型の第2のエピタキシャル層を成長させるステップと、

該半導体内に一対のメサを形成するために、該エピタキシャル層と該半導体とをエッチングするステップであって、該メサは、その間にトレンチを画定し、該トレンチは、該ドープ型井戸領域の深さよりも小さい該半導体への深さを有する、ステップと、

該第2のエピタキシャル層の一部分にわたって埋め込みチャネル層を成長させ、該メサ間の該トレンチ内に該埋め込みチャネル層を延在させるステップと

を包含する、方法。

【請求項28】

前記チャネル層は、炭化ケイ素から形成され、該炭化ケイ素のA面は、ソースからドレインに伝導性パスを提供する、請求項27に記載の方法。

【請求項29】

前記エッチングするステップの前に前記半導体上にN+型緩衝層を成長させ、次いで前記エピタキシャル層のすべてと、下にある該半導体の一部分とをエッチングするステップをさらに包含する、請求項27に記載の方法。

【請求項30】

トランジスタを形成するステップであって、

半導体内に第1の導電型のドープ型井戸領域を注入するステップと、

該半導体上に該第1の導電型の第1のエピタキシャル層を成長させることにより、該第1のエピタキシャル層は、該ドープ型井戸領域の少なくとも一部分を被覆するステップと、

該第1のエピタキシャル層の上部領域を第2の導電型に変換するステップと、

該半導体内に一対のメサを形成するために、該エピタキシャル層と該半導体とをエッチングするステップであって、該メサは、その間にトレンチを画定し、該トレンチは、該ドープ型井戸領域の深さよりも小さい該半導体への深さを有する、ステップと、

該エピタキシャル層の一部分にわたって埋め込みチャネル層を成長させ、該メサ間の該トレンチ内に該埋め込みチャネル層を延在させるステップと

を包含する、方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8a】

【図8b】

【図8c】

【図9a】

【図9b】

【図9c】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8a】

【図8b】

【図8c】

【図9a】

【図9b】

【図9c】

【公開番号】特開2009−141363(P2009−141363A)

【公開日】平成21年6月25日(2009.6.25)

【国際特許分類】

【外国語出願】

【出願番号】特願2008−310327(P2008−310327)

【出願日】平成20年12月4日(2008.12.4)

【出願人】(506078378)クリー, インコーポレイティッド (26)

【公開日】平成21年6月25日(2009.6.25)

【国際特許分類】

【出願番号】特願2008−310327(P2008−310327)

【出願日】平成20年12月4日(2008.12.4)

【出願人】(506078378)クリー, インコーポレイティッド (26)

[ Back to top ]