A/D変換器

【課題】任意のコモンモード電位の差動アナログ信号を入力でき、かつ任意のリファレンス電圧を設定可能なΔΣA/D変換器を提供する。

【解決手段】ΔΣA/D変換器のΔΣ変調器が有する(1ビットDAC+加算+積分)演算回路にて、オペアンプの正側入力ノード及び負側入力ノードに対してそれぞれ2つのリファレンス容量を設け、入力信号に変調器出力に応じた信号を加算又は減算する場合に、リファレンス容量の接続を正側入力ノード及び負側入力ノードにおいて相補的に切り替えることで、リファレンス電圧にかかわらずオペアンプの入力ノードに加算される電荷量を常に同一にして、オペアンプの入力ノードの電位が回路のコモンモード電位に収束するようにし、任意のコモンモード電位の差動アナログ信号を入力可能、かつ任意のリファレンス電圧を設定可能にする。

【解決手段】ΔΣA/D変換器のΔΣ変調器が有する(1ビットDAC+加算+積分)演算回路にて、オペアンプの正側入力ノード及び負側入力ノードに対してそれぞれ2つのリファレンス容量を設け、入力信号に変調器出力に応じた信号を加算又は減算する場合に、リファレンス容量の接続を正側入力ノード及び負側入力ノードにおいて相補的に切り替えることで、リファレンス電圧にかかわらずオペアンプの入力ノードに加算される電荷量を常に同一にして、オペアンプの入力ノードの電位が回路のコモンモード電位に収束するようにし、任意のコモンモード電位の差動アナログ信号を入力可能、かつ任意のリファレンス電圧を設定可能にする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、デルタシグマ型A/D変換器(アナログデジタル変換器)に関する。

【背景技術】

【0002】

デルタシグマ型アナログデジタル変換器(ΔΣA/D変換器)は、オーバーサンプリング技術に基づいたA/D変換方式で、オーディオやセンサ等の比較的速度の遅い信号のデジタイズのために用いられている。ΔΣA/D変換器は、単調増加性に優れ、比較的単純な回路で例えば16ビット等の高分解能を達成できる。ΔΣA/D変換器は、例えばマイクロコントローラ(MCU)に内蔵されるA/D変換回路として用いられている。

【0003】

ΔΣA/D変換器は、入力アナログ信号をΔΣ変調するΔΣ変調器、及びΔΣ変調信号からA/D変換結果を生成するデシメーションフィルタを有する。図6は、1ビットΔΣ変調器を含むΔΣA/D変換器の構成例を示す図である。図6において、MODはΔΣ変調器であり、FLTはデシメーションフィルタである。ΔΣ変調器MODは、入力アナログ信号Vinの信号周波数の数十倍から数百倍程度の周波数(オーバーサンプリング周波数)でΔΣ変調し、1ビットΔΣ変調信号D1を出力する。1ビットΔΣ変調信号D1は、パルス密度変調信号であり、入力アナログ信号Vinが大きい場合には“1”の含まれる割合が増し、入力アナログ信号Vinが小さい場合には“0”の含まれる割合が増す。デシメーションフィルタFLTは、ΔΣ変調器MODにより生成された1ビットΔΣ変調信号D1から信号帯域成分を抽出し、所望のビット幅へ拡張するとともに、低いデータレートにダウンサンプリングし、その結果をA/D変換結果として出力する。A/D変換結果は、入力アナログ信号Vinの大小に対応したデジタルコードとして出力される。図6に示す例では、16ビットデジタル出力D2がA/D変換器でのA/D変換結果として出力される。

【0004】

図7は、ΔΣA/D変換器が有するΔΣ変調器を実現するための信号経路の例を示す図である(非特許文献3:Fig.1、非特許文献4:Fig.1参照)。ΔΣ変調器には、出力コードのビット幅、雑音伝達関数の次数、その他信号経路の構造等に様々なバリエーションが存在するが、ここでは1ビット2次ΔΣ変調器を実現するための信号経路を一例として示している。図7において、AD1、AD2、AD3、AD4は、入力される2つの信号を加算して加算結果を出力する加算器である。図中、“−”(マイナス記号)が付されている加算器は、その入力の符号を反転した後に加算することを意味する。また、DL1、DL2、DL3、DL4は、入力される信号を1サイクル分遅延して出力する遅延器である。AM1は入力される信号を2倍して出力する増幅器であり、Q1は入力される信号を量子化する量子化器である。ここで、ΔΣ変調器は、多くの場合、スイッチドキャパシタ回路等によって構成され、演算が離散時間的に行われるため、遅延器を用いてサイクル間の時間関係を示している。

【0005】

図7において、加算器AD1は、入力アナログ信号Uから出力ΔΣ変調信号Vを減じ、結果を信号S3として出力する。加算器AD2は、遅延器DL1により生成された1サイクル前の加算器AD2自身の出力に信号S3を加え、結果を信号S4として出力する。すなわち、加算器AD2と遅延器DL1との組は、信号S3を時間で積分する積分器として機能する。加算器AD3は、遅延器DL2により生成された1サイクル前の加算器AD2の出力である信号S1から、増幅器AM1より出力された信号S7(2倍にされた出力ΔΣ変調信号V)を減じ、結果を信号S5として出力する。加算器AD4は、遅延器DL3により生成された1サイクル前の加算器AD4自身の出力に信号S5を加え、結果を信号S6として出力する。すなわち、加算器AD4と遅延器DL3との組は、信号S5を時間で積分する積分器として機能する。量子化器Q1は、遅延器DL4により生成された1サイクル前の加算器AD4の出力である信号S2を量子化し、“1”又は“−1”の出力ΔΣ変調信号Vを出力する。量子化器Q1は、入力される信号S2がS2>0である場合には“1”を出力し、S2<0である場合には“−1”を出力する。すなわち、量子化器Q1の出力である出力ΔΣ変調信号Vは、2値(1ビット)の信号である。

【0006】

図7に信号経路を示したΔΣ変調器では、出力ΔΣ変調信号Vは、加算器AD1及びAD3を介して二重に負帰還されている。そのため、信号S2が増加すれば出力ΔΣ変調信号Vが“1”となって信号S7が“2”になるので、信号S5及びS6が減少する方向に働き、結果として信号S2が減少する。また、信号S1が増加すれば、信号S5、S6及びS2が増加する方向に働き、出力ΔΣ変調信号Vが“1”となる。出力ΔΣ変調信号Vが“1”となると、信号S3は減少する方向に作用し、また信号S5も減少する方向に作用し、その結果、信号S1及びS2が減少する。このような負帰還によって、入力アナログ信号Uが過大ではない領域では、図7に示した信号経路は発散しないことが知られている。例えば、図7に信号経路を示したような演算回路を使用することで、図6に示したΔΣ変調器MODを実現できる。

【0007】

図8は、図7に示した1ビット2次ΔΣ変調器の信号経路をz演算子を用いて表記した図である。図8において、AD1、AD2は加算器であり、INT1、INT2は積分器である。また、AM1は入力される信号を2倍に増幅する増幅器であり、Q1は入力される信号を量子化する量子化器である。U1は、加算器AD1と積分器INT1により構成される演算ブロックである。図8に示すように、図7において加算器AD2及び遅延器DL1、DL2で構成される演算部は積分器INT1として表現でき、図7において加算器AD4及び遅延器DL3、DL4で構成される演算部は積分器INT2として表現できる。また、量子化器Q1は、入力される信号の大小を判別して2値化するが、この演算は入力された信号に量子化雑音を加えるとモデル化することができる。そこで、図8においては、信号S2に量子化誤差Eを加えた値を出力するブロックとしている。

【0008】

図7に示した信号経路を、図8に示すようにz演算子を用いて表記し整理すると、量子化雑音Eから出力Vへの雑音伝達関数NTF(z)、及び入力Uから出力Vへの信号伝達関数STF(z)は、

NTF(z)=(1−z-1)2

STF(z)=z-2

である。これは、入力Uはそのまま出力Vへ現れ、量子化雑音Eは高域へ拡散され出力されることを示している。ΔΣA/D変換器は、前述したようなΔΣ変調器の後段にデシメーションフィルタを設け、高域に拡散された量子化雑音を除去してA/D変換結果を得る。

【0009】

次に、前述したΔΣ変調器を実現するための信号経路を、半導体集積回路上に形成するための回路構成について説明する。図9は、シングルエンド構造の(加算+積分)演算回路の一例を示す図である(特許文献1:図1、特許文献3:図3・図6、特許文献4:Fig.6参照)。図9(A)に示す演算ブロックの機能を実現する回路構成の一例を図9(B)に示している。すなわち、図9(B)に示す演算回路は、図9(A)に示すように入力信号(入力電圧)V1、V2を加算する加算器ADD、及び加算器ADDでの加算結果を積分して演算結果を出力信号(出力電圧)Voutとして出力する積分器INTからなる演算ブロックを実現するものである。

【0010】

図9(B)において、C1、C2はサンプリング容量であり、C3は積分容量である。また、OPAはオペアンプであり、SW1、SW2、SW3、SW4、SW5、SW6はスイッチである。スイッチSW1、SW3、SW5は、信号φ1により導通/非導通(オン/オフ)が制御され、スイッチSW2、SW4、SW6は、信号φ2により導通/非導通(オン/オフ)が制御される。ここで、容量C1、C2、C3のそれぞれの容量値をC1、C2、C3とする。また、容量C1やC2において、左側ノード(スイッチSW1やSW3側の電極)をボトムプレートと呼び、右側ノード(スイッチSW6側の電極)をトッププレートと呼ぶ。

【0011】

図9(B)に示す回路は、クロック信号等に基づいて信号φ1、φ2を制御し、スイッチSW1、SW3、SW5の組とスイッチSW2、SW4、SW6の組とを組毎に交互にオンすることによって、入力信号V1とV2の加算及びその加算結果の積分を行う。

【0012】

まず、信号φ1によりスイッチSW1、SW3、SW5がオンし、信号φ2によりスイッチSW2、SW4、SW6がオフすると、容量C1のボトムプレートには電圧V1が印加され、容量C2のボトムプレートには電圧V2が印加される。また、容量C1、C2のトッププレートは0(V)に接続される。このとき、容量C1、C2にそれぞれ蓄えられる電荷Q1、Q2は、

Q1=−C1・V1

Q2=−C2・V2

であり、容量C1、C2に入力電圧V1、V2に応じた電荷がサンプリングされる。また、このときの出力電圧Voutの電圧値がVout1であるとすれば、容量C3に蓄えられる電荷Q3は、

Q3=−C3・Vout1

である。

【0013】

次に、信号φ1によりスイッチSW1、SW3、SW5がオフし、信号φ2によりスイッチSW2、SW4、SW6がオンすると、容量C1、C2のボトムプレートは0(V)に、容量C1、C2のトッププレートはオペアンプOPAの負側入力端子に接続される。その結果、オペアンプOPAの作用によって容量C1、C2に蓄えられた電荷が容量C3に転送されるように動作し、出力電圧Voutの電圧値がVout1からVout2に変化する。電荷保存則により、

−C3・Vout2=Q1+Q2+Q3

が成り立つので、電圧値Vout2は、

Vout2=Vout1+(C1/C3)V1+(C2/C3)V2

となる。つまり、一連の動作によって、出力電圧VoutとしてVout1に(C1/C3)V1と(C2/C3)V2とを加えたものが出力される。その後、信号φ1によりスイッチSW1、SW3、SW5がオンし、信号φ2によりスイッチSW2、SW4、SW6がオフするようにして、前述の動作を繰り返し行うことによって、入力信号V1とV2を加算し、その加算結果を積分する演算が実現される。

【0014】

以上の動作をz演算子で表記すれば、

Vout(z)=[(C1/C3)V1(z)+(C2/C3)V2(z)]/(z−1)

である。図9(B)に示した演算回路では、入力信号(入力電圧)V1は(C1/C3)倍にスケールされて演算され、入力信号(入力電圧)V2は(C2/C3)倍にスケールされて演算される。回路における信号の飽和を防ぐ目的や、その他信号経路設計の都合等に応じて(C1/C3)や(C2/C3)の比率は適宜変化される。

【0015】

図10は、オペアンプの入力部分の回路構成を示す図である(非特許文献5:Fig.2参照)。図10において、M1、M2、M3はN型MOSトランジスタである。MOSトランジスタM1は、MOSトランジスタM2及びM3をバイアスする役割を有する。MOSトランジスタM2、M3は、ソースを共通としたトランジスタ対を構成する。MOSトランジスタM2のゲートがオペアンプの正側入力ノード(正側入力端子)IMに対応しており、MOSトランジスタM3のゲートがオペアンプの負側入力ノード(負側入力端子)IPに対応している。

【0016】

図10に示す差動対が正常に動作するためには、MOSトランジスタM2及びM3のゲート−ソース間電圧は、トランジスタの閾値電圧Vthに0.2(V)程度のオーバードライブ電圧Vovを加えた電圧が必要である。例えば、トランジスタの閾値電圧が0.6(V)であるとすれば、MOSトランジスタM2及びM3は、そのゲート−ソース間電圧が0.2(V)+0.6(V)=0.8(V)以上となるようにバイアスされなければならない。また、MOSトランジスタM1のドレイン−ソース間電圧は、回路が正常に動作するためには、例えば0.2(V)以上が必要である。

【0017】

これらの各MOSトランジスタが正常に動作するために必要な制約により、オペアンプが正常動作するためには、入力端子IM及びIPのそれぞれに対して0.2(V)+0.8(V)=1.0(V)以上の電位を印加せねばならない。例えば、電源電圧が3.0(V)である場合には、入力端子IM及びIPのそれぞれの電位が1.0(V)から3.0(V)の範囲になければオペアンプとして期待した動作をしない。このように、実際には入力端子IM及びIPのそれぞれの電位がある程度高い電位でないとオペアンプは動作しない。そのため、ΔΣA/D変換器に含まれるオペアンプでも、オペアンプの入力端子に印加される電圧は必要な範囲に含まれなくてはならない。正常動作に必要なオペアンプの入力端子の電圧範囲は、コモンモード入力電圧範囲と呼ばれている。

【0018】

前述した図9に示した演算回路はシングルエンド構造であったが、シングルエンド構造に対して大きな信号振幅を使用できることや同相雑音の影響を受けにくいなどの利点から、実際の半導体集積回路において、それら演算回路は差動構造とする場合が多い。以下、ΔΣA/D変換器で用いられる差動構造の演算回路の例を説明する。

【0019】

図11は、差動構造のスイッチドキャパシタ積分器の回路構成例を示す図である(特許文献2:図7、特許文献6:Fig.7参照)。図11において、C1P、C1Mはサンプリング容量であり、C2P、C2Mは積分容量である。また、OPAは全差動オペアンプであり、SW1、SW2、SW3、SW4、SW5、SW6、SW7、SW8はスイッチである。スイッチSW1、SW2、SW5、SW6は、信号φ1により導通/非導通(オン/オフ)が制御され、スイッチSW3、SW4、SW7、SW8は、信号φ2により導通/非導通(オン/オフ)が制御される。また、VIPは正側入力ノード、VIMは負側入力ノード、VOPは正側出力ノード、VOMは負側出力ノードである。なお、以下では、各ノードに対して入力又は出力される信号名や各ノードの電圧値も、適宜ノードに付した符号と同様の表記を用いて示す。SGは、差動入力信号(VIP−VIM)を出力する信号源である。信号源SGは、差動構造のスイッチドキャパシタ積分器が形成される半導体集積回路(IC)の外部に設けられる。

【0020】

図11に示す演算回路(スイッチドキャパシタ積分器)は、信号源SGから供給される差動入力信号(VIP−VIM)を積分し、その結果を差動出力信号(VOP−VOM)により出力する機能を有する。図11に示す演算回路では、オペアンプOPAは、コモンモード電位VCMを参照して、出力信号VOP及びVOMのコモン電位がVCMとなるように、すなわち(VOP+VOM)/2=VCMとなるようにコモンモードフィードバックを行う。なお、図11において、コモンモード電位VCMは、電源電圧VDDと接地電圧VSS(0(V))との中間電位であるとする。VICMは、入力信号VIP及びVIMの中間電位、すなわち入力信号のコモンモード電位である。また、容量C1P及びC1Mの容量値は同一のC1とし、容量C2P及びC2Mの容量値は同一のC2とする。

【0021】

図11に示す演算回路では、まず、信号φ1によりスイッチSW1、SW2、SW5、SW6がオンし、信号φ2によりスイッチSW3、SW4、SW7、SW8がオフすると、容量C1P、C1Mのボトムプレートにはそれぞれ電圧VIP、VIMが印加される。また、容量C1P、C1Mのトッププレートは、コモンモード電位VCMに接続される。このとき、容量C1P、C1Mにそれぞれ蓄えられる電荷Q1P、Q1Mは、

Q1P=(VCM−VIP)C1

Q1M=(VCM−VIM)C1

であり、容量C1P、C1Mにコモンモード電位VCMと入力電圧VIP、VIMとの差に応じた電荷がサンプリングされる。また、このときの出力信号VOPの電圧値がVOP1であるとし、出力信号VOMの電圧値がVOM1であるとすれば、容量C2P及びC2Mに蓄えられている電荷の和は、

(VOP1−VCM)C2+(VCM−VOM1)C2=(VOP1−VOM1)C2

である。

【0022】

次に、信号φ1によりスイッチSW1、SW2、SW5、SW6がオフし、信号φ2によりスイッチSW3、SW4、SW7、SW8がオンすると、容量C1P及びC1Mのボトムプレートはコモンモード電位VCMに接続される。また、容量C1PのトッププレートはオペアンプOPAの負側入力端子に接続され、容量C1MのトッププレートはオペアンプOPAの正側入力端子に接続される。その結果、オペアンプOPAの作用によって、出力信号VOPの電圧値がVOP2に変化し、出力信号VOMの電圧値がVOM2に変化する。このとき、前の状態の電荷が保存されるとすれば、

(VOP2−VOM2)C2=(VOP1−VOM1)C2+Q1P−Q1M

であるので、

(VOP2−VOM2)=(VOP1−VOM1)+(VIP−VIM)C1/C2

である。すなわち、差動出力電圧(VOP2−VOM2)は、1つ前の差動出力電圧(VOP1−VOM1)に差動入力電圧と容量比との積((VIP−VIM)C1/C2)を加えたものになる。これは1回分の積分演算に相当する。

【0023】

ここで、半導体集積回路内における差動信号のコモンモード電位VCMは、半導体集積回路の電源電圧に応じて決まる電位であり、入力信号のコモンモード電位VICMは、半導体集積回路の外部の信号源SGに応じて決まる電位であり、両者は直接関係しない。一般に、差動入力A/D変換器には差動入力信号(VIP及びVIM)を入力するための2つの入力端子は存在するが、入力信号のコモンモード電位VICMを入力するための入力端子は設けられない。コモンモード電位VCMと入力信号のコモンモード電位VICMとがどのような関係であっても、回路が差動信号の演算を正常に行うことが望ましい。

【0024】

しかしながら、図11に示した演算回路において、コモンモード電位VCMと入力信号のコモンモード電位VICMとが著しく異なる電位となった場合には、ノードVAの電位がオペアンプOPAの適切な入力電圧範囲から逸脱し、積分器が動作しない問題がある。これは、ノードVAの電位が、φ1期間にサンプリングされた容量C1P、C1Mの電荷と、φ2期間にスイッチで設定される回路による容量分圧によって決まるためである。なお、φ1期間は、信号φ1により制御されるスイッチがオンとなる期間、すなわちスイッチSW1、SW2、SW5、SW6がオンし、スイッチSW3、SW4、SW7、SW8がオフする期間である。また、φ2期間は、信号φ2により制御されるスイッチがオンとなる期間、すなわちスイッチSW1、SW2、SW5、SW6がオフし、スイッチSW3、SW4、SW7、SW8がオンする期間である。

【0025】

図11に示した演算回路において、φ1期間に容量C1P及びC1Mにサンプリングされる電荷量は、φ2期間もそのまま保存されるので、

(VCM−VIP)C1+(VCM−VIM)C1=2(VA−VCM)C1

が成り立つ。VAについて整理すると、

VA=2VCM−(VIP+VIM)/2=2VCM−VICM

となる。つまり、オペアンプOPAの入力ノードVAの電位は、2VCMからVICMを減じた電位に収束することになる。例えば、コモンモード電位VCMが1.5(V)、入力信号のコモンモード電位VICMが2.5(V)のときには、オペアンプOPAの入力ノードVAの電位は0.5(V)に収束する。しかし、前述したようにオペアンプOPAのコモンモード入力電圧範囲には制約があり、例えば図10に示した回路ではオペアンプの入力ノードIM及びIPの電位が0.5(V)であると、差動対が遮断してしまい、所望の動作が行われない。図11に示した演算回路のオペアンプOPAの内部が図10に示した構成と同様であったとすれば、正常に動作させるためには、入力信号のコモンモード電位VICMは、0(V)<VICM<2.0(V)の電圧範囲でなければならない。

【0026】

この制約の存在は、差動入力A/D変換器を用いてシングルエンド信号をA/D変換する場合に、特に問題となる。例えば、差動入力A/D変換器でシングルエンド信号をA/D変換する場合には、2つの入力端子のうちの片側を所定の電位に固定すれば良い。しかし、図11に示した演算回路を用いたA/D変換器では、例えば負側入力端子VIMを1.5(V)とし、正側入力端子VIPを信号源に接続するようにした場合には、信号源から2.5(V)以上の信号が印加されると、入力信号のコモンモード電位VICMが2.0(V)より大きくなり回路が動作しない。このように、図11に示した演算回路をΔΣA/D変換器に用いた場合には、ユーザが信号源の設計に大きな制約を課されてしまうという課題がある。

【0027】

図11に示した演算回路における前述のような課題を解消する回路構成として、図12に示す演算回路が提案されている(特許文献7:Fig.4参照)。図12は、差動構造のスイッチドキャパシタ積分器の他の回路構成例を示す図である。図12において、図11に示した構成要素と同一の機能を有する構成要素には同一の符号を付し、重複する説明は省略する。図12に示す演算回路は、図11に示した演算回路は有していない容量素子C3P、C3Mが加えられている。C3PとC3Mは寄生容量でもよいので、破線で表記した。また、図11に示した演算回路では、容量C1PのボトムプレートはスイッチSW3を介してコモンモード電位VCMに接続でき、容量C1MのボトムプレートはスイッチSW4を介してコモンモード電位VCMに接続できるように構成されていた。それに対して、図12に示す演算回路では、容量C1P及びC1MのボトムプレートはスイッチSW3を介して互いに接続可能になっている。

【0028】

図12に示す演算回路では、φ1期間に容量素子C3P、C3Mのボトムプレートは0(V)に、容量素子C3P、C3Mのトッププレートはコモンモード電位VCMに接続される。また、容量C1P、C1Mのボトムプレートにはそれぞれ電圧VIP、VIMが印加され、容量C1P、C1Mのトッププレートがコモンモード電位VCMに接続される。これにより、容量素子C3P、C3Mはそれぞれコモンモード電位VCMに充電され、容量C1P、C1Mにコモンモード電位VCMと入力電圧VIP、VIMとの差に応じた電荷がサンプリングされる。

【0029】

次に、φ2期間に遷移しスイッチSW3、SW7、SW8がオンすると、オペアンプOPAの入力ノードVAは容量C3P及びC3Mに予め充電されていたコモンモード電位VCMに収束する。実際には、オペアンプOPAの入力ノードVAの電位は、オペアンプOPAや容量C2P、C2Mの寄生容量等によって、はじめはコモンモード電位VCMとは異なる電位である可能性があるが、数サイクル繰り返した後にコモンモード電位VCMに収束する。このように差動構造のスイッチドキャパシタ積分器は、図12に示すように構成することで、任意のコモンモード電位の差動入力信号を入力できる。

【0030】

図12に示した演算回路は単純な積分器であるが、ΔΣ変調器では、図8に示した演算ブロックU1のように入力電圧に2値の参照電圧を加えた値を積分する(1ビットDAC+加算+積分)演算回路が必要である。図13は、差動構造の(1ビットDAC+加算+積分)演算回路の一例を示す図である。図13において、C3P、C3Mはリファレンス容量であり、SW9、SW10、SW11、SW12、SW13、SW14はスイッチである。また、Vrefはリファレンス電圧である。その他の構成要素は、図12において同一の符号が付された構成要素と同様であるので、重複する説明は省略する。

【0031】

スイッチSW9、SW12は、信号φ1により導通/非導通(オン/オフ)が制御され、スイッチSW10、SW11、SW13、SW14は、信号φ2及び信号y(又は信号yの反転信号yx)により導通/非導通(オン/オフ)が制御される。スイッチSW10及びSW14は、信号φ2が“1”であり、かつ信号yが“+1”であるときに導通(オン)とされ、そうでないときは非導通(オフ)とされる。また、スイッチSW11及びSW13は、信号φ2が“1”であり、かつ信号yが“−1”であるときに導通(オン)とされ、そうでないときは非導通(オフ)とされる。ここで、信号yは、ΔΣ変調器のフィードバック信号に対応し、値は前述のように1ビット(2値)をとる。また、容量C3P及びC3Mの容量値は同一とする。

【先行技術文献】

【特許文献】

【0032】

【特許文献1】特開平8−125541号公報

【特許文献2】特開2002−261614号公報

【特許文献3】特開2001−358591号公報

【特許文献4】米国特許第4851841号明細書

【特許文献5】米国特許第4939516号明細書

【特許文献6】米国特許第4972436号明細書

【特許文献7】米国特許第6768436号明細書

【特許文献8】特開2007−300225号公報

【特許文献9】特開2006−41992号公報

【特許文献10】特表平10−508167号公報

【非特許文献】

【0033】

【非特許文献1】湯川彰著,「オーバーサンプリングA−D変換技術」,日経BP社,1990

【非特許文献2】Richard Schreier and Gabor C. Temes著,和保孝夫 安田彰 監訳,「ΔΣ型アナログ/デジタル変換器入門」,丸善,2007

【非特許文献3】B. E. Boser and B. A. Wooley, "The design of sigma-delta modulation analog-to-digital converters," IEEE Journal of Solid-State Circuits, Vol.23, pp.1298-1308, December 1988.

【非特許文献4】B. P. Brandt, D. E. Wingard, and B. A. Wooley, "Second-order sigma-delta modulation for digital-audio signal acquisition," IEEE Journal of Solid-State Circuits, Vol.26, pp.618-627, April 1991.

【非特許文献5】M. W. Hauser, P. J. Hurst, and R. W. Brodersen, "MOS ADC-Filter Combination That Does Not Require Precision Analog Components," IEEE International Solid-State Circuits Conference 1985 Digest of Technical Papers, pp.80-82, 1985.

【発明の概要】

【発明が解決しようとする課題】

【0034】

発明にいたる参考図である図13に示す演算回路は、差動入力信号から信号yを減じ、その結果を積分して出力する。実際には、リファレンス電圧Vrefとリファレンス容量C3P、C3Mとの積で表される電荷が信号yに相当する。

【0035】

図13に示す演算回路では、φ1期間に、容量C1P、C1Mのボトムプレートにそれぞれ電圧VIP、VIMが印加され、容量C1P、C1Mのトッププレートがコモンモード電位VCMに接続され、差動入力信号のサンプリングが行われる。このとき、容量素子C3P及びC3Mは、両電極(ボトムプレート及びトッププレート)がコモンモード電位VCMに接続されており、電荷がゼロとなる。

【0036】

次に、φ2期間に遷移すると、スイッチSW3、SW7、SW8がオンし、サンプリングにより容量C1P及びC1Mに蓄えられた電荷が、容量C2P及びC2Mに転送される。また、φ2期間において、信号yの値が“+1”の場合には、スイッチSW10及びSW14がオンして、容量C3Pのボトムプレートはリファレンス電圧Vrefに接続され、容量C3Mのボトムプレートは0(V)に接続される。逆に、信号yの値が“−1”の場合には、スイッチSW11及びSW13がオンして、容量C3Pのボトムプレートは0(V)に接続され、容量C3Mのボトムプレートはリファレンス電圧Vrefに接続される。その結果、サンプリングされた入力信号からリファレンス分の信号を減じた値、又はサンプリングされた入力信号にリファレンス分の信号を加えた値が、積分される。

【0037】

図13に示した演算回路を用いて、ΔΣA/D変換器が有するΔΣ変調器を構成した場合には、設定可能なリファレンス電圧Vrefの範囲が狭いという課題がある。ΔΣA/D変換器において、このリファレンス電圧Vrefは、A/D変換のフルスケールを規定するものであるため、ユーザが任意に設定できることが望ましい。図13に示した演算回路では、φ1期間には、容量C3P及びC3Mの電荷はゼロに放出される。次のφ2期間には、容量C3P及びC3Mがリファレンス電圧Vrefと0(V)との電位差を容量分圧するように各スイッチが制御され、オペアンプOPAの入力ノードVAの電位は、容量C3P及びC3Mで分圧された電圧となる。つまり、入力ノードVAの電位は、VA=Vref/2となる。

【0038】

そのため、入力ノードVAの電位(Vref/2)がオペアンプOPAのコモンモード入力電圧範囲を下回るような低いリファレンス電圧Vrefを用いると、回路は動作しない。例えば、電源電圧VDDが3.0(V)、接地電圧VSSが0(V)、コモンモード電位VCMが1.5(V)、リファレンス電圧Vrefが1.0(V)である場合には、入力ノードVAの電位は、VA=Vref/2=0.5(V)に収束する。しかし、図13に示した演算回路のオペアンプOPAの内部が図10に示した構成と同様であると、差動対が遮断して所望の動作が行われない。回路を正常に動作させるためには、リファレンス電圧Vrefは、Vref>2.0(V)でなければならない。このような場合には、図13に示した演算回路に対して、例えばバンドギャップリファレンス回路で発生した1.2(V)の電圧をリファレンス電圧Vrefとして使用することができない。リファレンス電圧Vrefの設定可能な電圧範囲は、半導体集積回路のユーザが行う設計の自由度を高めるために、可能な限り広いことが望ましい。

【0039】

本発明の目的は、任意のコモンモード電位の差動アナログ信号を入力でき、かつ任意のリファレンス電圧を設定可能なΔΣA/D変換器を提供することにある。

【課題を解決するための手段】

【0040】

A/D変換器の一態様は、入力される差動アナログ信号をデルタシグマ変調する変調器と、その出力を基にデジタルデータを生成するデシメーションフィルタとを備える。変調器は、入力信号をサンプリングする第1の容量及び第2の容量と、第1の容量の第1の電極に接続され、第1の基準電圧又は第2の基準電圧をサンプリングする第3の容量及び第4の容量と、第2の容量の第1の電極に接続され、第1の基準電圧又は第2の基準電圧をサンプリングする第5の容量及び第6の容量と、各容量にサンプリングされた電荷を加算又は減算して加算又は減算結果を得て、加算又は減算結果を積分し出力する演算器とを有する演算回路を1つ以上含む。

【発明の効果】

【0041】

演算回路にて入力信号に変調器出力に応じた信号を加算又は減算する場合に、第3の容量及び第4の容量の接続と第5の容量及び第6の容量の接続とを相補的に切り替えることで、基準電圧がどのような電圧であっても演算器の入力ノードに加算される電荷量は同一になる。したがって、演算器の入力ノードの電位は回路のコモンモード電位に収束するので、任意のコモンモード電位の差動アナログ信号を入力でき、かつ任意のリファレンス電圧を設定することができる。

【図面の簡単な説明】

【0042】

【図1】本実施形態によるΔΣA/D変換器の(1ビットDAC+加算+積分)演算回路の構成例を示す図である。

【図2A】図1に示した演算回路の動作を説明するための図である。

【図2B】図1に示した演算回路の動作を説明するための図である。

【図2C】図1に示した演算回路の動作を説明するための図である。

【図3】本実施形態によるΔΣA/D変換器の(1ビットDAC+加算+積分)演算回路の他の構成例を示す図である。

【図4】本実施形態における1ビット2次ΔΣ変調器の構成例を示す図である。

【図5】図4に示したΔΣ変調器の動作の流れを示す図である。

【図6】ΔΣA/D変換器の構成例を示す図である。

【図7】ΔΣ変調器を実現するための信号経路の例を示す図である。

【図8】図7に示したΔΣ変調器の信号経路をz演算子を用いて表記した図である。

【図9】シングルエンド構造の(加算+積分)演算回路の構成例を示す図である。

【図10】オペアンプの入力部分の回路構成を示す図である。

【図11】差動構造のスイッチドキャパシタ積分器の構成例を示す図である。

【図12】差動構造のスイッチドキャパシタ積分器の構成例を示す図である。

【図13】差動構造の(1ビットDAC+加算+積分)演算回路の参考図である。

【発明を実施するための形態】

【0043】

以下、本発明の実施形態を図面に基づいて説明する。

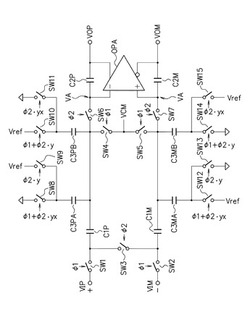

図1は、本発明の一実施形態によるΔΣA/D変換器の(1ビットDAC+加算+積分)演算回路の回路構成例を示す図である。なお、本実施形態によるΔΣA/D変換器の構成は、図6に示したΔΣA/D変換器の構成と同様である。すなわち、本実施形態によるΔΣA/D変換器は、入力される差動アナログ信号をΔΣ変調するΔΣ変調器、及びΔΣ変調信号を基にA/D変換結果(デジタルデータ)を生成するデシメーションフィルタを有する。

【0044】

図1に示す差動構造の(1ビットDAC+加算+積分)演算回路は、入力電圧に2値の参照電圧(リファレンス電圧)を加えた値を積分する演算回路であり、例えばΔΣA/D変換器が有するΔΣ変調器の第一段目の演算回路として用いられる。

【0045】

図1において、C1P及びC1Mはサンプリング容量であり、C2P及びC2Mは積分容量である。また、C3PA、C3PB、C3MA、及びC3MBは、リファレンス容量である。すなわち、本実施形態における演算回路では、正側ノードに2つのリファレンス容量C3PA及びC3PBが設けられ、負側ノードに2つのリファレンス容量C3MA及びC3MBが設けられる。容量C1P及びC1Mの容量値は同一のC1とし、容量C2P及びC2Mの容量値は同一のC2とし、容量C3PA、C3PB、C3MA、及びC3MBの容量値は同一のC3とする。

【0046】

OPAは全差動オペアンプである。また、VIPは差動アナログ信号の正側入力ノードであり、VIMは差動アナログ信号の負側入力ノードである。VAはオペアンプOPAの入力ノードであり、VOPはオペアンプOPAの正側出力ノード、VOMはオペアンプOPAの負側出力ノードである。なお、VOP及びVOMは図1に示す演算回路における差動信号の出力ノードでもある。以下では、これらの各ノードに対して入力又は出力される信号や各ノードの電圧値も、適宜ノードに付した符号と同様の表記を用いて示す。VCMは演算回路におけるコモンモード電位であり、Vrefはリファレンス電圧(リファレンス信号)である。例えば、コモンモード電位VCMは、電源電圧VDDと接地電圧VSS(0(V))との中間電位であるとする。

【0047】

また、SW1〜SW15は、スイッチである。スイッチSW1、SW2、SW4、及びSW5は、信号φ1により導通/非導通(オン/オフ)が制御され、スイッチSW3、SW6、及びSW7は、信号φ2により導通/非導通(オン/オフ)が制御される。スイッチSW8、SW10、SW12、及びSW14は、信号φ1、信号φ2、及び信号y(又は信号yの反転信号yx)により導通/非導通(オン/オフ)が制御される。スイッチSW9、SW11、SW13、及びSW15は、信号φ2及び信号y(又は信号yの反転信号yx)により導通/非導通(オン/オフ)が制御される。ここで、信号yは、ΔΣ変調器の出力(詳細にはΔΣ変調器が有する量子化器の出力)であり、値としては“+1”又は“−1”の2値(1ビット)をとる。

【0048】

スイッチSW1、SW2、SW4、及びSW5は、信号φ1が“1”(アクティブ)であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW3、SW6、SW7は、信号φ2が“1”(アクティブ)であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。

【0049】

スイッチSW8及びSW12は、信号φ1が“1”であるとき、又は信号φ2が“1”かつ信号y=−1であるときに、導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW9及びSW13は、信号φ2が“1”かつ信号y=+1であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。

【0050】

スイッチSW10及びSW14は、信号φ1が“1”であるとき、又は信号φ2が“1”かつ信号y=+1であるときに、導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW11及びSW15は、信号φ2が“1”かつ信号y=−1であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。

【0051】

容量C1Pは、一方の電極(ボトムプレート)がスイッチSW1を介して正側入力ノードVIPに接続され、他方の電極(トッププレート)がスイッチSW6を介してオペアンプOPAの負側入力ノードVAに接続される。容量C1Mは、一方の電極(ボトムプレート)がスイッチSW2を介して負側入力ノードVIMに接続され、他方の電極(トッププレート)がスイッチSW7を介してオペアンプOPAの正側入力ノードVAに接続される。また、容量C1P及びC1Mのボトムプレートは、スイッチSW3を介して互いに接続される。また、容量C1PのトッププレートはスイッチSW4を介してコモンモード電位VCMに接続され、容量C1MのトッププレートはスイッチSW5を介してコモンモード電位VCMに接続される。

【0052】

容量C2Pは、一方の電極がオペアンプOPAの正側出力ノードVOPに接続され、他方の電極がオペアンプOPAの負側入力ノードVAに接続される。容量C2Mは、一方の電極がオペアンプOPAの負側出力ノードVOMに接続され、他方の電極がオペアンプOPAの正側入力ノードVAに接続される。

【0053】

容量C3PAの一方の電極(ボトムプレート)は、スイッチSW8を介して接地電圧VSS(0(V))に接続されるとともに、スイッチSW9を介してリファレンス電圧Vrefに接続される。容量C3PBの一方の電極(ボトムプレート)は、スイッチSW10を介してリファレンス電圧Vrefに接続されるとともに、スイッチSW11を介して接地電圧VSS(0(V))に接続される。また、容量C3PA及びC3PBの他方の電極(トッププレート)は、スイッチSW4を介してコモンモード電位VCMに接続されるとともに、スイッチSW6を介してオペアンプOPAの負側入力ノードVAに接続される。

【0054】

容量C3MAの一方の電極(ボトムプレート)は、スイッチSW12を介してリファレンス電圧Vrefに接続されるとともに、スイッチSW13を介して接地電圧VSS(0(V))に接続される。容量C3MBの一方の電極(ボトムプレート)は、スイッチSW14を介して接地電圧VSS(0(V))に接続されるとともに、スイッチSW15を介してリファレンス電圧Vrefに接続される。また、容量C3MA及びC3MBの他方の電極(トッププレート)は、スイッチSW5を介してコモンモード電位VCMに接続されるとともに、スイッチSW7を介してオペアンプOPAの正側入力ノードVAに接続される。

【0055】

図1に示す回路は、クロック信号等に基づいて、信号φ1が“1”であるφ1期間と信号φ2が“1”であるφ2期間とを交互に繰り返し、入力される差動アナログ信号(VIP−VIM)から、基準信号を減じた信号又は加えた信号を積分し、その結果を差動信号(VOP−VOM)により出力する。基準信号を減じるか加えるかは、信号yによって決定される。

【0056】

φ1期間においては、図2Aに示すように各スイッチSW1〜SW15が制御されて信号のサンプリングが行われる。すなわち、スイッチSW1、SW2、SW4、SW5、SW8、SW10、SW12、及びSW14が導通(オン)とされ、スイッチSW3、SW6、SW7、SW9、SW11、SW13、及びSW15が非導通(オフ)とされる。

【0057】

これにより、容量C1Pは、ボトムプレートに電圧VIPが印加され、トッププレートがコモンモード電位VCMに接続される。容量C1Mは、ボトムプレートに電圧VIMが印加され、トッププレートがコモンモード電位VCMに接続される。したがって、容量C1P、C1Mにコモンモード電位VCMと入力電圧VIP、VIMとの差に応じた電荷がサンプリングされる。また、容量C3PA及びC3MBのボトムプレートは接地電圧VSS(0(V))に接続され、容量C3PB及びC3MAのボトムプレートはリファレンス電圧Vrefに接続される。容量C3PA、C3PB、C3MA、及びC3MBのトッププレートはコモンモード電位VCMに接続される。したがって、容量C3PA及びC3MBはそれぞれコモンモード電位VCMに充電され、容量C3PB及びC3MAのボトムプレートは(コモンモード電位VCM−リファレンス電圧Vref)に充電される。

【0058】

φ2期間においては、入力信号に対して基準信号を加える場合、すなわち信号y=−1の場合には、図2Bに示すように各スイッチSW1〜SW15が制御されて信号の加算及び積分が行われる。すなわち、スイッチSW1、SW2、SW4、SW5、SW9、SW10、SW13、及びSW14が非導通(オフ)とされ、スイッチSW3、SW6、SW7、SW8、SW11、SW12、及びSW15が導通(オン)とされる。

【0059】

これにより、容量C3PBのボトムプレートが接地電圧VSS(0(V))に接続され、容量C3MBのボトムプレートがリファレンス電圧Vrefに接続されるよう切り替えられる。容量C3PA及びC3MAのボトムプレートの接続は切り替わらない。この動作では、容量C3PBのボトムプレートの電圧がリファレンス電圧Vrefから接地電圧VSS(0(V))に、容量C3MBのボトムプレートの電圧が接地電圧VSS(0(V))からリファレンス電圧Vrefに変化するだけである。そのため、φ2期間における入力ノードVAの電位は、コモンモード電位VCMとなる。詳細には、容量C3PB及びC3MBは、φ1期間においてサンプリングを行い、φ2期間において容量分圧回路を形成し入力ノードVAの電位を決定する。式で表すと、

(VCM−0)C3+(VCM−Vref)C3=(VA−Vref)C3+(VA−0)C3

が成り立つ。よって、

VA=VCM

となる。つまり、入力ノードVAの電位は、リファレンス電圧Vrefや入力される差動アナログ信号のコモンモード電位VICMにかかわらず、回路におけるコモンモード電位VCMとなる。

【0060】

また、φ2期間において、入力信号に対して基準信号を減じる場合、すなわち信号y=+1の場合には、図2Cに示すように各スイッチSW1〜SW15が制御されて信号の加算及び積分が行われる。すなわち、スイッチSW1、SW2、SW4、SW5、SW8、SW11、SW12、及びSW15が非導通(オフ)とされ、スイッチSW3、SW6、SW7、SW9、SW10、SW13、及びSW14が導通(オン)とされる。

【0061】

これにより、容量C3PAのボトムプレートがリファレンス電圧Vrefに接続され、容量C3MAのボトムプレートが接地電圧VSS(0(V))に接続されるよう切り替えられる。容量C3PB及びC3MBのボトムプレートの接続は切り替わらない。この動作では、容量C3PAのボトムプレートの電圧が接地電圧VSS(0(V))からリファレンス電圧Vrefに、容量C3MAのボトムプレートの電圧がリファレンス電圧Vrefから接地電圧VSS(0(V))に変化するだけである。そのため、入力信号に対して基準信号を減じる場合にも、φ2期間における入力ノードVAの電位は、リファレンス電圧Vrefや入力される差動アナログ信号のコモンモード電位VICMにかかわらず、回路におけるコモンモード電位VCMとなる。

【0062】

以上のように、図1に示した演算回路を用いてΔΣA/D変換器を構成した場合には、任意のコモンモード電位の差動アナログ信号を入力でき、かつ任意のリファレンス電圧を設定することができる。

【0063】

また、1ビットΔΣA/D変換器には、内部DACが2値であるために内部DACの非線形性が存在せず、A/D変換の直線性を高くできるという利点があるが、図1に示した演算回路を用いてΔΣA/D変換器を構成してもこの利点は失われることはない。図2Bに示した状態ではリファレンス容量はC3PB及びC3MBのみが回路動作に寄与し、図2Cに示した状態では、リファレンス容量はC3PA及びC3MAのみが回路動作に寄与する。すなわち、入力信号に対して基準信号を加える場合に使用される容量と、入力信号に対して基準信号を減じる場合に使用される容量とが常に等しいため、非線形性が生じない。

【0064】

図3は、本発明の一実施形態によるΔΣA/D変換器の(1ビットDAC+加算+積分)演算回路の他の回路構成例を示す図である。図3には、相関二重サンプリング(CDS)を用いたΔΣA/D変換器に対して適用した例を示している。

【0065】

図3において、C1P及びC1Mはサンプリング容量であり、C2P及びC2Mは積分容量である。また、C3PA、C3PB、C3MA、及びC3MBは、リファレンス容量である。すなわち、本実施形態における演算回路では、正側ノードに2つのリファレンス容量C3PA及びC3PBが設けられ、負側ノードに2つのリファレンス容量C3MA及びC3MBが設けられる。容量C1P及びC1Mの容量値は同一のC1とし、容量C2P及びC2Mの容量値は同一のC2とし、容量C3PA、C3PB、C3MA、及びC3MBの容量値は同一のC3とする。

【0066】

OPAは全差動オペアンプである。また、VIPは差動アナログ信号の正側入力ノードであり、VIMは差動アナログ信号の負側入力ノードである。VOPはオペアンプOPAの正側出力ノード、VOMはオペアンプOPAの負側出力ノードである。なお、VOP及びVOMは図3に示す演算回路における差動信号の出力ノードでもある。Vrefはリファレンス電圧(リファレンス信号)である。

【0067】

また、SW1〜SW3、S4〜S7、及びSW8〜SW15は、スイッチである。スイッチSW1、SW2、S6、及びS7は、信号φ1が“1”であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW3、S4、S5は、信号φ2が“1”であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。

【0068】

スイッチSW8及びSW12は、信号φ1が“1”であるとき、又は信号φ2が“1”かつ信号y=−1であるときに、導通(オン)とされ、そうでないときには非導通(オフ)とされる。なお、信号yは、ΔΣ変調器の出力(詳細にはΔΣ変調器が有する量子化器の出力)であり、値としては“+1”又は“−1”の2値(1ビット)をとる。スイッチSW9及びSW13は、信号φ2が“1”かつ信号y=+1であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。

【0069】

スイッチSW10及びSW14は、信号φ1が“1”であるとき、又は信号φ2が“1”かつ信号y=+1であるときに、導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW11及びSW15は、信号φ2が“1”かつ信号y=−1であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。

【0070】

容量C1Pは、一方の電極(ボトムプレート)がスイッチSW1を介して正側入力ノードVIPに接続され、他方の電極(トッププレート)がオペアンプOPAの負側入力ノードに接続される。容量C1Mは、一方の電極(ボトムプレート)がスイッチSW2を介して負側入力ノードVIMに接続され、他方の電極(トッププレート)がオペアンプOPAの正側入力ノードに接続される。また、容量C1P及びC1Mのボトムプレートは、スイッチSW3を介して互いに接続される。

【0071】

容量C2Pは、一方の電極がオペアンプOPAの正側出力ノードVOPに接続され、他方の電極がスイッチS4を介してオペアンプOPAの負側入力ノードに接続される。容量C2Mは、一方の電極がオペアンプOPAの負側出力ノードVOMに接続され、他方の電極がスイッチS5を介してオペアンプOPAの正側入力ノードに接続される。すなわち、オペアンプOPAの負側入力ノードと正側出力ノードVOPとの間に、スイッチS4及び容量C2Pが直列に接続され、オペアンプOPAの正側入力ノードと負側出力ノードVOMとの間に、スイッチS5及び容量C2Mが直列に接続される。

【0072】

容量C3PAの一方の電極(ボトムプレート)は、スイッチSW8を介して接地電圧VSS(0(V))に接続されるとともに、スイッチSW9を介してリファレンス電圧Vrefに接続される。容量C3PBの一方の電極(ボトムプレート)は、スイッチSW10を介してリファレンス電圧Vrefに接続されるとともに、スイッチSW11を介して接地電圧VSS(0(V))に接続される。また、容量C3PA及びC3PBの他方の電極(トッププレート)は、オペアンプOPAの負側入力ノードに接続される。

【0073】

容量C3MAの一方の電極(ボトムプレート)は、スイッチSW12を介してリファレンス電圧Vrefに接続されるとともに、スイッチSW13を介して接地電圧VSS(0(V))に接続される。容量C3MBの一方の電極(ボトムプレート)は、スイッチSW14を介して接地電圧VSS(0(V))に接続されるとともに、スイッチSW15を介してリファレンス電圧Vrefに接続される。また、容量C3MA及びC3MBの他方の電極(トッププレート)は、オペアンプOPAの正側入力ノードに接続される。

【0074】

オペアンプOPAの正側出力ノードVOPとオペアンプOPAの負側入力ノードとがスイッチS6を介して接続され、オペアンプOPAの負側出力ノードVOMとオペアンプOPAの正側入力ノードとがスイッチS7を介して接続される。

【0075】

図3に示した演算回路は、オペアンプで生じるMOSトランジスタの1/f雑音がA/D変換特性を劣化させるという問題を回避するためにCDSの機構を備えている。図3に示した演算回路では、φ1期間において、オペアンプOPAの負側入力ノードと正側出力ノードとがスイッチS6を介して接続されるとともに、オペアンプOPAの正側入力ノードと負側出力ノードとがスイッチS7を介して接続される。その際、オペアンプOPAの2つの入力ノード間には、オペアンプOPAの入力オフセット電圧及び雑音による電圧(雑音電圧)が生じる。そのため、容量C1P及びC1Mには、信号による電荷とともに、オペアンプOPAの入力オフセット電圧及び雑音電圧による電荷がサンプリングされる。

【0076】

次に、φ2期間へ遷移すると、容量C1P及びC1Mにサンプリングされた信号による電荷とオペアンプOPAの入力オフセット電圧及び雑音電圧による電荷が容量C2P及びC2Mに転送される。ここで、φ2期間であっても、オペアンプOPAの入力オフセット電圧及び雑音電圧は存在するが、φ1期間においてサンプリングされ容量C1P及びC1Mから転送された電荷によってキャンセルされる。その結果、入力オフセット電圧は除去され、また、少なくともサンプリング周波数より低い周波数の雑音も除去されるので、高精度のA/D変換が可能になる。

【0077】

図3に示した演算回路を用いてΔΣA/D変換器を構成した場合に、任意のコモンモード電位の差動アナログ信号を入力でき、かつ任意のリファレンス電圧を設定することができることは、図1に示した演算回路と同様である。

【0078】

図4は、本実施形態における1ビット2次ΔΣ変調器の回路構成例を示す図である。

図4において、C1P及びC1Mは第1積分器のサンプリング容量、C2P及びC2Mは第1積分器の積分容量、C3PA、C3PB、C3MA、及びC3MBは、第1積分器のリファレンス容量である。また、C4P及びC4Mは第2積分器のサンプリング容量、C6P及びC6Mは第2積分器の積分容量、C5PA、C5PB、C5MA、及びC5MBは、第2積分器のリファレンス容量である。容量C1P及びC1Mの容量値は同一とし、容量C2P及びC2Mの容量値は同一とし、容量C3PA、C3PB、C3MA、及びC3MBの容量値は同一とする。また、容量C4P及びC4Mの容量値は同一とし、容量C5PA、C5PB、C5MA、及びC5MBの容量値は同一とし、容量C6P及びC6Mの容量値は同一とする。

【0079】

OPA1及びOPA2は全差動オペアンプであり、CMPは比較器であり、FFはDフリップフロップである。また、VIPは差動アナログ信号の正側入力ノードであり、VIMは差動アナログ信号の負側入力ノードである。VCMはコモンモード電位であり、Vrefはリファレンス電圧(リファレンス信号)であり、YはΔΣ変調器の出力であり、YXは出力Yの反転信号である。

【0080】

また、SW1〜SW15は、スイッチである。スイッチSW4、SW5、SW14、及びSW15は、クロック信号CK1が“1”であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW1、SW2、SW10、及びSW11は、クロック信号CK1Dが“1”であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW6、SW7、SW12、及びSW13は、クロック信号CK2が“1”であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW3、SW8、及びSW9は、クロック信号CK2Dが“1”であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。

【0081】

ここで、クロック信号CK1Dは、クロック信号CK1をわずかに遅延させたクロック信号であり、クロック信号CK2Dは、クロック信号CK2をわずかに遅延させたクロック信号である。また、クロック信号CK1とクロック信号CK2は逆極性であり、かつ同時には“1”とならないノンオーバーラップの関係を有する。より詳細には、クロック信号CK1及びCK1Dの少なくとも一方が“1”のときにクロック信号CK2及びCK2Dはともに“0”であり、クロック信号CK2及びCK2Dの少なくとも一方が“1”のときにクロック信号CK1及びCK1Dはともに“0”である。

【0082】

容量C1Pは、一方の電極(ボトムプレート)がスイッチSW1を介して正側入力ノードVIPに接続され、他方の電極(トッププレート)がオペアンプOPA1の負側入力ノードに接続される。容量C1Mは、一方の電極(ボトムプレート)がスイッチSW2を介して負側入力ノードVIMに接続され、他方の電極(トッププレート)がオペアンプOPA1の正側入力ノードに接続される。また、容量C1P及びC1Mのボトムプレートは、スイッチSW3を介して互いに接続される。

【0083】

容量C2Pは、一方の電極がオペアンプOPA1の正側出力ノードに接続され、他方の電極がスイッチSW6を介してオペアンプOPA1の負側入力ノードに接続される。容量C2Mは、一方の電極がオペアンプOPA1の負側出力ノードに接続され、他方の電極がスイッチSW7を介してオペアンプOPA1の正側入力ノードに接続される。また、オペアンプOPA1の正側出力ノードと負側入力ノードはスイッチSW4を介して接続され、オペアンプOPA1の負側出力ノードと正側入力ノードはスイッチSW5を介して接続される。

【0084】

容量C3PAの一方の電極(ボトムプレート)は、クロック信号CK2Dが“1”かつ出力Yが“1”のときにリファレンス電圧Vrefに接続され、その他のときは接地電圧VSS(0(V))に接続される。また、容量C3MAの一方の電極(ボトムプレート)は、クロック信号CK2Dが“1”かつ出力Yが“1”のときに接地電圧VSS(0(V))に接続され、その他のときはリファレンス電圧Vrefに接続される。同様に、容量C3PBの一方の電極(ボトムプレート)は、クロック信号CK2Dが“1”かつ反転信号YXが“1”のときに接地電圧VSS(0(V))に接続され、その他のときはリファレンス電圧Vrefに接続される。また、容量C3MBの一方の電極(ボトムプレート)は、クロック信号CK2Dが“1”かつ反転信号YXが“1”のときにリファレンス電圧Vrefに接続され、その他のときは接地電圧VSS(0(V))に接続される。また、容量C3PA及びC3PBの他方の電極(トッププレート)はオペアンプOPA1の負側入力ノードに接続され、容量C3MA及びC3MBの他方の電極(トッププレート)はオペアンプOPA1の正側入力ノードに接続される。

【0085】

容量C4Pは、一方の電極(ボトムプレート)がスイッチSW8を介してオペアンプOPA1の正側出力ノードに接続され、他方の電極(トッププレート)がスイッチSW14を介してオペアンプOPA2の負側入力ノードに接続される。容量C4Mは、一方の電極(ボトムプレート)がスイッチSW9を介してオペアンプOPA1の負側出力ノードに接続され、他方の電極(トッププレート)がスイッチSW15を介してオペアンプOPA2の正側入力ノードに接続される。また、容量C4P及びC4Mのボトムプレートは、スイッチSW10、SW11を介してコモンモード電位VCMに接続され、容量C4P及びC4Mのトッププレートは、スイッチSW12、SW13を介してコモンモード電位VCMに接続される。

【0086】

容量C6Pは、一方の電極がオペアンプOPA2の正側出力ノードに接続され、他方の電極がオペアンプOPA2の負側入力ノードに接続される。容量C6Mは、一方の電極がオペアンプOPA2の負側出力ノードに接続され、他方の電極がオペアンプOPA2の正側入力ノードに接続される。

【0087】

容量C5PAの一方の電極(ボトムプレート)は、クロック信号CK1Dが“1”かつ出力Yが“1”のときにリファレンス電圧Vrefに接続され、その他のときは接地電圧VSS(0(V))に接続される。また、容量C5MAの一方の電極(ボトムプレート)は、クロック信号CK1Dが“1”かつ出力Yが“1”のときに接地電圧VSS(0(V))に接続され、その他のときはリファレンス電圧Vrefに接続される。同様に、容量C5PBの一方の電極(ボトムプレート)は、クロック信号CK1Dが“1”かつ反転信号YXが“1”のときに接地電圧VSS(0(V))に接続され、その他のときはリファレンス電圧Vrefに接続される。また、容量C5MBの一方の電極(ボトムプレート)は、クロック信号CK1Dが“1”かつ反転信号YXが“1”のときにリファレンス電圧Vrefに接続され、その他のときは接地電圧VSS(0(V))に接続される。また、容量C5PA及びC5PBの他方の電極(トッププレート)はスイッチSW14を介してオペアンプOPA2の負側入力ノードに接続され、容量C5MA及びC5MBの他方の電極(トッププレート)はスイッチSW15を介してオペアンプOPA2の正側入力ノードに接続される。

【0088】

比較器CMPは、負側入力ノードがオペアンプOPA2の正側出力ノードに接続され、正側入力ノードがオペアンプOPA2の負側出力ノードに接続される。DフリップフロップFFは、クロック信号CK1で動作し、比較器CMPの出力を取り込んで出力Yとして出力する。

【0089】

図4に示すΔΣ変調器では、第2積分器の雑音はA/D変換特性にはほとんど影響を及ぼさないため、第1積分器にのみCDS(相関二重サンプリング)の機能を含み、第2積分器はCDSの機能を含まない。図4に示すΔΣ変調器における第1積分器は図3に示した演算回路に相当し、第2積分器は図1に示した演算回路に相当する。

【0090】

第1積分器は、クロック信号CK1(CK1D)が“1”の期間に信号のサンプリングを行い、クロック信号CK2(CK2D)が“1”の期間に信号の加算及び積分を行う。また、第2積分器は、クロック信号CK2(CK2D)が“1”の期間に信号のサンプリングを行い、クロック信号CK1(CK1D)が“1”の期間に信号の加算及び積分を行う。

【0091】

第1積分器におけるリファレンス容量C3PA、C3PB、C3MA、及びC3MBのボトムプレートの電圧は、出力Yとその反転信号YXとクロック信号CK2Dによって制御される。第1積分器で信号のサンプリングを行う期間においてクロック信号CK2Dは“0”であるので、容量C3PA及びC3MBのボトムプレートの電圧は接地電圧(0(V))とされ、容量C3PB及びC3MAのボトムプレートの電圧はリファレンス電圧Vrefとされる。

【0092】

次に、クロック信号CK2Dが“1”の期間に遷移すると、出力Yが“1”の場合には、容量C3PAのボトムプレートの電圧は接地電圧(0(V))からリファレンス電圧Vrefに変化し、容量C3MAのボトムプレートの電圧はリファレンス電圧Vrefから接地電圧(0(V))に変化する。なお、容量C3PBのボトムプレートの電圧はリファレンス電圧Vrefのままであり、容量C3MBのボトムプレートの電圧は接地電圧(0(V))のままである。したがって、オペアンプOPA1における入力ノードの電位は、前述したようにコモンモード電位VCMに収束することとなる。

【0093】

一方、クロック信号CK2Dが“1”の期間に遷移したとき、反転信号YXが“1”の場合には、容量C3PBのボトムプレートの電圧はリファレンス電圧Vrefから接地電圧(0(V))に変化し、容量C3MBのボトムプレートの電圧は接地電圧(0(V))からリファレンス電圧Vrefに変化する。なお、容量C3PAのボトムプレートの電圧は接地電圧(0(V))のままであり、容量C3MAのボトムプレートの電圧はリファレンス電圧Vrefのままである。したがって、オペアンプOPA1における入力ノードの電位は、前述したようにコモンモード電位VCMに収束することとなる。

【0094】

同様に、第2積分器におけるリファレンス容量C5PA、C5PB、C5MA、及びC5MBのボトムプレートの電圧は、出力Yとその反転信号YXとクロック信号CK1Dによって制御される。第2積分器で信号のサンプリングを行う期間においてクロック信号CK1Dは“0”であるので、容量C5PA及びC5MBのボトムプレートの電圧は接地電圧(0(V))とされ、容量C5PB及びC5MAのボトムプレートの電圧はリファレンス電圧Vrefとされる。

【0095】

次に、クロック信号CK1Dが“1”の期間に遷移すると、出力Yが“1”の場合には、容量C5PAのボトムプレートの電圧は接地電圧(0(V))からリファレンス電圧Vrefに変化し、容量C5MAのボトムプレートの電圧はリファレンス電圧Vrefから接地電圧(0(V))に変化する。なお、容量C5PBのボトムプレートの電圧はリファレンス電圧Vrefのままであり、容量C5MBのボトムプレートの電圧は接地電圧(0(V))のままである。したがって、オペアンプOPA2における入力ノードの電位は、前述したようにコモンモード電位VCMに収束することとなる。

【0096】

一方、クロック信号CK1Dが“1”の期間に遷移したとき、反転信号YXが“1”の場合には、容量C5PBのボトムプレートの電圧はリファレンス電圧Vrefから接地電圧(0(V))に変化し、容量C5MBのボトムプレートの電圧は接地電圧(0(V))からリファレンス電圧Vrefに変化する。なお、容量C5PAのボトムプレートの電圧は接地電圧(0(V))のままであり、容量C5MAのボトムプレートの電圧はリファレンス電圧Vrefのままである。したがって、オペアンプOPA2における入力ノードの電位は、前述したようにコモンモード電位VCMに収束することとなる。

【0097】

以上のように、図4に示したΔΣ変調器ではオペアンプOPA1及びOPA2の入力ノードの電位は、リファレンス電圧Vrefや入力される差動アナログ信号のコモンモード電位VICMにかかわらず、回路におけるコモンモード電位VCMとなる。図4に示したΔΣ変調器によれば、任意のコモンモード電位の差動アナログ信号を入力でき、かつ任意のリファレンス電圧を設定することができるΔΣA/D変換器を提供することが可能となる。

【0098】

図5は、図4に示したΔΣ変調器の動作の流れを示す図である。

図5において、CK1、CK1D、CK2、CK2Dはクロック信号を示し、SICA及びSIOAは第1積分器の動作及び出力を示し、SICB及びSIOBは第2積分器の動作及び出力を示している。また、CMPOは比較器の出力を示し、DFFはDフリップフロップの出力を示し、FBBは第2積分器へのフィードバック信号を示し、FBAは第1積分器へのフィードバック信号を示している。前述したように図4に示したΔΣ変調器では、クロック信号CK1(CK1D)が“1”の期間に、第1積分器は信号のサンプリングを行っており、第2積分器は信号の加算及び積分を行っている。また、クロック信号CK2(CK2D)が“1”の期間に、第1積分器は信号の加算及び積分を行っており、第2積分器は信号のサンプリングを行っている。

【0099】

まず、時刻T1にて、第1積分器が、1回目の信号のサンプリング(S1)を行う。続く時刻T2にて、第1積分器が、1回目の信号の加算及び積分(I1)を行う。また、それと同時に、第2積分器が、1回目の信号(第1積分器の出力)のサンプリング(S1)を行う。次の時刻T3にて、第1積分器が、2回目の信号のサンプリング(S2)を行うとともに、第2の積分器が、1回目の信号の加算及び積分(I1)を行う。

【0100】

次の時刻T4にて、第1積分器が、2回目の信号の加算及び積分(I2)を行う。また、それと同時に、第2積分器が、2回目の信号のサンプリング(S2)を行う。このとき、時刻T4となる直前に、比較器CMPが第2積分器の出力信号SIOBの正負を判定する。また、その際、DフリップフロップFFはスルー状態となっており、比較器CMPの出力CMPOによってDフリップフロップFFの出力DFFOが更新される。更新されたDフリップフロップFFの出力DFFOにより、信号のサンプリング(S2)に移行した第2積分器へフィードバック値FBBが供給される。このようにして1サイクル後に第2積分器に出力値がフィードバックされる。

【0101】

次の時刻T5にて、第1積分器が、3回目の信号のサンプリング(S3)を行うとともに、第2積分器が、2回目の信号の加算及び積分(I2)を行う。第1積分器における信号のサンプリングでは、先に更新されたDフリップフロップFFの出力DFFOにより第1積分器へフィードバック値FBAが供給される。このようにして2サイクル後に第1積分器に出力値がフィードバックされる。以降、時刻T6、T7、・・・と動作を順次繰り返し行うことで入力される差動アナログ信号のA/D変換を行う。

【0102】

なお、前述した説明では1ビット2次ΔΣ変調器を一例に説明したが、本発明はこれに限定されるものではなく、ビット幅や伝達関数が異なるΔΣ変調器を有するΔΣA/D変換器についても本発明は適用可能である。

【0103】

なお、前記実施形態は、何れも本発明を実施するにあたっての具体化のほんの一例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、またはその主要な特徴から逸脱することなく、様々な形で実施することができる。

【符号の説明】

【0104】

C1P、C1M サンプリング容量

C2P、C2M 積分容量

C3PA、C3PB、C3MA、C3MB リファレンス容量

C4P、C4M サンプリング容量

C5PA、C5PB、C5MA、C5MB リファレンス容量

C6P、C6M 積分容量

OPA 全差動オペアンプ

SW1〜SW15 スイッチ

VCM 回路のコモンモード電位

Vref リファレンス電圧

MOD ΔΣ変調器

FLT デシメーションフィルタ

【技術分野】

【0001】

本発明は、デルタシグマ型A/D変換器(アナログデジタル変換器)に関する。

【背景技術】

【0002】

デルタシグマ型アナログデジタル変換器(ΔΣA/D変換器)は、オーバーサンプリング技術に基づいたA/D変換方式で、オーディオやセンサ等の比較的速度の遅い信号のデジタイズのために用いられている。ΔΣA/D変換器は、単調増加性に優れ、比較的単純な回路で例えば16ビット等の高分解能を達成できる。ΔΣA/D変換器は、例えばマイクロコントローラ(MCU)に内蔵されるA/D変換回路として用いられている。

【0003】

ΔΣA/D変換器は、入力アナログ信号をΔΣ変調するΔΣ変調器、及びΔΣ変調信号からA/D変換結果を生成するデシメーションフィルタを有する。図6は、1ビットΔΣ変調器を含むΔΣA/D変換器の構成例を示す図である。図6において、MODはΔΣ変調器であり、FLTはデシメーションフィルタである。ΔΣ変調器MODは、入力アナログ信号Vinの信号周波数の数十倍から数百倍程度の周波数(オーバーサンプリング周波数)でΔΣ変調し、1ビットΔΣ変調信号D1を出力する。1ビットΔΣ変調信号D1は、パルス密度変調信号であり、入力アナログ信号Vinが大きい場合には“1”の含まれる割合が増し、入力アナログ信号Vinが小さい場合には“0”の含まれる割合が増す。デシメーションフィルタFLTは、ΔΣ変調器MODにより生成された1ビットΔΣ変調信号D1から信号帯域成分を抽出し、所望のビット幅へ拡張するとともに、低いデータレートにダウンサンプリングし、その結果をA/D変換結果として出力する。A/D変換結果は、入力アナログ信号Vinの大小に対応したデジタルコードとして出力される。図6に示す例では、16ビットデジタル出力D2がA/D変換器でのA/D変換結果として出力される。

【0004】

図7は、ΔΣA/D変換器が有するΔΣ変調器を実現するための信号経路の例を示す図である(非特許文献3:Fig.1、非特許文献4:Fig.1参照)。ΔΣ変調器には、出力コードのビット幅、雑音伝達関数の次数、その他信号経路の構造等に様々なバリエーションが存在するが、ここでは1ビット2次ΔΣ変調器を実現するための信号経路を一例として示している。図7において、AD1、AD2、AD3、AD4は、入力される2つの信号を加算して加算結果を出力する加算器である。図中、“−”(マイナス記号)が付されている加算器は、その入力の符号を反転した後に加算することを意味する。また、DL1、DL2、DL3、DL4は、入力される信号を1サイクル分遅延して出力する遅延器である。AM1は入力される信号を2倍して出力する増幅器であり、Q1は入力される信号を量子化する量子化器である。ここで、ΔΣ変調器は、多くの場合、スイッチドキャパシタ回路等によって構成され、演算が離散時間的に行われるため、遅延器を用いてサイクル間の時間関係を示している。

【0005】

図7において、加算器AD1は、入力アナログ信号Uから出力ΔΣ変調信号Vを減じ、結果を信号S3として出力する。加算器AD2は、遅延器DL1により生成された1サイクル前の加算器AD2自身の出力に信号S3を加え、結果を信号S4として出力する。すなわち、加算器AD2と遅延器DL1との組は、信号S3を時間で積分する積分器として機能する。加算器AD3は、遅延器DL2により生成された1サイクル前の加算器AD2の出力である信号S1から、増幅器AM1より出力された信号S7(2倍にされた出力ΔΣ変調信号V)を減じ、結果を信号S5として出力する。加算器AD4は、遅延器DL3により生成された1サイクル前の加算器AD4自身の出力に信号S5を加え、結果を信号S6として出力する。すなわち、加算器AD4と遅延器DL3との組は、信号S5を時間で積分する積分器として機能する。量子化器Q1は、遅延器DL4により生成された1サイクル前の加算器AD4の出力である信号S2を量子化し、“1”又は“−1”の出力ΔΣ変調信号Vを出力する。量子化器Q1は、入力される信号S2がS2>0である場合には“1”を出力し、S2<0である場合には“−1”を出力する。すなわち、量子化器Q1の出力である出力ΔΣ変調信号Vは、2値(1ビット)の信号である。

【0006】

図7に信号経路を示したΔΣ変調器では、出力ΔΣ変調信号Vは、加算器AD1及びAD3を介して二重に負帰還されている。そのため、信号S2が増加すれば出力ΔΣ変調信号Vが“1”となって信号S7が“2”になるので、信号S5及びS6が減少する方向に働き、結果として信号S2が減少する。また、信号S1が増加すれば、信号S5、S6及びS2が増加する方向に働き、出力ΔΣ変調信号Vが“1”となる。出力ΔΣ変調信号Vが“1”となると、信号S3は減少する方向に作用し、また信号S5も減少する方向に作用し、その結果、信号S1及びS2が減少する。このような負帰還によって、入力アナログ信号Uが過大ではない領域では、図7に示した信号経路は発散しないことが知られている。例えば、図7に信号経路を示したような演算回路を使用することで、図6に示したΔΣ変調器MODを実現できる。

【0007】

図8は、図7に示した1ビット2次ΔΣ変調器の信号経路をz演算子を用いて表記した図である。図8において、AD1、AD2は加算器であり、INT1、INT2は積分器である。また、AM1は入力される信号を2倍に増幅する増幅器であり、Q1は入力される信号を量子化する量子化器である。U1は、加算器AD1と積分器INT1により構成される演算ブロックである。図8に示すように、図7において加算器AD2及び遅延器DL1、DL2で構成される演算部は積分器INT1として表現でき、図7において加算器AD4及び遅延器DL3、DL4で構成される演算部は積分器INT2として表現できる。また、量子化器Q1は、入力される信号の大小を判別して2値化するが、この演算は入力された信号に量子化雑音を加えるとモデル化することができる。そこで、図8においては、信号S2に量子化誤差Eを加えた値を出力するブロックとしている。

【0008】

図7に示した信号経路を、図8に示すようにz演算子を用いて表記し整理すると、量子化雑音Eから出力Vへの雑音伝達関数NTF(z)、及び入力Uから出力Vへの信号伝達関数STF(z)は、

NTF(z)=(1−z-1)2

STF(z)=z-2

である。これは、入力Uはそのまま出力Vへ現れ、量子化雑音Eは高域へ拡散され出力されることを示している。ΔΣA/D変換器は、前述したようなΔΣ変調器の後段にデシメーションフィルタを設け、高域に拡散された量子化雑音を除去してA/D変換結果を得る。

【0009】

次に、前述したΔΣ変調器を実現するための信号経路を、半導体集積回路上に形成するための回路構成について説明する。図9は、シングルエンド構造の(加算+積分)演算回路の一例を示す図である(特許文献1:図1、特許文献3:図3・図6、特許文献4:Fig.6参照)。図9(A)に示す演算ブロックの機能を実現する回路構成の一例を図9(B)に示している。すなわち、図9(B)に示す演算回路は、図9(A)に示すように入力信号(入力電圧)V1、V2を加算する加算器ADD、及び加算器ADDでの加算結果を積分して演算結果を出力信号(出力電圧)Voutとして出力する積分器INTからなる演算ブロックを実現するものである。

【0010】

図9(B)において、C1、C2はサンプリング容量であり、C3は積分容量である。また、OPAはオペアンプであり、SW1、SW2、SW3、SW4、SW5、SW6はスイッチである。スイッチSW1、SW3、SW5は、信号φ1により導通/非導通(オン/オフ)が制御され、スイッチSW2、SW4、SW6は、信号φ2により導通/非導通(オン/オフ)が制御される。ここで、容量C1、C2、C3のそれぞれの容量値をC1、C2、C3とする。また、容量C1やC2において、左側ノード(スイッチSW1やSW3側の電極)をボトムプレートと呼び、右側ノード(スイッチSW6側の電極)をトッププレートと呼ぶ。

【0011】

図9(B)に示す回路は、クロック信号等に基づいて信号φ1、φ2を制御し、スイッチSW1、SW3、SW5の組とスイッチSW2、SW4、SW6の組とを組毎に交互にオンすることによって、入力信号V1とV2の加算及びその加算結果の積分を行う。

【0012】

まず、信号φ1によりスイッチSW1、SW3、SW5がオンし、信号φ2によりスイッチSW2、SW4、SW6がオフすると、容量C1のボトムプレートには電圧V1が印加され、容量C2のボトムプレートには電圧V2が印加される。また、容量C1、C2のトッププレートは0(V)に接続される。このとき、容量C1、C2にそれぞれ蓄えられる電荷Q1、Q2は、

Q1=−C1・V1

Q2=−C2・V2

であり、容量C1、C2に入力電圧V1、V2に応じた電荷がサンプリングされる。また、このときの出力電圧Voutの電圧値がVout1であるとすれば、容量C3に蓄えられる電荷Q3は、

Q3=−C3・Vout1

である。

【0013】

次に、信号φ1によりスイッチSW1、SW3、SW5がオフし、信号φ2によりスイッチSW2、SW4、SW6がオンすると、容量C1、C2のボトムプレートは0(V)に、容量C1、C2のトッププレートはオペアンプOPAの負側入力端子に接続される。その結果、オペアンプOPAの作用によって容量C1、C2に蓄えられた電荷が容量C3に転送されるように動作し、出力電圧Voutの電圧値がVout1からVout2に変化する。電荷保存則により、

−C3・Vout2=Q1+Q2+Q3

が成り立つので、電圧値Vout2は、

Vout2=Vout1+(C1/C3)V1+(C2/C3)V2

となる。つまり、一連の動作によって、出力電圧VoutとしてVout1に(C1/C3)V1と(C2/C3)V2とを加えたものが出力される。その後、信号φ1によりスイッチSW1、SW3、SW5がオンし、信号φ2によりスイッチSW2、SW4、SW6がオフするようにして、前述の動作を繰り返し行うことによって、入力信号V1とV2を加算し、その加算結果を積分する演算が実現される。

【0014】

以上の動作をz演算子で表記すれば、

Vout(z)=[(C1/C3)V1(z)+(C2/C3)V2(z)]/(z−1)

である。図9(B)に示した演算回路では、入力信号(入力電圧)V1は(C1/C3)倍にスケールされて演算され、入力信号(入力電圧)V2は(C2/C3)倍にスケールされて演算される。回路における信号の飽和を防ぐ目的や、その他信号経路設計の都合等に応じて(C1/C3)や(C2/C3)の比率は適宜変化される。

【0015】

図10は、オペアンプの入力部分の回路構成を示す図である(非特許文献5:Fig.2参照)。図10において、M1、M2、M3はN型MOSトランジスタである。MOSトランジスタM1は、MOSトランジスタM2及びM3をバイアスする役割を有する。MOSトランジスタM2、M3は、ソースを共通としたトランジスタ対を構成する。MOSトランジスタM2のゲートがオペアンプの正側入力ノード(正側入力端子)IMに対応しており、MOSトランジスタM3のゲートがオペアンプの負側入力ノード(負側入力端子)IPに対応している。

【0016】

図10に示す差動対が正常に動作するためには、MOSトランジスタM2及びM3のゲート−ソース間電圧は、トランジスタの閾値電圧Vthに0.2(V)程度のオーバードライブ電圧Vovを加えた電圧が必要である。例えば、トランジスタの閾値電圧が0.6(V)であるとすれば、MOSトランジスタM2及びM3は、そのゲート−ソース間電圧が0.2(V)+0.6(V)=0.8(V)以上となるようにバイアスされなければならない。また、MOSトランジスタM1のドレイン−ソース間電圧は、回路が正常に動作するためには、例えば0.2(V)以上が必要である。

【0017】

これらの各MOSトランジスタが正常に動作するために必要な制約により、オペアンプが正常動作するためには、入力端子IM及びIPのそれぞれに対して0.2(V)+0.8(V)=1.0(V)以上の電位を印加せねばならない。例えば、電源電圧が3.0(V)である場合には、入力端子IM及びIPのそれぞれの電位が1.0(V)から3.0(V)の範囲になければオペアンプとして期待した動作をしない。このように、実際には入力端子IM及びIPのそれぞれの電位がある程度高い電位でないとオペアンプは動作しない。そのため、ΔΣA/D変換器に含まれるオペアンプでも、オペアンプの入力端子に印加される電圧は必要な範囲に含まれなくてはならない。正常動作に必要なオペアンプの入力端子の電圧範囲は、コモンモード入力電圧範囲と呼ばれている。

【0018】

前述した図9に示した演算回路はシングルエンド構造であったが、シングルエンド構造に対して大きな信号振幅を使用できることや同相雑音の影響を受けにくいなどの利点から、実際の半導体集積回路において、それら演算回路は差動構造とする場合が多い。以下、ΔΣA/D変換器で用いられる差動構造の演算回路の例を説明する。

【0019】

図11は、差動構造のスイッチドキャパシタ積分器の回路構成例を示す図である(特許文献2:図7、特許文献6:Fig.7参照)。図11において、C1P、C1Mはサンプリング容量であり、C2P、C2Mは積分容量である。また、OPAは全差動オペアンプであり、SW1、SW2、SW3、SW4、SW5、SW6、SW7、SW8はスイッチである。スイッチSW1、SW2、SW5、SW6は、信号φ1により導通/非導通(オン/オフ)が制御され、スイッチSW3、SW4、SW7、SW8は、信号φ2により導通/非導通(オン/オフ)が制御される。また、VIPは正側入力ノード、VIMは負側入力ノード、VOPは正側出力ノード、VOMは負側出力ノードである。なお、以下では、各ノードに対して入力又は出力される信号名や各ノードの電圧値も、適宜ノードに付した符号と同様の表記を用いて示す。SGは、差動入力信号(VIP−VIM)を出力する信号源である。信号源SGは、差動構造のスイッチドキャパシタ積分器が形成される半導体集積回路(IC)の外部に設けられる。

【0020】

図11に示す演算回路(スイッチドキャパシタ積分器)は、信号源SGから供給される差動入力信号(VIP−VIM)を積分し、その結果を差動出力信号(VOP−VOM)により出力する機能を有する。図11に示す演算回路では、オペアンプOPAは、コモンモード電位VCMを参照して、出力信号VOP及びVOMのコモン電位がVCMとなるように、すなわち(VOP+VOM)/2=VCMとなるようにコモンモードフィードバックを行う。なお、図11において、コモンモード電位VCMは、電源電圧VDDと接地電圧VSS(0(V))との中間電位であるとする。VICMは、入力信号VIP及びVIMの中間電位、すなわち入力信号のコモンモード電位である。また、容量C1P及びC1Mの容量値は同一のC1とし、容量C2P及びC2Mの容量値は同一のC2とする。

【0021】

図11に示す演算回路では、まず、信号φ1によりスイッチSW1、SW2、SW5、SW6がオンし、信号φ2によりスイッチSW3、SW4、SW7、SW8がオフすると、容量C1P、C1Mのボトムプレートにはそれぞれ電圧VIP、VIMが印加される。また、容量C1P、C1Mのトッププレートは、コモンモード電位VCMに接続される。このとき、容量C1P、C1Mにそれぞれ蓄えられる電荷Q1P、Q1Mは、

Q1P=(VCM−VIP)C1

Q1M=(VCM−VIM)C1

であり、容量C1P、C1Mにコモンモード電位VCMと入力電圧VIP、VIMとの差に応じた電荷がサンプリングされる。また、このときの出力信号VOPの電圧値がVOP1であるとし、出力信号VOMの電圧値がVOM1であるとすれば、容量C2P及びC2Mに蓄えられている電荷の和は、

(VOP1−VCM)C2+(VCM−VOM1)C2=(VOP1−VOM1)C2

である。

【0022】

次に、信号φ1によりスイッチSW1、SW2、SW5、SW6がオフし、信号φ2によりスイッチSW3、SW4、SW7、SW8がオンすると、容量C1P及びC1Mのボトムプレートはコモンモード電位VCMに接続される。また、容量C1PのトッププレートはオペアンプOPAの負側入力端子に接続され、容量C1MのトッププレートはオペアンプOPAの正側入力端子に接続される。その結果、オペアンプOPAの作用によって、出力信号VOPの電圧値がVOP2に変化し、出力信号VOMの電圧値がVOM2に変化する。このとき、前の状態の電荷が保存されるとすれば、

(VOP2−VOM2)C2=(VOP1−VOM1)C2+Q1P−Q1M

であるので、

(VOP2−VOM2)=(VOP1−VOM1)+(VIP−VIM)C1/C2

である。すなわち、差動出力電圧(VOP2−VOM2)は、1つ前の差動出力電圧(VOP1−VOM1)に差動入力電圧と容量比との積((VIP−VIM)C1/C2)を加えたものになる。これは1回分の積分演算に相当する。

【0023】

ここで、半導体集積回路内における差動信号のコモンモード電位VCMは、半導体集積回路の電源電圧に応じて決まる電位であり、入力信号のコモンモード電位VICMは、半導体集積回路の外部の信号源SGに応じて決まる電位であり、両者は直接関係しない。一般に、差動入力A/D変換器には差動入力信号(VIP及びVIM)を入力するための2つの入力端子は存在するが、入力信号のコモンモード電位VICMを入力するための入力端子は設けられない。コモンモード電位VCMと入力信号のコモンモード電位VICMとがどのような関係であっても、回路が差動信号の演算を正常に行うことが望ましい。

【0024】

しかしながら、図11に示した演算回路において、コモンモード電位VCMと入力信号のコモンモード電位VICMとが著しく異なる電位となった場合には、ノードVAの電位がオペアンプOPAの適切な入力電圧範囲から逸脱し、積分器が動作しない問題がある。これは、ノードVAの電位が、φ1期間にサンプリングされた容量C1P、C1Mの電荷と、φ2期間にスイッチで設定される回路による容量分圧によって決まるためである。なお、φ1期間は、信号φ1により制御されるスイッチがオンとなる期間、すなわちスイッチSW1、SW2、SW5、SW6がオンし、スイッチSW3、SW4、SW7、SW8がオフする期間である。また、φ2期間は、信号φ2により制御されるスイッチがオンとなる期間、すなわちスイッチSW1、SW2、SW5、SW6がオフし、スイッチSW3、SW4、SW7、SW8がオンする期間である。

【0025】

図11に示した演算回路において、φ1期間に容量C1P及びC1Mにサンプリングされる電荷量は、φ2期間もそのまま保存されるので、

(VCM−VIP)C1+(VCM−VIM)C1=2(VA−VCM)C1

が成り立つ。VAについて整理すると、

VA=2VCM−(VIP+VIM)/2=2VCM−VICM

となる。つまり、オペアンプOPAの入力ノードVAの電位は、2VCMからVICMを減じた電位に収束することになる。例えば、コモンモード電位VCMが1.5(V)、入力信号のコモンモード電位VICMが2.5(V)のときには、オペアンプOPAの入力ノードVAの電位は0.5(V)に収束する。しかし、前述したようにオペアンプOPAのコモンモード入力電圧範囲には制約があり、例えば図10に示した回路ではオペアンプの入力ノードIM及びIPの電位が0.5(V)であると、差動対が遮断してしまい、所望の動作が行われない。図11に示した演算回路のオペアンプOPAの内部が図10に示した構成と同様であったとすれば、正常に動作させるためには、入力信号のコモンモード電位VICMは、0(V)<VICM<2.0(V)の電圧範囲でなければならない。

【0026】

この制約の存在は、差動入力A/D変換器を用いてシングルエンド信号をA/D変換する場合に、特に問題となる。例えば、差動入力A/D変換器でシングルエンド信号をA/D変換する場合には、2つの入力端子のうちの片側を所定の電位に固定すれば良い。しかし、図11に示した演算回路を用いたA/D変換器では、例えば負側入力端子VIMを1.5(V)とし、正側入力端子VIPを信号源に接続するようにした場合には、信号源から2.5(V)以上の信号が印加されると、入力信号のコモンモード電位VICMが2.0(V)より大きくなり回路が動作しない。このように、図11に示した演算回路をΔΣA/D変換器に用いた場合には、ユーザが信号源の設計に大きな制約を課されてしまうという課題がある。

【0027】

図11に示した演算回路における前述のような課題を解消する回路構成として、図12に示す演算回路が提案されている(特許文献7:Fig.4参照)。図12は、差動構造のスイッチドキャパシタ積分器の他の回路構成例を示す図である。図12において、図11に示した構成要素と同一の機能を有する構成要素には同一の符号を付し、重複する説明は省略する。図12に示す演算回路は、図11に示した演算回路は有していない容量素子C3P、C3Mが加えられている。C3PとC3Mは寄生容量でもよいので、破線で表記した。また、図11に示した演算回路では、容量C1PのボトムプレートはスイッチSW3を介してコモンモード電位VCMに接続でき、容量C1MのボトムプレートはスイッチSW4を介してコモンモード電位VCMに接続できるように構成されていた。それに対して、図12に示す演算回路では、容量C1P及びC1MのボトムプレートはスイッチSW3を介して互いに接続可能になっている。

【0028】

図12に示す演算回路では、φ1期間に容量素子C3P、C3Mのボトムプレートは0(V)に、容量素子C3P、C3Mのトッププレートはコモンモード電位VCMに接続される。また、容量C1P、C1Mのボトムプレートにはそれぞれ電圧VIP、VIMが印加され、容量C1P、C1Mのトッププレートがコモンモード電位VCMに接続される。これにより、容量素子C3P、C3Mはそれぞれコモンモード電位VCMに充電され、容量C1P、C1Mにコモンモード電位VCMと入力電圧VIP、VIMとの差に応じた電荷がサンプリングされる。

【0029】

次に、φ2期間に遷移しスイッチSW3、SW7、SW8がオンすると、オペアンプOPAの入力ノードVAは容量C3P及びC3Mに予め充電されていたコモンモード電位VCMに収束する。実際には、オペアンプOPAの入力ノードVAの電位は、オペアンプOPAや容量C2P、C2Mの寄生容量等によって、はじめはコモンモード電位VCMとは異なる電位である可能性があるが、数サイクル繰り返した後にコモンモード電位VCMに収束する。このように差動構造のスイッチドキャパシタ積分器は、図12に示すように構成することで、任意のコモンモード電位の差動入力信号を入力できる。

【0030】

図12に示した演算回路は単純な積分器であるが、ΔΣ変調器では、図8に示した演算ブロックU1のように入力電圧に2値の参照電圧を加えた値を積分する(1ビットDAC+加算+積分)演算回路が必要である。図13は、差動構造の(1ビットDAC+加算+積分)演算回路の一例を示す図である。図13において、C3P、C3Mはリファレンス容量であり、SW9、SW10、SW11、SW12、SW13、SW14はスイッチである。また、Vrefはリファレンス電圧である。その他の構成要素は、図12において同一の符号が付された構成要素と同様であるので、重複する説明は省略する。

【0031】

スイッチSW9、SW12は、信号φ1により導通/非導通(オン/オフ)が制御され、スイッチSW10、SW11、SW13、SW14は、信号φ2及び信号y(又は信号yの反転信号yx)により導通/非導通(オン/オフ)が制御される。スイッチSW10及びSW14は、信号φ2が“1”であり、かつ信号yが“+1”であるときに導通(オン)とされ、そうでないときは非導通(オフ)とされる。また、スイッチSW11及びSW13は、信号φ2が“1”であり、かつ信号yが“−1”であるときに導通(オン)とされ、そうでないときは非導通(オフ)とされる。ここで、信号yは、ΔΣ変調器のフィードバック信号に対応し、値は前述のように1ビット(2値)をとる。また、容量C3P及びC3Mの容量値は同一とする。

【先行技術文献】

【特許文献】

【0032】

【特許文献1】特開平8−125541号公報

【特許文献2】特開2002−261614号公報

【特許文献3】特開2001−358591号公報

【特許文献4】米国特許第4851841号明細書

【特許文献5】米国特許第4939516号明細書

【特許文献6】米国特許第4972436号明細書

【特許文献7】米国特許第6768436号明細書

【特許文献8】特開2007−300225号公報

【特許文献9】特開2006−41992号公報

【特許文献10】特表平10−508167号公報

【非特許文献】

【0033】

【非特許文献1】湯川彰著,「オーバーサンプリングA−D変換技術」,日経BP社,1990

【非特許文献2】Richard Schreier and Gabor C. Temes著,和保孝夫 安田彰 監訳,「ΔΣ型アナログ/デジタル変換器入門」,丸善,2007

【非特許文献3】B. E. Boser and B. A. Wooley, "The design of sigma-delta modulation analog-to-digital converters," IEEE Journal of Solid-State Circuits, Vol.23, pp.1298-1308, December 1988.

【非特許文献4】B. P. Brandt, D. E. Wingard, and B. A. Wooley, "Second-order sigma-delta modulation for digital-audio signal acquisition," IEEE Journal of Solid-State Circuits, Vol.26, pp.618-627, April 1991.

【非特許文献5】M. W. Hauser, P. J. Hurst, and R. W. Brodersen, "MOS ADC-Filter Combination That Does Not Require Precision Analog Components," IEEE International Solid-State Circuits Conference 1985 Digest of Technical Papers, pp.80-82, 1985.

【発明の概要】

【発明が解決しようとする課題】

【0034】

発明にいたる参考図である図13に示す演算回路は、差動入力信号から信号yを減じ、その結果を積分して出力する。実際には、リファレンス電圧Vrefとリファレンス容量C3P、C3Mとの積で表される電荷が信号yに相当する。

【0035】

図13に示す演算回路では、φ1期間に、容量C1P、C1Mのボトムプレートにそれぞれ電圧VIP、VIMが印加され、容量C1P、C1Mのトッププレートがコモンモード電位VCMに接続され、差動入力信号のサンプリングが行われる。このとき、容量素子C3P及びC3Mは、両電極(ボトムプレート及びトッププレート)がコモンモード電位VCMに接続されており、電荷がゼロとなる。

【0036】

次に、φ2期間に遷移すると、スイッチSW3、SW7、SW8がオンし、サンプリングにより容量C1P及びC1Mに蓄えられた電荷が、容量C2P及びC2Mに転送される。また、φ2期間において、信号yの値が“+1”の場合には、スイッチSW10及びSW14がオンして、容量C3Pのボトムプレートはリファレンス電圧Vrefに接続され、容量C3Mのボトムプレートは0(V)に接続される。逆に、信号yの値が“−1”の場合には、スイッチSW11及びSW13がオンして、容量C3Pのボトムプレートは0(V)に接続され、容量C3Mのボトムプレートはリファレンス電圧Vrefに接続される。その結果、サンプリングされた入力信号からリファレンス分の信号を減じた値、又はサンプリングされた入力信号にリファレンス分の信号を加えた値が、積分される。

【0037】

図13に示した演算回路を用いて、ΔΣA/D変換器が有するΔΣ変調器を構成した場合には、設定可能なリファレンス電圧Vrefの範囲が狭いという課題がある。ΔΣA/D変換器において、このリファレンス電圧Vrefは、A/D変換のフルスケールを規定するものであるため、ユーザが任意に設定できることが望ましい。図13に示した演算回路では、φ1期間には、容量C3P及びC3Mの電荷はゼロに放出される。次のφ2期間には、容量C3P及びC3Mがリファレンス電圧Vrefと0(V)との電位差を容量分圧するように各スイッチが制御され、オペアンプOPAの入力ノードVAの電位は、容量C3P及びC3Mで分圧された電圧となる。つまり、入力ノードVAの電位は、VA=Vref/2となる。

【0038】

そのため、入力ノードVAの電位(Vref/2)がオペアンプOPAのコモンモード入力電圧範囲を下回るような低いリファレンス電圧Vrefを用いると、回路は動作しない。例えば、電源電圧VDDが3.0(V)、接地電圧VSSが0(V)、コモンモード電位VCMが1.5(V)、リファレンス電圧Vrefが1.0(V)である場合には、入力ノードVAの電位は、VA=Vref/2=0.5(V)に収束する。しかし、図13に示した演算回路のオペアンプOPAの内部が図10に示した構成と同様であると、差動対が遮断して所望の動作が行われない。回路を正常に動作させるためには、リファレンス電圧Vrefは、Vref>2.0(V)でなければならない。このような場合には、図13に示した演算回路に対して、例えばバンドギャップリファレンス回路で発生した1.2(V)の電圧をリファレンス電圧Vrefとして使用することができない。リファレンス電圧Vrefの設定可能な電圧範囲は、半導体集積回路のユーザが行う設計の自由度を高めるために、可能な限り広いことが望ましい。

【0039】

本発明の目的は、任意のコモンモード電位の差動アナログ信号を入力でき、かつ任意のリファレンス電圧を設定可能なΔΣA/D変換器を提供することにある。

【課題を解決するための手段】

【0040】

A/D変換器の一態様は、入力される差動アナログ信号をデルタシグマ変調する変調器と、その出力を基にデジタルデータを生成するデシメーションフィルタとを備える。変調器は、入力信号をサンプリングする第1の容量及び第2の容量と、第1の容量の第1の電極に接続され、第1の基準電圧又は第2の基準電圧をサンプリングする第3の容量及び第4の容量と、第2の容量の第1の電極に接続され、第1の基準電圧又は第2の基準電圧をサンプリングする第5の容量及び第6の容量と、各容量にサンプリングされた電荷を加算又は減算して加算又は減算結果を得て、加算又は減算結果を積分し出力する演算器とを有する演算回路を1つ以上含む。

【発明の効果】

【0041】

演算回路にて入力信号に変調器出力に応じた信号を加算又は減算する場合に、第3の容量及び第4の容量の接続と第5の容量及び第6の容量の接続とを相補的に切り替えることで、基準電圧がどのような電圧であっても演算器の入力ノードに加算される電荷量は同一になる。したがって、演算器の入力ノードの電位は回路のコモンモード電位に収束するので、任意のコモンモード電位の差動アナログ信号を入力でき、かつ任意のリファレンス電圧を設定することができる。

【図面の簡単な説明】

【0042】

【図1】本実施形態によるΔΣA/D変換器の(1ビットDAC+加算+積分)演算回路の構成例を示す図である。

【図2A】図1に示した演算回路の動作を説明するための図である。

【図2B】図1に示した演算回路の動作を説明するための図である。

【図2C】図1に示した演算回路の動作を説明するための図である。

【図3】本実施形態によるΔΣA/D変換器の(1ビットDAC+加算+積分)演算回路の他の構成例を示す図である。

【図4】本実施形態における1ビット2次ΔΣ変調器の構成例を示す図である。

【図5】図4に示したΔΣ変調器の動作の流れを示す図である。

【図6】ΔΣA/D変換器の構成例を示す図である。

【図7】ΔΣ変調器を実現するための信号経路の例を示す図である。

【図8】図7に示したΔΣ変調器の信号経路をz演算子を用いて表記した図である。

【図9】シングルエンド構造の(加算+積分)演算回路の構成例を示す図である。

【図10】オペアンプの入力部分の回路構成を示す図である。

【図11】差動構造のスイッチドキャパシタ積分器の構成例を示す図である。

【図12】差動構造のスイッチドキャパシタ積分器の構成例を示す図である。

【図13】差動構造の(1ビットDAC+加算+積分)演算回路の参考図である。

【発明を実施するための形態】

【0043】

以下、本発明の実施形態を図面に基づいて説明する。

図1は、本発明の一実施形態によるΔΣA/D変換器の(1ビットDAC+加算+積分)演算回路の回路構成例を示す図である。なお、本実施形態によるΔΣA/D変換器の構成は、図6に示したΔΣA/D変換器の構成と同様である。すなわち、本実施形態によるΔΣA/D変換器は、入力される差動アナログ信号をΔΣ変調するΔΣ変調器、及びΔΣ変調信号を基にA/D変換結果(デジタルデータ)を生成するデシメーションフィルタを有する。

【0044】

図1に示す差動構造の(1ビットDAC+加算+積分)演算回路は、入力電圧に2値の参照電圧(リファレンス電圧)を加えた値を積分する演算回路であり、例えばΔΣA/D変換器が有するΔΣ変調器の第一段目の演算回路として用いられる。

【0045】

図1において、C1P及びC1Mはサンプリング容量であり、C2P及びC2Mは積分容量である。また、C3PA、C3PB、C3MA、及びC3MBは、リファレンス容量である。すなわち、本実施形態における演算回路では、正側ノードに2つのリファレンス容量C3PA及びC3PBが設けられ、負側ノードに2つのリファレンス容量C3MA及びC3MBが設けられる。容量C1P及びC1Mの容量値は同一のC1とし、容量C2P及びC2Mの容量値は同一のC2とし、容量C3PA、C3PB、C3MA、及びC3MBの容量値は同一のC3とする。

【0046】

OPAは全差動オペアンプである。また、VIPは差動アナログ信号の正側入力ノードであり、VIMは差動アナログ信号の負側入力ノードである。VAはオペアンプOPAの入力ノードであり、VOPはオペアンプOPAの正側出力ノード、VOMはオペアンプOPAの負側出力ノードである。なお、VOP及びVOMは図1に示す演算回路における差動信号の出力ノードでもある。以下では、これらの各ノードに対して入力又は出力される信号や各ノードの電圧値も、適宜ノードに付した符号と同様の表記を用いて示す。VCMは演算回路におけるコモンモード電位であり、Vrefはリファレンス電圧(リファレンス信号)である。例えば、コモンモード電位VCMは、電源電圧VDDと接地電圧VSS(0(V))との中間電位であるとする。

【0047】

また、SW1〜SW15は、スイッチである。スイッチSW1、SW2、SW4、及びSW5は、信号φ1により導通/非導通(オン/オフ)が制御され、スイッチSW3、SW6、及びSW7は、信号φ2により導通/非導通(オン/オフ)が制御される。スイッチSW8、SW10、SW12、及びSW14は、信号φ1、信号φ2、及び信号y(又は信号yの反転信号yx)により導通/非導通(オン/オフ)が制御される。スイッチSW9、SW11、SW13、及びSW15は、信号φ2及び信号y(又は信号yの反転信号yx)により導通/非導通(オン/オフ)が制御される。ここで、信号yは、ΔΣ変調器の出力(詳細にはΔΣ変調器が有する量子化器の出力)であり、値としては“+1”又は“−1”の2値(1ビット)をとる。

【0048】

スイッチSW1、SW2、SW4、及びSW5は、信号φ1が“1”(アクティブ)であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW3、SW6、SW7は、信号φ2が“1”(アクティブ)であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。

【0049】

スイッチSW8及びSW12は、信号φ1が“1”であるとき、又は信号φ2が“1”かつ信号y=−1であるときに、導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW9及びSW13は、信号φ2が“1”かつ信号y=+1であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。

【0050】

スイッチSW10及びSW14は、信号φ1が“1”であるとき、又は信号φ2が“1”かつ信号y=+1であるときに、導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW11及びSW15は、信号φ2が“1”かつ信号y=−1であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。

【0051】

容量C1Pは、一方の電極(ボトムプレート)がスイッチSW1を介して正側入力ノードVIPに接続され、他方の電極(トッププレート)がスイッチSW6を介してオペアンプOPAの負側入力ノードVAに接続される。容量C1Mは、一方の電極(ボトムプレート)がスイッチSW2を介して負側入力ノードVIMに接続され、他方の電極(トッププレート)がスイッチSW7を介してオペアンプOPAの正側入力ノードVAに接続される。また、容量C1P及びC1Mのボトムプレートは、スイッチSW3を介して互いに接続される。また、容量C1PのトッププレートはスイッチSW4を介してコモンモード電位VCMに接続され、容量C1MのトッププレートはスイッチSW5を介してコモンモード電位VCMに接続される。

【0052】

容量C2Pは、一方の電極がオペアンプOPAの正側出力ノードVOPに接続され、他方の電極がオペアンプOPAの負側入力ノードVAに接続される。容量C2Mは、一方の電極がオペアンプOPAの負側出力ノードVOMに接続され、他方の電極がオペアンプOPAの正側入力ノードVAに接続される。

【0053】

容量C3PAの一方の電極(ボトムプレート)は、スイッチSW8を介して接地電圧VSS(0(V))に接続されるとともに、スイッチSW9を介してリファレンス電圧Vrefに接続される。容量C3PBの一方の電極(ボトムプレート)は、スイッチSW10を介してリファレンス電圧Vrefに接続されるとともに、スイッチSW11を介して接地電圧VSS(0(V))に接続される。また、容量C3PA及びC3PBの他方の電極(トッププレート)は、スイッチSW4を介してコモンモード電位VCMに接続されるとともに、スイッチSW6を介してオペアンプOPAの負側入力ノードVAに接続される。

【0054】

容量C3MAの一方の電極(ボトムプレート)は、スイッチSW12を介してリファレンス電圧Vrefに接続されるとともに、スイッチSW13を介して接地電圧VSS(0(V))に接続される。容量C3MBの一方の電極(ボトムプレート)は、スイッチSW14を介して接地電圧VSS(0(V))に接続されるとともに、スイッチSW15を介してリファレンス電圧Vrefに接続される。また、容量C3MA及びC3MBの他方の電極(トッププレート)は、スイッチSW5を介してコモンモード電位VCMに接続されるとともに、スイッチSW7を介してオペアンプOPAの正側入力ノードVAに接続される。

【0055】

図1に示す回路は、クロック信号等に基づいて、信号φ1が“1”であるφ1期間と信号φ2が“1”であるφ2期間とを交互に繰り返し、入力される差動アナログ信号(VIP−VIM)から、基準信号を減じた信号又は加えた信号を積分し、その結果を差動信号(VOP−VOM)により出力する。基準信号を減じるか加えるかは、信号yによって決定される。

【0056】

φ1期間においては、図2Aに示すように各スイッチSW1〜SW15が制御されて信号のサンプリングが行われる。すなわち、スイッチSW1、SW2、SW4、SW5、SW8、SW10、SW12、及びSW14が導通(オン)とされ、スイッチSW3、SW6、SW7、SW9、SW11、SW13、及びSW15が非導通(オフ)とされる。

【0057】

これにより、容量C1Pは、ボトムプレートに電圧VIPが印加され、トッププレートがコモンモード電位VCMに接続される。容量C1Mは、ボトムプレートに電圧VIMが印加され、トッププレートがコモンモード電位VCMに接続される。したがって、容量C1P、C1Mにコモンモード電位VCMと入力電圧VIP、VIMとの差に応じた電荷がサンプリングされる。また、容量C3PA及びC3MBのボトムプレートは接地電圧VSS(0(V))に接続され、容量C3PB及びC3MAのボトムプレートはリファレンス電圧Vrefに接続される。容量C3PA、C3PB、C3MA、及びC3MBのトッププレートはコモンモード電位VCMに接続される。したがって、容量C3PA及びC3MBはそれぞれコモンモード電位VCMに充電され、容量C3PB及びC3MAのボトムプレートは(コモンモード電位VCM−リファレンス電圧Vref)に充電される。

【0058】

φ2期間においては、入力信号に対して基準信号を加える場合、すなわち信号y=−1の場合には、図2Bに示すように各スイッチSW1〜SW15が制御されて信号の加算及び積分が行われる。すなわち、スイッチSW1、SW2、SW4、SW5、SW9、SW10、SW13、及びSW14が非導通(オフ)とされ、スイッチSW3、SW6、SW7、SW8、SW11、SW12、及びSW15が導通(オン)とされる。

【0059】

これにより、容量C3PBのボトムプレートが接地電圧VSS(0(V))に接続され、容量C3MBのボトムプレートがリファレンス電圧Vrefに接続されるよう切り替えられる。容量C3PA及びC3MAのボトムプレートの接続は切り替わらない。この動作では、容量C3PBのボトムプレートの電圧がリファレンス電圧Vrefから接地電圧VSS(0(V))に、容量C3MBのボトムプレートの電圧が接地電圧VSS(0(V))からリファレンス電圧Vrefに変化するだけである。そのため、φ2期間における入力ノードVAの電位は、コモンモード電位VCMとなる。詳細には、容量C3PB及びC3MBは、φ1期間においてサンプリングを行い、φ2期間において容量分圧回路を形成し入力ノードVAの電位を決定する。式で表すと、

(VCM−0)C3+(VCM−Vref)C3=(VA−Vref)C3+(VA−0)C3

が成り立つ。よって、

VA=VCM

となる。つまり、入力ノードVAの電位は、リファレンス電圧Vrefや入力される差動アナログ信号のコモンモード電位VICMにかかわらず、回路におけるコモンモード電位VCMとなる。

【0060】

また、φ2期間において、入力信号に対して基準信号を減じる場合、すなわち信号y=+1の場合には、図2Cに示すように各スイッチSW1〜SW15が制御されて信号の加算及び積分が行われる。すなわち、スイッチSW1、SW2、SW4、SW5、SW8、SW11、SW12、及びSW15が非導通(オフ)とされ、スイッチSW3、SW6、SW7、SW9、SW10、SW13、及びSW14が導通(オン)とされる。

【0061】

これにより、容量C3PAのボトムプレートがリファレンス電圧Vrefに接続され、容量C3MAのボトムプレートが接地電圧VSS(0(V))に接続されるよう切り替えられる。容量C3PB及びC3MBのボトムプレートの接続は切り替わらない。この動作では、容量C3PAのボトムプレートの電圧が接地電圧VSS(0(V))からリファレンス電圧Vrefに、容量C3MAのボトムプレートの電圧がリファレンス電圧Vrefから接地電圧VSS(0(V))に変化するだけである。そのため、入力信号に対して基準信号を減じる場合にも、φ2期間における入力ノードVAの電位は、リファレンス電圧Vrefや入力される差動アナログ信号のコモンモード電位VICMにかかわらず、回路におけるコモンモード電位VCMとなる。

【0062】

以上のように、図1に示した演算回路を用いてΔΣA/D変換器を構成した場合には、任意のコモンモード電位の差動アナログ信号を入力でき、かつ任意のリファレンス電圧を設定することができる。

【0063】

また、1ビットΔΣA/D変換器には、内部DACが2値であるために内部DACの非線形性が存在せず、A/D変換の直線性を高くできるという利点があるが、図1に示した演算回路を用いてΔΣA/D変換器を構成してもこの利点は失われることはない。図2Bに示した状態ではリファレンス容量はC3PB及びC3MBのみが回路動作に寄与し、図2Cに示した状態では、リファレンス容量はC3PA及びC3MAのみが回路動作に寄与する。すなわち、入力信号に対して基準信号を加える場合に使用される容量と、入力信号に対して基準信号を減じる場合に使用される容量とが常に等しいため、非線形性が生じない。

【0064】

図3は、本発明の一実施形態によるΔΣA/D変換器の(1ビットDAC+加算+積分)演算回路の他の回路構成例を示す図である。図3には、相関二重サンプリング(CDS)を用いたΔΣA/D変換器に対して適用した例を示している。

【0065】

図3において、C1P及びC1Mはサンプリング容量であり、C2P及びC2Mは積分容量である。また、C3PA、C3PB、C3MA、及びC3MBは、リファレンス容量である。すなわち、本実施形態における演算回路では、正側ノードに2つのリファレンス容量C3PA及びC3PBが設けられ、負側ノードに2つのリファレンス容量C3MA及びC3MBが設けられる。容量C1P及びC1Mの容量値は同一のC1とし、容量C2P及びC2Mの容量値は同一のC2とし、容量C3PA、C3PB、C3MA、及びC3MBの容量値は同一のC3とする。

【0066】

OPAは全差動オペアンプである。また、VIPは差動アナログ信号の正側入力ノードであり、VIMは差動アナログ信号の負側入力ノードである。VOPはオペアンプOPAの正側出力ノード、VOMはオペアンプOPAの負側出力ノードである。なお、VOP及びVOMは図3に示す演算回路における差動信号の出力ノードでもある。Vrefはリファレンス電圧(リファレンス信号)である。

【0067】

また、SW1〜SW3、S4〜S7、及びSW8〜SW15は、スイッチである。スイッチSW1、SW2、S6、及びS7は、信号φ1が“1”であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW3、S4、S5は、信号φ2が“1”であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。

【0068】

スイッチSW8及びSW12は、信号φ1が“1”であるとき、又は信号φ2が“1”かつ信号y=−1であるときに、導通(オン)とされ、そうでないときには非導通(オフ)とされる。なお、信号yは、ΔΣ変調器の出力(詳細にはΔΣ変調器が有する量子化器の出力)であり、値としては“+1”又は“−1”の2値(1ビット)をとる。スイッチSW9及びSW13は、信号φ2が“1”かつ信号y=+1であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。

【0069】

スイッチSW10及びSW14は、信号φ1が“1”であるとき、又は信号φ2が“1”かつ信号y=+1であるときに、導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW11及びSW15は、信号φ2が“1”かつ信号y=−1であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。

【0070】

容量C1Pは、一方の電極(ボトムプレート)がスイッチSW1を介して正側入力ノードVIPに接続され、他方の電極(トッププレート)がオペアンプOPAの負側入力ノードに接続される。容量C1Mは、一方の電極(ボトムプレート)がスイッチSW2を介して負側入力ノードVIMに接続され、他方の電極(トッププレート)がオペアンプOPAの正側入力ノードに接続される。また、容量C1P及びC1Mのボトムプレートは、スイッチSW3を介して互いに接続される。

【0071】

容量C2Pは、一方の電極がオペアンプOPAの正側出力ノードVOPに接続され、他方の電極がスイッチS4を介してオペアンプOPAの負側入力ノードに接続される。容量C2Mは、一方の電極がオペアンプOPAの負側出力ノードVOMに接続され、他方の電極がスイッチS5を介してオペアンプOPAの正側入力ノードに接続される。すなわち、オペアンプOPAの負側入力ノードと正側出力ノードVOPとの間に、スイッチS4及び容量C2Pが直列に接続され、オペアンプOPAの正側入力ノードと負側出力ノードVOMとの間に、スイッチS5及び容量C2Mが直列に接続される。

【0072】

容量C3PAの一方の電極(ボトムプレート)は、スイッチSW8を介して接地電圧VSS(0(V))に接続されるとともに、スイッチSW9を介してリファレンス電圧Vrefに接続される。容量C3PBの一方の電極(ボトムプレート)は、スイッチSW10を介してリファレンス電圧Vrefに接続されるとともに、スイッチSW11を介して接地電圧VSS(0(V))に接続される。また、容量C3PA及びC3PBの他方の電極(トッププレート)は、オペアンプOPAの負側入力ノードに接続される。

【0073】

容量C3MAの一方の電極(ボトムプレート)は、スイッチSW12を介してリファレンス電圧Vrefに接続されるとともに、スイッチSW13を介して接地電圧VSS(0(V))に接続される。容量C3MBの一方の電極(ボトムプレート)は、スイッチSW14を介して接地電圧VSS(0(V))に接続されるとともに、スイッチSW15を介してリファレンス電圧Vrefに接続される。また、容量C3MA及びC3MBの他方の電極(トッププレート)は、オペアンプOPAの正側入力ノードに接続される。

【0074】

オペアンプOPAの正側出力ノードVOPとオペアンプOPAの負側入力ノードとがスイッチS6を介して接続され、オペアンプOPAの負側出力ノードVOMとオペアンプOPAの正側入力ノードとがスイッチS7を介して接続される。

【0075】

図3に示した演算回路は、オペアンプで生じるMOSトランジスタの1/f雑音がA/D変換特性を劣化させるという問題を回避するためにCDSの機構を備えている。図3に示した演算回路では、φ1期間において、オペアンプOPAの負側入力ノードと正側出力ノードとがスイッチS6を介して接続されるとともに、オペアンプOPAの正側入力ノードと負側出力ノードとがスイッチS7を介して接続される。その際、オペアンプOPAの2つの入力ノード間には、オペアンプOPAの入力オフセット電圧及び雑音による電圧(雑音電圧)が生じる。そのため、容量C1P及びC1Mには、信号による電荷とともに、オペアンプOPAの入力オフセット電圧及び雑音電圧による電荷がサンプリングされる。

【0076】

次に、φ2期間へ遷移すると、容量C1P及びC1Mにサンプリングされた信号による電荷とオペアンプOPAの入力オフセット電圧及び雑音電圧による電荷が容量C2P及びC2Mに転送される。ここで、φ2期間であっても、オペアンプOPAの入力オフセット電圧及び雑音電圧は存在するが、φ1期間においてサンプリングされ容量C1P及びC1Mから転送された電荷によってキャンセルされる。その結果、入力オフセット電圧は除去され、また、少なくともサンプリング周波数より低い周波数の雑音も除去されるので、高精度のA/D変換が可能になる。

【0077】

図3に示した演算回路を用いてΔΣA/D変換器を構成した場合に、任意のコモンモード電位の差動アナログ信号を入力でき、かつ任意のリファレンス電圧を設定することができることは、図1に示した演算回路と同様である。

【0078】

図4は、本実施形態における1ビット2次ΔΣ変調器の回路構成例を示す図である。

図4において、C1P及びC1Mは第1積分器のサンプリング容量、C2P及びC2Mは第1積分器の積分容量、C3PA、C3PB、C3MA、及びC3MBは、第1積分器のリファレンス容量である。また、C4P及びC4Mは第2積分器のサンプリング容量、C6P及びC6Mは第2積分器の積分容量、C5PA、C5PB、C5MA、及びC5MBは、第2積分器のリファレンス容量である。容量C1P及びC1Mの容量値は同一とし、容量C2P及びC2Mの容量値は同一とし、容量C3PA、C3PB、C3MA、及びC3MBの容量値は同一とする。また、容量C4P及びC4Mの容量値は同一とし、容量C5PA、C5PB、C5MA、及びC5MBの容量値は同一とし、容量C6P及びC6Mの容量値は同一とする。

【0079】

OPA1及びOPA2は全差動オペアンプであり、CMPは比較器であり、FFはDフリップフロップである。また、VIPは差動アナログ信号の正側入力ノードであり、VIMは差動アナログ信号の負側入力ノードである。VCMはコモンモード電位であり、Vrefはリファレンス電圧(リファレンス信号)であり、YはΔΣ変調器の出力であり、YXは出力Yの反転信号である。

【0080】

また、SW1〜SW15は、スイッチである。スイッチSW4、SW5、SW14、及びSW15は、クロック信号CK1が“1”であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW1、SW2、SW10、及びSW11は、クロック信号CK1Dが“1”であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW6、SW7、SW12、及びSW13は、クロック信号CK2が“1”であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。スイッチSW3、SW8、及びSW9は、クロック信号CK2Dが“1”であるときに導通(オン)とされ、そうでないときには非導通(オフ)とされる。

【0081】

ここで、クロック信号CK1Dは、クロック信号CK1をわずかに遅延させたクロック信号であり、クロック信号CK2Dは、クロック信号CK2をわずかに遅延させたクロック信号である。また、クロック信号CK1とクロック信号CK2は逆極性であり、かつ同時には“1”とならないノンオーバーラップの関係を有する。より詳細には、クロック信号CK1及びCK1Dの少なくとも一方が“1”のときにクロック信号CK2及びCK2Dはともに“0”であり、クロック信号CK2及びCK2Dの少なくとも一方が“1”のときにクロック信号CK1及びCK1Dはともに“0”である。

【0082】

容量C1Pは、一方の電極(ボトムプレート)がスイッチSW1を介して正側入力ノードVIPに接続され、他方の電極(トッププレート)がオペアンプOPA1の負側入力ノードに接続される。容量C1Mは、一方の電極(ボトムプレート)がスイッチSW2を介して負側入力ノードVIMに接続され、他方の電極(トッププレート)がオペアンプOPA1の正側入力ノードに接続される。また、容量C1P及びC1Mのボトムプレートは、スイッチSW3を介して互いに接続される。

【0083】

容量C2Pは、一方の電極がオペアンプOPA1の正側出力ノードに接続され、他方の電極がスイッチSW6を介してオペアンプOPA1の負側入力ノードに接続される。容量C2Mは、一方の電極がオペアンプOPA1の負側出力ノードに接続され、他方の電極がスイッチSW7を介してオペアンプOPA1の正側入力ノードに接続される。また、オペアンプOPA1の正側出力ノードと負側入力ノードはスイッチSW4を介して接続され、オペアンプOPA1の負側出力ノードと正側入力ノードはスイッチSW5を介して接続される。

【0084】

容量C3PAの一方の電極(ボトムプレート)は、クロック信号CK2Dが“1”かつ出力Yが“1”のときにリファレンス電圧Vrefに接続され、その他のときは接地電圧VSS(0(V))に接続される。また、容量C3MAの一方の電極(ボトムプレート)は、クロック信号CK2Dが“1”かつ出力Yが“1”のときに接地電圧VSS(0(V))に接続され、その他のときはリファレンス電圧Vrefに接続される。同様に、容量C3PBの一方の電極(ボトムプレート)は、クロック信号CK2Dが“1”かつ反転信号YXが“1”のときに接地電圧VSS(0(V))に接続され、その他のときはリファレンス電圧Vrefに接続される。また、容量C3MBの一方の電極(ボトムプレート)は、クロック信号CK2Dが“1”かつ反転信号YXが“1”のときにリファレンス電圧Vrefに接続され、その他のときは接地電圧VSS(0(V))に接続される。また、容量C3PA及びC3PBの他方の電極(トッププレート)はオペアンプOPA1の負側入力ノードに接続され、容量C3MA及びC3MBの他方の電極(トッププレート)はオペアンプOPA1の正側入力ノードに接続される。

【0085】

容量C4Pは、一方の電極(ボトムプレート)がスイッチSW8を介してオペアンプOPA1の正側出力ノードに接続され、他方の電極(トッププレート)がスイッチSW14を介してオペアンプOPA2の負側入力ノードに接続される。容量C4Mは、一方の電極(ボトムプレート)がスイッチSW9を介してオペアンプOPA1の負側出力ノードに接続され、他方の電極(トッププレート)がスイッチSW15を介してオペアンプOPA2の正側入力ノードに接続される。また、容量C4P及びC4Mのボトムプレートは、スイッチSW10、SW11を介してコモンモード電位VCMに接続され、容量C4P及びC4Mのトッププレートは、スイッチSW12、SW13を介してコモンモード電位VCMに接続される。

【0086】

容量C6Pは、一方の電極がオペアンプOPA2の正側出力ノードに接続され、他方の電極がオペアンプOPA2の負側入力ノードに接続される。容量C6Mは、一方の電極がオペアンプOPA2の負側出力ノードに接続され、他方の電極がオペアンプOPA2の正側入力ノードに接続される。

【0087】

容量C5PAの一方の電極(ボトムプレート)は、クロック信号CK1Dが“1”かつ出力Yが“1”のときにリファレンス電圧Vrefに接続され、その他のときは接地電圧VSS(0(V))に接続される。また、容量C5MAの一方の電極(ボトムプレート)は、クロック信号CK1Dが“1”かつ出力Yが“1”のときに接地電圧VSS(0(V))に接続され、その他のときはリファレンス電圧Vrefに接続される。同様に、容量C5PBの一方の電極(ボトムプレート)は、クロック信号CK1Dが“1”かつ反転信号YXが“1”のときに接地電圧VSS(0(V))に接続され、その他のときはリファレンス電圧Vrefに接続される。また、容量C5MBの一方の電極(ボトムプレート)は、クロック信号CK1Dが“1”かつ反転信号YXが“1”のときにリファレンス電圧Vrefに接続され、その他のときは接地電圧VSS(0(V))に接続される。また、容量C5PA及びC5PBの他方の電極(トッププレート)はスイッチSW14を介してオペアンプOPA2の負側入力ノードに接続され、容量C5MA及びC5MBの他方の電極(トッププレート)はスイッチSW15を介してオペアンプOPA2の正側入力ノードに接続される。

【0088】

比較器CMPは、負側入力ノードがオペアンプOPA2の正側出力ノードに接続され、正側入力ノードがオペアンプOPA2の負側出力ノードに接続される。DフリップフロップFFは、クロック信号CK1で動作し、比較器CMPの出力を取り込んで出力Yとして出力する。

【0089】

図4に示すΔΣ変調器では、第2積分器の雑音はA/D変換特性にはほとんど影響を及ぼさないため、第1積分器にのみCDS(相関二重サンプリング)の機能を含み、第2積分器はCDSの機能を含まない。図4に示すΔΣ変調器における第1積分器は図3に示した演算回路に相当し、第2積分器は図1に示した演算回路に相当する。

【0090】

第1積分器は、クロック信号CK1(CK1D)が“1”の期間に信号のサンプリングを行い、クロック信号CK2(CK2D)が“1”の期間に信号の加算及び積分を行う。また、第2積分器は、クロック信号CK2(CK2D)が“1”の期間に信号のサンプリングを行い、クロック信号CK1(CK1D)が“1”の期間に信号の加算及び積分を行う。

【0091】

第1積分器におけるリファレンス容量C3PA、C3PB、C3MA、及びC3MBのボトムプレートの電圧は、出力Yとその反転信号YXとクロック信号CK2Dによって制御される。第1積分器で信号のサンプリングを行う期間においてクロック信号CK2Dは“0”であるので、容量C3PA及びC3MBのボトムプレートの電圧は接地電圧(0(V))とされ、容量C3PB及びC3MAのボトムプレートの電圧はリファレンス電圧Vrefとされる。

【0092】

次に、クロック信号CK2Dが“1”の期間に遷移すると、出力Yが“1”の場合には、容量C3PAのボトムプレートの電圧は接地電圧(0(V))からリファレンス電圧Vrefに変化し、容量C3MAのボトムプレートの電圧はリファレンス電圧Vrefから接地電圧(0(V))に変化する。なお、容量C3PBのボトムプレートの電圧はリファレンス電圧Vrefのままであり、容量C3MBのボトムプレートの電圧は接地電圧(0(V))のままである。したがって、オペアンプOPA1における入力ノードの電位は、前述したようにコモンモード電位VCMに収束することとなる。

【0093】

一方、クロック信号CK2Dが“1”の期間に遷移したとき、反転信号YXが“1”の場合には、容量C3PBのボトムプレートの電圧はリファレンス電圧Vrefから接地電圧(0(V))に変化し、容量C3MBのボトムプレートの電圧は接地電圧(0(V))からリファレンス電圧Vrefに変化する。なお、容量C3PAのボトムプレートの電圧は接地電圧(0(V))のままであり、容量C3MAのボトムプレートの電圧はリファレンス電圧Vrefのままである。したがって、オペアンプOPA1における入力ノードの電位は、前述したようにコモンモード電位VCMに収束することとなる。

【0094】

同様に、第2積分器におけるリファレンス容量C5PA、C5PB、C5MA、及びC5MBのボトムプレートの電圧は、出力Yとその反転信号YXとクロック信号CK1Dによって制御される。第2積分器で信号のサンプリングを行う期間においてクロック信号CK1Dは“0”であるので、容量C5PA及びC5MBのボトムプレートの電圧は接地電圧(0(V))とされ、容量C5PB及びC5MAのボトムプレートの電圧はリファレンス電圧Vrefとされる。

【0095】

次に、クロック信号CK1Dが“1”の期間に遷移すると、出力Yが“1”の場合には、容量C5PAのボトムプレートの電圧は接地電圧(0(V))からリファレンス電圧Vrefに変化し、容量C5MAのボトムプレートの電圧はリファレンス電圧Vrefから接地電圧(0(V))に変化する。なお、容量C5PBのボトムプレートの電圧はリファレンス電圧Vrefのままであり、容量C5MBのボトムプレートの電圧は接地電圧(0(V))のままである。したがって、オペアンプOPA2における入力ノードの電位は、前述したようにコモンモード電位VCMに収束することとなる。

【0096】

一方、クロック信号CK1Dが“1”の期間に遷移したとき、反転信号YXが“1”の場合には、容量C5PBのボトムプレートの電圧はリファレンス電圧Vrefから接地電圧(0(V))に変化し、容量C5MBのボトムプレートの電圧は接地電圧(0(V))からリファレンス電圧Vrefに変化する。なお、容量C5PAのボトムプレートの電圧は接地電圧(0(V))のままであり、容量C5MAのボトムプレートの電圧はリファレンス電圧Vrefのままである。したがって、オペアンプOPA2における入力ノードの電位は、前述したようにコモンモード電位VCMに収束することとなる。

【0097】

以上のように、図4に示したΔΣ変調器ではオペアンプOPA1及びOPA2の入力ノードの電位は、リファレンス電圧Vrefや入力される差動アナログ信号のコモンモード電位VICMにかかわらず、回路におけるコモンモード電位VCMとなる。図4に示したΔΣ変調器によれば、任意のコモンモード電位の差動アナログ信号を入力でき、かつ任意のリファレンス電圧を設定することができるΔΣA/D変換器を提供することが可能となる。

【0098】

図5は、図4に示したΔΣ変調器の動作の流れを示す図である。

図5において、CK1、CK1D、CK2、CK2Dはクロック信号を示し、SICA及びSIOAは第1積分器の動作及び出力を示し、SICB及びSIOBは第2積分器の動作及び出力を示している。また、CMPOは比較器の出力を示し、DFFはDフリップフロップの出力を示し、FBBは第2積分器へのフィードバック信号を示し、FBAは第1積分器へのフィードバック信号を示している。前述したように図4に示したΔΣ変調器では、クロック信号CK1(CK1D)が“1”の期間に、第1積分器は信号のサンプリングを行っており、第2積分器は信号の加算及び積分を行っている。また、クロック信号CK2(CK2D)が“1”の期間に、第1積分器は信号の加算及び積分を行っており、第2積分器は信号のサンプリングを行っている。

【0099】

まず、時刻T1にて、第1積分器が、1回目の信号のサンプリング(S1)を行う。続く時刻T2にて、第1積分器が、1回目の信号の加算及び積分(I1)を行う。また、それと同時に、第2積分器が、1回目の信号(第1積分器の出力)のサンプリング(S1)を行う。次の時刻T3にて、第1積分器が、2回目の信号のサンプリング(S2)を行うとともに、第2の積分器が、1回目の信号の加算及び積分(I1)を行う。

【0100】

次の時刻T4にて、第1積分器が、2回目の信号の加算及び積分(I2)を行う。また、それと同時に、第2積分器が、2回目の信号のサンプリング(S2)を行う。このとき、時刻T4となる直前に、比較器CMPが第2積分器の出力信号SIOBの正負を判定する。また、その際、DフリップフロップFFはスルー状態となっており、比較器CMPの出力CMPOによってDフリップフロップFFの出力DFFOが更新される。更新されたDフリップフロップFFの出力DFFOにより、信号のサンプリング(S2)に移行した第2積分器へフィードバック値FBBが供給される。このようにして1サイクル後に第2積分器に出力値がフィードバックされる。

【0101】

次の時刻T5にて、第1積分器が、3回目の信号のサンプリング(S3)を行うとともに、第2積分器が、2回目の信号の加算及び積分(I2)を行う。第1積分器における信号のサンプリングでは、先に更新されたDフリップフロップFFの出力DFFOにより第1積分器へフィードバック値FBAが供給される。このようにして2サイクル後に第1積分器に出力値がフィードバックされる。以降、時刻T6、T7、・・・と動作を順次繰り返し行うことで入力される差動アナログ信号のA/D変換を行う。

【0102】

なお、前述した説明では1ビット2次ΔΣ変調器を一例に説明したが、本発明はこれに限定されるものではなく、ビット幅や伝達関数が異なるΔΣ変調器を有するΔΣA/D変換器についても本発明は適用可能である。

【0103】

なお、前記実施形態は、何れも本発明を実施するにあたっての具体化のほんの一例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、またはその主要な特徴から逸脱することなく、様々な形で実施することができる。

【符号の説明】

【0104】

C1P、C1M サンプリング容量

C2P、C2M 積分容量

C3PA、C3PB、C3MA、C3MB リファレンス容量

C4P、C4M サンプリング容量

C5PA、C5PB、C5MA、C5MB リファレンス容量

C6P、C6M 積分容量

OPA 全差動オペアンプ

SW1〜SW15 スイッチ

VCM 回路のコモンモード電位

Vref リファレンス電圧

MOD ΔΣ変調器

FLT デシメーションフィルタ

【特許請求の範囲】

【請求項1】

入力される差動アナログ信号をデジタルデータに変換するデルタシグマ型のA/D変換器であって、

前記差動アナログ信号をデルタシグマ変調する変調器と、

前記変調器の出力を基に前記デジタルデータを生成するデシメーションフィルタとを備え、

前記変調器は、

入力信号をサンプリングする第1の容量及び第2の容量と、

それぞれの第1の電極が前記第1の容量の第1の電極に接続され、第1の基準電圧又は前記第1の基準電圧とは異なる第2の基準電圧をサンプリングする第3の容量及び第4の容量と、

それぞれの第1の電極が前記第2の容量の第1の電極に接続され、前記第1の基準電圧又は前記第2の基準電圧をサンプリングする第5の容量及び第6の容量と、

前記第1の容量にサンプリングされた電荷と前記第3の容量及び前記第4の容量にサンプリングされた電荷とを加算又は減算して第1の加算又は減算結果を得るとともに、前記第2の容量にサンプリングされた電荷と前記第5の容量及び前記第6の容量にサンプリングされた電荷とを加算又は減算して第2の加算又は減算結果を得て、前記第1の加算又は減算結果を積分し出力するとともに、前記第2の加算又は減算結果を積分し出力する演算器とを有する演算回路を1つ以上含むことを特徴とするA/D変換器。

【請求項2】

前記第3の容量及び前記第4の容量の内の一方の容量の第2の電極が前記第1の基準電圧に接続され、他方の容量の第2の電極が前記第2の基準電圧に接続されるとともに、前記第5の容量及び前記第6の容量の内の一方の容量の第2の電極が前記第1の基準電圧に接続され、他方の容量の第2の電極が前記第2の基準電圧に接続される第1の状態と、

前記変調器の出力に基づくフィードバック信号に応じて、前記第3の容量及び前記第4の容量の各々の第2の電極が前記第1の基準電圧に接続されるとともに前記第5の容量及び前記第6の容量の各々の第2の電極が前記第2の基準電圧に接続されるか、又は前記第3の容量及び前記第4の容量の各々の第2の電極が前記第2の基準電圧に接続されるとともに前記第5の容量及び前記第6の容量の各々の第2の電極が前記第1の基準電圧に接続される第2の状態とを交互に繰り返すことを特徴とする請求項1記載のA/D変換器。

【請求項3】

前記変調器は複数の前記演算回路を有し、

前後に配置された前記複数の演算回路の一方の前記演算回路が前記第1の状態とされるとき、他方の前記演算回路は前記第2の状態とされることを特徴とする請求項2記載のA/D変換器。

【請求項4】

前記演算回路は、サンプリング状態と演算状態を交互に繰り返し、

前記サンプリング状態では、前記第3の容量及び前記第6の容量の各々の第2の電極は前記第1の基準電圧に接続され、前記第4の容量及び前記第5の容量の各々の第2の電極は前記第2の基準電圧に接続され、

前記演算状態で加算を行う場合には、前記第3の容量及び前記第4の容量の各々の第2の電極は前記第1の基準電圧に接続され、前記第5の容量及び前記第6の容量の各々の第2の電極は前記第2の基準電圧に接続され、

前記演算状態で減算を行う場合には、前記第3の容量及び前記第4の容量の各々の第2の電極は前記第2の基準電圧に接続され、前記第5の容量及び前記第6の容量の各々の第2の電極は前記第1の基準電圧に接続されることを特徴とする請求項1記載のA/D変換器。

【請求項5】

前記演算器は、

前記第1の容量、前記第3の容量、及び前記第4の容量の各々の前記第1の電極に第1のスイッチを介して負側入力ノードが接続され、前記第2の容量、前記第5の容量、及び前記第6の容量の各々の前記第1の電極に第2のスイッチを介して正側入力ノードが接続される全差動オペアンプと、

前記全差動オペアンプの前記負側入力ノードと正側出力ノードとの間に接続される第7の容量と、

前記全差動オペアンプの前記正側入力ノードと負側出力ノードとの間に接続される第8の容量とを有することを特徴とする請求項1〜4の何れか1項に記載のA/D変換器。

【請求項6】

前記演算器は、

前記第1の容量、前記第3の容量、及び前記第4の容量の各々の前記第1の電極に負側入力ノードが接続され、前記第2の容量、前記第5の容量、及び前記第6の容量の各々の前記第1の電極に正側入力ノードが接続される全差動オペアンプと、

前記全差動オペアンプの前記負側入力ノードと正側出力ノードとの間に直列接続される第1のスイッチ及び第7の容量と、

前記全差動オペアンプの前記負側入力ノードと前記正側出力ノードとの間に接続される第2のスイッチと、

前記全差動オペアンプの前記正側入力ノードと負側出力ノードとの間に直列接続される第3のスイッチ及び第8の容量と、

前記全差動オペアンプの前記正側入力ノードと前記負側出力ノードとの間に接続される第4のスイッチとを有することを特徴とする請求項1〜4の何れか1項に記載のA/D変換器。

【請求項7】

前記変調器は複数の前記演算回路を有し、少なくとも1つの演算回路の演算器は、

前記第1の容量、前記第3の容量、及び前記第4の容量の各々の前記第1の電極に負側入力ノードが接続され、前記第2の容量、前記第5の容量、及び前記第6の容量の各々の前記第1の電極に正側入力ノードが接続される全差動オペアンプと、

前記全差動オペアンプの前記負側入力ノードと正側出力ノードとの間に直列接続される第3のスイッチ及び第9の容量と、

前記全差動オペアンプの前記負側入力ノードと前記正側出力ノードとの間に接続される第4のスイッチと、

前記全差動オペアンプの前記正側入力ノードと負側出力ノードとの間に直列接続される第5のスイッチ及び第10の容量と、

前記全差動オペアンプの前記正側入力ノードと前記負側出力ノードとの間に接続される第6のスイッチとを有することを特徴とする請求項5記載のA/D変換器。

【請求項8】

前記変調器は複数の前記演算回路を有し、

一段目の演算回路の演算器は、

前記第1の容量、前記第3の容量、及び前記第4の容量の各々の前記第1の電極に負側入力ノードが接続され、前記第2の容量、前記第5の容量、及び前記第6の容量の各々の前記第1の電極に正側入力ノードが接続される全差動オペアンプと、

前記全差動オペアンプの前記負側入力ノードと正側出力ノードとの間に直列接続される第1のスイッチ及び第7の容量と、

前記全差動オペアンプの前記負側入力ノードと前記正側出力ノードとの間に接続される第2のスイッチと、

前記全差動オペアンプの前記正側入力ノードと負側出力ノードとの間に直列接続される第3のスイッチ及び第8の容量と、

前記全差動オペアンプの前記正側入力ノードと前記負側出力ノードとの間に接続される第4のスイッチとを有し、

一段目より後段の演算回路の演算器は、

前記第1の容量、前記第3の容量、及び前記第4の容量の各々の前記第1の電極に第5のスイッチを介して負側入力ノードが接続され、前記第2の容量、前記第5の容量、及び前記第6の容量の各々の前記第1の電極に第6のスイッチを介して正側入力ノードが接続される全差動オペアンプと、

前記全差動オペアンプの前記負側入力ノードと正側出力ノードとの間に接続される第9の容量と、

前記全差動オペアンプの前記正側入力ノードと負側出力ノードとの間に接続される第10の容量とを有することを特徴とする請求項1〜4の何れか1項に記載のA/D変換器。

【請求項9】

前記第1の基準電圧は接地電圧であり、前記第2の基準電圧は参照電圧であることを特徴とする請求項1〜8の何れか1項に記載のA/D変換器。

【請求項1】

入力される差動アナログ信号をデジタルデータに変換するデルタシグマ型のA/D変換器であって、

前記差動アナログ信号をデルタシグマ変調する変調器と、

前記変調器の出力を基に前記デジタルデータを生成するデシメーションフィルタとを備え、

前記変調器は、

入力信号をサンプリングする第1の容量及び第2の容量と、

それぞれの第1の電極が前記第1の容量の第1の電極に接続され、第1の基準電圧又は前記第1の基準電圧とは異なる第2の基準電圧をサンプリングする第3の容量及び第4の容量と、

それぞれの第1の電極が前記第2の容量の第1の電極に接続され、前記第1の基準電圧又は前記第2の基準電圧をサンプリングする第5の容量及び第6の容量と、

前記第1の容量にサンプリングされた電荷と前記第3の容量及び前記第4の容量にサンプリングされた電荷とを加算又は減算して第1の加算又は減算結果を得るとともに、前記第2の容量にサンプリングされた電荷と前記第5の容量及び前記第6の容量にサンプリングされた電荷とを加算又は減算して第2の加算又は減算結果を得て、前記第1の加算又は減算結果を積分し出力するとともに、前記第2の加算又は減算結果を積分し出力する演算器とを有する演算回路を1つ以上含むことを特徴とするA/D変換器。

【請求項2】

前記第3の容量及び前記第4の容量の内の一方の容量の第2の電極が前記第1の基準電圧に接続され、他方の容量の第2の電極が前記第2の基準電圧に接続されるとともに、前記第5の容量及び前記第6の容量の内の一方の容量の第2の電極が前記第1の基準電圧に接続され、他方の容量の第2の電極が前記第2の基準電圧に接続される第1の状態と、

前記変調器の出力に基づくフィードバック信号に応じて、前記第3の容量及び前記第4の容量の各々の第2の電極が前記第1の基準電圧に接続されるとともに前記第5の容量及び前記第6の容量の各々の第2の電極が前記第2の基準電圧に接続されるか、又は前記第3の容量及び前記第4の容量の各々の第2の電極が前記第2の基準電圧に接続されるとともに前記第5の容量及び前記第6の容量の各々の第2の電極が前記第1の基準電圧に接続される第2の状態とを交互に繰り返すことを特徴とする請求項1記載のA/D変換器。

【請求項3】

前記変調器は複数の前記演算回路を有し、

前後に配置された前記複数の演算回路の一方の前記演算回路が前記第1の状態とされるとき、他方の前記演算回路は前記第2の状態とされることを特徴とする請求項2記載のA/D変換器。

【請求項4】

前記演算回路は、サンプリング状態と演算状態を交互に繰り返し、

前記サンプリング状態では、前記第3の容量及び前記第6の容量の各々の第2の電極は前記第1の基準電圧に接続され、前記第4の容量及び前記第5の容量の各々の第2の電極は前記第2の基準電圧に接続され、

前記演算状態で加算を行う場合には、前記第3の容量及び前記第4の容量の各々の第2の電極は前記第1の基準電圧に接続され、前記第5の容量及び前記第6の容量の各々の第2の電極は前記第2の基準電圧に接続され、

前記演算状態で減算を行う場合には、前記第3の容量及び前記第4の容量の各々の第2の電極は前記第2の基準電圧に接続され、前記第5の容量及び前記第6の容量の各々の第2の電極は前記第1の基準電圧に接続されることを特徴とする請求項1記載のA/D変換器。

【請求項5】

前記演算器は、

前記第1の容量、前記第3の容量、及び前記第4の容量の各々の前記第1の電極に第1のスイッチを介して負側入力ノードが接続され、前記第2の容量、前記第5の容量、及び前記第6の容量の各々の前記第1の電極に第2のスイッチを介して正側入力ノードが接続される全差動オペアンプと、

前記全差動オペアンプの前記負側入力ノードと正側出力ノードとの間に接続される第7の容量と、

前記全差動オペアンプの前記正側入力ノードと負側出力ノードとの間に接続される第8の容量とを有することを特徴とする請求項1〜4の何れか1項に記載のA/D変換器。

【請求項6】

前記演算器は、

前記第1の容量、前記第3の容量、及び前記第4の容量の各々の前記第1の電極に負側入力ノードが接続され、前記第2の容量、前記第5の容量、及び前記第6の容量の各々の前記第1の電極に正側入力ノードが接続される全差動オペアンプと、

前記全差動オペアンプの前記負側入力ノードと正側出力ノードとの間に直列接続される第1のスイッチ及び第7の容量と、

前記全差動オペアンプの前記負側入力ノードと前記正側出力ノードとの間に接続される第2のスイッチと、

前記全差動オペアンプの前記正側入力ノードと負側出力ノードとの間に直列接続される第3のスイッチ及び第8の容量と、

前記全差動オペアンプの前記正側入力ノードと前記負側出力ノードとの間に接続される第4のスイッチとを有することを特徴とする請求項1〜4の何れか1項に記載のA/D変換器。

【請求項7】

前記変調器は複数の前記演算回路を有し、少なくとも1つの演算回路の演算器は、

前記第1の容量、前記第3の容量、及び前記第4の容量の各々の前記第1の電極に負側入力ノードが接続され、前記第2の容量、前記第5の容量、及び前記第6の容量の各々の前記第1の電極に正側入力ノードが接続される全差動オペアンプと、

前記全差動オペアンプの前記負側入力ノードと正側出力ノードとの間に直列接続される第3のスイッチ及び第9の容量と、

前記全差動オペアンプの前記負側入力ノードと前記正側出力ノードとの間に接続される第4のスイッチと、

前記全差動オペアンプの前記正側入力ノードと負側出力ノードとの間に直列接続される第5のスイッチ及び第10の容量と、

前記全差動オペアンプの前記正側入力ノードと前記負側出力ノードとの間に接続される第6のスイッチとを有することを特徴とする請求項5記載のA/D変換器。

【請求項8】

前記変調器は複数の前記演算回路を有し、

一段目の演算回路の演算器は、

前記第1の容量、前記第3の容量、及び前記第4の容量の各々の前記第1の電極に負側入力ノードが接続され、前記第2の容量、前記第5の容量、及び前記第6の容量の各々の前記第1の電極に正側入力ノードが接続される全差動オペアンプと、

前記全差動オペアンプの前記負側入力ノードと正側出力ノードとの間に直列接続される第1のスイッチ及び第7の容量と、

前記全差動オペアンプの前記負側入力ノードと前記正側出力ノードとの間に接続される第2のスイッチと、

前記全差動オペアンプの前記正側入力ノードと負側出力ノードとの間に直列接続される第3のスイッチ及び第8の容量と、

前記全差動オペアンプの前記正側入力ノードと前記負側出力ノードとの間に接続される第4のスイッチとを有し、

一段目より後段の演算回路の演算器は、

前記第1の容量、前記第3の容量、及び前記第4の容量の各々の前記第1の電極に第5のスイッチを介して負側入力ノードが接続され、前記第2の容量、前記第5の容量、及び前記第6の容量の各々の前記第1の電極に第6のスイッチを介して正側入力ノードが接続される全差動オペアンプと、

前記全差動オペアンプの前記負側入力ノードと正側出力ノードとの間に接続される第9の容量と、

前記全差動オペアンプの前記正側入力ノードと負側出力ノードとの間に接続される第10の容量とを有することを特徴とする請求項1〜4の何れか1項に記載のA/D変換器。

【請求項9】

前記第1の基準電圧は接地電圧であり、前記第2の基準電圧は参照電圧であることを特徴とする請求項1〜8の何れか1項に記載のA/D変換器。

【図1】

【図2A】

【図2B】

【図2C】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2A】

【図2B】

【図2C】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2013−55450(P2013−55450A)

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願番号】特願2011−191481(P2011−191481)

【出願日】平成23年9月2日(2011.9.2)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願日】平成23年9月2日(2011.9.2)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]