Auメッキ方法及びAuメッキによるAu回路の製造方法

【課題】Si基材上に均一にAuメッキ層を形成したり、ナノメータレベルの連続した金メッキ細線を形成したりする。

【解決手段】Si基材1上にAuメッキ層2を形成するAuメッキ方法であって、Si基材1上に、C、S及びAuを含み半導電性を有するC−S−Au膜よりなる下地層3を形成する下地層形成工程と、電気メッキによるAuメッキを施して下地層3上にAuメッキ層2を形成するAuメッキ工程とを備えている。Si基材1の表面に下地層3を形成してから、レジスト膜を部分的に形成して、レジスト膜以外の部分に下地層3のC−S−Au膜が表出したC−S−Au膜表出部を所定パターンで形成し、レジストの加工パターンをマスクとして、C−S−Au膜表出部上にAuメッキ層2を形成すれば、ナノメータレベルの連続したAuメッキ細線を形成することができる。

【解決手段】Si基材1上にAuメッキ層2を形成するAuメッキ方法であって、Si基材1上に、C、S及びAuを含み半導電性を有するC−S−Au膜よりなる下地層3を形成する下地層形成工程と、電気メッキによるAuメッキを施して下地層3上にAuメッキ層2を形成するAuメッキ工程とを備えている。Si基材1の表面に下地層3を形成してから、レジスト膜を部分的に形成して、レジスト膜以外の部分に下地層3のC−S−Au膜が表出したC−S−Au膜表出部を所定パターンで形成し、レジストの加工パターンをマスクとして、C−S−Au膜表出部上にAuメッキ層2を形成すれば、ナノメータレベルの連続したAuメッキ細線を形成することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、Si基材上にAuメッキ層を形成するAuメッキ方法、及びAuメッキ層よりなるAu回路をSi基材上に所定パターンで形成するAuメッキによるAu回路の製造方法に関する。

【背景技術】

【0002】

半導体集積回路には、従来、アルミニウム配線が用いられてきたが、近年、配線回路の微細化の要望により、導電率の高い銅配線も使われるようになってきている。そして、室温で動作する単一電子トランジスタの研究等が進むに連れて、高密度集積回路の素子デバイスをさらに微細化することが望まれている。このため、素子寸法のみならず、配線回路のさらなる微細化が必要になってきている。

【0003】

配線回路を微細化すると、断面積に対する表面積の割合が増加するので、実質的な導体断面積が減少する。また、多くの金属は酸化するので、実質的な導体断面積は、酸化によっても顕著に減少する。

【0004】

そこで、本発明者は、実質的導体断面積の減少を抑えつつ、配線回路のさらなる微細化を図るべく、配線用金属材料として、化学的に安定で酸化しにくい金を採択し、金メッキによって配線回路を形成することを創案した。

【0005】

しかしながら、半導体デバイスに用いられるSi基材上に金メッキしようとしても、均一なメッキ層を形成することができなかった。これは、SiとAuとの結合力が低いためと考えられる。

【0006】

また、Si基板上にナノメータレベルの金メッキ細線を形成すべく、例えば500nm幅の溝内に金メッキしても、不連続状となってしまい、連続した金メッキ細線を形成することができなかった。このように不連続細線になる理由としては、必ずしも明確ではないが、メッキ用電流の不均一性、Si基板の不均一酸化や、狭い部分にイオンが侵入しにくいことによるマイクロローディング効果が考えられる。

【0007】

なお、電子工学分野や光学分野などにおいて汎用されている従来の材料系を代替する新規な材料として、金属及び有機物を含む化合物薄膜が知られている(例えば、特許文献1参照)。

【0008】

この化合物薄膜は、高屈折率及び高透過性の新規な光学系材料を提供することを目的として案出されたもので、C、S及びAuよりなるC−S−Au膜である。このC−S−Au膜は、一対の平行平板電極間に炭化水素ガス、SF6 ガス及びArガスを導入し、一対の平行平板電極間に高周波電圧を印加して、前記ガスを放電によりプラズマ化するとともに、一方の電極面に設置されたAu板をスパッタリングすることにより、他方の電極面に設置された基板上にC−S−Au膜を堆積させて製造したものである。このC−S−Au膜では、比較的多量のAuを含有させても、Auが均一に分散してクラスターを構成していないため、透明で高い屈折率を有する光学系材料として有望である。

【特許文献1】特開2004−100012号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

本発明は上記実情に鑑みてなされたものであり、Si基材上に均一にAuメッキ層を形成することのできる新規なAuメッキ方法を創出することを第1の技術課題とし、また、そのAuメッキ方法を利用してSi基材上にナノメータレベルの連続した金メッキ細線を形成することを第2の技術課題とするものである。

【課題を解決するための手段】

【0010】

上記課題を解決する本発明のAuメッキ方法は、Si基材上にAuメッキ層を形成するAuメッキ方法であって、前記Si基材上に、C、S及びAuを含み半導電性を有するC−S−Au膜よりなる下地層を形成する下地層形成工程と、電気メッキによるAuメッキを施して前記下地層上に前記Auメッキ層を形成するAuメッキ工程とを備えていることを特徴とするものである。

【0011】

このAuメッキ方法では、下地層として形成された半導電性を有するC−S−Au膜上にAuメッキを施すことにより、均一なAuメッキ層を形成することができる。C−S−Au膜においては、C−S−Au分子がC、S、Auの順で結合している。なお、CとSとは共有結合又はイオン結合により結合し、SとAuとはイオン結合により結合していると考えられる。そして、C−S−Au膜中のCはSiと共有結合により結合し、C−S−Au膜のAuはAuメッキ層と金属結合により結合すると考えられる。このため、このC−S−Au膜中のCがSi基材と大きな結合力で結合し、C−S−Au膜中のAuがAuメッキ層と大きな結合力で結合する。したがって、接着層として機能するC−S−Au膜を介して、Si基材にAuメッキ層を確実に結合させることができ、均一なAuメッキ層の形成が可能になる。

【0012】

本発明のAuメッキ方法は、好適な態様において、前記下地層上にレジスト膜を部分的に形成して、該レジスト膜以外の部分に前記C−S−Au膜が表出したC−S−Au膜表出部を所定パターンで形成するレジスト工程を実施した後に、前記Auメッキ工程を実施して該C−S−Au膜表出部上に前記Auメッキ層を形成する。

【0013】

このAuメッキ方法では、下地層として形成された半導電性を有するC−S−Au膜上にレジスト膜を部分的に形成することにより、C−S−Au膜表出部を所定パターンで形成する。そして、C−S−Au膜表出部上にAuメッキを施すことにより、均一なAuメッキ層を形成する。このため、レジスト膜の形成により、C−S−Au膜表出部を所定パターンで形成することにより、Si基材上に所定のパターンで均一なAuメッキ層を形成することができる。

【0014】

また、このAuメッキ方法では、レジスト膜で区画された溝状のC−S−Au膜表出部にAuメッキ層を形成することになる。このため、C−S−Au膜表出部の幅を狭くした場合は、細い溝内にAuメッキ層を形成することになる。このように細い溝内にAuメッキ層を形成する場合、前述したマイクロローディング効果等により、連続したAuメッキ層の形成が困難になる。この点、本発明のメッキ方法では、半導電性を有するC−S−Au膜を下地層としてAuメッキ層を形成する。このため、C−S−Au膜表出部の幅を狭くして細い溝内にAuメッキ層を形成する場合であっても、連続したAuメッキ層を形成することが可能となる。

【0015】

したがって、前記Auメッキ工程後に、前記レジスト膜を酸化除去すれば、Si基材上にナノメータレベルの連続した金メッキ細線を形成することができる。

【0016】

本発明のAuメッキ方法は、好適な態様において、前記Si基材の表面をリソグラフィ加工して、所定のパターンのSi柱部及び/又はSi壁部と該Si柱部及び/又は該Si壁部以外のSi溝部とを該表面に形成するリソグラフィ工程と、少なくとも前記Si柱部及び/又は前記Si壁部の全体並びに前記Si溝部の表面を酸化して、SiO2 柱部及び/又はSiO2 壁部並びにSiO2 溝部を形成する酸化処理工程と、前記Si基材の表面が略平坦となるように等方エッチング処理することにより、前記SiO2 溝部の絶縁性SiO2 部を残しつつ少なくとも前記SiO2 柱部及び/又は前記SiO2 壁部を除去して、該SiO2 柱部及び/又は該SiO2 壁部が除去された部位にSi基材が表出した導電性Si表出部を形成する等方エッチング工程とを実施した後に、前記下地層形成工程を実施する。

【0017】

このAuメッキ方法では、まずリソグラフィ加工により、所定のパターンのSi柱部及び/又はSi壁部とSi溝部とをSi基材の表面に形成した後、酸化処理により、少なくともSi柱部及び/又はSi壁部の全体並びにSi溝部の表面を酸化して、SiO2 柱部及び/又はSiO2 壁部並びにSiO2 溝部を形成する。その後、Si基材の表面が略平坦となるように等方エッチング処理することにより、SiO2 溝部の絶縁性SiO2 部を残しつつ少なくともSiO2 柱部及び/又はSiO2 壁部を除去して、その除去された部位に導電性Si表出部を形成する。こうして、Si基材の表面に、所定のパターンで、絶縁性SiO2 部と、導電性Si表出部とを形成した後、前記下地層を形成する。そして、下地層として形成された半導電性を有するC−S−Au膜上にAuメッキを施すことにより、均一なAuメッキ層を形成する。このとき、電気メッキにより形成されるAuメッキ層は、絶縁性SiO2 部には形成されず、電流が流れる導電性Si表出部の上のみに形成される。このため、リソグラフィ加工により、所定のパターンのSi柱部及び/又はSi壁部を形成して、この部位にSi表出部を形成することにより、Si基材上に所定のパターンで均一なAuメッキ層を形成することができる。

【0018】

また、このAuメッキ方法では、等方エッチング処理により略平坦とされたSi基材上に前記下地層を介してAuメッキを施すので、前記マイクロローディング効果によってAuメッキ性が低下することもない。このため、請求項2記載のAuメッキ方法よりもさらに細い幅の連続したAuメッキ層の形成が可能となる。したがって、前記Si柱部の径を小さくしたり、前記Si壁部の厚さを薄くしたりすることで、さらに細いナノメータレベルの連続した金メッキ細線を形成することができる。

【0019】

請求項4に記載のAuメッキによるAu回路の製造方法は、Auメッキ層よりなるAu回路をSi基材上に所定パターンで形成するAuメッキによるAu回路の製造方法であって、前記Si基材上に、C、S及びAuを含み半導電性を有するC−S−Au膜よりなる下地層を形成する下地層形成工程と、前記下地層上にレジスト膜を部分的に形成して、該レジスト膜以外の部分に前記C−S−Au膜が表出したC−S−Au膜表出部を所定パターンで形成するレジスト工程と、前記C−S−Au膜表出部上に電気メッキによるAuメッキを施して前記Auメッキ層を形成するAuメッキ工程と、前記レジスト膜を除去するレジスト膜除去工程と、前記Si基材の表面を酸化処理して、前記Auメッキ層を該Si基材から絶縁する絶縁処理工程とを備えていることを特徴とするものである。

【0020】

このAuメッキによるAu回路の製造方法では、請求項2記載のAuメッキ方法を利用して、所定パターンの連続したAuメッキ層を形成する。そして、前記レジスト膜を除去した後、Si基材の表面を酸化処理して、前記Auメッキ層を該Si基材から絶縁する。こうして、Si基材上に絶縁SiO2 層を介して所定パターンのAuメッキ層よりなるAu回路を形成することできる。

【0021】

したがって、請求項4に記載のAuメッキによるAu回路の製造方法によれば、微細なナノメータレベルのAu回路の形成が可能となる。

【0022】

請求項5に記載のAuメッキによるAu回路の製造方法は、Auメッキ層よりなるAu回路をSi基材上に所定パターンで形成するAuメッキによるAu回路の製造方法であって、前記Si基材の表面をリソグラフィ加工して、所定のパターンのSi柱部及び/又はSi壁部と該Si柱部及び/又は該Si壁部以外のSi溝部とを該表面に形成するリソグラフィ工程と、少なくとも前記Si柱部及び/又は前記Si壁部の全体並びに前記Si溝部の表面を酸化して、SiO2 柱部及び/又はSiO2 壁部並びにSiO2 溝部を形成する酸化処理工程と、前記Si基材の表面が略平坦となるように等方エッチング処理することにより、前記SiO2 溝部の絶縁性SiO2 部を残しつつ少なくとも前記SiO2 柱部及び/又は前記SiO2 壁部を除去して、該SiO2 柱部及び/又は該SiO2 壁部が除去された部位にSi基材が表出した導電性Si表出部を形成する等方エッチング工程と、前記Si基材上に、C、S及びAuを含み半導電性を有するC−S−Auよりなる下地層を形成する下地層形成工程と、前記下地層上にAuメッキを施して、前記導電性Si部上のみに前記Auメッキ層を形成するAuメッキ工程と、前記Si基材の表面を酸化処理して、前記Auメッキ層を該Si基材から絶縁する絶縁処理工程とを備えていることを特徴とするものである。

【0023】

このAuメッキによるAu回路の製造方法では、請求項3記載のAuメッキ方法を利用して、所定パターンの連続したAuメッキ層を形成する。そして、Si基材の表面を酸化処理して、前記Auメッキ層を該Si基材から絶縁する。こうして、Si基材上に絶縁SiO2 層を介して所定パターンのAuメッキ層よりなるAu回路を形成することできる。

【0024】

したがって、請求項5に記載のAuメッキによるAu回路の製造方法によれば、請求項4に記載のAuメッキによるAu回路の製造方法よりもさらに微細な、ナノメータレベルのAu回路の形成が可能となる。

【発明を実施するための最良の形態】

【0025】

以下、本発明の具体的な実施形態について図面を参照しつつ説明する。

【0026】

なお、以下の説明において、「%」は「原子%」を意味する。

【0027】

(実施形態1)

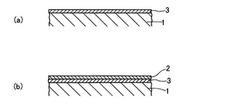

図1及び図2に示す本実施形態は請求項1記載のAuメッキ方法を具現化したものである。このAuメッキ方法は、Si基材1上にAuメッキ層2を形成するもので、下地層形成工程と、Auメッキ工程とを備えている。

【0028】

<下地層形成工程>

下地層形成工程では、図1(a)に示されるように、Si基材1上に、半導電性を有するC−S−Au膜よりなる下地層3を形成する。

【0029】

Si基材1としては、不純物のドープした半導電性を有するものであれば特に限定されない。

【0030】

下地層3は、C、S及びAuを含み半導電性を有するC−S−Au膜であり、Si基材1と下地層3上に形成されるAuメッキ層2との間に介在して、Si基材1に対してAuメッキ層2を接着させる接着性と、Auメッキ時に膜面と平行方向に電気を流してAuメッキを可能にする半導電性とを有するものである。

【0031】

ここに、半導電性を有するC−S−Au膜とは、絶縁物中に導体(導電性粒子)を分散させたもので、このC−S−Au膜上にAuメッキが可能となる膜を意味する。この半導電性を有するC−S−Au膜においては、印加電界によって電気伝導特性は変化するが、ホッピング等により電子が移動することで、膜面に垂直又は平行な方向に電気が流れる。そして、C−S−Au膜においては、C−S−Au分子が2〜3個結合してできた0.4〜1.5nm程度の導電性粒子が、C−S−Au膜に半導電性を付与する。このC−S−Au膜の半導電性は、膜中のAu含有量により変化する。

【0032】

C−S−Au膜中のAu含有量が7%未満になると、前記導電性粒子の大きさや数が不足して半導電性が減じられる。逆に、膜中のAu含有量が7%以上になると、2〜3個のC−S−Au分子が結合した多数の導電性粒子が膜中に均一分散し、良好な半導電性を発揮する。C−S−Au膜の半導電性をより良好にする観点より、膜中のAu含有量は8%以上とすることがより好ましく、10%以上とすることが特に好ましい。このC−S−Au膜におけるAu含有量は、プラズマCVD法でC−S−Au膜を作成する際の、ガス圧や、供給する反応ガス(Ar等)の流量を変化させることで調整することができる。ただし、このAu含有量を増やすことは必ずしも容易ではない。また、C−S−Au膜中のAu含有量が多くなりすぎると、膜中のC含有量の不足により、C−S−Au膜とSi基材との結合力が低下するおそれがある。したがって、Au含有量の上限は30%程度とすることが好ましく、15%程度とすることがより好ましい。

【0033】

また、C−S−Au膜中のS含有量は、Au含有量と同等以上とすることが好ましく、Au含有量と同等とすることが特に好ましい。C−S−Au膜において、Auは、Cと結合しておらず、Sと結合している。このため、膜中のS含有量がAu含有量未満になると、膜中におけるC−S−Au分子が不足し、半導電性が低下する。一方、C−S−Au膜中のS含有量が多くなりすぎると、膜中のC含有量の不足により、C−S−Au膜とSi基材との結合力が低下するおそれがある。

【0034】

なお、C−S−Au膜中のC含有量は、Si基材との結合力を確保する観点より、S含有量よりも多くすることが好ましい。

【0035】

また、前記C−S−Au膜は、不純物元素の含有量が少なければ少ない方が好ましいが、C−S−Au膜として求められる機能(接着性及び半導電性)を損なわない程度の少量なら、C、S及びAu以外の元素(FやO等)を含んでいてもよい。

【0036】

C−S−Au膜よりなる下地層3の厚さは、2〜3個のC−S−Au分子が結合した一つの導電性粒子の大きさ、すなわち0.4〜5nm程度とすることが好ましい。この下地層3が薄すぎると、C−S−Au膜をアンダーコーティングすることの効果が十分に得られない。一方、下地層3の厚さが厚すぎると、下地層3が不安定となり、Auメッキ層4の密着性や均一性が低下するおそれがある。このため、下地層3の厚さは、0.8〜1.5nm程度とすることがより好ましい。

【0037】

このC−S−Au膜よりなる下地層3は、図2に概略的に示される装置を用いて好適に形成することができる。

【0038】

この装置は、プラズマCVD及びAuスパッタリング用反応槽で、チャンバ4と、チャンバ4内に互いに対向して配設された一対の平行平板電極5、6と、一対の平行平板電極5、6に所定の高周波電力を印加する高周波電源7と、チャンバ4内に反応ガスを供給するためのガス供給路8と、チャンバ4内を所定のガス圧に保持するための排気ポンプ9とを備えている。

【0039】

そして、一方(図2の下側)の平行平板電極5の対向面5aに前記Si基材1を設置するとともに、他方(図2の上側)の平行平板電極6のメッシュ状の対向面6aにAu板10を設置した状態で、チャンバ4内にガス供給路8から反応ガスを導入するとともに、一対の平行平板電極5、6に高周波電源7から所定の高周波電力を印加することにより、所定のガス圧の下で、反応ガスを放電させるとともにAu板10をスパッタリングして、Si基材1上にC−S−Au膜を形成する。このとき、チャンバ4内のガス圧や、反応ガスの流量比を変えることで、形成されるC−S−Au膜の組成比を調整することができる。

【0040】

前記反応ガスとしては、例えば、C源としての炭化水素ガスと、S源としてのSF6 ガス及びArガスの混合ガスを好適に用いることができる。また、チャンバ4内のガス圧は、0.07〜0.2Torr程度とすることで、C−S−Au膜におけるAu含有量を7〜15%程度とすることができ、好ましい。

【0041】

こうして形成されたC−S−Au膜においては、Auは凝集してクラスターを形成することなく、膜中で均一に分散する。

【0042】

<Auメッキ工程>

Auメッキ工程では、図1(b)に示されるように、電気メッキによるAuメッキを施して前記下地層3上にAuメッキ層2を形成する。

【0043】

この電気メッキによるAuメッキにおけるメッキ条件は特に限定されず、適宜設定可能である。また、Auメッキ層2の厚さも特に限定されず、適宜設定可能である。

【0044】

なお、本発明者の実験によると、電気メッキする際、Si基材1を負極側に接続することで、このSi基材1上にAuメッキ層2を形成することができた。

【0045】

こうして得られるAuメッキ層2は、Si基材1に確実に結合した均一な膜となる。

【0046】

(実施形態2)

図3に示す本実施形態は請求項2記載のAuメッキ方法を具現化したものである。このAuメッキ方法では、前記実施形態1において、前記下地層形成工程の後にレジスト工程を実施するとともに、前記Auメッキ工程の後にレジスト膜除去工程を実施する。

【0047】

<下地層形成工程>

前記実施形態1と同様に、下地層形成工程では、図3(a)に示されるように、Si基材1上に、半導電性を有するC−S−Au膜よりなる下地層3を形成する。

【0048】

<レジスト工程>

レジスト工程では、図3(b)に示されるように、前記下地層3上に、パターン加工したレジスト膜11を部分的に形成する。

【0049】

このレジスト膜11の形成方法は特に限定されず、例えば、電子線レジストをSi基材1上にスピンコーティング、パターン描画した後、現像する方法を好適に用いることができる。このときの条件は特に限定されず、適宜設定可能である。

【0050】

こうして、下地層3上にレジスト膜11を部分的に形成し、レジスト膜11以外の部分に下地層3のC−S−Au膜が表出したC−S−Au膜表出部12を所定パターンで形成する。

【0051】

<Auメッキ工程>

Auメッキ工程では、図3(c)に示されるように、電気メッキによるAuメッキを施して、前記下地層3上に形成された前記C−S−Au膜表出部12上に前記Auメッキ層2を形成する。

【0052】

<レジスト膜除去工程>

レジスト膜除去工程では、図3(d)に示されるように、前記レジスト膜11を除去する。

【0053】

レジスト膜11の除去方法としては特に限定されず、例えば、酸素プラズマを利用した酸化除去方法を好適に用いることができる。このときの条件は特に限定されず、適宜設定可能である。

【0054】

こうして、Si基材1の表面に、所定のパターンで線状等のAuメッキ層2を形成することができる。

【0055】

そして、本実施形態のAuメッキ方法では、半導電性を有するC−S−Au膜を下地層としてAuメッキ層を形成する。このため、Si表出部12の幅を狭くして細い溝内にAuメッキ層2を形成する場合であっても、連続したAuメッキ層2を形成することが可能となる。したがって、この実施形態によれば、Si基材1上にナノメータレベルの連続した金メッキ細線を形成することができる。

【0056】

(実施形態3)

図4に示す本実施形態は請求項4に記載のAuメッキによるAu回路の製造方法を具現化したものである。このAuメッキによるAu回路の製造方法では、前記実施形態2と同様の前記下地層形成工程、前記レジスト工程、前記Auメッキ工程及び前記レジスト膜除去工程(図4(a)〜(d))を実施した後に、絶縁処理工程を実施する。

【0057】

<絶縁処理工程>

この絶縁処理工程では、図4(e)に示されるように、前記Si基材1の表面を酸化処理して、表層部に所定厚さの絶縁SiO2 層13を形成することにより、前記Auメッキ層2をSi基材1から絶縁する。

【0058】

こうして、Si基材1上に絶縁SiO2 層13を介して所定パターンのAuメッキ層2よりなるAu回路14を形成することできる。

【0059】

したがって、本実施形態のAuメッキによるAu回路の製造方法によれば、微細なナノメータレベルのAu回路14の形成が可能となる。

【0060】

(実施形態4)

図5に示す本実施形態は請求項3記載のAuメッキ方法を具現化したものである。このAuメッキ方法では、前記実施形態1において、前記下地層形成工程の前に、リソグラフィ工程と、酸化処理工程及び等方エッチング工程を実施する。

【0061】

<リソグラフィ工程>

リソグラフィ工程では、図5(a)に示されるように、前記Si基材1の表面をリソグラフィ加工して、所定のパターンのSi柱部及び/又はSi壁部15と、このSi柱部及び/又はSi壁部15以外のSi溝部16とを該表面に形成する。

【0062】

このリソグラフィ工程で加工するSi柱部及び/又はSi壁部15の形状や大きさ等は、形成したいAuメッキ層2に応じて適宜設定可能である。また、Si柱部及びSi壁部のうちのどちらか一方のみを形成してもよいし、双方を組み合わせて形成してもよい。

【0063】

また、リソグラフィ加工の方法や条件等も特に限定されず、適宜設定可能である。例えば、電子線ネガレジストを使用して、Siエッチング加工に耐える厚さのレジスト膜を形成し、電子線描画、現像した後、レジストパターンをマスクにしてSi基材1表面を、RIEプラズマエッチング等によりエッチング加工することで、所定パターンのSi柱部及び/又はSi壁部15を形成することができる。

【0064】

<酸化処理工程>

酸化処理工程では、図5(b)に示されるように、少なくともSi柱部及び/又はSi壁部15の全体並びにSi溝部16の表面を酸化して、SiO2 柱部及び/又はSiO2 壁部17並びにSiO2 溝部18を形成する。

【0065】

このとき、Si柱部及び/又はSi壁部15が全て酸化するまで、酸化処理する。なお、Si柱部及び/又はSi壁部15が立っている部分におけるSi基板1の表面は酸化されなくても、あるいは多少酸化されていてもいずれでもよい。

【0066】

<等方エッチング工程>

等方エッチング工程では、図5(c)に示されるように、Si基材1の表面が略平坦となるように等方エッチング処理することにより、前記SiO2 溝部18の部分に絶縁性SiO2 部19を残しつつ少なくともSiO2 柱部及び/又はSiO2 壁部15を除去して、SiO2 柱部及び/又はSiO2 壁部15が除去された部位にSi基材1が表出した導電性Si表出部20を形成する。

【0067】

このとき、SiO2 柱部及び/又はSiO2 壁部15を完全に除去するとともに、この部分にSi基材1が表出するまで、等方エッチング処理する。この等方エッチング処理の方法や条件等も特に限定されず、適宜設定可能である。例えば、SiO2 の等方エッチングプラズマに晒すことにより、水平方向からSiO2 柱部及び/又はSiO2 壁部15を除去することができ、SiO2 柱部及び/又はSiO2 壁部15がなくなった時点で、Si基材1の表面をほぼ平坦にすることができる。そして、さらに等方エッチングを続けることで、酸化されていないSi基材1を所定の大きさで表出させることができる。

【0068】

こうして、Si基材1の表面に、所定のパターンで、絶縁性SiO2 部19と、導電性Si表出部20とを形成する。

【0069】

その後、前記下地層形成工程を実施して、Si基材1の表面全体に前記下地層3を形成する。

【0070】

そして、前記Auメッキ工程を実施して、下地層3として形成された半導電性を有するC−S−Au膜上にAuメッキを施すことにより、均一なAuメッキ層2を形成する。このとき、電気メッキにより形成されるAuメッキ層2は、下地層3としてのC−S−Au膜が極めて薄いので、絶縁性SiO2 部19の上には形成されず、電流が流れる導電性Si表出部20の上のみに形成される。

【0071】

このため、リソグラフィ加工により、所定のパターンのSi柱部及び/又はSi壁部15を形成して、この部位にSi表出部20を形成することにより、Si基材1上に所定のパターンで均一なAuメッキ層2を形成することができる。

【0072】

また、このAuメッキ方法では、等方エッチング処理により略平坦とされたSi基材1上に前記下地層3を介してAuメッキを施すので、前記マイクロローディング効果によってAuメッキ性が低下することもない。このため、実施形態2のAuメッキ方法よりもさらに細い幅の連続したAuメッキ層2の形成が可能となる。したがって、例えば、Si壁部の厚さを薄くすることで、さらに細いナノメータレベルの連続した金メッキ細線を形成することができる。

【0073】

(実施形態5)

図6に示す本実施形態は請求項5に記載のAuメッキによるAu回路の製造方法を具現化したものである。このAuメッキによるAu回路の製造方法では、前記実施形態4と同様の前記リソグラフィ工程、前記酸化処理工程、前記等方エッチング工程、前記下地層形成工程及び前記Auメッキ工程(図6(a)〜(e))を実施した後に、絶縁処理工程を実施する。

【0074】

<絶縁処理工程>

この絶縁処理工程では、図6(f)に示されるように、前記Si基材1の表面を酸化処理し、前記絶縁性SiO2 部19に重ねるようにSiO2 層を形成することにより、表層部に所定厚さの絶縁SiO2 層13を形成して前記Auメッキ層2をSi基材1から絶縁する。

【0075】

なお、この酸化処理によって、Auメッキ層2で覆われていない領域の下地層3のC−S−Au膜は酸化され、炭素やCO2 、硫黄はSO2 などとして気化除去される。

【0076】

こうして、Si基材1上に絶縁SiO2 層13を介して所定パターンのAuメッキ層2よりなるAu回路20を形成することできる。

【0077】

したがって、本実施形態のAuメッキによるAu回路の製造方法によれば、前記実施形態3で形成したAu回路14よりもさらに微細な、ナノメータレベルのAu回路21の形成が可能となる。

【実施例】

【0078】

(実施例1)

前記実施形態2のAuメッキ方法に準じて、Si基板上に500nm幅のAu細線を形成した。

【0079】

不純物ドープ半導電性n型Si基板上に、電子線レジスト(「SAL601」、シップレー社製)をスピンコーティングしてレジスト膜を形成し、パターン描写した後、現像して、このレジスト膜を溝加工して500nm幅の溝(図3に示すSi表出部12に相当する)を形成した。

【0080】

なお、パターンの描画は、電子線描画装置(「JBX−6000SG」、JEOL社製)を用い、50kV、1000pA、照射量100μC/cm2 の条件で行った。

【0081】

そして、レジストの加工パターンをマスクとした、前記プラズマCVD及びAuスパッタリング用反応槽を用いて、下記表1に示す条件で、前記溝内に約1nm厚のC−S−Au膜よりなる下地層3を形成した。なお、表1中、SCCMとは、1分当たりの理想気体(0℃、760mmHg)換算の流量(cm3 )のことである。また、高周波電源7からは、100W、13.56MHzの高周波電力を印加し、反応時間は30分とした。

【0082】

これにより、表1に原子比が示されるようにAu原子を8%含有し、0.4〜0.6nmの導電性粒子を含んで半導電性を示すC−S−Au膜を形成した。なお、このC−S−Au膜の原子比は、ESCA(Electron Spectro Scopy for Chemical Analysis)にて分析した。また、このC−S−Au膜が半導電性を示すことは、1mmギャップで対向配置された蒸着Cu膜よりなる一対の電極間に、直流電圧4〜5kVを印加したときに、両電極間で放電しなかったことにより確認した。

【0083】

【表1】

【0084】

その後、レジストの加工パターンをマスクとした、Auメッキを行った。このAuメッキでは、NaAuCl4 をエタノールに0.5原子%溶かしたメッキ液を用い、不純物ドープ半導電性n型Si基板を負極として、9Vの電圧印加によって電気メッキした。

【0085】

その結果、図7のSEM像に示されるように、500nm幅の連続的なAu細線を作成することができた。

【0086】

(比較例1)

表1に示されるガス圧及びガス流量に変更すること以外は、前記実施例1と同様にして、C−S−Au膜を作成した。

【0087】

その結果、表1に原子比が示されるように、Au原子の含有量が2%で、半導電性を示さないC−S−Au膜となった。

【0088】

(比較例2)

前記C−S−Au膜よりなる下地層3を形成しないこと以外は、前記実施例1と同様にして、レジストの加工パターンをマスクとした、Auメッキを行った。

【0089】

その結果、図8のSEM像に示されるように、ライン及びスペースの幅がそれそれ100nmの細線パターンが確認された。しかし、このAu細線は不連続状であり、例えば回路配線に利用できるものではなかった。

【図面の簡単な説明】

【0090】

【図1】実施形態1のAuメッキ方法を模式的に説明する部分断面図であり、(a)は下地層形成工程を示し、(b)はAuメッキ工程を示す。

【図2】実施形態1のAuメッキ方法で用いた、プラズマCVD及びAuスパッタリング用反応槽を概略的に示す図である。

【図3】実施形態2のAuメッキ方法を模式的に説明する部分断面図であり、(a)は下地層形成肯定を示し、(b)はレジスト工程を示し、(c)はAuメッキ工程を示し、(d)はレジスト膜除去工程を示す。

【図4】実施形態3のAuメッキによるAu回路の製造方法を模式的に説明する部分断面図であり、(a)はレジスト工程を示し、(b)は下地層形成工程を示し、(c)はAuメッキ工程を示し、(d)はレジスト膜除去工程を示し、(e)は絶縁処理工程を示す。

【図5】実施形態4のAuメッキ方法を模式的に説明する部分断面図であり、(a)はリソグラフィ工程を示し、(b)は酸化処理工程を示し、(c)は等方エッチング工程を示し、(d)は下地層形成工程を示し、(e)はAuメッキ工程を示す。

【図6】実施形態5のAuメッキによるAu回路の製造方法を模式的に説明する部分断面図であり、(a)はリソグラフィ工程を示し、(b)は酸化処理工程を示し、(c)は等方エッチング工程を示し、(d)は下地層形成工程を示し、(e)はAuメッキ工程を示し、(f)は絶縁処理工程を示す。

【図7】実施例1で作成したAu細線を示すSEM(走査型電子顕微鏡)写真である。

【図8】比較例2で作成したAu細線を示すSEM(走査型電子顕微鏡)写真である。

【符号の説明】

【0091】

1…Si基材 2…Auメッキ層

3…下地層(C−S−Au膜) 11…レジスト膜

12…Si表出部 13…絶縁SiO2 層

14、21…Au回路 15…Si柱部(Si壁部)

16…Si溝部 17…SiO2 柱部(SiO2 壁部)

18…SiO2 溝部 19…絶縁性SiO2 部

20…導電性Si表出部

【技術分野】

【0001】

本発明は、Si基材上にAuメッキ層を形成するAuメッキ方法、及びAuメッキ層よりなるAu回路をSi基材上に所定パターンで形成するAuメッキによるAu回路の製造方法に関する。

【背景技術】

【0002】

半導体集積回路には、従来、アルミニウム配線が用いられてきたが、近年、配線回路の微細化の要望により、導電率の高い銅配線も使われるようになってきている。そして、室温で動作する単一電子トランジスタの研究等が進むに連れて、高密度集積回路の素子デバイスをさらに微細化することが望まれている。このため、素子寸法のみならず、配線回路のさらなる微細化が必要になってきている。

【0003】

配線回路を微細化すると、断面積に対する表面積の割合が増加するので、実質的な導体断面積が減少する。また、多くの金属は酸化するので、実質的な導体断面積は、酸化によっても顕著に減少する。

【0004】

そこで、本発明者は、実質的導体断面積の減少を抑えつつ、配線回路のさらなる微細化を図るべく、配線用金属材料として、化学的に安定で酸化しにくい金を採択し、金メッキによって配線回路を形成することを創案した。

【0005】

しかしながら、半導体デバイスに用いられるSi基材上に金メッキしようとしても、均一なメッキ層を形成することができなかった。これは、SiとAuとの結合力が低いためと考えられる。

【0006】

また、Si基板上にナノメータレベルの金メッキ細線を形成すべく、例えば500nm幅の溝内に金メッキしても、不連続状となってしまい、連続した金メッキ細線を形成することができなかった。このように不連続細線になる理由としては、必ずしも明確ではないが、メッキ用電流の不均一性、Si基板の不均一酸化や、狭い部分にイオンが侵入しにくいことによるマイクロローディング効果が考えられる。

【0007】

なお、電子工学分野や光学分野などにおいて汎用されている従来の材料系を代替する新規な材料として、金属及び有機物を含む化合物薄膜が知られている(例えば、特許文献1参照)。

【0008】

この化合物薄膜は、高屈折率及び高透過性の新規な光学系材料を提供することを目的として案出されたもので、C、S及びAuよりなるC−S−Au膜である。このC−S−Au膜は、一対の平行平板電極間に炭化水素ガス、SF6 ガス及びArガスを導入し、一対の平行平板電極間に高周波電圧を印加して、前記ガスを放電によりプラズマ化するとともに、一方の電極面に設置されたAu板をスパッタリングすることにより、他方の電極面に設置された基板上にC−S−Au膜を堆積させて製造したものである。このC−S−Au膜では、比較的多量のAuを含有させても、Auが均一に分散してクラスターを構成していないため、透明で高い屈折率を有する光学系材料として有望である。

【特許文献1】特開2004−100012号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

本発明は上記実情に鑑みてなされたものであり、Si基材上に均一にAuメッキ層を形成することのできる新規なAuメッキ方法を創出することを第1の技術課題とし、また、そのAuメッキ方法を利用してSi基材上にナノメータレベルの連続した金メッキ細線を形成することを第2の技術課題とするものである。

【課題を解決するための手段】

【0010】

上記課題を解決する本発明のAuメッキ方法は、Si基材上にAuメッキ層を形成するAuメッキ方法であって、前記Si基材上に、C、S及びAuを含み半導電性を有するC−S−Au膜よりなる下地層を形成する下地層形成工程と、電気メッキによるAuメッキを施して前記下地層上に前記Auメッキ層を形成するAuメッキ工程とを備えていることを特徴とするものである。

【0011】

このAuメッキ方法では、下地層として形成された半導電性を有するC−S−Au膜上にAuメッキを施すことにより、均一なAuメッキ層を形成することができる。C−S−Au膜においては、C−S−Au分子がC、S、Auの順で結合している。なお、CとSとは共有結合又はイオン結合により結合し、SとAuとはイオン結合により結合していると考えられる。そして、C−S−Au膜中のCはSiと共有結合により結合し、C−S−Au膜のAuはAuメッキ層と金属結合により結合すると考えられる。このため、このC−S−Au膜中のCがSi基材と大きな結合力で結合し、C−S−Au膜中のAuがAuメッキ層と大きな結合力で結合する。したがって、接着層として機能するC−S−Au膜を介して、Si基材にAuメッキ層を確実に結合させることができ、均一なAuメッキ層の形成が可能になる。

【0012】

本発明のAuメッキ方法は、好適な態様において、前記下地層上にレジスト膜を部分的に形成して、該レジスト膜以外の部分に前記C−S−Au膜が表出したC−S−Au膜表出部を所定パターンで形成するレジスト工程を実施した後に、前記Auメッキ工程を実施して該C−S−Au膜表出部上に前記Auメッキ層を形成する。

【0013】

このAuメッキ方法では、下地層として形成された半導電性を有するC−S−Au膜上にレジスト膜を部分的に形成することにより、C−S−Au膜表出部を所定パターンで形成する。そして、C−S−Au膜表出部上にAuメッキを施すことにより、均一なAuメッキ層を形成する。このため、レジスト膜の形成により、C−S−Au膜表出部を所定パターンで形成することにより、Si基材上に所定のパターンで均一なAuメッキ層を形成することができる。

【0014】

また、このAuメッキ方法では、レジスト膜で区画された溝状のC−S−Au膜表出部にAuメッキ層を形成することになる。このため、C−S−Au膜表出部の幅を狭くした場合は、細い溝内にAuメッキ層を形成することになる。このように細い溝内にAuメッキ層を形成する場合、前述したマイクロローディング効果等により、連続したAuメッキ層の形成が困難になる。この点、本発明のメッキ方法では、半導電性を有するC−S−Au膜を下地層としてAuメッキ層を形成する。このため、C−S−Au膜表出部の幅を狭くして細い溝内にAuメッキ層を形成する場合であっても、連続したAuメッキ層を形成することが可能となる。

【0015】

したがって、前記Auメッキ工程後に、前記レジスト膜を酸化除去すれば、Si基材上にナノメータレベルの連続した金メッキ細線を形成することができる。

【0016】

本発明のAuメッキ方法は、好適な態様において、前記Si基材の表面をリソグラフィ加工して、所定のパターンのSi柱部及び/又はSi壁部と該Si柱部及び/又は該Si壁部以外のSi溝部とを該表面に形成するリソグラフィ工程と、少なくとも前記Si柱部及び/又は前記Si壁部の全体並びに前記Si溝部の表面を酸化して、SiO2 柱部及び/又はSiO2 壁部並びにSiO2 溝部を形成する酸化処理工程と、前記Si基材の表面が略平坦となるように等方エッチング処理することにより、前記SiO2 溝部の絶縁性SiO2 部を残しつつ少なくとも前記SiO2 柱部及び/又は前記SiO2 壁部を除去して、該SiO2 柱部及び/又は該SiO2 壁部が除去された部位にSi基材が表出した導電性Si表出部を形成する等方エッチング工程とを実施した後に、前記下地層形成工程を実施する。

【0017】

このAuメッキ方法では、まずリソグラフィ加工により、所定のパターンのSi柱部及び/又はSi壁部とSi溝部とをSi基材の表面に形成した後、酸化処理により、少なくともSi柱部及び/又はSi壁部の全体並びにSi溝部の表面を酸化して、SiO2 柱部及び/又はSiO2 壁部並びにSiO2 溝部を形成する。その後、Si基材の表面が略平坦となるように等方エッチング処理することにより、SiO2 溝部の絶縁性SiO2 部を残しつつ少なくともSiO2 柱部及び/又はSiO2 壁部を除去して、その除去された部位に導電性Si表出部を形成する。こうして、Si基材の表面に、所定のパターンで、絶縁性SiO2 部と、導電性Si表出部とを形成した後、前記下地層を形成する。そして、下地層として形成された半導電性を有するC−S−Au膜上にAuメッキを施すことにより、均一なAuメッキ層を形成する。このとき、電気メッキにより形成されるAuメッキ層は、絶縁性SiO2 部には形成されず、電流が流れる導電性Si表出部の上のみに形成される。このため、リソグラフィ加工により、所定のパターンのSi柱部及び/又はSi壁部を形成して、この部位にSi表出部を形成することにより、Si基材上に所定のパターンで均一なAuメッキ層を形成することができる。

【0018】

また、このAuメッキ方法では、等方エッチング処理により略平坦とされたSi基材上に前記下地層を介してAuメッキを施すので、前記マイクロローディング効果によってAuメッキ性が低下することもない。このため、請求項2記載のAuメッキ方法よりもさらに細い幅の連続したAuメッキ層の形成が可能となる。したがって、前記Si柱部の径を小さくしたり、前記Si壁部の厚さを薄くしたりすることで、さらに細いナノメータレベルの連続した金メッキ細線を形成することができる。

【0019】

請求項4に記載のAuメッキによるAu回路の製造方法は、Auメッキ層よりなるAu回路をSi基材上に所定パターンで形成するAuメッキによるAu回路の製造方法であって、前記Si基材上に、C、S及びAuを含み半導電性を有するC−S−Au膜よりなる下地層を形成する下地層形成工程と、前記下地層上にレジスト膜を部分的に形成して、該レジスト膜以外の部分に前記C−S−Au膜が表出したC−S−Au膜表出部を所定パターンで形成するレジスト工程と、前記C−S−Au膜表出部上に電気メッキによるAuメッキを施して前記Auメッキ層を形成するAuメッキ工程と、前記レジスト膜を除去するレジスト膜除去工程と、前記Si基材の表面を酸化処理して、前記Auメッキ層を該Si基材から絶縁する絶縁処理工程とを備えていることを特徴とするものである。

【0020】

このAuメッキによるAu回路の製造方法では、請求項2記載のAuメッキ方法を利用して、所定パターンの連続したAuメッキ層を形成する。そして、前記レジスト膜を除去した後、Si基材の表面を酸化処理して、前記Auメッキ層を該Si基材から絶縁する。こうして、Si基材上に絶縁SiO2 層を介して所定パターンのAuメッキ層よりなるAu回路を形成することできる。

【0021】

したがって、請求項4に記載のAuメッキによるAu回路の製造方法によれば、微細なナノメータレベルのAu回路の形成が可能となる。

【0022】

請求項5に記載のAuメッキによるAu回路の製造方法は、Auメッキ層よりなるAu回路をSi基材上に所定パターンで形成するAuメッキによるAu回路の製造方法であって、前記Si基材の表面をリソグラフィ加工して、所定のパターンのSi柱部及び/又はSi壁部と該Si柱部及び/又は該Si壁部以外のSi溝部とを該表面に形成するリソグラフィ工程と、少なくとも前記Si柱部及び/又は前記Si壁部の全体並びに前記Si溝部の表面を酸化して、SiO2 柱部及び/又はSiO2 壁部並びにSiO2 溝部を形成する酸化処理工程と、前記Si基材の表面が略平坦となるように等方エッチング処理することにより、前記SiO2 溝部の絶縁性SiO2 部を残しつつ少なくとも前記SiO2 柱部及び/又は前記SiO2 壁部を除去して、該SiO2 柱部及び/又は該SiO2 壁部が除去された部位にSi基材が表出した導電性Si表出部を形成する等方エッチング工程と、前記Si基材上に、C、S及びAuを含み半導電性を有するC−S−Auよりなる下地層を形成する下地層形成工程と、前記下地層上にAuメッキを施して、前記導電性Si部上のみに前記Auメッキ層を形成するAuメッキ工程と、前記Si基材の表面を酸化処理して、前記Auメッキ層を該Si基材から絶縁する絶縁処理工程とを備えていることを特徴とするものである。

【0023】

このAuメッキによるAu回路の製造方法では、請求項3記載のAuメッキ方法を利用して、所定パターンの連続したAuメッキ層を形成する。そして、Si基材の表面を酸化処理して、前記Auメッキ層を該Si基材から絶縁する。こうして、Si基材上に絶縁SiO2 層を介して所定パターンのAuメッキ層よりなるAu回路を形成することできる。

【0024】

したがって、請求項5に記載のAuメッキによるAu回路の製造方法によれば、請求項4に記載のAuメッキによるAu回路の製造方法よりもさらに微細な、ナノメータレベルのAu回路の形成が可能となる。

【発明を実施するための最良の形態】

【0025】

以下、本発明の具体的な実施形態について図面を参照しつつ説明する。

【0026】

なお、以下の説明において、「%」は「原子%」を意味する。

【0027】

(実施形態1)

図1及び図2に示す本実施形態は請求項1記載のAuメッキ方法を具現化したものである。このAuメッキ方法は、Si基材1上にAuメッキ層2を形成するもので、下地層形成工程と、Auメッキ工程とを備えている。

【0028】

<下地層形成工程>

下地層形成工程では、図1(a)に示されるように、Si基材1上に、半導電性を有するC−S−Au膜よりなる下地層3を形成する。

【0029】

Si基材1としては、不純物のドープした半導電性を有するものであれば特に限定されない。

【0030】

下地層3は、C、S及びAuを含み半導電性を有するC−S−Au膜であり、Si基材1と下地層3上に形成されるAuメッキ層2との間に介在して、Si基材1に対してAuメッキ層2を接着させる接着性と、Auメッキ時に膜面と平行方向に電気を流してAuメッキを可能にする半導電性とを有するものである。

【0031】

ここに、半導電性を有するC−S−Au膜とは、絶縁物中に導体(導電性粒子)を分散させたもので、このC−S−Au膜上にAuメッキが可能となる膜を意味する。この半導電性を有するC−S−Au膜においては、印加電界によって電気伝導特性は変化するが、ホッピング等により電子が移動することで、膜面に垂直又は平行な方向に電気が流れる。そして、C−S−Au膜においては、C−S−Au分子が2〜3個結合してできた0.4〜1.5nm程度の導電性粒子が、C−S−Au膜に半導電性を付与する。このC−S−Au膜の半導電性は、膜中のAu含有量により変化する。

【0032】

C−S−Au膜中のAu含有量が7%未満になると、前記導電性粒子の大きさや数が不足して半導電性が減じられる。逆に、膜中のAu含有量が7%以上になると、2〜3個のC−S−Au分子が結合した多数の導電性粒子が膜中に均一分散し、良好な半導電性を発揮する。C−S−Au膜の半導電性をより良好にする観点より、膜中のAu含有量は8%以上とすることがより好ましく、10%以上とすることが特に好ましい。このC−S−Au膜におけるAu含有量は、プラズマCVD法でC−S−Au膜を作成する際の、ガス圧や、供給する反応ガス(Ar等)の流量を変化させることで調整することができる。ただし、このAu含有量を増やすことは必ずしも容易ではない。また、C−S−Au膜中のAu含有量が多くなりすぎると、膜中のC含有量の不足により、C−S−Au膜とSi基材との結合力が低下するおそれがある。したがって、Au含有量の上限は30%程度とすることが好ましく、15%程度とすることがより好ましい。

【0033】

また、C−S−Au膜中のS含有量は、Au含有量と同等以上とすることが好ましく、Au含有量と同等とすることが特に好ましい。C−S−Au膜において、Auは、Cと結合しておらず、Sと結合している。このため、膜中のS含有量がAu含有量未満になると、膜中におけるC−S−Au分子が不足し、半導電性が低下する。一方、C−S−Au膜中のS含有量が多くなりすぎると、膜中のC含有量の不足により、C−S−Au膜とSi基材との結合力が低下するおそれがある。

【0034】

なお、C−S−Au膜中のC含有量は、Si基材との結合力を確保する観点より、S含有量よりも多くすることが好ましい。

【0035】

また、前記C−S−Au膜は、不純物元素の含有量が少なければ少ない方が好ましいが、C−S−Au膜として求められる機能(接着性及び半導電性)を損なわない程度の少量なら、C、S及びAu以外の元素(FやO等)を含んでいてもよい。

【0036】

C−S−Au膜よりなる下地層3の厚さは、2〜3個のC−S−Au分子が結合した一つの導電性粒子の大きさ、すなわち0.4〜5nm程度とすることが好ましい。この下地層3が薄すぎると、C−S−Au膜をアンダーコーティングすることの効果が十分に得られない。一方、下地層3の厚さが厚すぎると、下地層3が不安定となり、Auメッキ層4の密着性や均一性が低下するおそれがある。このため、下地層3の厚さは、0.8〜1.5nm程度とすることがより好ましい。

【0037】

このC−S−Au膜よりなる下地層3は、図2に概略的に示される装置を用いて好適に形成することができる。

【0038】

この装置は、プラズマCVD及びAuスパッタリング用反応槽で、チャンバ4と、チャンバ4内に互いに対向して配設された一対の平行平板電極5、6と、一対の平行平板電極5、6に所定の高周波電力を印加する高周波電源7と、チャンバ4内に反応ガスを供給するためのガス供給路8と、チャンバ4内を所定のガス圧に保持するための排気ポンプ9とを備えている。

【0039】

そして、一方(図2の下側)の平行平板電極5の対向面5aに前記Si基材1を設置するとともに、他方(図2の上側)の平行平板電極6のメッシュ状の対向面6aにAu板10を設置した状態で、チャンバ4内にガス供給路8から反応ガスを導入するとともに、一対の平行平板電極5、6に高周波電源7から所定の高周波電力を印加することにより、所定のガス圧の下で、反応ガスを放電させるとともにAu板10をスパッタリングして、Si基材1上にC−S−Au膜を形成する。このとき、チャンバ4内のガス圧や、反応ガスの流量比を変えることで、形成されるC−S−Au膜の組成比を調整することができる。

【0040】

前記反応ガスとしては、例えば、C源としての炭化水素ガスと、S源としてのSF6 ガス及びArガスの混合ガスを好適に用いることができる。また、チャンバ4内のガス圧は、0.07〜0.2Torr程度とすることで、C−S−Au膜におけるAu含有量を7〜15%程度とすることができ、好ましい。

【0041】

こうして形成されたC−S−Au膜においては、Auは凝集してクラスターを形成することなく、膜中で均一に分散する。

【0042】

<Auメッキ工程>

Auメッキ工程では、図1(b)に示されるように、電気メッキによるAuメッキを施して前記下地層3上にAuメッキ層2を形成する。

【0043】

この電気メッキによるAuメッキにおけるメッキ条件は特に限定されず、適宜設定可能である。また、Auメッキ層2の厚さも特に限定されず、適宜設定可能である。

【0044】

なお、本発明者の実験によると、電気メッキする際、Si基材1を負極側に接続することで、このSi基材1上にAuメッキ層2を形成することができた。

【0045】

こうして得られるAuメッキ層2は、Si基材1に確実に結合した均一な膜となる。

【0046】

(実施形態2)

図3に示す本実施形態は請求項2記載のAuメッキ方法を具現化したものである。このAuメッキ方法では、前記実施形態1において、前記下地層形成工程の後にレジスト工程を実施するとともに、前記Auメッキ工程の後にレジスト膜除去工程を実施する。

【0047】

<下地層形成工程>

前記実施形態1と同様に、下地層形成工程では、図3(a)に示されるように、Si基材1上に、半導電性を有するC−S−Au膜よりなる下地層3を形成する。

【0048】

<レジスト工程>

レジスト工程では、図3(b)に示されるように、前記下地層3上に、パターン加工したレジスト膜11を部分的に形成する。

【0049】

このレジスト膜11の形成方法は特に限定されず、例えば、電子線レジストをSi基材1上にスピンコーティング、パターン描画した後、現像する方法を好適に用いることができる。このときの条件は特に限定されず、適宜設定可能である。

【0050】

こうして、下地層3上にレジスト膜11を部分的に形成し、レジスト膜11以外の部分に下地層3のC−S−Au膜が表出したC−S−Au膜表出部12を所定パターンで形成する。

【0051】

<Auメッキ工程>

Auメッキ工程では、図3(c)に示されるように、電気メッキによるAuメッキを施して、前記下地層3上に形成された前記C−S−Au膜表出部12上に前記Auメッキ層2を形成する。

【0052】

<レジスト膜除去工程>

レジスト膜除去工程では、図3(d)に示されるように、前記レジスト膜11を除去する。

【0053】

レジスト膜11の除去方法としては特に限定されず、例えば、酸素プラズマを利用した酸化除去方法を好適に用いることができる。このときの条件は特に限定されず、適宜設定可能である。

【0054】

こうして、Si基材1の表面に、所定のパターンで線状等のAuメッキ層2を形成することができる。

【0055】

そして、本実施形態のAuメッキ方法では、半導電性を有するC−S−Au膜を下地層としてAuメッキ層を形成する。このため、Si表出部12の幅を狭くして細い溝内にAuメッキ層2を形成する場合であっても、連続したAuメッキ層2を形成することが可能となる。したがって、この実施形態によれば、Si基材1上にナノメータレベルの連続した金メッキ細線を形成することができる。

【0056】

(実施形態3)

図4に示す本実施形態は請求項4に記載のAuメッキによるAu回路の製造方法を具現化したものである。このAuメッキによるAu回路の製造方法では、前記実施形態2と同様の前記下地層形成工程、前記レジスト工程、前記Auメッキ工程及び前記レジスト膜除去工程(図4(a)〜(d))を実施した後に、絶縁処理工程を実施する。

【0057】

<絶縁処理工程>

この絶縁処理工程では、図4(e)に示されるように、前記Si基材1の表面を酸化処理して、表層部に所定厚さの絶縁SiO2 層13を形成することにより、前記Auメッキ層2をSi基材1から絶縁する。

【0058】

こうして、Si基材1上に絶縁SiO2 層13を介して所定パターンのAuメッキ層2よりなるAu回路14を形成することできる。

【0059】

したがって、本実施形態のAuメッキによるAu回路の製造方法によれば、微細なナノメータレベルのAu回路14の形成が可能となる。

【0060】

(実施形態4)

図5に示す本実施形態は請求項3記載のAuメッキ方法を具現化したものである。このAuメッキ方法では、前記実施形態1において、前記下地層形成工程の前に、リソグラフィ工程と、酸化処理工程及び等方エッチング工程を実施する。

【0061】

<リソグラフィ工程>

リソグラフィ工程では、図5(a)に示されるように、前記Si基材1の表面をリソグラフィ加工して、所定のパターンのSi柱部及び/又はSi壁部15と、このSi柱部及び/又はSi壁部15以外のSi溝部16とを該表面に形成する。

【0062】

このリソグラフィ工程で加工するSi柱部及び/又はSi壁部15の形状や大きさ等は、形成したいAuメッキ層2に応じて適宜設定可能である。また、Si柱部及びSi壁部のうちのどちらか一方のみを形成してもよいし、双方を組み合わせて形成してもよい。

【0063】

また、リソグラフィ加工の方法や条件等も特に限定されず、適宜設定可能である。例えば、電子線ネガレジストを使用して、Siエッチング加工に耐える厚さのレジスト膜を形成し、電子線描画、現像した後、レジストパターンをマスクにしてSi基材1表面を、RIEプラズマエッチング等によりエッチング加工することで、所定パターンのSi柱部及び/又はSi壁部15を形成することができる。

【0064】

<酸化処理工程>

酸化処理工程では、図5(b)に示されるように、少なくともSi柱部及び/又はSi壁部15の全体並びにSi溝部16の表面を酸化して、SiO2 柱部及び/又はSiO2 壁部17並びにSiO2 溝部18を形成する。

【0065】

このとき、Si柱部及び/又はSi壁部15が全て酸化するまで、酸化処理する。なお、Si柱部及び/又はSi壁部15が立っている部分におけるSi基板1の表面は酸化されなくても、あるいは多少酸化されていてもいずれでもよい。

【0066】

<等方エッチング工程>

等方エッチング工程では、図5(c)に示されるように、Si基材1の表面が略平坦となるように等方エッチング処理することにより、前記SiO2 溝部18の部分に絶縁性SiO2 部19を残しつつ少なくともSiO2 柱部及び/又はSiO2 壁部15を除去して、SiO2 柱部及び/又はSiO2 壁部15が除去された部位にSi基材1が表出した導電性Si表出部20を形成する。

【0067】

このとき、SiO2 柱部及び/又はSiO2 壁部15を完全に除去するとともに、この部分にSi基材1が表出するまで、等方エッチング処理する。この等方エッチング処理の方法や条件等も特に限定されず、適宜設定可能である。例えば、SiO2 の等方エッチングプラズマに晒すことにより、水平方向からSiO2 柱部及び/又はSiO2 壁部15を除去することができ、SiO2 柱部及び/又はSiO2 壁部15がなくなった時点で、Si基材1の表面をほぼ平坦にすることができる。そして、さらに等方エッチングを続けることで、酸化されていないSi基材1を所定の大きさで表出させることができる。

【0068】

こうして、Si基材1の表面に、所定のパターンで、絶縁性SiO2 部19と、導電性Si表出部20とを形成する。

【0069】

その後、前記下地層形成工程を実施して、Si基材1の表面全体に前記下地層3を形成する。

【0070】

そして、前記Auメッキ工程を実施して、下地層3として形成された半導電性を有するC−S−Au膜上にAuメッキを施すことにより、均一なAuメッキ層2を形成する。このとき、電気メッキにより形成されるAuメッキ層2は、下地層3としてのC−S−Au膜が極めて薄いので、絶縁性SiO2 部19の上には形成されず、電流が流れる導電性Si表出部20の上のみに形成される。

【0071】

このため、リソグラフィ加工により、所定のパターンのSi柱部及び/又はSi壁部15を形成して、この部位にSi表出部20を形成することにより、Si基材1上に所定のパターンで均一なAuメッキ層2を形成することができる。

【0072】

また、このAuメッキ方法では、等方エッチング処理により略平坦とされたSi基材1上に前記下地層3を介してAuメッキを施すので、前記マイクロローディング効果によってAuメッキ性が低下することもない。このため、実施形態2のAuメッキ方法よりもさらに細い幅の連続したAuメッキ層2の形成が可能となる。したがって、例えば、Si壁部の厚さを薄くすることで、さらに細いナノメータレベルの連続した金メッキ細線を形成することができる。

【0073】

(実施形態5)

図6に示す本実施形態は請求項5に記載のAuメッキによるAu回路の製造方法を具現化したものである。このAuメッキによるAu回路の製造方法では、前記実施形態4と同様の前記リソグラフィ工程、前記酸化処理工程、前記等方エッチング工程、前記下地層形成工程及び前記Auメッキ工程(図6(a)〜(e))を実施した後に、絶縁処理工程を実施する。

【0074】

<絶縁処理工程>

この絶縁処理工程では、図6(f)に示されるように、前記Si基材1の表面を酸化処理し、前記絶縁性SiO2 部19に重ねるようにSiO2 層を形成することにより、表層部に所定厚さの絶縁SiO2 層13を形成して前記Auメッキ層2をSi基材1から絶縁する。

【0075】

なお、この酸化処理によって、Auメッキ層2で覆われていない領域の下地層3のC−S−Au膜は酸化され、炭素やCO2 、硫黄はSO2 などとして気化除去される。

【0076】

こうして、Si基材1上に絶縁SiO2 層13を介して所定パターンのAuメッキ層2よりなるAu回路20を形成することできる。

【0077】

したがって、本実施形態のAuメッキによるAu回路の製造方法によれば、前記実施形態3で形成したAu回路14よりもさらに微細な、ナノメータレベルのAu回路21の形成が可能となる。

【実施例】

【0078】

(実施例1)

前記実施形態2のAuメッキ方法に準じて、Si基板上に500nm幅のAu細線を形成した。

【0079】

不純物ドープ半導電性n型Si基板上に、電子線レジスト(「SAL601」、シップレー社製)をスピンコーティングしてレジスト膜を形成し、パターン描写した後、現像して、このレジスト膜を溝加工して500nm幅の溝(図3に示すSi表出部12に相当する)を形成した。

【0080】

なお、パターンの描画は、電子線描画装置(「JBX−6000SG」、JEOL社製)を用い、50kV、1000pA、照射量100μC/cm2 の条件で行った。

【0081】

そして、レジストの加工パターンをマスクとした、前記プラズマCVD及びAuスパッタリング用反応槽を用いて、下記表1に示す条件で、前記溝内に約1nm厚のC−S−Au膜よりなる下地層3を形成した。なお、表1中、SCCMとは、1分当たりの理想気体(0℃、760mmHg)換算の流量(cm3 )のことである。また、高周波電源7からは、100W、13.56MHzの高周波電力を印加し、反応時間は30分とした。

【0082】

これにより、表1に原子比が示されるようにAu原子を8%含有し、0.4〜0.6nmの導電性粒子を含んで半導電性を示すC−S−Au膜を形成した。なお、このC−S−Au膜の原子比は、ESCA(Electron Spectro Scopy for Chemical Analysis)にて分析した。また、このC−S−Au膜が半導電性を示すことは、1mmギャップで対向配置された蒸着Cu膜よりなる一対の電極間に、直流電圧4〜5kVを印加したときに、両電極間で放電しなかったことにより確認した。

【0083】

【表1】

【0084】

その後、レジストの加工パターンをマスクとした、Auメッキを行った。このAuメッキでは、NaAuCl4 をエタノールに0.5原子%溶かしたメッキ液を用い、不純物ドープ半導電性n型Si基板を負極として、9Vの電圧印加によって電気メッキした。

【0085】

その結果、図7のSEM像に示されるように、500nm幅の連続的なAu細線を作成することができた。

【0086】

(比較例1)

表1に示されるガス圧及びガス流量に変更すること以外は、前記実施例1と同様にして、C−S−Au膜を作成した。

【0087】

その結果、表1に原子比が示されるように、Au原子の含有量が2%で、半導電性を示さないC−S−Au膜となった。

【0088】

(比較例2)

前記C−S−Au膜よりなる下地層3を形成しないこと以外は、前記実施例1と同様にして、レジストの加工パターンをマスクとした、Auメッキを行った。

【0089】

その結果、図8のSEM像に示されるように、ライン及びスペースの幅がそれそれ100nmの細線パターンが確認された。しかし、このAu細線は不連続状であり、例えば回路配線に利用できるものではなかった。

【図面の簡単な説明】

【0090】

【図1】実施形態1のAuメッキ方法を模式的に説明する部分断面図であり、(a)は下地層形成工程を示し、(b)はAuメッキ工程を示す。

【図2】実施形態1のAuメッキ方法で用いた、プラズマCVD及びAuスパッタリング用反応槽を概略的に示す図である。

【図3】実施形態2のAuメッキ方法を模式的に説明する部分断面図であり、(a)は下地層形成肯定を示し、(b)はレジスト工程を示し、(c)はAuメッキ工程を示し、(d)はレジスト膜除去工程を示す。

【図4】実施形態3のAuメッキによるAu回路の製造方法を模式的に説明する部分断面図であり、(a)はレジスト工程を示し、(b)は下地層形成工程を示し、(c)はAuメッキ工程を示し、(d)はレジスト膜除去工程を示し、(e)は絶縁処理工程を示す。

【図5】実施形態4のAuメッキ方法を模式的に説明する部分断面図であり、(a)はリソグラフィ工程を示し、(b)は酸化処理工程を示し、(c)は等方エッチング工程を示し、(d)は下地層形成工程を示し、(e)はAuメッキ工程を示す。

【図6】実施形態5のAuメッキによるAu回路の製造方法を模式的に説明する部分断面図であり、(a)はリソグラフィ工程を示し、(b)は酸化処理工程を示し、(c)は等方エッチング工程を示し、(d)は下地層形成工程を示し、(e)はAuメッキ工程を示し、(f)は絶縁処理工程を示す。

【図7】実施例1で作成したAu細線を示すSEM(走査型電子顕微鏡)写真である。

【図8】比較例2で作成したAu細線を示すSEM(走査型電子顕微鏡)写真である。

【符号の説明】

【0091】

1…Si基材 2…Auメッキ層

3…下地層(C−S−Au膜) 11…レジスト膜

12…Si表出部 13…絶縁SiO2 層

14、21…Au回路 15…Si柱部(Si壁部)

16…Si溝部 17…SiO2 柱部(SiO2 壁部)

18…SiO2 溝部 19…絶縁性SiO2 部

20…導電性Si表出部

【特許請求の範囲】

【請求項1】

Si基材上にAuメッキ層を形成するAuメッキ方法であって、

前記Si基材上に、C、S及びAuを含み半導電性を有するC−S−Au膜よりなる下地層を形成する下地層形成工程と、

電気メッキによるAuメッキを施して前記下地層上に前記Auメッキ層を形成するAuメッキ工程とを備えていることを特徴とするAuメッキ方法。

【請求項2】

前記下地層上にレジスト膜を部分的に形成して、該レジスト膜以外の部分に前記C−S−Au膜が表出したC−S−Au膜表出部を所定パターンで形成するレジスト工程を実施した後に、前記Auメッキ工程を実施して該C−S−Au膜表出部上に前記Auメッキ層を形成することを特徴とする請求項1記載のAuメッキ方法。

【請求項3】

前記Si基材の表面をリソグラフィ加工して、所定のパターンのSi柱部及び/又はSi壁部と該Si柱部及び/又は該Si壁部以外のSi溝部とを該表面に形成するリソグラフィ工程と、

少なくとも前記Si柱部及び/又は前記Si壁部の全体並びに前記Si溝部の表面を酸化して、SiO2 柱部及び/又はSiO2 壁部並びにSiO2 溝部を形成する酸化処理工程と、

前記Si基材の表面が略平坦となるように等方エッチング処理することにより、前記SiO2 溝部の絶縁性SiO2 部を残しつつ少なくとも前記SiO2 柱部及び/又は前記SiO2 壁部を除去して、該SiO2 柱部及び/又は該SiO2 壁部が除去された部位にSi基材が表出した導電性Si表出部を形成する等方エッチング工程とを実施した後に、前記下地層形成工程を実施することを特徴とする請求項1記載のAuメッキ方法。

【請求項4】

Auメッキ層よりなるAu回路をSi基材上に所定パターンで形成するAuメッキによるAu回路の製造方法であって、

前記Si基材上に、C、S及びAuを含み半導電性を有するC−S−Au膜よりなる下地層を形成する下地層形成工程と、

前記下地層上にレジスト膜を部分的に形成して、該レジスト膜以外の部分に前記C−S−Au膜が表出したC−S−Au膜表出部を所定パターンで形成するレジスト工程と、

前記C−S−Au膜表出部上に電気メッキによるAuメッキを施して前記Auメッキ層を形成するAuメッキ工程と、

前記レジスト膜を除去するレジスト膜除去工程と、

前記Si基材の表面を酸化処理して、前記Auメッキ層を該Si基材から絶縁する絶縁処理工程とを備えていることを特徴とするAuメッキによるAu回路の製造方法。

【請求項5】

Auメッキ層よりなるAu回路をSi基材上に所定パターンで形成するAuメッキによるAu回路の製造方法であって、

前記Si基材の表面をリソグラフィ加工して、所定のパターンのSi柱部及び/又はSi壁部と該Si柱部及び/又は該Si壁部以外のSi溝部とを該表面に形成するリソグラフィ工程と、

少なくとも前記Si柱部及び/又は前記Si壁部の全体並びに前記Si溝部の表面を酸化して、SiO2 柱部及び/又はSiO2 壁部並びにSiO2 溝部を形成する酸化処理工程と、

前記Si基材の表面が略平坦となるように等方エッチング処理することにより、前記SiO2 溝部の絶縁性SiO2 部を残しつつ少なくとも前記SiO2 柱部及び/又は前記SiO2 壁部を除去して、該SiO2 柱部及び/又は該SiO2 壁部が除去された部位にSi基材が表出した導電性Si表出部を形成する等方エッチング工程と、

前記Si基材上に、C、S及びAuを含み半導電性を有するC−S−Au膜よりなる下地層を形成する下地層形成工程と、

前記下地層上に電気メッキによるAuメッキを施して、前記導電性Si部上のみに前記Auメッキ層を形成するAuメッキ工程と、

前記Si基材の表面を酸化処理して、前記Auメッキ層を該Si基材から絶縁する絶縁処理工程とを備えていることを特徴とするAuメッキによるAu回路の製造方法。

【請求項1】

Si基材上にAuメッキ層を形成するAuメッキ方法であって、

前記Si基材上に、C、S及びAuを含み半導電性を有するC−S−Au膜よりなる下地層を形成する下地層形成工程と、

電気メッキによるAuメッキを施して前記下地層上に前記Auメッキ層を形成するAuメッキ工程とを備えていることを特徴とするAuメッキ方法。

【請求項2】

前記下地層上にレジスト膜を部分的に形成して、該レジスト膜以外の部分に前記C−S−Au膜が表出したC−S−Au膜表出部を所定パターンで形成するレジスト工程を実施した後に、前記Auメッキ工程を実施して該C−S−Au膜表出部上に前記Auメッキ層を形成することを特徴とする請求項1記載のAuメッキ方法。

【請求項3】

前記Si基材の表面をリソグラフィ加工して、所定のパターンのSi柱部及び/又はSi壁部と該Si柱部及び/又は該Si壁部以外のSi溝部とを該表面に形成するリソグラフィ工程と、

少なくとも前記Si柱部及び/又は前記Si壁部の全体並びに前記Si溝部の表面を酸化して、SiO2 柱部及び/又はSiO2 壁部並びにSiO2 溝部を形成する酸化処理工程と、

前記Si基材の表面が略平坦となるように等方エッチング処理することにより、前記SiO2 溝部の絶縁性SiO2 部を残しつつ少なくとも前記SiO2 柱部及び/又は前記SiO2 壁部を除去して、該SiO2 柱部及び/又は該SiO2 壁部が除去された部位にSi基材が表出した導電性Si表出部を形成する等方エッチング工程とを実施した後に、前記下地層形成工程を実施することを特徴とする請求項1記載のAuメッキ方法。

【請求項4】

Auメッキ層よりなるAu回路をSi基材上に所定パターンで形成するAuメッキによるAu回路の製造方法であって、

前記Si基材上に、C、S及びAuを含み半導電性を有するC−S−Au膜よりなる下地層を形成する下地層形成工程と、

前記下地層上にレジスト膜を部分的に形成して、該レジスト膜以外の部分に前記C−S−Au膜が表出したC−S−Au膜表出部を所定パターンで形成するレジスト工程と、

前記C−S−Au膜表出部上に電気メッキによるAuメッキを施して前記Auメッキ層を形成するAuメッキ工程と、

前記レジスト膜を除去するレジスト膜除去工程と、

前記Si基材の表面を酸化処理して、前記Auメッキ層を該Si基材から絶縁する絶縁処理工程とを備えていることを特徴とするAuメッキによるAu回路の製造方法。

【請求項5】

Auメッキ層よりなるAu回路をSi基材上に所定パターンで形成するAuメッキによるAu回路の製造方法であって、

前記Si基材の表面をリソグラフィ加工して、所定のパターンのSi柱部及び/又はSi壁部と該Si柱部及び/又は該Si壁部以外のSi溝部とを該表面に形成するリソグラフィ工程と、

少なくとも前記Si柱部及び/又は前記Si壁部の全体並びに前記Si溝部の表面を酸化して、SiO2 柱部及び/又はSiO2 壁部並びにSiO2 溝部を形成する酸化処理工程と、

前記Si基材の表面が略平坦となるように等方エッチング処理することにより、前記SiO2 溝部の絶縁性SiO2 部を残しつつ少なくとも前記SiO2 柱部及び/又は前記SiO2 壁部を除去して、該SiO2 柱部及び/又は該SiO2 壁部が除去された部位にSi基材が表出した導電性Si表出部を形成する等方エッチング工程と、

前記Si基材上に、C、S及びAuを含み半導電性を有するC−S−Au膜よりなる下地層を形成する下地層形成工程と、

前記下地層上に電気メッキによるAuメッキを施して、前記導電性Si部上のみに前記Auメッキ層を形成するAuメッキ工程と、

前記Si基材の表面を酸化処理して、前記Auメッキ層を該Si基材から絶縁する絶縁処理工程とを備えていることを特徴とするAuメッキによるAu回路の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2007−239003(P2007−239003A)

【公開日】平成19年9月20日(2007.9.20)

【国際特許分類】

【出願番号】特願2006−61494(P2006−61494)

【出願日】平成18年3月7日(2006.3.7)

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 平成17年9月7日 名城大学発行の「平成17年度電気関係学会東海支部連合大会講演論文集」に発表

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 2006年1月20日 社団法人電子情報通信学会発行の「電子情報通信学会技術研究報告 信学技報Vol.105 No.576」に発表

【出願人】(504139662)国立大学法人名古屋大学 (996)

【Fターム(参考)】

【公開日】平成19年9月20日(2007.9.20)

【国際特許分類】

【出願日】平成18年3月7日(2006.3.7)

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 平成17年9月7日 名城大学発行の「平成17年度電気関係学会東海支部連合大会講演論文集」に発表

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 2006年1月20日 社団法人電子情報通信学会発行の「電子情報通信学会技術研究報告 信学技報Vol.105 No.576」に発表

【出願人】(504139662)国立大学法人名古屋大学 (996)

【Fターム(参考)】

[ Back to top ]