CDR回路

【課題】線形位相比較器を用いながら、チャージポンプやVCO等のアナログ回路を不要とすることができ、回路面積を抑えたCDR回路を提供する。

【解決手段】位相比較器902は、データエッジ検出回路111〜114により伝送データのエッジを検出し、データエッジマスク回路115〜118、サンプリング回路119〜122、低域通過型フィルタ123〜126、及びアナログ・デジタル変換回路127〜130により、伝送データのエッジを検出したときの再生クロックの電圧を検出し、検出した電圧に基づいて再生クロックの位相調整を行う。

【解決手段】位相比較器902は、データエッジ検出回路111〜114により伝送データのエッジを検出し、データエッジマスク回路115〜118、サンプリング回路119〜122、低域通過型フィルタ123〜126、及びアナログ・デジタル変換回路127〜130により、伝送データのエッジを検出したときの再生クロックの電圧を検出し、検出した電圧に基づいて再生クロックの位相調整を行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はCDR回路に関し、特に、再生クロックの位相調整に利用して有効な技術に関するものである。

【背景技術】

【0002】

データの転送においては、クロックに同期させたデータを伝送路により送信し、受信側で受信データからクロックを抽出し、受信データを復元する方法が一般的に用いられている。受信データからクロックを抽出する機能を実現する回路はCDR(Clock and Data Recovery)回路と呼ばれる。CDR回路で、伝送データと伝送データから生成したクロックの位相差を判定する回路は、位相比較器と呼ばれ、非線形位相比較器と線形位相比較器に大別される(特許文献1)。非線形位相比較器が用いられる場合には、再生クロックのエッジの前後に伝送データのエッジが存在しているか否かから再生クロックの位相を制御するための信号が生成される。一方、線形位相比較器が用いられる場合には、伝送データと再生クロックの位相差は厳密に算出され、非線形位相比較器を用いた場合と比べ、再生クロックの高い位相調整精度を実現できる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2002−84187号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

近年、データ転送、特にシリアル伝送の高速化に伴い、CDR回路のクロック生成の高性能化が求められている。これに対して、非線形位相比較器を用いたCDR回路では、エッジの存在と不存在の情報のみから位相差を判定するため、再生クロックの位相調整精度を向上させることが難しい。

【0005】

そこで、本願発明者等は本願に先立って、図8に示す従来の線形位相比較器801について検討を行った。線形位相比較器801は、フリップフロップ回路802、803と、AND回路804、805、806と、制御論理(CL)回路807とを具備し、伝送データ808とCDR回路の再生クロック809で高電圧であるVDDレベル(ハイレベル)をラッチすることで、再生クロックの位相制御信号、すなわちアップ信号(UP)810およびダウン信号(DOWN)811とを生成する。

【0006】

線形位相比較器801では、伝送データ808と再生クロック809のうち位相の早い方で先にVDDレベル(ハイレベル)がラッチされる。線形位相比較器801は、伝送データ808の位相が早い場合には、ラッチした信号を位相進み信号としてのアップ信号810として、再生クロックの位相が早い場合には、ラッチした信号を位相遅れ信号としてのダウン信号811として出力する。伝送データ808と再生クロック809がともにハイレベルになった場合、フリップフロップ802および803にリセットをかけることで、伝送データ808と再生クロック809の位相差分だけの時間幅の信号が生成できる。また、伝送データ808の切り替わりがない場合、適切な位相制御信号が得られないため、制御論理回路807にて位相制御信号を制御する。

【0007】

この線形位相比較器801を用いるCDR回路は、伝送データ808と再生クロック809の位相差をハイレベルの時間幅に変換するため、後段の回路はチャージポンプや電圧制御発振器(VCO)等のアナログ回路の使用が前提となり、回路面積の増大が避けられない。ゆえに、線形位相比較器801を使用してCDR回路を構成した場合、回路面積の面で不利であることを本願発明者等は見出した。

【0008】

本願発明は、上述の課題を鑑みてなされたものであり、線形位相比較器を用いた、回路面積を抑えたCDR回路を提供することにある。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば、以下の通りである。本発明のCDR回路では、伝送データのエッジを検出し、伝送データのエッジを検出したときの再生クロックの電圧を検出し、検出した電圧に基づいて再生クロックの位相調整を行う。

【発明の効果】

【0010】

上記手段により、従来の線形位相比較器を用いたCDR回路と異なり、チャージポンプやVCO等のアナログ回路を不要とし、線形位相比較器で伝送データに対する再生クロックの位相調整をするCDR回路の回路面積の低減が図れる。

【図面の簡単な説明】

【0011】

【図1】本発明の実施例における位相比較回路のブロック図である。

【図2】本発明の実施例にかかる立ち上がりデータエッジ用データエッジ検出回路の構成を示す回路図である。

【図3】本発明の実施例にかかる立下りデータエッジ用データエッジ検出回路の構成を示す回路図である。

【図4】本発明の実施例にかかる再生クロック立ち上がり区間用データエッジマスク回路の構成を示す回路図である。

【図5】本発明の実施例にかかる再生クロック立下り区間用データエッジマスク回路の構成を示す回路図である。

【図6】本発明の実施例にかかるサンプリング回路の構成を示す回路図である。

【図7】本発明の実施例におけるデータエッジパルス生成過程の例を示した図である。

【図8】本発明にあたり検討を行った線形位相比較器の構成を示す回路図である。

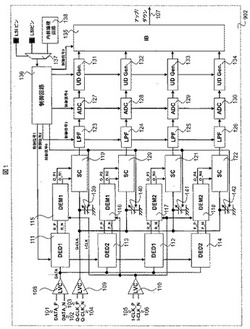

【図9】本発明の実施例にかかるCDR回路を示すブロック図である。

【発明を実施するための形態】

【0012】

以下、本発明を実施例に基づいて詳細に説明する。

【実施例1】

【0013】

図9に本発明の実施例としてCDR回路901を示す。CDR回路901は、位相比較器902と平均化回路903とポインタ回路904とインタポレータ回路905とPLL(Phase Locked Loop)回路906とを備える。

【0014】

位相比較器902は、伝送データ907、908と再生クロック910、911との間の位相差を検出し、再生クロック910、911の位相を制御するための位相制御信号であるアップ/ダウン信号912を生成する。伝送データ907、908の位相に対して、再生クロック910、911の位相が遅れている場合に位相進み信号であるアップ信号を、位相が進んでいる場合に位相遅れ信号であるダウン信号を生成する。

【0015】

平均化回路903は、位相制御信号であるアップ/ダウン信号912を平均化し、ポインタ回路904を制御するための位相制御信号であるアップ/ダウン信号913を生成する。ポインタ回路904は入力される位相制御信号であるアップ/ダウン信号913により、再生クロックの位相を調整し、調整した位相を保持する。インタポレータ回路905は、PLL回路906からクロック信号としてI_CLK914およびQ_CLK915が入力され、ポインタ回路904により指定された位相の再生クロック910、911を生成する。

【0016】

位相比較器902の実施例を図1に示す。位相比較器902は、伝送データのP極(DATA_P)101と、伝送データのN極(DATA_N)102と、QクロックのP極(Q−CLK_P)103と、QクロックのN極(Q−CLK_N)104と、IクロックのP極(I−CLK_P)105と、IクロックのN極(I−CLK_N)106とを入力とし、アップ/ダウン信号107を出力とする。

【0017】

位相比較器902は、差動伝送データを単相CMOSレベルに変換する差動単相変換回路(LVC)108〜110と、単相CMOSレベルの伝送データの立ち上がりエッジを検出しパルス信号を生成するデータエッジ検出回路(DED1)111、112と、単相CMOSレベルの伝送データの立下りエッジを検出しパルス信号を生成するデータエッジ検出回路(DED2)113、114と、データエッジマスク回路(DEM1)115、116と、データエッジマスク回路(DEM2)117、118と、再生クロックをパルス信号でサンプリングするサンプリング回路(SC)119〜122と、サンプリングされた電圧値を平滑化する低域通過型フィルタ(LPF)123〜126と、アナログ電圧値をデジタル値へと変換するアナログ・デジタル変換回路(ADC)127〜130と、再生クロックの位相を制御するための位相制御信号を生成するアップ/ダウン信号生成回路(UD Gen.)131〜134と、アップ/ダウン信号生成回路131〜134の出力を多数決処理により統合するアップ/ダウン信号統合回路(IB)135と、各回路ブロックの特性を制御する制御回路136と、制御回路136をLSI外部/内部論理回路のどちらで制御するかを決定するセレクタ回路137と、本願発明回路の上位論理回路である内部論理回路138と、CDR回路901の再生クロックの立ち上がり時間および立下り時間調整用の可変容量139〜142とを備える。

【0018】

差動単相変換回路108には、伝送データ101および伝送データ102が入力される。差動単相変換回路108からの出力は、CMOSレベルのデータ信号(DATA)としてデータエッジ検出回路111〜114に入力される。差動単相変換回路109には、Qクロック103およびQクロック104が入力される。差動単相変換回路109の出力は、CMOSレベルのQクロック(Q−CLK)として、それぞれ可変容量139〜142に接続されて各サンプリング回路119〜122に入力される。差動単相変換回路110には、Iクロック105およびIクロック106が入力される。差動単相変換回路110の出力は、Q−CLKと90度位相が異なるCMOSレベルのIクロック(I−CLK)として、各データエッジマスク回路115〜118に入力される。

【0019】

図1に示すように、データエッジ検出回路111〜114の出力は、それぞれデータエッジマスク回路115〜118に入力される。データエッジマスク回路115〜118の出力は、それぞれサンプリング回路119〜122に入力される。サンプリング回路119〜122の出力は、それぞれ低域通過型フィルタ123〜126に入力される。低域通過型フィルタ123〜126の出力は、それぞれアナログ・デジタル変換回路127〜130に入力される。アナログ・デジタル変換回路127〜130の出力は、それぞれアップ/ダウン信号生成回路131〜134に入力される。アップ/ダウン信号生成回路131〜134の出力は、アップ/ダウン信号統合回路135に入力される。アップ/ダウン信号統合回路135は、アップ/ダウン信号生成回路131〜134のアップ/ダウン信号出力を多数決処理し、アップ/ダウン信号107を結果として出力する。

【0020】

以下、図7のグラフ701を用いて、位相比較器902の動作を説明する。グラフ702は、差動単相変換回路110の出力のCMOSレベルのIクロック(I−CLK)の電圧の時間変化を示す。グラフ703は、差動単相変換回路109の出力のCMOSレベルのQクロック(Q−CLK)の電圧の時間変化を示す。グラフ704は伝送データのN極(DATA_N)102の電圧の時間変化を示す。グラフ705は伝送データのP極(DATA_P)101の電圧の時間変化を示す。グラフ706は、差動単相変換回路108からの出力のCMOSレベルのデータ信号(DATA)の電圧の時間変化を示す。CDR回路901は、図示していないラッチ回路で、伝送データであるデータ信号(DATA)を再生クロックのIクロック(I−CLK)でラッチして、データを復元する。

【0021】

グラフ707、708は、データエッジ検出回路111およびデータエッジ検出回路112の出力電圧(R_N、R_P)の時間変化を示す。グラフ709、710は、データエッジ検出回路113およびデータエッジ検出回路114の出力電圧(F_N、F_P)の時間変化を示す。

【0022】

グラフ711、712は、データエッジマスク回路115からの出力電圧(O_N1、O_P1)の時間変化を示す。グラフ713、714は、データエッジマスク回路116からの出力電圧(O_N2、O_P2)の時間変化を示す。グラフ715、716は、データエッジマスク回路117からの出力電圧(O_N3、O_P3)の時間変化を示す。グラフ717、718は、データエッジマスク回路118からの出力電圧(O_N4、O_P4)の時間変化を示す。

【0023】

グラフ707、708に示すように、データエッジ検出回路111およびデータエッジ検出回路112は、グラフ706で示す差動単相変換回路108からの出力のCMOSレベルのデータ信号の立ち上がりエッジを検出する。グラフ709、710に示すように、データエッジ検出回路113およびデータエッジ検出回路114は、グラフ706で示す差動単相変換回路108からの出力のCMOSレベルのデータ信号の立ち下がりエッジを検出する。

【0024】

グラフ711、712に示すように、データエッジマスク回路115は、グラフ702に示すIクロックの電圧が高電圧の場合に、データエッジ検出回路111からの出力をマスクする。したがって、グラフ703で示される再生クロックであるQクロックの立ち上がり区間における、データエッジ検出回路111からの出力をマスクする。従って、グラフ711、712に示すように、グラフ703に示すQクロックの立ち下がり区間における、グラフ706に示すデータ信号の立ち上がりのデータエッジの検出信号が残る。

【0025】

グラフ713、714に示すように、データエッジマスク回路116は、グラフ702に示すIクロックの電圧が高電圧の場合に、データエッジ検出回路113からの出力をマスクする。したがって、グラフ703で示される再生クロックであるQクロックの立ち上がり区間における、データエッジ検出回路113からの出力をマスクする。従って、グラフ713、714に示すように、グラフ703に示すQクロックの立ち下がり区間における、グラフ706に示すデータ信号の立ち下がりのデータエッジの検出信号が残る。

【0026】

グラフ715、716に示すように、データエッジマスク回路117は、グラフ702に示すIクロックの電圧が低電圧の場合に、データエッジ検出回路112からの出力をマスクする。したがって、グラフ703で示される再生クロックであるQクロックの立ち下がり区間における、データエッジ検出回路112からの出力をマスクする。従って、グラフ715、716に示すように、グラフ703に示すQクロックの立ち上がり区間における、グラフ706に示すデータ信号の立ち上がりのデータエッジの検出信号が残る。

【0027】

グラフ717、718に示すように、データエッジマスク回路118は、グラフ702に示すIクロックの電圧が低電圧の場合に、データエッジ検出回路114からの出力をマスクする。したがって、グラフ703で示される再生クロックであるQクロックの立ち下がり区間における、データエッジ検出回路114からの出力をマスクする。従って、グラフ717、718に示すように、グラフ703に示すQクロックの立ち上がり区間における、グラフ706に示すデータ信号の立ち下がりのデータエッジの検出信号が残る。

【0028】

サンプリング回路119〜122は、それぞれグラフ711〜718の検出信号のタイミングで、グラフ703に示す再生クロックであるQクロックの電圧をサンプリングする。サンプリング回路119〜122でサンプリングされた電圧は、低域通過型フィルタ123〜126を経て、アナログ・デジタル変換回路127〜130で、それぞれ電圧値としてデジタル化される。このデジタル化された電圧値が、位相比較結果となる。電圧値が大きいほど進みまたは遅れが大きいことを意味する。また、伝送データおよび再生クロックの立ち上がりと立下りのいずれのエッジで比較しているのかで、電圧値が位相の進みを示すのか、遅れを示すのかが分かる。伝送データの立ち上がりと立下り、再生クロックの立ち上がりと立下りの4つの組み合わせからの位相比較結果となる電圧値がそれぞれ出力される。例えば、図7のAおよびDで示された領域では、信号の電圧の中央値であるVDD/2よりも小さい電圧として、再生クロックが伝送データに対して遅れていることが出力される。図7のBおよびCで示された領域では、信号の電圧の中央値であるVDD/2よりも大きい電圧として、再生クロックが伝送データに対して遅れていることが出力される。

【0029】

アナログ・デジタル変換回路127〜130からの位相比較結果となるデジタル化された電圧値は、アップ/ダウン信号生成回路131〜134とアップ/ダウン信号統合回路135とで、出力107に変換されて出力される。

【0030】

以上のように、CDR回路901では、その位相比較器902において、位相比較の結果がパルス時間幅ではなく、デジタル化された電圧値として得られるので、線形位相比較器で再生クロックの位相調整をおこなうものでありながら、チャージポンプやVCO等のアナログ回路の使用が不要であり、回路規模を小さくすることができる。すなわち、本発明では、伝送データのエッジを検出し、伝送データのエッジを検出したときの再生クロックの電圧を検出し、検出した電圧に基づいて再生クロックの位相調整を行うことで、小さい面積で線形位相比較器を用いたCDR回路を実現できる。

【0031】

また、CDR回路901では、上述のように伝送データの立ち上がりと立下り、再生クロックの立ち上がりと立下りの4通りの組み合わせからの位相比較の結果に基づいて位相調整を行っている。伝送データの品質に応じて、この4つの組み合わせのうち実際の位相比較に使用する組み合わせを選択することで伝送状況に応じた位相比較が行える。

【0032】

以下に、位相比較器902に含まれる各回路の詳細を述べる。

【0033】

データエッジ検出回路111、112は、図2に示すように、インバータ回路201とパルス生成回路202から構成される。パルス生成回路202は、図7に示すように、データ信号(DATA)が低電圧であるローレベルの場合に、出力信号R_Pにはローレベル、R_Nにはハイレベルが出力される。データ信号(DATA)がローレベルからハイレベルに遷移する際、インバータ回路201を3段経由しないパスは、直ちにローレベルからハイレベルへ状態遷移し、出力信号R_Pはハイレベルへ、R_Nはローレベルへ切り替わる。その後、インバータを3段経由したパスの状態遷移が起こり、短時間のうちに出力信号R_Pはローレベル、R_Nはハイレベルへ切り替わる。このインバータを3段経由するパスと経由しないパスの時間差を利用して、伝送データの立ち上がりエッジを検出しパルス信号を生成している。この実施例では、インバータの段数を3段にしているが、段数を変えた回路を複数用意し、制御回路136からの制御信号により回路を切り替えて段数を変更することにより、パルス信号幅およびパルス信号の電圧値を変更することが可能である。

【0034】

データエッジ検出回路113、114は、図3に示すように、インバータ回路301とパルス生成回路302から構成される。パルス生成回路302は、図7に示すように、データ信号(DATA)がハイレベルの時、出力信号F_Pにはローレベル、F_Nにはハイレベルが出力される。データ信号(DATA)がハイレベルからローレベルに遷移する際、インバータ回路301を3段経由しないパスは、直ちにハイレベルからローレベルへ状態遷移し、出力信号F_Pはハイレベル、F_Nはローレベルへ切り替わる。その後、インバータを3段経由したパスの状態遷移が起こり、短時間のうちに出力信号F_Pはローレベルへ、F_Nはハイレベルへ切り替わる。このインバータを3段経由するパスと経由しないパスの時間差を利用して、伝送データの立ち上がりエッジを検出しパルス信号を生成している。この実施例では、インバータの段数を3段にしているが、段数を変えた回路を複数用意し、制御回路136からの制御信号により回路を切り替えて段数を変更することにより、パルス信号幅およびパルス信号の電圧値を変更することが可能である。

【0035】

データエッジマスク回路115、116は、図4に示すように、インバータ回路401とマスク回路402から構成される。本実施例では、伝送データであるデータ信号(DATA)の立ち上がり/立下りと再生クロックであるQ_CLKの立ち上がり/立下りの4通りの組み合わせにおいて、それぞれ伝送データと再生クロックの位相差を独立に求める構成となっている。そのため、図7に示すように、再生クロック(Q_CLK)の立ち上がり区間、すなわちもう一方の再生クロック(I_CLK)がハイレベルの区間内に存在するデータエッジのパルス信号と、再生クロック(Q_CLK)の立下り区間、すなわちもう一方の再生クロック(I_CLK)がローレベルの区間内に存在するデータエッジのパルス信号とに分離する必要がある。データエッジマスク回路115、116は、再生クロック(Q_CLK)の立ち上がり区間、すなわちもう一方の再生クロックであるI_CLKがハイレベルの区間における伝送データエッジのパルス信号をマスクする。CDR回路901が生成する再生クロックであるI_CLKに応じて、前段のデータエッジ検出回路111、113からの出力信号をローレベルであるグランドレベルまたはハイレベルである電源レベル(VDD)へ切り替えることで、データエッジ検出回路からのパルス信号の選択的な通過を実現することができる。

【0036】

データエッジマスク回路117、118は、図5に示すように、インバータ回路501とマスク回路502から構成される。基本的な動作は、データエッジマスク回路115、116と同様であり、再生クロックであるQ_CLKの立下り区間、すなわちもう一方の再生クロックであるI_CLKがローレベルの区間における伝送データエッジのパルス信号をマスクする。

【0037】

サンプリング回路119〜122は、図6に示すように、n型MOSトランジスタとp型MOSトランジスタの組み合わせにより構成される。サンプリング回路119〜122は、伝送データエッジから生成されるパルス信号で、再生クロックであるQ_CLKの電圧値をサンプリングする機能を実現している。例えば、伝送データと再生クロック間の位相が一致している場合は、サンプリング結果として再生クロックの電圧値の中央値であるVDD/2が得られる。しかし、伝送データと再生クロック間の位相にずれが生じている場合は、位相差および再生クロックの立ち上がり・立下り時間に応じてサンプリングされる電圧値が変わってくる。図7に示すように、再生クロックに対して、データの位相がずれている場合、VDD/2から上下にずれた電圧値をサンプリングする(図中A、B、C、D)。同じ位相ずれ場合でも、伝送データの立ち上がり/立下りエッジと再生クロックの立ち上がり/立下りエッジの組み合わせ次第で、位相ずれの進み遅れの方向に対する、サンプリングされる電圧のVDD/2からの電圧の上下の変動の方向が変わってくる。この位相ずれの進み遅れの方向とVDD/2からの電圧の上下の方向は、後述するアップ/ダウン信号生成回路131〜134で対応づけられている。

【0038】

低域通過型フィルタ123〜126とアナログ・デジタル変換回路127〜130は、一般的な構成にて実現されるため、ここでは詳細な説明を省略する。

【0039】

アップ/ダウン信号生成回路131〜134は、デジタル化されたサンプリング電圧値が予め設定された閾値を越えているか否かを、組み合わせ論理回路にて判断する構成であり、再生クロックの位相を制御するための位相制御信号、すなわち位相遅れ信号(ダウン信号)と位相進み信号(アップ信号)を生成する。閾値を複数用意することで、位相遅れ信号(ダウン信号)と位相進み信号(アップ信号)の重みを変更することが可能である。また、サンプリング回路119〜122にて、同じ位相ずれに対してサンプリングされる電圧値のVDD/2を基準とした上下の方向は、このアップ/ダウン信号生成回路131〜134の出力を適宜反転させることで対応づけられている。例えば、再生クロックに対して伝送データの位相が進んでいる図7では、位相進み信号(アップ信号)が必要となる。アップ/ダウン信号生成回路131〜134のすべてでVDD/2よりも小さい電圧に対して位相進み信号(アップ信号)を割り当てた場合、図7中BおよびCにて位相進み信号(アップ信号)とは逆の位相遅れ信号(ダウン信号)が出てしまう。そこで、BおよびCの場合、すなわち再生クロックの立下りに対して処理を行うアップ/ダウン信号生成回路131、132では、アップ信号をダウン信号へ、ダウン信号をアップ信号へ反転によってスイッチすることで、適切な位相制御信号が算出されるようにしている。

【0040】

アップ/ダウン信号統合回路135は、多数決回路にて構成され、複数のアップ/ダウン信号生成回路131〜134が生成する位相制御情報を多数決回路の多数決処理によって統合する。多数決回路に、アップ/ダウン信号生成回路131〜134と同様に、複数の閾値を設定することで、位相制御信号に対して重みを加えた信号を用意することが可能となる。位相制御信号に複数の重みを持たせることで、後段の再生クロックを制御する回路にて、通常の1相シフトの他に複数相シフトも実現できる。その結果としてCDR回路の追従帯域を上げることが可能となる。

【0041】

制御回路136は、データエッジ検出回路111〜114と、低域通過型フィルタ123〜126と、アナログ・デジタル変換回路127〜130と、アップ/ダウン信号生成回路131〜134と、アップ/ダウン信号統合回路135と、可変容量139〜142の設定を独立に制御することで、伝送データと再生クロック間の位相差検出感度を変更することができる。本実施例では、伝送データの立ち上がり/立下りエッジと再生クロックの立ち上がり/立下りエッジの組み合わせにより4つの位相検出パスを用意している。この4つの位相検出パスそれぞれに対して、特性調整や機能の有効/無効を制御回路136から独立に制御を行うことで、各エッジの組み合わせ別に位相追従の感度調整が可能となり、デューティ変動やシンボル間干渉等で信号品質が劣化した伝送信号に対して適切な位相追従特性を得ることが可能となる。

【0042】

制御回路136は、LSIピンおよび本願回路の上位論理回路である内部論理回路138から制御できる。LSIピン/内部論理回路138の切り替えは、セレクタ回路137にて行われる。

【0043】

サンプリング回路の入力側に接続されている可変容量139〜142は、再生クロックの立ち上がり時間/立下り時間を制御するために使用される。本願発明は、伝送データエッジから生成されるパルス信号で、再生クロックの電圧値をサンプリングするため、再生クロックの立ち上がり/立下り時間が位相追従特性に大きく依存する。例えば、再生クロックの立ち上がり時間/立下り時間が小さい場合、再生クロックエッジの電圧の中央値VDD/2近傍の線形領域が狭くなるため、短時間での引き込みができる反面、引き込んだ後の位相追従精度が下がる。逆に再生クロックの立ち上がり時間/立下り時間が大きい場合、再生クロックエッジの電圧の中央値VDD/2近傍の線形領域が広くなるため、微小な電圧差を感知でき位相追従精度が向上する反面、引き込み速度が遅くなる。この可変容量139〜142の容量を制御回路136から制御することで、位相追従特性の最適化を行うことができる。

【0044】

本実施例では、伝送データとCDR回路が生成する再生クロックの位相差が、パルス時間幅ではなくデジタル変換された電圧値として得られるため、位相制御信号を処理する後段回路をデジタル回路で構成できる。そのため、図8の線形位相比較器を使用したCDR回路と比較して回路面積の低減を図ることができる。

【0045】

本発明は上記実施例に限定されるものではなく、その要旨を逸脱しない範囲で変更が可能である。

【符号の説明】

【0046】

108〜110…差動単相変換回路、111〜114…データエッジ検出回路、115〜118…データエッジマスク回路、119〜122…サンプリング回路、123〜126…低域通過型フィルタ、127〜130…アナログ・デジタル変換回路、131〜134…アップ/ダウン信号生成回路、135…アップ/ダウン信号統合回路、136…制御回路、137…セレクタ回路、138…内部論理回路、139〜142…可変容量、201…インバータ回路、202…パルス生成回路、301…インバータ回路、302…パルス生成回路、401…インバータ回路、402…マスク回路、501…インバータ回路、502…マスク回路、801…線形位相比較器、802〜803…フリップフロップ回路、804〜806…AND回路、807…制御論理回路、901…CDR回路、902…位相比較器、903…平均化回路、904…ポインタ回路、905…インタポレータ回路、906…PLL回路。

【技術分野】

【0001】

本発明はCDR回路に関し、特に、再生クロックの位相調整に利用して有効な技術に関するものである。

【背景技術】

【0002】

データの転送においては、クロックに同期させたデータを伝送路により送信し、受信側で受信データからクロックを抽出し、受信データを復元する方法が一般的に用いられている。受信データからクロックを抽出する機能を実現する回路はCDR(Clock and Data Recovery)回路と呼ばれる。CDR回路で、伝送データと伝送データから生成したクロックの位相差を判定する回路は、位相比較器と呼ばれ、非線形位相比較器と線形位相比較器に大別される(特許文献1)。非線形位相比較器が用いられる場合には、再生クロックのエッジの前後に伝送データのエッジが存在しているか否かから再生クロックの位相を制御するための信号が生成される。一方、線形位相比較器が用いられる場合には、伝送データと再生クロックの位相差は厳密に算出され、非線形位相比較器を用いた場合と比べ、再生クロックの高い位相調整精度を実現できる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2002−84187号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

近年、データ転送、特にシリアル伝送の高速化に伴い、CDR回路のクロック生成の高性能化が求められている。これに対して、非線形位相比較器を用いたCDR回路では、エッジの存在と不存在の情報のみから位相差を判定するため、再生クロックの位相調整精度を向上させることが難しい。

【0005】

そこで、本願発明者等は本願に先立って、図8に示す従来の線形位相比較器801について検討を行った。線形位相比較器801は、フリップフロップ回路802、803と、AND回路804、805、806と、制御論理(CL)回路807とを具備し、伝送データ808とCDR回路の再生クロック809で高電圧であるVDDレベル(ハイレベル)をラッチすることで、再生クロックの位相制御信号、すなわちアップ信号(UP)810およびダウン信号(DOWN)811とを生成する。

【0006】

線形位相比較器801では、伝送データ808と再生クロック809のうち位相の早い方で先にVDDレベル(ハイレベル)がラッチされる。線形位相比較器801は、伝送データ808の位相が早い場合には、ラッチした信号を位相進み信号としてのアップ信号810として、再生クロックの位相が早い場合には、ラッチした信号を位相遅れ信号としてのダウン信号811として出力する。伝送データ808と再生クロック809がともにハイレベルになった場合、フリップフロップ802および803にリセットをかけることで、伝送データ808と再生クロック809の位相差分だけの時間幅の信号が生成できる。また、伝送データ808の切り替わりがない場合、適切な位相制御信号が得られないため、制御論理回路807にて位相制御信号を制御する。

【0007】

この線形位相比較器801を用いるCDR回路は、伝送データ808と再生クロック809の位相差をハイレベルの時間幅に変換するため、後段の回路はチャージポンプや電圧制御発振器(VCO)等のアナログ回路の使用が前提となり、回路面積の増大が避けられない。ゆえに、線形位相比較器801を使用してCDR回路を構成した場合、回路面積の面で不利であることを本願発明者等は見出した。

【0008】

本願発明は、上述の課題を鑑みてなされたものであり、線形位相比較器を用いた、回路面積を抑えたCDR回路を提供することにある。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば、以下の通りである。本発明のCDR回路では、伝送データのエッジを検出し、伝送データのエッジを検出したときの再生クロックの電圧を検出し、検出した電圧に基づいて再生クロックの位相調整を行う。

【発明の効果】

【0010】

上記手段により、従来の線形位相比較器を用いたCDR回路と異なり、チャージポンプやVCO等のアナログ回路を不要とし、線形位相比較器で伝送データに対する再生クロックの位相調整をするCDR回路の回路面積の低減が図れる。

【図面の簡単な説明】

【0011】

【図1】本発明の実施例における位相比較回路のブロック図である。

【図2】本発明の実施例にかかる立ち上がりデータエッジ用データエッジ検出回路の構成を示す回路図である。

【図3】本発明の実施例にかかる立下りデータエッジ用データエッジ検出回路の構成を示す回路図である。

【図4】本発明の実施例にかかる再生クロック立ち上がり区間用データエッジマスク回路の構成を示す回路図である。

【図5】本発明の実施例にかかる再生クロック立下り区間用データエッジマスク回路の構成を示す回路図である。

【図6】本発明の実施例にかかるサンプリング回路の構成を示す回路図である。

【図7】本発明の実施例におけるデータエッジパルス生成過程の例を示した図である。

【図8】本発明にあたり検討を行った線形位相比較器の構成を示す回路図である。

【図9】本発明の実施例にかかるCDR回路を示すブロック図である。

【発明を実施するための形態】

【0012】

以下、本発明を実施例に基づいて詳細に説明する。

【実施例1】

【0013】

図9に本発明の実施例としてCDR回路901を示す。CDR回路901は、位相比較器902と平均化回路903とポインタ回路904とインタポレータ回路905とPLL(Phase Locked Loop)回路906とを備える。

【0014】

位相比較器902は、伝送データ907、908と再生クロック910、911との間の位相差を検出し、再生クロック910、911の位相を制御するための位相制御信号であるアップ/ダウン信号912を生成する。伝送データ907、908の位相に対して、再生クロック910、911の位相が遅れている場合に位相進み信号であるアップ信号を、位相が進んでいる場合に位相遅れ信号であるダウン信号を生成する。

【0015】

平均化回路903は、位相制御信号であるアップ/ダウン信号912を平均化し、ポインタ回路904を制御するための位相制御信号であるアップ/ダウン信号913を生成する。ポインタ回路904は入力される位相制御信号であるアップ/ダウン信号913により、再生クロックの位相を調整し、調整した位相を保持する。インタポレータ回路905は、PLL回路906からクロック信号としてI_CLK914およびQ_CLK915が入力され、ポインタ回路904により指定された位相の再生クロック910、911を生成する。

【0016】

位相比較器902の実施例を図1に示す。位相比較器902は、伝送データのP極(DATA_P)101と、伝送データのN極(DATA_N)102と、QクロックのP極(Q−CLK_P)103と、QクロックのN極(Q−CLK_N)104と、IクロックのP極(I−CLK_P)105と、IクロックのN極(I−CLK_N)106とを入力とし、アップ/ダウン信号107を出力とする。

【0017】

位相比較器902は、差動伝送データを単相CMOSレベルに変換する差動単相変換回路(LVC)108〜110と、単相CMOSレベルの伝送データの立ち上がりエッジを検出しパルス信号を生成するデータエッジ検出回路(DED1)111、112と、単相CMOSレベルの伝送データの立下りエッジを検出しパルス信号を生成するデータエッジ検出回路(DED2)113、114と、データエッジマスク回路(DEM1)115、116と、データエッジマスク回路(DEM2)117、118と、再生クロックをパルス信号でサンプリングするサンプリング回路(SC)119〜122と、サンプリングされた電圧値を平滑化する低域通過型フィルタ(LPF)123〜126と、アナログ電圧値をデジタル値へと変換するアナログ・デジタル変換回路(ADC)127〜130と、再生クロックの位相を制御するための位相制御信号を生成するアップ/ダウン信号生成回路(UD Gen.)131〜134と、アップ/ダウン信号生成回路131〜134の出力を多数決処理により統合するアップ/ダウン信号統合回路(IB)135と、各回路ブロックの特性を制御する制御回路136と、制御回路136をLSI外部/内部論理回路のどちらで制御するかを決定するセレクタ回路137と、本願発明回路の上位論理回路である内部論理回路138と、CDR回路901の再生クロックの立ち上がり時間および立下り時間調整用の可変容量139〜142とを備える。

【0018】

差動単相変換回路108には、伝送データ101および伝送データ102が入力される。差動単相変換回路108からの出力は、CMOSレベルのデータ信号(DATA)としてデータエッジ検出回路111〜114に入力される。差動単相変換回路109には、Qクロック103およびQクロック104が入力される。差動単相変換回路109の出力は、CMOSレベルのQクロック(Q−CLK)として、それぞれ可変容量139〜142に接続されて各サンプリング回路119〜122に入力される。差動単相変換回路110には、Iクロック105およびIクロック106が入力される。差動単相変換回路110の出力は、Q−CLKと90度位相が異なるCMOSレベルのIクロック(I−CLK)として、各データエッジマスク回路115〜118に入力される。

【0019】

図1に示すように、データエッジ検出回路111〜114の出力は、それぞれデータエッジマスク回路115〜118に入力される。データエッジマスク回路115〜118の出力は、それぞれサンプリング回路119〜122に入力される。サンプリング回路119〜122の出力は、それぞれ低域通過型フィルタ123〜126に入力される。低域通過型フィルタ123〜126の出力は、それぞれアナログ・デジタル変換回路127〜130に入力される。アナログ・デジタル変換回路127〜130の出力は、それぞれアップ/ダウン信号生成回路131〜134に入力される。アップ/ダウン信号生成回路131〜134の出力は、アップ/ダウン信号統合回路135に入力される。アップ/ダウン信号統合回路135は、アップ/ダウン信号生成回路131〜134のアップ/ダウン信号出力を多数決処理し、アップ/ダウン信号107を結果として出力する。

【0020】

以下、図7のグラフ701を用いて、位相比較器902の動作を説明する。グラフ702は、差動単相変換回路110の出力のCMOSレベルのIクロック(I−CLK)の電圧の時間変化を示す。グラフ703は、差動単相変換回路109の出力のCMOSレベルのQクロック(Q−CLK)の電圧の時間変化を示す。グラフ704は伝送データのN極(DATA_N)102の電圧の時間変化を示す。グラフ705は伝送データのP極(DATA_P)101の電圧の時間変化を示す。グラフ706は、差動単相変換回路108からの出力のCMOSレベルのデータ信号(DATA)の電圧の時間変化を示す。CDR回路901は、図示していないラッチ回路で、伝送データであるデータ信号(DATA)を再生クロックのIクロック(I−CLK)でラッチして、データを復元する。

【0021】

グラフ707、708は、データエッジ検出回路111およびデータエッジ検出回路112の出力電圧(R_N、R_P)の時間変化を示す。グラフ709、710は、データエッジ検出回路113およびデータエッジ検出回路114の出力電圧(F_N、F_P)の時間変化を示す。

【0022】

グラフ711、712は、データエッジマスク回路115からの出力電圧(O_N1、O_P1)の時間変化を示す。グラフ713、714は、データエッジマスク回路116からの出力電圧(O_N2、O_P2)の時間変化を示す。グラフ715、716は、データエッジマスク回路117からの出力電圧(O_N3、O_P3)の時間変化を示す。グラフ717、718は、データエッジマスク回路118からの出力電圧(O_N4、O_P4)の時間変化を示す。

【0023】

グラフ707、708に示すように、データエッジ検出回路111およびデータエッジ検出回路112は、グラフ706で示す差動単相変換回路108からの出力のCMOSレベルのデータ信号の立ち上がりエッジを検出する。グラフ709、710に示すように、データエッジ検出回路113およびデータエッジ検出回路114は、グラフ706で示す差動単相変換回路108からの出力のCMOSレベルのデータ信号の立ち下がりエッジを検出する。

【0024】

グラフ711、712に示すように、データエッジマスク回路115は、グラフ702に示すIクロックの電圧が高電圧の場合に、データエッジ検出回路111からの出力をマスクする。したがって、グラフ703で示される再生クロックであるQクロックの立ち上がり区間における、データエッジ検出回路111からの出力をマスクする。従って、グラフ711、712に示すように、グラフ703に示すQクロックの立ち下がり区間における、グラフ706に示すデータ信号の立ち上がりのデータエッジの検出信号が残る。

【0025】

グラフ713、714に示すように、データエッジマスク回路116は、グラフ702に示すIクロックの電圧が高電圧の場合に、データエッジ検出回路113からの出力をマスクする。したがって、グラフ703で示される再生クロックであるQクロックの立ち上がり区間における、データエッジ検出回路113からの出力をマスクする。従って、グラフ713、714に示すように、グラフ703に示すQクロックの立ち下がり区間における、グラフ706に示すデータ信号の立ち下がりのデータエッジの検出信号が残る。

【0026】

グラフ715、716に示すように、データエッジマスク回路117は、グラフ702に示すIクロックの電圧が低電圧の場合に、データエッジ検出回路112からの出力をマスクする。したがって、グラフ703で示される再生クロックであるQクロックの立ち下がり区間における、データエッジ検出回路112からの出力をマスクする。従って、グラフ715、716に示すように、グラフ703に示すQクロックの立ち上がり区間における、グラフ706に示すデータ信号の立ち上がりのデータエッジの検出信号が残る。

【0027】

グラフ717、718に示すように、データエッジマスク回路118は、グラフ702に示すIクロックの電圧が低電圧の場合に、データエッジ検出回路114からの出力をマスクする。したがって、グラフ703で示される再生クロックであるQクロックの立ち下がり区間における、データエッジ検出回路114からの出力をマスクする。従って、グラフ717、718に示すように、グラフ703に示すQクロックの立ち上がり区間における、グラフ706に示すデータ信号の立ち下がりのデータエッジの検出信号が残る。

【0028】

サンプリング回路119〜122は、それぞれグラフ711〜718の検出信号のタイミングで、グラフ703に示す再生クロックであるQクロックの電圧をサンプリングする。サンプリング回路119〜122でサンプリングされた電圧は、低域通過型フィルタ123〜126を経て、アナログ・デジタル変換回路127〜130で、それぞれ電圧値としてデジタル化される。このデジタル化された電圧値が、位相比較結果となる。電圧値が大きいほど進みまたは遅れが大きいことを意味する。また、伝送データおよび再生クロックの立ち上がりと立下りのいずれのエッジで比較しているのかで、電圧値が位相の進みを示すのか、遅れを示すのかが分かる。伝送データの立ち上がりと立下り、再生クロックの立ち上がりと立下りの4つの組み合わせからの位相比較結果となる電圧値がそれぞれ出力される。例えば、図7のAおよびDで示された領域では、信号の電圧の中央値であるVDD/2よりも小さい電圧として、再生クロックが伝送データに対して遅れていることが出力される。図7のBおよびCで示された領域では、信号の電圧の中央値であるVDD/2よりも大きい電圧として、再生クロックが伝送データに対して遅れていることが出力される。

【0029】

アナログ・デジタル変換回路127〜130からの位相比較結果となるデジタル化された電圧値は、アップ/ダウン信号生成回路131〜134とアップ/ダウン信号統合回路135とで、出力107に変換されて出力される。

【0030】

以上のように、CDR回路901では、その位相比較器902において、位相比較の結果がパルス時間幅ではなく、デジタル化された電圧値として得られるので、線形位相比較器で再生クロックの位相調整をおこなうものでありながら、チャージポンプやVCO等のアナログ回路の使用が不要であり、回路規模を小さくすることができる。すなわち、本発明では、伝送データのエッジを検出し、伝送データのエッジを検出したときの再生クロックの電圧を検出し、検出した電圧に基づいて再生クロックの位相調整を行うことで、小さい面積で線形位相比較器を用いたCDR回路を実現できる。

【0031】

また、CDR回路901では、上述のように伝送データの立ち上がりと立下り、再生クロックの立ち上がりと立下りの4通りの組み合わせからの位相比較の結果に基づいて位相調整を行っている。伝送データの品質に応じて、この4つの組み合わせのうち実際の位相比較に使用する組み合わせを選択することで伝送状況に応じた位相比較が行える。

【0032】

以下に、位相比較器902に含まれる各回路の詳細を述べる。

【0033】

データエッジ検出回路111、112は、図2に示すように、インバータ回路201とパルス生成回路202から構成される。パルス生成回路202は、図7に示すように、データ信号(DATA)が低電圧であるローレベルの場合に、出力信号R_Pにはローレベル、R_Nにはハイレベルが出力される。データ信号(DATA)がローレベルからハイレベルに遷移する際、インバータ回路201を3段経由しないパスは、直ちにローレベルからハイレベルへ状態遷移し、出力信号R_Pはハイレベルへ、R_Nはローレベルへ切り替わる。その後、インバータを3段経由したパスの状態遷移が起こり、短時間のうちに出力信号R_Pはローレベル、R_Nはハイレベルへ切り替わる。このインバータを3段経由するパスと経由しないパスの時間差を利用して、伝送データの立ち上がりエッジを検出しパルス信号を生成している。この実施例では、インバータの段数を3段にしているが、段数を変えた回路を複数用意し、制御回路136からの制御信号により回路を切り替えて段数を変更することにより、パルス信号幅およびパルス信号の電圧値を変更することが可能である。

【0034】

データエッジ検出回路113、114は、図3に示すように、インバータ回路301とパルス生成回路302から構成される。パルス生成回路302は、図7に示すように、データ信号(DATA)がハイレベルの時、出力信号F_Pにはローレベル、F_Nにはハイレベルが出力される。データ信号(DATA)がハイレベルからローレベルに遷移する際、インバータ回路301を3段経由しないパスは、直ちにハイレベルからローレベルへ状態遷移し、出力信号F_Pはハイレベル、F_Nはローレベルへ切り替わる。その後、インバータを3段経由したパスの状態遷移が起こり、短時間のうちに出力信号F_Pはローレベルへ、F_Nはハイレベルへ切り替わる。このインバータを3段経由するパスと経由しないパスの時間差を利用して、伝送データの立ち上がりエッジを検出しパルス信号を生成している。この実施例では、インバータの段数を3段にしているが、段数を変えた回路を複数用意し、制御回路136からの制御信号により回路を切り替えて段数を変更することにより、パルス信号幅およびパルス信号の電圧値を変更することが可能である。

【0035】

データエッジマスク回路115、116は、図4に示すように、インバータ回路401とマスク回路402から構成される。本実施例では、伝送データであるデータ信号(DATA)の立ち上がり/立下りと再生クロックであるQ_CLKの立ち上がり/立下りの4通りの組み合わせにおいて、それぞれ伝送データと再生クロックの位相差を独立に求める構成となっている。そのため、図7に示すように、再生クロック(Q_CLK)の立ち上がり区間、すなわちもう一方の再生クロック(I_CLK)がハイレベルの区間内に存在するデータエッジのパルス信号と、再生クロック(Q_CLK)の立下り区間、すなわちもう一方の再生クロック(I_CLK)がローレベルの区間内に存在するデータエッジのパルス信号とに分離する必要がある。データエッジマスク回路115、116は、再生クロック(Q_CLK)の立ち上がり区間、すなわちもう一方の再生クロックであるI_CLKがハイレベルの区間における伝送データエッジのパルス信号をマスクする。CDR回路901が生成する再生クロックであるI_CLKに応じて、前段のデータエッジ検出回路111、113からの出力信号をローレベルであるグランドレベルまたはハイレベルである電源レベル(VDD)へ切り替えることで、データエッジ検出回路からのパルス信号の選択的な通過を実現することができる。

【0036】

データエッジマスク回路117、118は、図5に示すように、インバータ回路501とマスク回路502から構成される。基本的な動作は、データエッジマスク回路115、116と同様であり、再生クロックであるQ_CLKの立下り区間、すなわちもう一方の再生クロックであるI_CLKがローレベルの区間における伝送データエッジのパルス信号をマスクする。

【0037】

サンプリング回路119〜122は、図6に示すように、n型MOSトランジスタとp型MOSトランジスタの組み合わせにより構成される。サンプリング回路119〜122は、伝送データエッジから生成されるパルス信号で、再生クロックであるQ_CLKの電圧値をサンプリングする機能を実現している。例えば、伝送データと再生クロック間の位相が一致している場合は、サンプリング結果として再生クロックの電圧値の中央値であるVDD/2が得られる。しかし、伝送データと再生クロック間の位相にずれが生じている場合は、位相差および再生クロックの立ち上がり・立下り時間に応じてサンプリングされる電圧値が変わってくる。図7に示すように、再生クロックに対して、データの位相がずれている場合、VDD/2から上下にずれた電圧値をサンプリングする(図中A、B、C、D)。同じ位相ずれ場合でも、伝送データの立ち上がり/立下りエッジと再生クロックの立ち上がり/立下りエッジの組み合わせ次第で、位相ずれの進み遅れの方向に対する、サンプリングされる電圧のVDD/2からの電圧の上下の変動の方向が変わってくる。この位相ずれの進み遅れの方向とVDD/2からの電圧の上下の方向は、後述するアップ/ダウン信号生成回路131〜134で対応づけられている。

【0038】

低域通過型フィルタ123〜126とアナログ・デジタル変換回路127〜130は、一般的な構成にて実現されるため、ここでは詳細な説明を省略する。

【0039】

アップ/ダウン信号生成回路131〜134は、デジタル化されたサンプリング電圧値が予め設定された閾値を越えているか否かを、組み合わせ論理回路にて判断する構成であり、再生クロックの位相を制御するための位相制御信号、すなわち位相遅れ信号(ダウン信号)と位相進み信号(アップ信号)を生成する。閾値を複数用意することで、位相遅れ信号(ダウン信号)と位相進み信号(アップ信号)の重みを変更することが可能である。また、サンプリング回路119〜122にて、同じ位相ずれに対してサンプリングされる電圧値のVDD/2を基準とした上下の方向は、このアップ/ダウン信号生成回路131〜134の出力を適宜反転させることで対応づけられている。例えば、再生クロックに対して伝送データの位相が進んでいる図7では、位相進み信号(アップ信号)が必要となる。アップ/ダウン信号生成回路131〜134のすべてでVDD/2よりも小さい電圧に対して位相進み信号(アップ信号)を割り当てた場合、図7中BおよびCにて位相進み信号(アップ信号)とは逆の位相遅れ信号(ダウン信号)が出てしまう。そこで、BおよびCの場合、すなわち再生クロックの立下りに対して処理を行うアップ/ダウン信号生成回路131、132では、アップ信号をダウン信号へ、ダウン信号をアップ信号へ反転によってスイッチすることで、適切な位相制御信号が算出されるようにしている。

【0040】

アップ/ダウン信号統合回路135は、多数決回路にて構成され、複数のアップ/ダウン信号生成回路131〜134が生成する位相制御情報を多数決回路の多数決処理によって統合する。多数決回路に、アップ/ダウン信号生成回路131〜134と同様に、複数の閾値を設定することで、位相制御信号に対して重みを加えた信号を用意することが可能となる。位相制御信号に複数の重みを持たせることで、後段の再生クロックを制御する回路にて、通常の1相シフトの他に複数相シフトも実現できる。その結果としてCDR回路の追従帯域を上げることが可能となる。

【0041】

制御回路136は、データエッジ検出回路111〜114と、低域通過型フィルタ123〜126と、アナログ・デジタル変換回路127〜130と、アップ/ダウン信号生成回路131〜134と、アップ/ダウン信号統合回路135と、可変容量139〜142の設定を独立に制御することで、伝送データと再生クロック間の位相差検出感度を変更することができる。本実施例では、伝送データの立ち上がり/立下りエッジと再生クロックの立ち上がり/立下りエッジの組み合わせにより4つの位相検出パスを用意している。この4つの位相検出パスそれぞれに対して、特性調整や機能の有効/無効を制御回路136から独立に制御を行うことで、各エッジの組み合わせ別に位相追従の感度調整が可能となり、デューティ変動やシンボル間干渉等で信号品質が劣化した伝送信号に対して適切な位相追従特性を得ることが可能となる。

【0042】

制御回路136は、LSIピンおよび本願回路の上位論理回路である内部論理回路138から制御できる。LSIピン/内部論理回路138の切り替えは、セレクタ回路137にて行われる。

【0043】

サンプリング回路の入力側に接続されている可変容量139〜142は、再生クロックの立ち上がり時間/立下り時間を制御するために使用される。本願発明は、伝送データエッジから生成されるパルス信号で、再生クロックの電圧値をサンプリングするため、再生クロックの立ち上がり/立下り時間が位相追従特性に大きく依存する。例えば、再生クロックの立ち上がり時間/立下り時間が小さい場合、再生クロックエッジの電圧の中央値VDD/2近傍の線形領域が狭くなるため、短時間での引き込みができる反面、引き込んだ後の位相追従精度が下がる。逆に再生クロックの立ち上がり時間/立下り時間が大きい場合、再生クロックエッジの電圧の中央値VDD/2近傍の線形領域が広くなるため、微小な電圧差を感知でき位相追従精度が向上する反面、引き込み速度が遅くなる。この可変容量139〜142の容量を制御回路136から制御することで、位相追従特性の最適化を行うことができる。

【0044】

本実施例では、伝送データとCDR回路が生成する再生クロックの位相差が、パルス時間幅ではなくデジタル変換された電圧値として得られるため、位相制御信号を処理する後段回路をデジタル回路で構成できる。そのため、図8の線形位相比較器を使用したCDR回路と比較して回路面積の低減を図ることができる。

【0045】

本発明は上記実施例に限定されるものではなく、その要旨を逸脱しない範囲で変更が可能である。

【符号の説明】

【0046】

108〜110…差動単相変換回路、111〜114…データエッジ検出回路、115〜118…データエッジマスク回路、119〜122…サンプリング回路、123〜126…低域通過型フィルタ、127〜130…アナログ・デジタル変換回路、131〜134…アップ/ダウン信号生成回路、135…アップ/ダウン信号統合回路、136…制御回路、137…セレクタ回路、138…内部論理回路、139〜142…可変容量、201…インバータ回路、202…パルス生成回路、301…インバータ回路、302…パルス生成回路、401…インバータ回路、402…マスク回路、501…インバータ回路、502…マスク回路、801…線形位相比較器、802〜803…フリップフロップ回路、804〜806…AND回路、807…制御論理回路、901…CDR回路、902…位相比較器、903…平均化回路、904…ポインタ回路、905…インタポレータ回路、906…PLL回路。

【特許請求の範囲】

【請求項1】

伝送データのエッジを検出するデータエッジ検出回路と、

前記データエッジ検出回路の検出結果に応じて、再生クロックの電圧を検出するサンプリング回路とを有し、

前記サンプリング回路の前記再生クロックの電圧の検出結果に応じて、前記再生クロックの位相を調整することを特徴とするCDR回路。

【請求項2】

請求項1に記載のCDR回路において、

前記再生クロックの位相を調整する際に、

前記サンプリング回路の検出結果の前記再生クロックの電圧の中央値からのずれに応じて、前記再生クロックの位相を調整することを特徴とするCDR回路。

【請求項3】

請求項1に記載のCDR回路において、

前記調整された位相に基づいて前記再生クロックを生成するインタポレータ回路を有することを特徴とするCDR回路。

【請求項4】

請求項1に記載のCDR回路において、

前記サンプリング回路への前記再生クロックの入力には可変容量が設けられていることを特徴とするCDR回路。

【請求項5】

請求項1に記載のCDR回路において、

前記サンプリング回路の検出結果をアナログ−デジタル変換するアナログ−デジタル変換回路を有し、

前記再生クロックの位相を調整する際に、

前記アナログ−デジタル変換器の出力に基づいて、前記再生クロックの位相を調整することを特徴とするCDR回路。

【請求項6】

伝送データに対して位相調整された再生クロックで伝送データの取り込みを行うCDR回路であって、

前記伝送データのエッジを検出し、

前記伝送データのエッジを検出したときの前記再生クロックの電圧を検出し、検出した電圧に基づいて再生クロックの位相調整を行うCDR回路。

【請求項7】

伝送データの立ち上がりエッジを検出する第1のデータエッジ検出回路と、

伝送データの立ち下がりエッジを検出する第2のデータエッジ検出回路と、

前記第1のデータエッジ検出回路の検出結果に応じて、再生クロックの電圧を検出する第1のサンプリング回路と、

前記第2のデータエッジ検出回路の検出結果に応じて、前記再生クロックの電圧を検出する第2のサンプリング回路とを有し、

前記第1および第2のサンプリング回路の検出結果に応じて、前記再生クロックの位相を調整することを特徴とするCDR回路。

【請求項1】

伝送データのエッジを検出するデータエッジ検出回路と、

前記データエッジ検出回路の検出結果に応じて、再生クロックの電圧を検出するサンプリング回路とを有し、

前記サンプリング回路の前記再生クロックの電圧の検出結果に応じて、前記再生クロックの位相を調整することを特徴とするCDR回路。

【請求項2】

請求項1に記載のCDR回路において、

前記再生クロックの位相を調整する際に、

前記サンプリング回路の検出結果の前記再生クロックの電圧の中央値からのずれに応じて、前記再生クロックの位相を調整することを特徴とするCDR回路。

【請求項3】

請求項1に記載のCDR回路において、

前記調整された位相に基づいて前記再生クロックを生成するインタポレータ回路を有することを特徴とするCDR回路。

【請求項4】

請求項1に記載のCDR回路において、

前記サンプリング回路への前記再生クロックの入力には可変容量が設けられていることを特徴とするCDR回路。

【請求項5】

請求項1に記載のCDR回路において、

前記サンプリング回路の検出結果をアナログ−デジタル変換するアナログ−デジタル変換回路を有し、

前記再生クロックの位相を調整する際に、

前記アナログ−デジタル変換器の出力に基づいて、前記再生クロックの位相を調整することを特徴とするCDR回路。

【請求項6】

伝送データに対して位相調整された再生クロックで伝送データの取り込みを行うCDR回路であって、

前記伝送データのエッジを検出し、

前記伝送データのエッジを検出したときの前記再生クロックの電圧を検出し、検出した電圧に基づいて再生クロックの位相調整を行うCDR回路。

【請求項7】

伝送データの立ち上がりエッジを検出する第1のデータエッジ検出回路と、

伝送データの立ち下がりエッジを検出する第2のデータエッジ検出回路と、

前記第1のデータエッジ検出回路の検出結果に応じて、再生クロックの電圧を検出する第1のサンプリング回路と、

前記第2のデータエッジ検出回路の検出結果に応じて、前記再生クロックの電圧を検出する第2のサンプリング回路とを有し、

前記第1および第2のサンプリング回路の検出結果に応じて、前記再生クロックの位相を調整することを特徴とするCDR回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2012−253529(P2012−253529A)

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願番号】特願2011−123915(P2011−123915)

【出願日】平成23年6月2日(2011.6.2)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願日】平成23年6月2日(2011.6.2)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

[ Back to top ]