CMISトランジスタの製造方法

【課題】本発明は、PMISトランジスタ側とNMISトランジスタ側とでシリサイド層の組成のバラツキを防止でき、またトランジスタのゲート形状の不安定化を防止できる、CMISトランジスタの製造方法を提供する。

【解決手段】ゲート絶縁膜103とN−metal104と多結晶シリコン106とが当該順に積層した第一のゲート構造G1を形成する。ゲート絶縁膜103と多結晶シリコン106とが当該順に積層した第二のゲート構造G2を形成する。第一、二のゲート構造G1,G2をマスクした状態で、各ゲート構造G1,G2の両脇における半導体基板101上を、シリサイド化させる。そして、第一、二のゲート構造G1,G2を構成する多結晶シリコン106を、シリサイド化させる。

【解決手段】ゲート絶縁膜103とN−metal104と多結晶シリコン106とが当該順に積層した第一のゲート構造G1を形成する。ゲート絶縁膜103と多結晶シリコン106とが当該順に積層した第二のゲート構造G2を形成する。第一、二のゲート構造G1,G2をマスクした状態で、各ゲート構造G1,G2の両脇における半導体基板101上を、シリサイド化させる。そして、第一、二のゲート構造G1,G2を構成する多結晶シリコン106を、シリサイド化させる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、半導体基板1にPMISトランジスタとNMISトランジスタとが形成されたCMISトランジスタの製造方法に係る発明である。

【背景技術】

【0002】

MISトランジスタのゲート電極に多結晶シリコンを用いる場合には、ゲート空乏化現象により、実効的なゲート絶縁膜厚を増加させる。当該実効的なゲート絶縁膜の増加は、トランジスタの性能向上を妨げる。上記ゲート空乏化を抑えてMISトランジスタの性能向上を図るには、ゲート電極材料として、多結晶シリコンの代わりに、金属やシリサイド材料を用いる。特に、ゲート多結晶シリコンを全てシリサイド化するフルシリサイド(FUSI:Fully Silicide)ゲート構造が有効である。当該FUSI化ゲート構造は、従来のトランジスタ作製フローとの整合性が良く、上記ゲート空乏化抑制に対しても効果的である。

【0003】

FUSIゲート構造を有するトランジスタにおいて、ゲート絶縁膜として高誘電率(high−k)絶縁膜(たとえばHfSiONなど)を用いる場合には、シリサイドの組成を変えて閾値電圧Vthを制御する手法が提唱されている(たとえば、非特許文献1)。

【0004】

シリサイド金属材料としてニッケルを用いたとする。この場合、NiSi(ニッケルモノシリサイド)よりもニッケル含有率が高いNi3Si(トリニッケルシリサイド)から成るFUSIゲートの実効仕事関数は、NiSiから成るFUSIゲートの実効仕事関数と比べて約0.35eV程度高い。上記非特許文献1では、前記シリサイド組成に応じて実行仕事関数が変化する現象を利用している。具体的に、NMISトランジスタには、NiSiをFUSIゲート材料として用いる。また、PMISトランジスタには、Ni3Si等のNi含有率の高いニッケルシリサイドをFUSIゲート材料として用いる。これにより、当該非特許文献1では、低閾値電圧Vthデバイスを実現することができると提唱している。

【0005】

上記シリサイド相制御したFUSIゲート電極を形成する方法としては、たとえば次のような製造方法が挙げられる。つまり、PMISトランジスタ側およびNMISトランジスタ側の両ゲート構造において、同じ膜厚である多結晶シリコン膜を形成する。その後、たとえばPMISトランジスタ側の多結晶シリコン膜の膜厚を削減(薄膜化)する。そして、PMISトランジスタ側およびNMISトランジスタ側の両ゲート構造において、多結晶シリコン膜を各々シリサイド化する。

【0006】

当該製造方法により、NMISトランジスタ側では、シリサイド金属含有量の少ないフルシリサイド層が形成される。他方、PMISトランジスタ側では、シリサイド金属含有量の多いフルシリサイド層が形成される。当該製造方法を採用した場合には、PMISトランジスタ側とNMISトランジスタ側とで、組成の異なるFUSIゲート構造を同時に形成できるという利点がある。

【0007】

【非特許文献1】K.Takahashi et al.,IEDM2004 Tech.Dig.,pp91

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかし、上記例示した製造方法の場合には、以下のような問題点が生じる。

【0009】

第一の問題としてに、フルシリサイド層の組成のバラツキが挙げられる。

【0010】

NMISトランジスタ側にシリサイド金属含有量の少ないフルシリサイド層を形成する際、ゲート長の大きさ違いにより、形成されるフルシリサイド層の組成が異なることが懸念される。たとえばゲート長=1μm程度の場合では、多結晶シリコンゲート露出面積が大きい。したがって、この場合では、シリサイド化金属と多結晶シリコンは理想的な状態(シリサイド化金属とシリコンが1対1に反応が進んでいく状態)で反応する。

【0011】

一方、たとえばゲート長=40nm程度の場合では、多結晶シリコンゲート露出面積が小さい。したがって、この場合では、ゲート中央部に比べてゲートエッジ部におけるシリサイド化金属の拡散量が相対的に多くなる。よって、所望の組成に比べてシリサイド化金属含有量の多いフルシリサイド相が、形成される可能性が高くなる。

【0012】

このように、ゲート長に依存して、フルシリサイド相が異なったトランジスタが形成される。フルシリサイド層の組成のバラツキは、閾値電圧のバラツキを発生させる要因となる。

【0013】

第二の問題として、トランジスタのゲート形状の不安定化が挙げられる。

【0014】

PMISトランジスタおよびNMISトランジスタにおいて、フルシリサイドゲートを同じNi体積膜厚、同じシリサイド化熱処理条件で形成する場合を想定する。この場合には、シリサイド金属含有量の多いPMISトランジスタ側の多結晶シリコンゲートは、予め薄膜化する必要がある。具体的に、シリサイド化金属堆積前に、PMISトランジスタ側において多結晶シリコンゲート電極のみを、既存のウェットエッチ処理やドライエッチ処理によりエッチバックする手法が必要である。

【0015】

しかし、上記手法では、PMISトランジスタ側とNMISトランジスタ側とで、ゲート高さが大きく異なるという不具合が起こる。たとえば、多結晶シリコンの初期膜厚が100nmの場合、PMISトランジスタ側の多結晶シリコンを35nm程度までエッチバックする。これにより、PMISトランジスタ側では、シリサイド化金属含有率の高いフルシリサイドゲートが形成される。しかし、NMISトランジスタ側のゲート構造と比べて、約60nm以上の高さバラツキが発生し、トランジスタのゲート形状が不安定なものとなる。

【0016】

そこで、本発明は、PMISトランジスタ側とNMISトランジスタ側とでシリサイド層の組成のバラツキを防止でき、またトランジスタのゲート形状の不安定化を防止できる、CMISトランジスタの製造方法を提供することを目的とする。

【課題を解決するための手段】

【0017】

本発明に係る1の実施の形態においては、ゲート絶縁膜と金属膜と半導体膜とが当該順に積層した第一のゲート構造を形成する。さらに、ゲート絶縁膜と半導体膜とが当該順に積層した第二のゲート構造を形成する。そして、第一のゲート構造および第二のゲート構造をマスクした状態で、各ゲート構造の両脇における半導体基板上を、低抵抗化させる。そして、第一のゲート構造を構成する半導体膜および第二のゲート構造を構成する半導体膜を低抵抗化させる。

【発明の効果】

【0018】

上記実施の形態によれば、たとえばPMISトランジスタ側とNMISトランジスタ側とでシリサイド層の組成のバラツキを防止でき、またトランジスタのゲート形状の不安定化を防止できる。

【0019】

また、活性領域の低抵抗化と半導体膜の低抵抗化とを、別工程で行うことにより、半導体膜の低抵抗化の制御も容易に成る。

【発明を実施するための最良の形態】

【0020】

以下、この発明をその実施の形態を示す図面に基づいて具体的に説明する。

【0021】

<実施の形態1>

本実施の形態に係るCMIS(Complementary Metal Insulation Semiconductor)トランジスタの製造方法を、工程断面図を用いて説明する。

【0022】

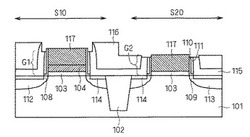

まず、図1に示すように、第一の領域S10と第二の領域S20とを有する半導体基板101を用意する。半導体基板101は、たとえば、シリコンの(100)面をエピタキシャル成長させることにより形成される。

【0023】

ここで、第一の領域S10の半導体基板101の上面内には、第一の導電型の第一のMISトランジスタが形成される。第二の領域S20の半導体基板101の上面内には、第二の導電型の第二のMISトランジスタが形成される。本実施の形態では、第一の導電型は、「N型」とする。また、第二の導電型は、「P型」とする。したがって、本実施の形態では、第一のMISトランジスタはNMISトランジスタであり、第二のMISトランジスタはPMISトランジスタである。

【0024】

また、NMISトランジスタとPMISトランジスタとは、分離酸化膜(STI:Shallow Trench Isolation)102により、電気的に分離されている。当該分離酸化膜102は、半導体基板101に対する部分的エッチング、酸化膜の堆積、および平坦化処理を組み合わせることにより、半導体基板101の表面内に形成される。

【0025】

また、通常の各導電型のイオン注入処理により、半導体基板101内には、N型のウエル領域およびP型のウエル領域が形成される(図1では図示せず)。

【0026】

次に、第一の領域S10の半導体基板101上に、ゲート絶縁膜103と金属膜104と半導体膜106とが当該順に積層した積層構造である、第一のゲート構造G1を形成する。また、第二の領域S20記半導体基板101上に、ゲート絶縁膜103と半導体膜106とが当該順に積層した積層構造である、第二のゲート構造G2を形成する。

【0027】

ここで、第一のゲート構造G1は、NMISトランジスタの構成要素である。また、第二のゲート構造G2は、PMISトランジスタの構成要素である。後述において、具体的な第一のゲート構造G1および第二のゲート構造G2の製造方法を、図2から図5を用いて説明する。

【0028】

まず、CVD(Chemical Vapor Deposition)法等により、第一の領域S10および第二の領域S20の半導体基板101の上面に、ゲート絶縁膜103を形成する(図2)。ゲート絶縁膜103として、たとえばハフニウムシリケイト膜(HfSiOまたはHfSiON)などを採用できる。

【0029】

次に、たとえばCVD法により、図2に示すように、ゲート絶縁膜103上に金属膜104を形成する。本実施の形態では、金属膜104は、N型の仕事関数を有する金属である。以後、本実施の形態では、金属膜104をN−metal104と称する。

【0030】

ここで、N型の仕事関数を有する金属とは、シリコンの伝導帯(Conduction Band:Ec=4.05eV)端近傍のエネルギーに相当する仕事関数を有する材料のことである。具体的には、N型の仕事関数を有する金属とは、その仕事関数値が4.05±0.3eVの範囲ある材料のことを指す。当該N−metal104の材料として、たとえば、Ta系化合物(Ta、TaN、TaC、TaSiN等)やHf系化合物(Hf、HfN、HfC、HfSiN等)が挙げられる。なお、当該N−metal104の膜厚は、5〜30nm程度の範囲内が好ましく、たとえば10nm程度とする。

【0031】

次に、N−metal104上に、レジスト105を形成する。その後、通常のリソグラフィ工程により、レジスト105をパターニングする。ここで、図3に示すように、パターニング後のレジスト105は、第一の領域S10にのみ残存する。換言すれば、第二の領域S20のレジスト105は除去される。次に、パターニング後のレジスト105をマスクとして使用して、N−metal104に対してウェットエッチ等を施す。これにより、図3に示すように、第二の領域S20に形成されていたN−metal104が除去される。

【0032】

第一の領域S10からレジスト105を除去した後、CVD法等により、N−metal104上およびゲート絶縁膜103上に、シリコン膜(半導体膜と把握できる)106を成膜する(図4)。シリコン膜106は、成膜時には、多結晶状でもアモルファス状でも良い。シリコン膜106は、この後に行われる活性化熱処理により、多結晶シリコン膜106となる。ここで、シリコン膜106の膜厚は、たとえば100nm程度とする。

【0033】

次に、図4に示すように、シリコン膜106上に、シリコン酸化膜やシリコン窒化膜等のゲートハードマスク107を形成する。後述するように、ソース・ドレイン領域のシリサイド化工程後に、別途、多結晶シリコン膜106をフルシリサイド化させる。当該ソース・ドレイン領域のシリサイド化工程において、多結晶シリコン膜106がシリサイド化されないように、当該ゲートハードマスク107は、多結晶シリコン膜106の保護膜として機能する。

【0034】

なお、図4から分かるように、シリコン膜106およびゲートハードマスク107は、第一の領域S10および第二の領域S20の両方に形成されている。

【0035】

次に、ゲート絶縁膜103、N−metal104、シリコン膜106およびゲートハードマスク107に対して、ドライエッチング、ウェットエッチング等を施す。これにより、図5に示すように、第一の領域S10の半導体基板101上には、第一のゲート構造G1が形成され、第二の領域S20の半導体基板101上には、第二のゲート構造G2が形成される。

【0036】

ここで、第一のゲート構造G1は、ゲート絶縁膜103、N−metal104およびシリコン膜106とが当該順に積層された積層構造である(図5)。他方、第二のゲート構造G2は、ゲート絶縁膜103およびシリコン膜106とが当該順に積層された積層構造である(図5)。また、第一のゲート構造G1上および第二のゲート構造G2上には、各々ゲートハードマスク107が形成されている(図5)。

【0037】

次に、第二の領域S20をマスクし、第一のゲート構造G1の両脇における半導体基板101に対して、N型の不純物イオンを注入する。当該イオン注入により、第一のゲート構造G1の両脇における半導体基板101には、比較的浅い不純物イオン注入領域108が形成される(図6)。

【0038】

他方、第一の領域S10をマスクして、第二のゲート構造G2の両脇における半導体基板101に対して、P型の不純物イオンを注入する。当該イオン注入により、第二のゲート構造G2の両脇における半導体基板101には、比較的浅い不純物イオン注入領域109が形成される(図6)。

【0039】

次に、第一のゲート構造G1および第二のゲート構造G2を覆うように、半導体基板101上に、シリコン酸化膜110およびシリコン窒化膜111を当該順に成膜する。その後、シリコン酸化膜110およびシリコン窒化膜111に対して、異方性エッチング処理を実施する。これにより、図7に示すように、第一のゲート構造G1の両側面および第二のゲート構造G2両側面には、積層構造のサイドウォール膜110,111が形成される。

【0040】

次に、第二の領域S20をマスクし、第一のゲート構造G1の両脇における半導体基板101に対して、N型の不純物イオンを再び注入する。当該イオン注入により、第一のゲート構造G1の両脇における半導体基板101には、比較的深い不純物イオン注入領域112が形成される(図8)。

【0041】

他方、第一の領域S10をマスクして、第二のゲート構造G2の両脇における半導体基板101に対して、P型の不純物イオンを再び注入する。当該イオン注入により、第二のゲート構造G2の両脇における半導体基板101には、比較的深い不純物イオン注入領域113が形成される(図8)。

【0042】

次に、不純物イオン注入領域108,109,112,113を活性化するために、図8に示した構造体に対して、熱処理を施す。これにより、第一のゲート構造G1の両脇における半導体基板101の表面内には、NMISトランジスタを構成するソース・ドレイン領域108,112が形成される。他方、第二のゲート構造G2の両脇における半導体基板101の表面内には、PMISトランジスタを構成するソース・ドレイン領域109,113が形成される。なお、活性化のための熱処理により、シリコン膜106は多結晶シリコン106となる。

【0043】

次に、第一のゲート構造G1および第二のゲート構造G2をマスクした状態で、ソース・ドレイン領域108,109,112,113を低抵抗化させる工程を実施する。

【0044】

具体的に、第一のゲート構造G1および第二のゲート構造G2を覆うように、半導体基板101上に、ニッケル膜を成膜する。そして、シリサイド化(低抵抗化と把握できる)処理を実施する。その後、未反応のニッケル膜を除去する。以上により、図9に示すように、ソース・ドレイン領域108,109,112,113の表面内には、ニッケルシリサイド114が形成される。つまり、当該ニッケルシリサイド114の形成により、第一のゲート構造G1の両脇における半導体基板101の上面および第二のゲート構造G2の両脇における半導体基板101の上面は、低抵抗化される。

【0045】

ここで、第一のゲート構造G1および第二のゲート構造G2の上面には、各々ゲートハードマスク107が形成されている。また、第一のゲート構造G1および第二のゲート構造G2の両側面には、各々サイドウォール膜110,111が形成されている。したがって、ゲートハードマスク107およびサイドウォール膜110,111はキャップ層として機能し、多結晶シリコン膜106はシリサイド化されない。

【0046】

次に、第一のゲート構造G1および第二のゲート構造G2を覆うように、半導体基板101上に、層間ライナー膜115および層間絶縁膜116を当該順に形成する(図10)。

【0047】

次に、第一のゲート電極G1を構成する多結晶シリコン膜106の上面、および第二のゲート電極G2を構成する多結晶シリコン膜106の上面を露出させる。その後、前記各多結晶シリコン膜(上述したように、半導体膜と把握できる)106を低抵抗化させる処理を実施する。

【0048】

具体的に、露出している各多結晶シリコン膜106の上面に、シリサイド化金属(たとえば、Ni等)を堆積する。その後、当該シリサイド化金属堆積後の半導体基板101に対して、熱処理を施す。これにより、各多結晶シリコン膜106をフルシリサイド化(低抵抗化と把握できる)される。つまり、図11に示すように、第一のゲート構造G1は、ゲート絶縁膜103、N−metal104およびフルシリサイド膜117の積層構造となり、第二のゲート構造G2は、ゲート絶縁膜103およびフルシリサイド膜117の積層構造となる。

【0049】

なお、上記シリサイド化金属としては、Ni以外に、Pt、Ti、Co、Hf、Ta、Yb、Er、およびAlなどが挙げられ、これらのいずれか一つ以上を含むことが望ましい。

【0050】

ここで、N−metal104の膜厚が5nm以上あれば、当該N−metal104は上記所望の仕事関数を示す。N−metal104が当該所望の仕事関数を有すれば、NMISトランジスタは、所望の閾値電圧動作が可能となる。このため、N−metal104の上層の組成は閾値電圧制御には関わらず、フルシリサイド膜117の組成を所望の組成に制御する必要が無い。つまり、第一のゲート構造G1を構成するフルシリサイド膜117と第二のゲート構造G2を構成するフルシリサイド膜117とは、共に同じ組成であっても良い。

【0051】

背景技術で説明した方法では、NMISトランジスタ側とPMISトランジスタ側で、組成の異なるシリサイド膜を形成する必要がある。そのため、NMISトランジスタ側の多結晶シリコン膜の膜厚とPMIS多結晶シリコン膜の膜厚とを、異ならせる処理が必要であった。

【0052】

しかし、本実施の形態に係る方法では、上記の通り、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜117の組成を作り分ける必要が無い。つまり、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜117の組成が同じであっても良い。このため、背景技術で説明したような、他方のMISトランジスタを構成する多結晶シリコン膜を、選択的にエッチングする必要も無い。

【0053】

なお、フルシリサイド膜117の形成に際して、ソース・ドレイン領域のニッケルシリサイド114は、層間絶縁膜116により覆われている。したがって、当該フルシリサイド膜117の形成により、当該ニッケルシリサイド114が、再シリサイド化されたり、エッチングダメージを受けたりすることを防止できる。よって、所望のデバイス特性を維持できる。

【0054】

また、上記フルシリサイド膜117の形成に際して、シリサイド化金属膜厚、シリサイド化熱処理条件、熱処理を施すタイミング、未反応シリサイド化金属除去のタイミング等を制御する。これにより、第一のゲート構造G1および第二のゲート構造G2を構成するフルシリサイド膜117を、シリサイド金属含有量の多いフルシリサイドとすることできる。シリサイド金属含有量の多いフルシリサイドとは、Ni3Si、Ni31Si12、およびNi2Siのいずれかの組成を有するフルシリサイド膜である。

【0055】

たとえば、50nmの膜厚を有する多結晶シリコン膜106に対して、シリサイド金属膜として、Ni膜を70nm以上の膜厚で堆積する。その後、Ni膜形成後の半導体基板101に対して1回目の熱処理を施す。ここで、当該1回目の熱処理は、400℃以下、30秒程度の条件で実施される。当該1回目の熱処理により、多結晶シリコン膜106とNi膜を反応させる。次に未反応Ni膜のみを選択ウェットエッチングにより除去する。その後、半導体基板101に対して2回目の熱処理を施す。当該2回目の熱処理は、500℃、30秒程度の条件で実施される。以上の形成条件により、シリサイド金属含有量の多いNiフルシリサイド層(この場合、Ni31Si12層)が形成される。

【0056】

このように、少なくともPMISトランジスタを構成する第二のゲート構造G2において、フルシリサイド膜117をシリサイド金属含有量の多いフルシリサイドとする。これにより、PMISトランジスタ側においても、所望の閾値電圧動作が可能となる。

【0057】

上記フルシリサイド膜117形成後、層間絶縁膜を積み増しし、CMP(Chemical Mechanical Polishing)処理による平坦化、コンタクトプラグ形成等のフローを経て、通常のバックエンドフローを実施する。以上により、CMISトランジスタが完成する。

【0058】

ところで、上記非特許文献1では、前記シリサイド組成に応じて実行仕事関数が変化する現象を利用している。具体的に、NMISトランジスタには、NiSiをFUSIゲート材料として用いる。また、PMISトランジスタには、Ni3Si等のNi含有率の高いニッケルシリサイドをFUSIゲート材料として用いる。これにより、当該非特許文献1では、低閾値電圧Vthデバイスを実現することができると提唱している。

【0059】

上記シリサイド相制御したFUSIゲート電極を形成する方法としては、たとえば次のような製造方法が挙げられる。

【0060】

つまり、PMISトランジスタ側およびNMISトランジスタ側の両ゲート構造において、同じ膜厚である多結晶シリコン膜1004,1005を形成する(図12)。その後、NMISトランジスタ側の多結晶シリコン膜1004をレジスト1016で覆い、PMISトランジスタ側の多結晶シリコン膜1005の膜厚を削減(薄膜化)する(図13)。そして、PMISトランジスタ側およびNMISトランジスタ側の両ゲート構造において、多結晶シリコン膜を各々シリサイド化する(図14)。

【0061】

当該製造方法により、NMISトランジスタ側では、シリサイド金属含有量の少ないフルシリサイド膜1018が形成される。他方、PMISトランジスタ側では、シリサイド金属含有量の多いフルシリサイド膜1019が形成される。当該製造方法を採用した場合には、PMISトランジスタ側とNMISトランジスタ側とで、組成の異なるFUSIゲート構造を同時に形成される。

【0062】

本実施の形態に係るCMISトランジスタの製造方法では、第一のゲート構造G1側には、ゲート絶縁膜103と多結晶シリコン膜106との間に、N−metal104を形成する工程を含んでいる。

【0063】

したがって、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜117の組成を作り分ける必要がなくなる。よって、多結晶シリコン膜106の低抵抗化(シリサイド化)処理前に、第一のゲート構造G1側と第二のゲート構造G2側とで、多結晶シリコン膜106の膜厚を異ならせる処理も不要となる。また、N−metal104の存在により、多結晶シリコン膜106の低抵抗化(シリサイド化)処理に際して、半導体基板101側からの拡散を考慮する必要がなくなる。したがって、フルシリサイド膜117の形成制御を容易にコントロールできる。

【0064】

なお、たとえば、NMISトランジスタ側とPMISトランジスタ側とで、同時に組成の異なるフルシリサイド膜を形成するとする。この場合、組成を安定形成できるプロセスウィンドウが狭いために、フルシリサイド組成のバラツキが問題視される。たとえば、NMISトランジスタ側において金属含有率の少ないフルシリサイド膜を形成しようとしても、局所的にNi反応量の多い箇所が現れ、シリサイド金属含有率の多いフルシリサイド相が形成されるという不具合が起こる。また逆に、P型のトランジスタ側において金属含有率の多いフルシリサイドゲートを形成しようとしても、局所的にNi反応量の少ない箇所が現れ、シリサイド金属含有率の少ないフルシリサイド相が形成されるという不具合が起こる。

【0065】

上記のように、本実施の形態では、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜117の組成を作り分ける必要がなくなる。したがって、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜117の形成に際して、同熱処理条件、同シリコン/シリサイド金属膜厚により、同一組成を作ることが可能となる。このため、プロセス制御ウィンドウは広がり、フルシリサイド膜117の組成のバラツキを防止できる。

【0066】

また、第一のゲート構造G1側と第二のゲート構造G2側とで、多結晶シリコン膜106の膜厚を異ならせる処理が必要な場合には、既存のサイドウォール110,111やオフセットスペーサ、および層間絶縁膜等もエッチングされることになる。これにより、Ni堆積前のゲート形状が悪化する、或いは、ソース・ドレイン領域108,109,112,113に形成されているNiシリサイド等が露出、変質する恐れ等がある。

【0067】

本実施の形態では、上記の通り、第一のゲート構造G1側と第二のゲート構造G2側とで、多結晶シリコン膜106の膜厚を異ならせる処理も不要である。したがって、MISトランジスタのゲート形状不安定化を防止することができる。

【0068】

以上の観点より、本実施の形態に係る製造方法により、良好な特性を有するデュアルメタルゲートデバイス(CMISデバイス)を容易に作成することが可能となる。

【0069】

また、本実施の形態に係るCMISトランジスタの製造方法では、ニッケルシリサイド114の形成処理と、フルシリサイド膜117の形成処理とを、各々別のシリサイド工程にて実施している。特に、ニッケルシリサイド114の形成処理後に、フルシリサイド膜117の形成を行っている。

【0070】

したがって、ソース・ドレイン領域108,109,112,113の低抵抗化と、フルシリサイド膜117を有するゲート構造G1,G2の閾値制御とを、同時に満たすことが可能である。また、ニッケルシリサイド114の形成処理の際に、多結晶シリコン膜106の一部をシリサイド化する場合よりも、上記別工程を採用する方が、フルシリサイド膜117の形成制御も容易に成る。

【0071】

また、本実施の形態に係るCMISトランジスタの製造方法では、金属膜104として、N−metal104を一層だけを形成している。したがって、金属膜104が複層である場合よりも、本実施の形態に係る方法の方が、より容易に、金属膜104のパターニングができる。つまり、本実施の形態に係る方法の方が、より容易に、第一のゲート構造G1を形成できる。

【0072】

また、本実施の形態に係るCMISトランジスタの製造方法では、各多結晶シリコン膜106を、フルシリサイド化させている。したがって、ゲート構造G1,G2の全体低抵抗化を図ることができる。

【0073】

また、本実施の形態に係るCMISトランジスタの製造方法では、金属膜104は、N型の仕事関数を有するN−metal(Ta化合物またはHf化合物)104である。NMISトランジスタは、所望の閾値電圧動作が可能となる。

【0074】

また、本実施の形態に係るCMISトランジスタの製造方法では、5〜30nm程度の膜厚のN−metal104を形成している。したがって、N−metal104が有する仕事関数を4.05±0.3eVの範囲とすることができる。これにより、NMISトランジスタは、所望の閾値電圧動作が可能となる。

【0075】

また、本実施の形態に係るCMISトランジスタの製造方法では、第二のゲート構造G2を構成する多結晶シリコン膜106を、Ni3Si、Ni31Si12、およびNi2Siのいずれかの組成に、シリサイド化させている。したがって、PMISトランジスタは、所望の閾値電圧動作が可能となる。

【0076】

また、本実施の形態に係るCMISトランジスタの製造方法では、多結晶シリコン膜106を、Ni、Pt、Ti、Co、Hf、Ta、Yb、Er、およびAlのうち、少なくとも1以上を含む金属を用いて、フルシリサイド化している。したがって、容易に、フルシリサイド膜117を形成することができる。

【0077】

なお、本実施の形態1では、半導体膜106として、多結晶シリコン膜106を用いた場合について記した。しかし、半導体膜106として、ゲルマニウム膜やシリコンゲルマニウム膜を用いても良い。この場合、低抵抗化処理により、半導体膜106は、フルジャーマナイトゲート等となる。

【0078】

このように、半導体膜106として、ゲルマニウム膜やシリコンゲルマニウム膜を用いることにより、低抵抗化後のゲート電極の仕事関数制御範囲が、多結晶シリコン膜を採用したときと比べて変化する。したがって、デバイスの仕様に応じて、材料を変えることにより所望の閾値電圧を有するデバイスが実現できる。

【0079】

<実施の形態2>

本実施の形態に係るCMISトランジスタの製造方法を、工程断面図を用いて説明する。

【0080】

まず、図15に示すように、第一の領域S30と第二の領域S40とを有する半導体基板201を用意する。半導体基板201は、たとえば、シリコンの(100)面をエピタキシャル成長させることにより形成される。

【0081】

ここで、第一の領域S30の半導体基板201の上面内には、第一の導電型の第一のMISトランジスタが形成される。第二の領域S40の半導体基板201の上面内には、第二の導電型の第二のMISトランジスタが形成される。本実施の形態では、第一の導電型は、「P型」とする。また、第二の導電型は、「N型」とする。したがって、本実施の形態では、第一のMISトランジスタはPMISトランジスタであり、第二のMISトランジスタはNMISトランジスタである。

【0082】

また、NMISトランジスタとPMISトランジスタとは、半導体基板202の表面内に形成された分離酸化膜202により、電気的に分離されている。当該分離酸化膜202の形成方法は、実施の形態1で説明した分離酸化膜102の形成方法と同じである。

【0083】

また、通常の各導電型のイオン注入処理により、半導体基板201内には、N型のウエル領域およびP型のウエル領域が形成される(図15では図示せず)。

【0084】

次に、第一の領域S30の半導体基板201上に、ゲート絶縁膜203と金属膜204と半導体膜206とが当該順に積層した積層構造である、第一のゲート構造G11を形成する。また、第二の領域S40記半導体基板201上に、ゲート絶縁膜203と半導体膜206とが当該順に積層した積層構造である、第二のゲート構造G12を形成する。

【0085】

ここで、第一のゲート構造G11は、PMISトランジスタの構成要素である。また、第二のゲート構造G12は、NMISトランジスタの構成要素である。後述において、具体的な第一のゲート構造G11および第二のゲート構造G12の製造方法を、図16から図19を用いて説明する。

【0086】

まず、CVD法等により、第一の領域S30および第二の領域S40の半導体基板201の上面に、ゲート絶縁膜203を形成する(図16)。ゲート絶縁膜203として、たとえばハフニウムシリケイト膜(HfSiOまたはHfSiON)などを採用できる。

【0087】

次に、たとえばCVD法により、図16に示すように、ゲート絶縁膜203上に金属膜204を形成する。本実施の形態では、金属膜204は、P型の仕事関数を有する金属である。以後、本実施の形態では、金属膜204をP−metal204と称する。

【0088】

ここで、P型の仕事関数を有する金属とは、シリコンの価電子帯(Valence Band:Ev=5.12eV)端近傍のエネルギーに相当する仕事関数を有する材料のことである。具体的には、P型の仕事関数を有する金属とは、その仕事関数値が5.17±0.3eVの範囲ある材料のことを指す。当該P−metal204の材料として、たとえば、Ti系化合物(TiN、TiAlN等)、W系化合物(W、WN等)、Ru系化合物(Ru、RuO2等)およびPt系化合物等が挙げられる。なお、当該P−metal204の膜厚は、5〜30nm程度の範囲内が好ましく、たとえば10nm程度とする。

【0089】

次に、P−metal204上に、レジスト205を形成する。その後、通常のリソグラフィ工程により、レジスト205をパターニングする。ここで、図17に示すように、パターニング後のレジスト205は、第一の領域S30にのみ残存する。換言すれば、第二の領域S40のレジスト205は除去される。次に、パターニング後のレジスト205をマスクとして使用して、P−metal204に対してウェットエッチ等を施す。これにより、図17に示すように、第二の領域S40に形成されていたP−metal204が除去される。

【0090】

第一の領域S30からレジスト205を除去した後、CVD法等により、P−metal204上およびゲート絶縁膜203上に、シリコン膜(半導体膜と把握できる)206を成膜する(図18)。シリコン膜206は、成膜時には、多結晶状でもアモルファス状でも良い。シリコン膜206は、この後に行われる活性化熱処理により、多結晶シリコン膜206となる。ここで、シリコン膜206の膜厚は、たとえば100nm程度とする。

【0091】

次に、図18に示すように、シリコン膜206上に、シリコン酸化膜やシリコン窒化膜等のゲートハードマスク207を形成する。後述するように、ソース・ドレイン領域のシリサイド化工程後に、別途、多結晶シリコン膜206をフルシリサイド化させる。当該ソース・ドレイン領域のシリサイド化工程において、多結晶シリコン膜206がシリサイド化されないように、当該ゲートハードマスク207は、多結晶シリコン膜206の保護膜として機能する。

【0092】

なお、図18から分かるように、シリコン膜206およびゲートハードマスク207は、第一の領域S30および第二の領域S40の両方に形成されている。

【0093】

次に、ゲート絶縁膜203、P−metal204、シリコン膜206およびゲートハードマスク207に対して、ドライエッチング、ウェットエッチング等を施す。これにより、図19に示すように、第一の領域S30の半導体基板201上には、第一のゲート構造G11が形成され、第二の領域S40の半導体基板201上には、第二のゲート構造G2が形成される。

【0094】

ここで、第一のゲート構造G11は、ゲート絶縁膜203、P−metal204およびシリコン膜206とが当該順に積層された積層構造である(図19)。他方、第二のゲート構造G12は、ゲート絶縁膜203およびシリコン膜206とが当該順に積層された積層構造である(図19)。また、第一のゲート構造G11上および第二のゲート構造G12上には、各々ゲートハードマスク207が形成されている(図19)。

【0095】

次に、第二の領域S40をマスクし、第一のゲート構造G11の両脇における半導体基板201に対して、P型の不純物イオンを注入する。当該イオン注入により、第一のゲート構造G11の両脇における半導体基板201には、比較的浅い不純物イオン注入領域208が形成される(図20)。

【0096】

他方、第一の領域S30をマスクして、第二のゲート構造G12の両脇における半導体基板201に対して、N型の不純物イオンを注入する。当該イオン注入により、第二のゲート構造G12の両脇における半導体基板201には、比較的浅い不純物イオン注入領域209が形成される(図20)。

【0097】

次に、第一のゲート構造G11および第二のゲート構造G12を覆うように、半導体基板201上に、シリコン酸化膜210およびシリコン窒化膜211を当該順に成膜する。その後、シリコン酸化膜210およびシリコン窒化膜211に対して、異方性エッチング処理を実施する。これにより、図21に示すように、第一のゲート構造G11の両側面および第二のゲート構造G12両側面には、積層構造のサイドウォール膜210,211が形成される。

【0098】

次に、第二の領域S40をマスクし、第一のゲート構造G11の両脇における半導体基板201に対して、P型の不純物イオンを再び注入する。当該イオン注入により、第一のゲート構造G11の両脇における半導体基板201には、比較的深い不純物イオン注入領域212が形成される(図22)。

【0099】

他方、第一の領域S30をマスクして、第二のゲート構造G12の両脇における半導体基板201に対して、N型の不純物イオンを再び注入する。当該イオン注入により、第二のゲート構造G12の両脇における半導体基板201には、比較的深い不純物イオン注入領域213が形成される(図22)。

【0100】

次に、不純物イオン注入領域208,209,212,213を活性化するために、図22に示した構造体に対して、熱処理を施す。これにより、第一のゲート構造G11の両脇における半導体基板201の表面内には、PMISトランジスタを構成するソース・ドレイン領域208,212が形成される。他方、第二のゲート構造G12の両脇における半導体基板201の表面内には、NMISトランジスタを構成するソース・ドレイン領域209,213が形成される。なお、活性化のための熱処理により、シリコン膜206は多結晶シリコン206となる。

【0101】

次に、第一のゲート構造G11および第二のゲート構造G12をマスクした状態で、ソース・ドレイン領域208,209,212,213を低抵抗化させる工程を実施する。

【0102】

具体的に、第一のゲート構造G11および第二のゲート構造G12を覆うように、半導体基板201上に、ニッケル膜を成膜する。そして、シリサイド化(低抵抗化と把握できる)処理を実施する。その後、未反応のニッケル膜を除去する。以上により、図23に示すように、ソース・ドレイン領域208,209,212,213の表面内には、ニッケルシリサイド214が形成される。つまり、当該ニッケルシリサイド214の形成により、第一のゲート構造G11の両脇における半導体基板201の上面および第二のゲート構造G12の両脇における半導体基板201の上面は、低抵抗化される。

【0103】

ここで、第一のゲート構造G11および第二のゲート構造G12の上面には、各々ゲートハードマスク207が形成されている。また、第一のゲート構造G11および第二のゲート構造G12の両側面には、各々サイドウォール膜210,211が形成されている。したがって、ゲートハードマスク207およびサイドウォール膜210,211はキャップ層として機能し、多結晶シリコン膜206はシリサイド化されない。

【0104】

次に、第一のゲート構造G11および第二のゲート構造G12を覆うように、半導体基板201上に、層間ライナー膜215および層間絶縁膜216を当該順に形成する(図24)。

【0105】

次に、第一のゲート電極G11を構成する多結晶シリコン膜206の上面、および第二のゲート電極G12を構成する多結晶シリコン膜206の上面を露出させる。その後、前記各多結晶シリコン膜(上述したように、半導体膜と把握できる)206を低抵抗化させる処理を実施する。

【0106】

具体的に、露出している各多結晶シリコン膜206の上面に、シリサイド化金属(たとえば、Ni等)を堆積する。その後、当該シリサイド化金属堆積後の半導体基板201に対して、熱処理を施す。これにより、各多結晶シリコン膜206をフルシリサイド化(低抵抗化と把握できる)される。つまり、図25に示すように、第一のゲート構造G11は、ゲート絶縁膜203、P−metal204およびフルシリサイド膜217の積層構造となり、第二のゲート構造G12は、ゲート絶縁膜203およびフルシリサイド膜217の積層構造となる。

【0107】

なお、上記シリサイド化金属としては、Ni以外に、Pt、Ti、Co、Hf、Ta、Yb、Er、およびAlなどが挙げられ、これらのいずれか一つ以上を含むことが望ましい。

【0108】

ここで、P−metal204の膜厚が5nm以上あれば、当該P−metal204は上記所望の仕事関数を示す。P−metal204が当該所望の仕事関数を有すれば、PMISトランジスタは、所望の閾値電圧動作が可能となる。このため、P−metal204の上層の組成は閾値電圧制御には関わらず、フルシリサイド膜217の組成を所望の組成に制御する必要が無い。つまり、第一のゲート構造G11を構成するフルシリサイド膜217と第二のゲート構造G12を構成するフルシリサイド膜217とは、共に同じ組成であっても良い。

【0109】

背景技術で説明した方法では、NMISトランジスタ側とPMISトランジスタ側で、組成の異なるシリサイド膜を形成する必要がある。そのため、NMISトランジスタ側の多結晶シリコン膜の膜厚とPMIS多結晶シリコン膜の膜厚とを、異ならせる処理が必要であった。

【0110】

しかし、本実施の形態に係る方法では、上記の通り、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜217の組成を作り分ける必要が無い。つまり、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜217の組成が同じであっても良い。このため、背景技術で説明したような、他方のMISトランジスタを構成する多結晶シリコン膜を、選択的にエッチングする必要も無い。

【0111】

なお、フルシリサイド膜217の形成に際して、ニッケルシリサイド214は、層間絶縁膜216により覆われている。したがって、当該フルシリサイド膜217の形成により、当該ニッケルシリサイド214が、再シリサイド化されたり、エッチングダメージを受けたりすることを防止できる。よって、所望のデバイス特性を維持できる。

【0112】

また、上記フルシリサイド膜217の形成に際して、シリサイド化金属膜厚、シリサイド化熱処理条件、熱処理を施すタイミング、未反応シリサイド化金属除去のタイミング等を制御する。これにより、第一のゲート構造G11および第二のゲート構造G12を構成するフルシリサイド膜217を、シリサイド金属含有量の少ないフルシリサイドとすることできる。シリサイド金属含有量の少ないフルシリサイドとは、NiSiまたはNiSi2等の組成を有するフルシリサイド膜である。

【0113】

たとえば、50nmの膜厚を有する多結晶シリコン膜206に対して、シリサイド金属膜として、Ni膜を30nm以上の膜厚で堆積する。その後、Ni膜形成後の半導体基板201に対して1回目の熱処理を施す。ここで、当該1回目の熱処理は、400℃以下、30秒程度の条件で実施される。当該1回目の熱処理により、多結晶シリコン膜206とNi膜を反応させる。次に未反応Ni膜のみを選択ウェットエッチングにより除去する。その後、半導体基板201に対して2回目の熱処理を施す。当該2回目の熱処理は、500℃、30秒程度の条件で実施される。以上の形成条件により、シリサイド金属含有量の少ないNiフルシリサイド層(この場合、NiSi層)が形成される。

【0114】

このように、少なくともNMISトランジスタを構成する第二のゲート構造G12において、フルシリサイド膜217をシリサイド金属含有量の少ないフルシリサイドとする。これにより、NMISトランジスタ側においても、所望の閾値電圧動作が可能となる。

【0115】

上記フルシリサイド膜217形成後、層間絶縁膜を積み増しし、CMP処理による平坦化、コンタクトプラグ形成等のフローを経て、通常のバックエンドフローを実施する。以上により、CMISトランジスタが完成する。

【0116】

本実施の形態に係るCMISトランジスタの製造方法では、第一のゲート構造G11側には、ゲート絶縁膜203と多結晶シリコン膜206との間に、P−metal204を形成する工程を含んでいる。

【0117】

したがって、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜217の組成を作り分ける必要がなくなる。よって、多結晶シリコン膜206の低抵抗化(シリサイド化)処理前に、第一のゲート構造G11側と第二のゲート構造G12側とで、多結晶シリコン膜206の膜厚を異ならせる処理も不要となる。また、P−metal204の存在により、多結晶シリコン膜206の低抵抗化(シリサイド化)処理に際して、半導体基板201側からの拡散を考慮する必要がなくなる。したがって、フルシリサイド膜217の形成制御を容易にコントロールできる。

【0118】

上記のように、本実施の形態では、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜217の組成を作り分ける必要がなくなる。したがって、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜217の形成に際して、同熱処理条件、同シリコン/シリサイド金属膜厚により、同一組成を作ることが可能となる。このため、プロセス制御ウィンドウは広がり、フルシリサイド膜217の組成のバラツキを防止できる。

【0119】

本実施の形態では、上記の通り、第一のゲート構造G11側と第二のゲート構造G12側とで、多結晶シリコン膜206の膜厚を異ならせる処理も不要である。したがって、MISトランジスタのゲート形状不安定化を防止することができる。

【0120】

以上の観点より、本実施の形態に係る製造方法により、良好な特性を有するデュアルメタルゲートデバイス(CMISデバイス)を容易に作成することが可能となる。

【0121】

また、本実施の形態に係るCMISトランジスタの製造方法では、ニッケルシリサイド214の形成処理と、フルシリサイド膜217の形成処理とを、各々別のシリサイド工程にて実施している。特に、ニッケルシリサイド214の形成処理後に、フルシリサイド膜217の形成を行っている。

【0122】

したがって、ソース・ドレイン領域208,209,212,213の低抵抗化と、フルシリサイド膜217を有するゲート構造G11,G12の閾値制御とを、同時に満たすことが可能である。また、ニッケルシリサイド214の形成処理の際に、多結晶シリコン膜206の一部をシリサイド化する場合よりも、上記別工程を採用する方が、フルシリサイド膜217の形成制御も容易に成る。

【0123】

また、本実施の形態に係るCMISトランジスタの製造方法では、金属膜204として、P−metal204を一層だけを形成している。したがって、金属膜204が複層である場合よりも、本実施の形態に係る方法の方が、より容易に、金属膜204のパターニングができる。つまり、本実施の形態に係る方法の方が、より容易に、第一のゲート構造G11を形成できる。

【0124】

また、本実施の形態に係るCMISトランジスタの製造方法では、各多結晶シリコン膜206を、フルシリサイド化させている。したがって、ゲート構造G11,G12の全体低抵抗化を図ることができる。

【0125】

また、本実施の形態に係るCMISトランジスタの製造方法では、金属膜204は、P型の仕事関数を有するP−metal(Ti化合物、W化合物、Ru化合物、およびPt化合物)204である。PMISトランジスタは、所望の閾値電圧動作が可能となる。

【0126】

また、本実施の形態に係るCMISトランジスタの製造方法では、5〜30nm程度の膜厚のP−metal204を形成している。したがって、P−metal204が有する仕事関数を5.17±0.3eVの範囲とすることができる。これにより、PMISトランジスタは、所望の閾値電圧動作が可能となる。

【0127】

また、本実施の形態に係るCMISトランジスタの製造方法では、第二のゲート構造G12を構成する多結晶シリコン膜206を、NiSiまたはNiSi2の組成に、シリサイド化させている。したがって、NMISトランジスタは、所望の閾値電圧動作が可能となる。

【0128】

また、本実施の形態に係るCMISトランジスタの製造方法では、多結晶シリコン膜206を、Ni、Pt、Ti、Co、Hf、Ta、Yb、Er、およびAlのうち、少なくとも1以上を含む金属を用いて、フルシリサイド化している。したがって、容易に、フルシリサイド膜217を形成することができる。

【0129】

なお、本実施の形態2では、半導体膜206として、多結晶シリコン膜206を用いた場合について記した。しかし、半導体膜206として、ゲルマニウム膜やシリコンゲルマニウム膜を用いても良い。この場合、低抵抗化処理により、半導体膜206は、フルジャーマナイトゲート等となる。

【0130】

このように、半導体膜206として、ゲルマニウム膜やシリコンゲルマニウム膜を用いることにより、低抵抗化後のゲート電極の仕事関数制御範囲が、多結晶シリコン膜を採用したときと比べて変化する。したがって、デバイスの仕様に応じて、材料を変えることにより所望の閾値電圧を有するデバイスが実現できる。

【0131】

<実施の形態3>

本実施の形態に係るCMISトランジスタの製造方法を、工程断面図を用いて説明する。

【0132】

図1から図10までの工程は、実施の形態1と同様である。したがって、これらの工程の詳細な説明は、ここでは省略する。

【0133】

ここで、本実施の形態では、実施の形態1と同様に、第一の領域S10の半導体基板101の上面内には、第一の導電型の第一のMISトランジスタが形成される。第二の領域S20の半導体基板101の上面内には、第二の導電型の第二のMISトランジスタが形成される。本実施の形態では、第一の導電型は、「N型」とする。また、第二の導電型は、「P型」とする。したがって、本実施の形態では、実施の形態1と同様に、第一のMISトランジスタはNMISトランジスタであり、第二のMISトランジスタはPMISトランジスタである。

【0134】

次に、図10の構成において、第一のゲート電極G1を構成する多結晶シリコン膜106の上面、および第二のゲート電極G2を構成する多結晶シリコン膜106の上面を露出させる。次に、第二の領域S20をレジストとマスクする。そして、第一のゲート構造G1を構成する多結晶シリコン膜106に対して、たとえば窒素、酸素、燐等の少なくとも1種類以上をイオン注入によりドーピングする。

【0135】

当該イオン注入により、図26に示すように、第一のゲート構造G1を構成する多結晶シリコン膜106aが形成される。後に実施される多結晶シリコン膜106aのシリサイド化工程において、当該多結晶シリコン膜106aは、シリサイド金属の半導体基板101方向への拡散を抑制する機能を有する。具体的に、シリサイド金属のN−metal104膜への侵入を抑制できる。なお、図26は、第二の領域S20に形成されていたレジストマスク除去後の構成を示している。

【0136】

その後、多結晶シリコン膜(上述したように、半導体膜と把握できる)106,106aを低抵抗化させる処理を実施する。

【0137】

具体的に、露出している各多結晶シリコン膜106,106aの上面に、シリサイド化金属(たとえば、Ni等)を堆積する。その後、当該シリサイド化金属堆積後の半導体基板101に対して、熱処理を施す。これにより、各多結晶シリコン膜106,106aをシリサイド化(低抵抗化と把握できる)される。

【0138】

ここで、多結晶シリコン106aはシリサイド金属の拡散を抑制する。したがって、第一のゲート電極G1側においては、多結晶シリコン106aはすべてシリサイド化されない。つまり、図27に示すように、第一のゲート構造G1は、ゲート絶縁膜103、N−metal104、不純物イオンが注入された多結晶ポリシリコン膜106aおよびシリサイド膜117の積層構造となる。なお、第二のゲート構造G2は、ゲート絶縁膜103およびフルシリサイド膜117の積層構造となる。

【0139】

また、上記シリサイド化金属としては、Ni以外に、Pt、Ti、Co、Hf、Ta、Yb、Er、およびAlなどが挙げられ、これらのいずれか一つ以上を含むことが望ましい。

【0140】

多結晶シリコン膜106aが形成される場合においても、N−metal104の膜厚が5nm以上であれば、NMISトランジスタは所望の仕事関数を示す。したがって、当該N−metal104の上層の電極構造に関わらず、NMISトランジスタは、所望の閾値電圧動作が可能である。このため、N−metal104の上層の組成は閾値電圧制御には関わらず、シリサイド膜117の組成を所望の組成に制御する必要が無い。つまり、第一のゲート構造G1を構成するシリサイド膜117と第二のゲート構造G2を構成するフルシリサイド膜117とは、共に同じ組成であっても良い。

【0141】

なお、シリサイド膜117の形成に際して、ニッケルシリサイド114は、層間絶縁膜116により覆われている。したがって、当該シリサイド膜117の形成により、当該ニッケルシリサイド114が、再シリサイド化されたり、エッチングダメージを受けたりすることを防止できる。よって、所望のデバイス特性を維持できる。

【0142】

また、上記シリサイド膜117の形成に際して、シリサイド化金属膜厚、シリサイド化熱処理条件、熱処理を施すタイミング、未反応シリサイド化金属除去のタイミング等を制御する(形成条件の一例は、実施の形態1で説明した通りである)。これにより、第一のゲート構造G1および第二のゲート構造G2を構成するシリサイド膜117を、シリサイド金属含有量の多いフルシリサイドとすることできる。シリサイド金属含有量の多いシリサイドとは、Ni3Si、Ni31Si12、およびNi2Siのいずれかの組成を有するシリサイド膜である。

【0143】

このように、少なくともPMISトランジスタを構成する第二のゲート構造G2において、フルシリサイド膜117をシリサイド金属含有量の多いフルシリサイドとする。これにより、PMISトランジスタ側においても、所望の閾値電圧動作が可能となる。

【0144】

上記シリサイド膜117形成後、層間絶縁膜を積み増しし、CMP処理による平坦化、コンタクトプラグ形成等のフローを経て、通常のバックエンドフローを実施する。以上により、CMISトランジスタが完成する。

【0145】

本実施の形態では上記工程が実施されるので、実施の形態1で説明した効果に加えて、次のような効果も有する。

【0146】

具体的に、本実施の形態では、第一のゲート構造G1を構成する多結晶シリコン106のシリサイド化前に、当該多結晶シリコン106に対して、燐、砒素、および酸素のうち、少なくとも1つをイオン注入している。

【0147】

したがって、当該イオン注入された多結晶シリコン膜106aの形成により、多結晶シリコン膜106aのシリサイド化の際に、シリサイド金属の半導体基板101方向への拡散を抑制できる。具体的に、N−metal104へのシリサイド金属の侵入を抑制できる。これにより、NMISトランジスタ側において、仕事関数を変化させる等の影響がなくなり、安定したCMISデバイスが実現可能となる。

【0148】

なお、当該イオン注入処理を施すことにより、第一のゲート構造G1は、ゲート絶縁膜103、N−metal104、不純物イオンが注入された多結晶ポリシリコン膜106aおよびシリサイド膜117が当該順に積層した、積層構造となる。

【0149】

また、半導体膜106として、多結晶シリコンの代わりに、ゲルマニウム膜やシリコンゲルマニウム膜を用いても良い。この場合、低抵抗化処理により、半導体膜106は、ジャーマナイトゲート等となる。

【0150】

<実施の形態4>

本実施の形態に係るCMISトランジスタの製造方法を、工程断面図を用いて説明する。

【0151】

図15から図24までの工程は、実施の形態2と同様である。したがって、これらの工程の詳細な説明は、ここでは省略する。

【0152】

ここで、本実施の形態では、実施の形態2と同様に、第一の領域S30の半導体基板201の上面内には、第一の導電型の第一のMISトランジスタが形成される。第二の領域S40の半導体基板201の上面内には、第二の導電型の第二のMISトランジスタが形成される。本実施の形態では、第一の導電型は、「P型」とする。また、第二の導電型は、「N型」とする。したがって、本実施の形態では、実施の形態2と同様に、第一のMISトランジスタはPMISトランジスタであり、第二のMISトランジスタはNMISトランジスタである。

【0153】

次に、図24の構成において、第一のゲート電極G11を構成する多結晶シリコン膜206の上面、および第二のゲート電極G12を構成する多結晶シリコン膜206の上面を露出させる。次に、第二の領域S40をレジストとマスクする。そして、第一のゲート構造G11を構成する多結晶シリコン膜206に対して、たとえば窒素、酸素、燐等の少なくとも1種類以上をイオン注入によりドーピングする。

【0154】

当該イオン注入により、図28に示すように、第一のゲート構造G11を構成する多結晶シリコン膜206aが形成される。後に実施される多結晶シリコン膜206aのシリサイド化工程において、当該多結晶シリコン膜206aは、シリサイド金属の半導体基板201方向への拡散を抑制する機能を有する。具体的に、シリサイド金属のP−metal204膜への侵入を抑制できる。なお、図28は、第二の領域S40に形成されていたレジストマスク除去後の構成を示している。

【0155】

その後、多結晶シリコン膜(上述したように、半導体膜と把握できる)206,206aを低抵抗化させる処理を実施する。

【0156】

具体的に、露出している各多結晶シリコン膜206,206aの上面に、シリサイド化金属(たとえば、Ni等)を堆積する。その後、当該シリサイド化金属堆積後の半導体基板201に対して、熱処理を施す。これにより、各多結晶シリコン膜206,206aをシリサイド化(低抵抗化と把握できる)される。

【0157】

ここで、多結晶シリコン206aはシリサイド金属の拡散を抑制する。したがって、第一のゲート電極G11側においては、多結晶シリコン206aはすべてシリサイド化されない。つまり、図29に示すように、第一のゲート構造G11は、ゲート絶縁膜203、P−metal204、不純物イオンが注入された多結晶ポリシリコン膜206aおよびシリサイド膜217の積層構造となる。なお、第二のゲート構造G12は、ゲート絶縁膜203およびフルシリサイド膜217の積層構造となる。

【0158】

また、上記シリサイド化金属としては、Ni以外に、Pt、Ti、Co、Hf、Ta、Yb、Er、およびAlなどが挙げられ、これらのいずれか一つ以上を含むことが望ましい。

【0159】

多結晶シリコン膜206aが形成される場合においても、P−metal204の膜厚が5nm以上であれば、PMISトランジスタは所望の仕事関数を示す。したがって、当該P−metal204の上層の電極構造に関わらず、PMISトランジスタは、所望の閾値電圧動作が可能である。このため、P−metal204の上層の組成は閾値電圧制御には関わらず、シリサイド膜217の組成を所望の組成に制御する必要が無い。つまり、第一のゲート構造G11を構成するシリサイド膜217と第二のゲート構造G12を構成するシリサイド膜217とは、共に同じ組成であっても良い。

【0160】

なお、シリサイド膜217の形成に際して、ニッケルシリサイド214は、層間絶縁膜216により覆われている。したがって、当該シリサイド膜217の形成により、当該ニッケルシリサイド214が、再シリサイド化されたり、エッチングダメージを受けたりすることを防止できる。よって、所望のデバイス特性を維持できる。

【0161】

また、上記シリサイド膜217の形成に際して、シリサイド化金属膜厚、シリサイド化熱処理条件、熱処理を施すタイミング、未反応シリサイド化金属除去のタイミング等を制御する。これにより、第一のゲート構造G11および第二のゲート構造G12を構成するシリサイド膜217を、シリサイド金属含有量の少ないフルシリサイドとすることできる。シリサイド金属含有量の少ないシリサイドとは、NiSiまたはNiSi2等の組成を有するシリサイド膜である。

【0162】

このように、少なくともNMISトランジスタを構成する第二のゲート構造G12において、フルシリサイド膜217をシリサイド金属含有量の少ないフルシリサイドとする。これにより、NMISトランジスタ側においても、所望の閾値電圧動作が可能となる。

【0163】

上記シリサイド膜217形成後、層間絶縁膜を積み増しし、CMP処理による平坦化、コンタクトプラグ形成等のフローを経て、通常のバックエンドフローを実施する。以上により、CMISトランジスタが完成する。

【0164】

本実施の形態では上記工程が実施されるので、実施の形態2で説明した効果に加えて、次のような効果も有する。

【0165】

具体的に、本実施の形態では、第一のゲート構造G11を構成する多結晶シリコン206のシリサイド化前に、当該多結晶シリコン206に対して、燐、砒素、および酸素のうち、少なくとも1つをイオン注入している。

【0166】

したがって、当該イオン注入された多結晶シリコン膜206aの形成により、多結晶シリコン膜206aのシリサイド化の際に、シリサイド金属の半導体基板201方向への拡散を抑制できる。具体的に、P−metal204へのシリサイド金属の侵入を抑制できる。これにより、PMISトランジスタ側において、仕事関数を変化させる等の影響がなくなり、安定したCMISデバイスが実現可能となる。

【0167】

なお、当該イオン注入処理を施すことにより、第一のゲート構造G11は、ゲート絶縁膜203、P−metal204、不純物イオンが注入された多結晶ポリシリコン膜206aおよびシリサイド膜217が当該順に積層した、積層構造となる。

【0168】

また、半導体膜206として、多結晶シリコンの代わりに、ゲルマニウム膜やシリコンゲルマニウム膜を用いても良い。この場合、低抵抗化処理により、半導体膜206は、ジャーマナイトゲート等となる。

【0169】

<実施の形態5>

本実施の形態に係るCMISトランジスタの製造方法は、実施の形態1に係るCMISトランジスタの製造方法の応用形態である。本実施の形態に係る製造方法を、工程断面図を用いて説明する。

【0170】

図1に示した半導体基板101を用意する。実施の形態1で説明したように、第一の領域S10には、NMISトランジスタが形成され、第二の領域S20には、PMISトランジスタが形成される。イオン注入処理により、半導体基板101内には、N型のウエル領域およびP型のウエル領域が形成される(図1では図示せず)。

【0171】

次に、第一の領域S10の半導体基板101上に、ゲート絶縁膜103と金属膜(N−metal)104と上層金属膜404と半導体膜(多結晶シリコン膜)106とが当該順に積層した積層構造である、第一のゲート構造G31を形成する。また、第二の領域S20記半導体基板101上に、ゲート絶縁膜103と半導体膜(多結晶シリコン膜)106とが当該順に積層した積層構造である、第二のゲート構造G2を形成する。

【0172】

ここで、第一のゲート構造G31は、NMISトランジスタの構成要素である。また、第二のゲート構造G2は、PMISトランジスタの構成要素である。後述において、具体的な第一のゲート構造G31および第二のゲート構造G2の製造方法を、図30から図33を用いて説明する。

【0173】

まず、実施の形態1で説明したように、第一の領域S10および第二の領域S20の半導体基板101上に、ハフニウムシリケイト膜から成るゲート絶縁膜103を形成する(図30)。次に、実施の形態1と同様に、ゲート絶縁膜103上にN−metal104を形成する(図30)。N−metal104の膜厚は、5nm〜30nm程度であり、たとえば10nmである。

【0174】

次に、本実施の形態では、N−metal104上に、上層金属膜404を形成する(図30)。当該上層金属膜404は、N−metal104の酸化防止膜として機能する。当該機能を有する上層金属膜404として、たとえばTiN、TaN、およびHfNのいずれかが適している。

【0175】

次に、上層金属膜404上に、所定のパターンのレジスト105を形成する(図31)。図31に示すように、パターニング後のレジスト105は、第一の領域S10にのみ残存する。次に、パターニング後のレジスト105をマスクとして使用して、上層金属膜404およびN−metal104に対してウェットエッチ等を施す。これにより、図31に示すように、第二の領域S20に形成されていた、上層金属膜404およびN−metal104が除去される。

【0176】

第一の領域S10からレジスト105を除去した後、上層金属膜404上およびゲート絶縁膜103上に、実施の形態1で示したシリコン膜106を成膜する(図32)。次に、図32に示すように、多結晶シリコン膜106上に、実施の形態1で示したゲートハードマスク107を形成する。なお、図32から分かるように、多結晶シリコン膜106およびゲートハードマスク107は、第一の領域S10および第二の領域S20の両方に形成されている。

【0177】

次に、ゲート絶縁膜103、N−metal104、上層金属膜404、多結晶シリコン膜106およびゲートハードマスク107に対して、ドライエッチング、ウェットエッチング等を施す。これにより、図33に示すように、第一の領域S10の半導体基板101上には、第一のゲート構造G31が形成され、第二の領域S20の半導体基板101上には、第二のゲート構造G2が形成される。

【0178】

ここで、第一のゲート構造G31は、ゲート絶縁膜103、N−metal104、上層金属膜404および多結晶シリコン膜106とが当該順に積層された積層構造である(図33)。他方、第二のゲート構造G2は、ゲート絶縁膜103および多結晶シリコン膜106とが当該順に積層された積層構造である(図33)。また、第一のゲート構造G31上および第二のゲート構造G2上には、各々ゲートハードマスク107が形成されている(図33)。

【0179】

以後、実施の形態1と同様に、ソース・ドレイン領域108,112,109,113の形成、サイドウォール膜110,111の形成、ニッケルシリサイド114形成、層間ライナー膜115と層間絶縁膜116の形成、および多結晶シリコン膜106のフルシリサイド化処理等を実施する。

【0180】

これにより、図34に示す構造が形成される。図34に示すように、第一のゲート構造G31は、ゲート絶縁膜103、N−metal104、上層金属膜404およびフルシリサイド膜117の積層構造となり、第二のゲート構造G2は、ゲート絶縁膜103およびフルシリサイド膜117の積層構造となる。なお、実施の形態1で説明したように、第二のゲート構造G2を構成するフルシリサイド膜117は、シリサイド金属含有量の多いフルシリサイドである。

【0181】

上記フルシリサイド膜117形成後、層間絶縁膜を積み増しし、CMP処理による平坦化、コンタクトプラグ形成等のフローを経て、通常のバックエンドフローを実施する。以上により、CMISトランジスタが完成する。

【0182】

本実施の形態では上記工程が実施されるので、実施の形態1で説明した効果に加えて、次のような効果も有する。

【0183】

具体的に、本実施の形態では、ゲート絶縁膜103、N−metal104、上層金属膜404、および多結晶シリコン膜106(後に、フルシリサイド膜117となる)とが当該順に積層した積層構造である、第一のゲート構造G31を形成する工程を含んでいる。ここで、上層金属膜404は、TiN、TaN、およびHfNのいずれかである。

【0184】

したがって、N−metal104上に上層金属膜404が形成されているので、多結晶シリコン106のフルシリサイド化処理の際に、シリサイド金属がN−metal104中に侵入することを抑制できる。さらに、上層金属膜404は、TiN、TaN、およびHfN等であるので、N−metal104の酸化防止層として機能する。よって、N−metal104がウェハプロセス中に変質することを防止できる。以上により、安定したデバイス特性が実現できる。

【0185】

また、半導体膜106として、多結晶シリコンの代わりに、ゲルマニウム膜やシリコンゲルマニウム膜を用いても良い。この場合、低抵抗化処理により、半導体膜106は、フルジャーマナイトゲート等となる。

【0186】

<実施の形態6>

本実施の形態に係るCMISトランジスタの製造方法は、実施の形態2に係るCMISトランジスタの製造方法の応用形態である。本実施の形態に係る製造方法を、工程断面図を用いて説明する。

【0187】

図15に示した半導体基板201を用意する。実施の形態2で説明したように、第一の領域S30には、PMISトランジスタが形成され、第二の領域S40には、NMISトランジスタが形成される。イオン注入処理により、半導体基板201内には、N型のウエル領域およびP型のウエル領域が形成される(図15では図示せず)。

【0188】

次に、第一の領域S30の半導体基板201上に、ゲート絶縁膜203と金属膜(P−metal)204と上層金属膜504と半導体膜(多結晶シリコン膜)206とが当該順に積層した積層構造である、第一のゲート構造G41を形成する。また、第二の領域S40記半導体基板201上に、ゲート絶縁膜203と半導体膜(多結晶シリコン膜)206とが当該順に積層した積層構造である、第二のゲート構造G12を形成する。

【0189】

ここで、第一のゲート構造G41は、PMISトランジスタの構成要素である。また、第二のゲート構造G12は、NMISトランジスタの構成要素である。後述において、具体的な第一のゲート構造G41および第二のゲート構造G12の製造方法を、図35から図38を用いて説明する。

【0190】

まず、実施の形態2で説明したように、第一の領域S30および第二の領域S40の半導体基板201上に、ハフニウムシリケイト膜から成るゲート絶縁膜203を形成する(図35)。次に、実施の形態2と同様に、ゲート絶縁膜203上にP−metal204を形成する(図35)。P−metal204の膜厚は、5nm〜30nm程度であり、たとえば10nmである。

【0191】

次に、本実施の形態では、P−metal204上に、上層金属膜504を形成する(図35)。当該上層金属膜504は、P−metal204の酸化防止膜として機能する。当該機能を有する上層金属膜504として、たとえばTiN、TaN、およびHfNのいずれかが適している。

【0192】

次に、上層金属膜504上に、所定のパターンのレジスト205を形成する(図36)。図36に示すように、パターニング後のレジスト205は、第一の領域S30にのみ残存する。次に、パターニング後のレジスト205をマスクとして使用して、上層金属膜504およびP−metal204に対してウェットエッチ等を施す。これにより、図36に示すように、第二の領域S40に形成されていた、上層金属膜504およびP−metal204が除去される。

【0193】

第一の領域S30からレジスト205を除去した後、上層金属膜504上およびゲート絶縁膜203上に、実施の形態2で示した多結晶シリコン膜206を成膜する(図37)。次に、図37に示すように、多結晶シリコン膜206上に、実施の形態2で示したゲートハードマスク207を形成する。なお、図37から分かるように、多結晶シリコン膜206およびゲートハードマスク207は、第一の領域S30および第二の領域S40の両方に形成されている。

【0194】

次に、ゲート絶縁膜203、P−metal204、上層金属膜504、多結晶シリコン膜206およびゲートハードマスク207に対して、ドライエッチング、ウェットエッチング等を施す。これにより、図38に示すように、第一の領域S30の半導体基板201上には、第一のゲート構造G41が形成され、第二の領域S40の半導体基板201上には、第二のゲート構造G12が形成される。

【0195】

ここで、第一のゲート構造G41は、ゲート絶縁膜203、P−metal204、上層金属膜504および多結晶シリコン膜206とが当該順に積層された積層構造である(図38)。他方、第二のゲート構造G12は、ゲート絶縁膜203および多結晶シリコン膜206とが当該順に積層された積層構造である(図38)。また、第一のゲート構造G41上および第二のゲート構造G12上には、各々ゲートハードマスク207が形成されている(図38)。

【0196】

以後、実施の形態2と同様に、ソース・ドレイン領域208,212,209,213の形成、サイドウォール膜210,211の形成、ニッケルシリサイド214形成、層間ライナー膜215と層間絶縁膜216の形成、および多結晶シリコン膜206のフルシリサイド化処理等を実施する。

【0197】

これにより、図39に示す構造が形成される。図39に示すように、第一のゲート構造G41は、ゲート絶縁膜203、P−metal204、上層金属膜504およびフルシリサイド膜217の積層構造となり、第二のゲート構造G12は、ゲート絶縁膜203およびフルシリサイド膜217の積層構造となる。なお、実施の形態2で説明したように、第二のゲート構造G12を構成するフルシリサイド膜217は、シリサイド金属含有量の少ないフルシリサイドである。

【0198】

上記フルシリサイド膜217形成後、層間絶縁膜を積み増しし、CMP処理による平坦化、コンタクトプラグ形成等のフローを経て、通常のバックエンドフローを実施する。以上により、CMISトランジスタが完成する。

【0199】

本実施の形態では上記工程が実施されるので、実施の形態2で説明した効果に加えて、次のような効果も有する。

【0200】

具体的に、本実施の形態では、ゲート絶縁膜203、P−metal204、上層金属膜504、および多結晶シリコン膜206(後に、フルシリサイド膜217となる)とが当該順に積層した積層構造である、第一のゲート構造G41を形成する工程を含んでいる。ここで、上層金属膜504は、TiN、TaN、およびHfNのいずれかである。

【0201】

したがって、P−metal204上に上層金属膜504が形成されているので、多結晶シリコン206のフルシリサイド化処理の際に、シリサイド金属がP−metal204中に侵入することを抑制できる。さらに、上層金属膜504は、TiN、TaN、およびHfN等であるので、P−metal204の酸化防止層として機能する。よって、P−metal204がウェハプロセス中に変質することを防止できる。以上により、安定したデバイス特性が実現できる。

【0202】

また、半導体膜206として、多結晶シリコンの代わりに、ゲルマニウム膜やシリコンゲルマニウム膜を用いても良い。この場合、低抵抗化処理により、半導体膜206は、フルジャーマナイトゲート等となる。

【0203】

上記各実施の形態に記載のCMISトランジスタの形成方法は、45nmノード以降のシリコン半導体集積回路製品の全てが対象となる。特に、トランジスタの電流駆動能力の向上が望まれるものに適する。具体的に、本発明は、高速動作を求められるロジック回路の製造方法に適する。

【図面の簡単な説明】

【0204】

【図1】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図2】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図3】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図4】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図5】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図6】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図7】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図8】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図9】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図10】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図11】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図12】従来技術に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図13】従来技術に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図14】従来技術に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図15】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図16】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図17】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図18】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図19】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図20】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図21】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図22】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図23】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図24】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図25】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図26】実施の形態3に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図27】実施の形態3に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図28】実施の形態4に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図29】実施の形態4に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図30】実施の形態5に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図31】実施の形態5に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図32】実施の形態5に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図33】実施の形態5に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図34】実施の形態5に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図35】実施の形態6に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図36】実施の形態6に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図37】実施の形態6に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図38】実施の形態6に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図39】実施の形態6に係るCMISトランジスタの製造方法を説明する工程断面図である。

【符号の説明】

【0205】

101,201 半導体基板、103,203 ゲート絶縁膜、104 金属膜(N−metal)、106,206 多結晶シリコン(半導体膜)、106a,206a イオン注入された多結晶シリコン、114,214 ニッケルシリサイド、117,217 フルシリサイド膜(シリサイド膜)、204 金属膜(P−metal)、404,504 上層金属膜、G1,G11 第一のゲート構造、G2,G12 第二のゲート構造、S10,S30 第一の領域、S20,S40 第二の領域。

【技術分野】

【0001】

この発明は、半導体基板1にPMISトランジスタとNMISトランジスタとが形成されたCMISトランジスタの製造方法に係る発明である。

【背景技術】

【0002】

MISトランジスタのゲート電極に多結晶シリコンを用いる場合には、ゲート空乏化現象により、実効的なゲート絶縁膜厚を増加させる。当該実効的なゲート絶縁膜の増加は、トランジスタの性能向上を妨げる。上記ゲート空乏化を抑えてMISトランジスタの性能向上を図るには、ゲート電極材料として、多結晶シリコンの代わりに、金属やシリサイド材料を用いる。特に、ゲート多結晶シリコンを全てシリサイド化するフルシリサイド(FUSI:Fully Silicide)ゲート構造が有効である。当該FUSI化ゲート構造は、従来のトランジスタ作製フローとの整合性が良く、上記ゲート空乏化抑制に対しても効果的である。

【0003】

FUSIゲート構造を有するトランジスタにおいて、ゲート絶縁膜として高誘電率(high−k)絶縁膜(たとえばHfSiONなど)を用いる場合には、シリサイドの組成を変えて閾値電圧Vthを制御する手法が提唱されている(たとえば、非特許文献1)。

【0004】

シリサイド金属材料としてニッケルを用いたとする。この場合、NiSi(ニッケルモノシリサイド)よりもニッケル含有率が高いNi3Si(トリニッケルシリサイド)から成るFUSIゲートの実効仕事関数は、NiSiから成るFUSIゲートの実効仕事関数と比べて約0.35eV程度高い。上記非特許文献1では、前記シリサイド組成に応じて実行仕事関数が変化する現象を利用している。具体的に、NMISトランジスタには、NiSiをFUSIゲート材料として用いる。また、PMISトランジスタには、Ni3Si等のNi含有率の高いニッケルシリサイドをFUSIゲート材料として用いる。これにより、当該非特許文献1では、低閾値電圧Vthデバイスを実現することができると提唱している。

【0005】

上記シリサイド相制御したFUSIゲート電極を形成する方法としては、たとえば次のような製造方法が挙げられる。つまり、PMISトランジスタ側およびNMISトランジスタ側の両ゲート構造において、同じ膜厚である多結晶シリコン膜を形成する。その後、たとえばPMISトランジスタ側の多結晶シリコン膜の膜厚を削減(薄膜化)する。そして、PMISトランジスタ側およびNMISトランジスタ側の両ゲート構造において、多結晶シリコン膜を各々シリサイド化する。

【0006】

当該製造方法により、NMISトランジスタ側では、シリサイド金属含有量の少ないフルシリサイド層が形成される。他方、PMISトランジスタ側では、シリサイド金属含有量の多いフルシリサイド層が形成される。当該製造方法を採用した場合には、PMISトランジスタ側とNMISトランジスタ側とで、組成の異なるFUSIゲート構造を同時に形成できるという利点がある。

【0007】

【非特許文献1】K.Takahashi et al.,IEDM2004 Tech.Dig.,pp91

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかし、上記例示した製造方法の場合には、以下のような問題点が生じる。

【0009】

第一の問題としてに、フルシリサイド層の組成のバラツキが挙げられる。

【0010】

NMISトランジスタ側にシリサイド金属含有量の少ないフルシリサイド層を形成する際、ゲート長の大きさ違いにより、形成されるフルシリサイド層の組成が異なることが懸念される。たとえばゲート長=1μm程度の場合では、多結晶シリコンゲート露出面積が大きい。したがって、この場合では、シリサイド化金属と多結晶シリコンは理想的な状態(シリサイド化金属とシリコンが1対1に反応が進んでいく状態)で反応する。

【0011】

一方、たとえばゲート長=40nm程度の場合では、多結晶シリコンゲート露出面積が小さい。したがって、この場合では、ゲート中央部に比べてゲートエッジ部におけるシリサイド化金属の拡散量が相対的に多くなる。よって、所望の組成に比べてシリサイド化金属含有量の多いフルシリサイド相が、形成される可能性が高くなる。

【0012】

このように、ゲート長に依存して、フルシリサイド相が異なったトランジスタが形成される。フルシリサイド層の組成のバラツキは、閾値電圧のバラツキを発生させる要因となる。

【0013】

第二の問題として、トランジスタのゲート形状の不安定化が挙げられる。

【0014】

PMISトランジスタおよびNMISトランジスタにおいて、フルシリサイドゲートを同じNi体積膜厚、同じシリサイド化熱処理条件で形成する場合を想定する。この場合には、シリサイド金属含有量の多いPMISトランジスタ側の多結晶シリコンゲートは、予め薄膜化する必要がある。具体的に、シリサイド化金属堆積前に、PMISトランジスタ側において多結晶シリコンゲート電極のみを、既存のウェットエッチ処理やドライエッチ処理によりエッチバックする手法が必要である。

【0015】

しかし、上記手法では、PMISトランジスタ側とNMISトランジスタ側とで、ゲート高さが大きく異なるという不具合が起こる。たとえば、多結晶シリコンの初期膜厚が100nmの場合、PMISトランジスタ側の多結晶シリコンを35nm程度までエッチバックする。これにより、PMISトランジスタ側では、シリサイド化金属含有率の高いフルシリサイドゲートが形成される。しかし、NMISトランジスタ側のゲート構造と比べて、約60nm以上の高さバラツキが発生し、トランジスタのゲート形状が不安定なものとなる。

【0016】

そこで、本発明は、PMISトランジスタ側とNMISトランジスタ側とでシリサイド層の組成のバラツキを防止でき、またトランジスタのゲート形状の不安定化を防止できる、CMISトランジスタの製造方法を提供することを目的とする。

【課題を解決するための手段】

【0017】

本発明に係る1の実施の形態においては、ゲート絶縁膜と金属膜と半導体膜とが当該順に積層した第一のゲート構造を形成する。さらに、ゲート絶縁膜と半導体膜とが当該順に積層した第二のゲート構造を形成する。そして、第一のゲート構造および第二のゲート構造をマスクした状態で、各ゲート構造の両脇における半導体基板上を、低抵抗化させる。そして、第一のゲート構造を構成する半導体膜および第二のゲート構造を構成する半導体膜を低抵抗化させる。

【発明の効果】

【0018】

上記実施の形態によれば、たとえばPMISトランジスタ側とNMISトランジスタ側とでシリサイド層の組成のバラツキを防止でき、またトランジスタのゲート形状の不安定化を防止できる。

【0019】

また、活性領域の低抵抗化と半導体膜の低抵抗化とを、別工程で行うことにより、半導体膜の低抵抗化の制御も容易に成る。

【発明を実施するための最良の形態】

【0020】

以下、この発明をその実施の形態を示す図面に基づいて具体的に説明する。

【0021】

<実施の形態1>

本実施の形態に係るCMIS(Complementary Metal Insulation Semiconductor)トランジスタの製造方法を、工程断面図を用いて説明する。

【0022】

まず、図1に示すように、第一の領域S10と第二の領域S20とを有する半導体基板101を用意する。半導体基板101は、たとえば、シリコンの(100)面をエピタキシャル成長させることにより形成される。

【0023】

ここで、第一の領域S10の半導体基板101の上面内には、第一の導電型の第一のMISトランジスタが形成される。第二の領域S20の半導体基板101の上面内には、第二の導電型の第二のMISトランジスタが形成される。本実施の形態では、第一の導電型は、「N型」とする。また、第二の導電型は、「P型」とする。したがって、本実施の形態では、第一のMISトランジスタはNMISトランジスタであり、第二のMISトランジスタはPMISトランジスタである。

【0024】

また、NMISトランジスタとPMISトランジスタとは、分離酸化膜(STI:Shallow Trench Isolation)102により、電気的に分離されている。当該分離酸化膜102は、半導体基板101に対する部分的エッチング、酸化膜の堆積、および平坦化処理を組み合わせることにより、半導体基板101の表面内に形成される。

【0025】

また、通常の各導電型のイオン注入処理により、半導体基板101内には、N型のウエル領域およびP型のウエル領域が形成される(図1では図示せず)。

【0026】

次に、第一の領域S10の半導体基板101上に、ゲート絶縁膜103と金属膜104と半導体膜106とが当該順に積層した積層構造である、第一のゲート構造G1を形成する。また、第二の領域S20記半導体基板101上に、ゲート絶縁膜103と半導体膜106とが当該順に積層した積層構造である、第二のゲート構造G2を形成する。

【0027】

ここで、第一のゲート構造G1は、NMISトランジスタの構成要素である。また、第二のゲート構造G2は、PMISトランジスタの構成要素である。後述において、具体的な第一のゲート構造G1および第二のゲート構造G2の製造方法を、図2から図5を用いて説明する。

【0028】

まず、CVD(Chemical Vapor Deposition)法等により、第一の領域S10および第二の領域S20の半導体基板101の上面に、ゲート絶縁膜103を形成する(図2)。ゲート絶縁膜103として、たとえばハフニウムシリケイト膜(HfSiOまたはHfSiON)などを採用できる。

【0029】

次に、たとえばCVD法により、図2に示すように、ゲート絶縁膜103上に金属膜104を形成する。本実施の形態では、金属膜104は、N型の仕事関数を有する金属である。以後、本実施の形態では、金属膜104をN−metal104と称する。

【0030】

ここで、N型の仕事関数を有する金属とは、シリコンの伝導帯(Conduction Band:Ec=4.05eV)端近傍のエネルギーに相当する仕事関数を有する材料のことである。具体的には、N型の仕事関数を有する金属とは、その仕事関数値が4.05±0.3eVの範囲ある材料のことを指す。当該N−metal104の材料として、たとえば、Ta系化合物(Ta、TaN、TaC、TaSiN等)やHf系化合物(Hf、HfN、HfC、HfSiN等)が挙げられる。なお、当該N−metal104の膜厚は、5〜30nm程度の範囲内が好ましく、たとえば10nm程度とする。

【0031】

次に、N−metal104上に、レジスト105を形成する。その後、通常のリソグラフィ工程により、レジスト105をパターニングする。ここで、図3に示すように、パターニング後のレジスト105は、第一の領域S10にのみ残存する。換言すれば、第二の領域S20のレジスト105は除去される。次に、パターニング後のレジスト105をマスクとして使用して、N−metal104に対してウェットエッチ等を施す。これにより、図3に示すように、第二の領域S20に形成されていたN−metal104が除去される。

【0032】

第一の領域S10からレジスト105を除去した後、CVD法等により、N−metal104上およびゲート絶縁膜103上に、シリコン膜(半導体膜と把握できる)106を成膜する(図4)。シリコン膜106は、成膜時には、多結晶状でもアモルファス状でも良い。シリコン膜106は、この後に行われる活性化熱処理により、多結晶シリコン膜106となる。ここで、シリコン膜106の膜厚は、たとえば100nm程度とする。

【0033】

次に、図4に示すように、シリコン膜106上に、シリコン酸化膜やシリコン窒化膜等のゲートハードマスク107を形成する。後述するように、ソース・ドレイン領域のシリサイド化工程後に、別途、多結晶シリコン膜106をフルシリサイド化させる。当該ソース・ドレイン領域のシリサイド化工程において、多結晶シリコン膜106がシリサイド化されないように、当該ゲートハードマスク107は、多結晶シリコン膜106の保護膜として機能する。

【0034】

なお、図4から分かるように、シリコン膜106およびゲートハードマスク107は、第一の領域S10および第二の領域S20の両方に形成されている。

【0035】

次に、ゲート絶縁膜103、N−metal104、シリコン膜106およびゲートハードマスク107に対して、ドライエッチング、ウェットエッチング等を施す。これにより、図5に示すように、第一の領域S10の半導体基板101上には、第一のゲート構造G1が形成され、第二の領域S20の半導体基板101上には、第二のゲート構造G2が形成される。

【0036】

ここで、第一のゲート構造G1は、ゲート絶縁膜103、N−metal104およびシリコン膜106とが当該順に積層された積層構造である(図5)。他方、第二のゲート構造G2は、ゲート絶縁膜103およびシリコン膜106とが当該順に積層された積層構造である(図5)。また、第一のゲート構造G1上および第二のゲート構造G2上には、各々ゲートハードマスク107が形成されている(図5)。

【0037】

次に、第二の領域S20をマスクし、第一のゲート構造G1の両脇における半導体基板101に対して、N型の不純物イオンを注入する。当該イオン注入により、第一のゲート構造G1の両脇における半導体基板101には、比較的浅い不純物イオン注入領域108が形成される(図6)。

【0038】

他方、第一の領域S10をマスクして、第二のゲート構造G2の両脇における半導体基板101に対して、P型の不純物イオンを注入する。当該イオン注入により、第二のゲート構造G2の両脇における半導体基板101には、比較的浅い不純物イオン注入領域109が形成される(図6)。

【0039】

次に、第一のゲート構造G1および第二のゲート構造G2を覆うように、半導体基板101上に、シリコン酸化膜110およびシリコン窒化膜111を当該順に成膜する。その後、シリコン酸化膜110およびシリコン窒化膜111に対して、異方性エッチング処理を実施する。これにより、図7に示すように、第一のゲート構造G1の両側面および第二のゲート構造G2両側面には、積層構造のサイドウォール膜110,111が形成される。

【0040】

次に、第二の領域S20をマスクし、第一のゲート構造G1の両脇における半導体基板101に対して、N型の不純物イオンを再び注入する。当該イオン注入により、第一のゲート構造G1の両脇における半導体基板101には、比較的深い不純物イオン注入領域112が形成される(図8)。

【0041】

他方、第一の領域S10をマスクして、第二のゲート構造G2の両脇における半導体基板101に対して、P型の不純物イオンを再び注入する。当該イオン注入により、第二のゲート構造G2の両脇における半導体基板101には、比較的深い不純物イオン注入領域113が形成される(図8)。

【0042】

次に、不純物イオン注入領域108,109,112,113を活性化するために、図8に示した構造体に対して、熱処理を施す。これにより、第一のゲート構造G1の両脇における半導体基板101の表面内には、NMISトランジスタを構成するソース・ドレイン領域108,112が形成される。他方、第二のゲート構造G2の両脇における半導体基板101の表面内には、PMISトランジスタを構成するソース・ドレイン領域109,113が形成される。なお、活性化のための熱処理により、シリコン膜106は多結晶シリコン106となる。

【0043】

次に、第一のゲート構造G1および第二のゲート構造G2をマスクした状態で、ソース・ドレイン領域108,109,112,113を低抵抗化させる工程を実施する。

【0044】

具体的に、第一のゲート構造G1および第二のゲート構造G2を覆うように、半導体基板101上に、ニッケル膜を成膜する。そして、シリサイド化(低抵抗化と把握できる)処理を実施する。その後、未反応のニッケル膜を除去する。以上により、図9に示すように、ソース・ドレイン領域108,109,112,113の表面内には、ニッケルシリサイド114が形成される。つまり、当該ニッケルシリサイド114の形成により、第一のゲート構造G1の両脇における半導体基板101の上面および第二のゲート構造G2の両脇における半導体基板101の上面は、低抵抗化される。

【0045】

ここで、第一のゲート構造G1および第二のゲート構造G2の上面には、各々ゲートハードマスク107が形成されている。また、第一のゲート構造G1および第二のゲート構造G2の両側面には、各々サイドウォール膜110,111が形成されている。したがって、ゲートハードマスク107およびサイドウォール膜110,111はキャップ層として機能し、多結晶シリコン膜106はシリサイド化されない。

【0046】

次に、第一のゲート構造G1および第二のゲート構造G2を覆うように、半導体基板101上に、層間ライナー膜115および層間絶縁膜116を当該順に形成する(図10)。

【0047】

次に、第一のゲート電極G1を構成する多結晶シリコン膜106の上面、および第二のゲート電極G2を構成する多結晶シリコン膜106の上面を露出させる。その後、前記各多結晶シリコン膜(上述したように、半導体膜と把握できる)106を低抵抗化させる処理を実施する。

【0048】

具体的に、露出している各多結晶シリコン膜106の上面に、シリサイド化金属(たとえば、Ni等)を堆積する。その後、当該シリサイド化金属堆積後の半導体基板101に対して、熱処理を施す。これにより、各多結晶シリコン膜106をフルシリサイド化(低抵抗化と把握できる)される。つまり、図11に示すように、第一のゲート構造G1は、ゲート絶縁膜103、N−metal104およびフルシリサイド膜117の積層構造となり、第二のゲート構造G2は、ゲート絶縁膜103およびフルシリサイド膜117の積層構造となる。

【0049】

なお、上記シリサイド化金属としては、Ni以外に、Pt、Ti、Co、Hf、Ta、Yb、Er、およびAlなどが挙げられ、これらのいずれか一つ以上を含むことが望ましい。

【0050】

ここで、N−metal104の膜厚が5nm以上あれば、当該N−metal104は上記所望の仕事関数を示す。N−metal104が当該所望の仕事関数を有すれば、NMISトランジスタは、所望の閾値電圧動作が可能となる。このため、N−metal104の上層の組成は閾値電圧制御には関わらず、フルシリサイド膜117の組成を所望の組成に制御する必要が無い。つまり、第一のゲート構造G1を構成するフルシリサイド膜117と第二のゲート構造G2を構成するフルシリサイド膜117とは、共に同じ組成であっても良い。

【0051】

背景技術で説明した方法では、NMISトランジスタ側とPMISトランジスタ側で、組成の異なるシリサイド膜を形成する必要がある。そのため、NMISトランジスタ側の多結晶シリコン膜の膜厚とPMIS多結晶シリコン膜の膜厚とを、異ならせる処理が必要であった。

【0052】

しかし、本実施の形態に係る方法では、上記の通り、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜117の組成を作り分ける必要が無い。つまり、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜117の組成が同じであっても良い。このため、背景技術で説明したような、他方のMISトランジスタを構成する多結晶シリコン膜を、選択的にエッチングする必要も無い。

【0053】

なお、フルシリサイド膜117の形成に際して、ソース・ドレイン領域のニッケルシリサイド114は、層間絶縁膜116により覆われている。したがって、当該フルシリサイド膜117の形成により、当該ニッケルシリサイド114が、再シリサイド化されたり、エッチングダメージを受けたりすることを防止できる。よって、所望のデバイス特性を維持できる。

【0054】

また、上記フルシリサイド膜117の形成に際して、シリサイド化金属膜厚、シリサイド化熱処理条件、熱処理を施すタイミング、未反応シリサイド化金属除去のタイミング等を制御する。これにより、第一のゲート構造G1および第二のゲート構造G2を構成するフルシリサイド膜117を、シリサイド金属含有量の多いフルシリサイドとすることできる。シリサイド金属含有量の多いフルシリサイドとは、Ni3Si、Ni31Si12、およびNi2Siのいずれかの組成を有するフルシリサイド膜である。

【0055】

たとえば、50nmの膜厚を有する多結晶シリコン膜106に対して、シリサイド金属膜として、Ni膜を70nm以上の膜厚で堆積する。その後、Ni膜形成後の半導体基板101に対して1回目の熱処理を施す。ここで、当該1回目の熱処理は、400℃以下、30秒程度の条件で実施される。当該1回目の熱処理により、多結晶シリコン膜106とNi膜を反応させる。次に未反応Ni膜のみを選択ウェットエッチングにより除去する。その後、半導体基板101に対して2回目の熱処理を施す。当該2回目の熱処理は、500℃、30秒程度の条件で実施される。以上の形成条件により、シリサイド金属含有量の多いNiフルシリサイド層(この場合、Ni31Si12層)が形成される。

【0056】

このように、少なくともPMISトランジスタを構成する第二のゲート構造G2において、フルシリサイド膜117をシリサイド金属含有量の多いフルシリサイドとする。これにより、PMISトランジスタ側においても、所望の閾値電圧動作が可能となる。

【0057】

上記フルシリサイド膜117形成後、層間絶縁膜を積み増しし、CMP(Chemical Mechanical Polishing)処理による平坦化、コンタクトプラグ形成等のフローを経て、通常のバックエンドフローを実施する。以上により、CMISトランジスタが完成する。

【0058】

ところで、上記非特許文献1では、前記シリサイド組成に応じて実行仕事関数が変化する現象を利用している。具体的に、NMISトランジスタには、NiSiをFUSIゲート材料として用いる。また、PMISトランジスタには、Ni3Si等のNi含有率の高いニッケルシリサイドをFUSIゲート材料として用いる。これにより、当該非特許文献1では、低閾値電圧Vthデバイスを実現することができると提唱している。

【0059】

上記シリサイド相制御したFUSIゲート電極を形成する方法としては、たとえば次のような製造方法が挙げられる。

【0060】

つまり、PMISトランジスタ側およびNMISトランジスタ側の両ゲート構造において、同じ膜厚である多結晶シリコン膜1004,1005を形成する(図12)。その後、NMISトランジスタ側の多結晶シリコン膜1004をレジスト1016で覆い、PMISトランジスタ側の多結晶シリコン膜1005の膜厚を削減(薄膜化)する(図13)。そして、PMISトランジスタ側およびNMISトランジスタ側の両ゲート構造において、多結晶シリコン膜を各々シリサイド化する(図14)。

【0061】

当該製造方法により、NMISトランジスタ側では、シリサイド金属含有量の少ないフルシリサイド膜1018が形成される。他方、PMISトランジスタ側では、シリサイド金属含有量の多いフルシリサイド膜1019が形成される。当該製造方法を採用した場合には、PMISトランジスタ側とNMISトランジスタ側とで、組成の異なるFUSIゲート構造を同時に形成される。

【0062】

本実施の形態に係るCMISトランジスタの製造方法では、第一のゲート構造G1側には、ゲート絶縁膜103と多結晶シリコン膜106との間に、N−metal104を形成する工程を含んでいる。

【0063】

したがって、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜117の組成を作り分ける必要がなくなる。よって、多結晶シリコン膜106の低抵抗化(シリサイド化)処理前に、第一のゲート構造G1側と第二のゲート構造G2側とで、多結晶シリコン膜106の膜厚を異ならせる処理も不要となる。また、N−metal104の存在により、多結晶シリコン膜106の低抵抗化(シリサイド化)処理に際して、半導体基板101側からの拡散を考慮する必要がなくなる。したがって、フルシリサイド膜117の形成制御を容易にコントロールできる。

【0064】

なお、たとえば、NMISトランジスタ側とPMISトランジスタ側とで、同時に組成の異なるフルシリサイド膜を形成するとする。この場合、組成を安定形成できるプロセスウィンドウが狭いために、フルシリサイド組成のバラツキが問題視される。たとえば、NMISトランジスタ側において金属含有率の少ないフルシリサイド膜を形成しようとしても、局所的にNi反応量の多い箇所が現れ、シリサイド金属含有率の多いフルシリサイド相が形成されるという不具合が起こる。また逆に、P型のトランジスタ側において金属含有率の多いフルシリサイドゲートを形成しようとしても、局所的にNi反応量の少ない箇所が現れ、シリサイド金属含有率の少ないフルシリサイド相が形成されるという不具合が起こる。

【0065】

上記のように、本実施の形態では、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜117の組成を作り分ける必要がなくなる。したがって、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜117の形成に際して、同熱処理条件、同シリコン/シリサイド金属膜厚により、同一組成を作ることが可能となる。このため、プロセス制御ウィンドウは広がり、フルシリサイド膜117の組成のバラツキを防止できる。

【0066】

また、第一のゲート構造G1側と第二のゲート構造G2側とで、多結晶シリコン膜106の膜厚を異ならせる処理が必要な場合には、既存のサイドウォール110,111やオフセットスペーサ、および層間絶縁膜等もエッチングされることになる。これにより、Ni堆積前のゲート形状が悪化する、或いは、ソース・ドレイン領域108,109,112,113に形成されているNiシリサイド等が露出、変質する恐れ等がある。

【0067】

本実施の形態では、上記の通り、第一のゲート構造G1側と第二のゲート構造G2側とで、多結晶シリコン膜106の膜厚を異ならせる処理も不要である。したがって、MISトランジスタのゲート形状不安定化を防止することができる。

【0068】

以上の観点より、本実施の形態に係る製造方法により、良好な特性を有するデュアルメタルゲートデバイス(CMISデバイス)を容易に作成することが可能となる。

【0069】

また、本実施の形態に係るCMISトランジスタの製造方法では、ニッケルシリサイド114の形成処理と、フルシリサイド膜117の形成処理とを、各々別のシリサイド工程にて実施している。特に、ニッケルシリサイド114の形成処理後に、フルシリサイド膜117の形成を行っている。

【0070】

したがって、ソース・ドレイン領域108,109,112,113の低抵抗化と、フルシリサイド膜117を有するゲート構造G1,G2の閾値制御とを、同時に満たすことが可能である。また、ニッケルシリサイド114の形成処理の際に、多結晶シリコン膜106の一部をシリサイド化する場合よりも、上記別工程を採用する方が、フルシリサイド膜117の形成制御も容易に成る。

【0071】

また、本実施の形態に係るCMISトランジスタの製造方法では、金属膜104として、N−metal104を一層だけを形成している。したがって、金属膜104が複層である場合よりも、本実施の形態に係る方法の方が、より容易に、金属膜104のパターニングができる。つまり、本実施の形態に係る方法の方が、より容易に、第一のゲート構造G1を形成できる。

【0072】

また、本実施の形態に係るCMISトランジスタの製造方法では、各多結晶シリコン膜106を、フルシリサイド化させている。したがって、ゲート構造G1,G2の全体低抵抗化を図ることができる。

【0073】

また、本実施の形態に係るCMISトランジスタの製造方法では、金属膜104は、N型の仕事関数を有するN−metal(Ta化合物またはHf化合物)104である。NMISトランジスタは、所望の閾値電圧動作が可能となる。

【0074】

また、本実施の形態に係るCMISトランジスタの製造方法では、5〜30nm程度の膜厚のN−metal104を形成している。したがって、N−metal104が有する仕事関数を4.05±0.3eVの範囲とすることができる。これにより、NMISトランジスタは、所望の閾値電圧動作が可能となる。

【0075】

また、本実施の形態に係るCMISトランジスタの製造方法では、第二のゲート構造G2を構成する多結晶シリコン膜106を、Ni3Si、Ni31Si12、およびNi2Siのいずれかの組成に、シリサイド化させている。したがって、PMISトランジスタは、所望の閾値電圧動作が可能となる。

【0076】

また、本実施の形態に係るCMISトランジスタの製造方法では、多結晶シリコン膜106を、Ni、Pt、Ti、Co、Hf、Ta、Yb、Er、およびAlのうち、少なくとも1以上を含む金属を用いて、フルシリサイド化している。したがって、容易に、フルシリサイド膜117を形成することができる。

【0077】

なお、本実施の形態1では、半導体膜106として、多結晶シリコン膜106を用いた場合について記した。しかし、半導体膜106として、ゲルマニウム膜やシリコンゲルマニウム膜を用いても良い。この場合、低抵抗化処理により、半導体膜106は、フルジャーマナイトゲート等となる。

【0078】

このように、半導体膜106として、ゲルマニウム膜やシリコンゲルマニウム膜を用いることにより、低抵抗化後のゲート電極の仕事関数制御範囲が、多結晶シリコン膜を採用したときと比べて変化する。したがって、デバイスの仕様に応じて、材料を変えることにより所望の閾値電圧を有するデバイスが実現できる。

【0079】

<実施の形態2>

本実施の形態に係るCMISトランジスタの製造方法を、工程断面図を用いて説明する。

【0080】

まず、図15に示すように、第一の領域S30と第二の領域S40とを有する半導体基板201を用意する。半導体基板201は、たとえば、シリコンの(100)面をエピタキシャル成長させることにより形成される。

【0081】

ここで、第一の領域S30の半導体基板201の上面内には、第一の導電型の第一のMISトランジスタが形成される。第二の領域S40の半導体基板201の上面内には、第二の導電型の第二のMISトランジスタが形成される。本実施の形態では、第一の導電型は、「P型」とする。また、第二の導電型は、「N型」とする。したがって、本実施の形態では、第一のMISトランジスタはPMISトランジスタであり、第二のMISトランジスタはNMISトランジスタである。

【0082】

また、NMISトランジスタとPMISトランジスタとは、半導体基板202の表面内に形成された分離酸化膜202により、電気的に分離されている。当該分離酸化膜202の形成方法は、実施の形態1で説明した分離酸化膜102の形成方法と同じである。

【0083】

また、通常の各導電型のイオン注入処理により、半導体基板201内には、N型のウエル領域およびP型のウエル領域が形成される(図15では図示せず)。

【0084】

次に、第一の領域S30の半導体基板201上に、ゲート絶縁膜203と金属膜204と半導体膜206とが当該順に積層した積層構造である、第一のゲート構造G11を形成する。また、第二の領域S40記半導体基板201上に、ゲート絶縁膜203と半導体膜206とが当該順に積層した積層構造である、第二のゲート構造G12を形成する。

【0085】

ここで、第一のゲート構造G11は、PMISトランジスタの構成要素である。また、第二のゲート構造G12は、NMISトランジスタの構成要素である。後述において、具体的な第一のゲート構造G11および第二のゲート構造G12の製造方法を、図16から図19を用いて説明する。

【0086】

まず、CVD法等により、第一の領域S30および第二の領域S40の半導体基板201の上面に、ゲート絶縁膜203を形成する(図16)。ゲート絶縁膜203として、たとえばハフニウムシリケイト膜(HfSiOまたはHfSiON)などを採用できる。

【0087】

次に、たとえばCVD法により、図16に示すように、ゲート絶縁膜203上に金属膜204を形成する。本実施の形態では、金属膜204は、P型の仕事関数を有する金属である。以後、本実施の形態では、金属膜204をP−metal204と称する。

【0088】

ここで、P型の仕事関数を有する金属とは、シリコンの価電子帯(Valence Band:Ev=5.12eV)端近傍のエネルギーに相当する仕事関数を有する材料のことである。具体的には、P型の仕事関数を有する金属とは、その仕事関数値が5.17±0.3eVの範囲ある材料のことを指す。当該P−metal204の材料として、たとえば、Ti系化合物(TiN、TiAlN等)、W系化合物(W、WN等)、Ru系化合物(Ru、RuO2等)およびPt系化合物等が挙げられる。なお、当該P−metal204の膜厚は、5〜30nm程度の範囲内が好ましく、たとえば10nm程度とする。

【0089】

次に、P−metal204上に、レジスト205を形成する。その後、通常のリソグラフィ工程により、レジスト205をパターニングする。ここで、図17に示すように、パターニング後のレジスト205は、第一の領域S30にのみ残存する。換言すれば、第二の領域S40のレジスト205は除去される。次に、パターニング後のレジスト205をマスクとして使用して、P−metal204に対してウェットエッチ等を施す。これにより、図17に示すように、第二の領域S40に形成されていたP−metal204が除去される。

【0090】

第一の領域S30からレジスト205を除去した後、CVD法等により、P−metal204上およびゲート絶縁膜203上に、シリコン膜(半導体膜と把握できる)206を成膜する(図18)。シリコン膜206は、成膜時には、多結晶状でもアモルファス状でも良い。シリコン膜206は、この後に行われる活性化熱処理により、多結晶シリコン膜206となる。ここで、シリコン膜206の膜厚は、たとえば100nm程度とする。

【0091】

次に、図18に示すように、シリコン膜206上に、シリコン酸化膜やシリコン窒化膜等のゲートハードマスク207を形成する。後述するように、ソース・ドレイン領域のシリサイド化工程後に、別途、多結晶シリコン膜206をフルシリサイド化させる。当該ソース・ドレイン領域のシリサイド化工程において、多結晶シリコン膜206がシリサイド化されないように、当該ゲートハードマスク207は、多結晶シリコン膜206の保護膜として機能する。

【0092】

なお、図18から分かるように、シリコン膜206およびゲートハードマスク207は、第一の領域S30および第二の領域S40の両方に形成されている。

【0093】

次に、ゲート絶縁膜203、P−metal204、シリコン膜206およびゲートハードマスク207に対して、ドライエッチング、ウェットエッチング等を施す。これにより、図19に示すように、第一の領域S30の半導体基板201上には、第一のゲート構造G11が形成され、第二の領域S40の半導体基板201上には、第二のゲート構造G2が形成される。

【0094】

ここで、第一のゲート構造G11は、ゲート絶縁膜203、P−metal204およびシリコン膜206とが当該順に積層された積層構造である(図19)。他方、第二のゲート構造G12は、ゲート絶縁膜203およびシリコン膜206とが当該順に積層された積層構造である(図19)。また、第一のゲート構造G11上および第二のゲート構造G12上には、各々ゲートハードマスク207が形成されている(図19)。

【0095】

次に、第二の領域S40をマスクし、第一のゲート構造G11の両脇における半導体基板201に対して、P型の不純物イオンを注入する。当該イオン注入により、第一のゲート構造G11の両脇における半導体基板201には、比較的浅い不純物イオン注入領域208が形成される(図20)。

【0096】

他方、第一の領域S30をマスクして、第二のゲート構造G12の両脇における半導体基板201に対して、N型の不純物イオンを注入する。当該イオン注入により、第二のゲート構造G12の両脇における半導体基板201には、比較的浅い不純物イオン注入領域209が形成される(図20)。

【0097】

次に、第一のゲート構造G11および第二のゲート構造G12を覆うように、半導体基板201上に、シリコン酸化膜210およびシリコン窒化膜211を当該順に成膜する。その後、シリコン酸化膜210およびシリコン窒化膜211に対して、異方性エッチング処理を実施する。これにより、図21に示すように、第一のゲート構造G11の両側面および第二のゲート構造G12両側面には、積層構造のサイドウォール膜210,211が形成される。

【0098】

次に、第二の領域S40をマスクし、第一のゲート構造G11の両脇における半導体基板201に対して、P型の不純物イオンを再び注入する。当該イオン注入により、第一のゲート構造G11の両脇における半導体基板201には、比較的深い不純物イオン注入領域212が形成される(図22)。

【0099】

他方、第一の領域S30をマスクして、第二のゲート構造G12の両脇における半導体基板201に対して、N型の不純物イオンを再び注入する。当該イオン注入により、第二のゲート構造G12の両脇における半導体基板201には、比較的深い不純物イオン注入領域213が形成される(図22)。

【0100】

次に、不純物イオン注入領域208,209,212,213を活性化するために、図22に示した構造体に対して、熱処理を施す。これにより、第一のゲート構造G11の両脇における半導体基板201の表面内には、PMISトランジスタを構成するソース・ドレイン領域208,212が形成される。他方、第二のゲート構造G12の両脇における半導体基板201の表面内には、NMISトランジスタを構成するソース・ドレイン領域209,213が形成される。なお、活性化のための熱処理により、シリコン膜206は多結晶シリコン206となる。

【0101】

次に、第一のゲート構造G11および第二のゲート構造G12をマスクした状態で、ソース・ドレイン領域208,209,212,213を低抵抗化させる工程を実施する。

【0102】

具体的に、第一のゲート構造G11および第二のゲート構造G12を覆うように、半導体基板201上に、ニッケル膜を成膜する。そして、シリサイド化(低抵抗化と把握できる)処理を実施する。その後、未反応のニッケル膜を除去する。以上により、図23に示すように、ソース・ドレイン領域208,209,212,213の表面内には、ニッケルシリサイド214が形成される。つまり、当該ニッケルシリサイド214の形成により、第一のゲート構造G11の両脇における半導体基板201の上面および第二のゲート構造G12の両脇における半導体基板201の上面は、低抵抗化される。

【0103】

ここで、第一のゲート構造G11および第二のゲート構造G12の上面には、各々ゲートハードマスク207が形成されている。また、第一のゲート構造G11および第二のゲート構造G12の両側面には、各々サイドウォール膜210,211が形成されている。したがって、ゲートハードマスク207およびサイドウォール膜210,211はキャップ層として機能し、多結晶シリコン膜206はシリサイド化されない。

【0104】

次に、第一のゲート構造G11および第二のゲート構造G12を覆うように、半導体基板201上に、層間ライナー膜215および層間絶縁膜216を当該順に形成する(図24)。

【0105】

次に、第一のゲート電極G11を構成する多結晶シリコン膜206の上面、および第二のゲート電極G12を構成する多結晶シリコン膜206の上面を露出させる。その後、前記各多結晶シリコン膜(上述したように、半導体膜と把握できる)206を低抵抗化させる処理を実施する。

【0106】

具体的に、露出している各多結晶シリコン膜206の上面に、シリサイド化金属(たとえば、Ni等)を堆積する。その後、当該シリサイド化金属堆積後の半導体基板201に対して、熱処理を施す。これにより、各多結晶シリコン膜206をフルシリサイド化(低抵抗化と把握できる)される。つまり、図25に示すように、第一のゲート構造G11は、ゲート絶縁膜203、P−metal204およびフルシリサイド膜217の積層構造となり、第二のゲート構造G12は、ゲート絶縁膜203およびフルシリサイド膜217の積層構造となる。

【0107】

なお、上記シリサイド化金属としては、Ni以外に、Pt、Ti、Co、Hf、Ta、Yb、Er、およびAlなどが挙げられ、これらのいずれか一つ以上を含むことが望ましい。

【0108】

ここで、P−metal204の膜厚が5nm以上あれば、当該P−metal204は上記所望の仕事関数を示す。P−metal204が当該所望の仕事関数を有すれば、PMISトランジスタは、所望の閾値電圧動作が可能となる。このため、P−metal204の上層の組成は閾値電圧制御には関わらず、フルシリサイド膜217の組成を所望の組成に制御する必要が無い。つまり、第一のゲート構造G11を構成するフルシリサイド膜217と第二のゲート構造G12を構成するフルシリサイド膜217とは、共に同じ組成であっても良い。

【0109】

背景技術で説明した方法では、NMISトランジスタ側とPMISトランジスタ側で、組成の異なるシリサイド膜を形成する必要がある。そのため、NMISトランジスタ側の多結晶シリコン膜の膜厚とPMIS多結晶シリコン膜の膜厚とを、異ならせる処理が必要であった。

【0110】

しかし、本実施の形態に係る方法では、上記の通り、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜217の組成を作り分ける必要が無い。つまり、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜217の組成が同じであっても良い。このため、背景技術で説明したような、他方のMISトランジスタを構成する多結晶シリコン膜を、選択的にエッチングする必要も無い。

【0111】

なお、フルシリサイド膜217の形成に際して、ニッケルシリサイド214は、層間絶縁膜216により覆われている。したがって、当該フルシリサイド膜217の形成により、当該ニッケルシリサイド214が、再シリサイド化されたり、エッチングダメージを受けたりすることを防止できる。よって、所望のデバイス特性を維持できる。

【0112】

また、上記フルシリサイド膜217の形成に際して、シリサイド化金属膜厚、シリサイド化熱処理条件、熱処理を施すタイミング、未反応シリサイド化金属除去のタイミング等を制御する。これにより、第一のゲート構造G11および第二のゲート構造G12を構成するフルシリサイド膜217を、シリサイド金属含有量の少ないフルシリサイドとすることできる。シリサイド金属含有量の少ないフルシリサイドとは、NiSiまたはNiSi2等の組成を有するフルシリサイド膜である。

【0113】

たとえば、50nmの膜厚を有する多結晶シリコン膜206に対して、シリサイド金属膜として、Ni膜を30nm以上の膜厚で堆積する。その後、Ni膜形成後の半導体基板201に対して1回目の熱処理を施す。ここで、当該1回目の熱処理は、400℃以下、30秒程度の条件で実施される。当該1回目の熱処理により、多結晶シリコン膜206とNi膜を反応させる。次に未反応Ni膜のみを選択ウェットエッチングにより除去する。その後、半導体基板201に対して2回目の熱処理を施す。当該2回目の熱処理は、500℃、30秒程度の条件で実施される。以上の形成条件により、シリサイド金属含有量の少ないNiフルシリサイド層(この場合、NiSi層)が形成される。

【0114】

このように、少なくともNMISトランジスタを構成する第二のゲート構造G12において、フルシリサイド膜217をシリサイド金属含有量の少ないフルシリサイドとする。これにより、NMISトランジスタ側においても、所望の閾値電圧動作が可能となる。

【0115】

上記フルシリサイド膜217形成後、層間絶縁膜を積み増しし、CMP処理による平坦化、コンタクトプラグ形成等のフローを経て、通常のバックエンドフローを実施する。以上により、CMISトランジスタが完成する。

【0116】

本実施の形態に係るCMISトランジスタの製造方法では、第一のゲート構造G11側には、ゲート絶縁膜203と多結晶シリコン膜206との間に、P−metal204を形成する工程を含んでいる。

【0117】

したがって、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜217の組成を作り分ける必要がなくなる。よって、多結晶シリコン膜206の低抵抗化(シリサイド化)処理前に、第一のゲート構造G11側と第二のゲート構造G12側とで、多結晶シリコン膜206の膜厚を異ならせる処理も不要となる。また、P−metal204の存在により、多結晶シリコン膜206の低抵抗化(シリサイド化)処理に際して、半導体基板201側からの拡散を考慮する必要がなくなる。したがって、フルシリサイド膜217の形成制御を容易にコントロールできる。

【0118】

上記のように、本実施の形態では、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜217の組成を作り分ける必要がなくなる。したがって、NMISトランジスタ側とPMISトランジスタ側とで、フルシリサイド膜217の形成に際して、同熱処理条件、同シリコン/シリサイド金属膜厚により、同一組成を作ることが可能となる。このため、プロセス制御ウィンドウは広がり、フルシリサイド膜217の組成のバラツキを防止できる。

【0119】

本実施の形態では、上記の通り、第一のゲート構造G11側と第二のゲート構造G12側とで、多結晶シリコン膜206の膜厚を異ならせる処理も不要である。したがって、MISトランジスタのゲート形状不安定化を防止することができる。

【0120】

以上の観点より、本実施の形態に係る製造方法により、良好な特性を有するデュアルメタルゲートデバイス(CMISデバイス)を容易に作成することが可能となる。

【0121】

また、本実施の形態に係るCMISトランジスタの製造方法では、ニッケルシリサイド214の形成処理と、フルシリサイド膜217の形成処理とを、各々別のシリサイド工程にて実施している。特に、ニッケルシリサイド214の形成処理後に、フルシリサイド膜217の形成を行っている。

【0122】

したがって、ソース・ドレイン領域208,209,212,213の低抵抗化と、フルシリサイド膜217を有するゲート構造G11,G12の閾値制御とを、同時に満たすことが可能である。また、ニッケルシリサイド214の形成処理の際に、多結晶シリコン膜206の一部をシリサイド化する場合よりも、上記別工程を採用する方が、フルシリサイド膜217の形成制御も容易に成る。

【0123】

また、本実施の形態に係るCMISトランジスタの製造方法では、金属膜204として、P−metal204を一層だけを形成している。したがって、金属膜204が複層である場合よりも、本実施の形態に係る方法の方が、より容易に、金属膜204のパターニングができる。つまり、本実施の形態に係る方法の方が、より容易に、第一のゲート構造G11を形成できる。

【0124】

また、本実施の形態に係るCMISトランジスタの製造方法では、各多結晶シリコン膜206を、フルシリサイド化させている。したがって、ゲート構造G11,G12の全体低抵抗化を図ることができる。

【0125】

また、本実施の形態に係るCMISトランジスタの製造方法では、金属膜204は、P型の仕事関数を有するP−metal(Ti化合物、W化合物、Ru化合物、およびPt化合物)204である。PMISトランジスタは、所望の閾値電圧動作が可能となる。

【0126】

また、本実施の形態に係るCMISトランジスタの製造方法では、5〜30nm程度の膜厚のP−metal204を形成している。したがって、P−metal204が有する仕事関数を5.17±0.3eVの範囲とすることができる。これにより、PMISトランジスタは、所望の閾値電圧動作が可能となる。

【0127】

また、本実施の形態に係るCMISトランジスタの製造方法では、第二のゲート構造G12を構成する多結晶シリコン膜206を、NiSiまたはNiSi2の組成に、シリサイド化させている。したがって、NMISトランジスタは、所望の閾値電圧動作が可能となる。

【0128】

また、本実施の形態に係るCMISトランジスタの製造方法では、多結晶シリコン膜206を、Ni、Pt、Ti、Co、Hf、Ta、Yb、Er、およびAlのうち、少なくとも1以上を含む金属を用いて、フルシリサイド化している。したがって、容易に、フルシリサイド膜217を形成することができる。

【0129】

なお、本実施の形態2では、半導体膜206として、多結晶シリコン膜206を用いた場合について記した。しかし、半導体膜206として、ゲルマニウム膜やシリコンゲルマニウム膜を用いても良い。この場合、低抵抗化処理により、半導体膜206は、フルジャーマナイトゲート等となる。

【0130】

このように、半導体膜206として、ゲルマニウム膜やシリコンゲルマニウム膜を用いることにより、低抵抗化後のゲート電極の仕事関数制御範囲が、多結晶シリコン膜を採用したときと比べて変化する。したがって、デバイスの仕様に応じて、材料を変えることにより所望の閾値電圧を有するデバイスが実現できる。

【0131】

<実施の形態3>

本実施の形態に係るCMISトランジスタの製造方法を、工程断面図を用いて説明する。

【0132】

図1から図10までの工程は、実施の形態1と同様である。したがって、これらの工程の詳細な説明は、ここでは省略する。

【0133】

ここで、本実施の形態では、実施の形態1と同様に、第一の領域S10の半導体基板101の上面内には、第一の導電型の第一のMISトランジスタが形成される。第二の領域S20の半導体基板101の上面内には、第二の導電型の第二のMISトランジスタが形成される。本実施の形態では、第一の導電型は、「N型」とする。また、第二の導電型は、「P型」とする。したがって、本実施の形態では、実施の形態1と同様に、第一のMISトランジスタはNMISトランジスタであり、第二のMISトランジスタはPMISトランジスタである。

【0134】

次に、図10の構成において、第一のゲート電極G1を構成する多結晶シリコン膜106の上面、および第二のゲート電極G2を構成する多結晶シリコン膜106の上面を露出させる。次に、第二の領域S20をレジストとマスクする。そして、第一のゲート構造G1を構成する多結晶シリコン膜106に対して、たとえば窒素、酸素、燐等の少なくとも1種類以上をイオン注入によりドーピングする。

【0135】

当該イオン注入により、図26に示すように、第一のゲート構造G1を構成する多結晶シリコン膜106aが形成される。後に実施される多結晶シリコン膜106aのシリサイド化工程において、当該多結晶シリコン膜106aは、シリサイド金属の半導体基板101方向への拡散を抑制する機能を有する。具体的に、シリサイド金属のN−metal104膜への侵入を抑制できる。なお、図26は、第二の領域S20に形成されていたレジストマスク除去後の構成を示している。

【0136】

その後、多結晶シリコン膜(上述したように、半導体膜と把握できる)106,106aを低抵抗化させる処理を実施する。

【0137】

具体的に、露出している各多結晶シリコン膜106,106aの上面に、シリサイド化金属(たとえば、Ni等)を堆積する。その後、当該シリサイド化金属堆積後の半導体基板101に対して、熱処理を施す。これにより、各多結晶シリコン膜106,106aをシリサイド化(低抵抗化と把握できる)される。

【0138】

ここで、多結晶シリコン106aはシリサイド金属の拡散を抑制する。したがって、第一のゲート電極G1側においては、多結晶シリコン106aはすべてシリサイド化されない。つまり、図27に示すように、第一のゲート構造G1は、ゲート絶縁膜103、N−metal104、不純物イオンが注入された多結晶ポリシリコン膜106aおよびシリサイド膜117の積層構造となる。なお、第二のゲート構造G2は、ゲート絶縁膜103およびフルシリサイド膜117の積層構造となる。

【0139】

また、上記シリサイド化金属としては、Ni以外に、Pt、Ti、Co、Hf、Ta、Yb、Er、およびAlなどが挙げられ、これらのいずれか一つ以上を含むことが望ましい。

【0140】

多結晶シリコン膜106aが形成される場合においても、N−metal104の膜厚が5nm以上であれば、NMISトランジスタは所望の仕事関数を示す。したがって、当該N−metal104の上層の電極構造に関わらず、NMISトランジスタは、所望の閾値電圧動作が可能である。このため、N−metal104の上層の組成は閾値電圧制御には関わらず、シリサイド膜117の組成を所望の組成に制御する必要が無い。つまり、第一のゲート構造G1を構成するシリサイド膜117と第二のゲート構造G2を構成するフルシリサイド膜117とは、共に同じ組成であっても良い。

【0141】

なお、シリサイド膜117の形成に際して、ニッケルシリサイド114は、層間絶縁膜116により覆われている。したがって、当該シリサイド膜117の形成により、当該ニッケルシリサイド114が、再シリサイド化されたり、エッチングダメージを受けたりすることを防止できる。よって、所望のデバイス特性を維持できる。

【0142】

また、上記シリサイド膜117の形成に際して、シリサイド化金属膜厚、シリサイド化熱処理条件、熱処理を施すタイミング、未反応シリサイド化金属除去のタイミング等を制御する(形成条件の一例は、実施の形態1で説明した通りである)。これにより、第一のゲート構造G1および第二のゲート構造G2を構成するシリサイド膜117を、シリサイド金属含有量の多いフルシリサイドとすることできる。シリサイド金属含有量の多いシリサイドとは、Ni3Si、Ni31Si12、およびNi2Siのいずれかの組成を有するシリサイド膜である。

【0143】

このように、少なくともPMISトランジスタを構成する第二のゲート構造G2において、フルシリサイド膜117をシリサイド金属含有量の多いフルシリサイドとする。これにより、PMISトランジスタ側においても、所望の閾値電圧動作が可能となる。

【0144】

上記シリサイド膜117形成後、層間絶縁膜を積み増しし、CMP処理による平坦化、コンタクトプラグ形成等のフローを経て、通常のバックエンドフローを実施する。以上により、CMISトランジスタが完成する。

【0145】

本実施の形態では上記工程が実施されるので、実施の形態1で説明した効果に加えて、次のような効果も有する。

【0146】

具体的に、本実施の形態では、第一のゲート構造G1を構成する多結晶シリコン106のシリサイド化前に、当該多結晶シリコン106に対して、燐、砒素、および酸素のうち、少なくとも1つをイオン注入している。

【0147】

したがって、当該イオン注入された多結晶シリコン膜106aの形成により、多結晶シリコン膜106aのシリサイド化の際に、シリサイド金属の半導体基板101方向への拡散を抑制できる。具体的に、N−metal104へのシリサイド金属の侵入を抑制できる。これにより、NMISトランジスタ側において、仕事関数を変化させる等の影響がなくなり、安定したCMISデバイスが実現可能となる。

【0148】

なお、当該イオン注入処理を施すことにより、第一のゲート構造G1は、ゲート絶縁膜103、N−metal104、不純物イオンが注入された多結晶ポリシリコン膜106aおよびシリサイド膜117が当該順に積層した、積層構造となる。

【0149】

また、半導体膜106として、多結晶シリコンの代わりに、ゲルマニウム膜やシリコンゲルマニウム膜を用いても良い。この場合、低抵抗化処理により、半導体膜106は、ジャーマナイトゲート等となる。

【0150】

<実施の形態4>

本実施の形態に係るCMISトランジスタの製造方法を、工程断面図を用いて説明する。

【0151】

図15から図24までの工程は、実施の形態2と同様である。したがって、これらの工程の詳細な説明は、ここでは省略する。

【0152】

ここで、本実施の形態では、実施の形態2と同様に、第一の領域S30の半導体基板201の上面内には、第一の導電型の第一のMISトランジスタが形成される。第二の領域S40の半導体基板201の上面内には、第二の導電型の第二のMISトランジスタが形成される。本実施の形態では、第一の導電型は、「P型」とする。また、第二の導電型は、「N型」とする。したがって、本実施の形態では、実施の形態2と同様に、第一のMISトランジスタはPMISトランジスタであり、第二のMISトランジスタはNMISトランジスタである。

【0153】

次に、図24の構成において、第一のゲート電極G11を構成する多結晶シリコン膜206の上面、および第二のゲート電極G12を構成する多結晶シリコン膜206の上面を露出させる。次に、第二の領域S40をレジストとマスクする。そして、第一のゲート構造G11を構成する多結晶シリコン膜206に対して、たとえば窒素、酸素、燐等の少なくとも1種類以上をイオン注入によりドーピングする。

【0154】

当該イオン注入により、図28に示すように、第一のゲート構造G11を構成する多結晶シリコン膜206aが形成される。後に実施される多結晶シリコン膜206aのシリサイド化工程において、当該多結晶シリコン膜206aは、シリサイド金属の半導体基板201方向への拡散を抑制する機能を有する。具体的に、シリサイド金属のP−metal204膜への侵入を抑制できる。なお、図28は、第二の領域S40に形成されていたレジストマスク除去後の構成を示している。

【0155】

その後、多結晶シリコン膜(上述したように、半導体膜と把握できる)206,206aを低抵抗化させる処理を実施する。

【0156】

具体的に、露出している各多結晶シリコン膜206,206aの上面に、シリサイド化金属(たとえば、Ni等)を堆積する。その後、当該シリサイド化金属堆積後の半導体基板201に対して、熱処理を施す。これにより、各多結晶シリコン膜206,206aをシリサイド化(低抵抗化と把握できる)される。

【0157】

ここで、多結晶シリコン206aはシリサイド金属の拡散を抑制する。したがって、第一のゲート電極G11側においては、多結晶シリコン206aはすべてシリサイド化されない。つまり、図29に示すように、第一のゲート構造G11は、ゲート絶縁膜203、P−metal204、不純物イオンが注入された多結晶ポリシリコン膜206aおよびシリサイド膜217の積層構造となる。なお、第二のゲート構造G12は、ゲート絶縁膜203およびフルシリサイド膜217の積層構造となる。

【0158】

また、上記シリサイド化金属としては、Ni以外に、Pt、Ti、Co、Hf、Ta、Yb、Er、およびAlなどが挙げられ、これらのいずれか一つ以上を含むことが望ましい。

【0159】

多結晶シリコン膜206aが形成される場合においても、P−metal204の膜厚が5nm以上であれば、PMISトランジスタは所望の仕事関数を示す。したがって、当該P−metal204の上層の電極構造に関わらず、PMISトランジスタは、所望の閾値電圧動作が可能である。このため、P−metal204の上層の組成は閾値電圧制御には関わらず、シリサイド膜217の組成を所望の組成に制御する必要が無い。つまり、第一のゲート構造G11を構成するシリサイド膜217と第二のゲート構造G12を構成するシリサイド膜217とは、共に同じ組成であっても良い。

【0160】

なお、シリサイド膜217の形成に際して、ニッケルシリサイド214は、層間絶縁膜216により覆われている。したがって、当該シリサイド膜217の形成により、当該ニッケルシリサイド214が、再シリサイド化されたり、エッチングダメージを受けたりすることを防止できる。よって、所望のデバイス特性を維持できる。

【0161】

また、上記シリサイド膜217の形成に際して、シリサイド化金属膜厚、シリサイド化熱処理条件、熱処理を施すタイミング、未反応シリサイド化金属除去のタイミング等を制御する。これにより、第一のゲート構造G11および第二のゲート構造G12を構成するシリサイド膜217を、シリサイド金属含有量の少ないフルシリサイドとすることできる。シリサイド金属含有量の少ないシリサイドとは、NiSiまたはNiSi2等の組成を有するシリサイド膜である。

【0162】

このように、少なくともNMISトランジスタを構成する第二のゲート構造G12において、フルシリサイド膜217をシリサイド金属含有量の少ないフルシリサイドとする。これにより、NMISトランジスタ側においても、所望の閾値電圧動作が可能となる。

【0163】

上記シリサイド膜217形成後、層間絶縁膜を積み増しし、CMP処理による平坦化、コンタクトプラグ形成等のフローを経て、通常のバックエンドフローを実施する。以上により、CMISトランジスタが完成する。

【0164】

本実施の形態では上記工程が実施されるので、実施の形態2で説明した効果に加えて、次のような効果も有する。

【0165】

具体的に、本実施の形態では、第一のゲート構造G11を構成する多結晶シリコン206のシリサイド化前に、当該多結晶シリコン206に対して、燐、砒素、および酸素のうち、少なくとも1つをイオン注入している。

【0166】

したがって、当該イオン注入された多結晶シリコン膜206aの形成により、多結晶シリコン膜206aのシリサイド化の際に、シリサイド金属の半導体基板201方向への拡散を抑制できる。具体的に、P−metal204へのシリサイド金属の侵入を抑制できる。これにより、PMISトランジスタ側において、仕事関数を変化させる等の影響がなくなり、安定したCMISデバイスが実現可能となる。

【0167】

なお、当該イオン注入処理を施すことにより、第一のゲート構造G11は、ゲート絶縁膜203、P−metal204、不純物イオンが注入された多結晶ポリシリコン膜206aおよびシリサイド膜217が当該順に積層した、積層構造となる。

【0168】

また、半導体膜206として、多結晶シリコンの代わりに、ゲルマニウム膜やシリコンゲルマニウム膜を用いても良い。この場合、低抵抗化処理により、半導体膜206は、ジャーマナイトゲート等となる。

【0169】

<実施の形態5>

本実施の形態に係るCMISトランジスタの製造方法は、実施の形態1に係るCMISトランジスタの製造方法の応用形態である。本実施の形態に係る製造方法を、工程断面図を用いて説明する。

【0170】

図1に示した半導体基板101を用意する。実施の形態1で説明したように、第一の領域S10には、NMISトランジスタが形成され、第二の領域S20には、PMISトランジスタが形成される。イオン注入処理により、半導体基板101内には、N型のウエル領域およびP型のウエル領域が形成される(図1では図示せず)。

【0171】

次に、第一の領域S10の半導体基板101上に、ゲート絶縁膜103と金属膜(N−metal)104と上層金属膜404と半導体膜(多結晶シリコン膜)106とが当該順に積層した積層構造である、第一のゲート構造G31を形成する。また、第二の領域S20記半導体基板101上に、ゲート絶縁膜103と半導体膜(多結晶シリコン膜)106とが当該順に積層した積層構造である、第二のゲート構造G2を形成する。

【0172】

ここで、第一のゲート構造G31は、NMISトランジスタの構成要素である。また、第二のゲート構造G2は、PMISトランジスタの構成要素である。後述において、具体的な第一のゲート構造G31および第二のゲート構造G2の製造方法を、図30から図33を用いて説明する。

【0173】

まず、実施の形態1で説明したように、第一の領域S10および第二の領域S20の半導体基板101上に、ハフニウムシリケイト膜から成るゲート絶縁膜103を形成する(図30)。次に、実施の形態1と同様に、ゲート絶縁膜103上にN−metal104を形成する(図30)。N−metal104の膜厚は、5nm〜30nm程度であり、たとえば10nmである。

【0174】

次に、本実施の形態では、N−metal104上に、上層金属膜404を形成する(図30)。当該上層金属膜404は、N−metal104の酸化防止膜として機能する。当該機能を有する上層金属膜404として、たとえばTiN、TaN、およびHfNのいずれかが適している。

【0175】

次に、上層金属膜404上に、所定のパターンのレジスト105を形成する(図31)。図31に示すように、パターニング後のレジスト105は、第一の領域S10にのみ残存する。次に、パターニング後のレジスト105をマスクとして使用して、上層金属膜404およびN−metal104に対してウェットエッチ等を施す。これにより、図31に示すように、第二の領域S20に形成されていた、上層金属膜404およびN−metal104が除去される。

【0176】

第一の領域S10からレジスト105を除去した後、上層金属膜404上およびゲート絶縁膜103上に、実施の形態1で示したシリコン膜106を成膜する(図32)。次に、図32に示すように、多結晶シリコン膜106上に、実施の形態1で示したゲートハードマスク107を形成する。なお、図32から分かるように、多結晶シリコン膜106およびゲートハードマスク107は、第一の領域S10および第二の領域S20の両方に形成されている。

【0177】

次に、ゲート絶縁膜103、N−metal104、上層金属膜404、多結晶シリコン膜106およびゲートハードマスク107に対して、ドライエッチング、ウェットエッチング等を施す。これにより、図33に示すように、第一の領域S10の半導体基板101上には、第一のゲート構造G31が形成され、第二の領域S20の半導体基板101上には、第二のゲート構造G2が形成される。

【0178】

ここで、第一のゲート構造G31は、ゲート絶縁膜103、N−metal104、上層金属膜404および多結晶シリコン膜106とが当該順に積層された積層構造である(図33)。他方、第二のゲート構造G2は、ゲート絶縁膜103および多結晶シリコン膜106とが当該順に積層された積層構造である(図33)。また、第一のゲート構造G31上および第二のゲート構造G2上には、各々ゲートハードマスク107が形成されている(図33)。

【0179】

以後、実施の形態1と同様に、ソース・ドレイン領域108,112,109,113の形成、サイドウォール膜110,111の形成、ニッケルシリサイド114形成、層間ライナー膜115と層間絶縁膜116の形成、および多結晶シリコン膜106のフルシリサイド化処理等を実施する。

【0180】

これにより、図34に示す構造が形成される。図34に示すように、第一のゲート構造G31は、ゲート絶縁膜103、N−metal104、上層金属膜404およびフルシリサイド膜117の積層構造となり、第二のゲート構造G2は、ゲート絶縁膜103およびフルシリサイド膜117の積層構造となる。なお、実施の形態1で説明したように、第二のゲート構造G2を構成するフルシリサイド膜117は、シリサイド金属含有量の多いフルシリサイドである。

【0181】

上記フルシリサイド膜117形成後、層間絶縁膜を積み増しし、CMP処理による平坦化、コンタクトプラグ形成等のフローを経て、通常のバックエンドフローを実施する。以上により、CMISトランジスタが完成する。

【0182】

本実施の形態では上記工程が実施されるので、実施の形態1で説明した効果に加えて、次のような効果も有する。

【0183】

具体的に、本実施の形態では、ゲート絶縁膜103、N−metal104、上層金属膜404、および多結晶シリコン膜106(後に、フルシリサイド膜117となる)とが当該順に積層した積層構造である、第一のゲート構造G31を形成する工程を含んでいる。ここで、上層金属膜404は、TiN、TaN、およびHfNのいずれかである。

【0184】

したがって、N−metal104上に上層金属膜404が形成されているので、多結晶シリコン106のフルシリサイド化処理の際に、シリサイド金属がN−metal104中に侵入することを抑制できる。さらに、上層金属膜404は、TiN、TaN、およびHfN等であるので、N−metal104の酸化防止層として機能する。よって、N−metal104がウェハプロセス中に変質することを防止できる。以上により、安定したデバイス特性が実現できる。

【0185】

また、半導体膜106として、多結晶シリコンの代わりに、ゲルマニウム膜やシリコンゲルマニウム膜を用いても良い。この場合、低抵抗化処理により、半導体膜106は、フルジャーマナイトゲート等となる。

【0186】

<実施の形態6>

本実施の形態に係るCMISトランジスタの製造方法は、実施の形態2に係るCMISトランジスタの製造方法の応用形態である。本実施の形態に係る製造方法を、工程断面図を用いて説明する。

【0187】

図15に示した半導体基板201を用意する。実施の形態2で説明したように、第一の領域S30には、PMISトランジスタが形成され、第二の領域S40には、NMISトランジスタが形成される。イオン注入処理により、半導体基板201内には、N型のウエル領域およびP型のウエル領域が形成される(図15では図示せず)。

【0188】

次に、第一の領域S30の半導体基板201上に、ゲート絶縁膜203と金属膜(P−metal)204と上層金属膜504と半導体膜(多結晶シリコン膜)206とが当該順に積層した積層構造である、第一のゲート構造G41を形成する。また、第二の領域S40記半導体基板201上に、ゲート絶縁膜203と半導体膜(多結晶シリコン膜)206とが当該順に積層した積層構造である、第二のゲート構造G12を形成する。

【0189】

ここで、第一のゲート構造G41は、PMISトランジスタの構成要素である。また、第二のゲート構造G12は、NMISトランジスタの構成要素である。後述において、具体的な第一のゲート構造G41および第二のゲート構造G12の製造方法を、図35から図38を用いて説明する。

【0190】

まず、実施の形態2で説明したように、第一の領域S30および第二の領域S40の半導体基板201上に、ハフニウムシリケイト膜から成るゲート絶縁膜203を形成する(図35)。次に、実施の形態2と同様に、ゲート絶縁膜203上にP−metal204を形成する(図35)。P−metal204の膜厚は、5nm〜30nm程度であり、たとえば10nmである。

【0191】

次に、本実施の形態では、P−metal204上に、上層金属膜504を形成する(図35)。当該上層金属膜504は、P−metal204の酸化防止膜として機能する。当該機能を有する上層金属膜504として、たとえばTiN、TaN、およびHfNのいずれかが適している。

【0192】

次に、上層金属膜504上に、所定のパターンのレジスト205を形成する(図36)。図36に示すように、パターニング後のレジスト205は、第一の領域S30にのみ残存する。次に、パターニング後のレジスト205をマスクとして使用して、上層金属膜504およびP−metal204に対してウェットエッチ等を施す。これにより、図36に示すように、第二の領域S40に形成されていた、上層金属膜504およびP−metal204が除去される。

【0193】

第一の領域S30からレジスト205を除去した後、上層金属膜504上およびゲート絶縁膜203上に、実施の形態2で示した多結晶シリコン膜206を成膜する(図37)。次に、図37に示すように、多結晶シリコン膜206上に、実施の形態2で示したゲートハードマスク207を形成する。なお、図37から分かるように、多結晶シリコン膜206およびゲートハードマスク207は、第一の領域S30および第二の領域S40の両方に形成されている。

【0194】

次に、ゲート絶縁膜203、P−metal204、上層金属膜504、多結晶シリコン膜206およびゲートハードマスク207に対して、ドライエッチング、ウェットエッチング等を施す。これにより、図38に示すように、第一の領域S30の半導体基板201上には、第一のゲート構造G41が形成され、第二の領域S40の半導体基板201上には、第二のゲート構造G12が形成される。

【0195】

ここで、第一のゲート構造G41は、ゲート絶縁膜203、P−metal204、上層金属膜504および多結晶シリコン膜206とが当該順に積層された積層構造である(図38)。他方、第二のゲート構造G12は、ゲート絶縁膜203および多結晶シリコン膜206とが当該順に積層された積層構造である(図38)。また、第一のゲート構造G41上および第二のゲート構造G12上には、各々ゲートハードマスク207が形成されている(図38)。

【0196】

以後、実施の形態2と同様に、ソース・ドレイン領域208,212,209,213の形成、サイドウォール膜210,211の形成、ニッケルシリサイド214形成、層間ライナー膜215と層間絶縁膜216の形成、および多結晶シリコン膜206のフルシリサイド化処理等を実施する。

【0197】

これにより、図39に示す構造が形成される。図39に示すように、第一のゲート構造G41は、ゲート絶縁膜203、P−metal204、上層金属膜504およびフルシリサイド膜217の積層構造となり、第二のゲート構造G12は、ゲート絶縁膜203およびフルシリサイド膜217の積層構造となる。なお、実施の形態2で説明したように、第二のゲート構造G12を構成するフルシリサイド膜217は、シリサイド金属含有量の少ないフルシリサイドである。

【0198】

上記フルシリサイド膜217形成後、層間絶縁膜を積み増しし、CMP処理による平坦化、コンタクトプラグ形成等のフローを経て、通常のバックエンドフローを実施する。以上により、CMISトランジスタが完成する。

【0199】

本実施の形態では上記工程が実施されるので、実施の形態2で説明した効果に加えて、次のような効果も有する。

【0200】

具体的に、本実施の形態では、ゲート絶縁膜203、P−metal204、上層金属膜504、および多結晶シリコン膜206(後に、フルシリサイド膜217となる)とが当該順に積層した積層構造である、第一のゲート構造G41を形成する工程を含んでいる。ここで、上層金属膜504は、TiN、TaN、およびHfNのいずれかである。

【0201】

したがって、P−metal204上に上層金属膜504が形成されているので、多結晶シリコン206のフルシリサイド化処理の際に、シリサイド金属がP−metal204中に侵入することを抑制できる。さらに、上層金属膜504は、TiN、TaN、およびHfN等であるので、P−metal204の酸化防止層として機能する。よって、P−metal204がウェハプロセス中に変質することを防止できる。以上により、安定したデバイス特性が実現できる。

【0202】

また、半導体膜206として、多結晶シリコンの代わりに、ゲルマニウム膜やシリコンゲルマニウム膜を用いても良い。この場合、低抵抗化処理により、半導体膜206は、フルジャーマナイトゲート等となる。

【0203】

上記各実施の形態に記載のCMISトランジスタの形成方法は、45nmノード以降のシリコン半導体集積回路製品の全てが対象となる。特に、トランジスタの電流駆動能力の向上が望まれるものに適する。具体的に、本発明は、高速動作を求められるロジック回路の製造方法に適する。

【図面の簡単な説明】

【0204】

【図1】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図2】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図3】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図4】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図5】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図6】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図7】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図8】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図9】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図10】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図11】実施の形態1に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図12】従来技術に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図13】従来技術に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図14】従来技術に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図15】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図16】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図17】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図18】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図19】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図20】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図21】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図22】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図23】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図24】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図25】実施の形態2に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図26】実施の形態3に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図27】実施の形態3に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図28】実施の形態4に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図29】実施の形態4に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図30】実施の形態5に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図31】実施の形態5に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図32】実施の形態5に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図33】実施の形態5に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図34】実施の形態5に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図35】実施の形態6に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図36】実施の形態6に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図37】実施の形態6に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図38】実施の形態6に係るCMISトランジスタの製造方法を説明する工程断面図である。

【図39】実施の形態6に係るCMISトランジスタの製造方法を説明する工程断面図である。

【符号の説明】

【0205】

101,201 半導体基板、103,203 ゲート絶縁膜、104 金属膜(N−metal)、106,206 多結晶シリコン(半導体膜)、106a,206a イオン注入された多結晶シリコン、114,214 ニッケルシリサイド、117,217 フルシリサイド膜(シリサイド膜)、204 金属膜(P−metal)、404,504 上層金属膜、G1,G11 第一のゲート構造、G2,G12 第二のゲート構造、S10,S30 第一の領域、S20,S40 第二の領域。

【特許請求の範囲】

【請求項1】

(A)第一の導電型の第一のトランジスタが形成される第一の領域と、第二の導電型の第二のトランジスタが形成される第二の領域とを、有する半導体基板を用意する工程と、

(B)前記第一の領域の前記半導体基板上に、ゲート絶縁膜と金属膜と半導体膜とが当該順に積層した積層構造であり、前記第一のトランジスタを構成する第一のゲート構造を形成する工程と、

(C)前記第二の領域の前記半導体基板上に、ゲート絶縁膜と半導体膜とが当該順に積層した積層構造であり、前記第二のトランジスタを構成する第二のゲート構造を形成する工程と、

(D)前記第一のゲート構造および前記第二のゲート構造をマスクした状態で、前記第一のゲート構造の両脇における前記半導体基板上および前記第二のゲート構造の両脇における前記半導体基板上を、低抵抗化させる工程と、

(E)前記第一のゲート構造を構成する前記半導体膜および前記第二のゲート構造を構成する前記半導体膜を低抵抗化させる工程とを、備えている、

ことを特徴とするCMISトランジスタの製造方法。

【請求項2】

前記半導体膜は、

多結晶シリコン膜である、

ことを特徴とする請求項1に記載のCMISトランジスタの製造方法。

【請求項3】

前記工程(E)は、

各前記多結晶シリコン膜を、フルシリサイド化させる工程である、

ことを特徴とする請求項2に記載のCMISトランジスタの製造方法。

【請求項4】

前記半導体膜は、

ゲルマニウム膜である、

ことを特徴とする請求項1に記載のCMISトランジスタの製造方法。

【請求項5】

前記半導体膜は、

シリコンゲルマニウム膜である、

ことを特徴とする請求項1に記載のCMISトランジスタの製造方法。

【請求項6】

前記工程(E)は、

各前記半導体膜全体を、低抵抗化させる工程である、

ことを特徴とする請求項4または請求項5に記載のCMISトランジスタの製造方法。

【請求項7】

前記第一のトランジスタは、

N型トランジスタであり、

前記金属膜は、

N型の仕事関数を有する金属である、

ことを特徴とする請求項1に記載のCMISトランジスタの製造方法。

【請求項8】

前記金属膜は、

Ta化合物またはHf化合物である、

ことを特徴とする請求項7に記載のCMISトランジスタの製造方法。

【請求項9】

前記第二のトランジスタは、

P型トランジスタであり、

前記工程(E)は、

前記第二のゲート構造を構成する前記半導体膜を、Ni3Si、Ni31Si12、およびNi2Siのいずれかの組成に、シリサイド化させる工程である、

ことを特徴とする請求項7に記載のCMISトランジスタの製造方法。

【請求項10】

前記第一のトランジスタは、

P型トランジスタであり、

前記金属膜は、

P型の仕事関数を有する金属である、

ことを特徴とする請求項1に記載のCMISトランジスタの製造方法。

【請求項11】

前記金属膜は、

Ti化合物、W化合物、Ru化合物、およびPt化合物のいずれかである、

ことを特徴とする請求項10に記載のCMISトランジスタの製造方法。

【請求項12】

前記第二のトランジスタは、

N型トランジスタであり、

前記工程(E)は、

前記第一のゲート構造を構成する前記半導体膜を、NiSiまたはNiSi2の組成に、シリサイド化させる工程である、

ことを特徴とする請求項10に記載のCMISトランジスタの製造方法。

【請求項13】

前記工程(E)は、

前記工程(D)の後に、実施する、

ことを特徴とする請求項1に記載のCMISトランジスタの製造方法。

【請求項14】

前記工程(E)は、

Ni、Pt、Ti、Co、Hf、Ta、Yb、Er、およびAlのうち、少なくとも1以上を含む金属を用いたシリサイド化工程である、

ことを特徴とする請求項1に記載のCMISトランジスタの製造方法。

【請求項15】

前記金属膜の膜厚は、

5〜30nmである、

ことを特徴とする請求項7または請求項10に記載のCMISトランジスタの製造方法。

【請求項16】

(F)前記工程(E)の前に、前記第一のゲート構造を構成する前記多結晶シリコン膜に対して、イオン注入処理を行う工程を、さらに備えている、

ことを特徴とする請求項2に記載のCMISトランジスタの製造方法。

【請求項17】

前記工程(F)は、

燐、砒素、および酸素のうち、少なくとも1つを注入する工程である、

ことを特徴とする請求項16に記載のCMISトランジスタの製造方法。

【請求項18】

前記工程(B)は、

前記ゲート絶縁膜と前記金属膜と上層金属膜と前記半導体膜とが当該順に積層した積層構造である、前記第一のゲート構造を形成する工程である、

ことを特徴とする請求項1に記載のCMISトランジスタの製造方法。

【請求項19】

前記上層金属膜は、

TiN、TaN、およびHfNのいずれかである、

ことを特徴とする請求項18に記載のCMISトランジスタの製造方法。

【請求項1】

(A)第一の導電型の第一のトランジスタが形成される第一の領域と、第二の導電型の第二のトランジスタが形成される第二の領域とを、有する半導体基板を用意する工程と、

(B)前記第一の領域の前記半導体基板上に、ゲート絶縁膜と金属膜と半導体膜とが当該順に積層した積層構造であり、前記第一のトランジスタを構成する第一のゲート構造を形成する工程と、

(C)前記第二の領域の前記半導体基板上に、ゲート絶縁膜と半導体膜とが当該順に積層した積層構造であり、前記第二のトランジスタを構成する第二のゲート構造を形成する工程と、

(D)前記第一のゲート構造および前記第二のゲート構造をマスクした状態で、前記第一のゲート構造の両脇における前記半導体基板上および前記第二のゲート構造の両脇における前記半導体基板上を、低抵抗化させる工程と、

(E)前記第一のゲート構造を構成する前記半導体膜および前記第二のゲート構造を構成する前記半導体膜を低抵抗化させる工程とを、備えている、

ことを特徴とするCMISトランジスタの製造方法。

【請求項2】

前記半導体膜は、

多結晶シリコン膜である、

ことを特徴とする請求項1に記載のCMISトランジスタの製造方法。

【請求項3】

前記工程(E)は、

各前記多結晶シリコン膜を、フルシリサイド化させる工程である、

ことを特徴とする請求項2に記載のCMISトランジスタの製造方法。

【請求項4】

前記半導体膜は、

ゲルマニウム膜である、

ことを特徴とする請求項1に記載のCMISトランジスタの製造方法。

【請求項5】

前記半導体膜は、

シリコンゲルマニウム膜である、

ことを特徴とする請求項1に記載のCMISトランジスタの製造方法。

【請求項6】

前記工程(E)は、

各前記半導体膜全体を、低抵抗化させる工程である、

ことを特徴とする請求項4または請求項5に記載のCMISトランジスタの製造方法。

【請求項7】

前記第一のトランジスタは、

N型トランジスタであり、

前記金属膜は、

N型の仕事関数を有する金属である、

ことを特徴とする請求項1に記載のCMISトランジスタの製造方法。

【請求項8】

前記金属膜は、

Ta化合物またはHf化合物である、

ことを特徴とする請求項7に記載のCMISトランジスタの製造方法。

【請求項9】

前記第二のトランジスタは、

P型トランジスタであり、

前記工程(E)は、

前記第二のゲート構造を構成する前記半導体膜を、Ni3Si、Ni31Si12、およびNi2Siのいずれかの組成に、シリサイド化させる工程である、

ことを特徴とする請求項7に記載のCMISトランジスタの製造方法。

【請求項10】

前記第一のトランジスタは、

P型トランジスタであり、

前記金属膜は、

P型の仕事関数を有する金属である、

ことを特徴とする請求項1に記載のCMISトランジスタの製造方法。

【請求項11】

前記金属膜は、

Ti化合物、W化合物、Ru化合物、およびPt化合物のいずれかである、

ことを特徴とする請求項10に記載のCMISトランジスタの製造方法。

【請求項12】

前記第二のトランジスタは、

N型トランジスタであり、

前記工程(E)は、

前記第一のゲート構造を構成する前記半導体膜を、NiSiまたはNiSi2の組成に、シリサイド化させる工程である、

ことを特徴とする請求項10に記載のCMISトランジスタの製造方法。

【請求項13】

前記工程(E)は、

前記工程(D)の後に、実施する、

ことを特徴とする請求項1に記載のCMISトランジスタの製造方法。

【請求項14】

前記工程(E)は、

Ni、Pt、Ti、Co、Hf、Ta、Yb、Er、およびAlのうち、少なくとも1以上を含む金属を用いたシリサイド化工程である、

ことを特徴とする請求項1に記載のCMISトランジスタの製造方法。

【請求項15】

前記金属膜の膜厚は、

5〜30nmである、

ことを特徴とする請求項7または請求項10に記載のCMISトランジスタの製造方法。

【請求項16】