CMOSデバイス用シリコンウェハの製造方法

【課題】 同じ特性のn−MOSトランジスタとp−MOSトランジスタとを有し、n−MOSトランジスタに最適な応力による歪特性をもたらすSiGe膜と、p−MOSトランジスタに最適な応力による歪特性をもたらすSiC膜とを同一シリコン基材上に備えた、小さいサイズのトランジスタに対しても、最適な特性を持つCMOSデバイス用のシリコンウェハの製造方法の提供。

【解決手段】 CMOSデバイス用シリコンウェハの製造方法において、同一シリコン基材の表面に、選択エピタキシャル法又はイオン注入法を用い、SiGe膜及びSiC膜を分離して形成し、CMOSデバイスを構成するために必要なn−MOSデバイス、及びp−MOSデバイスを同一シリコン基材上に島状に分離して製造する。

【解決手段】 CMOSデバイス用シリコンウェハの製造方法において、同一シリコン基材の表面に、選択エピタキシャル法又はイオン注入法を用い、SiGe膜及びSiC膜を分離して形成し、CMOSデバイスを構成するために必要なn−MOSデバイス、及びp−MOSデバイスを同一シリコン基材上に島状に分離して製造する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、CMOSデバイス用シリコンウェハの製造方法に関し、特に、同一シリコン基材上にn−MOS用歪シリコン(n−MOSトランジスタ)とp−MOS用歪シリコン(p−MOSトランジスタ)とを一緒に製造する方法に関する。

【背景技術】

【0002】

近年、半導体デバイスの微細化が進められると共に、デバイスの動作速度の高速化、高集積化や、薄膜化の要求がますます高まっている。その際に、基材(例えば、シリコン基材)上に各種の薄膜を形成するが、このような種々の成膜工程、例えばCMOSデバイス製造工程においては、その下地となるシリコン基材表面に自然酸化膜(SiO2膜)が存在する場合、デバイス特性が悪化するため、成膜前に自然酸化膜等を除去し、活性状態の基材表面とし、その上に所望の薄膜を堆積させ、CMOSデバイス用シリコンウェハを製造することが必要である。

【0003】

また、従来、CMOSデバイスにおいて、歪シリコンデバイス用SiGe膜の形成された歪シリコンウェハでは、電子と正孔の両方に最適な移動度をもたらす歪を与えることができず、n−MOSトランジスタとp−MOSトランジスタとの特性のそろったCMOSデバイスを構成することが困難であった。最適なCMOSデバイスを構成する方法としては、それぞれのトランジスタに最適な歪を別個に与えるローカル歪による歪トランジスタの作製方法がある。しかし、このローカル歪トランジスタの作製方法では、それぞれのデバイスに最適なプロセスを用いるために、長く複雑なデバイス作製プロセスを必要としていた。また、応力膜を用いた歪シリコンデバイスでは、トランジスタのサイズが小さくなると、応力が必要なチャネル部分に充分な応力が掛らず、トランジスタの性能の向上が見込まれない欠点があった。

【0004】

CMOSデバイスを作製する場合、上記したように、ほぼ同じ特性のn−MOSトランジスタとp−MOSトランジスタとが必要になるが、従来技術の上記歪シリコン技術を用いた場合、n−MOSトランジスタとp−MOSトランジスタとの特性をあわせるのが難しく、より複雑なローカル歪技術を用いてもトランジスタのサイズが小さくなると効果が小さくなるという欠点を有していた。

【0005】

CMOSデバイスを作製する場合、従来は、一枚の同一シリコン基材の表面にSiGe膜及びSiC膜を同じように製造することができなかった。そのため、例えば、図12に示すように、Si基板1201上にSiO2膜(BOX酸化膜)1202、その上に活性シリコン膜1203(実際にデバイスを作製する部分)を作製して、通常のSOI基板とし、このSOI基板上に応力用SiN膜1204、スペーサ絶縁膜1205及びゲート電極1206を作製している。ここで、従来技術の場合、応力用SiN膜1204の膨張応力で活性シリコン膜1203に応力をかける。また、スペーサ絶縁膜1205は、ゲートLDD構造作製のスペーサであり、例えば、SiO2又はSiNからなり、ゲート電極1206は、例えば、ポリシリコン、シリサイド又は高融点金属からなる。

【0006】

さらに、SiGe層及びSiC層を用いる半導体装置として、半導体基板と、半導体基板上に形成される積層体であるゲート構造と、半導体基板の表面内に形成される電極領域と、この電極領域の直下部に形成される低比誘電率層とを備えている半導体装置が知られている(例えば、特許文献1参照)。この場合、電極領域はp型SiGe層であり、低比誘電率層はSiC層であって、SiGe層の直下部にSiC層が形成されている。

【0007】

CMOSデバイス作製の前処理としての上記自然酸化膜の除去には、従来、フッ酸等を使用する湿式処理や、1000℃程度の高温による水素アニール処理が用いられていた。しかし、この湿式処理では、微細なホールの底部まで液が浸透し難いこと及びウェハ表面に好ましくないフッ素が残留すること等の問題があった。そのため、近年の処理温度の低温化と半導体デバイスの微細化に伴って、乾式処理による自然酸化膜除去の要求がある。

【0008】

このような低温での乾式処理による自然酸化膜除去方法の一つとして、少なくとも水素原子を含むガスを高周波放電させ、プラズマを発生させて生成した少なくとも水素を含むラジカルと三フッ化窒素ガス(NF3ガス)との混合物から生成したフッ化アンモニウムをエッチングガスとして用いたドライエッチング方法が知られている(例えば、特許文献2及び3参照)。このドライエッチング方法では、前記エッチングガスと基板表面の自然酸化膜とを反応せしめることで基板表面にケイフッ化アンモニウム((NH4)2SiF6)等の反応生成物を生じせしめ、この反応生成物を所定の温度に加熱して分解、蒸発させて除去することにより、酸化膜のない清浄な基板表面を得ている。

【0009】

特許文献3の場合、自然酸化物を除去するために要する温度は120〜150℃であり、自然酸化物の除去処理に要する時間は30分強である。しかし、自然酸化膜を除去処理した基材を取り出すために、室温まで冷却する必要があり、その待機時間を入れると、時間がかかり過ぎるという問題がある。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2009−26972号公報

【特許文献2】特開2003−133284号公報

【特許文献3】特開2006−229085号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明の課題は、上述の従来技術の問題点を解決することにあり、CMOSデバイスを作製する場合において、同じ特性のn−MOSトランジスタとp−MOSトランジスタとを有し、n−MOSトランジスタに最適な応力による歪特性をもたらすSiGe膜と、p−MOSトランジスタに最適な応力による歪特性をもたらすSiC膜とを同一シリコン基材上に備えた、小さいサイズのトランジスタに対しても、最適な特性を持つCMOSデバイス用のシリコンウェハの製造方法を提供することにある。

【課題を解決するための手段】

【0012】

本発明のCMOSデバイス用シリコンウェハの製造方法は、同一シリコン基材の表面に、選択エピタキシャル法又はイオン注入法を用い、SiGe膜及びSiC膜を分離して形成し、CMOSデバイスを構成するために必要なn−MOSデバイス、及びp−MOSデバイスを同一シリコン基材上に島状に製造することを特徴とする。

【0013】

前記シリコン基材が、シリコン基板又はSOI基板であることを特徴とする。

【0014】

前記SiGe膜及びSiC膜に関し、最初にSiGe膜を形成し、次いでSiC膜を形成するか、又は最初にSiC膜を形成し、次いでSiGe膜を形成することを特徴とする。

【0015】

本発明のシリコンウェハの製造方法は、隣接するシリコン基材同士の間隔を2mm乃至5mmに設定して配置された複数のシリコン基材の表面上の自然酸化膜をフッ化水素又はフッ化アンモニウムと反応させる第1の工程と、前記反応によって生じた反応生成物を200℃以上、530℃以下で加熱・蒸発させて除去する第2の工程とを有するドライエッチング工程を実施してシリコン基材表面の自然酸化膜を除去し、同一シリコン基材の表面に、選択エピタキシャル法又はイオン注入法を用い、SiGe膜及びSiC膜を分離して形成し、CMOSデバイスを構成するために必要なn−MOSデバイス、及びp−MOSデバイスを同一シリコン基材上に島状に製造することを特徴とする。

【0016】

前記隣接するシリコン基材同士の間隔が2mm未満であると、作業が困難であり、5mmを超えると、自然酸化膜の除去が困難になる。また、前記反応生成物の加熱・蒸発温度が200℃未満であると、反応生成物の蒸発が困難であり、反応生成物が残留しやすいという問題があり、530℃を超えると、現在の装置構成上好ましくない。

【0017】

前記第2の工程における圧力を大気圧に設定することを特徴とし、また、前記ドライエッチング工程を、表面から自然酸化膜を除去したシリコン基材表面上にさらに成膜する次工程を実施する成膜装置内で実施することを特徴とする。これにより、シリコンウェハの製造工程がコンパクトになる。

【発明の効果】

【0018】

本発明によれば、同一のシリコン基材上のn−MOSトランジスタ作製部にSiGe膜を、また、p−MOSトランジスタ作製部にSiC膜をそれぞれ分離して選択的エピタキシャル成長することによって、最適な歪特性をもつn−MOSトランジスタと最適な歪特性を持つp−MOSトランジスタとを島状に製造できるので、CMOSデバイスとして最適な動作をするデバイスの作製が可能となるという効果を奏する。

【図面の簡単な説明】

【0019】

【図1】本発明のCMOSデバイス用シリコンウェハを製造する前処理として使用できる自然酸化膜の除去方法に用いるドライエッチング装置の一構成例を示す模式的断面図。

【図2】図1に示したドライエッチング装置によりエッチング処理した後のウェハを加熱処理して反応生成物を蒸発せしめる縦型炉(高温炉)の一構成例を示す模式的断面図。

【図3】ウェハを載置するウェハボートの一構成例を示す模式的断面図であり、(a)は従来のウェハボートの模式的断面図、(b)は本発明における前処理で用いることができるウェハボートの模式的断面図。

【図4】図1に示すドライエッチング装置及び図2に示す高温炉を用いて自然酸化膜の除去を実施するプロセスを説明するためのフローチャートであり、(a)はドライエッチング装置での処理、(b)は高温炉での処理。

【図5】本発明のCMOSデバイス用シリコンウェハを製造する際のSiGe膜成長装置の一構成例を示す模式的断面図。

【図6】本発明のCMOSデバイス用シリコンウェハを製造する際のSiGe膜成長装置とその前処理としての自然酸化膜除去装置とを組み合わせた場合の一構成例を示す模式的断面図。

【図7】本発明の実施の形態1のプロセスにおけるSiGe膜成長装置での処理を説明するためのフローチャート。

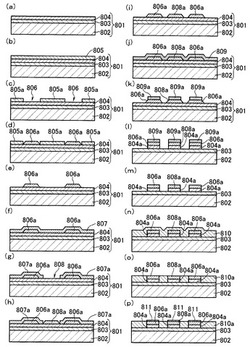

【図8】本発明の実施の形態1における選択エピタキシャル法によるSiGe膜及びSiC膜の成長プロセスを説明するための工程図。

【図9】本発明の実施の形態2のプロセスにおける自然酸化物除去処理及びSiGe膜成長装置での処理を説明するためのフローチャート。

【図10】本発明の実施の形態2における選択エピタキシャル法によるSiGe膜及びSiC膜の成長プロセスを説明するための工程図。

【図11】本明の実施の形態3におけるイオン注入法によるGeイオン注入及びCイオン注入プロセスを説明するための工程図。

【図12】従来技術によるCMOS用シリコンウェハ。

【発明を実施するための形態】

【0020】

まず、本発明に従ってCMOSデバイス用シリコンウェハを製造する際に、その前処理として実施する自然酸化膜の除去方法について説明し、次いでCMOS用シリコンウェハの製造方法について説明する。

【0021】

図1は、本発明に従ってCMOSデバイス用シリコンウェハを製造する際に、その前処理として実施することができる自然酸化膜の除去方法に用いるドライエッチング装置1の一構成例を示す模式的断面図である。ドライエッチング装置1は、例えば、50枚程度のバッチ単位でシリコン基材101の自然酸化膜の除去処理を行うものであり、エッチング室102と、エッチング室内へ導入される反応ガス(N2、NH3)を励起して活性種(ラジカル)を発生させるためのマイクロ波励起機構103と、エッチング室と連結されているロードロック室104と、ロードロック室と連結されているクリーンブース105とで構成されている。エッチング室102内には、図面上では、処理されるシリコン基材101を所定の間隔で載置してある石英製ウェハボート106(図3(b)参照)が、ロードロック室104から搬送され、配置されている状態が示されている。エッチング室102の外周には、ヒータ107等の加熱手段が設けられ、また、このエッチング室には、エッチング室内を排気できるように真空ポンプ108が取り付けられている。ロードロック室104には、室内を排気するための真空ポンプ109が取り付けられている。クリーンブース105内には、ウェハカセット110が載置され、このウェハカセットをロボット111によりクリーンブース105とロードロック室104との間を搬送できるように構成されている。

【0022】

図2は、図1に示したドライエッチング装置1によりエッチング処理した後のウェハを加熱処理して揮発性反応生成物を蒸発せしめる縦型炉(高温炉)の一構成例を示す模式的断面図である。この縦型炉2は、例えば、チャンバ201と、チャンバに連結されているロードロック室202と、ロードロック室と連結されているクリーンブース203とで構成されている。チャンバ201内には、図面上では、処理されるシリコン基材204を所定の間隔で載置してある石英製ウェハボート205(図3(b))が、ロードロック室202から搬送され、配置されている状態が示されている。チャンバ201の外周には、ヒータ206等の加熱手段が設けられ、また、チャンバ201には、チャンバ内を排気できるように真空ポンプ207が取り付けられている。ロードロック室202には、室内を排気するための真空ポンプ208が取り付けられている。クリーンブース203内には、ウェハカセット209が載置され、このウェハカセットをロボット210によりクリーンブース203とロードロック室202との間を搬送できるように構成されている。

【0023】

上記したように、ドライエッチング装置1と縦型炉2とを別々に示して説明したが、これらを組み合わせて一つの自然酸化膜除去装置としてもよいことは勿論である。

【0024】

図3はシリコン基材の載置されている石英製ウェハボートの一構成例を示す模式的断面図であり、(a)は従来のウェハボートを示し、(b)は本発明で用いるウェハボートを示す。図3(a)において、301はシリコン基材、302はウェハボートであり、隣接するシリコン基材同士の間隔は、5mmを超えているが、図3(b)において、303はシリコン基材、304はウェハボートであり、隣接するシリコン基材同士の間隔は2mm乃至5mmの範囲で等間隔に設定されていることが好ましい。

【0025】

以下、図3(b)に示すウェハボート304を用い、図1に示すドライエッチング装置1及び図2に示す縦型炉2を用いて自然酸化膜除去を実施するプロセスについて、エッチング装置での処理を示すフローチャート(図4(a))及び高温炉での処理を示すフローチャート(図4(b))を参照して説明する。

【0026】

例えば、図4(a)に示すように、まず、図1に示すドライエッチング装置1のクリーンブース105内に載置されているウェハカセット110をロボット111によりロードロック室104へ移送し、ここでシリコン基材101をウェハカセット110から石英製ウェハボート106(図3(b)のウェハボート304)に移し、ロードロック室104内を所定の圧力(例えば、200〜400Pa)まで排気する。次いで、ウェハボート106をエッチング室102内に移送した後、反応ガス(例えば、窒素ガス、アンモニアガス等)を導入する際に、マイクロ波励起機構103によりマイクロ波を印加(5〜10分間、また、1〜2kW、好ましくは1.8kW投入)し、励起して生成したHラジカルをエッチング室102内へ導入し、温度25〜50℃で反応(エッチング)を行う。この反応ガスの導入量は、一般に4000〜6000sccmであればよい。また、反応ガスとしての三フッ化窒素(NF3)ガスは、マイクロ波励起機構103を介さずに直接エッチング室102内へ導入する(一般に、3000〜4000sccm)。また、反応ガスとしてのアンモニアガス:窒素ガス:三フッ化窒素ガスの混合比は、一般には1〜3:5〜7:2〜4、好ましくは2:6:3であって、その合計流量が13〜15リットル/分、好ましくは14.4リットル/分であれば良い。このような条件下で所定の時間(2〜5分)エッチングする。

【0027】

上記エッチングプロセスにおいては、アンモニアガスと窒素ガスとの混合ガスを励起して得られる水素ラジカルと三フッ化窒素ガスとの反応により、エッチング室102内でフッ化アンモニウムを生成せしめ、このフッ化アンモニウムとシリコン基材101上の自然酸化膜との反応により、ケイフッ化アンモニウムを形成せしめる。これは、以下の反応式で示される。

【0028】

[化1]

NH3 → NH2 + H*

H* + NF3 → NH4F

SiO2 + NH4F → H2O + (NH4)2SiF6

【0029】

エッチングの終了後、反応ガスの導入及びマイクロ波の印加を停止し、エッチング室102の排気を行う。ヒータ107に通電してシリコン基材101を200℃に加熱する。その後、ヒータ107への通電を停止し、エッチング室102中のウェハボート106をロードロック室104内へ移送し、このボートからシリコン基材101をウェハカセット110に移す。

【0030】

次いで、図4(b)に示すように、上記したようにして得られたケイフッ化アンモニウムが表面に形成されたシリコン基材が載置されている図1に示すウェハカセット110(図2に示すウェハカセット209)を、図2に示す縦型炉2のクリーンブース203からロボット210によりロードロック室202内へ移送し、ここでシリコン基材204をウェハカセット209からウェハボート205(図3(b)のウェハボート304)に移し、このウェハボートを、所定の温度及び圧力(例えば、200℃を超える温度及び大気圧程度の圧力)に保持されているチャンバ(高温炉)201内に移送した後、チャンバ内を排気し、30分間保持し、ケイフッ化アンモニウムを蒸発させる。次いで、チャンバ内に窒素ガス等のパージガスを流しながら、チャンバ201内をベントした後、チャンバ内のウェハボート205をロードロック室202内に移送し、このボートからシリコン基材204をウェハカセット209に移し、このカセットをクリーンブース203内へ移送して自然酸化膜の除去プロセスを終了する。この全工程の処理時間は、従来よりも短かった。

【0031】

上記のようにして自然酸化膜を除去したシリコン基材を用いてCMOSデバイス用シリコンウェハを製造するために、まず、図5に示すSiGe膜成長装置により、基材表面にSiGe膜を形成する。図5にその一構成例の模式的断面図を示すSiGe膜成長装置5は、50枚程度のバッチ単位でシリコン基材表面にSiGe膜の形成を行うものであり、内部にシリコン基材501を設置できるようになっており、かつ反応ガス(例えば、H2、SiH4、GeH4ガス等)を導入できるように構成されているSiGe成膜室502と、この成膜室と連結されているロードロック室503と、このロードロック室と連結されているクリーンブース504とで構成されている。成膜室502には、図面上では、処理されるシリコン基材501を所定の間隔で載置してあるウェハボート505が、ロードロック室503から搬送され、設置されている状態が示されている。成膜室502の外周には、ヒータ506等の加熱手段が設けられ、また、この成膜室には、室内を排気するための真空ポンプ507が取り付けられている。ロードロック室503には、室内を排気するための真空ポンプ508が取り付けられている。クリーンブース504内には、ウェハカセット509が設置された状態が示され、このウェハカセットをロボット510によりクリーンブース504とロードロック室503との間を搬送できるように構成されている。

【0032】

図6は、上記した図1に示す自然酸化膜除去装置(エッチング室102)と図5に示すSiGe膜成長装置5とを組み合わせた場合の一構成例を示す模式的断面図である。この自然酸化膜除去装置及びSiGe膜成長装置については、上記図1及び図5と同じであるので、説明を省略する。なお、同じ構成要素に対しては同じ参照番号を付してある。

【0033】

実施の形態1:

本実施の形態では、高速デバイス用としてSOI(silicon on insulator)基板を用い、その上にSiGe膜/SiC膜を成長せしめたCMOSデバイス用シリコンウェハの製造方法について、SiGe膜成長装置での処理を示すフローチャート(図7)及びSiGe膜及びSiC膜の成長プロセスを説明するための工程図(図8(a)〜(p))を参照して説明する。

【0034】

図7に示すように、まず、図5に示すSiGe膜成長装置5のクリーンブース504内に載置されているウェハカセット509をロボット510によりロードロック室503へ移送し、ここでシリコン基材501をウェハカセット509から石英製ウェハボート505に移し、ロードロック室内を所定の圧力(例えば、10〜10−2Pa)まで排気する。次いで、ウェハボート505をSiGe成膜室(SiGe成長室)502内に移送した後、ヒータ506に通電してシリコン基材501を例えば450℃に加熱し、反応ガス(例えば、H2、SiH4、GeH4等)を導入しSiGe膜の成長を行う。この反応ガスの導入量は、一般に100〜2000sccmであればよい。また、反応ガスとしての例えば、H2:SiH4:GeH4ガスの混合比は、一般には、10〜1000:1〜10:1〜10、好ましくは20:1:1であって、その合計流量が0.1〜2リットル/分、好ましくは0.5リットル/分であれば良い。このような条件下で所定の時間(10〜120分)成膜する。

【0035】

次いで、ヒータへの通電を停止すると共に、反応ガスの導入を停止し、SiGe成膜室502内を排気した後、ウェハボート505をロードロック室503に移送し、SiGe成膜されたシリコン基材501をウェハボート505からウェハカセット509へ移す。その後、以下述べるように、SiGe膜及びSiC膜の成長を行う。

【0036】

例えば図8の工程図に示すように、まず、SOI基板801を準備する(図8(a))。このSOI基板801は、シリコン基板802と表面のシリコン層804との間にSiO2膜(BOX酸化膜)803が挿入された構造の基板である。本実施の形態では、シリコン基板802上に100〜1000nm程度のBOX酸化膜803及び10〜100nm程度のシリコン層804を備えたSOI801基板を用いる。

【0037】

このSOI基板801上に、SiGe選択成長時のマスクとなるシリコン酸化膜805を厚さ100〜1000nm程度で形成した(図8(b))後、この酸化膜805に対して、n−MOSトランジスタ(n−チャネルトランジスタ)作製領域806の部分の酸化膜を取り除くパターンニングを行い、この作製領域806のみにシリコンが露出し、残りの部分がマスク酸化膜805aで覆われた状態とする(図8((c))。

【0038】

この状態で、酸化膜805が除去されてシリコンが露出した作製領域806の表面上に、CVD法により、Si原子含有ガス(例えば、SiH4ガス又はSi2H6ガス等)、Ge原子含有ガス(例えば、GeH4ガス等)、及びハロゲンガス(例えば、Cl2ガス等)を用い、成長温度450〜650℃程度で選択的エピタキシャル成長を実施し、膜厚10〜100nm程度のSiGe膜806aを成長せしめる(図8(d))。成長温度が450℃未満であると膜の成長が起こらず、650℃を超えるとマスク酸化膜805a上にも膜の成長が起こり、ポリシリコンが生じてしまう。この選択的エピタキシャル成長はハロゲンを用いる方法でも用いない方法でもいずれでも良い。この選択的エピタキシャル成長の場合、Siに対するGeの濃度は作製するn−MOSトランジスタに必要とされる特性に依存するが、通常5〜80%程度、好ましくは10%〜50%程度であれば、所望の特性が得られる。

【0039】

この状態で一旦マスク酸化膜805aを除去し(図8(e))、次いでSiC選択的エピタキシャル成長用のマスクとなる酸化膜(SiO2膜)807を100〜1000nm程度の厚さで形成した(図8(f))後、この酸化膜807に対して、p−MOSトランジスタ(p−チャネルトランジスタ)作製領域808の酸化膜を取り除くパターンニングを行い、この作製領域808のみにシリコンが露出し、残りの部分がマスク酸化膜807aで覆われている状態とする(図8(g))。

【0040】

この状態で、酸化膜807が除去されてシリコンが露出した作製領域808の表面上に、CVD法により、Si原子含有ガス(例えば、SiH4ガス又はSi2H6ガス)、C原子含有ガス(例えば、CH3SiH5ガス又はC3H8ガス)、及びハロゲンガス(例えば、Cl2ガス)を用い、成長温度500〜700℃程度で選択的エピタキシャル成長を実施し、膜厚10〜100nm程度のSiC膜808aを成長せしめる(図8(h))。成長温度が500℃未満であると膜の成長が起こらず、700℃を超えるとマスク酸化膜807a上にも膜の成長が起こり、ポリシリコンが生じてしまう。この選択的エピタキシャル成長の場合、Siに対するCの濃度は作製するp−MOSトランジスタに必要とされる特性に依存するが、通常0.5〜3%程度、好ましくは1〜2%程度であれば、所望の特性が得られる。0.5%未満であると所望の特性が得られず、また、3%を超えると歪みが大きくなり過ぎ、膜の成長中に歪みに耐えられなくなり、結晶が割れてしまう。

【0041】

この状態で一旦マスク酸化膜807aを除去する(図8(i))。

【0042】

上記例では、最初にSiGe膜806aを作製し、次いでSiC膜808aを作製したが、この順番は逆であっても良い。

【0043】

次いで、SOI基板801の表面全体に、この基板表層のシリコン層804の所定の領域を除去する際のマスクとして、窒化膜(SiN膜)809を100〜1000nm程度で形成した(図8(j))後、SiGe膜806a及びSiC膜808aが形成されている領域に対抗する表面上の窒化膜809aを残すように窒化膜809をパターンニングする(図8(k))。このシリコン層の除去は、CMOSデバイス特性の改善のためである。この状態で、シリコン層804の選択的エッチングを行い、シリコン基板802上のBOX酸化膜803の上に、シリコン層804a上に形成されたSiGe形成部分(n−MOSトランジスタ作製領域806a)とシリコン層804a上に形成されたSiC形成部分(p−MOSトランジスタ作製領域808a)とが島状に離間して配置されるようにする(図8(l))。次いで、窒化膜809aを除去した(図8(m))後、各島が埋まる程度のシリコン酸化膜810を、例えば200〜2000nm程度の厚さで形成する(図8(n))。このシリコン酸化膜形成方法は、例えばHDP−CVD法で行うことができる。

【0044】

シリコン酸化膜810の形成後、CMP処理を行い、それぞれの島の頭が出るレベルまでシリコン酸化膜810を研磨・除去する(図8(o))。ここでは、SiGe膜806a部分とSiC膜808a部分とがシリコン酸化膜810aによって分離された形に見える。SiGe膜806a部分とSiC膜808a部分とが同じ一つの基板上に島状に形成されている。

【0045】

次いで、シリコンの選択成長を行う。SiGe膜806a部分とSiC膜808a部分との表面上に、アクティブシリコン層811を炉内圧力10〜0.1Pa、成長温度450〜600℃、水素流量100〜1000sccm、シラン流量10〜200sccm、成長時間10〜120分の条件で選択成長により形成する(図8(p))。このシリコン層811の厚さはトランジスタに求められる特性に依存するが、通常、10〜100nm程度の範囲であれば所望の特性が得られる。

【0046】

その後、500〜800℃で熱処理を実施し、SiGe膜806a内とSiC膜808a内の歪を緩和させ、各膜の上に形成したシリコン層811に歪応力を発生させる。SiGe膜及びその上のシリコンがn−MOSトランジスタ作製部位となり、SiC膜及びその上のシリコンがp−MOSトランジスタ作製部位となる。かくして得られたシリコンウェハは、それぞれのMOSトランジスタに最適なキャリア移動度を得られる点から、CMOSデバイス用として有用であることが確認できた。

【0047】

なお、上記SiGe膜及びSiC膜に関し、SiGe膜の場合は、Ge原子径がSi原子径より大きいため、シリコン層上に成長して2層となったときに歪みが生じて、引っ張り方向に応力がかかり、電子のスピードが速くなるので、n−チャネルトランジスタとして適しており、また、SiCの場合は、C原子径はSi原子径より小さいため、シリコン層上に成長して2層となったときに縮こまる方向(圧縮方向)の応力が掛かり、応力を外側に分散させ、ホールのスピードが速くなるので、ホールをチャネルとするのに良く、p−チャネルトランジスタとして適している。

【0048】

実施の形態2:

本実施の形態では、SOI基板の代わりに通常のシリコン基板を用いて実施の形態1と同様に、SiGe膜/SiC膜が形成されたCMOSデバイス用シリコンウェハを製造する方法について、SiGe膜の成長プロセスのフローチャート及びSiGe膜及びSiC膜の成長プロセスの工程図をそれぞれ示す図9及び図10(a)〜(l)を参照して説明する。

【0049】

例えば、図9に示すように、図4(a)の場合と同様に、まず、図1に示すドライエッチング装置1のクリーンブース105内に載置されているウェハカセット110をロボット111によりロードロック室104へ移送し、ここでシリコン基材101をウェハカセット110からウェハボート106(図3(b)のウェハボート304)に移し、ロードロック室104内を所定の圧力まで排気する。次いで、ウェハボート106をエッチング室102内に移送した後、反応ガス(例えば、窒素ガス、アンモニアガス等)をエッチング室102内へ導入する際に、マイクロ波励起機構103によりマイクロ波を印加(5〜10分間、また、1〜2kW、好ましくは1.8kW投入)して、励起して生成したHラジカルをエッチング室102内へ導入し、圧力200〜400Pa、温度25〜50℃で反応(エッチング)を行う。この反応ガスの導入量は、一般に4000〜6000sccmであればよい。また、反応ガスとしての三フッ化窒素ガスは、マイクロ波励起機構103を介さずに直接エッチング室102内へ導入する(一般に、3000〜4000sccm)。また、反応ガスとしてのアンモニアガス:窒素ガス:三フッ化窒素ガスの混合比は、一般には、1〜3:5〜7:2〜4、好ましくは2:6:3であって、その合計流量が13〜15リットル/分、好ましくは14.4リットル/分であれば良い。このような条件下で所定の時間(2〜5分)エッチングする。

【0050】

上記エッチングプロセスにおいては、アンモニアガスと窒素ガスとの混合ガスを励起して得られる水素ラジカルと三フッ化窒素ガスとの反応により、エッチング室102内でフッ化アンモニウムを生成せしめ、このフッ化アンモニウムとシリコン基材101上の自然酸化膜との反応により、ケイフッ化アンモニウムを形成せしめる。これは、上記の反応式で示される。

【0051】

エッチングの終了後、反応ガスの導入及びマイクロ波の印加を停止し、エッチング室102の排気を行う。その後、ヒータ107に通電してシリコン基材101を200℃程度に加熱しても良い。通電した場合は、ヒータ107への通電を停止した後、エッチング室102中のウェハボート106をロードロック室104内へ移送し、次いでこのボートを図5に示すSiGe成膜室502に移送する。

【0052】

ウェハボートを成膜室502内に移送した後、ヒータ506に通電してシリコン基材501を例えば500℃に加熱し、反応ガス(例えば、H2、SiH4、GeH4等)を導入し、SiGe膜の成長を行う。この反応ガスの導入量、混合比及び合計流量は、上記した通りであればよい。

【0053】

次いで、ヒータ506への通電を停止すると共に、反応ガスの導入を停止し、SiGe成膜室502内を排気する。その後、ウェハボート505をロードロック室503に移送し、SiGe成膜されたシリコン基材501をウェハボート505からウェハカセット509へ移す。

【0054】

以下、SiGe膜/SiC膜を成長せしめたCMOSデバイス用シリコンウェハの製造方法について、SiGe膜及びSiC膜の成長プロセスの工程図を示す図10(a)〜(l)を参照して説明する。

【0055】

まず、シリコン基板1001を準備する(図10(a))。このシリコン基板1001上に、SiGe選択成長時のマスクとなるシリコン酸化膜1002を厚さ100〜1000nm程度で形成した(図10(b))後、この酸化膜1002に対して、n−MOSトランジスタ(n−チャネルトランジスタ)作製領域1003の酸化膜を取り除くパターンニングを行い、この作製領域1003のみにシリコンが露出し、残りの部分がマスク酸化膜1002aで覆われた状態とする(図10((c))。

【0056】

この状態で、シリコン酸化膜1002が除去されてシリコンが露出した作製領域1003の表面上に、CVD法により、Si原子含有ガス(例えば、SiH4ガス又はSi2H6ガス等)、Ge原子含有ガス(例えば、GeH4ガス等)、及びハロゲンガス(Cl2ガス等)を用い、成長温度450〜650℃程度で選択的エピタキシャル成長を実施し、膜厚10〜100nm程度のSiGe膜1003aを成長せしめる(図10(d))。成膜温度が450℃未満であると膜の成長が起こらず、650℃を超えるとマスク酸化膜1002a上にも膜の成長が起こり、ポリシリコンが生じてしまう。この選択的エピタキシャル成長はハロゲンを用いる方法でも用いない方法でもいずれでも良い。この選択的エピタキシャル成長の場合、Siに対するGeの濃度は上記した通りであれば、所望の特性が得られる。

【0057】

この状態で一旦マスク酸化膜1002aを除去し(図10(e))、次いでSiC選択成長用のマスク酸化膜(SiO2膜)1004を100〜1000nm程度の厚さで形成した(図10(f))後、この酸化膜1004に対して、p−MOSトランジスタ(p−チャネルトランジスタ)作製領域1005の酸化膜を取り除くパターンニングを行い、この作製領域1005のみにシリコンが露出し、残りの部分がマスク酸化膜1004aで覆われた状態とする(図10(g))。

【0058】

この状態で、酸化膜1004が除去されてシリコンが露出した作製領域1005の表面上に、CVD法により、Si原子含有ガス(例えば、SiH4ガス又はSi2H6ガス等)、C原子含有ガス(例えば、CH3SiH5ガス又はC3H8ガス等)、及びハロゲンガス(例えば、Cl2ガス等)を用い、成長温度500〜700℃程度で選択的エピタキシャル成長を実施し、膜厚10〜100nm程度のSiC膜1005aを成長せしめる(図10(h))。成長温度が500℃未満であると膜の成長が起こらず、700℃を超えるとマスク酸化膜1004a上にも膜の成長が起こり、ポリシリコンが生じてしまう。この選択的エピタキシャル成長の場合、Siに対するCの濃度は上記した通りであれば、所望の特性が得られる。

【0059】

この状態で一旦マスク酸化膜1004aを除去し、シリコン基板1001上のSiGe形成部分(n−MOSトランジスタ作製部分1003a)とSiC形成部分(p−MOSトランジスタ作製部分1005a)とが島状に離間して配置されるようにする(図10(i))。

【0060】

上記例では、最初にSiGe膜1003aを作製し、次いでSiC膜1005aを作製したが、この順番は逆であっても良い。

【0061】

次いで、シリコン基板1001の表面全体に、各島が埋まる程度のシリコン酸化膜1006を、例えば200〜2000nm程度の厚さで成長せしめる(図10(j))。このシリコン酸化膜形成方法は、例えばHDP−CVD法で行うことができる。

【0062】

酸化膜1006の形成後、CMP処理を行い、それぞれの島の頭が出るレベルまでシリコン酸化膜1006を研磨・除去する(図10(k))。ここでは、SiGe膜1003a部分とSiC膜1005a部分とが酸化膜1006aによって分離された形に見える。SiGe膜1003a部分とSiC膜1005a部分とが同じ一つの基板上に島状に形成されている。

【0063】

次いで、シリコンの選択成長を行った。SiGe膜1003a部分とSiC膜1005a部分との表面上に、アクティブシリコン層を炉内圧力10〜0.1Pa、成長温度450〜600℃、水素流量100〜1000sccm、シラン流量10〜200sccm、成長時間10〜120分の条件で選択成長により形成する(図10(l))。このシリコン層の厚さはトランジスタに求められる特性に依存するが、通常、10〜100nm程度の範囲であれば所望の特性が得られる。

【0064】

その後、500〜800℃程度の温度で熱処理を実施し、SiGe膜1003a内とSiC膜1005a内の歪を緩和させ、各膜の上に形成したシリコン層1007に歪応力を発生させた。SiGe膜及びその上のシリコンがn−MOSトランジスタ作製部位となり、SiC膜及びその上のシリコンがp−MOSトランジスタ作製部位となる。かくして得られたシリコンウェハは、上記したように、それぞれのMOSトランジスタに最適なキャリア移動度が得られる点から、CMOSデバイス用として有用であることが確認できた。

【0065】

実施の形態3:

本実施の形態は、イオン注入法を用い、SOI基板の表層のシリコン層内にGeイオン及びCイオンを注入し、BOX酸化膜上に、SiGe膜/SiC膜を島状に形成せしめたCMOSデバイス用シリコンウェハの製造方法に係わり、この点について、図11(a)〜(p)を参照して説明する。

【0066】

まず、SOI基板1101を準備する(図11(a))。このSOI基板1101は、実施の形態1で説明したように、シリコン基板1102と表面のシリコン層1104との間にSiO2膜(BOX酸化膜)1103が挿入された構造の基板である。本実施の形態では、シリコン基板1102上に100〜1000nm程度のBOX酸化膜1103及び10〜100nm程度のシリコン層1104を備えたSOI基板1101を用いる。

【0067】

このSOI基板1101上に、Geイオン注入時のマスクとなるシリコン酸化膜1105を厚さ100〜1000nm程度で形成した(図11(b))後、この酸化膜1105に対して、n−MOSトランジスタ(n−チャネルトランジスタ)作製領域の酸化膜を取り除くパターンニングを行い、この領域のみにシリコンが露出し、残りの領域がマスク酸化膜1105aで覆われた状態とする(図11((c))。

【0068】

この状態で、酸化膜1105が除去されたn−MOSトランジスタ作製領域のシリコン層に対して、A方向からGeイオンを注入する(図11((d))。この際、エネルギー:10〜50keV程度、及びイオン注入量:1E14〜1E17cm−2程度として行う。この場合、シリコン層1104に対するGeイオン注入量は、体積換算でシリコン層中のGe濃度が5〜50%程度となるようにした。この濃度であれば、n−MOSトランジスタに必要とされる所望の特性が得られる。

【0069】

次いで、マスク酸化膜1105aをエッチング除去し、Geイオンが注入されたGeイオン注入シリコン領域層1104aを有するシリコン層1104を形成する(図11(e))。

【0070】

このシリコン層1104の全表面上に、Cイオン注入時のマスクとなるシリコン酸化膜1106を100〜1000nm程度の厚さで形成し(図11(f))、p−MOSトランジスタ(p−チャネルトランジスタ)作製領域の酸化膜を取り除くパターニングを行い、この領域のみにシリコンが露出し、残りの領域がマスク酸化膜1106aで覆われた状態とする(図11(g))。

【0071】

この状態で、シリコン酸化膜1106が除去されたp−MOSトランジスタ作製領域のシリコン層に対して、B方向からCイオンを注入する(図11((h))。この際、エネルギー:10〜50keV程度、及び注入量:1E13〜1E16cm−2程度として行う。この場合、シリコン層に対するCイオン注入量は、体積換算でシリコン層中のGe濃度が0.5〜3.0%程度となるようにした。これによりp−MOSトランジスタに必要とされる所望の特性が得られる。

【0072】

マスクとして用いた酸化膜1106aを、エッチング除去し、Geイオン注入シリコン領域層1104a及びCイオン注入シリコン領域層1104bを有するシリコン層1104を得る(図11(i))。

【0073】

次いで、SOI基板表面上に薄い(10〜100nm程度)シリコン層1107をエピタキシャル成長させ(図11(j))、このシリコン層1107上に、シリコン層1107及び1104をエッチ除去する際のマスクとしての窒化シリコン膜1108を100〜1000nm程度の厚さで成長させた(図11(k))後、Geイオン注入シリコン領域層1104a及びCイオン注入シリコン領域層1104bの上の窒化膜を残すようにパターニングし、マスク窒化膜1108aを形成する(図11(l))。

【0074】

この状態で、シリコン層1107及び1104の選択シリコンエッチングを行い、SOI基板のBOX酸化膜1103上にGeイオン注入シリコン領域層1104a(n−MOSトランジスタ作製領域)とCイオン注入シリコン領域層1104b(p−MOSトランジスタ作製領域)とが島状に配置されるようにした(図11(m))後、マスク窒化膜1108aを除去する(図11(n))。その結果、窒化膜除去を実施したSOI基板のBOX酸化膜1103上に、Geイオン注入シリコン領域層1104aとCイオン注入シリコン領域層1104bとがそれぞれ表面の薄いシリコン層1107aと共に島状に離間して形成された。Geイオン注入シリコン領域層1104aとCイオン注入シリコン領域層1104bとが同じ一つの基板上に島状に形成されている。

【0075】

次いで、イオン活性化及びストレス緩和熱処理を実施し(図11(o))、シリコン層1107aに歪を導入する。この熱処理温度は、600〜1000℃で行う。かくして、Geイオンを注入した領域がn−MOSトランジスタ作製領域(n−チャネル(n−ch))となり、Cイオンを注入した領域がp−MOSトランジスタ作製領域(p−チャネル(p−ch))となる(図11(p))。

【0076】

実施の形態4:

本実施の形態では、図1に示すドライエッチング装置1及び図2に示す縦型炉2並びに図3(b)に示す石英製ウェハボート304を用い、図4(a)及び(b)に示すフローチャートに従ってシリコン基材表面上の自然酸化膜を除去した。このウェハボート304としては、複数枚のシリコン基材を、隣接する基材同士を2mm、3mm、4mm及び5mmの等間隔で載置できるように構成されたものをそれぞれ用い、また、比較のために1.5mm、5.5mm及び6mmの等間隔で載置できるように構成されたものをそれぞれ用いた。

【0077】

始めに、真空中で、アンモニアガスと窒素ガスとの混合ガスに対してマイクロ波を印加して励起し、水素ラジカルを得た。かくして得られた水素ラジカルと三フッ化窒素ガスとを反応させてフッ化アンモニウムガスを生成せしめ、エッチングガスとしてのこのフッ化アンモニウムガスとシリコン基材表面上の自然酸化膜とを反応させてケイフッ化アンモニウムを生成させた。このとき、シリコン基材を、アンモニアガス、窒素ガス、及び三フッ化窒素ガスの混合比が2:6:3で合計流量が14.4リットル/分、圧力が266Paの雰囲気に晒し、8分間励起マイクロ波を2.8kW投入して処理した。

【0078】

次に、表面にケイフッ化アンモニウムが形成されたシリコン基材を200℃に保持した高温炉のチャンバ内に入れ、チャンバ内を大気圧程度に設定し、30分間処理して、ケイフッ化アンモニウムを蒸発させた後、ウェハを取り出した。

【0079】

上記全工程の処理時間は、約30分であった。

【0080】

上記のようにして得たエッチング済みシリコン基材のエッチング量について、エッチング前のシリコン酸化膜の膜厚と、エッチング後のシリコン酸化膜の膜厚とをそれぞれ複数箇所測定し、各測定箇所におけるエッチング量(エッチング前とエッチング後との膜厚差)を測定した。その結果、隣接するシリコン基材同士を2mm、3mm、4mm及び5mmの間隔で載置できるように構成された各ウェハボートを用いた場合は、シリコン基材間に生じるエッチングガスがシリコン基材同士の間からシリコン基材の外側へ拡散し、流出するのが抑制されて、二次エッチングによるエッチング量の増大と面内均一化を実現できた。一方、隣接するシリコン基材同士を1.5mm、5.5mm及び6mmの間隔で載置できるように構成された各ウェハボートを用いた場合、1.5mmでは、好ましいエッチングができず、また、5.5mm及び6mmでは、間隔が広くなるに従って、シリコン基材間に生じるエッチングガスがシリコン基材同士の間からシリコン基材の外側へ拡散し、流出するために、二次エッチングの作用を利用できず、エッチング量の増大や面内均一化を達成できなかった。

【産業上の利用可能性】

【0081】

本発明によれば、CMOSデバイス作製工程で特別な追加工程を必要とせず、高速動作尚且つ低消費電力を達成できるCMOSデバイス用シリコンウェハの製造方法を提供できるので、半導体デバイス、特にCMOSデバイスの技術分野で利用可能である。

【符号の説明】

【0082】

1 ドライエッチング装置 2 縦型炉

5 膜成長装置 101 シリコン基材

102 エッチング室 103 マイクロ波励起機構

104 ロードロック室 105 クリーンブース

106 ウェハボート 107 ヒータ

108、109 真空ポンプ 110 ウェハカセット

111 ロボット 201 チャンバ

202 ロードロック室 203 クリーンブース

204 シリコン基材 205 ウェハボート

205 石英製ウェハボート 206 ヒータ

207、208 真空ポンプ 209 ウェハカセット

210 ロボット 304 ウェハボート

501 シリコン基材 502 成膜室

503 ロードロック室 504 クリーンブース

505 ウェハボート 506 ヒータ

507、508 真空ポンプ 509 ウェハカセット

510 ロボット 801 基板

802 シリコン基板 803 酸化膜

804 シリコン層 804a シリコン層

805 シリコン酸化膜 805a マスク酸化膜

806 n−MOSトランジスタ作製領域

806a SiGe膜(n−MOSトランジスタ作製領域)

807 酸化膜 807a マスク酸化膜

808 p−MOSトランジスタ作製領域

808a SiC膜(p−MOSトランジスタ作製領域)

809、809a 窒化膜 810、810a シリコン酸化膜

811 シリコン層 1001 シリコン基板

1002 シリコン酸化膜 1002a マスク酸化膜

1003 n−MOSトランジスタ作製領域

1003a SiGe膜(n−MOSトランジスタ作製部分)

1004 酸化膜 1004a マスク酸化膜

1005 p−MOSトランジスタ作製領域

1005a SiC膜(p−MOSトランジスタ作製部分)

1006 シリコン酸化膜 1006a 酸化膜

1007 シリコン層 1101 基板

1102 シリコン基板 1103 酸化膜

1104 シリコン層 1104a イオン注入シリコン領域層

1104b イオン注入シリコン領域層 1105 シリコン酸化膜

1105a マスク酸化膜 1106 シリコン酸化膜

1106a マスク酸化膜 1107 シリコン層

1107a シリコン層 1108 窒化膜

1108a マスク窒化膜 1201 Si基板

1202 SiO2膜 1203 活性シリコン膜

1204 応力用SiN膜 1205 スペーサ絶縁膜

1206 ゲート電極

【技術分野】

【0001】

本発明は、CMOSデバイス用シリコンウェハの製造方法に関し、特に、同一シリコン基材上にn−MOS用歪シリコン(n−MOSトランジスタ)とp−MOS用歪シリコン(p−MOSトランジスタ)とを一緒に製造する方法に関する。

【背景技術】

【0002】

近年、半導体デバイスの微細化が進められると共に、デバイスの動作速度の高速化、高集積化や、薄膜化の要求がますます高まっている。その際に、基材(例えば、シリコン基材)上に各種の薄膜を形成するが、このような種々の成膜工程、例えばCMOSデバイス製造工程においては、その下地となるシリコン基材表面に自然酸化膜(SiO2膜)が存在する場合、デバイス特性が悪化するため、成膜前に自然酸化膜等を除去し、活性状態の基材表面とし、その上に所望の薄膜を堆積させ、CMOSデバイス用シリコンウェハを製造することが必要である。

【0003】

また、従来、CMOSデバイスにおいて、歪シリコンデバイス用SiGe膜の形成された歪シリコンウェハでは、電子と正孔の両方に最適な移動度をもたらす歪を与えることができず、n−MOSトランジスタとp−MOSトランジスタとの特性のそろったCMOSデバイスを構成することが困難であった。最適なCMOSデバイスを構成する方法としては、それぞれのトランジスタに最適な歪を別個に与えるローカル歪による歪トランジスタの作製方法がある。しかし、このローカル歪トランジスタの作製方法では、それぞれのデバイスに最適なプロセスを用いるために、長く複雑なデバイス作製プロセスを必要としていた。また、応力膜を用いた歪シリコンデバイスでは、トランジスタのサイズが小さくなると、応力が必要なチャネル部分に充分な応力が掛らず、トランジスタの性能の向上が見込まれない欠点があった。

【0004】

CMOSデバイスを作製する場合、上記したように、ほぼ同じ特性のn−MOSトランジスタとp−MOSトランジスタとが必要になるが、従来技術の上記歪シリコン技術を用いた場合、n−MOSトランジスタとp−MOSトランジスタとの特性をあわせるのが難しく、より複雑なローカル歪技術を用いてもトランジスタのサイズが小さくなると効果が小さくなるという欠点を有していた。

【0005】

CMOSデバイスを作製する場合、従来は、一枚の同一シリコン基材の表面にSiGe膜及びSiC膜を同じように製造することができなかった。そのため、例えば、図12に示すように、Si基板1201上にSiO2膜(BOX酸化膜)1202、その上に活性シリコン膜1203(実際にデバイスを作製する部分)を作製して、通常のSOI基板とし、このSOI基板上に応力用SiN膜1204、スペーサ絶縁膜1205及びゲート電極1206を作製している。ここで、従来技術の場合、応力用SiN膜1204の膨張応力で活性シリコン膜1203に応力をかける。また、スペーサ絶縁膜1205は、ゲートLDD構造作製のスペーサであり、例えば、SiO2又はSiNからなり、ゲート電極1206は、例えば、ポリシリコン、シリサイド又は高融点金属からなる。

【0006】

さらに、SiGe層及びSiC層を用いる半導体装置として、半導体基板と、半導体基板上に形成される積層体であるゲート構造と、半導体基板の表面内に形成される電極領域と、この電極領域の直下部に形成される低比誘電率層とを備えている半導体装置が知られている(例えば、特許文献1参照)。この場合、電極領域はp型SiGe層であり、低比誘電率層はSiC層であって、SiGe層の直下部にSiC層が形成されている。

【0007】

CMOSデバイス作製の前処理としての上記自然酸化膜の除去には、従来、フッ酸等を使用する湿式処理や、1000℃程度の高温による水素アニール処理が用いられていた。しかし、この湿式処理では、微細なホールの底部まで液が浸透し難いこと及びウェハ表面に好ましくないフッ素が残留すること等の問題があった。そのため、近年の処理温度の低温化と半導体デバイスの微細化に伴って、乾式処理による自然酸化膜除去の要求がある。

【0008】

このような低温での乾式処理による自然酸化膜除去方法の一つとして、少なくとも水素原子を含むガスを高周波放電させ、プラズマを発生させて生成した少なくとも水素を含むラジカルと三フッ化窒素ガス(NF3ガス)との混合物から生成したフッ化アンモニウムをエッチングガスとして用いたドライエッチング方法が知られている(例えば、特許文献2及び3参照)。このドライエッチング方法では、前記エッチングガスと基板表面の自然酸化膜とを反応せしめることで基板表面にケイフッ化アンモニウム((NH4)2SiF6)等の反応生成物を生じせしめ、この反応生成物を所定の温度に加熱して分解、蒸発させて除去することにより、酸化膜のない清浄な基板表面を得ている。

【0009】

特許文献3の場合、自然酸化物を除去するために要する温度は120〜150℃であり、自然酸化物の除去処理に要する時間は30分強である。しかし、自然酸化膜を除去処理した基材を取り出すために、室温まで冷却する必要があり、その待機時間を入れると、時間がかかり過ぎるという問題がある。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2009−26972号公報

【特許文献2】特開2003−133284号公報

【特許文献3】特開2006−229085号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明の課題は、上述の従来技術の問題点を解決することにあり、CMOSデバイスを作製する場合において、同じ特性のn−MOSトランジスタとp−MOSトランジスタとを有し、n−MOSトランジスタに最適な応力による歪特性をもたらすSiGe膜と、p−MOSトランジスタに最適な応力による歪特性をもたらすSiC膜とを同一シリコン基材上に備えた、小さいサイズのトランジスタに対しても、最適な特性を持つCMOSデバイス用のシリコンウェハの製造方法を提供することにある。

【課題を解決するための手段】

【0012】

本発明のCMOSデバイス用シリコンウェハの製造方法は、同一シリコン基材の表面に、選択エピタキシャル法又はイオン注入法を用い、SiGe膜及びSiC膜を分離して形成し、CMOSデバイスを構成するために必要なn−MOSデバイス、及びp−MOSデバイスを同一シリコン基材上に島状に製造することを特徴とする。

【0013】

前記シリコン基材が、シリコン基板又はSOI基板であることを特徴とする。

【0014】

前記SiGe膜及びSiC膜に関し、最初にSiGe膜を形成し、次いでSiC膜を形成するか、又は最初にSiC膜を形成し、次いでSiGe膜を形成することを特徴とする。

【0015】

本発明のシリコンウェハの製造方法は、隣接するシリコン基材同士の間隔を2mm乃至5mmに設定して配置された複数のシリコン基材の表面上の自然酸化膜をフッ化水素又はフッ化アンモニウムと反応させる第1の工程と、前記反応によって生じた反応生成物を200℃以上、530℃以下で加熱・蒸発させて除去する第2の工程とを有するドライエッチング工程を実施してシリコン基材表面の自然酸化膜を除去し、同一シリコン基材の表面に、選択エピタキシャル法又はイオン注入法を用い、SiGe膜及びSiC膜を分離して形成し、CMOSデバイスを構成するために必要なn−MOSデバイス、及びp−MOSデバイスを同一シリコン基材上に島状に製造することを特徴とする。

【0016】

前記隣接するシリコン基材同士の間隔が2mm未満であると、作業が困難であり、5mmを超えると、自然酸化膜の除去が困難になる。また、前記反応生成物の加熱・蒸発温度が200℃未満であると、反応生成物の蒸発が困難であり、反応生成物が残留しやすいという問題があり、530℃を超えると、現在の装置構成上好ましくない。

【0017】

前記第2の工程における圧力を大気圧に設定することを特徴とし、また、前記ドライエッチング工程を、表面から自然酸化膜を除去したシリコン基材表面上にさらに成膜する次工程を実施する成膜装置内で実施することを特徴とする。これにより、シリコンウェハの製造工程がコンパクトになる。

【発明の効果】

【0018】

本発明によれば、同一のシリコン基材上のn−MOSトランジスタ作製部にSiGe膜を、また、p−MOSトランジスタ作製部にSiC膜をそれぞれ分離して選択的エピタキシャル成長することによって、最適な歪特性をもつn−MOSトランジスタと最適な歪特性を持つp−MOSトランジスタとを島状に製造できるので、CMOSデバイスとして最適な動作をするデバイスの作製が可能となるという効果を奏する。

【図面の簡単な説明】

【0019】

【図1】本発明のCMOSデバイス用シリコンウェハを製造する前処理として使用できる自然酸化膜の除去方法に用いるドライエッチング装置の一構成例を示す模式的断面図。

【図2】図1に示したドライエッチング装置によりエッチング処理した後のウェハを加熱処理して反応生成物を蒸発せしめる縦型炉(高温炉)の一構成例を示す模式的断面図。

【図3】ウェハを載置するウェハボートの一構成例を示す模式的断面図であり、(a)は従来のウェハボートの模式的断面図、(b)は本発明における前処理で用いることができるウェハボートの模式的断面図。

【図4】図1に示すドライエッチング装置及び図2に示す高温炉を用いて自然酸化膜の除去を実施するプロセスを説明するためのフローチャートであり、(a)はドライエッチング装置での処理、(b)は高温炉での処理。

【図5】本発明のCMOSデバイス用シリコンウェハを製造する際のSiGe膜成長装置の一構成例を示す模式的断面図。

【図6】本発明のCMOSデバイス用シリコンウェハを製造する際のSiGe膜成長装置とその前処理としての自然酸化膜除去装置とを組み合わせた場合の一構成例を示す模式的断面図。

【図7】本発明の実施の形態1のプロセスにおけるSiGe膜成長装置での処理を説明するためのフローチャート。

【図8】本発明の実施の形態1における選択エピタキシャル法によるSiGe膜及びSiC膜の成長プロセスを説明するための工程図。

【図9】本発明の実施の形態2のプロセスにおける自然酸化物除去処理及びSiGe膜成長装置での処理を説明するためのフローチャート。

【図10】本発明の実施の形態2における選択エピタキシャル法によるSiGe膜及びSiC膜の成長プロセスを説明するための工程図。

【図11】本明の実施の形態3におけるイオン注入法によるGeイオン注入及びCイオン注入プロセスを説明するための工程図。

【図12】従来技術によるCMOS用シリコンウェハ。

【発明を実施するための形態】

【0020】

まず、本発明に従ってCMOSデバイス用シリコンウェハを製造する際に、その前処理として実施する自然酸化膜の除去方法について説明し、次いでCMOS用シリコンウェハの製造方法について説明する。

【0021】

図1は、本発明に従ってCMOSデバイス用シリコンウェハを製造する際に、その前処理として実施することができる自然酸化膜の除去方法に用いるドライエッチング装置1の一構成例を示す模式的断面図である。ドライエッチング装置1は、例えば、50枚程度のバッチ単位でシリコン基材101の自然酸化膜の除去処理を行うものであり、エッチング室102と、エッチング室内へ導入される反応ガス(N2、NH3)を励起して活性種(ラジカル)を発生させるためのマイクロ波励起機構103と、エッチング室と連結されているロードロック室104と、ロードロック室と連結されているクリーンブース105とで構成されている。エッチング室102内には、図面上では、処理されるシリコン基材101を所定の間隔で載置してある石英製ウェハボート106(図3(b)参照)が、ロードロック室104から搬送され、配置されている状態が示されている。エッチング室102の外周には、ヒータ107等の加熱手段が設けられ、また、このエッチング室には、エッチング室内を排気できるように真空ポンプ108が取り付けられている。ロードロック室104には、室内を排気するための真空ポンプ109が取り付けられている。クリーンブース105内には、ウェハカセット110が載置され、このウェハカセットをロボット111によりクリーンブース105とロードロック室104との間を搬送できるように構成されている。

【0022】

図2は、図1に示したドライエッチング装置1によりエッチング処理した後のウェハを加熱処理して揮発性反応生成物を蒸発せしめる縦型炉(高温炉)の一構成例を示す模式的断面図である。この縦型炉2は、例えば、チャンバ201と、チャンバに連結されているロードロック室202と、ロードロック室と連結されているクリーンブース203とで構成されている。チャンバ201内には、図面上では、処理されるシリコン基材204を所定の間隔で載置してある石英製ウェハボート205(図3(b))が、ロードロック室202から搬送され、配置されている状態が示されている。チャンバ201の外周には、ヒータ206等の加熱手段が設けられ、また、チャンバ201には、チャンバ内を排気できるように真空ポンプ207が取り付けられている。ロードロック室202には、室内を排気するための真空ポンプ208が取り付けられている。クリーンブース203内には、ウェハカセット209が載置され、このウェハカセットをロボット210によりクリーンブース203とロードロック室202との間を搬送できるように構成されている。

【0023】

上記したように、ドライエッチング装置1と縦型炉2とを別々に示して説明したが、これらを組み合わせて一つの自然酸化膜除去装置としてもよいことは勿論である。

【0024】

図3はシリコン基材の載置されている石英製ウェハボートの一構成例を示す模式的断面図であり、(a)は従来のウェハボートを示し、(b)は本発明で用いるウェハボートを示す。図3(a)において、301はシリコン基材、302はウェハボートであり、隣接するシリコン基材同士の間隔は、5mmを超えているが、図3(b)において、303はシリコン基材、304はウェハボートであり、隣接するシリコン基材同士の間隔は2mm乃至5mmの範囲で等間隔に設定されていることが好ましい。

【0025】

以下、図3(b)に示すウェハボート304を用い、図1に示すドライエッチング装置1及び図2に示す縦型炉2を用いて自然酸化膜除去を実施するプロセスについて、エッチング装置での処理を示すフローチャート(図4(a))及び高温炉での処理を示すフローチャート(図4(b))を参照して説明する。

【0026】

例えば、図4(a)に示すように、まず、図1に示すドライエッチング装置1のクリーンブース105内に載置されているウェハカセット110をロボット111によりロードロック室104へ移送し、ここでシリコン基材101をウェハカセット110から石英製ウェハボート106(図3(b)のウェハボート304)に移し、ロードロック室104内を所定の圧力(例えば、200〜400Pa)まで排気する。次いで、ウェハボート106をエッチング室102内に移送した後、反応ガス(例えば、窒素ガス、アンモニアガス等)を導入する際に、マイクロ波励起機構103によりマイクロ波を印加(5〜10分間、また、1〜2kW、好ましくは1.8kW投入)し、励起して生成したHラジカルをエッチング室102内へ導入し、温度25〜50℃で反応(エッチング)を行う。この反応ガスの導入量は、一般に4000〜6000sccmであればよい。また、反応ガスとしての三フッ化窒素(NF3)ガスは、マイクロ波励起機構103を介さずに直接エッチング室102内へ導入する(一般に、3000〜4000sccm)。また、反応ガスとしてのアンモニアガス:窒素ガス:三フッ化窒素ガスの混合比は、一般には1〜3:5〜7:2〜4、好ましくは2:6:3であって、その合計流量が13〜15リットル/分、好ましくは14.4リットル/分であれば良い。このような条件下で所定の時間(2〜5分)エッチングする。

【0027】

上記エッチングプロセスにおいては、アンモニアガスと窒素ガスとの混合ガスを励起して得られる水素ラジカルと三フッ化窒素ガスとの反応により、エッチング室102内でフッ化アンモニウムを生成せしめ、このフッ化アンモニウムとシリコン基材101上の自然酸化膜との反応により、ケイフッ化アンモニウムを形成せしめる。これは、以下の反応式で示される。

【0028】

[化1]

NH3 → NH2 + H*

H* + NF3 → NH4F

SiO2 + NH4F → H2O + (NH4)2SiF6

【0029】

エッチングの終了後、反応ガスの導入及びマイクロ波の印加を停止し、エッチング室102の排気を行う。ヒータ107に通電してシリコン基材101を200℃に加熱する。その後、ヒータ107への通電を停止し、エッチング室102中のウェハボート106をロードロック室104内へ移送し、このボートからシリコン基材101をウェハカセット110に移す。

【0030】

次いで、図4(b)に示すように、上記したようにして得られたケイフッ化アンモニウムが表面に形成されたシリコン基材が載置されている図1に示すウェハカセット110(図2に示すウェハカセット209)を、図2に示す縦型炉2のクリーンブース203からロボット210によりロードロック室202内へ移送し、ここでシリコン基材204をウェハカセット209からウェハボート205(図3(b)のウェハボート304)に移し、このウェハボートを、所定の温度及び圧力(例えば、200℃を超える温度及び大気圧程度の圧力)に保持されているチャンバ(高温炉)201内に移送した後、チャンバ内を排気し、30分間保持し、ケイフッ化アンモニウムを蒸発させる。次いで、チャンバ内に窒素ガス等のパージガスを流しながら、チャンバ201内をベントした後、チャンバ内のウェハボート205をロードロック室202内に移送し、このボートからシリコン基材204をウェハカセット209に移し、このカセットをクリーンブース203内へ移送して自然酸化膜の除去プロセスを終了する。この全工程の処理時間は、従来よりも短かった。

【0031】

上記のようにして自然酸化膜を除去したシリコン基材を用いてCMOSデバイス用シリコンウェハを製造するために、まず、図5に示すSiGe膜成長装置により、基材表面にSiGe膜を形成する。図5にその一構成例の模式的断面図を示すSiGe膜成長装置5は、50枚程度のバッチ単位でシリコン基材表面にSiGe膜の形成を行うものであり、内部にシリコン基材501を設置できるようになっており、かつ反応ガス(例えば、H2、SiH4、GeH4ガス等)を導入できるように構成されているSiGe成膜室502と、この成膜室と連結されているロードロック室503と、このロードロック室と連結されているクリーンブース504とで構成されている。成膜室502には、図面上では、処理されるシリコン基材501を所定の間隔で載置してあるウェハボート505が、ロードロック室503から搬送され、設置されている状態が示されている。成膜室502の外周には、ヒータ506等の加熱手段が設けられ、また、この成膜室には、室内を排気するための真空ポンプ507が取り付けられている。ロードロック室503には、室内を排気するための真空ポンプ508が取り付けられている。クリーンブース504内には、ウェハカセット509が設置された状態が示され、このウェハカセットをロボット510によりクリーンブース504とロードロック室503との間を搬送できるように構成されている。

【0032】

図6は、上記した図1に示す自然酸化膜除去装置(エッチング室102)と図5に示すSiGe膜成長装置5とを組み合わせた場合の一構成例を示す模式的断面図である。この自然酸化膜除去装置及びSiGe膜成長装置については、上記図1及び図5と同じであるので、説明を省略する。なお、同じ構成要素に対しては同じ参照番号を付してある。

【0033】

実施の形態1:

本実施の形態では、高速デバイス用としてSOI(silicon on insulator)基板を用い、その上にSiGe膜/SiC膜を成長せしめたCMOSデバイス用シリコンウェハの製造方法について、SiGe膜成長装置での処理を示すフローチャート(図7)及びSiGe膜及びSiC膜の成長プロセスを説明するための工程図(図8(a)〜(p))を参照して説明する。

【0034】

図7に示すように、まず、図5に示すSiGe膜成長装置5のクリーンブース504内に載置されているウェハカセット509をロボット510によりロードロック室503へ移送し、ここでシリコン基材501をウェハカセット509から石英製ウェハボート505に移し、ロードロック室内を所定の圧力(例えば、10〜10−2Pa)まで排気する。次いで、ウェハボート505をSiGe成膜室(SiGe成長室)502内に移送した後、ヒータ506に通電してシリコン基材501を例えば450℃に加熱し、反応ガス(例えば、H2、SiH4、GeH4等)を導入しSiGe膜の成長を行う。この反応ガスの導入量は、一般に100〜2000sccmであればよい。また、反応ガスとしての例えば、H2:SiH4:GeH4ガスの混合比は、一般には、10〜1000:1〜10:1〜10、好ましくは20:1:1であって、その合計流量が0.1〜2リットル/分、好ましくは0.5リットル/分であれば良い。このような条件下で所定の時間(10〜120分)成膜する。

【0035】

次いで、ヒータへの通電を停止すると共に、反応ガスの導入を停止し、SiGe成膜室502内を排気した後、ウェハボート505をロードロック室503に移送し、SiGe成膜されたシリコン基材501をウェハボート505からウェハカセット509へ移す。その後、以下述べるように、SiGe膜及びSiC膜の成長を行う。

【0036】

例えば図8の工程図に示すように、まず、SOI基板801を準備する(図8(a))。このSOI基板801は、シリコン基板802と表面のシリコン層804との間にSiO2膜(BOX酸化膜)803が挿入された構造の基板である。本実施の形態では、シリコン基板802上に100〜1000nm程度のBOX酸化膜803及び10〜100nm程度のシリコン層804を備えたSOI801基板を用いる。

【0037】

このSOI基板801上に、SiGe選択成長時のマスクとなるシリコン酸化膜805を厚さ100〜1000nm程度で形成した(図8(b))後、この酸化膜805に対して、n−MOSトランジスタ(n−チャネルトランジスタ)作製領域806の部分の酸化膜を取り除くパターンニングを行い、この作製領域806のみにシリコンが露出し、残りの部分がマスク酸化膜805aで覆われた状態とする(図8((c))。

【0038】

この状態で、酸化膜805が除去されてシリコンが露出した作製領域806の表面上に、CVD法により、Si原子含有ガス(例えば、SiH4ガス又はSi2H6ガス等)、Ge原子含有ガス(例えば、GeH4ガス等)、及びハロゲンガス(例えば、Cl2ガス等)を用い、成長温度450〜650℃程度で選択的エピタキシャル成長を実施し、膜厚10〜100nm程度のSiGe膜806aを成長せしめる(図8(d))。成長温度が450℃未満であると膜の成長が起こらず、650℃を超えるとマスク酸化膜805a上にも膜の成長が起こり、ポリシリコンが生じてしまう。この選択的エピタキシャル成長はハロゲンを用いる方法でも用いない方法でもいずれでも良い。この選択的エピタキシャル成長の場合、Siに対するGeの濃度は作製するn−MOSトランジスタに必要とされる特性に依存するが、通常5〜80%程度、好ましくは10%〜50%程度であれば、所望の特性が得られる。

【0039】

この状態で一旦マスク酸化膜805aを除去し(図8(e))、次いでSiC選択的エピタキシャル成長用のマスクとなる酸化膜(SiO2膜)807を100〜1000nm程度の厚さで形成した(図8(f))後、この酸化膜807に対して、p−MOSトランジスタ(p−チャネルトランジスタ)作製領域808の酸化膜を取り除くパターンニングを行い、この作製領域808のみにシリコンが露出し、残りの部分がマスク酸化膜807aで覆われている状態とする(図8(g))。

【0040】

この状態で、酸化膜807が除去されてシリコンが露出した作製領域808の表面上に、CVD法により、Si原子含有ガス(例えば、SiH4ガス又はSi2H6ガス)、C原子含有ガス(例えば、CH3SiH5ガス又はC3H8ガス)、及びハロゲンガス(例えば、Cl2ガス)を用い、成長温度500〜700℃程度で選択的エピタキシャル成長を実施し、膜厚10〜100nm程度のSiC膜808aを成長せしめる(図8(h))。成長温度が500℃未満であると膜の成長が起こらず、700℃を超えるとマスク酸化膜807a上にも膜の成長が起こり、ポリシリコンが生じてしまう。この選択的エピタキシャル成長の場合、Siに対するCの濃度は作製するp−MOSトランジスタに必要とされる特性に依存するが、通常0.5〜3%程度、好ましくは1〜2%程度であれば、所望の特性が得られる。0.5%未満であると所望の特性が得られず、また、3%を超えると歪みが大きくなり過ぎ、膜の成長中に歪みに耐えられなくなり、結晶が割れてしまう。

【0041】

この状態で一旦マスク酸化膜807aを除去する(図8(i))。

【0042】

上記例では、最初にSiGe膜806aを作製し、次いでSiC膜808aを作製したが、この順番は逆であっても良い。

【0043】

次いで、SOI基板801の表面全体に、この基板表層のシリコン層804の所定の領域を除去する際のマスクとして、窒化膜(SiN膜)809を100〜1000nm程度で形成した(図8(j))後、SiGe膜806a及びSiC膜808aが形成されている領域に対抗する表面上の窒化膜809aを残すように窒化膜809をパターンニングする(図8(k))。このシリコン層の除去は、CMOSデバイス特性の改善のためである。この状態で、シリコン層804の選択的エッチングを行い、シリコン基板802上のBOX酸化膜803の上に、シリコン層804a上に形成されたSiGe形成部分(n−MOSトランジスタ作製領域806a)とシリコン層804a上に形成されたSiC形成部分(p−MOSトランジスタ作製領域808a)とが島状に離間して配置されるようにする(図8(l))。次いで、窒化膜809aを除去した(図8(m))後、各島が埋まる程度のシリコン酸化膜810を、例えば200〜2000nm程度の厚さで形成する(図8(n))。このシリコン酸化膜形成方法は、例えばHDP−CVD法で行うことができる。

【0044】

シリコン酸化膜810の形成後、CMP処理を行い、それぞれの島の頭が出るレベルまでシリコン酸化膜810を研磨・除去する(図8(o))。ここでは、SiGe膜806a部分とSiC膜808a部分とがシリコン酸化膜810aによって分離された形に見える。SiGe膜806a部分とSiC膜808a部分とが同じ一つの基板上に島状に形成されている。

【0045】

次いで、シリコンの選択成長を行う。SiGe膜806a部分とSiC膜808a部分との表面上に、アクティブシリコン層811を炉内圧力10〜0.1Pa、成長温度450〜600℃、水素流量100〜1000sccm、シラン流量10〜200sccm、成長時間10〜120分の条件で選択成長により形成する(図8(p))。このシリコン層811の厚さはトランジスタに求められる特性に依存するが、通常、10〜100nm程度の範囲であれば所望の特性が得られる。

【0046】

その後、500〜800℃で熱処理を実施し、SiGe膜806a内とSiC膜808a内の歪を緩和させ、各膜の上に形成したシリコン層811に歪応力を発生させる。SiGe膜及びその上のシリコンがn−MOSトランジスタ作製部位となり、SiC膜及びその上のシリコンがp−MOSトランジスタ作製部位となる。かくして得られたシリコンウェハは、それぞれのMOSトランジスタに最適なキャリア移動度を得られる点から、CMOSデバイス用として有用であることが確認できた。

【0047】

なお、上記SiGe膜及びSiC膜に関し、SiGe膜の場合は、Ge原子径がSi原子径より大きいため、シリコン層上に成長して2層となったときに歪みが生じて、引っ張り方向に応力がかかり、電子のスピードが速くなるので、n−チャネルトランジスタとして適しており、また、SiCの場合は、C原子径はSi原子径より小さいため、シリコン層上に成長して2層となったときに縮こまる方向(圧縮方向)の応力が掛かり、応力を外側に分散させ、ホールのスピードが速くなるので、ホールをチャネルとするのに良く、p−チャネルトランジスタとして適している。

【0048】

実施の形態2:

本実施の形態では、SOI基板の代わりに通常のシリコン基板を用いて実施の形態1と同様に、SiGe膜/SiC膜が形成されたCMOSデバイス用シリコンウェハを製造する方法について、SiGe膜の成長プロセスのフローチャート及びSiGe膜及びSiC膜の成長プロセスの工程図をそれぞれ示す図9及び図10(a)〜(l)を参照して説明する。

【0049】

例えば、図9に示すように、図4(a)の場合と同様に、まず、図1に示すドライエッチング装置1のクリーンブース105内に載置されているウェハカセット110をロボット111によりロードロック室104へ移送し、ここでシリコン基材101をウェハカセット110からウェハボート106(図3(b)のウェハボート304)に移し、ロードロック室104内を所定の圧力まで排気する。次いで、ウェハボート106をエッチング室102内に移送した後、反応ガス(例えば、窒素ガス、アンモニアガス等)をエッチング室102内へ導入する際に、マイクロ波励起機構103によりマイクロ波を印加(5〜10分間、また、1〜2kW、好ましくは1.8kW投入)して、励起して生成したHラジカルをエッチング室102内へ導入し、圧力200〜400Pa、温度25〜50℃で反応(エッチング)を行う。この反応ガスの導入量は、一般に4000〜6000sccmであればよい。また、反応ガスとしての三フッ化窒素ガスは、マイクロ波励起機構103を介さずに直接エッチング室102内へ導入する(一般に、3000〜4000sccm)。また、反応ガスとしてのアンモニアガス:窒素ガス:三フッ化窒素ガスの混合比は、一般には、1〜3:5〜7:2〜4、好ましくは2:6:3であって、その合計流量が13〜15リットル/分、好ましくは14.4リットル/分であれば良い。このような条件下で所定の時間(2〜5分)エッチングする。

【0050】

上記エッチングプロセスにおいては、アンモニアガスと窒素ガスとの混合ガスを励起して得られる水素ラジカルと三フッ化窒素ガスとの反応により、エッチング室102内でフッ化アンモニウムを生成せしめ、このフッ化アンモニウムとシリコン基材101上の自然酸化膜との反応により、ケイフッ化アンモニウムを形成せしめる。これは、上記の反応式で示される。

【0051】

エッチングの終了後、反応ガスの導入及びマイクロ波の印加を停止し、エッチング室102の排気を行う。その後、ヒータ107に通電してシリコン基材101を200℃程度に加熱しても良い。通電した場合は、ヒータ107への通電を停止した後、エッチング室102中のウェハボート106をロードロック室104内へ移送し、次いでこのボートを図5に示すSiGe成膜室502に移送する。

【0052】

ウェハボートを成膜室502内に移送した後、ヒータ506に通電してシリコン基材501を例えば500℃に加熱し、反応ガス(例えば、H2、SiH4、GeH4等)を導入し、SiGe膜の成長を行う。この反応ガスの導入量、混合比及び合計流量は、上記した通りであればよい。

【0053】

次いで、ヒータ506への通電を停止すると共に、反応ガスの導入を停止し、SiGe成膜室502内を排気する。その後、ウェハボート505をロードロック室503に移送し、SiGe成膜されたシリコン基材501をウェハボート505からウェハカセット509へ移す。

【0054】

以下、SiGe膜/SiC膜を成長せしめたCMOSデバイス用シリコンウェハの製造方法について、SiGe膜及びSiC膜の成長プロセスの工程図を示す図10(a)〜(l)を参照して説明する。

【0055】

まず、シリコン基板1001を準備する(図10(a))。このシリコン基板1001上に、SiGe選択成長時のマスクとなるシリコン酸化膜1002を厚さ100〜1000nm程度で形成した(図10(b))後、この酸化膜1002に対して、n−MOSトランジスタ(n−チャネルトランジスタ)作製領域1003の酸化膜を取り除くパターンニングを行い、この作製領域1003のみにシリコンが露出し、残りの部分がマスク酸化膜1002aで覆われた状態とする(図10((c))。

【0056】

この状態で、シリコン酸化膜1002が除去されてシリコンが露出した作製領域1003の表面上に、CVD法により、Si原子含有ガス(例えば、SiH4ガス又はSi2H6ガス等)、Ge原子含有ガス(例えば、GeH4ガス等)、及びハロゲンガス(Cl2ガス等)を用い、成長温度450〜650℃程度で選択的エピタキシャル成長を実施し、膜厚10〜100nm程度のSiGe膜1003aを成長せしめる(図10(d))。成膜温度が450℃未満であると膜の成長が起こらず、650℃を超えるとマスク酸化膜1002a上にも膜の成長が起こり、ポリシリコンが生じてしまう。この選択的エピタキシャル成長はハロゲンを用いる方法でも用いない方法でもいずれでも良い。この選択的エピタキシャル成長の場合、Siに対するGeの濃度は上記した通りであれば、所望の特性が得られる。

【0057】

この状態で一旦マスク酸化膜1002aを除去し(図10(e))、次いでSiC選択成長用のマスク酸化膜(SiO2膜)1004を100〜1000nm程度の厚さで形成した(図10(f))後、この酸化膜1004に対して、p−MOSトランジスタ(p−チャネルトランジスタ)作製領域1005の酸化膜を取り除くパターンニングを行い、この作製領域1005のみにシリコンが露出し、残りの部分がマスク酸化膜1004aで覆われた状態とする(図10(g))。

【0058】

この状態で、酸化膜1004が除去されてシリコンが露出した作製領域1005の表面上に、CVD法により、Si原子含有ガス(例えば、SiH4ガス又はSi2H6ガス等)、C原子含有ガス(例えば、CH3SiH5ガス又はC3H8ガス等)、及びハロゲンガス(例えば、Cl2ガス等)を用い、成長温度500〜700℃程度で選択的エピタキシャル成長を実施し、膜厚10〜100nm程度のSiC膜1005aを成長せしめる(図10(h))。成長温度が500℃未満であると膜の成長が起こらず、700℃を超えるとマスク酸化膜1004a上にも膜の成長が起こり、ポリシリコンが生じてしまう。この選択的エピタキシャル成長の場合、Siに対するCの濃度は上記した通りであれば、所望の特性が得られる。

【0059】

この状態で一旦マスク酸化膜1004aを除去し、シリコン基板1001上のSiGe形成部分(n−MOSトランジスタ作製部分1003a)とSiC形成部分(p−MOSトランジスタ作製部分1005a)とが島状に離間して配置されるようにする(図10(i))。

【0060】

上記例では、最初にSiGe膜1003aを作製し、次いでSiC膜1005aを作製したが、この順番は逆であっても良い。

【0061】

次いで、シリコン基板1001の表面全体に、各島が埋まる程度のシリコン酸化膜1006を、例えば200〜2000nm程度の厚さで成長せしめる(図10(j))。このシリコン酸化膜形成方法は、例えばHDP−CVD法で行うことができる。

【0062】

酸化膜1006の形成後、CMP処理を行い、それぞれの島の頭が出るレベルまでシリコン酸化膜1006を研磨・除去する(図10(k))。ここでは、SiGe膜1003a部分とSiC膜1005a部分とが酸化膜1006aによって分離された形に見える。SiGe膜1003a部分とSiC膜1005a部分とが同じ一つの基板上に島状に形成されている。

【0063】

次いで、シリコンの選択成長を行った。SiGe膜1003a部分とSiC膜1005a部分との表面上に、アクティブシリコン層を炉内圧力10〜0.1Pa、成長温度450〜600℃、水素流量100〜1000sccm、シラン流量10〜200sccm、成長時間10〜120分の条件で選択成長により形成する(図10(l))。このシリコン層の厚さはトランジスタに求められる特性に依存するが、通常、10〜100nm程度の範囲であれば所望の特性が得られる。

【0064】

その後、500〜800℃程度の温度で熱処理を実施し、SiGe膜1003a内とSiC膜1005a内の歪を緩和させ、各膜の上に形成したシリコン層1007に歪応力を発生させた。SiGe膜及びその上のシリコンがn−MOSトランジスタ作製部位となり、SiC膜及びその上のシリコンがp−MOSトランジスタ作製部位となる。かくして得られたシリコンウェハは、上記したように、それぞれのMOSトランジスタに最適なキャリア移動度が得られる点から、CMOSデバイス用として有用であることが確認できた。

【0065】

実施の形態3:

本実施の形態は、イオン注入法を用い、SOI基板の表層のシリコン層内にGeイオン及びCイオンを注入し、BOX酸化膜上に、SiGe膜/SiC膜を島状に形成せしめたCMOSデバイス用シリコンウェハの製造方法に係わり、この点について、図11(a)〜(p)を参照して説明する。

【0066】

まず、SOI基板1101を準備する(図11(a))。このSOI基板1101は、実施の形態1で説明したように、シリコン基板1102と表面のシリコン層1104との間にSiO2膜(BOX酸化膜)1103が挿入された構造の基板である。本実施の形態では、シリコン基板1102上に100〜1000nm程度のBOX酸化膜1103及び10〜100nm程度のシリコン層1104を備えたSOI基板1101を用いる。

【0067】

このSOI基板1101上に、Geイオン注入時のマスクとなるシリコン酸化膜1105を厚さ100〜1000nm程度で形成した(図11(b))後、この酸化膜1105に対して、n−MOSトランジスタ(n−チャネルトランジスタ)作製領域の酸化膜を取り除くパターンニングを行い、この領域のみにシリコンが露出し、残りの領域がマスク酸化膜1105aで覆われた状態とする(図11((c))。

【0068】

この状態で、酸化膜1105が除去されたn−MOSトランジスタ作製領域のシリコン層に対して、A方向からGeイオンを注入する(図11((d))。この際、エネルギー:10〜50keV程度、及びイオン注入量:1E14〜1E17cm−2程度として行う。この場合、シリコン層1104に対するGeイオン注入量は、体積換算でシリコン層中のGe濃度が5〜50%程度となるようにした。この濃度であれば、n−MOSトランジスタに必要とされる所望の特性が得られる。

【0069】

次いで、マスク酸化膜1105aをエッチング除去し、Geイオンが注入されたGeイオン注入シリコン領域層1104aを有するシリコン層1104を形成する(図11(e))。

【0070】

このシリコン層1104の全表面上に、Cイオン注入時のマスクとなるシリコン酸化膜1106を100〜1000nm程度の厚さで形成し(図11(f))、p−MOSトランジスタ(p−チャネルトランジスタ)作製領域の酸化膜を取り除くパターニングを行い、この領域のみにシリコンが露出し、残りの領域がマスク酸化膜1106aで覆われた状態とする(図11(g))。

【0071】

この状態で、シリコン酸化膜1106が除去されたp−MOSトランジスタ作製領域のシリコン層に対して、B方向からCイオンを注入する(図11((h))。この際、エネルギー:10〜50keV程度、及び注入量:1E13〜1E16cm−2程度として行う。この場合、シリコン層に対するCイオン注入量は、体積換算でシリコン層中のGe濃度が0.5〜3.0%程度となるようにした。これによりp−MOSトランジスタに必要とされる所望の特性が得られる。

【0072】

マスクとして用いた酸化膜1106aを、エッチング除去し、Geイオン注入シリコン領域層1104a及びCイオン注入シリコン領域層1104bを有するシリコン層1104を得る(図11(i))。

【0073】

次いで、SOI基板表面上に薄い(10〜100nm程度)シリコン層1107をエピタキシャル成長させ(図11(j))、このシリコン層1107上に、シリコン層1107及び1104をエッチ除去する際のマスクとしての窒化シリコン膜1108を100〜1000nm程度の厚さで成長させた(図11(k))後、Geイオン注入シリコン領域層1104a及びCイオン注入シリコン領域層1104bの上の窒化膜を残すようにパターニングし、マスク窒化膜1108aを形成する(図11(l))。

【0074】

この状態で、シリコン層1107及び1104の選択シリコンエッチングを行い、SOI基板のBOX酸化膜1103上にGeイオン注入シリコン領域層1104a(n−MOSトランジスタ作製領域)とCイオン注入シリコン領域層1104b(p−MOSトランジスタ作製領域)とが島状に配置されるようにした(図11(m))後、マスク窒化膜1108aを除去する(図11(n))。その結果、窒化膜除去を実施したSOI基板のBOX酸化膜1103上に、Geイオン注入シリコン領域層1104aとCイオン注入シリコン領域層1104bとがそれぞれ表面の薄いシリコン層1107aと共に島状に離間して形成された。Geイオン注入シリコン領域層1104aとCイオン注入シリコン領域層1104bとが同じ一つの基板上に島状に形成されている。

【0075】

次いで、イオン活性化及びストレス緩和熱処理を実施し(図11(o))、シリコン層1107aに歪を導入する。この熱処理温度は、600〜1000℃で行う。かくして、Geイオンを注入した領域がn−MOSトランジスタ作製領域(n−チャネル(n−ch))となり、Cイオンを注入した領域がp−MOSトランジスタ作製領域(p−チャネル(p−ch))となる(図11(p))。

【0076】

実施の形態4:

本実施の形態では、図1に示すドライエッチング装置1及び図2に示す縦型炉2並びに図3(b)に示す石英製ウェハボート304を用い、図4(a)及び(b)に示すフローチャートに従ってシリコン基材表面上の自然酸化膜を除去した。このウェハボート304としては、複数枚のシリコン基材を、隣接する基材同士を2mm、3mm、4mm及び5mmの等間隔で載置できるように構成されたものをそれぞれ用い、また、比較のために1.5mm、5.5mm及び6mmの等間隔で載置できるように構成されたものをそれぞれ用いた。

【0077】

始めに、真空中で、アンモニアガスと窒素ガスとの混合ガスに対してマイクロ波を印加して励起し、水素ラジカルを得た。かくして得られた水素ラジカルと三フッ化窒素ガスとを反応させてフッ化アンモニウムガスを生成せしめ、エッチングガスとしてのこのフッ化アンモニウムガスとシリコン基材表面上の自然酸化膜とを反応させてケイフッ化アンモニウムを生成させた。このとき、シリコン基材を、アンモニアガス、窒素ガス、及び三フッ化窒素ガスの混合比が2:6:3で合計流量が14.4リットル/分、圧力が266Paの雰囲気に晒し、8分間励起マイクロ波を2.8kW投入して処理した。

【0078】

次に、表面にケイフッ化アンモニウムが形成されたシリコン基材を200℃に保持した高温炉のチャンバ内に入れ、チャンバ内を大気圧程度に設定し、30分間処理して、ケイフッ化アンモニウムを蒸発させた後、ウェハを取り出した。

【0079】

上記全工程の処理時間は、約30分であった。

【0080】

上記のようにして得たエッチング済みシリコン基材のエッチング量について、エッチング前のシリコン酸化膜の膜厚と、エッチング後のシリコン酸化膜の膜厚とをそれぞれ複数箇所測定し、各測定箇所におけるエッチング量(エッチング前とエッチング後との膜厚差)を測定した。その結果、隣接するシリコン基材同士を2mm、3mm、4mm及び5mmの間隔で載置できるように構成された各ウェハボートを用いた場合は、シリコン基材間に生じるエッチングガスがシリコン基材同士の間からシリコン基材の外側へ拡散し、流出するのが抑制されて、二次エッチングによるエッチング量の増大と面内均一化を実現できた。一方、隣接するシリコン基材同士を1.5mm、5.5mm及び6mmの間隔で載置できるように構成された各ウェハボートを用いた場合、1.5mmでは、好ましいエッチングができず、また、5.5mm及び6mmでは、間隔が広くなるに従って、シリコン基材間に生じるエッチングガスがシリコン基材同士の間からシリコン基材の外側へ拡散し、流出するために、二次エッチングの作用を利用できず、エッチング量の増大や面内均一化を達成できなかった。

【産業上の利用可能性】

【0081】

本発明によれば、CMOSデバイス作製工程で特別な追加工程を必要とせず、高速動作尚且つ低消費電力を達成できるCMOSデバイス用シリコンウェハの製造方法を提供できるので、半導体デバイス、特にCMOSデバイスの技術分野で利用可能である。

【符号の説明】

【0082】

1 ドライエッチング装置 2 縦型炉

5 膜成長装置 101 シリコン基材

102 エッチング室 103 マイクロ波励起機構

104 ロードロック室 105 クリーンブース

106 ウェハボート 107 ヒータ

108、109 真空ポンプ 110 ウェハカセット

111 ロボット 201 チャンバ

202 ロードロック室 203 クリーンブース

204 シリコン基材 205 ウェハボート

205 石英製ウェハボート 206 ヒータ

207、208 真空ポンプ 209 ウェハカセット

210 ロボット 304 ウェハボート

501 シリコン基材 502 成膜室

503 ロードロック室 504 クリーンブース

505 ウェハボート 506 ヒータ

507、508 真空ポンプ 509 ウェハカセット

510 ロボット 801 基板

802 シリコン基板 803 酸化膜

804 シリコン層 804a シリコン層

805 シリコン酸化膜 805a マスク酸化膜

806 n−MOSトランジスタ作製領域

806a SiGe膜(n−MOSトランジスタ作製領域)

807 酸化膜 807a マスク酸化膜

808 p−MOSトランジスタ作製領域

808a SiC膜(p−MOSトランジスタ作製領域)

809、809a 窒化膜 810、810a シリコン酸化膜

811 シリコン層 1001 シリコン基板

1002 シリコン酸化膜 1002a マスク酸化膜

1003 n−MOSトランジスタ作製領域

1003a SiGe膜(n−MOSトランジスタ作製部分)

1004 酸化膜 1004a マスク酸化膜

1005 p−MOSトランジスタ作製領域

1005a SiC膜(p−MOSトランジスタ作製部分)

1006 シリコン酸化膜 1006a 酸化膜

1007 シリコン層 1101 基板

1102 シリコン基板 1103 酸化膜

1104 シリコン層 1104a イオン注入シリコン領域層

1104b イオン注入シリコン領域層 1105 シリコン酸化膜

1105a マスク酸化膜 1106 シリコン酸化膜

1106a マスク酸化膜 1107 シリコン層

1107a シリコン層 1108 窒化膜

1108a マスク窒化膜 1201 Si基板

1202 SiO2膜 1203 活性シリコン膜

1204 応力用SiN膜 1205 スペーサ絶縁膜

1206 ゲート電極

【特許請求の範囲】

【請求項1】

CMOSデバイス用シリコンウェハの製造方法において、同一シリコン基材の表面に、選択エピタキシャル法又はイオン注入法を用い、SiGe膜及びSiC膜を分離して形成し、CMOSデバイスを構成するために必要なn−MOSデバイス、及びp−MOSデバイスを同一シリコン基材上に島状に製造することを特徴とするシリコンウェハの製造方法。

【請求項2】

前記シリコン基材が、Si基板又はSOI基板であることを特徴とする請求項1記載のシリコンウェハの製造方法。

【請求項3】

前記SiGe膜及びSiC膜に関し、最初にSiGe膜を形成し、次いでSiC膜を形成するか、又は最初にSiC膜を形成し、次いでSiGe膜を形成することを特徴とする請求項1又は2記載のシリコンウェハの製造方法。

【請求項4】

隣接するシリコン基材同士の間隔を2mm乃至5mmに設定して配置された複数のシリコン基材の表面上の自然酸化膜をフッ化水素又はフッ化アンモニウムと反応させる第1の工程と、前記反応によって生じた反応生成物を200℃以上、530℃以下で加熱・蒸発させて除去する第2の工程とを有するドライエッチング工程を実施してシリコン基材表面の自然酸化膜を除去し、同一シリコン基材の表面に、選択エピタキシャル法又はイオン注入法を用い、SiGe膜及びSiC膜を分離して形成し、CMOSデバイスを構成するために必要なn−MOSデバイス、及びp−MOSデバイスを同一シリコン基材上に島状に製造することを特徴とするシリコンウェハの製造方法。

【請求項5】

前記第2の工程における圧力を大気圧に設定することを特徴とする請求項4記載のシリコンウェハの製造方法。

【請求項6】

前記ドライエッチング工程を、表面から自然酸化膜を除去したシリコン基材表面上にさらに成膜する次工程を実施する成膜装置内で実施することを特徴とする請求項4又は5記載のシリコンウェハの製造方法。

【請求項1】

CMOSデバイス用シリコンウェハの製造方法において、同一シリコン基材の表面に、選択エピタキシャル法又はイオン注入法を用い、SiGe膜及びSiC膜を分離して形成し、CMOSデバイスを構成するために必要なn−MOSデバイス、及びp−MOSデバイスを同一シリコン基材上に島状に製造することを特徴とするシリコンウェハの製造方法。

【請求項2】

前記シリコン基材が、Si基板又はSOI基板であることを特徴とする請求項1記載のシリコンウェハの製造方法。

【請求項3】

前記SiGe膜及びSiC膜に関し、最初にSiGe膜を形成し、次いでSiC膜を形成するか、又は最初にSiC膜を形成し、次いでSiGe膜を形成することを特徴とする請求項1又は2記載のシリコンウェハの製造方法。

【請求項4】

隣接するシリコン基材同士の間隔を2mm乃至5mmに設定して配置された複数のシリコン基材の表面上の自然酸化膜をフッ化水素又はフッ化アンモニウムと反応させる第1の工程と、前記反応によって生じた反応生成物を200℃以上、530℃以下で加熱・蒸発させて除去する第2の工程とを有するドライエッチング工程を実施してシリコン基材表面の自然酸化膜を除去し、同一シリコン基材の表面に、選択エピタキシャル法又はイオン注入法を用い、SiGe膜及びSiC膜を分離して形成し、CMOSデバイスを構成するために必要なn−MOSデバイス、及びp−MOSデバイスを同一シリコン基材上に島状に製造することを特徴とするシリコンウェハの製造方法。

【請求項5】

前記第2の工程における圧力を大気圧に設定することを特徴とする請求項4記載のシリコンウェハの製造方法。

【請求項6】

前記ドライエッチング工程を、表面から自然酸化膜を除去したシリコン基材表面上にさらに成膜する次工程を実施する成膜装置内で実施することを特徴とする請求項4又は5記載のシリコンウェハの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2011−108692(P2011−108692A)

【公開日】平成23年6月2日(2011.6.2)

【国際特許分類】

【出願番号】特願2009−259275(P2009−259275)

【出願日】平成21年11月12日(2009.11.12)

【出願人】(000231464)株式会社アルバック (1,740)

【Fターム(参考)】

【公開日】平成23年6月2日(2011.6.2)

【国際特許分類】

【出願日】平成21年11月12日(2009.11.12)

【出願人】(000231464)株式会社アルバック (1,740)

【Fターム(参考)】

[ Back to top ]