CMOS集積回路及び増幅回路

【課題】入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能なCMOS集積回路を提供する。

【解決手段】トランジスタは、ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、ゲート配線に対向した位置に形成されるソース配線から、ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、ゲート配線に対向した位置に形成されるドレイン配線から、ゲート電極の櫛歯の間のソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、を備え、ゲート電極と、ソース電極またはドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路が提供される。

【解決手段】トランジスタは、ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、ゲート配線に対向した位置に形成されるソース配線から、ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、ゲート配線に対向した位置に形成されるドレイン配線から、ゲート電極の櫛歯の間のソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、を備え、ゲート電極と、ソース電極またはドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路が提供される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、CMOS集積回路及び増幅回路に関する。

【背景技術】

【0002】

携帯電話や無線データ通信装置のような無線通信システムにおいて、受信側では受信した信号を増幅するための増幅回路が設けられる。そのような増幅回路の一つとして、例えばローノイズアンプ(LNA)がある。LNAは、その回路自身が発生するノイズを出来る限り小さくして信号を増幅する回路であり、無線受信回路のフロントエンドに配置される必須の回路である。

【0003】

LNAをCMOS(Complementary Metal Oxide Semiconductor;相補型金属酸化膜半導体)で実現することは、LNAの低価格化に対して大きな需要がある。そして、LNAの本来の役割から、ノイズフィギュア(Noise Figure:雑音指数)の低減は常に求められる。

【0004】

CMOSで実現するLNA(CMOS LNA)の入力トランジスタにおいて、トランジスタ本来の部位であるソース・ゲート・ドレインが発生する雑音以外に、トランジスタの各部位からの配線によって抵抗が生じ、NFが劣化することが知られている。NFが劣化する要因の一つはゲート配線の抵抗からのノイズの発生によるものであり、このノイズを抑えるために、入力トランジスタの構造を櫛形構造にして、櫛の両端からゲートの電位を接続することで、ゲート配線の抵抗を最小にする方法がある。

【先行技術文献】

【非特許文献】

【0005】

【非特許文献1】The design of CMOS radio-frequency integrated circuits / Thomas H.Lee, Cambridge University Press. Page.287

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、入力トランジスタの構造を櫛形構造にして、櫛の両端からゲートの電位を接続すると、必然的にゲート−ソース間およびゲート−ドレイン間の配線間容量が大きくなる(非特許文献1参照)。従って、ゲート−ソース間およびゲート−ドレイン間の配線間容量の増大によって、NFが増大し、CMOS LNAの性能が劣化してしまうという問題があった。

【0007】

そこで、本発明は、上記問題に鑑みてなされたものであり、本発明の目的とするところは、入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能な、新規かつ改良されたCMOS集積回路及び増幅回路を提供することにある。

【課題を解決するための手段】

【0008】

上記課題を解決するために、本発明のある観点によれば、トランジスタを形成したCMOS集積回路であって、前記トランジスタは、ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、前記ゲート配線に対向した位置に形成されるソース配線から、前記ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、前記ゲート配線に対向した位置に形成されるドレイン配線から、前記ゲート電極の櫛歯の間の前記ソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、を備え、前記ゲート電極と、前記ソース電極または前記ドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路が提供される。

【0009】

かかる構成によれば、ゲート電極は、ゲート配線から櫛歯状に延びて形成されて信号入力端子からの入力信号が供給され、ソース電極は、ゲート配線に対向した位置に形成されるソース配線から、ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成されて接地端子に接続され、ドレイン電極は、ゲート配線に対向した位置に形成されるドレイン配線から、ゲート電極の櫛歯の間のソース電極が存在しない箇所に櫛歯状に延びて形成されて電源端子に接続される。そしてゲート電極と、ソース電極またはドレイン電極とは、重なり合う領域が存在しないよう構成される。その結果、入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能となる。

【0010】

前記ゲート電極と、前記ソース電極および前記ドレイン電極との間の距離は、前記トランジスタのノイズフィギュアを所定値以下にするものであってもよい。

【0011】

前記ゲート電極と、前記ソース電極および前記ドレイン電極との間の距離は、プロセス・ルールで定まる最小距離より長くてもよい。

【0012】

前記ソース電極間の距離および前記ドレイン電極間の距離は、プロセス・ルールで定まる最小距離より長くてもよい。

【0013】

上記増幅回路は、SOI基板に形成するようにしてもよい。

【0014】

また、上記課題を解決するために、本発明の別の観点によれば、上記CMOS集積回路を有することを特徴とする、増幅回路が提供される。

【発明の効果】

【0015】

以上説明したように本発明によれば、入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能な、新規かつ改良されたCMOS集積回路及び増幅回路を提供することができる。

【図面の簡単な説明】

【0016】

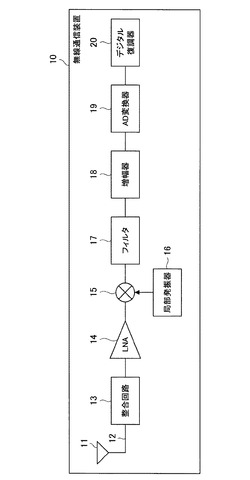

【図1】本発明の一実施形態にかかる無線通信装置10の構成例を示す説明図である。

【図2】LNA14の構成例を示す説明図である。

【図3】従来のMOSFETのレイアウト配置例である。

【図4】MOSFETにおけるゲート−ソース間、ゲート−ドレイン間およびソース−ドレイン間の配線間容量の存在を示す説明図である。

【図5】本発明の一実施形態にかかるLNA14に含まれるMOSFET111のレイアウト配置例を示す説明図である。

【図6】従来のLNAのNFと、本発明の一実施形態にかかるLNAのNFとを比較したものをグラフで示す説明図である。

【図7】本発明の一実施形態にかかるLNA14に含まれるMOSFET111のレイアウト配置例を示す説明図である。

【発明を実施するための形態】

【0017】

以下に添付図面を参照しながら、本発明の好適な実施の形態について詳細に説明する。なお、本明細書及び図面において、実質的に同一の機能構成を有する構成要素については、同一の符号を付することにより重複説明を省略する。

【0018】

<1.本発明の一実施形態>

[無線通信装置の構成例]

まず、本発明の一実施形態にかかる無線通信装置の構成例について説明する。図1は、本発明の一実施形態にかかる無線通信装置10の構成例を示す説明図である。以下、図1を用いて、本発明の一実施形態にかかる無線通信装置10の構成例について説明する。

【0019】

図1に示したように、本発明の一実施形態にかかる無線通信装置10は、アンテナ11と、伝送線路12と、インピーダンス整合回路13と、LNA14と、ミキサ15と、局部発振器16と、フィルタ17と、増幅器18と、AD変換器19と、デジタル復調器20と、を含んで構成される。

【0020】

アンテナ11は、電波を送信及び受信するものである。本実施形態では、無線通信装置10は、GHz帯の高周波信号、特に5GHz帯の高周波信号を送受信する。アンテナ11で受信された高周波信号は、伝送線路12を通じてインピーダンス整合回路13に送られる。

【0021】

インピーダンス整合回路13は、伝送線路12への高周波信号の反射が最小となるようなインピーダンスマッチングを行う回路である。アンテナ11で受信された高周波信号は、伝送線路12を通じてインピーダンス整合回路13に送られた後にLNA14に送られる。

【0022】

LNA14は、インピーダンス整合回路13から送られてくる高周波信号を増幅する。上述したように、LNA14は、回路自身が発生するノイズを出来る限り小さくして信号を増幅する回路である。そして本実施形態では、LNA14はCMOSで実現される。LNA14で増幅された高周波信号はミキサ15に送られる。

【0023】

ミキサ15は、LNA14で増幅された高周波信号と、局部発振器16が出力する高周波信号とを乗算するものである。ミキサ15で、LNA14で増幅された高周波信号と、局部発振器16が出力する高周波信号とが乗算されることで、GHz帯の高周波信号はMHz帯の信号に変換される。ミキサ15は、MHz帯の信号をフィルタ17に出力する。

【0024】

局部発振器16は、所定の周波数の高周波信号を出力する。局部発振器16が出力する高周波信号はミキサ15に送られる。上述したように、ミキサ15で、LNA14で増幅された高周波信号と、局部発振器16が出力する高周波信号とが乗算されることで、GHz帯の高周波信号はMHz帯の信号に変換される。

【0025】

フィルタ17は、ミキサ15から出力される信号の内、所定の周波数領域のみを通過させる。フィルタ17を通過した信号は増幅器18に送られる。増幅器18は、フィルタ17を通過した信号を増幅させる。増幅器18によって増幅された信号はAD変換器19に送られる。

【0026】

AD変換器19は、増幅器18から送られるアナログ信号をデジタル信号に変換する。AD変換器19によって変換されたデジタル信号はデジタル復調器20に送られる。デジタル復調器20は、AD変換器19によって変換されたデジタル信号を復調する。デジタル復調器20がデジタル信号を復調することで、無線通信装置10は受信した高周波信号の内容を把握することができる。

【0027】

以上、図1を用いて、本発明の一実施形態にかかる無線通信装置10の構成例について説明した。次に、本発明の一実施形態にかかる無線通信装置10に含まれるLNA14の構成例について説明する。

【0028】

[LNAの構成例]

図2は、本発明の一実施形態にかかる無線通信装置10に含まれるLNA14の構成例を示す説明図である。以下、図2を用いて本発明の一実施形態にかかる無線通信装置10に含まれるLNA14の構成について説明する。

【0029】

図2に示したように、本発明の一実施形態にかかる無線通信装置10に含まれるLNA14は、入力端子101と、インダクタ102と、保護回路103と、増幅回路104と、出力端子105と、を含んで構成される。増幅回路104は、NチャネルMOSFET111と、負荷抵抗112と、インダクタ113と、を含んで構成される。

【0030】

入力端子101は、インピーダンス整合回路13から送られてくる高周波信号が到達する端子である。入力端子101は、増幅回路104に含まれるNチャネルMOSFET111のゲートに、インダクタ102を介して接続される。保護回路103は、増幅回路104に大信号が入力されるのを防ぐための回路であり、所定の電圧以上の電圧が発生すると、その電圧以上の成分をカットして増幅回路104へ出力する。

【0031】

増幅回路104は、入力端子101が受けた高周波信号を増幅して、出力端子104へ出力する。上述したように、増幅回路103は、MOSFET111と、負荷抵抗112と、インダクタ113と、を含んで構成される。図2に示したように、MOSFET111は、ドレインが負荷抵抗112の一端に、ゲートが入力端子101に、ソースがインダクタ113の一端に、それぞれ接続されている。

【0032】

LNA14は、SOI(Silicon On Insulator)基板上に形成してもよい。SOI基板は、基板の高抵抗化による高いQ値を持つインダクタやトランジスタに付く寄生容量が小さく、LNA回路に適している。

【0033】

上述したように、CMOSで実現するLNA14の入力トランジスタであるMOSFET111において、トランジスタ本来の部位であるソース・ゲート・ドレインが発生する雑音以外に、トランジスタの各部位からの配線によって、NFが劣化する。そこで本実施形態では、レイアウト配置を工夫することでNFの増大を抑えることができるMOSFET111について説明する。

【0034】

以上、図2を用いて本発明の一実施形態にかかる無線通信装置10に含まれるLNA14の構成について説明した。次に、図2を用いて本発明の一実施形態にかかるLNA14に含まれるMOSFET111のレイアウト配置について説明する。

【0035】

[MOSFETのレイアウト配置例]

まず、従来のMOSFETのレイアウト配置例を説明する。図3は、従来のMOSFETのレイアウト配置例であり、ゲート抵抗の最小化を図るMOSFETのレイアウト配置例を示したものである。図3には、ゲート層21と、ソース層22と、ドレイン層23と、ウェル層24と、が図示されている。

【0036】

MOSFETのゲート抵抗の最小化を図るには、従来は、図3に示したように、ゲート層21の上に設けられるソース層22及びドレイン層23の構造を櫛形の構造としていた。このようにMOSFETを構成することで、ゲート抵抗を最小化することが可能となる。

【0037】

しかし、図3に示すようにMOSFETをレイアウトすると、ゲート−ソース間およびゲート−ドレイン間の配線間容量が大きくなる。図4は、MOSFETにおけるゲート−ソース間、ゲート−ドレイン間およびソース−ドレイン間の配線間容量の存在を示す説明図である。

【0038】

図3に示すようにMOSFETをレイアウトすると、ゲート層21と、ソース層22またはドレイン層23とが重なりあう領域において容量が存在する。すなわち、図4に示した容量Cgd及びCgsの存在によりNFが増大し、図3に示したようなMOSFETをCMOS LNAに使用すると、CMOS LNAの性能が劣化してしまうという問題があった。CMOS LNAの性能が劣化するということは、遮断周波数を向上させることが出来なくなり、高周波帯域におけるゲインを取ることが難しくなるという問題が生じる。

【0039】

そこで本実施形態では、MOSFET111のレイアウト配置を工夫することでNFの増大を抑える。MOSFET111のNFの増大を抑えることで、LNA14の性能の劣化を抑えることができる。

【0040】

図5は、本発明の一実施形態にかかるLNA14に含まれるMOSFET111のレイアウト配置例を示す説明図である。図5に示したように、本発明の一実施形態にかかるLNA14に含まれるMOSFET111は、一の基幹部(ゲート配線)から延びているゲート層121と、他の基幹部(ソース配線及びドレイン配線)から延びているソース層122およびドレイン層123と、ウェル層124とを有する。

【0041】

図5に示したように、本実施形態のMOSFET111は、ゲート層121と、ソース層122またはドレイン層123とは、重なりあう領域が存在していない。ゲート層121と、ソース層122またはドレイン層123とが重なり合っていないことで、ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsが最小限に抑えられ、LNA104の遮断周波数Ftの向上が見込める。遮断周波数Ftの向上が見込めることで、LNA104の重要な特性であるNFの向上が見込めることになる。

【0042】

図6は、従来のMOSFETを用いたLNAのNFと、本実施形態のMOSFET111を用いたLNA104のNFとを比較したものをグラフで示す説明図である。図6に示したグラフは、横軸が周波数を、縦軸がNFを示している。

【0043】

本実施形態にかかる無線通信装置10は、上述したように、GHz帯の高周波信号、特に5GHz帯の高周波信号を送受信する。従って図6に示したグラフは、高周波信号の周波数が4.9GHz〜5.9GHzにおけるLNAのNFを示している。

【0044】

図6に示したように、高周波信号の周波数が4.9GHz〜5.9GHzの範囲においては、いずれの周波数においても、従来のMOSFETを用いたLNAのNFより、本実施形態のMOSFET111を用いたLNA104のNFの方が優れていることが分かる。従って、本実施形態のMOSFET111は、図5に示したようにレイアウトすることで、図3に示すようなレイアウトを有する従来のMOSFETを用いたLNAに比べてNFが向上する。

【0045】

LNA104に含まれるMOSFETのレイアウト配置の別の例について説明する。図7は、本発明の一実施形態にかかるLNA14に含まれるMOSFET111’のレイアウト配置例を示す説明図である。図7に示したように、本発明の一実施形態にかかるLNA14に含まれるMOSFET111’は、一の基幹部から延びているゲート層121’と、他の基幹部から延びているソース層122’およびドレイン層123’とを有する。

【0046】

図7に示したMOSFET111’は、図5に示したものと同様の構成であるが、図5のMOSFET111と比べて、ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsを更に小さくするために、ゲート配線とソース層122’およびドレイン層123’との幅W1と、ドレイン幅W2と、ソース幅W3とを、図5のMOSFET111より広くしたものである。

【0047】

通常、トランジスタ周りのレイアウトは、チップ面積を最小限にするために、各々のプロセステクノロジのルールで定められる最小距離(最小ルール)で、ゲート配線とソース層122’およびドレイン層123’との幅W1、ドレイン幅W2、およびソース幅W3を設計する。図7に示したMOSFET111’のW1は、その最小ルールよりも広い幅を有するように設計する。またMOSFET111’のW2およびW3についても、同様に、その最小ルールよりも広い幅を有するように設計してもよい。

【0048】

ゲート長0.18μmのCMOSプロセスの場合に、MOSFET111’のソース、ドレイン領域およびゲート配線に最下層のメタル(1M)を張ったとして、例えば、ソース層122’およびドレイン層123’との幅W1を3μm、メタルの膜厚を0.3μm、ソース領域およびドレイン領域のメタル幅を0.2μm、MOSFET111’の櫛の数を100とすると、ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsは、およそ1fF程度となる。

【0049】

MOSFETの本来のゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsが例えば1pFであるとすれば、MOSFET111’のW1の幅が上記の値になれば、MOSFETの本来のゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsの1/1000程度になり、ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsを大きく低減させることができる。

【0050】

また、ドレイン幅W2やソース幅W3については、例えばゲート長0.18μmのCMOSプロセスでは、例えば1μm以上であれば、ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsの低減に寄与することができる。

【0051】

図7に示したMOSFET111’は、ゲート層121’と、ソース層122’またはドレイン層123’とで、重なりあう領域が存在せず、また、ゲート配線とソース層122’およびドレイン層123’との幅W1と、ドレイン幅W2と、ソース幅W3とを、図5のMOSFET111より広くすることで、ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsが最小限に抑えられ、LNA104の遮断周波数Ftの向上が見込める。遮断周波数Ftの向上が見込めることで、LNA104の重要な特性であるNFの向上が見込めることになる。

【0052】

<2.まとめ>

以上説明したように本発明の一実施形態によれば、LNA104に含まれるMOSFET111のレイアウトを、ゲート層121と、ソース層122またはドレイン層123とは、重なりあう領域が存在しないように設計する。MOSFET111を、ゲート層121と、ソース層122またはドレイン層123とで重なりあう領域が存在しないように設計することで、ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsを小さくすることができる。

【0053】

ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsを小さくすることで、LNA104は、遮断周波数Ftを向上させることができ、その結果として、LNAの重要特性であるNFを向上させることができる。

【0054】

以上、添付図面を参照しながら本発明の好適な実施形態について詳細に説明したが、本発明はかかる例に限定されない。本発明の属する技術の分野における通常の知識を有する者であれば、特許請求の範囲に記載された技術的思想の範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、これらについても、当然に本発明の技術的範囲に属するものと了解される。

【符号の説明】

【0055】

10 無線通信装置

11 アンテナ

12 伝送線路

13 インピーダンス整合回路

14 LNA

15 ミキサ

16 局部発振器

17 フィルタ

18 増幅器

19 AD変換器

20 デジタル復調器

101 入力端子

102 インダクタ

103 保護回路

104 増幅回路

105 出力端子

111 MOSFET

112 負荷抵抗

113 インダクタ

121 ゲート層

122 ソース層

123 ドレイン層

【技術分野】

【0001】

本発明は、CMOS集積回路及び増幅回路に関する。

【背景技術】

【0002】

携帯電話や無線データ通信装置のような無線通信システムにおいて、受信側では受信した信号を増幅するための増幅回路が設けられる。そのような増幅回路の一つとして、例えばローノイズアンプ(LNA)がある。LNAは、その回路自身が発生するノイズを出来る限り小さくして信号を増幅する回路であり、無線受信回路のフロントエンドに配置される必須の回路である。

【0003】

LNAをCMOS(Complementary Metal Oxide Semiconductor;相補型金属酸化膜半導体)で実現することは、LNAの低価格化に対して大きな需要がある。そして、LNAの本来の役割から、ノイズフィギュア(Noise Figure:雑音指数)の低減は常に求められる。

【0004】

CMOSで実現するLNA(CMOS LNA)の入力トランジスタにおいて、トランジスタ本来の部位であるソース・ゲート・ドレインが発生する雑音以外に、トランジスタの各部位からの配線によって抵抗が生じ、NFが劣化することが知られている。NFが劣化する要因の一つはゲート配線の抵抗からのノイズの発生によるものであり、このノイズを抑えるために、入力トランジスタの構造を櫛形構造にして、櫛の両端からゲートの電位を接続することで、ゲート配線の抵抗を最小にする方法がある。

【先行技術文献】

【非特許文献】

【0005】

【非特許文献1】The design of CMOS radio-frequency integrated circuits / Thomas H.Lee, Cambridge University Press. Page.287

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、入力トランジスタの構造を櫛形構造にして、櫛の両端からゲートの電位を接続すると、必然的にゲート−ソース間およびゲート−ドレイン間の配線間容量が大きくなる(非特許文献1参照)。従って、ゲート−ソース間およびゲート−ドレイン間の配線間容量の増大によって、NFが増大し、CMOS LNAの性能が劣化してしまうという問題があった。

【0007】

そこで、本発明は、上記問題に鑑みてなされたものであり、本発明の目的とするところは、入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能な、新規かつ改良されたCMOS集積回路及び増幅回路を提供することにある。

【課題を解決するための手段】

【0008】

上記課題を解決するために、本発明のある観点によれば、トランジスタを形成したCMOS集積回路であって、前記トランジスタは、ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、前記ゲート配線に対向した位置に形成されるソース配線から、前記ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、前記ゲート配線に対向した位置に形成されるドレイン配線から、前記ゲート電極の櫛歯の間の前記ソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、を備え、前記ゲート電極と、前記ソース電極または前記ドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路が提供される。

【0009】

かかる構成によれば、ゲート電極は、ゲート配線から櫛歯状に延びて形成されて信号入力端子からの入力信号が供給され、ソース電極は、ゲート配線に対向した位置に形成されるソース配線から、ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成されて接地端子に接続され、ドレイン電極は、ゲート配線に対向した位置に形成されるドレイン配線から、ゲート電極の櫛歯の間のソース電極が存在しない箇所に櫛歯状に延びて形成されて電源端子に接続される。そしてゲート電極と、ソース電極またはドレイン電極とは、重なり合う領域が存在しないよう構成される。その結果、入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能となる。

【0010】

前記ゲート電極と、前記ソース電極および前記ドレイン電極との間の距離は、前記トランジスタのノイズフィギュアを所定値以下にするものであってもよい。

【0011】

前記ゲート電極と、前記ソース電極および前記ドレイン電極との間の距離は、プロセス・ルールで定まる最小距離より長くてもよい。

【0012】

前記ソース電極間の距離および前記ドレイン電極間の距離は、プロセス・ルールで定まる最小距離より長くてもよい。

【0013】

上記増幅回路は、SOI基板に形成するようにしてもよい。

【0014】

また、上記課題を解決するために、本発明の別の観点によれば、上記CMOS集積回路を有することを特徴とする、増幅回路が提供される。

【発明の効果】

【0015】

以上説明したように本発明によれば、入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能な、新規かつ改良されたCMOS集積回路及び増幅回路を提供することができる。

【図面の簡単な説明】

【0016】

【図1】本発明の一実施形態にかかる無線通信装置10の構成例を示す説明図である。

【図2】LNA14の構成例を示す説明図である。

【図3】従来のMOSFETのレイアウト配置例である。

【図4】MOSFETにおけるゲート−ソース間、ゲート−ドレイン間およびソース−ドレイン間の配線間容量の存在を示す説明図である。

【図5】本発明の一実施形態にかかるLNA14に含まれるMOSFET111のレイアウト配置例を示す説明図である。

【図6】従来のLNAのNFと、本発明の一実施形態にかかるLNAのNFとを比較したものをグラフで示す説明図である。

【図7】本発明の一実施形態にかかるLNA14に含まれるMOSFET111のレイアウト配置例を示す説明図である。

【発明を実施するための形態】

【0017】

以下に添付図面を参照しながら、本発明の好適な実施の形態について詳細に説明する。なお、本明細書及び図面において、実質的に同一の機能構成を有する構成要素については、同一の符号を付することにより重複説明を省略する。

【0018】

<1.本発明の一実施形態>

[無線通信装置の構成例]

まず、本発明の一実施形態にかかる無線通信装置の構成例について説明する。図1は、本発明の一実施形態にかかる無線通信装置10の構成例を示す説明図である。以下、図1を用いて、本発明の一実施形態にかかる無線通信装置10の構成例について説明する。

【0019】

図1に示したように、本発明の一実施形態にかかる無線通信装置10は、アンテナ11と、伝送線路12と、インピーダンス整合回路13と、LNA14と、ミキサ15と、局部発振器16と、フィルタ17と、増幅器18と、AD変換器19と、デジタル復調器20と、を含んで構成される。

【0020】

アンテナ11は、電波を送信及び受信するものである。本実施形態では、無線通信装置10は、GHz帯の高周波信号、特に5GHz帯の高周波信号を送受信する。アンテナ11で受信された高周波信号は、伝送線路12を通じてインピーダンス整合回路13に送られる。

【0021】

インピーダンス整合回路13は、伝送線路12への高周波信号の反射が最小となるようなインピーダンスマッチングを行う回路である。アンテナ11で受信された高周波信号は、伝送線路12を通じてインピーダンス整合回路13に送られた後にLNA14に送られる。

【0022】

LNA14は、インピーダンス整合回路13から送られてくる高周波信号を増幅する。上述したように、LNA14は、回路自身が発生するノイズを出来る限り小さくして信号を増幅する回路である。そして本実施形態では、LNA14はCMOSで実現される。LNA14で増幅された高周波信号はミキサ15に送られる。

【0023】

ミキサ15は、LNA14で増幅された高周波信号と、局部発振器16が出力する高周波信号とを乗算するものである。ミキサ15で、LNA14で増幅された高周波信号と、局部発振器16が出力する高周波信号とが乗算されることで、GHz帯の高周波信号はMHz帯の信号に変換される。ミキサ15は、MHz帯の信号をフィルタ17に出力する。

【0024】

局部発振器16は、所定の周波数の高周波信号を出力する。局部発振器16が出力する高周波信号はミキサ15に送られる。上述したように、ミキサ15で、LNA14で増幅された高周波信号と、局部発振器16が出力する高周波信号とが乗算されることで、GHz帯の高周波信号はMHz帯の信号に変換される。

【0025】

フィルタ17は、ミキサ15から出力される信号の内、所定の周波数領域のみを通過させる。フィルタ17を通過した信号は増幅器18に送られる。増幅器18は、フィルタ17を通過した信号を増幅させる。増幅器18によって増幅された信号はAD変換器19に送られる。

【0026】

AD変換器19は、増幅器18から送られるアナログ信号をデジタル信号に変換する。AD変換器19によって変換されたデジタル信号はデジタル復調器20に送られる。デジタル復調器20は、AD変換器19によって変換されたデジタル信号を復調する。デジタル復調器20がデジタル信号を復調することで、無線通信装置10は受信した高周波信号の内容を把握することができる。

【0027】

以上、図1を用いて、本発明の一実施形態にかかる無線通信装置10の構成例について説明した。次に、本発明の一実施形態にかかる無線通信装置10に含まれるLNA14の構成例について説明する。

【0028】

[LNAの構成例]

図2は、本発明の一実施形態にかかる無線通信装置10に含まれるLNA14の構成例を示す説明図である。以下、図2を用いて本発明の一実施形態にかかる無線通信装置10に含まれるLNA14の構成について説明する。

【0029】

図2に示したように、本発明の一実施形態にかかる無線通信装置10に含まれるLNA14は、入力端子101と、インダクタ102と、保護回路103と、増幅回路104と、出力端子105と、を含んで構成される。増幅回路104は、NチャネルMOSFET111と、負荷抵抗112と、インダクタ113と、を含んで構成される。

【0030】

入力端子101は、インピーダンス整合回路13から送られてくる高周波信号が到達する端子である。入力端子101は、増幅回路104に含まれるNチャネルMOSFET111のゲートに、インダクタ102を介して接続される。保護回路103は、増幅回路104に大信号が入力されるのを防ぐための回路であり、所定の電圧以上の電圧が発生すると、その電圧以上の成分をカットして増幅回路104へ出力する。

【0031】

増幅回路104は、入力端子101が受けた高周波信号を増幅して、出力端子104へ出力する。上述したように、増幅回路103は、MOSFET111と、負荷抵抗112と、インダクタ113と、を含んで構成される。図2に示したように、MOSFET111は、ドレインが負荷抵抗112の一端に、ゲートが入力端子101に、ソースがインダクタ113の一端に、それぞれ接続されている。

【0032】

LNA14は、SOI(Silicon On Insulator)基板上に形成してもよい。SOI基板は、基板の高抵抗化による高いQ値を持つインダクタやトランジスタに付く寄生容量が小さく、LNA回路に適している。

【0033】

上述したように、CMOSで実現するLNA14の入力トランジスタであるMOSFET111において、トランジスタ本来の部位であるソース・ゲート・ドレインが発生する雑音以外に、トランジスタの各部位からの配線によって、NFが劣化する。そこで本実施形態では、レイアウト配置を工夫することでNFの増大を抑えることができるMOSFET111について説明する。

【0034】

以上、図2を用いて本発明の一実施形態にかかる無線通信装置10に含まれるLNA14の構成について説明した。次に、図2を用いて本発明の一実施形態にかかるLNA14に含まれるMOSFET111のレイアウト配置について説明する。

【0035】

[MOSFETのレイアウト配置例]

まず、従来のMOSFETのレイアウト配置例を説明する。図3は、従来のMOSFETのレイアウト配置例であり、ゲート抵抗の最小化を図るMOSFETのレイアウト配置例を示したものである。図3には、ゲート層21と、ソース層22と、ドレイン層23と、ウェル層24と、が図示されている。

【0036】

MOSFETのゲート抵抗の最小化を図るには、従来は、図3に示したように、ゲート層21の上に設けられるソース層22及びドレイン層23の構造を櫛形の構造としていた。このようにMOSFETを構成することで、ゲート抵抗を最小化することが可能となる。

【0037】

しかし、図3に示すようにMOSFETをレイアウトすると、ゲート−ソース間およびゲート−ドレイン間の配線間容量が大きくなる。図4は、MOSFETにおけるゲート−ソース間、ゲート−ドレイン間およびソース−ドレイン間の配線間容量の存在を示す説明図である。

【0038】

図3に示すようにMOSFETをレイアウトすると、ゲート層21と、ソース層22またはドレイン層23とが重なりあう領域において容量が存在する。すなわち、図4に示した容量Cgd及びCgsの存在によりNFが増大し、図3に示したようなMOSFETをCMOS LNAに使用すると、CMOS LNAの性能が劣化してしまうという問題があった。CMOS LNAの性能が劣化するということは、遮断周波数を向上させることが出来なくなり、高周波帯域におけるゲインを取ることが難しくなるという問題が生じる。

【0039】

そこで本実施形態では、MOSFET111のレイアウト配置を工夫することでNFの増大を抑える。MOSFET111のNFの増大を抑えることで、LNA14の性能の劣化を抑えることができる。

【0040】

図5は、本発明の一実施形態にかかるLNA14に含まれるMOSFET111のレイアウト配置例を示す説明図である。図5に示したように、本発明の一実施形態にかかるLNA14に含まれるMOSFET111は、一の基幹部(ゲート配線)から延びているゲート層121と、他の基幹部(ソース配線及びドレイン配線)から延びているソース層122およびドレイン層123と、ウェル層124とを有する。

【0041】

図5に示したように、本実施形態のMOSFET111は、ゲート層121と、ソース層122またはドレイン層123とは、重なりあう領域が存在していない。ゲート層121と、ソース層122またはドレイン層123とが重なり合っていないことで、ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsが最小限に抑えられ、LNA104の遮断周波数Ftの向上が見込める。遮断周波数Ftの向上が見込めることで、LNA104の重要な特性であるNFの向上が見込めることになる。

【0042】

図6は、従来のMOSFETを用いたLNAのNFと、本実施形態のMOSFET111を用いたLNA104のNFとを比較したものをグラフで示す説明図である。図6に示したグラフは、横軸が周波数を、縦軸がNFを示している。

【0043】

本実施形態にかかる無線通信装置10は、上述したように、GHz帯の高周波信号、特に5GHz帯の高周波信号を送受信する。従って図6に示したグラフは、高周波信号の周波数が4.9GHz〜5.9GHzにおけるLNAのNFを示している。

【0044】

図6に示したように、高周波信号の周波数が4.9GHz〜5.9GHzの範囲においては、いずれの周波数においても、従来のMOSFETを用いたLNAのNFより、本実施形態のMOSFET111を用いたLNA104のNFの方が優れていることが分かる。従って、本実施形態のMOSFET111は、図5に示したようにレイアウトすることで、図3に示すようなレイアウトを有する従来のMOSFETを用いたLNAに比べてNFが向上する。

【0045】

LNA104に含まれるMOSFETのレイアウト配置の別の例について説明する。図7は、本発明の一実施形態にかかるLNA14に含まれるMOSFET111’のレイアウト配置例を示す説明図である。図7に示したように、本発明の一実施形態にかかるLNA14に含まれるMOSFET111’は、一の基幹部から延びているゲート層121’と、他の基幹部から延びているソース層122’およびドレイン層123’とを有する。

【0046】

図7に示したMOSFET111’は、図5に示したものと同様の構成であるが、図5のMOSFET111と比べて、ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsを更に小さくするために、ゲート配線とソース層122’およびドレイン層123’との幅W1と、ドレイン幅W2と、ソース幅W3とを、図5のMOSFET111より広くしたものである。

【0047】

通常、トランジスタ周りのレイアウトは、チップ面積を最小限にするために、各々のプロセステクノロジのルールで定められる最小距離(最小ルール)で、ゲート配線とソース層122’およびドレイン層123’との幅W1、ドレイン幅W2、およびソース幅W3を設計する。図7に示したMOSFET111’のW1は、その最小ルールよりも広い幅を有するように設計する。またMOSFET111’のW2およびW3についても、同様に、その最小ルールよりも広い幅を有するように設計してもよい。

【0048】

ゲート長0.18μmのCMOSプロセスの場合に、MOSFET111’のソース、ドレイン領域およびゲート配線に最下層のメタル(1M)を張ったとして、例えば、ソース層122’およびドレイン層123’との幅W1を3μm、メタルの膜厚を0.3μm、ソース領域およびドレイン領域のメタル幅を0.2μm、MOSFET111’の櫛の数を100とすると、ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsは、およそ1fF程度となる。

【0049】

MOSFETの本来のゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsが例えば1pFであるとすれば、MOSFET111’のW1の幅が上記の値になれば、MOSFETの本来のゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsの1/1000程度になり、ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsを大きく低減させることができる。

【0050】

また、ドレイン幅W2やソース幅W3については、例えばゲート長0.18μmのCMOSプロセスでは、例えば1μm以上であれば、ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsの低減に寄与することができる。

【0051】

図7に示したMOSFET111’は、ゲート層121’と、ソース層122’またはドレイン層123’とで、重なりあう領域が存在せず、また、ゲート配線とソース層122’およびドレイン層123’との幅W1と、ドレイン幅W2と、ソース幅W3とを、図5のMOSFET111より広くすることで、ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsが最小限に抑えられ、LNA104の遮断周波数Ftの向上が見込める。遮断周波数Ftの向上が見込めることで、LNA104の重要な特性であるNFの向上が見込めることになる。

【0052】

<2.まとめ>

以上説明したように本発明の一実施形態によれば、LNA104に含まれるMOSFET111のレイアウトを、ゲート層121と、ソース層122またはドレイン層123とは、重なりあう領域が存在しないように設計する。MOSFET111を、ゲート層121と、ソース層122またはドレイン層123とで重なりあう領域が存在しないように設計することで、ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsを小さくすることができる。

【0053】

ゲート−ドレイン間容量Cgd及びゲート−ソース間容量Cgsを小さくすることで、LNA104は、遮断周波数Ftを向上させることができ、その結果として、LNAの重要特性であるNFを向上させることができる。

【0054】

以上、添付図面を参照しながら本発明の好適な実施形態について詳細に説明したが、本発明はかかる例に限定されない。本発明の属する技術の分野における通常の知識を有する者であれば、特許請求の範囲に記載された技術的思想の範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、これらについても、当然に本発明の技術的範囲に属するものと了解される。

【符号の説明】

【0055】

10 無線通信装置

11 アンテナ

12 伝送線路

13 インピーダンス整合回路

14 LNA

15 ミキサ

16 局部発振器

17 フィルタ

18 増幅器

19 AD変換器

20 デジタル復調器

101 入力端子

102 インダクタ

103 保護回路

104 増幅回路

105 出力端子

111 MOSFET

112 負荷抵抗

113 インダクタ

121 ゲート層

122 ソース層

123 ドレイン層

【特許請求の範囲】

【請求項1】

トランジスタを形成したCMOS集積回路であって、

前記トランジスタは、

ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、

前記ゲート配線に対向した位置に形成されるソース配線から、前記ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、

前記ゲート配線に対向した位置に形成されるドレイン配線から、前記ゲート電極の櫛歯の間の前記ソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、

を備え、

前記ゲート電極と、前記ソース電極または前記ドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路。

【請求項2】

前記ゲート電極と、前記ソース電極および前記ドレイン電極との間の距離は、前記トランジスタのノイズフィギュアを所定値以下にするものであることを特徴とする、請求項1に記載のCMOS集積回路。

【請求項3】

前記ゲート電極と、前記ソース電極および前記ドレイン電極との間の距離は、プロセス・ルールで定まる最小距離より長いことを特徴とする、請求項1に記載のCMOS集積回路。

【請求項4】

前記ソース電極間の距離および前記ドレイン電極間の距離は、プロセス・ルールで定まる最小距離より長いことを特徴とする、請求項3に記載のCMOS集積回路。

【請求項5】

SOI基板に形成することを特徴とする、請求項1に記載の増幅回路。

【請求項6】

請求項1〜5のいずれかに記載のCMOS集積回路を有することを特徴とする、増幅回路。

【請求項1】

トランジスタを形成したCMOS集積回路であって、

前記トランジスタは、

ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、

前記ゲート配線に対向した位置に形成されるソース配線から、前記ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、

前記ゲート配線に対向した位置に形成されるドレイン配線から、前記ゲート電極の櫛歯の間の前記ソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、

を備え、

前記ゲート電極と、前記ソース電極または前記ドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路。

【請求項2】

前記ゲート電極と、前記ソース電極および前記ドレイン電極との間の距離は、前記トランジスタのノイズフィギュアを所定値以下にするものであることを特徴とする、請求項1に記載のCMOS集積回路。

【請求項3】

前記ゲート電極と、前記ソース電極および前記ドレイン電極との間の距離は、プロセス・ルールで定まる最小距離より長いことを特徴とする、請求項1に記載のCMOS集積回路。

【請求項4】

前記ソース電極間の距離および前記ドレイン電極間の距離は、プロセス・ルールで定まる最小距離より長いことを特徴とする、請求項3に記載のCMOS集積回路。

【請求項5】

SOI基板に形成することを特徴とする、請求項1に記載の増幅回路。

【請求項6】

請求項1〜5のいずれかに記載のCMOS集積回路を有することを特徴とする、増幅回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−110269(P2013−110269A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−254071(P2011−254071)

【出願日】平成23年11月21日(2011.11.21)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月21日(2011.11.21)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

[ Back to top ]