CPUシステム

【課題】 新たに運用系となったホストユニットにおける共通メモリ内の不正データに起因した障害を未然に防止することを目的とする。

【解決手段】 ホストユニットが冗長構成を成し、運用系のホストユニットのみアクセス可能で共通バス上に配置する共通メモリ3を有することでホストユニットの系切り替え時に処理の引き継ぎを行うCPUシステムにおいて、ホストユニットの系切替が発生したタイミングにおける共通バスの状態を保持する。

【解決手段】 ホストユニットが冗長構成を成し、運用系のホストユニットのみアクセス可能で共通バス上に配置する共通メモリ3を有することでホストユニットの系切り替え時に処理の引き継ぎを行うCPUシステムにおいて、ホストユニットの系切替が発生したタイミングにおける共通バスの状態を保持する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、CPUシステムに関し、特に、ホストユニットの系の切替を行えるCPUシステムに関する。

【背景技術】

【0002】

プロセッサ(以下CPU)を搭載したホストユニットが冗長構成を成し、運用系のホストユニットのみアクセス可能で共通バス上に配置する共通メモリを有することで、ホストユニットの系切り替え時に処理の引き継ぎを行う従来のCPUシステムの構成を図5、運用系ホストユニットに障害が発生した場合の共通バスの状態を図6に示し説明する。

【0003】

本構成において、ホストユニット1が運用状態、ホストユニット2が待機状態であるとした場合、ホストユニット1は該CPUシステムを機能させるためのデータ(情報)を共通バス103を介して共通メモリ部3へ書き込み又は、読み出しを行う。

【0004】

この状態で保守者によるホストユニットの系切り替え制御が実行された場合、ホストユニット1のソフトウェアは実行途中の処理を完了後、切替信号101によりホストユニット2に対して、自系が待機となることを通知し、正常待機状態であったホストユニット2は切替信号102により運用状態に遷移したことをホストユニット1へ通知する。

【0005】

これによりソフトウェアが介在した正規の系切り替え手順を踏んだ系切り替えが完了する。

【0006】

一方、運用系ホストユニット1にハードウェア障害が発生した場合や強制リセットが実行された場合には実行中の処理に関係無く、切替信号101によりホストユニット2に対して、自系が運用できない状態となったことを通知し、正常待機状態であったホストユニット2は運用状態に遷移することで強制的に系切り替えが行われる。

【特許文献1】特開平01−099138号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかし、従来の冗長構成におけるホストユニット切り替え方法には次のような問題点があった。

【0008】

その問題点は、運用系ホストユニット1にハードウェア障害が発生した場合や強制リセットが実行された場合には実行中の処理に関係無く強制的に系切り替えが行われ、この時、ホストユニット1による共通メモリ部3に対するバスアクセスが実行中であれば、共通バス103上のバスアクセスは中断され、ライトアクセスであった場合にはそのアドレスのデータは不正データに書き変わってしまう恐れがあり、新たに運用系となったホストユニット2がホストユニット1の処理引き継ぎとして該アドレスのデータを使用した場合に不正データであるためにホストユニット2も障害に至り、システムダウンに陥る可能があるということである。

【0009】

そこで、本発明は、新たに運用系となったホストユニットにおける共通メモリ内の不正データに起因した障害を未然に防止することを目的とする。

【課題を解決するための手段】

【0010】

本発明は、上記課題を解決するための手段として、ホストユニットが冗長構成を成し、運用系の前記ホストユニットのみアクセス可能で共通バス上に配置する共通メモリを有することで前記ホストユニットの系切り替え時に処理の引き継ぎを行うCPUシステムにおいて、前記ホストユニットの系切替が発生したタイミングにおける共通バスの状態を保持する共通バス状態記録部を備える。

【0011】

本発明は、ホストユニットが負荷分散を目的とした複数の前記ホストユニットが全て運用系となるCPUシステムにおいて、共通バス状態を保持する契機となる前記ホストユニットの切替信号に変え、前記ホストユニットの運用状態を示す信号を使用する。

【発明の効果】

【0012】

本発明によれば、ホストユニットが冗長構成を成し、運用系のホストユニットのみアクセス可能で共通バス上に配置する共通メモリを有することでホストユニットの系切り替え時に処理の引き継ぎを行うCPUシステムにおいて、新たに運用系となったホストユニットにおける共通メモリ内の不正データに起因した障害を未然に防止することができる。

【0013】

その理由は、ホストユニットの系切り替えが発生したタイミングにおける共通バスの状態を保持することで、新たに運用系となったホストユニットは中断されたバスアクセスが存在するか否か、中断されたバスアクセスが存在する場合は、アドレス情報から不正データに書き変わってしまっている恐れのある共通メモリ内の特定データを認識することが可能となるためである。

【0014】

本発明によれば、ホストユニットが冗長構成を成す場合に限らず、負荷分散を目的とした複数のホストユニットが全て運用系となるCPUシステムにおいても共通メモリ内の不正データに起因した障害を未然に防止することができる。

【0015】

その理由は、共通バス状態を保持する契機となるホストユニットの切替信号に変え、ホストユニットの運用状態を示す信号を使用することで、運用を続けるホストユニットは障害が発生したホストユニットが共通メモリを更新中であったか否かを確認することが可能となり、中断されたバスアクセスが存在する場合は、アドレス情報から不正データに書き変わってしまっている恐れのある共通メモリ内の特定データを認識することが可能となるためである。

【発明を実施するための最良の形態】

【0016】

以下、添付図面を参照して本発明を実施するための最良の実施の形態を説明する。

【0017】

[構成の説明]

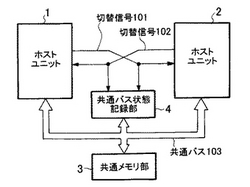

本発明の一実施の形態として、ホストユニットが冗長構成を成し、運用系のホストユニットのみアクセス可能で共通バス上に配置する共通メモリを有することでホストユニットの系切り替え時に処理の引き継ぎを行うCPUシステムにおけるホストユニット及び共通メモリ周辺の構成を図1、共通バス状態記録部4の内部構成を図2に示し説明する。

【0018】

図1において、ホストユニット1及び2は共通バス103を介して共通メモリ部3へ接続され、共通メモリ部3に格納するデータの書き込み及び、読み出しを行う。

【0019】

また、共通バス103は共通バス状態記録部4へも接続され、ホストユニット1及び2が実行する共通バス103上のバスアクセスは共通バス状態記録部4へも入力される。

【0020】

ホストユニット1とホストユニット2の系切り替えを制御する切替信号101及び102は、ホストユニット間に配線され、共通バス状態記録部4へも入力される。

【0021】

図2において、共通バス状態記録部4に入力される共通バス103は共通バスラッチ部5へ接続され、切替信号101及び102はラッチ信号生成部7へ接続される。

【0022】

切替信号101又は102によりホストユニットの系切り替えが発生したことを検出したラッチ信号生成部7は共通バスラッチ部5へ接続されるラッチ信号を生成し、共通バスラッチ部5はそのタイミングにおける共通バス103上のアドレス、データ、書き込み又は読み出しを示す転送方法、転送サイズなどの転送属性から成る系切り替え発生時の共通バス状態を保持する。

【0023】

ホストユニットの系切り替え発生タイミングにおける共通バス状態の読み出しは、共通バス状態記録部4に予め割り当てられたアドレスに対するリードバスアクセスにより実行され、バッファ制御部8は入力される共通バス103のアドレスバス及び転送属性からホストユニットにより開始されたバスアクセスが共通バス状態記録部4に予め割り当てられたアドレスであること且つリードアクセスであることを検出すると、リードバッファ6のイネーブル信号を有効にする。

【0024】

イネーブルされたリードバッファ6は共通バスラッチ部5に保持されている情報を共通バス103のデータバスへ中継し、ホストユニットは自ユニットが運用系となった系切り替え発生タイミングにおける共通バス103の状態を得ることができる。

【0025】

[動作の説明]

前述のCPUシステムにおけるホストユニット及び共通メモリ周辺の構成を図1、共通バス状態記録部4の内部構成を図2、運用系ホストユニットの障害発生により系切り替えが発生した場合の動作フローチャートを図3に示し本発明の動作を説明する。

【0026】

ホストユニット1が運用状態、ホストユニット2が待機状態であるとした場合、ホストユニット1は該CPUシステムを機能させるためのデータ(情報)を共通バス101を介して共通メモリ部3へ書き込み又は、読み出しを随時実行しており、ホストユニット1が実行する共通バス103上のバスアクセスは共通バス状態記録部4へも入力され、ホストユニットの系切り替えを制御する切替信号101及び102も共通バス状態記録部4へ入力される。

【0027】

この状態で保守者によるホストユニットの系切り替え制御が実行された場合、ホストユニット1のソフトウェアは実行途中の処理を完了後、切替信号101によりホストユニット2に対して、自系が待機となることを通知し、正常待機状態であったホストユニット2は切替信号102により運用状態に遷移したことをホストユニット1へ通知する。

【0028】

これによりソフトウェアが介在した正規の系切り替え手順を踏んだ系切り替えが完了する。

【0029】

共通バス状態記録部4においては、切替信号101の変化によりホストユニットの系切替が発生したことを検出したラッチ信号生成部7は共通バスラッチ部5へ接続されるラッチ信号を生成し、共通バスラッチ部5はそのタイミングにおける共通バス103上のアドレス、データ、書き込み又は読み出しを示す転送方法、転送サイズなどの転送属性から成る系切り替え発生時の共通バス状態を保持する。

【0030】

この時、ホストユニット1による実行途中の処理はないため、共通バス103上で実行されているバスアクセスは存在せず、共通バスラッチ部5は非アクティブ状態の共通バス状態を保持することになる。

【0031】

系切り替えにより新たに運用系となったホストユニット2は共通バス状態記録部4に予め割り当てられたアドレスに対するリードバスアクセスを実行する。

【0032】

共通バス103のアドレスバス及び転送属性が入力されるバッファ制御部8はホストユニット2により開始されたバスアクセスが共通バス記録部4に予め割り当てられたアドレスであること且つリードアクセスであることを検出し、リードバッファ6のイネーブル信号を有効にする。

【0033】

イネーブルされたリードバッファ6は共通バスラッチ部5に保持されている情報を共通バス103のデータバスへ中継し、ホストユニット2は自ユニットが運用系となった系切り替え発生タイミングにおける共通バス103の状態、即ち、非アクティブ状態を示す状態(プルアップ終端であれば全信号がHiレベル)を得て、共通メモリ部3に格納されるデータに、不正な可能性があるデータが存在しないことを認識した上で運用系ホストユニットとしての処理を引き継ぐ。

【0034】

一方、ハードウェア障害や強制リセットに代表される正規の系切り替え手順を踏まない系切り替えは、ホストユニット1が実行中の処理に関係無く、切替信号101によりホストユニット2に対して、自系が運用できない状態となったことを通知し、正常待機状態であったホストユニット2は運用状態に遷移することで強制的に系切り替えが行われる。

【0035】

正規な系切り替え時と同様に、共通バス状態記録部4において、切替信号101の変化によりホストユニットの系切り替えが発生したことを検出したラッチ信号生成部7は共通バスラッチ部5へ接続されるラッチ信号を生成し、共通バスラッチ部5はそのタイミングにおける共通バス103上のアドレス、データ、書き込み又は読み出しを示す転送方法、転送サイズなどの転送属性から成る系切り替え発生時の共通バス状態を保持する。

【0036】

系切り替え発生時にホストユニット1による共通メモリ部3に対するバスアクセス実行中であれば、バスラッチ部5はそのバスアクセスが示すアドレス、データ、転送属性を保持し、バスアクセス実行中でなければ共通非アクティブ状態の共通バス状態を保持する。

【0037】

系切り替えにより新たに運用系となったホストユニット2は共通バス状態記録部4に予め割り当てられたアドレスに対するリードバスアクセスを実行する。

【0038】

共通バス103のアドレスバス及び転送属性が入力されるバッファ制御部8はホストユニット2により開始されたバスアクセスが共通バス記録部4に予め割り当てられたアドレスであること且つリードアクセスであることを検出し、リードバッファ6のイネーブル信号を有効にする。

【0039】

イネーブルされたリードバッファ6は共通バスラッチ部5に保持されている情報を共通バス103のデータバスへ中継し、ホストユニット2は自ユニットが運用系となった系切り替え発生タイミングにおける共通バス103の状態、即ち、系切り替え発生時にホストユニット1による共通メモリ部3に対するバスアクセス実行中であれば、強制的に中断されたバスアクセスが示すアドレス、データ、転送属性、バスアクセス実行中でなければ非アクティブ状態を示す状態(プルアップ終端であれば全信号がHiレベル)を得る。

【0040】

共通バスの状態が非アクティブ状態であれば、共通メモリ部3に格納されるデータに、不正な可能性があるデータが存在しないことを認識した上で運用系ホストユニットとしての処理を継続し、共通メモリ部3へのライトアクセスを示す場合は、そのアドレスのデータは不正データに書き変わっている可能性があると判断し、以降の処理では使用しないなど、そのデータを無効として運用系ホストユニットとしての処理を引き継ぐ。

【0041】

[他の実施の形態]

本発明の他の実施の形態について、図4を参照して説明する。

【0042】

図1に示すホストユニットが冗長構成を成し、共通バス上に配置する共通メモリを有することでホストユニットの系切り替え時に処理の引き継ぎを行うCPUシステムにおけるホストユニット及び共通メモリ周辺の構成に対し、共通メモリ部が3−1及び3−2による冗長構成を成し、共通メモリの切替信号301及び302が共通バス記録部4へ入力され、共通バス状態記録部4では共通メモリ部の系切り替え発生時も切替信号301又は302の変化により共通メモリ部の系切り替えが発生したことを検出し、そのタイミングにおける共通バス103の状態を保持する。

【0043】

なお、共通メモリ部3−1及び3−2へ対するバスアクセスは運用系アドレスへのみ実行され、ライトアクセスでは運用系共通メモリへの書き込みと同時に待機系共通メモリも同じデータが書き込まれ、リードアクセスでは運用系共通メモリのみがデータ出力を行うものとする。

【0044】

本実施の形態は、共通メモリ部の系切り替えが発生したタイミングにおける共通バスの状態を確認することが可能となるため、運用系共通メモリ部のメモリ不良が原因の様な障害により系切り替えが発生した場合に不良箇所の特定など障害調査のために有益な情報を得ることができるという新たな効果を有する。

【産業上の利用可能性】

【0045】

本発明は、共通メモリ内の不正データに起因した障害を未然に防止するようなCPUシステムに利用できる。

【図面の簡単な説明】

【0046】

【図1】本発明の一実施の形態としてのCPUシステムの構成を示すブロック図である。

【図2】共通バス状態記録部の内部構成を示すブロック図である。

【図3】本発明の一実施の形態としてのCPUシステムの動作を示すブロック図である。

【図4】本発明の他の実施の形態の構成を示すブロック図である。

【図5】従来のCPUシステムの構成を示すブロック図である。

【図6】運用系ホストユニットに障害が発生した場合の共通バスの状態を示すブロック図である。

【符号の説明】

【0047】

1 ホストユニット

2 ホストユニット

3 共通メモリ部

4 共通バス状態記録部

5 共通バスラッチ部

6 リードバッファ

7 ラッチ信号生成部

8 バッファ制御部

101 切替信号

102 切替信号

103 共通バス

【技術分野】

【0001】

本発明は、CPUシステムに関し、特に、ホストユニットの系の切替を行えるCPUシステムに関する。

【背景技術】

【0002】

プロセッサ(以下CPU)を搭載したホストユニットが冗長構成を成し、運用系のホストユニットのみアクセス可能で共通バス上に配置する共通メモリを有することで、ホストユニットの系切り替え時に処理の引き継ぎを行う従来のCPUシステムの構成を図5、運用系ホストユニットに障害が発生した場合の共通バスの状態を図6に示し説明する。

【0003】

本構成において、ホストユニット1が運用状態、ホストユニット2が待機状態であるとした場合、ホストユニット1は該CPUシステムを機能させるためのデータ(情報)を共通バス103を介して共通メモリ部3へ書き込み又は、読み出しを行う。

【0004】

この状態で保守者によるホストユニットの系切り替え制御が実行された場合、ホストユニット1のソフトウェアは実行途中の処理を完了後、切替信号101によりホストユニット2に対して、自系が待機となることを通知し、正常待機状態であったホストユニット2は切替信号102により運用状態に遷移したことをホストユニット1へ通知する。

【0005】

これによりソフトウェアが介在した正規の系切り替え手順を踏んだ系切り替えが完了する。

【0006】

一方、運用系ホストユニット1にハードウェア障害が発生した場合や強制リセットが実行された場合には実行中の処理に関係無く、切替信号101によりホストユニット2に対して、自系が運用できない状態となったことを通知し、正常待機状態であったホストユニット2は運用状態に遷移することで強制的に系切り替えが行われる。

【特許文献1】特開平01−099138号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかし、従来の冗長構成におけるホストユニット切り替え方法には次のような問題点があった。

【0008】

その問題点は、運用系ホストユニット1にハードウェア障害が発生した場合や強制リセットが実行された場合には実行中の処理に関係無く強制的に系切り替えが行われ、この時、ホストユニット1による共通メモリ部3に対するバスアクセスが実行中であれば、共通バス103上のバスアクセスは中断され、ライトアクセスであった場合にはそのアドレスのデータは不正データに書き変わってしまう恐れがあり、新たに運用系となったホストユニット2がホストユニット1の処理引き継ぎとして該アドレスのデータを使用した場合に不正データであるためにホストユニット2も障害に至り、システムダウンに陥る可能があるということである。

【0009】

そこで、本発明は、新たに運用系となったホストユニットにおける共通メモリ内の不正データに起因した障害を未然に防止することを目的とする。

【課題を解決するための手段】

【0010】

本発明は、上記課題を解決するための手段として、ホストユニットが冗長構成を成し、運用系の前記ホストユニットのみアクセス可能で共通バス上に配置する共通メモリを有することで前記ホストユニットの系切り替え時に処理の引き継ぎを行うCPUシステムにおいて、前記ホストユニットの系切替が発生したタイミングにおける共通バスの状態を保持する共通バス状態記録部を備える。

【0011】

本発明は、ホストユニットが負荷分散を目的とした複数の前記ホストユニットが全て運用系となるCPUシステムにおいて、共通バス状態を保持する契機となる前記ホストユニットの切替信号に変え、前記ホストユニットの運用状態を示す信号を使用する。

【発明の効果】

【0012】

本発明によれば、ホストユニットが冗長構成を成し、運用系のホストユニットのみアクセス可能で共通バス上に配置する共通メモリを有することでホストユニットの系切り替え時に処理の引き継ぎを行うCPUシステムにおいて、新たに運用系となったホストユニットにおける共通メモリ内の不正データに起因した障害を未然に防止することができる。

【0013】

その理由は、ホストユニットの系切り替えが発生したタイミングにおける共通バスの状態を保持することで、新たに運用系となったホストユニットは中断されたバスアクセスが存在するか否か、中断されたバスアクセスが存在する場合は、アドレス情報から不正データに書き変わってしまっている恐れのある共通メモリ内の特定データを認識することが可能となるためである。

【0014】

本発明によれば、ホストユニットが冗長構成を成す場合に限らず、負荷分散を目的とした複数のホストユニットが全て運用系となるCPUシステムにおいても共通メモリ内の不正データに起因した障害を未然に防止することができる。

【0015】

その理由は、共通バス状態を保持する契機となるホストユニットの切替信号に変え、ホストユニットの運用状態を示す信号を使用することで、運用を続けるホストユニットは障害が発生したホストユニットが共通メモリを更新中であったか否かを確認することが可能となり、中断されたバスアクセスが存在する場合は、アドレス情報から不正データに書き変わってしまっている恐れのある共通メモリ内の特定データを認識することが可能となるためである。

【発明を実施するための最良の形態】

【0016】

以下、添付図面を参照して本発明を実施するための最良の実施の形態を説明する。

【0017】

[構成の説明]

本発明の一実施の形態として、ホストユニットが冗長構成を成し、運用系のホストユニットのみアクセス可能で共通バス上に配置する共通メモリを有することでホストユニットの系切り替え時に処理の引き継ぎを行うCPUシステムにおけるホストユニット及び共通メモリ周辺の構成を図1、共通バス状態記録部4の内部構成を図2に示し説明する。

【0018】

図1において、ホストユニット1及び2は共通バス103を介して共通メモリ部3へ接続され、共通メモリ部3に格納するデータの書き込み及び、読み出しを行う。

【0019】

また、共通バス103は共通バス状態記録部4へも接続され、ホストユニット1及び2が実行する共通バス103上のバスアクセスは共通バス状態記録部4へも入力される。

【0020】

ホストユニット1とホストユニット2の系切り替えを制御する切替信号101及び102は、ホストユニット間に配線され、共通バス状態記録部4へも入力される。

【0021】

図2において、共通バス状態記録部4に入力される共通バス103は共通バスラッチ部5へ接続され、切替信号101及び102はラッチ信号生成部7へ接続される。

【0022】

切替信号101又は102によりホストユニットの系切り替えが発生したことを検出したラッチ信号生成部7は共通バスラッチ部5へ接続されるラッチ信号を生成し、共通バスラッチ部5はそのタイミングにおける共通バス103上のアドレス、データ、書き込み又は読み出しを示す転送方法、転送サイズなどの転送属性から成る系切り替え発生時の共通バス状態を保持する。

【0023】

ホストユニットの系切り替え発生タイミングにおける共通バス状態の読み出しは、共通バス状態記録部4に予め割り当てられたアドレスに対するリードバスアクセスにより実行され、バッファ制御部8は入力される共通バス103のアドレスバス及び転送属性からホストユニットにより開始されたバスアクセスが共通バス状態記録部4に予め割り当てられたアドレスであること且つリードアクセスであることを検出すると、リードバッファ6のイネーブル信号を有効にする。

【0024】

イネーブルされたリードバッファ6は共通バスラッチ部5に保持されている情報を共通バス103のデータバスへ中継し、ホストユニットは自ユニットが運用系となった系切り替え発生タイミングにおける共通バス103の状態を得ることができる。

【0025】

[動作の説明]

前述のCPUシステムにおけるホストユニット及び共通メモリ周辺の構成を図1、共通バス状態記録部4の内部構成を図2、運用系ホストユニットの障害発生により系切り替えが発生した場合の動作フローチャートを図3に示し本発明の動作を説明する。

【0026】

ホストユニット1が運用状態、ホストユニット2が待機状態であるとした場合、ホストユニット1は該CPUシステムを機能させるためのデータ(情報)を共通バス101を介して共通メモリ部3へ書き込み又は、読み出しを随時実行しており、ホストユニット1が実行する共通バス103上のバスアクセスは共通バス状態記録部4へも入力され、ホストユニットの系切り替えを制御する切替信号101及び102も共通バス状態記録部4へ入力される。

【0027】

この状態で保守者によるホストユニットの系切り替え制御が実行された場合、ホストユニット1のソフトウェアは実行途中の処理を完了後、切替信号101によりホストユニット2に対して、自系が待機となることを通知し、正常待機状態であったホストユニット2は切替信号102により運用状態に遷移したことをホストユニット1へ通知する。

【0028】

これによりソフトウェアが介在した正規の系切り替え手順を踏んだ系切り替えが完了する。

【0029】

共通バス状態記録部4においては、切替信号101の変化によりホストユニットの系切替が発生したことを検出したラッチ信号生成部7は共通バスラッチ部5へ接続されるラッチ信号を生成し、共通バスラッチ部5はそのタイミングにおける共通バス103上のアドレス、データ、書き込み又は読み出しを示す転送方法、転送サイズなどの転送属性から成る系切り替え発生時の共通バス状態を保持する。

【0030】

この時、ホストユニット1による実行途中の処理はないため、共通バス103上で実行されているバスアクセスは存在せず、共通バスラッチ部5は非アクティブ状態の共通バス状態を保持することになる。

【0031】

系切り替えにより新たに運用系となったホストユニット2は共通バス状態記録部4に予め割り当てられたアドレスに対するリードバスアクセスを実行する。

【0032】

共通バス103のアドレスバス及び転送属性が入力されるバッファ制御部8はホストユニット2により開始されたバスアクセスが共通バス記録部4に予め割り当てられたアドレスであること且つリードアクセスであることを検出し、リードバッファ6のイネーブル信号を有効にする。

【0033】

イネーブルされたリードバッファ6は共通バスラッチ部5に保持されている情報を共通バス103のデータバスへ中継し、ホストユニット2は自ユニットが運用系となった系切り替え発生タイミングにおける共通バス103の状態、即ち、非アクティブ状態を示す状態(プルアップ終端であれば全信号がHiレベル)を得て、共通メモリ部3に格納されるデータに、不正な可能性があるデータが存在しないことを認識した上で運用系ホストユニットとしての処理を引き継ぐ。

【0034】

一方、ハードウェア障害や強制リセットに代表される正規の系切り替え手順を踏まない系切り替えは、ホストユニット1が実行中の処理に関係無く、切替信号101によりホストユニット2に対して、自系が運用できない状態となったことを通知し、正常待機状態であったホストユニット2は運用状態に遷移することで強制的に系切り替えが行われる。

【0035】

正規な系切り替え時と同様に、共通バス状態記録部4において、切替信号101の変化によりホストユニットの系切り替えが発生したことを検出したラッチ信号生成部7は共通バスラッチ部5へ接続されるラッチ信号を生成し、共通バスラッチ部5はそのタイミングにおける共通バス103上のアドレス、データ、書き込み又は読み出しを示す転送方法、転送サイズなどの転送属性から成る系切り替え発生時の共通バス状態を保持する。

【0036】

系切り替え発生時にホストユニット1による共通メモリ部3に対するバスアクセス実行中であれば、バスラッチ部5はそのバスアクセスが示すアドレス、データ、転送属性を保持し、バスアクセス実行中でなければ共通非アクティブ状態の共通バス状態を保持する。

【0037】

系切り替えにより新たに運用系となったホストユニット2は共通バス状態記録部4に予め割り当てられたアドレスに対するリードバスアクセスを実行する。

【0038】

共通バス103のアドレスバス及び転送属性が入力されるバッファ制御部8はホストユニット2により開始されたバスアクセスが共通バス記録部4に予め割り当てられたアドレスであること且つリードアクセスであることを検出し、リードバッファ6のイネーブル信号を有効にする。

【0039】

イネーブルされたリードバッファ6は共通バスラッチ部5に保持されている情報を共通バス103のデータバスへ中継し、ホストユニット2は自ユニットが運用系となった系切り替え発生タイミングにおける共通バス103の状態、即ち、系切り替え発生時にホストユニット1による共通メモリ部3に対するバスアクセス実行中であれば、強制的に中断されたバスアクセスが示すアドレス、データ、転送属性、バスアクセス実行中でなければ非アクティブ状態を示す状態(プルアップ終端であれば全信号がHiレベル)を得る。

【0040】

共通バスの状態が非アクティブ状態であれば、共通メモリ部3に格納されるデータに、不正な可能性があるデータが存在しないことを認識した上で運用系ホストユニットとしての処理を継続し、共通メモリ部3へのライトアクセスを示す場合は、そのアドレスのデータは不正データに書き変わっている可能性があると判断し、以降の処理では使用しないなど、そのデータを無効として運用系ホストユニットとしての処理を引き継ぐ。

【0041】

[他の実施の形態]

本発明の他の実施の形態について、図4を参照して説明する。

【0042】

図1に示すホストユニットが冗長構成を成し、共通バス上に配置する共通メモリを有することでホストユニットの系切り替え時に処理の引き継ぎを行うCPUシステムにおけるホストユニット及び共通メモリ周辺の構成に対し、共通メモリ部が3−1及び3−2による冗長構成を成し、共通メモリの切替信号301及び302が共通バス記録部4へ入力され、共通バス状態記録部4では共通メモリ部の系切り替え発生時も切替信号301又は302の変化により共通メモリ部の系切り替えが発生したことを検出し、そのタイミングにおける共通バス103の状態を保持する。

【0043】

なお、共通メモリ部3−1及び3−2へ対するバスアクセスは運用系アドレスへのみ実行され、ライトアクセスでは運用系共通メモリへの書き込みと同時に待機系共通メモリも同じデータが書き込まれ、リードアクセスでは運用系共通メモリのみがデータ出力を行うものとする。

【0044】

本実施の形態は、共通メモリ部の系切り替えが発生したタイミングにおける共通バスの状態を確認することが可能となるため、運用系共通メモリ部のメモリ不良が原因の様な障害により系切り替えが発生した場合に不良箇所の特定など障害調査のために有益な情報を得ることができるという新たな効果を有する。

【産業上の利用可能性】

【0045】

本発明は、共通メモリ内の不正データに起因した障害を未然に防止するようなCPUシステムに利用できる。

【図面の簡単な説明】

【0046】

【図1】本発明の一実施の形態としてのCPUシステムの構成を示すブロック図である。

【図2】共通バス状態記録部の内部構成を示すブロック図である。

【図3】本発明の一実施の形態としてのCPUシステムの動作を示すブロック図である。

【図4】本発明の他の実施の形態の構成を示すブロック図である。

【図5】従来のCPUシステムの構成を示すブロック図である。

【図6】運用系ホストユニットに障害が発生した場合の共通バスの状態を示すブロック図である。

【符号の説明】

【0047】

1 ホストユニット

2 ホストユニット

3 共通メモリ部

4 共通バス状態記録部

5 共通バスラッチ部

6 リードバッファ

7 ラッチ信号生成部

8 バッファ制御部

101 切替信号

102 切替信号

103 共通バス

【特許請求の範囲】

【請求項1】

ホストユニットが冗長構成を成し、運用系の前記ホストユニットのみアクセス可能で共通バス上に配置する共通メモリを有することで前記ホストユニットの系切り替え時に処理の引き継ぎを行うCPUシステムにおいて、

前記ホストユニットの系切替が発生したタイミングにおける共通バスの状態を保持する共通バス状態記録部を備えることを特徴とするCPUシステム。

【請求項2】

ホストユニットが負荷分散を目的とした複数の前記ホストユニットが全て運用系となるCPUシステムにおいて、

共通バス状態を保持する契機となる前記ホストユニットの切替信号に変え、前記ホストユニットの運用状態を示す信号を使用することを特徴とするCPUシステム。

【請求項3】

前記共通バス状態記録部は、前記ホストユニットの系切り替えが発生したことを検出しラッチ信号を生成するラッチ信号生成部と、

共通バス上の転送属性からなる系切り替え発生時の共通バス状態を保持する共通バスラッチ部と、を備えることを特徴とする請求項1記載のCPUシステム。

【請求項4】

入力される前記共通バスのアドレスバス及び転送属性からホストユニットにより開始されたバスアクセスが前記共通バス状態記録部に予め割り当てられたアドレスであること且つリードアクセスであることを検出するバッファ制御部をさらに備えることを特徴とする請求項3記載のCPUシステム。

【請求項5】

前記共通メモリを複数備えることを特徴とする請求項1又は2記載のCPUシステム。

【請求項6】

前記共通メモリは二つであることを特徴とする請求項5記載のCPUシステム。

【請求項1】

ホストユニットが冗長構成を成し、運用系の前記ホストユニットのみアクセス可能で共通バス上に配置する共通メモリを有することで前記ホストユニットの系切り替え時に処理の引き継ぎを行うCPUシステムにおいて、

前記ホストユニットの系切替が発生したタイミングにおける共通バスの状態を保持する共通バス状態記録部を備えることを特徴とするCPUシステム。

【請求項2】

ホストユニットが負荷分散を目的とした複数の前記ホストユニットが全て運用系となるCPUシステムにおいて、

共通バス状態を保持する契機となる前記ホストユニットの切替信号に変え、前記ホストユニットの運用状態を示す信号を使用することを特徴とするCPUシステム。

【請求項3】

前記共通バス状態記録部は、前記ホストユニットの系切り替えが発生したことを検出しラッチ信号を生成するラッチ信号生成部と、

共通バス上の転送属性からなる系切り替え発生時の共通バス状態を保持する共通バスラッチ部と、を備えることを特徴とする請求項1記載のCPUシステム。

【請求項4】

入力される前記共通バスのアドレスバス及び転送属性からホストユニットにより開始されたバスアクセスが前記共通バス状態記録部に予め割り当てられたアドレスであること且つリードアクセスであることを検出するバッファ制御部をさらに備えることを特徴とする請求項3記載のCPUシステム。

【請求項5】

前記共通メモリを複数備えることを特徴とする請求項1又は2記載のCPUシステム。

【請求項6】

前記共通メモリは二つであることを特徴とする請求項5記載のCPUシステム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2006−260393(P2006−260393A)

【公開日】平成18年9月28日(2006.9.28)

【国際特許分類】

【出願番号】特願2005−79503(P2005−79503)

【出願日】平成17年3月18日(2005.3.18)

【出願人】(390010179)埼玉日本電気株式会社 (1,228)

【Fターム(参考)】

【公開日】平成18年9月28日(2006.9.28)

【国際特許分類】

【出願日】平成17年3月18日(2005.3.18)

【出願人】(390010179)埼玉日本電気株式会社 (1,228)

【Fターム(参考)】

[ Back to top ]