DA変換装置

【課題】より高精度でビット拡張ができるDA変換装置を提供する。

【解決手段】DA変換装置12は、2m個のnビットのDAコンバータ14と、このDAコンバータ14からの出力を加算する演算器16と、前記DAコンバータに入力するnビットの中間データを生成するデータプロセッサ12と、を備えている。データプロセッサは、各DAコンバータ14の中間データとして、入力データの上位nビットデータに、補正値を付加したデータを生成する。補正値は、その総和が、入力データの下位mビットデータが示す値に等しくなるように設定される。

【解決手段】DA変換装置12は、2m個のnビットのDAコンバータ14と、このDAコンバータ14からの出力を加算する演算器16と、前記DAコンバータに入力するnビットの中間データを生成するデータプロセッサ12と、を備えている。データプロセッサは、各DAコンバータ14の中間データとして、入力データの上位nビットデータに、補正値を付加したデータを生成する。補正値は、その総和が、入力データの下位mビットデータが示す値に等しくなるように設定される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、デジタルデータをアナログデータに変換するDA変換装置に関し、特に複数のDAコンバータから構成されるDA変換装置に関する。

【背景技術】

【0002】

従来より、複数のDAコンバータを組み合わせて、DAコンバータ単体がもつ分解能以上の分解能をもったDA変換装置を構築するビット拡張の技術が知られている。たとえば、特許文献1には、(m+n)ビットのデジタルデータのうち上位mビットが入力される第1のDAコンバータと、前記でジタルデータのうち下位nビットが入力される第2のDAコンバータと、を設けるとともに、各DAコンバータからの出力を、重み付け加算するビット拡張技術が開示されている。かかる技術によれば、nビットのDAコンバータで、n+mビットのデータを取り扱うことができる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平7−162311号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、こうした従来のビット拡張技術では、抵抗器などのアナログ素子を用いて各DAコンバータからの出力値(アナログ信号)を重み付け処理する必要がある。かかる、アナログ素子を用いて、アナログ信号の重み付け処理を精度よく行なうことは非常に困難であった。そして、結果として、DA変換装置の変換精度が低くなるという問題があった。

【0005】

そこで、本発明では、より高精度でビット拡張ができるDA変換装置を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明のDA変換装置は、2m個のnビットの第一DAコンバータと、上流側から入力されるn+mビットの入力データに基づいて、前記第一DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、前記第一DAコンバータからの出力を加算する演算器と、を備え、前記データ生成手段は、第一DAコンバータの中間データとして入力データの上位nビットデータに補正値を付加したデータを生成し、前記補正値は、入力データの下位mビットデータに基づいて各DAコンバータごとに設定される0以上の数値であって、その総和が前記入力データの下位mビットデータが示す値に等しくなるように設定される数値である、ことを特徴とする。

【0007】

他の本発明であるDA変換装置は、2m個のnビットの第一DAコンバータと、1個のnビットの第二DAコンバータと、上流側から入力されるn+mビットの入力データに基づいて、前記第一、第二DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、前記第一、第二DAコンバータからの出力を加算する演算器と、を備え、前記データ生成手段は、第一DAコンバータの中間データとして入力データの上位nビットデータに補正値を付加したデータを、第二DAコンバータの中間データとして0に補正値を付加したデータを、それぞれ生成し、前記補正値は、入力データの下位mビットデータに基づいて各DAコンバータごとに設定される0以上の数値であって、その総和が前記入力データの下位mビットデータが示す値に等しくなるように設定される数値である、ことを特徴とする。この場合、前記データ生成手段は、入力データの上位nビットデータが最大値の場合、前記第一DAコンバータの補正値を0とし、第二DAコンバータの補正値を入力データの下位mビットデータが示す値として、中間データを生成する、ことが望ましい。

【0008】

また、上述のDA変換装置においては、前記データ生成手段は、入力データの上位nビットデータが最大値未満の場合、前記下位mビットデータが示す値の個数の第一DAコンバータの補正値を1とし、他のDAコンバータの補正値を0として、中間データを生成する、ことが望ましい。

【0009】

他の本発明であるDA変換装置は、2m個のnビットの第一DAコンバータと、1個のnビットの第二DAコンバータと、上流側から入力されるn+mビットの入力データに基づいて、前記第一、第二DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、前記第一、第二DAコンバータからの出力を加算する演算器と、を備え、前記データ生成手段は、第一DAコンバータの中間データとして入力データの上位nビットデータを、第二DAコンバータの中間データとして入力データの下位mビットデータを、それぞれ生成する、ことを特徴とする。

【0010】

他の本発明であるDA変換装置は、2m個以上のnビットのDAコンバータと、上流側から入力されるn+mビットの入力データに基づいて、前記DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、前記DAコンバータからの出力を加算する演算器と、を備え、前記データ生成手段は、2m個のDAコンバータの中間データとして前記入力データの上位nビットデータに補正値を付加したデータを生成し、他のDAコンバータの中間データとして補正値を示すデータを生成し、前記補正値は、入力データの下位mビットデータに基づいて各DAコンバータごとに設定される0以上の数値であって、その総和が前記入力データの下位mビットデータが示す値に等しくなるように設定される数値である、ことを特徴とする。

【発明の効果】

【0011】

本発明によれば、アナログ素子による重み付け演算などを行なう必要がないため、より高精度でビット拡張ができる。

【図面の簡単な説明】

【0012】

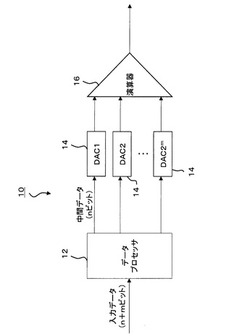

【図1】第一実施形態であるDA変換装置の概略構成図である。

【図2】第一実施形態における中間データ生成のパターンの一例を示す図である。

【図3】第一実施形態における中間データ生成のパターンの一例を示す図である。

【図4】第二実施形態であるDA変換装置の概略構成図である。

【図5】第二実施形態における中間データ生成のパターンの一例を示す図である。

【図6】第二実施形態における中間データ生成のパターンの一例を示す図である。

【図7】第三実施形態における中間データ生成のパターンの一例を示す図である。

【発明を実施するための形態】

【0013】

以下、本発明の実施形態において図面を参照して説明する。なお、以下の説明において、アルファベット“b”以降の数値は2進数表記の数値を、アルファベットd以降の数値は10進数表記の数値を、それぞれ示している。たとえば、「b101」とは2進数の「101」、10進数の「5」を意味しており、「d10」とは10進数の10、2進数の「1010」を意味している。

【0014】

図1は、本発明の実施形態であるDA変換装置10の概略構成図である。このDA変換装置10は、複数のDAコンバータ14と、当該DAコンバータ14に入力する中間データを生成するデータプロセッサ12、および、DAコンバータ14からの出力値を加算する演算器16を備えている。

【0015】

複数のDAコンバータ14は、いずれも同じ構成を有しており、nビットの分解能を有している。本実施形態では、このnビットのDAコンバータ14で、(n+m)ビットデータの取り扱いを可能にする(換言すればmビット拡張する)ために、nビットのDAコンバータ14を2m個設けている。演算器16は、この2m個のDAコンバータ14からの出力を加算し、2mで割る。なお、n≧mである。

【0016】

データプロセッサ12は、上位回路から出力された(n+m)ビットの入力データに基づいて、各DAコンバータ14に入力するnビットの中間データを生成し、出力するデータ生成手段として機能する。このデータプロセッサ12が予め規定されたパターンにしたがって中間データを生成し、各DAコンバータ14に入力することで、分解能が低いDAコンバータ14でも、高い分解能で入力信号をDA変換できる。以下、これについて詳説する。

【0017】

データプロセッサ12を介することなく、直接、(n+m)ビットの入力データを、nビットのDAコンバータ14に入力すると、DAコンバータ14は、上位nビットデータしか認識せず、下位mビットデータが示す値が抜け落ちることになる。例えば、3ビットのDAコンバータに、入力データとしてb0100を入力する場合、および、b0101を入力する場合を考える。この場合、入力データがb0100、b0101のいずれであったとしても、DAコンバータは、これらの入力データを同じb010の信号として取り扱うことになる。その結果、最終的に得られる出力も同じ値となる。つまり、入力段階には異なる値として取り扱われていたデータが、出力段階には同じデータになってしまい、結果として分解能が低下していた。

【0018】

この問題を解決するために、従来、(n+m)ビットの入力データのうち、上位nビットを第一のDAコンバータに、下位mビットを第二のDAコンバータに入力し、各DAコンバータからの出力を重み付け加算して、ビット拡張する技術があった。しかし、かかるビット拡張技術において、出力信号の精度を高く維持するためには、各DAコンバータからの出力の重み付け演算を高精度で行う必要があった。しかし、アナログ信号であるDAコンバータの出力信号を、精度よく重み付け演算することは非常に困難であった。

【0019】

本実施形態では、こうした問題を解決し、簡易な構成で精度よくビット拡張するために、DAコンバータ14を2m個設けている。そして、この複数のDAコンバータ14に入力する中間データとして、入力データの上位nビットデータに、補正値を付加したデータを生成し、各DAコンバータ14に入力している。ここで、補正値は、入力データの下位mビットデータに基づいて各DAコンバータ14ごとに設定される0以上の数値であって、その総和が入力データの下位mビットデータが示す値に等しくなるように設定される数値である。例えば、5ビットの入力データをb01010を、3ビット分解能をもつ4つのDAコンバータ(DAC1〜DAC4)で取り扱う場合を考える。この場合、DAC1〜DAC4の中間データは、入力データの上位3ビットデータb010に、補正値を付加した値となる。そして、DAC1〜DAC4の補正値をそれぞれe1〜e4とした場合、e1〜e4の総和は、入力データの下位mビットデータが示す値b10(d2)に等しくなるように(e1+e2+e3+e4=b10(d2)となるように)設定する。

【0020】

より具体的に説明すると、本実施形態では、補正値として0または1を用いており、入力データの下位mビットデータが示す値の個数のDAコンバータ14の補正値を1とし、他のDAコンバータ14の補正値を0として、中間データを生成する。例えば、5ビットの入力データを3ビット分解能を持つ4つのDAコンバータ、DAC1〜DAC4で取り扱う場合、すなわち、n=3、m=2の場合を考える。この場合において、入力データがb01010のとき(下位2ビットデータ(mビットデータ)がb10(d2)のとき)、DAC1〜DAC4の中間データのうち二つは、入力データの上位3ビットデータ(nビットデータ)のb010に、残りの二つは、上位3ビットデータb010に補正値b1を付加したb011とする。また、入力データがb01011のとき(下位2ビットデータがb11(d3)のとき)、DAC1〜DAC4の中間データのうち一つは、入力データの上位3ビットデータb010に、残りの三つは、上位3ビットデータb010に補正値b1を付加したb011とする。

【0021】

本実施形態では、この2m個のDAコンバータ14からの出力を演算器16で加算している。ここで、補正値の総和を入力データの下位mビットデータが示す値に等しくさせた場合、2m個のDAコンバータ14からの出力値の加算値Sは、S=[(上位nビットデータ)×2m+(下位mビットデータ)]となる。ここで、2m倍とは、すなわち、2進数の数値を、m個左シフトさせることを意味している。したがって、[(上位nビットデータ)×2m+(下位mビットデータ)]とは、すなわち、(n+m)ビットの入力データと同じデータが算出されることを意味している。そして、その結果、nビットのDAコンバータ14でも、n+mビットの分解能のデータを出力することが可能となる。また、本実施形態では、各DAコンバータ14からの出力(アナログ信号)に対して、誤差が生じやすい重み付けなどの処理を施していない。そのため、出力値の精度を高く維持することができる。なお、本実施形態では、この加算値Sを、適正なレベルにするために、2mで割っているが、この除算は、適宜、省略してもよい。

【0022】

次に、本実施形態のビット拡張の具体例を、具体的数値を挙げて説明する。まず、3ビットのDAコンバータ14で、4ビットの入力データを取り扱う場合を考える。この場合、n=3、m=1となり、DAコンバータ14は21=2個設けられることになる。

【0023】

図2は、この場合における中間データ生成のパターンを示す表である。この図2に示すように、本実施形態において、データプロセッサ12は、入力データの下位1ビット(mビット)がb0の場合は、DAC1の中間データおよびDAC2の中間データとして、入力データの上位3ビットデータ(nビットデータ)を、そのまま用いる。すなわち、補正値を0としている。

【0024】

一方、入力データの下位1ビットがb1の場合は、DAC1の中間データとして、入力データの上位3ビットデータに補正値b1を付加した値を用い(補正値はb1)、DAC2の中間データは、入力データの上位3ビットデータ(nビットデータ)を用いる(補正値は0)。

【0025】

かかる生成のパターンに従った場合に、最終的に演算器16から出力される値を考える。入力データがb0100の場合、(DAC1の中間データ、DAC2の中間データ)は、(b010,b010)となる。その結果、DAC1,DAC2からは、b010相当のアナログ信号が出力される。演算器16は、この二つの信号を加算する。その結果、演算器16からは(b010+b010)/2=b100/2=b0100相当の値が出力される。

【0026】

一方、入力データがb0101の場合、DAC1,DAC2の中間データは、(b010+b001,b010)=(b011,b010)となる。この場合、演算器16からは、(b011+b010)/2=b101/2=b0101相当の値が出力される。

【0027】

つまり、データプロセッサ12が介在しない従来技術では、同じ値に変換されていた入力データb0100とb0101が、本実施形態によれば、適切に階調付けられた異なる値のアナログデータとして出力されることになる。

【0028】

次に、3ビットのDAコンバータ14で、5ビットの入力データを取り扱う場合を考える。この場合、n=3、m=2となり、DAコンバータ14は22=4個設けられることになる。図3は、この場合における中間データ生成のパターンを示す表である。この図3に示すように、本実施形態において、データプロセッサ12は、入力データの下位2ビット(mビット)がb00の場合は、DAC1〜DAC4すべての中間データとして、入力データの上位3ビットデータ(nビットデータ)を、そのまま用いる(すなわち補正値は0)。また、下位2ビットがb01の場合はDAC1の中間データとして、上位3ビットデータにb01を付加した値を用い(補正値は1)、他のDAC2〜DAC4の中間データとして、入力データの上位3ビットデータをそのまま用いる(補正値は0)。さらに、下位2ビットがb10の場合はDAC1、DAC2の中間データとして、上位3ビットデータにb01を付加した値を、下位2ビットがb11の場合はDAC1〜DAC3の中間データとして、上位3ビットデータにb01を付加した値を、用いる。

【0029】

この生成パターンに従った場合に、演算器16から出力される値を考える。入力データがb01000の場合には、DAC1〜DAC4の中間データは、(b010,b010,b010,b010)となり、演算器16から出力される信号は、(b010+b010+b010+b010)/4=b1000/4=b01000となる。

【0030】

また、同様に、入力データがb01001の場合、中間データは(b011,b010,b010,b010)となり、演算器16から出力される信号は、(b011+b010+b010+b010)/4=b1001/4=b01001となる。

【0031】

また、入力データがb01010の場合、中間データは(b011,b011,b010,b010)となり、演算器16から出力される信号は、(b011+b010+b010+b010)/4=b1001/4=b01010となる。

【0032】

さらに、入力データがb01011の場合、中間データは(b011,b011,b011,b010)となり、演算器16から出力される信号は、(b011+b010+b010+b010)/4=b1011/4=b01011となる。

【0033】

ここで、b01000〜01011は、上位nビットデータをそのままDAコンバータ14に入力していた従来技術では、同じ値、b010として出力されるデータである。本実施形態によれば、かかるデータも、適切に階調付けられた互いに異なる値として出力することが可能である。そして、これにより、出力データの分解能をより高めることができる。

【0034】

なお、上述の例では、中間データを生成するために、補正値として、0または1のみを用いている。しかし、各DAコンバータ14に付加される補正値の総和が、下位mビットデータが示す値になるのであれば、補正値は、他の値であってもよい。

【0035】

例えば、入力データがb01011の場合(下位mビットデータがb11(d3)の場合)において、DAC1に適用される補正値をb11(d3)、他のDACに適用される補正値を0としてもよい。この場合、DAC1〜DAC4の中間データは、(b010+b011,b010,b010,b010)=(b101,b010,b010,b010)となる。この場合でも、最終的に演算器16から出力される信号は、(b101+b010+b010+b010)/4=b1011/4=b01011となる。

【0036】

また、別の形態として、入力データがb01011の場合に、DAC1に適用される補正値をb10(d2)、DAC2に適用される補正値をb01(d1)、他のDACに適用される補正値を0としてもよい。この場合、DAC1〜DAC4の中間データは、(b010+b010,b010+b001,b010,b010)=(b100,b011,b010,b010)となる。この場合でも、最終的に演算器16から出力される信号は、(b100+b011+b010+b010)/4=b1011/4=b01011となる。

【0037】

つまり、上位nビットデータの他に付加される補正値の総和が、下位mビットデータが示す値と等しくなるように中間データを生成すれば、図2、図3で説明した場合と同様に、出力データの分解能を高めることができる。

【0038】

次に、第二実施形態について図4を参照して説明する。図4は、第二実施形態におけるDA変換装置10の概略構成図である。このDA変換装置10では、2m個のDAコンバータ14に加えて、さらに、別の1個のDAコンバータ20を設けている点で上述の実施形態と異なる。以下では、2m個のDAコンバータと追加の1個のDAコンバータとを区別する場合には、前者を「第一DAコンバータ14」、後者を「第二DAコンバータ20」と呼ぶ。

【0039】

第二DAコンバータ20は、入力データの上位nビットデータが最大値を取った場合の問題を解決するために設けられている。すなわち、上述した第一実施形態では、第一DAコンバータ14には、上位nビットデータ、あるいは、上位nビットデータに補正値b1が付加された値が入力される。ここで、上位nビットデータが最大値をとった場合には、新たに補正値b1を付加することはできない。

【0040】

例えば、n=3、m=1において、入力データがb1111の場合を考える。この場合、下位mビットデータはb1であるため、図2に示した中間データ生成のパターンに従えば、DAC1には、上位3ビットデータb111にb1を付加した値を入力する必要がある。しかし、入力データがb1111の場合、上位3ビットデータb111は、既に最大値であるため、さらに、補正値b1を付加することはできない。その結果、入力データがb1111の場合、DAC1,DAC2の中間データは、いずれも、b111となる。これは、入力データがb1110の場合と同じである。つまり、第一実施形態では、入力データがb1111、b1110のいずれであっても、得られる出力値は同じになる。同様に、n=3、m=2の場合は、入力データがb11101、b11110、b11111のいずれであっても、得られる出力値は同じになる。つまり、第一実施形態では、最大値近傍において、データ分解能が低下するという問題があった。

【0041】

本実施形態では、この問題を解決するために、2m+1個目のDAコンバータ、すなわち、第二DAコンバータ20を追加している。第一DAコンバータ14の中間データとして入力データの上位nビットデータに補正値を付加したデータを、第二DAコンバータ20の中間データとして0データに補正値を付加したデータを、生成している。補正値は、その総和が、下位mビットデータが示す値と等しくなるような数値である。本実施形態では、入力データの上位nビットデータが最大値の場合、第一DAコンバータ14の補正値は0、第二DAコンバータ20の補正値は入力データの下位mビットデータとしている。また、入力データの上位nビットデータが最大値未満の場合、下位mビットデータが示す値の個数の第一DAコンバータ14の補正値を1とし、他のDAコンバータ14,20の補正値を0として、中間データを生成している。

【0042】

図5は、本実施形態において、n=3、m=1の場合における中間データ生成のパターンを示す図である。このテーブルに示すように、入力データの上位3ビットが最大値b111未満の場合は、図3の場合と同じパターンで、中間データが生成される。すなわち、下位1ビットがb1の場合には、上位nビットデータに補正値b1を付加したデータをDAC1の中間データとして生成する。その他の場合は、入力データの上位nビットデータを、DAC1,2の中間データとして生成する。また、第二DAコンバータ20(DAC3)の中間データは、入力データの値に関わらず、b000とする。換言すれば、入力データの上位3ビットが最大値未満の場合、第二DAコンバータの中間データとして、0データに、補正値0が付加された値が生成される。

【0043】

一方、入力データの上位3ビットが最大値b111となった場合を考える。この場合には、上位nビットデータを第一DAコンバータ14(DAC1,DAC2)の中間データとして(補正値は0)、下位1ビットの値を第二DAコンバータ20(DAC3)の中間データとして生成する。すなわち、入力データがb1110の場合はb000を、入力データがb1111の場合はb001を、DAC3の中間データとする。

【0044】

かかる構成とした場合において演算器16から出力される値を考える。入力データがb1110の場合は、DAC1〜DAC3の中間データは、(b111,b111,b000)となる。この場合、演算器16からは、(b111+b111+b000)/2=b1110相当の信号が出力されることになる。

【0045】

また、入力データがb1111の場合は、DAC1〜DAC3の中間データは、(b111,b111,b001)となる。この場合、演算器16からは、(b111+b111+b001)/2=b1111相当の信号が出力されることになる。

【0046】

つまり、第一実施形態では同じ値に変換されるb1110、b1111を、本実施形態によれば、適切に階調付けられた異なる値に変換できる。そして、これにより、最大値近傍においても、高い分解能を得ることができる。

【0047】

同様に、n=3,m=2の場合についても説明する。図6は、n=3、m=2の場合における中間データ生成のパターンを示す図である。この図6に示すように、入力データの上位3ビットがb111未満の場合は、上述の実施形態と同じルールで、中間データが生成される。すなわち、入力データの下位2ビットがb01の場合はDAC1に、下位2ビットがb10の場合はDAC1,DAC2に、下位2ビットがb11の場合はDAC1〜DAC3に、(上位nビットデータ+b001)のデータが入力され、他のDACには、上位nビットデータが入力される。

【0048】

一方、上位3ビットが最大値b111となった場合には、第一DAコンバータ14(DAC1〜DAC4)には上位3ビットデータ(nビットデータ)が、第二DAコンバータ20(DAC5)には下位2ビットデータ(mビットデータ)が入力される。すなわち、DAC5の中間データは、入力データがb11100の場合はb000、b11101の場合はb001、b11110の場合はb010、b11111の場合はb011となる。

【0049】

かかる構成とした場合において演算器16から出力される値を考える。入力データがb11100の場合は、DAC1〜DAC4にはb111が、DAC5にはb000が入力される。演算器16からは、(b111+b111+b111+b111+b000)/4=(b11100+b00000)/4=b11100相当の信号が出力されることになる。

【0050】

入力データがb11101の場合は、DAC1〜DAC4にはb111が、DAC5にはb001が入力される。演算器16からは、(b11100+b001)/4=b11101相当の信号が出力されることになる。

【0051】

入力データがb11110の場合は、DAC1〜DAC4にはb111が、DAC5にはb010が入力される。演算器16からは、(b11100+b010)/4=b11110相当の信号が出力されることになる。

【0052】

入力データがb11111の場合は、DAC1〜DAC4にはb111が、DAC5にはb011が入力される。演算器16からは、(b11100+b011)/4=b11111相当の信号が出力されることになる。

【0053】

つまり、第二DAコンバータ20を設けた本実施形態によれば、上述の実施形態では同じ値に変換されるb11100〜b11111を、適切に階調付けられた異なる値に変換することができる。

【0054】

なお、上述の例では、第一DAコンバータ14の中間データ生成に用いられる補正値として0または1のみを用いている。しかし、各DAコンバータ14に付加される補正値の総和が、下位mビットデータが示す値になるのであれば、補正値は、他の値であってもよい。したがって、例えば、n=3,m=2、入力データがb01011の場合において、DAC1に適用される補正値をb11(d3)、他のDACに適用される補正値を0としてもよい。また、別の形態として、DAC1に適用される補正値をb10(d2)、DAC2に適用される補正値をb01(d1)、他のDACに適用される補正値を0のようにしてもよい。

【0055】

また、本実施形態では、第二DAコンバータ20を1個のみとしているが、複数設けてもよい。この場合であっても、全てのDAコンバータに適用される補正値の総和が、下位mビットデータが示す値に等しくなるように、補正値を設定すればよい。

【0056】

次に、第三実施形態について、図7を参照して説明する。第三実施形態における物理的構成は、第二実施形態と同様である。すなわち、本実施形態では、2m個の第一DAコンバータ14と1個の第二DAコンバータ20を有しており、演算器16は、これら2m+1個のDAコンバータ14からの出力を加算し、2mで割る。

【0057】

本実施形態では、第一、第二DAコンバータ14,20に入力する中間データの生成パターンを、第二実施形態と異ならせている。これについて図7を参照して説明する。

【0058】

図7は、本実施形態においてn=3,m=2の場合における中間データ生成のパターンを示す図である。この図7に示すとおり、本実施形態では、入力データの上位nビットデータの値に関わらず、常に、第一DAコンバータ14の中間データとして上位nビットデータを、第二DAコンバータ20の中間データとして下位mビットデータを、用いている。

【0059】

例えば、入力データがb01000の場合、第一DAコンバータ14(DAC1〜DAC4)にはb010が、第二DAコンバータ20(DAC5)にはb000が、中間データとして入力される。また、入力データがb01001の場合、第一DAコンバータ14(DAC1〜DAC4)にはb010が、第二DAコンバータ20(DAC5)にはb001が、中間データとして入力される。

【0060】

かかる構成とした場合において演算器16から出力される値を考える。入力データがb01000の場合は、DAC1〜DAC5の中間データは、(b010,b010,b010,b010,b000)であり、演算器16からは(b010×4+b000)/4=(b01000+b000)/4=b01000が出力される。

【0061】

また、入力データがb01001の場合は、DAC1〜DAC5の中間データは、(b010,b010,b010,b010,b001)であり、演算器16からは(b01000+b001)/4=b01001が出力される。

【0062】

また、入力データがb01010の場合は、DAC1〜DAC5の中間データは、(b010,b010,b010,b010,b010)であり、演算器16からは(b01000+b010)/4=b01010が出力される。

【0063】

また、入力データがb01011の場合は、DAC1〜DAC5の中間データは、(b010,b010,b010,b010,b011)であり、演算器16からは(b01000+b010)/4=b01011が出力される。

【0064】

つまり、本実施形態でも、DAコンバータ14のビット数以上のデータが取り扱い可能となる。また、アナログ信号の重み付け処理などが不要であるため、より高精度でビット拡張ができる。

【0065】

なお、本実施形態においても、第二DAコンバータ20を複数設けてもよい。第二DAコンバータ20を複数設けた場合には、この複数の第二DAコンバータ20の中間データの総和が、下位mビットデータが示す値に等しくなるように設定する。

【0066】

また、これまで説明した構成は、いずれも一例であり、DAコンバータが2m個以上設けられており、これらDAコンバータに適用される補正値の総和が前記入力データの下位mビットデータが示す値に等しくなるように設定されており、2m個のDAコンバータの中間データが(上位nビットデータ+補正値)、他のDAコンバータの中間データが(補正値)となるのであれば、他の構成でもよい。

【0067】

そして、こうした構成を採用すれば、アナログ素子による重み付け演算などが行なう必要がないため、より高精度でビット拡張ができる。

【符号の説明】

【0068】

10 DA変換装置、12,20 DAコンバータ、16 演算器。

【技術分野】

【0001】

本発明は、デジタルデータをアナログデータに変換するDA変換装置に関し、特に複数のDAコンバータから構成されるDA変換装置に関する。

【背景技術】

【0002】

従来より、複数のDAコンバータを組み合わせて、DAコンバータ単体がもつ分解能以上の分解能をもったDA変換装置を構築するビット拡張の技術が知られている。たとえば、特許文献1には、(m+n)ビットのデジタルデータのうち上位mビットが入力される第1のDAコンバータと、前記でジタルデータのうち下位nビットが入力される第2のDAコンバータと、を設けるとともに、各DAコンバータからの出力を、重み付け加算するビット拡張技術が開示されている。かかる技術によれば、nビットのDAコンバータで、n+mビットのデータを取り扱うことができる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平7−162311号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、こうした従来のビット拡張技術では、抵抗器などのアナログ素子を用いて各DAコンバータからの出力値(アナログ信号)を重み付け処理する必要がある。かかる、アナログ素子を用いて、アナログ信号の重み付け処理を精度よく行なうことは非常に困難であった。そして、結果として、DA変換装置の変換精度が低くなるという問題があった。

【0005】

そこで、本発明では、より高精度でビット拡張ができるDA変換装置を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明のDA変換装置は、2m個のnビットの第一DAコンバータと、上流側から入力されるn+mビットの入力データに基づいて、前記第一DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、前記第一DAコンバータからの出力を加算する演算器と、を備え、前記データ生成手段は、第一DAコンバータの中間データとして入力データの上位nビットデータに補正値を付加したデータを生成し、前記補正値は、入力データの下位mビットデータに基づいて各DAコンバータごとに設定される0以上の数値であって、その総和が前記入力データの下位mビットデータが示す値に等しくなるように設定される数値である、ことを特徴とする。

【0007】

他の本発明であるDA変換装置は、2m個のnビットの第一DAコンバータと、1個のnビットの第二DAコンバータと、上流側から入力されるn+mビットの入力データに基づいて、前記第一、第二DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、前記第一、第二DAコンバータからの出力を加算する演算器と、を備え、前記データ生成手段は、第一DAコンバータの中間データとして入力データの上位nビットデータに補正値を付加したデータを、第二DAコンバータの中間データとして0に補正値を付加したデータを、それぞれ生成し、前記補正値は、入力データの下位mビットデータに基づいて各DAコンバータごとに設定される0以上の数値であって、その総和が前記入力データの下位mビットデータが示す値に等しくなるように設定される数値である、ことを特徴とする。この場合、前記データ生成手段は、入力データの上位nビットデータが最大値の場合、前記第一DAコンバータの補正値を0とし、第二DAコンバータの補正値を入力データの下位mビットデータが示す値として、中間データを生成する、ことが望ましい。

【0008】

また、上述のDA変換装置においては、前記データ生成手段は、入力データの上位nビットデータが最大値未満の場合、前記下位mビットデータが示す値の個数の第一DAコンバータの補正値を1とし、他のDAコンバータの補正値を0として、中間データを生成する、ことが望ましい。

【0009】

他の本発明であるDA変換装置は、2m個のnビットの第一DAコンバータと、1個のnビットの第二DAコンバータと、上流側から入力されるn+mビットの入力データに基づいて、前記第一、第二DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、前記第一、第二DAコンバータからの出力を加算する演算器と、を備え、前記データ生成手段は、第一DAコンバータの中間データとして入力データの上位nビットデータを、第二DAコンバータの中間データとして入力データの下位mビットデータを、それぞれ生成する、ことを特徴とする。

【0010】

他の本発明であるDA変換装置は、2m個以上のnビットのDAコンバータと、上流側から入力されるn+mビットの入力データに基づいて、前記DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、前記DAコンバータからの出力を加算する演算器と、を備え、前記データ生成手段は、2m個のDAコンバータの中間データとして前記入力データの上位nビットデータに補正値を付加したデータを生成し、他のDAコンバータの中間データとして補正値を示すデータを生成し、前記補正値は、入力データの下位mビットデータに基づいて各DAコンバータごとに設定される0以上の数値であって、その総和が前記入力データの下位mビットデータが示す値に等しくなるように設定される数値である、ことを特徴とする。

【発明の効果】

【0011】

本発明によれば、アナログ素子による重み付け演算などを行なう必要がないため、より高精度でビット拡張ができる。

【図面の簡単な説明】

【0012】

【図1】第一実施形態であるDA変換装置の概略構成図である。

【図2】第一実施形態における中間データ生成のパターンの一例を示す図である。

【図3】第一実施形態における中間データ生成のパターンの一例を示す図である。

【図4】第二実施形態であるDA変換装置の概略構成図である。

【図5】第二実施形態における中間データ生成のパターンの一例を示す図である。

【図6】第二実施形態における中間データ生成のパターンの一例を示す図である。

【図7】第三実施形態における中間データ生成のパターンの一例を示す図である。

【発明を実施するための形態】

【0013】

以下、本発明の実施形態において図面を参照して説明する。なお、以下の説明において、アルファベット“b”以降の数値は2進数表記の数値を、アルファベットd以降の数値は10進数表記の数値を、それぞれ示している。たとえば、「b101」とは2進数の「101」、10進数の「5」を意味しており、「d10」とは10進数の10、2進数の「1010」を意味している。

【0014】

図1は、本発明の実施形態であるDA変換装置10の概略構成図である。このDA変換装置10は、複数のDAコンバータ14と、当該DAコンバータ14に入力する中間データを生成するデータプロセッサ12、および、DAコンバータ14からの出力値を加算する演算器16を備えている。

【0015】

複数のDAコンバータ14は、いずれも同じ構成を有しており、nビットの分解能を有している。本実施形態では、このnビットのDAコンバータ14で、(n+m)ビットデータの取り扱いを可能にする(換言すればmビット拡張する)ために、nビットのDAコンバータ14を2m個設けている。演算器16は、この2m個のDAコンバータ14からの出力を加算し、2mで割る。なお、n≧mである。

【0016】

データプロセッサ12は、上位回路から出力された(n+m)ビットの入力データに基づいて、各DAコンバータ14に入力するnビットの中間データを生成し、出力するデータ生成手段として機能する。このデータプロセッサ12が予め規定されたパターンにしたがって中間データを生成し、各DAコンバータ14に入力することで、分解能が低いDAコンバータ14でも、高い分解能で入力信号をDA変換できる。以下、これについて詳説する。

【0017】

データプロセッサ12を介することなく、直接、(n+m)ビットの入力データを、nビットのDAコンバータ14に入力すると、DAコンバータ14は、上位nビットデータしか認識せず、下位mビットデータが示す値が抜け落ちることになる。例えば、3ビットのDAコンバータに、入力データとしてb0100を入力する場合、および、b0101を入力する場合を考える。この場合、入力データがb0100、b0101のいずれであったとしても、DAコンバータは、これらの入力データを同じb010の信号として取り扱うことになる。その結果、最終的に得られる出力も同じ値となる。つまり、入力段階には異なる値として取り扱われていたデータが、出力段階には同じデータになってしまい、結果として分解能が低下していた。

【0018】

この問題を解決するために、従来、(n+m)ビットの入力データのうち、上位nビットを第一のDAコンバータに、下位mビットを第二のDAコンバータに入力し、各DAコンバータからの出力を重み付け加算して、ビット拡張する技術があった。しかし、かかるビット拡張技術において、出力信号の精度を高く維持するためには、各DAコンバータからの出力の重み付け演算を高精度で行う必要があった。しかし、アナログ信号であるDAコンバータの出力信号を、精度よく重み付け演算することは非常に困難であった。

【0019】

本実施形態では、こうした問題を解決し、簡易な構成で精度よくビット拡張するために、DAコンバータ14を2m個設けている。そして、この複数のDAコンバータ14に入力する中間データとして、入力データの上位nビットデータに、補正値を付加したデータを生成し、各DAコンバータ14に入力している。ここで、補正値は、入力データの下位mビットデータに基づいて各DAコンバータ14ごとに設定される0以上の数値であって、その総和が入力データの下位mビットデータが示す値に等しくなるように設定される数値である。例えば、5ビットの入力データをb01010を、3ビット分解能をもつ4つのDAコンバータ(DAC1〜DAC4)で取り扱う場合を考える。この場合、DAC1〜DAC4の中間データは、入力データの上位3ビットデータb010に、補正値を付加した値となる。そして、DAC1〜DAC4の補正値をそれぞれe1〜e4とした場合、e1〜e4の総和は、入力データの下位mビットデータが示す値b10(d2)に等しくなるように(e1+e2+e3+e4=b10(d2)となるように)設定する。

【0020】

より具体的に説明すると、本実施形態では、補正値として0または1を用いており、入力データの下位mビットデータが示す値の個数のDAコンバータ14の補正値を1とし、他のDAコンバータ14の補正値を0として、中間データを生成する。例えば、5ビットの入力データを3ビット分解能を持つ4つのDAコンバータ、DAC1〜DAC4で取り扱う場合、すなわち、n=3、m=2の場合を考える。この場合において、入力データがb01010のとき(下位2ビットデータ(mビットデータ)がb10(d2)のとき)、DAC1〜DAC4の中間データのうち二つは、入力データの上位3ビットデータ(nビットデータ)のb010に、残りの二つは、上位3ビットデータb010に補正値b1を付加したb011とする。また、入力データがb01011のとき(下位2ビットデータがb11(d3)のとき)、DAC1〜DAC4の中間データのうち一つは、入力データの上位3ビットデータb010に、残りの三つは、上位3ビットデータb010に補正値b1を付加したb011とする。

【0021】

本実施形態では、この2m個のDAコンバータ14からの出力を演算器16で加算している。ここで、補正値の総和を入力データの下位mビットデータが示す値に等しくさせた場合、2m個のDAコンバータ14からの出力値の加算値Sは、S=[(上位nビットデータ)×2m+(下位mビットデータ)]となる。ここで、2m倍とは、すなわち、2進数の数値を、m個左シフトさせることを意味している。したがって、[(上位nビットデータ)×2m+(下位mビットデータ)]とは、すなわち、(n+m)ビットの入力データと同じデータが算出されることを意味している。そして、その結果、nビットのDAコンバータ14でも、n+mビットの分解能のデータを出力することが可能となる。また、本実施形態では、各DAコンバータ14からの出力(アナログ信号)に対して、誤差が生じやすい重み付けなどの処理を施していない。そのため、出力値の精度を高く維持することができる。なお、本実施形態では、この加算値Sを、適正なレベルにするために、2mで割っているが、この除算は、適宜、省略してもよい。

【0022】

次に、本実施形態のビット拡張の具体例を、具体的数値を挙げて説明する。まず、3ビットのDAコンバータ14で、4ビットの入力データを取り扱う場合を考える。この場合、n=3、m=1となり、DAコンバータ14は21=2個設けられることになる。

【0023】

図2は、この場合における中間データ生成のパターンを示す表である。この図2に示すように、本実施形態において、データプロセッサ12は、入力データの下位1ビット(mビット)がb0の場合は、DAC1の中間データおよびDAC2の中間データとして、入力データの上位3ビットデータ(nビットデータ)を、そのまま用いる。すなわち、補正値を0としている。

【0024】

一方、入力データの下位1ビットがb1の場合は、DAC1の中間データとして、入力データの上位3ビットデータに補正値b1を付加した値を用い(補正値はb1)、DAC2の中間データは、入力データの上位3ビットデータ(nビットデータ)を用いる(補正値は0)。

【0025】

かかる生成のパターンに従った場合に、最終的に演算器16から出力される値を考える。入力データがb0100の場合、(DAC1の中間データ、DAC2の中間データ)は、(b010,b010)となる。その結果、DAC1,DAC2からは、b010相当のアナログ信号が出力される。演算器16は、この二つの信号を加算する。その結果、演算器16からは(b010+b010)/2=b100/2=b0100相当の値が出力される。

【0026】

一方、入力データがb0101の場合、DAC1,DAC2の中間データは、(b010+b001,b010)=(b011,b010)となる。この場合、演算器16からは、(b011+b010)/2=b101/2=b0101相当の値が出力される。

【0027】

つまり、データプロセッサ12が介在しない従来技術では、同じ値に変換されていた入力データb0100とb0101が、本実施形態によれば、適切に階調付けられた異なる値のアナログデータとして出力されることになる。

【0028】

次に、3ビットのDAコンバータ14で、5ビットの入力データを取り扱う場合を考える。この場合、n=3、m=2となり、DAコンバータ14は22=4個設けられることになる。図3は、この場合における中間データ生成のパターンを示す表である。この図3に示すように、本実施形態において、データプロセッサ12は、入力データの下位2ビット(mビット)がb00の場合は、DAC1〜DAC4すべての中間データとして、入力データの上位3ビットデータ(nビットデータ)を、そのまま用いる(すなわち補正値は0)。また、下位2ビットがb01の場合はDAC1の中間データとして、上位3ビットデータにb01を付加した値を用い(補正値は1)、他のDAC2〜DAC4の中間データとして、入力データの上位3ビットデータをそのまま用いる(補正値は0)。さらに、下位2ビットがb10の場合はDAC1、DAC2の中間データとして、上位3ビットデータにb01を付加した値を、下位2ビットがb11の場合はDAC1〜DAC3の中間データとして、上位3ビットデータにb01を付加した値を、用いる。

【0029】

この生成パターンに従った場合に、演算器16から出力される値を考える。入力データがb01000の場合には、DAC1〜DAC4の中間データは、(b010,b010,b010,b010)となり、演算器16から出力される信号は、(b010+b010+b010+b010)/4=b1000/4=b01000となる。

【0030】

また、同様に、入力データがb01001の場合、中間データは(b011,b010,b010,b010)となり、演算器16から出力される信号は、(b011+b010+b010+b010)/4=b1001/4=b01001となる。

【0031】

また、入力データがb01010の場合、中間データは(b011,b011,b010,b010)となり、演算器16から出力される信号は、(b011+b010+b010+b010)/4=b1001/4=b01010となる。

【0032】

さらに、入力データがb01011の場合、中間データは(b011,b011,b011,b010)となり、演算器16から出力される信号は、(b011+b010+b010+b010)/4=b1011/4=b01011となる。

【0033】

ここで、b01000〜01011は、上位nビットデータをそのままDAコンバータ14に入力していた従来技術では、同じ値、b010として出力されるデータである。本実施形態によれば、かかるデータも、適切に階調付けられた互いに異なる値として出力することが可能である。そして、これにより、出力データの分解能をより高めることができる。

【0034】

なお、上述の例では、中間データを生成するために、補正値として、0または1のみを用いている。しかし、各DAコンバータ14に付加される補正値の総和が、下位mビットデータが示す値になるのであれば、補正値は、他の値であってもよい。

【0035】

例えば、入力データがb01011の場合(下位mビットデータがb11(d3)の場合)において、DAC1に適用される補正値をb11(d3)、他のDACに適用される補正値を0としてもよい。この場合、DAC1〜DAC4の中間データは、(b010+b011,b010,b010,b010)=(b101,b010,b010,b010)となる。この場合でも、最終的に演算器16から出力される信号は、(b101+b010+b010+b010)/4=b1011/4=b01011となる。

【0036】

また、別の形態として、入力データがb01011の場合に、DAC1に適用される補正値をb10(d2)、DAC2に適用される補正値をb01(d1)、他のDACに適用される補正値を0としてもよい。この場合、DAC1〜DAC4の中間データは、(b010+b010,b010+b001,b010,b010)=(b100,b011,b010,b010)となる。この場合でも、最終的に演算器16から出力される信号は、(b100+b011+b010+b010)/4=b1011/4=b01011となる。

【0037】

つまり、上位nビットデータの他に付加される補正値の総和が、下位mビットデータが示す値と等しくなるように中間データを生成すれば、図2、図3で説明した場合と同様に、出力データの分解能を高めることができる。

【0038】

次に、第二実施形態について図4を参照して説明する。図4は、第二実施形態におけるDA変換装置10の概略構成図である。このDA変換装置10では、2m個のDAコンバータ14に加えて、さらに、別の1個のDAコンバータ20を設けている点で上述の実施形態と異なる。以下では、2m個のDAコンバータと追加の1個のDAコンバータとを区別する場合には、前者を「第一DAコンバータ14」、後者を「第二DAコンバータ20」と呼ぶ。

【0039】

第二DAコンバータ20は、入力データの上位nビットデータが最大値を取った場合の問題を解決するために設けられている。すなわち、上述した第一実施形態では、第一DAコンバータ14には、上位nビットデータ、あるいは、上位nビットデータに補正値b1が付加された値が入力される。ここで、上位nビットデータが最大値をとった場合には、新たに補正値b1を付加することはできない。

【0040】

例えば、n=3、m=1において、入力データがb1111の場合を考える。この場合、下位mビットデータはb1であるため、図2に示した中間データ生成のパターンに従えば、DAC1には、上位3ビットデータb111にb1を付加した値を入力する必要がある。しかし、入力データがb1111の場合、上位3ビットデータb111は、既に最大値であるため、さらに、補正値b1を付加することはできない。その結果、入力データがb1111の場合、DAC1,DAC2の中間データは、いずれも、b111となる。これは、入力データがb1110の場合と同じである。つまり、第一実施形態では、入力データがb1111、b1110のいずれであっても、得られる出力値は同じになる。同様に、n=3、m=2の場合は、入力データがb11101、b11110、b11111のいずれであっても、得られる出力値は同じになる。つまり、第一実施形態では、最大値近傍において、データ分解能が低下するという問題があった。

【0041】

本実施形態では、この問題を解決するために、2m+1個目のDAコンバータ、すなわち、第二DAコンバータ20を追加している。第一DAコンバータ14の中間データとして入力データの上位nビットデータに補正値を付加したデータを、第二DAコンバータ20の中間データとして0データに補正値を付加したデータを、生成している。補正値は、その総和が、下位mビットデータが示す値と等しくなるような数値である。本実施形態では、入力データの上位nビットデータが最大値の場合、第一DAコンバータ14の補正値は0、第二DAコンバータ20の補正値は入力データの下位mビットデータとしている。また、入力データの上位nビットデータが最大値未満の場合、下位mビットデータが示す値の個数の第一DAコンバータ14の補正値を1とし、他のDAコンバータ14,20の補正値を0として、中間データを生成している。

【0042】

図5は、本実施形態において、n=3、m=1の場合における中間データ生成のパターンを示す図である。このテーブルに示すように、入力データの上位3ビットが最大値b111未満の場合は、図3の場合と同じパターンで、中間データが生成される。すなわち、下位1ビットがb1の場合には、上位nビットデータに補正値b1を付加したデータをDAC1の中間データとして生成する。その他の場合は、入力データの上位nビットデータを、DAC1,2の中間データとして生成する。また、第二DAコンバータ20(DAC3)の中間データは、入力データの値に関わらず、b000とする。換言すれば、入力データの上位3ビットが最大値未満の場合、第二DAコンバータの中間データとして、0データに、補正値0が付加された値が生成される。

【0043】

一方、入力データの上位3ビットが最大値b111となった場合を考える。この場合には、上位nビットデータを第一DAコンバータ14(DAC1,DAC2)の中間データとして(補正値は0)、下位1ビットの値を第二DAコンバータ20(DAC3)の中間データとして生成する。すなわち、入力データがb1110の場合はb000を、入力データがb1111の場合はb001を、DAC3の中間データとする。

【0044】

かかる構成とした場合において演算器16から出力される値を考える。入力データがb1110の場合は、DAC1〜DAC3の中間データは、(b111,b111,b000)となる。この場合、演算器16からは、(b111+b111+b000)/2=b1110相当の信号が出力されることになる。

【0045】

また、入力データがb1111の場合は、DAC1〜DAC3の中間データは、(b111,b111,b001)となる。この場合、演算器16からは、(b111+b111+b001)/2=b1111相当の信号が出力されることになる。

【0046】

つまり、第一実施形態では同じ値に変換されるb1110、b1111を、本実施形態によれば、適切に階調付けられた異なる値に変換できる。そして、これにより、最大値近傍においても、高い分解能を得ることができる。

【0047】

同様に、n=3,m=2の場合についても説明する。図6は、n=3、m=2の場合における中間データ生成のパターンを示す図である。この図6に示すように、入力データの上位3ビットがb111未満の場合は、上述の実施形態と同じルールで、中間データが生成される。すなわち、入力データの下位2ビットがb01の場合はDAC1に、下位2ビットがb10の場合はDAC1,DAC2に、下位2ビットがb11の場合はDAC1〜DAC3に、(上位nビットデータ+b001)のデータが入力され、他のDACには、上位nビットデータが入力される。

【0048】

一方、上位3ビットが最大値b111となった場合には、第一DAコンバータ14(DAC1〜DAC4)には上位3ビットデータ(nビットデータ)が、第二DAコンバータ20(DAC5)には下位2ビットデータ(mビットデータ)が入力される。すなわち、DAC5の中間データは、入力データがb11100の場合はb000、b11101の場合はb001、b11110の場合はb010、b11111の場合はb011となる。

【0049】

かかる構成とした場合において演算器16から出力される値を考える。入力データがb11100の場合は、DAC1〜DAC4にはb111が、DAC5にはb000が入力される。演算器16からは、(b111+b111+b111+b111+b000)/4=(b11100+b00000)/4=b11100相当の信号が出力されることになる。

【0050】

入力データがb11101の場合は、DAC1〜DAC4にはb111が、DAC5にはb001が入力される。演算器16からは、(b11100+b001)/4=b11101相当の信号が出力されることになる。

【0051】

入力データがb11110の場合は、DAC1〜DAC4にはb111が、DAC5にはb010が入力される。演算器16からは、(b11100+b010)/4=b11110相当の信号が出力されることになる。

【0052】

入力データがb11111の場合は、DAC1〜DAC4にはb111が、DAC5にはb011が入力される。演算器16からは、(b11100+b011)/4=b11111相当の信号が出力されることになる。

【0053】

つまり、第二DAコンバータ20を設けた本実施形態によれば、上述の実施形態では同じ値に変換されるb11100〜b11111を、適切に階調付けられた異なる値に変換することができる。

【0054】

なお、上述の例では、第一DAコンバータ14の中間データ生成に用いられる補正値として0または1のみを用いている。しかし、各DAコンバータ14に付加される補正値の総和が、下位mビットデータが示す値になるのであれば、補正値は、他の値であってもよい。したがって、例えば、n=3,m=2、入力データがb01011の場合において、DAC1に適用される補正値をb11(d3)、他のDACに適用される補正値を0としてもよい。また、別の形態として、DAC1に適用される補正値をb10(d2)、DAC2に適用される補正値をb01(d1)、他のDACに適用される補正値を0のようにしてもよい。

【0055】

また、本実施形態では、第二DAコンバータ20を1個のみとしているが、複数設けてもよい。この場合であっても、全てのDAコンバータに適用される補正値の総和が、下位mビットデータが示す値に等しくなるように、補正値を設定すればよい。

【0056】

次に、第三実施形態について、図7を参照して説明する。第三実施形態における物理的構成は、第二実施形態と同様である。すなわち、本実施形態では、2m個の第一DAコンバータ14と1個の第二DAコンバータ20を有しており、演算器16は、これら2m+1個のDAコンバータ14からの出力を加算し、2mで割る。

【0057】

本実施形態では、第一、第二DAコンバータ14,20に入力する中間データの生成パターンを、第二実施形態と異ならせている。これについて図7を参照して説明する。

【0058】

図7は、本実施形態においてn=3,m=2の場合における中間データ生成のパターンを示す図である。この図7に示すとおり、本実施形態では、入力データの上位nビットデータの値に関わらず、常に、第一DAコンバータ14の中間データとして上位nビットデータを、第二DAコンバータ20の中間データとして下位mビットデータを、用いている。

【0059】

例えば、入力データがb01000の場合、第一DAコンバータ14(DAC1〜DAC4)にはb010が、第二DAコンバータ20(DAC5)にはb000が、中間データとして入力される。また、入力データがb01001の場合、第一DAコンバータ14(DAC1〜DAC4)にはb010が、第二DAコンバータ20(DAC5)にはb001が、中間データとして入力される。

【0060】

かかる構成とした場合において演算器16から出力される値を考える。入力データがb01000の場合は、DAC1〜DAC5の中間データは、(b010,b010,b010,b010,b000)であり、演算器16からは(b010×4+b000)/4=(b01000+b000)/4=b01000が出力される。

【0061】

また、入力データがb01001の場合は、DAC1〜DAC5の中間データは、(b010,b010,b010,b010,b001)であり、演算器16からは(b01000+b001)/4=b01001が出力される。

【0062】

また、入力データがb01010の場合は、DAC1〜DAC5の中間データは、(b010,b010,b010,b010,b010)であり、演算器16からは(b01000+b010)/4=b01010が出力される。

【0063】

また、入力データがb01011の場合は、DAC1〜DAC5の中間データは、(b010,b010,b010,b010,b011)であり、演算器16からは(b01000+b010)/4=b01011が出力される。

【0064】

つまり、本実施形態でも、DAコンバータ14のビット数以上のデータが取り扱い可能となる。また、アナログ信号の重み付け処理などが不要であるため、より高精度でビット拡張ができる。

【0065】

なお、本実施形態においても、第二DAコンバータ20を複数設けてもよい。第二DAコンバータ20を複数設けた場合には、この複数の第二DAコンバータ20の中間データの総和が、下位mビットデータが示す値に等しくなるように設定する。

【0066】

また、これまで説明した構成は、いずれも一例であり、DAコンバータが2m個以上設けられており、これらDAコンバータに適用される補正値の総和が前記入力データの下位mビットデータが示す値に等しくなるように設定されており、2m個のDAコンバータの中間データが(上位nビットデータ+補正値)、他のDAコンバータの中間データが(補正値)となるのであれば、他の構成でもよい。

【0067】

そして、こうした構成を採用すれば、アナログ素子による重み付け演算などが行なう必要がないため、より高精度でビット拡張ができる。

【符号の説明】

【0068】

10 DA変換装置、12,20 DAコンバータ、16 演算器。

【特許請求の範囲】

【請求項1】

2m個のnビットの第一DAコンバータと、

上流側から入力されるn+mビットの入力データに基づいて、前記第一DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、

前記第一DAコンバータからの出力を加算する演算器と、

を備え、

前記データ生成手段は、第一DAコンバータの中間データとして入力データの上位nビットデータに補正値を付加したデータを生成し、

前記補正値は、入力データの下位mビットデータに基づいて各DAコンバータごとに設定される0以上の数値であって、その総和が前記入力データの下位mビットデータが示す値に等しくなるように設定される数値である、

ことを特徴とするDA変換装置。

【請求項2】

2m個のnビットの第一DAコンバータと、

1個のnビットの第二DAコンバータと、

上流側から入力されるn+mビットの入力データに基づいて、前記第一、第二DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、

前記第一、第二DAコンバータからの出力を加算する演算器と、

を備え、

前記データ生成手段は、第一DAコンバータの中間データとして入力データの上位nビットデータに補正値を付加したデータを、第二DAコンバータの中間データとして0に補正値を付加したデータを、それぞれ生成し、

前記補正値は、入力データの下位mビットデータに基づいて各DAコンバータごとに設定される0以上の数値であって、その総和が前記入力データの下位mビットデータが示す値に等しくなるように設定される数値である、

ことを特徴とするDA変換装置。

【請求項3】

請求項2に記載のDA変換装置であって、

前記データ生成手段は、入力データの上位nビットデータが最大値の場合、前記第一DAコンバータの補正値を0とし、第二DAコンバータの補正値を入力データの下位mビットデータが示す値として、中間データを生成する、

ことを特徴とするDA変換装置。

【請求項4】

請求項1から3のいずれか1項に記載のDA変換装置であって、

前記データ生成手段は、入力データの上位nビットデータが最大値未満の場合、前記下位mビットデータが示す値の個数の第一DAコンバータの補正値を1とし、他のDAコンバータの補正値を0として、中間データを生成する、ことを特徴とするDA変換装置。

【請求項5】

2m個のnビットの第一DAコンバータと、

1個のnビットの第二DAコンバータと、

上流側から入力されるn+mビットの入力データに基づいて、前記第一、第二DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、

前記第一、第二DAコンバータからの出力を加算する演算器と、

を備え、

前記データ生成手段は、第一DAコンバータの中間データとして入力データの上位nビットデータを、第二DAコンバータの中間データとして入力データの下位mビットデータを、それぞれ生成する、

ことを特徴とするDA変換装置。

【請求項6】

2m個以上のnビットのDAコンバータと、

上流側から入力されるn+mビットの入力データに基づいて、前記DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、

前記DAコンバータからの出力を加算する演算器と、

を備え、

前記データ生成手段は、2m個のDAコンバータの中間データとして前記入力データの上位nビットデータに補正値を付加したデータを生成し、他のDAコンバータの中間データとして補正値を示すデータを生成し、

前記補正値は、入力データの下位mビットデータに基づいて各DAコンバータごとに設定される0以上の数値であって、その総和が前記入力データの下位mビットデータが示す値に等しくなるように設定される数値である、

ことを特徴とするDA変換装置。

【請求項1】

2m個のnビットの第一DAコンバータと、

上流側から入力されるn+mビットの入力データに基づいて、前記第一DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、

前記第一DAコンバータからの出力を加算する演算器と、

を備え、

前記データ生成手段は、第一DAコンバータの中間データとして入力データの上位nビットデータに補正値を付加したデータを生成し、

前記補正値は、入力データの下位mビットデータに基づいて各DAコンバータごとに設定される0以上の数値であって、その総和が前記入力データの下位mビットデータが示す値に等しくなるように設定される数値である、

ことを特徴とするDA変換装置。

【請求項2】

2m個のnビットの第一DAコンバータと、

1個のnビットの第二DAコンバータと、

上流側から入力されるn+mビットの入力データに基づいて、前記第一、第二DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、

前記第一、第二DAコンバータからの出力を加算する演算器と、

を備え、

前記データ生成手段は、第一DAコンバータの中間データとして入力データの上位nビットデータに補正値を付加したデータを、第二DAコンバータの中間データとして0に補正値を付加したデータを、それぞれ生成し、

前記補正値は、入力データの下位mビットデータに基づいて各DAコンバータごとに設定される0以上の数値であって、その総和が前記入力データの下位mビットデータが示す値に等しくなるように設定される数値である、

ことを特徴とするDA変換装置。

【請求項3】

請求項2に記載のDA変換装置であって、

前記データ生成手段は、入力データの上位nビットデータが最大値の場合、前記第一DAコンバータの補正値を0とし、第二DAコンバータの補正値を入力データの下位mビットデータが示す値として、中間データを生成する、

ことを特徴とするDA変換装置。

【請求項4】

請求項1から3のいずれか1項に記載のDA変換装置であって、

前記データ生成手段は、入力データの上位nビットデータが最大値未満の場合、前記下位mビットデータが示す値の個数の第一DAコンバータの補正値を1とし、他のDAコンバータの補正値を0として、中間データを生成する、ことを特徴とするDA変換装置。

【請求項5】

2m個のnビットの第一DAコンバータと、

1個のnビットの第二DAコンバータと、

上流側から入力されるn+mビットの入力データに基づいて、前記第一、第二DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、

前記第一、第二DAコンバータからの出力を加算する演算器と、

を備え、

前記データ生成手段は、第一DAコンバータの中間データとして入力データの上位nビットデータを、第二DAコンバータの中間データとして入力データの下位mビットデータを、それぞれ生成する、

ことを特徴とするDA変換装置。

【請求項6】

2m個以上のnビットのDAコンバータと、

上流側から入力されるn+mビットの入力データに基づいて、前記DAコンバータに入力するnビットの中間データを生成するデータ生成手段と、

前記DAコンバータからの出力を加算する演算器と、

を備え、

前記データ生成手段は、2m個のDAコンバータの中間データとして前記入力データの上位nビットデータに補正値を付加したデータを生成し、他のDAコンバータの中間データとして補正値を示すデータを生成し、

前記補正値は、入力データの下位mビットデータに基づいて各DAコンバータごとに設定される0以上の数値であって、その総和が前記入力データの下位mビットデータが示す値に等しくなるように設定される数値である、

ことを特徴とするDA変換装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−5330(P2013−5330A)

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願番号】特願2011−136359(P2011−136359)

【出願日】平成23年6月20日(2011.6.20)

【出願人】(000003676)ティアック株式会社 (339)

【Fターム(参考)】

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願日】平成23年6月20日(2011.6.20)

【出願人】(000003676)ティアック株式会社 (339)

【Fターム(参考)】

[ Back to top ]