DC−DCコンバータ回路

【課題】従来よりもスイッチング素子の導通損を低減でき、これにより電力変換効率を向上させることができるDC−DCコンバータ回路を提供する。

【解決手段】DC−DCコンバータ回路10は、第1半導体スイッチS1及び第1ダイオードD1を含む第1スイッチング素子SW1と、第2半導体スイッチS2及び第2ダイオードD2を含む第2スイッチング素子SW2と、第1及び第2ダイオードD1,D2のアノードとの間に接続されたインダクタLと、第1及び第2ダイオードD1,D2のカソード側に互いに逆向きになるように設けられた第3スイッチング素子SW3及び第4スイッチング素子SW4とを備え、第1ダイオードD1のカソード側と第2ダイオードD2のアノード側との間に第1電圧源E1が接続され、第1ダイオードD1のアノード側と第2ダイオードD2のカソード側との間に第2電圧源E2が接続される。

【解決手段】DC−DCコンバータ回路10は、第1半導体スイッチS1及び第1ダイオードD1を含む第1スイッチング素子SW1と、第2半導体スイッチS2及び第2ダイオードD2を含む第2スイッチング素子SW2と、第1及び第2ダイオードD1,D2のアノードとの間に接続されたインダクタLと、第1及び第2ダイオードD1,D2のカソード側に互いに逆向きになるように設けられた第3スイッチング素子SW3及び第4スイッチング素子SW4とを備え、第1ダイオードD1のカソード側と第2ダイオードD2のアノード側との間に第1電圧源E1が接続され、第1ダイオードD1のアノード側と第2ダイオードD2のカソード側との間に第2電圧源E2が接続される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、DC−DCコンバータ回路に関するものであり、特に、双方向昇降圧形DC−DCコンバータ回路における導通損低減に関するものである。

【背景技術】

【0002】

DC−DCコンバータ回路は、例えば、第1及び第2直流電圧源(以下、単に第1及び第2電圧源という)の間に接続され、第1及び第2電圧源の出力電圧に基づき、第1電圧源から第2電圧源に電力を供給したり、或いは、第2電圧源から第1電圧源に電力を供給したりすることが可能な双方向形のスイッチング回路として用いられる。

【0003】

例えば、DC−DCコンバータ回路は、作業車両などの電動車両に用いられることがある。電動車両は、一般的に、バッテリやキャパシタ等の蓄電装置からの直流電力をインバータ回路等の電力変換回路にて交流電力に変換して得られた交流電力でモータ等の車両駆動電動機を作動させるようになっている。そして、DC−DCコンバータ回路は、第1電圧源として作用する蓄電装置と、インバータ回路等の電力変換回路が接続された第2電圧源との間に設けられ、力行モード時には蓄電装置から電力変換回路に電力を供給する一方、回生モード時には電力変換回路から蓄電装置に電力を供給することが可能な構成とされている。

【0004】

従来のDC−DCコンバータ回路として、例えば、下記特許文献1に記載のチョッパ回路(特許文献1の図4参照)がある。

【0005】

図9は、従来のDC−DCコンバータ回路の一例を示す回路図である。図9に示すDC−DCコンバータ回路は、第1から第4スイッチング素子121〜124と、インダクタ125とを備えている。

【0006】

第1から第4スイッチング素子121〜124は、それぞれ、一方向にのみ電流を流すことができる第1から第4半導体スイッチ121a〜124aと、第1から第4半導体スイッチ121a〜124aに対して電流を流すことができる方向を逆にしてそれぞれ並列接続された第1から第4ダイオード121b〜124bとからなっている。

【0007】

インダクタ125は、一端が第1スイッチング素子121に含まれる第1ダイオード121bのアノード側及び第2スイッチング素子122に含まれる第2ダイオード122bのカソード側の双方に接続され、かつ、他端が第3スイッチング素子123に含まれる第3ダイオード123bのアノード側及び第4スイッチング素子124に含まれる第2ダイオード124bのカソード側の双方に接続されている。

【0008】

そして、図9に示すDC−DCコンバータ回路は、第1スイッチング素子121に含まれる第1ダイオード121bのカソード側と第2スイッチング素子122に含まれる第2ダイオード122bのアノード側との間に第1電圧源110が接続され、第3スイッチング素子123に含まれる第3ダイオード123bのカソード側と第4スイッチング素子124に含まれる第4ダイオード124bのアノード側との間に第2電圧源120が接続されるようになっている。

【0009】

このような従来のDC−DCコンバータ回路において、各スイッチング素子121〜124のオン状態及びオフ状態を示す動作モードとして、力行モードで動作する次の第1モードから第3モードと、回生モードで動作する次の第4モードから第6モードとを例示できる。

【0010】

図10は、図9に示すDC−DCコンバータ回路において力行モードで動作している状態を示す図である。図10(a)は、第1モードを示しており、図10(b)は、第2モードを示しており、図10(c)は、第3モードを示している。

【0011】

例えば、力行モードにおいては、図10(a)に示すように、第1モードは、第1電圧源110から第1スイッチング素子121、インダクタ125及び第4スイッチング素子124を経て第1電圧源110に戻る電流経路R1aを形成するモードとされている。図10(b)に示すように、第2モードは、第1電圧源110から第1スイッチング素子121、インダクタ125、第3スイッチング素子123及び第2電圧源120を経て第1電圧源110に戻る電流経路R2aを形成するモードとされている。図10(c)に示すように、第3モードは、第2電圧源120から第2スイッチング素子122、インダクタ125及び第3スイッチング素子123を経て第2電圧源120に戻る電流経路R3aを形成するモードとされている。

【0012】

そして、力行モードを実行するときは、第1電圧源110の出力電圧V1と第2電圧源120の出力電圧V2との大小関係に応じて、第1モードと第2モードと第3モードとのうち少なくとも二つのモードを短い周期(例えば10kHz〜100kHz程度のうち何れかの周期)で切り換える各種切り換え動作が実行される。

【0013】

また、図11は、図9に示すDC−DCコンバータ回路において回生モードで動作している状態を示す図である。図11(a)は、第4モードを示しており、図11(b)は、第5モードを示しており、図11(c)は、第6モードを示している。

【0014】

例えば、回生モードにおいては、図11(a)に示すように、第4モードは、第1電圧源110から第4スイッチング素子124、インダクタ125及び第1スイッチング素子121を経て第1電圧源110に戻る電流経路R4aを形成するモードとされている。図11(b)に示すように、第5モードは、第1電圧源110から第2電圧源120、第3スイッチング素子123、インダクタ125及び第1スイッチング素子121を経て第1電圧源110に戻る電流経路R5aを形成するモードとされている。図11(c)に示すように、第6モードは、第2電圧源120から第3スイッチング素子123、インダクタ125及び第2スイッチング素子122を経て第2電圧源120に戻る電流経路R6aを形成するモードとされている。

【0015】

そして、回生モードを実行するときは、第1電圧源110の出力電圧V1と第2電圧源120の出力電圧V2との大小関係に応じて、第4モードと第5モードと第6モードとのうち少なくとも二つのモードを短い周期(例えば10kHz〜100kHz程度のうち何れかの周期)で切り換える各種切り換え動作モードが実行される。

【先行技術文献】

【特許文献】

【0016】

【特許文献1】特開2000−295715号公報

【発明の概要】

【発明が解決しようとする課題】

【0017】

ところで、DC−DCコンバータ回路においては、各種切り換え動作モードにおいて電流が通過するスイッチング素子の数が多くなれば、それだけ導通損が大きくなり、それに伴って電力変換効率が低下する。

【0018】

図9に示す従来のDC−DCコンバータ回路では、スイッチング素子として、例えば、第1モード(図10(a)参照)及び第4モード(図11(a)参照)で第1スイッチング素子121及び第4スイッチング素子124に、第2モード(図10(b)参照)及び第5モード(図11(b)参照)で第1スイッチング素子121及び第3スイッチング素子123に、また、第3モード(図10(c)参照)及び第6モード(図11(c)参照)で第2スイッチング素子122及び第3スイッチング素子123にそれぞれ電流が通過することになる。つまり、第1モードから第6モードの何れのモードにおいても(力行モード及び回生モードの何れにおいても)、少なくとも二つのスイッチング素子に対して電流が通過するため、それだけ導通損が大きくなり、それに伴って電力変換効率が低下する。

【0019】

そこで、本発明は、従来よりもスイッチング素子の導通損を低減でき、これにより電力変換効率を向上させることができるDC−DCコンバータ回路を提供することを目的とする。

【課題を解決するための手段】

【0020】

本発明は、前記課題を解決するために、一方向に電流をオン,オフ制御可能な第1半導体スイッチ、及び、前記第1半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第1半導体スイッチに並列接続された第1ダイオードを含む第1スイッチング素子と、一方向に電流をオン,オフ制御可能な第2半導体スイッチ、及び、前記第2半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第2半導体スイッチに並列接続された第2ダイオードを含む第2スイッチング素子と、一端が前記第1スイッチング素子に含まれる前記第1ダイオードのアノード側に接続され、かつ、他端が前記第2スイッチング素子に含まれる前記第2ダイオードのアノード側に接続されたインダクタと、前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側から前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側への一方向に電流を流すことができるように設けられた第3スイッチング素子と、前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側から前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側への一方向に電流を流すことができるように設けられた第4スイッチング素子とを備え、前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側と前記第2スイッチング素子に含まれる前記第2ダイオードのアノード側との間に、前記第1スイッチング素子側が陽極になるように第1電圧源が接続され、前記第1スイッチング素子に含まれる前記第1ダイオードのアノード側と前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側との間に、前記第2スイッチング素子側が陽極になるように第2電圧源が接続されることを特徴とするDC−DCコンバータ回路を提供する。

【0021】

本発明に係るDC−DCコンバータ回路によれば、前記第1電圧源と前記第2電圧源との間で双方向に出力電圧の昇降圧を行うことができる。また、前記第1電圧源と前記第2電圧源との間で双方向に電力を供給することができる。さらに、少なくとも一つのスイッチング素子(従来に比べて半分のスイッチング素子)に対して電流を通過させることができ、それだけ導通損を低減でき、これにより電力変換効率を向上させることができる。なお、この作用効果については、以下の実施の形態で詳しく説明する。

【0022】

ところで、インバータ回路等の電力変換回路に利用されているモジュールとして、二つの逆導通形の半導体素子を直列接続して一体的に形成したモジュール(いわゆる2in1モジュール)が市販されている。本発明に係るDC−DCコンバータ回路おいて、電力容量等の設計仕様によっては、この2in1モジュールを用いることが好ましい場合がある。

【0023】

かかる観点から、本発明に係るDC−DCコンバータ回路において、2in1モジュールを適用できる回路を構成することが可能な態様として、次の(a)及び(b)の態様を例示できる。すなわち、

(a)の態様として、前記第3スイッチング素子は、一方向に電流をオン,オフ制御可能な第3半導体スイッチと、第3ダイオードと、第5ダイオードとを含んでおり、前記第4スイッチング素子は、一方向に電流をオン,オフ制御可能な第4半導体スイッチと、第4ダイオードと、第6ダイオードとを含んでおり、前記第3ダイオードは、前記第3半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第3半導体スイッチに並列接続されており、前記第4ダイオードは、前記第4半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第4半導体スイッチに並列接続されており、前記第5ダイオードは、前記第3半導体スイッチに並列接続された前記第3ダイオードのカソード側と前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側との間に、前記第3ダイオードと逆方向に電流を流すことができるように接続されており、前記第6ダイオードは、前記第4半導体スイッチに並列接続された前記第4ダイオードのカソード側と前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側との間に、前記第4ダイオードと逆方向に電流を流すことができるように接続されており、前記第3半導体スイッチに並列接続された前記第3ダイオードのアノード側が、前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側に接続されており、前記第4半導体スイッチに並列接続された前記第4ダイオードのアノード側が、前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側に接続されている態様を例示できる。

【0024】

(b)の態様として、前記第3スイッチング素子は、一方向に電流をオン,オフ制御可能な第3半導体スイッチと、第3ダイオードとを含んでおり、前記第4スイッチング素子は、一方向に電流をオン,オフ制御可能な第4半導体スイッチと、第4ダイオードとを含んでおり、前記第3ダイオードは、前記第4半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第4半導体スイッチに並列接続されており、前記第4ダイオードは、前記第3半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第3半導体スイッチに並列接続されており、前記第4半導体スイッチに並列接続された前記第3ダイオードのアノード側が、前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側に接続されており、前記第3半導体スイッチに並列接続された前記第4ダイオードのアノード側が、前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側に接続されており、前記第3ダイオード及び前記第4ダイオードのカソード側同士が接続されている態様を例示できる。

【0025】

なお、前記半導体スイッチとしては、IGBT(Insulated Gate Bipolar Transistor)、MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)及びGTO(Gate Turn-Off thyristor)等の半導体スイッチを例示できる。前記逆導通形の半導体素子としては、IGBT、GTO等の半導体スイッチに対して電流を流すことができる方向を逆にしてダイオードを並列接続した半導体素子、MOSFET等のように半導体の構造的に寄生ダイオード(または、ボディダイオード)が存在する半導体素子を例示でき、例えば、逆導通形のIGBT素子、逆導通形のMOSFET素子、逆導通形のGTO素子を挙げることができる。

【0026】

また、過電流による前記第1から第4までのスイッチング素子の破壊を防止する観点からは、本発明に係るDC−DCコンバータ回路において、次の(c)から(f)までの態様にすることが好ましい。すなわち、

(c)の態様として、前記第1スイッチング素子と前記第2スイッチング素子との双方が同時にオン状態とならないように制御する手段を備える態様を例示できる。

【0027】

(d)の態様として、前記第1スイッチング素子と前記第4スイッチング素子との双方が同時にオン状態とならないように制御する手段を備える態様を例示できる。

【0028】

(e)の態様として、前記第2スイッチング素子と前記第3スイッチング素子との双方が同時にオン状態とならないように制御する手段を備える態様を例示できる。

【0029】

(f)の態様として、前記(c)から前記(e)までの態様のうち少なくとも二つを組み合わせた態様を例示できる。

【発明の効果】

【0030】

以上説明したように、本発明によると、従来よりもスイッチング素子の導通損を低減でき、これにより電力変換効率を向上させることができるDC−DCコンバータ回路を提供することができる。

【図面の簡単な説明】

【0031】

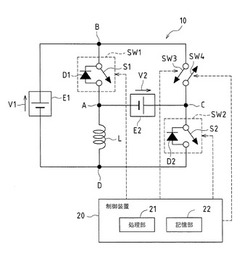

【図1】本発明の実施の形態に係るDC−DCコンバータ回路を示す回路図である。

【図2】図1に示すDC−DCコンバータにおいて力行モードで動作している状態を示す図であって、図(a)は、第1モードを示す図であり、図(b)は、第2モードを示す図であり、図(c)は、第3モードを示す図である。

【図3】図1に示すDC−DCコンバータにおいて回生モードで動作している状態を示す図であって、図(a)は、第4モードを示す図であり、図(b)は、第5モードを示す図であり、図(c)は、第6モードを示す図である。

【図4】第1から第4スイッチング素子に用いることができる半導体スイッチの例を示す図であって、図(a)は、第1及び第2スイッチング素子として逆導通形のIGBT素子を用いたい例を示す図であり、図(b)は、第3スイッチング素子と第4スイッチング素子との接続構成を逆阻止形のIGBTのみで構成した例を示す図であり、図(c)は、第3スイッチング素子と第4スイッチング素子との接続構成を逆導通形のIGBTとダイオードとで構成した例を示す図であり、図(d)は、第3スイッチング素子と第4スイッチング素子との接続構成を逆導通形のIGBTで構成した例を示す図である。

【図5】第1から第4スイッチング素子に用いることができる2in1モジュールの例を示す図である。

【図6】2in1モジュールを適用できる回路を構成することが可能な第1実施例の回路図である。

【図7】2in1モジュールを適用できる回路を構成することが可能な第2実施例の回路図である。

【図8】第1から第4スイッチング素子に対するスイッチング動作の第1から第3制御例により禁止する第7から第9電流経路を示す図であって、図(a)は、第7電流経路を示す図であり、図(b)は、第8電流経路を示す図であり、図(c)は、第9電流経路を示す図である。

【図9】従来のDC−DCコンバータ回路の一例を示す回路図である。

【図10】図9に示すDC−DCコンバータ回路において力行モードで動作している状態を示す図であって、図(a)は、第1モードを示す図であり、図(b)は、第2モードを示す図であり、図(c)は、第3モードを示す図である。

【図11】図9に示すDC−DCコンバータ回路において回生モードで動作している状態を示す図であって、図(a)は、第4モードを示す図であり、図(b)は、第5モードを示す図であり、図(c)は、第6モードを示す図である。

【発明を実施するための形態】

【0032】

以下、本発明の実施の形態について添付図面を参照しつつ説明する。なお、以下の実施の形態は、本発明を具体化した例であって、本発明の技術的範囲を限定する性格のものではない。

【0033】

図1は、本発明の実施の形態に係るDC−DCコンバータ回路10を示す回路図である。

【0034】

図1に示すDC−DCコンバータ回路10は、第1スイッチング素子SW1と、第2スイッチング素子SW2と、インダクタLと、第3スイッチング素子SW3と、第4スイッチング素子SW4とを備えている。

【0035】

第1スイッチング素子SW1は、第1半導体スイッチS1と第1ダイオードD1とからなっている。第1半導体スイッチS1は、一方向にのみ電流をオン,オフ制御可能な半導体デバイスとされている。第1ダイオードD1は、第1半導体スイッチS1が電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように第1半導体スイッチS1に並列接続されている。

【0036】

第2スイッチング素子SW2は、第2半導体スイッチS2と第2ダイオードD2とからなっている。第2半導体スイッチS2は、一方向にのみ電流をオン,オフ制御可能な半導体デバイスとされている。第2ダイオードD2は、第2半導体スイッチS2が電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように第2半導体スイッチS2に並列接続されている。

【0037】

インダクタLは、一端が第1スイッチング素子SW1に含まれる第1ダイオードD1のアノード側(接続点A参照)に接続され、かつ、他端が第2スイッチング素子SW2に含まれる第2ダイオードD2のアノード側(接続点D参照)に接続されている。

【0038】

第3スイッチング素子SW3は、第1スイッチング素子SW1に含まれる第1ダイオードD1のカソード側から第2スイッチング素子SW2に含まれる第2ダイオードD2のカソード側への一方向にのみ電流を流すことができるように構成されている。

【0039】

第4スイッチング素子SW4は、第2スイッチング素子SW2に含まれる第2ダイオードD2のカソード側から第1スイッチング素子SW1に含まれる第1ダイオードD1のカソード側への一方向にのみ電流を流すことができるように構成されている。

【0040】

そして、DC−DCコンバータ回路10は、第1スイッチング素子SW1に含まれる第1ダイオードD1のカソード側(接続点B参照)と第2スイッチング素子SW2に含まれる第2ダイオードD2のアノード側(接続点D参照)との間に、第1スイッチング素子SW1側が陽極になるように第1電圧源E1が接続されるようになっている。

【0041】

また、DC−DCコンバータ回路10は、第1スイッチング素子SW1に含まれる第1ダイオードD1のアノード側(接続点A参照)と第2スイッチング素子SW2に含まれる第2ダイオードD2のカソード側(接続点C参照)との間に、第2スイッチング素子SW2側が陽極になるように第2電圧源E2が接続されるようになっている。

【0042】

なお、DC−DCコンバータ回路10が作業車両に適用される場合には、例えば、第1及び第2電圧源E1,E2は、バッテリやキャパシタ等の蓄電装置とすることができる。また、第1及び第2電圧源E1,E2には、モータ等の車両駆動電動機を作動させるインバータ回路等の電力変換回路を接続することができる。

【0043】

本実施の形態に係るDC−DCコンバータ回路10は、さらに制御装置20を備えている。制御装置20は、CPU(Central Processing Unit)等の処理部21と、記憶部22とを備えている。記憶部22は、ROM(Read Only Memory)やRAM(Random Access Memory)等の記憶メモリを含み、各種制御プログラムや必要な関数およびテーブルや、各種のデータを記憶するようになっている。

【0044】

制御装置20は、DC−DCコンバータ回路10の第1から第4スイッチング素子SW1〜SW4のスイッチング動作を制御するように構成されている。

【0045】

本実施の形態に係るDC−DCコンバータ回路10において、第1から第4スイッチング素子SW1〜SW4のオン状態及びオフ状態を示す動作モードとして、力行モードで動作する次の第1モードから第3モードと、回生モードで動作する次の第4モードから第6モードとを例示できる。

【0046】

図2は、図1に示すDC−DCコンバータ回路10において力行モードで動作している状態を示す図である。図2(a)は、第1モードを示しており、図2(b)は、第2モードを示しており、図2(c)は、第3モードを示している。

【0047】

また、図3は、図1に示すDC−DCコンバータ回路10において回生モードで動作している状態を示す図である。図3(a)は、第4モードを示しており、図3(b)は、第5モードを示しており、図3(c)は、第6モードを示している。

【0048】

力行モードにおいては、例えば、第1モードは、図2(a)に示すように、第1スイッチング素子SW1がオン状態となり、それ以外の第2、第3及び第4スイッチング素子SW2,SW3,SW4がオフ状態となって、第1電圧源E1から第1スイッチング素子SW1及びインダクタLを経て第1電圧源E1に戻る第1電流経路R1を形成するモードとすることができる。

【0049】

第2モードは、図2(b)に示すように、第3スイッチング素子SW3がオン状態となり、それ以外の第1、第2及び第4スイッチング素子SW1,SW2,SW4がオフ状態となって、第1電圧源E1から第3スイッチング素子SW3、第2電圧源E2及びインダクタLを経て第1電圧源E1に戻る第2電流経路R2を形成するモードとすることができる。

【0050】

第3モードは、図2(c)に示すように、第1から第4スイッチング素子SW1〜SW4が全てオフ状態となって、第2電圧源E2からインダクタL及び第2スイッチング素子SW2を経て第2電圧源E2に戻る第3電流経路R3を形成するモードとすることができる。

【0051】

そして、力行モードを実行するときは、第1電圧源E1の出力電圧V1と第2電圧源E2の出力電圧V2との大小関係に応じて、第1モードと第2モードと第3モードとのうち少なくとも二つのモードを短い周期(例えば10kHz〜100kHz程度の何れかの周期)で切り換える各種切り換え動作を実行することができる。

【0052】

具体的には、第1電圧源E1の出力電圧V1が第2電圧源E2の出力電圧V2よりも大きい場合には、例えば、第2モードと第3モードとを切り換える切り換え動作を実行することができ、第1電圧源E1の出力電圧V1が第2電圧源E2の出力電圧V2よりも小さい場合には、例えば、第1モードと第2モードとを切り換える切り換え動作を実行することができる。第1電圧源E1の出力電圧V1と第2電圧源E2の出力電圧V2とが等しい場合には、例えば、第1モードと第3モードとを切り換える切り換え動作を実行するか、或いは、第2モードのみを実行することができる。なお、第1電圧源E1の出力電圧V1と第2電圧源E2の出力電圧V2とがほぼ等しい場合(電圧V1と電圧V2との差の絶対値が所定範囲内にある場合)に、第1モードと第3モードとを切り換える切り換え動作を実行するか、或いは、第2モードのみを実行してもよい。

【0053】

また、回生モードにおいては、例えば、第4モードは、図3(a)に示すように、第1から第4スイッチング素子SW1〜SW4が全てオフ状態となって、第1電圧源E1からインダクタL及び第1スイッチング素子SW1を経て第1電圧源E1に戻る第4電流経路R4を形成するモードとすることができる。

【0054】

第5モードは、図3(b)に示すように、第4スイッチング素子SW4がオン状態となり、それ以外の第1、第2及び第3スイッチング素子SW1,SW2,SW3がオフ状態となって、第2電圧源E2から第4スイッチング素子SW4、第1電圧源E1及びインダクタLを経て第2電圧源E2に戻る第5電流経路R5を形成するモードとすることができる。

【0055】

第6モードは、図3(c)に示すように、第2スイッチング素子SW2がオン状態となり、それ以外の第1、第3及び第4スイッチング素子SW1,SW3,SW4がオフ状態となって、第2電圧源E2から第2スイッチング素子SW2及びインダクタLを経て第2電圧源E2に戻る第6電流経路R6を形成するモードとすることができる。

【0056】

そして、回生モードを実行するときは、第1電圧源E1の出力電圧V1と第2電圧源E2の出力電圧V2との大小関係に応じて、第4モードと第5モードと第6モードとのうち少なくとも二つのモードを短い周期(例えば10kHz〜100kHz程度の何れかの周期)で切り換える各種切り換え動作を実行することができる。

【0057】

具体的には、第1電圧源E1の出力電圧V1が第2電圧源E2の出力電圧V2よりも大きい場合には、例えば、第5モードと第6モードとを切り換える切り換え動作を実行することができ、第1電圧源E1の出力電圧V1が第2電圧源E2の出力電圧V2よりも小さい場合には、例えば、第4モードと第5モードとを切り換える切り換え動作を実行することができる。第1電圧源E1の出力電圧V1と第2電圧源E2の出力電圧V2とが等しい場合には、例えば、第4モードと第6モードとを切り換える切り換え動作を実行するか、或いは、第5モードのみを実行することができる。なお、第1電圧源E1の出力電圧V1と第2電圧源E2の出力電圧V2とがほぼ等しい場合(電圧V1と電圧V2との差の絶対値が所定範囲内にある場合)に、第4モードと第6モードとを切り換える切り換え動作を実行するか、或いは、第5モードのみを実行してもよい。

【0058】

なお、第1電圧源E1の出力電圧V1、第2電圧源E2の出力電圧V2は、図示を省略した電圧計にて測定することができる。

【0059】

以上説明したように、本発明の実施の形態に係るDC−DCコンバータ10では、第1電圧源E1と第2電圧源E2との間で双方向に出力電圧V1,V2の昇降圧を行うことができる。また、第1電圧源E1と第2電圧源E2との間で双方向に電力を供給することができる。さらに、スイッチング素子として、例えば、第1モード(図2(a)参照)及び第4モード(図3(a)参照)で第1スイッチング素子SW1に、第2モード(図2(b)参照)で第3スイッチング素子SW3に、第5モード(図3(b)参照)で第4スイッチング素子SW4に、また、第3モード(図2(c)参照)及び第6モード(図3(c)参照)で第2スイッチング素子SW2にそれぞれ電流が通過するだけで済む。つまり、第1モードから第6モードの何れのモードにおいても(力行モード及び回生モードの何れにおいても)、少なくとも一つのスイッチング素子(従来に比べて半分のスイッチング素子)に対して電流を通過させることができ、それだけ導通損を低減でき、これにより電力変換効率を向上させることができる。

【0060】

特に、各モードの切り換え周期が短い程、第1から第4スイッチング素子SW1〜SW4のスイッチングロスが大きくなるため、それだけ前記した作用効果を有効なものとすることができる。

【0061】

なお、第1から第4スイッチング素子SW1〜SW4に用いることができる半導体スイッチとして、例えば、IGBT、MOSFET、GTOを用いることができる。ここで、MOSFETは200V程度以下、IGBTは2kV程度以下のシステムで使用されることが多い。また、第1から第4スイッチング素子SW1〜SW4としてMOSFETを用いる場合には、逆並列接続されているダイオードに電流が流れている時に当該MOSFETをオンとする同期整流により当該MOSFETでの導通損失を低減することが可能である。

【0062】

図4は、第1から第4スイッチング素子SW1〜SW4に用いることができる半導体スイッチの例を示す図である。図4(a)は、第1及び第2スイッチング素子SW1,SW2として逆導通形のIGBT素子を用いたい例(図中右側)を示している。図4(b)は、第3スイッチング素子SW3と第4スイッチング素子SW4との接続構成を逆阻止形のIGBTのみで構成した例(図中右側)を示している。図4(c)は、第3スイッチング素子SW3と第4スイッチング素子SW4との接続構成を逆導通形のIGBTとダイオードとで構成した例(図中右側)を示している。図4(d)は、第3スイッチング素子SW3と第4スイッチング素子SW4との接続構成を逆導通形のIGBTで構成した例(図中右側)を示している。なお、図4(c)及び図4(d)に示す接続例については、以下の第1実施例及び第2実施例で説明する。

【0063】

図4に示す例では、半導体スイッチをIGBTとしているが、半導体スイッチをMOSFETとしてもよいし、GTOとしてもよい。

【0064】

また、第1から第4スイッチング素子SW1〜SW4は、例えば、二つの逆導通形の半導体素子を直列接続して一体的に形成した2in1モジュールを用いることができる。

【0065】

図5は、第1から第4スイッチング素子SW1〜SW4に用いることができる2in1モジュールの例を示す図である。図5に示す例では、2in1モジュールMを逆導通形のIGBT素子で構成している。但し、それに限定されるものではなく、例えば、2in1モジュールを逆導通形のMOSFET素子で構成してもよいし、逆導通形のGTO素子で構成してよい。

【0066】

DC−DCコンバータ回路10において、2in1モジュールを適用できる回路を構成することが可能な実施例として、次の第1実施例及び第2実施例を例示できる。

【0067】

[第1実施例]

図6は、2in1モジュールを適用できる回路を構成することが可能な第1実施例の回路図である。なお、図6に示す各接続点A〜Dは、図1に示す各接続点A〜Dに対応している。また、図6において、電圧源等は図示を省略してある。これらのことは、後述する図7の回路についても同様である。

【0068】

第1実施例では、図6に示すように、第3スイッチング素子SW3は、一方向にのみ電流をオン,オフ制御可能な第3半導体スイッチS3と、第3ダイオードD3と、第5ダイオードD5とで構成されている。

【0069】

第4スイッチング素子SW4は、一方向にのみ電流をオン,オフ制御可能な第4半導体スイッチS4と、第4ダイオードD4と、第6ダイオードD6とで構成されている。

【0070】

第3ダイオードD3は、第3半導体スイッチS3が電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように第3半導体スイッチS3に並列接続されている。

【0071】

第4ダイオードD4は、第4半導体スイッチS4が電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように第4半導体スイッチS4に並列接続されている。

【0072】

第5ダイオードD5は、第3半導体スイッチS3に並列接続された第3ダイオードD3のカソード側と第1スイッチング素子SW1に含まれる第1ダイオードD1のカソード側(接続点B参照)との間に、第3ダイオードD3と逆方向に電流を流すことができるように接続されている。

【0073】

第6ダイオードD6は、第4半導体スイッチS4に並列接続された第4ダイオードD4のカソード側と第2スイッチング素子SW2に含まれる第2ダイオードD2のカソード側(接続点C参照)との間に、第4ダイオードD4と逆方向に電流を流すことができるように接続されている。

【0074】

そして、第3半導体スイッチS3に並列接続された第3ダイオードD3のアノード側が、第2スイッチング素子SW3に含まれる第2ダイオードD2のカソード側(接続点C参照)に接続されている。第4半導体スイッチS4に並列接続された第4ダイオードD4のアノード側が、第1スイッチング素子SW1に含まれる第1ダイオードD1のカソード側(接続点B参照)に接続されている。

【0075】

この第1実施例では、第4半導体スイッチS4と第4ダイオードD4とからなる半導体素子を上アームの第1逆導通形の半導体素子H1とし、第1半導体スイッチS1と第1ダイオードD1とからなる半導体素子(第1スイッチング素子SW1)を下アームの第2逆導通形の半導体素子H2とすることができる。

【0076】

これより、DC−DCコンバータ回路10において、第1逆導通形の半導体素子H1と第2逆導通形の半導体素子H2とを直列接続して一体的に形成した2in1モジュールM1を用いることができる。

【0077】

また、第3半導体スイッチS3と第3ダイオードD3とからなる半導体素子を上アームの第3逆導通形の半導体素子H3とし、第2半導体スイッチS2と第2ダイオードD2とからなる半導体素子(第2スイッチング素子SW2)を下アームの第4逆導通形の半導体素子H4とすることができる。

【0078】

これにより、DC−DCコンバータ回路10において、第3逆導通形の半導体素子H3と第4逆導通形の半導体素子H4とを直列接続して一体的に形成した2in1モジュールM2を用いることができる。

【0079】

このように、2in1モジュールM1,M2を用いることができるので、使い勝手のよい回路構成を実現することが可能となる。

【0080】

[第2実施例]

図7は、2in1モジュールを適用できる回路を構成することが可能な第2実施例の回路図である。

【0081】

第2実施例では、図7に示すように、第3スイッチング素子SW3は、一方向にのみ電流をオン,オフ制御可能な第3半導体スイッチS3と、第3ダイオードD3とで構成されている。

【0082】

第4スイッチング素子SW4は、一方向にのみ電流をオン,オフ制御可能な第4半導体スイッチS4と、第4ダイオードD4とで構成されている。

【0083】

第3ダイオードD3は、第4半導体スイッチS4が電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように第4半導体スイッチS4に並列接続されている。

【0084】

第4ダイオードD4は、第3半導体スイッチS3が電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように第3半導体スイッチS3に並列接続されている。

【0085】

そして、第4半導体スイッチS4に並列接続された第3ダイオードD3のアノード側が、第1スイッチング素子SW1に含まれる第1ダイオードD1のカソード側(接続点B参照)に接続されている。第3半導体スイッチS3に並列接続された第4ダイオードD4のアノード側が、第2スイッチング素子SW2に含まれる第2ダイオードD2のカソード側(接続点C参照)に接続されている。また、第3ダイオードD3及び第4ダイオードD4のカソード側同士が接続されている。

【0086】

この第2実施例では、第4半導体スイッチS4と第3ダイオードD3とからなる半導体素子を上アームの第1逆導通形の半導体素子H1とし、第1半導体スイッチS1と第1ダイオードD1とからなる半導体素子(第1スイッチング素子SW1)を下アームの第2逆導通形の半導体素子H2とすることができる。

【0087】

これにより、DC−DCコンバータ回路10において、第1逆導通形の半導体素子H1と第2逆導通形の半導体素子H2とを直列接続して一体的に形成した2in1モジュールM1を用いることができる。

【0088】

また、第3半導体スイッチS3と第4ダイオードD4とからなる半導体素子を上アームの第3逆導通形の半導体素子H3とし、第2半導体スイッチS2と第2ダイオードD2とからなる半導体素子(第2スイッチング素子SW2)を下アームの第4逆導通形の半導体素子H4とすることができる。

【0089】

これにより、DC−DCコンバータ回路10において、第3逆導通形の半導体素子H3と第4逆導通形の半導体素子H4とを直列接続して一体的に形成した2in1モジュールM2を用いることができる。

【0090】

このように、2in1モジュールM1,M2を用いることができるので、使い勝手のよい回路構成を実現することが可能となる。

【0091】

しかも、第1実施例に比べて、第5ダイオードD5及び第6ダイオードD6を設けなくてもよいので、それだけ簡素化した回路構成を実現することができる。

【0092】

次に、第1から第4スイッチング素子SW1〜SW4の制御装置20による制御例について説明する。

【0093】

本実施の形態では、過電流による第1から第4スイッチング素子SW1〜SW4の破壊を防止する観点から、DC−DCコンバータ回路10は、制御装置20による次のスイッチング動作の制御例を行う保護機能を備えている。

【0094】

図8は、第1から第4スイッチング素子SW1〜SW4に対するスイッチング動作の第1から第3制御例により禁止する第7から第9電流経路R7〜R9を示す図である。図8(a)は、第7電流経路R7を示しており、図8(b)は、第8電流経路R8を示しており、図8(c)は、第9電流経路R9を示している。

【0095】

[第1制御例]

図8(a)に示すように、第1電圧源E1から第1スイッチング素子SW1、第2電圧源E2及び第2スイッチング素子SW2を経て第1電圧源E1に戻る第7電流経路(電圧源短絡経路)R7が形成されると、第1スイッチング素子SW1及び第2スイッチング素子SW2が過電流により破壊されることがある。

【0096】

このため、第1制御例では、制御装置20は、第1スイッチング素子SW1と第2スイッチング素子SW2との双方が同時にオン状態とならないように、第1半導体スイッチS1及び第2半導体スイッチS2の制御電圧を制御する構成とされている。

【0097】

こうすることで、第1電圧源E1から第1スイッチング素子SW1、第2電圧源E2及び第2スイッチング素子SW2を経て第1電圧源E1に戻る第7電流経路R7の形成を回避でき、過電流による第1スイッチング素子SW1及び第2スイッチング素子SW2の破壊を防止することができる。

【0098】

[第2制御例]

また、図8(b)に示すように、第2電圧源E2から第4スイッチング素子SW4及び第1スイッチング素子SW1を経て第2電圧源E2に戻る第8電流経路(電圧源短絡経路)R8が形成されると、第1スイッチング素子SW1及び第4スイッチング素子SW4が過電流により破壊されることがある。

【0099】

このため、第2制御例では、制御装置20は、前記の制御構成に代えて、或いは、加えて、第1スイッチング素子SW1と第4スイッチング素子SW4との双方が同時にオン状態とならないように、第1半導体スイッチS1及び第4半導体スイッチS4の制御電圧を制御する構成とされている。

【0100】

こうすることで、第2電圧源E2から第4スイッチング素子SW4及び第1スイッチング素子SW1を経て第2電圧源E2に戻る第8電流経路R8の形成を回避でき、過電流による第1スイッチング素子SW1及び第4スイッチング素子SW4の破壊を防止することができる。

【0101】

[第3制御例]

また、図8(c)に示すように、第1電圧源E1から第3スイッチング素子SW3及び第2スイッチング素子SW2を経て第1電圧源E1に戻る第9電流経路(電圧源短絡経路)R9が形成されると、第2スイッチング素子SW2及び第3スイッチング素子SW3が過電流により破壊されることがある。

【0102】

このため、第2制御例では、制御装置20は、前記の制御構成に代えて、或いは、加えて、第2スイッチング素子SW2と第3スイッチング素子SW3との双方が同時にオン状態とならないように、第2半導体スイッチS2及び第3半導体スイッチS3の制御電圧を制御する構成とされている。

【0103】

こうすることで、1電圧源E1から第3スイッチング素子SW3及び第2スイッチング素子SW2を経て第1電圧源E1に戻る第9電流経路R9の形成を回避でき、過電流による第2スイッチング素子SW2及び第3スイッチング素子SW3の破壊を防止することができる。

【符号の説明】

【0104】

10 DC−DCコンバータ回路

20 制御装置

D1 第1ダイオード

D2 第2ダイオード

D3 第3ダイオード

D4 第4ダイオード

D5 第5ダイオード

D6 第6ダイオード

E1 第1電圧源

E2 第2電圧源

L インダクタ

S1 第1半導体スイッチ

S2 第2半導体スイッチ

S3 第3半導体スイッチ

S4 第4半導体スイッチ

SW1 第1スイッチング素子

SW2 第2スイッチング素子

SW3 第3スイッチング素子

SW4 第4スイッチング素子

【技術分野】

【0001】

本発明は、DC−DCコンバータ回路に関するものであり、特に、双方向昇降圧形DC−DCコンバータ回路における導通損低減に関するものである。

【背景技術】

【0002】

DC−DCコンバータ回路は、例えば、第1及び第2直流電圧源(以下、単に第1及び第2電圧源という)の間に接続され、第1及び第2電圧源の出力電圧に基づき、第1電圧源から第2電圧源に電力を供給したり、或いは、第2電圧源から第1電圧源に電力を供給したりすることが可能な双方向形のスイッチング回路として用いられる。

【0003】

例えば、DC−DCコンバータ回路は、作業車両などの電動車両に用いられることがある。電動車両は、一般的に、バッテリやキャパシタ等の蓄電装置からの直流電力をインバータ回路等の電力変換回路にて交流電力に変換して得られた交流電力でモータ等の車両駆動電動機を作動させるようになっている。そして、DC−DCコンバータ回路は、第1電圧源として作用する蓄電装置と、インバータ回路等の電力変換回路が接続された第2電圧源との間に設けられ、力行モード時には蓄電装置から電力変換回路に電力を供給する一方、回生モード時には電力変換回路から蓄電装置に電力を供給することが可能な構成とされている。

【0004】

従来のDC−DCコンバータ回路として、例えば、下記特許文献1に記載のチョッパ回路(特許文献1の図4参照)がある。

【0005】

図9は、従来のDC−DCコンバータ回路の一例を示す回路図である。図9に示すDC−DCコンバータ回路は、第1から第4スイッチング素子121〜124と、インダクタ125とを備えている。

【0006】

第1から第4スイッチング素子121〜124は、それぞれ、一方向にのみ電流を流すことができる第1から第4半導体スイッチ121a〜124aと、第1から第4半導体スイッチ121a〜124aに対して電流を流すことができる方向を逆にしてそれぞれ並列接続された第1から第4ダイオード121b〜124bとからなっている。

【0007】

インダクタ125は、一端が第1スイッチング素子121に含まれる第1ダイオード121bのアノード側及び第2スイッチング素子122に含まれる第2ダイオード122bのカソード側の双方に接続され、かつ、他端が第3スイッチング素子123に含まれる第3ダイオード123bのアノード側及び第4スイッチング素子124に含まれる第2ダイオード124bのカソード側の双方に接続されている。

【0008】

そして、図9に示すDC−DCコンバータ回路は、第1スイッチング素子121に含まれる第1ダイオード121bのカソード側と第2スイッチング素子122に含まれる第2ダイオード122bのアノード側との間に第1電圧源110が接続され、第3スイッチング素子123に含まれる第3ダイオード123bのカソード側と第4スイッチング素子124に含まれる第4ダイオード124bのアノード側との間に第2電圧源120が接続されるようになっている。

【0009】

このような従来のDC−DCコンバータ回路において、各スイッチング素子121〜124のオン状態及びオフ状態を示す動作モードとして、力行モードで動作する次の第1モードから第3モードと、回生モードで動作する次の第4モードから第6モードとを例示できる。

【0010】

図10は、図9に示すDC−DCコンバータ回路において力行モードで動作している状態を示す図である。図10(a)は、第1モードを示しており、図10(b)は、第2モードを示しており、図10(c)は、第3モードを示している。

【0011】

例えば、力行モードにおいては、図10(a)に示すように、第1モードは、第1電圧源110から第1スイッチング素子121、インダクタ125及び第4スイッチング素子124を経て第1電圧源110に戻る電流経路R1aを形成するモードとされている。図10(b)に示すように、第2モードは、第1電圧源110から第1スイッチング素子121、インダクタ125、第3スイッチング素子123及び第2電圧源120を経て第1電圧源110に戻る電流経路R2aを形成するモードとされている。図10(c)に示すように、第3モードは、第2電圧源120から第2スイッチング素子122、インダクタ125及び第3スイッチング素子123を経て第2電圧源120に戻る電流経路R3aを形成するモードとされている。

【0012】

そして、力行モードを実行するときは、第1電圧源110の出力電圧V1と第2電圧源120の出力電圧V2との大小関係に応じて、第1モードと第2モードと第3モードとのうち少なくとも二つのモードを短い周期(例えば10kHz〜100kHz程度のうち何れかの周期)で切り換える各種切り換え動作が実行される。

【0013】

また、図11は、図9に示すDC−DCコンバータ回路において回生モードで動作している状態を示す図である。図11(a)は、第4モードを示しており、図11(b)は、第5モードを示しており、図11(c)は、第6モードを示している。

【0014】

例えば、回生モードにおいては、図11(a)に示すように、第4モードは、第1電圧源110から第4スイッチング素子124、インダクタ125及び第1スイッチング素子121を経て第1電圧源110に戻る電流経路R4aを形成するモードとされている。図11(b)に示すように、第5モードは、第1電圧源110から第2電圧源120、第3スイッチング素子123、インダクタ125及び第1スイッチング素子121を経て第1電圧源110に戻る電流経路R5aを形成するモードとされている。図11(c)に示すように、第6モードは、第2電圧源120から第3スイッチング素子123、インダクタ125及び第2スイッチング素子122を経て第2電圧源120に戻る電流経路R6aを形成するモードとされている。

【0015】

そして、回生モードを実行するときは、第1電圧源110の出力電圧V1と第2電圧源120の出力電圧V2との大小関係に応じて、第4モードと第5モードと第6モードとのうち少なくとも二つのモードを短い周期(例えば10kHz〜100kHz程度のうち何れかの周期)で切り換える各種切り換え動作モードが実行される。

【先行技術文献】

【特許文献】

【0016】

【特許文献1】特開2000−295715号公報

【発明の概要】

【発明が解決しようとする課題】

【0017】

ところで、DC−DCコンバータ回路においては、各種切り換え動作モードにおいて電流が通過するスイッチング素子の数が多くなれば、それだけ導通損が大きくなり、それに伴って電力変換効率が低下する。

【0018】

図9に示す従来のDC−DCコンバータ回路では、スイッチング素子として、例えば、第1モード(図10(a)参照)及び第4モード(図11(a)参照)で第1スイッチング素子121及び第4スイッチング素子124に、第2モード(図10(b)参照)及び第5モード(図11(b)参照)で第1スイッチング素子121及び第3スイッチング素子123に、また、第3モード(図10(c)参照)及び第6モード(図11(c)参照)で第2スイッチング素子122及び第3スイッチング素子123にそれぞれ電流が通過することになる。つまり、第1モードから第6モードの何れのモードにおいても(力行モード及び回生モードの何れにおいても)、少なくとも二つのスイッチング素子に対して電流が通過するため、それだけ導通損が大きくなり、それに伴って電力変換効率が低下する。

【0019】

そこで、本発明は、従来よりもスイッチング素子の導通損を低減でき、これにより電力変換効率を向上させることができるDC−DCコンバータ回路を提供することを目的とする。

【課題を解決するための手段】

【0020】

本発明は、前記課題を解決するために、一方向に電流をオン,オフ制御可能な第1半導体スイッチ、及び、前記第1半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第1半導体スイッチに並列接続された第1ダイオードを含む第1スイッチング素子と、一方向に電流をオン,オフ制御可能な第2半導体スイッチ、及び、前記第2半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第2半導体スイッチに並列接続された第2ダイオードを含む第2スイッチング素子と、一端が前記第1スイッチング素子に含まれる前記第1ダイオードのアノード側に接続され、かつ、他端が前記第2スイッチング素子に含まれる前記第2ダイオードのアノード側に接続されたインダクタと、前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側から前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側への一方向に電流を流すことができるように設けられた第3スイッチング素子と、前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側から前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側への一方向に電流を流すことができるように設けられた第4スイッチング素子とを備え、前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側と前記第2スイッチング素子に含まれる前記第2ダイオードのアノード側との間に、前記第1スイッチング素子側が陽極になるように第1電圧源が接続され、前記第1スイッチング素子に含まれる前記第1ダイオードのアノード側と前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側との間に、前記第2スイッチング素子側が陽極になるように第2電圧源が接続されることを特徴とするDC−DCコンバータ回路を提供する。

【0021】

本発明に係るDC−DCコンバータ回路によれば、前記第1電圧源と前記第2電圧源との間で双方向に出力電圧の昇降圧を行うことができる。また、前記第1電圧源と前記第2電圧源との間で双方向に電力を供給することができる。さらに、少なくとも一つのスイッチング素子(従来に比べて半分のスイッチング素子)に対して電流を通過させることができ、それだけ導通損を低減でき、これにより電力変換効率を向上させることができる。なお、この作用効果については、以下の実施の形態で詳しく説明する。

【0022】

ところで、インバータ回路等の電力変換回路に利用されているモジュールとして、二つの逆導通形の半導体素子を直列接続して一体的に形成したモジュール(いわゆる2in1モジュール)が市販されている。本発明に係るDC−DCコンバータ回路おいて、電力容量等の設計仕様によっては、この2in1モジュールを用いることが好ましい場合がある。

【0023】

かかる観点から、本発明に係るDC−DCコンバータ回路において、2in1モジュールを適用できる回路を構成することが可能な態様として、次の(a)及び(b)の態様を例示できる。すなわち、

(a)の態様として、前記第3スイッチング素子は、一方向に電流をオン,オフ制御可能な第3半導体スイッチと、第3ダイオードと、第5ダイオードとを含んでおり、前記第4スイッチング素子は、一方向に電流をオン,オフ制御可能な第4半導体スイッチと、第4ダイオードと、第6ダイオードとを含んでおり、前記第3ダイオードは、前記第3半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第3半導体スイッチに並列接続されており、前記第4ダイオードは、前記第4半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第4半導体スイッチに並列接続されており、前記第5ダイオードは、前記第3半導体スイッチに並列接続された前記第3ダイオードのカソード側と前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側との間に、前記第3ダイオードと逆方向に電流を流すことができるように接続されており、前記第6ダイオードは、前記第4半導体スイッチに並列接続された前記第4ダイオードのカソード側と前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側との間に、前記第4ダイオードと逆方向に電流を流すことができるように接続されており、前記第3半導体スイッチに並列接続された前記第3ダイオードのアノード側が、前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側に接続されており、前記第4半導体スイッチに並列接続された前記第4ダイオードのアノード側が、前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側に接続されている態様を例示できる。

【0024】

(b)の態様として、前記第3スイッチング素子は、一方向に電流をオン,オフ制御可能な第3半導体スイッチと、第3ダイオードとを含んでおり、前記第4スイッチング素子は、一方向に電流をオン,オフ制御可能な第4半導体スイッチと、第4ダイオードとを含んでおり、前記第3ダイオードは、前記第4半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第4半導体スイッチに並列接続されており、前記第4ダイオードは、前記第3半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第3半導体スイッチに並列接続されており、前記第4半導体スイッチに並列接続された前記第3ダイオードのアノード側が、前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側に接続されており、前記第3半導体スイッチに並列接続された前記第4ダイオードのアノード側が、前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側に接続されており、前記第3ダイオード及び前記第4ダイオードのカソード側同士が接続されている態様を例示できる。

【0025】

なお、前記半導体スイッチとしては、IGBT(Insulated Gate Bipolar Transistor)、MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)及びGTO(Gate Turn-Off thyristor)等の半導体スイッチを例示できる。前記逆導通形の半導体素子としては、IGBT、GTO等の半導体スイッチに対して電流を流すことができる方向を逆にしてダイオードを並列接続した半導体素子、MOSFET等のように半導体の構造的に寄生ダイオード(または、ボディダイオード)が存在する半導体素子を例示でき、例えば、逆導通形のIGBT素子、逆導通形のMOSFET素子、逆導通形のGTO素子を挙げることができる。

【0026】

また、過電流による前記第1から第4までのスイッチング素子の破壊を防止する観点からは、本発明に係るDC−DCコンバータ回路において、次の(c)から(f)までの態様にすることが好ましい。すなわち、

(c)の態様として、前記第1スイッチング素子と前記第2スイッチング素子との双方が同時にオン状態とならないように制御する手段を備える態様を例示できる。

【0027】

(d)の態様として、前記第1スイッチング素子と前記第4スイッチング素子との双方が同時にオン状態とならないように制御する手段を備える態様を例示できる。

【0028】

(e)の態様として、前記第2スイッチング素子と前記第3スイッチング素子との双方が同時にオン状態とならないように制御する手段を備える態様を例示できる。

【0029】

(f)の態様として、前記(c)から前記(e)までの態様のうち少なくとも二つを組み合わせた態様を例示できる。

【発明の効果】

【0030】

以上説明したように、本発明によると、従来よりもスイッチング素子の導通損を低減でき、これにより電力変換効率を向上させることができるDC−DCコンバータ回路を提供することができる。

【図面の簡単な説明】

【0031】

【図1】本発明の実施の形態に係るDC−DCコンバータ回路を示す回路図である。

【図2】図1に示すDC−DCコンバータにおいて力行モードで動作している状態を示す図であって、図(a)は、第1モードを示す図であり、図(b)は、第2モードを示す図であり、図(c)は、第3モードを示す図である。

【図3】図1に示すDC−DCコンバータにおいて回生モードで動作している状態を示す図であって、図(a)は、第4モードを示す図であり、図(b)は、第5モードを示す図であり、図(c)は、第6モードを示す図である。

【図4】第1から第4スイッチング素子に用いることができる半導体スイッチの例を示す図であって、図(a)は、第1及び第2スイッチング素子として逆導通形のIGBT素子を用いたい例を示す図であり、図(b)は、第3スイッチング素子と第4スイッチング素子との接続構成を逆阻止形のIGBTのみで構成した例を示す図であり、図(c)は、第3スイッチング素子と第4スイッチング素子との接続構成を逆導通形のIGBTとダイオードとで構成した例を示す図であり、図(d)は、第3スイッチング素子と第4スイッチング素子との接続構成を逆導通形のIGBTで構成した例を示す図である。

【図5】第1から第4スイッチング素子に用いることができる2in1モジュールの例を示す図である。

【図6】2in1モジュールを適用できる回路を構成することが可能な第1実施例の回路図である。

【図7】2in1モジュールを適用できる回路を構成することが可能な第2実施例の回路図である。

【図8】第1から第4スイッチング素子に対するスイッチング動作の第1から第3制御例により禁止する第7から第9電流経路を示す図であって、図(a)は、第7電流経路を示す図であり、図(b)は、第8電流経路を示す図であり、図(c)は、第9電流経路を示す図である。

【図9】従来のDC−DCコンバータ回路の一例を示す回路図である。

【図10】図9に示すDC−DCコンバータ回路において力行モードで動作している状態を示す図であって、図(a)は、第1モードを示す図であり、図(b)は、第2モードを示す図であり、図(c)は、第3モードを示す図である。

【図11】図9に示すDC−DCコンバータ回路において回生モードで動作している状態を示す図であって、図(a)は、第4モードを示す図であり、図(b)は、第5モードを示す図であり、図(c)は、第6モードを示す図である。

【発明を実施するための形態】

【0032】

以下、本発明の実施の形態について添付図面を参照しつつ説明する。なお、以下の実施の形態は、本発明を具体化した例であって、本発明の技術的範囲を限定する性格のものではない。

【0033】

図1は、本発明の実施の形態に係るDC−DCコンバータ回路10を示す回路図である。

【0034】

図1に示すDC−DCコンバータ回路10は、第1スイッチング素子SW1と、第2スイッチング素子SW2と、インダクタLと、第3スイッチング素子SW3と、第4スイッチング素子SW4とを備えている。

【0035】

第1スイッチング素子SW1は、第1半導体スイッチS1と第1ダイオードD1とからなっている。第1半導体スイッチS1は、一方向にのみ電流をオン,オフ制御可能な半導体デバイスとされている。第1ダイオードD1は、第1半導体スイッチS1が電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように第1半導体スイッチS1に並列接続されている。

【0036】

第2スイッチング素子SW2は、第2半導体スイッチS2と第2ダイオードD2とからなっている。第2半導体スイッチS2は、一方向にのみ電流をオン,オフ制御可能な半導体デバイスとされている。第2ダイオードD2は、第2半導体スイッチS2が電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように第2半導体スイッチS2に並列接続されている。

【0037】

インダクタLは、一端が第1スイッチング素子SW1に含まれる第1ダイオードD1のアノード側(接続点A参照)に接続され、かつ、他端が第2スイッチング素子SW2に含まれる第2ダイオードD2のアノード側(接続点D参照)に接続されている。

【0038】

第3スイッチング素子SW3は、第1スイッチング素子SW1に含まれる第1ダイオードD1のカソード側から第2スイッチング素子SW2に含まれる第2ダイオードD2のカソード側への一方向にのみ電流を流すことができるように構成されている。

【0039】

第4スイッチング素子SW4は、第2スイッチング素子SW2に含まれる第2ダイオードD2のカソード側から第1スイッチング素子SW1に含まれる第1ダイオードD1のカソード側への一方向にのみ電流を流すことができるように構成されている。

【0040】

そして、DC−DCコンバータ回路10は、第1スイッチング素子SW1に含まれる第1ダイオードD1のカソード側(接続点B参照)と第2スイッチング素子SW2に含まれる第2ダイオードD2のアノード側(接続点D参照)との間に、第1スイッチング素子SW1側が陽極になるように第1電圧源E1が接続されるようになっている。

【0041】

また、DC−DCコンバータ回路10は、第1スイッチング素子SW1に含まれる第1ダイオードD1のアノード側(接続点A参照)と第2スイッチング素子SW2に含まれる第2ダイオードD2のカソード側(接続点C参照)との間に、第2スイッチング素子SW2側が陽極になるように第2電圧源E2が接続されるようになっている。

【0042】

なお、DC−DCコンバータ回路10が作業車両に適用される場合には、例えば、第1及び第2電圧源E1,E2は、バッテリやキャパシタ等の蓄電装置とすることができる。また、第1及び第2電圧源E1,E2には、モータ等の車両駆動電動機を作動させるインバータ回路等の電力変換回路を接続することができる。

【0043】

本実施の形態に係るDC−DCコンバータ回路10は、さらに制御装置20を備えている。制御装置20は、CPU(Central Processing Unit)等の処理部21と、記憶部22とを備えている。記憶部22は、ROM(Read Only Memory)やRAM(Random Access Memory)等の記憶メモリを含み、各種制御プログラムや必要な関数およびテーブルや、各種のデータを記憶するようになっている。

【0044】

制御装置20は、DC−DCコンバータ回路10の第1から第4スイッチング素子SW1〜SW4のスイッチング動作を制御するように構成されている。

【0045】

本実施の形態に係るDC−DCコンバータ回路10において、第1から第4スイッチング素子SW1〜SW4のオン状態及びオフ状態を示す動作モードとして、力行モードで動作する次の第1モードから第3モードと、回生モードで動作する次の第4モードから第6モードとを例示できる。

【0046】

図2は、図1に示すDC−DCコンバータ回路10において力行モードで動作している状態を示す図である。図2(a)は、第1モードを示しており、図2(b)は、第2モードを示しており、図2(c)は、第3モードを示している。

【0047】

また、図3は、図1に示すDC−DCコンバータ回路10において回生モードで動作している状態を示す図である。図3(a)は、第4モードを示しており、図3(b)は、第5モードを示しており、図3(c)は、第6モードを示している。

【0048】

力行モードにおいては、例えば、第1モードは、図2(a)に示すように、第1スイッチング素子SW1がオン状態となり、それ以外の第2、第3及び第4スイッチング素子SW2,SW3,SW4がオフ状態となって、第1電圧源E1から第1スイッチング素子SW1及びインダクタLを経て第1電圧源E1に戻る第1電流経路R1を形成するモードとすることができる。

【0049】

第2モードは、図2(b)に示すように、第3スイッチング素子SW3がオン状態となり、それ以外の第1、第2及び第4スイッチング素子SW1,SW2,SW4がオフ状態となって、第1電圧源E1から第3スイッチング素子SW3、第2電圧源E2及びインダクタLを経て第1電圧源E1に戻る第2電流経路R2を形成するモードとすることができる。

【0050】

第3モードは、図2(c)に示すように、第1から第4スイッチング素子SW1〜SW4が全てオフ状態となって、第2電圧源E2からインダクタL及び第2スイッチング素子SW2を経て第2電圧源E2に戻る第3電流経路R3を形成するモードとすることができる。

【0051】

そして、力行モードを実行するときは、第1電圧源E1の出力電圧V1と第2電圧源E2の出力電圧V2との大小関係に応じて、第1モードと第2モードと第3モードとのうち少なくとも二つのモードを短い周期(例えば10kHz〜100kHz程度の何れかの周期)で切り換える各種切り換え動作を実行することができる。

【0052】

具体的には、第1電圧源E1の出力電圧V1が第2電圧源E2の出力電圧V2よりも大きい場合には、例えば、第2モードと第3モードとを切り換える切り換え動作を実行することができ、第1電圧源E1の出力電圧V1が第2電圧源E2の出力電圧V2よりも小さい場合には、例えば、第1モードと第2モードとを切り換える切り換え動作を実行することができる。第1電圧源E1の出力電圧V1と第2電圧源E2の出力電圧V2とが等しい場合には、例えば、第1モードと第3モードとを切り換える切り換え動作を実行するか、或いは、第2モードのみを実行することができる。なお、第1電圧源E1の出力電圧V1と第2電圧源E2の出力電圧V2とがほぼ等しい場合(電圧V1と電圧V2との差の絶対値が所定範囲内にある場合)に、第1モードと第3モードとを切り換える切り換え動作を実行するか、或いは、第2モードのみを実行してもよい。

【0053】

また、回生モードにおいては、例えば、第4モードは、図3(a)に示すように、第1から第4スイッチング素子SW1〜SW4が全てオフ状態となって、第1電圧源E1からインダクタL及び第1スイッチング素子SW1を経て第1電圧源E1に戻る第4電流経路R4を形成するモードとすることができる。

【0054】

第5モードは、図3(b)に示すように、第4スイッチング素子SW4がオン状態となり、それ以外の第1、第2及び第3スイッチング素子SW1,SW2,SW3がオフ状態となって、第2電圧源E2から第4スイッチング素子SW4、第1電圧源E1及びインダクタLを経て第2電圧源E2に戻る第5電流経路R5を形成するモードとすることができる。

【0055】

第6モードは、図3(c)に示すように、第2スイッチング素子SW2がオン状態となり、それ以外の第1、第3及び第4スイッチング素子SW1,SW3,SW4がオフ状態となって、第2電圧源E2から第2スイッチング素子SW2及びインダクタLを経て第2電圧源E2に戻る第6電流経路R6を形成するモードとすることができる。

【0056】

そして、回生モードを実行するときは、第1電圧源E1の出力電圧V1と第2電圧源E2の出力電圧V2との大小関係に応じて、第4モードと第5モードと第6モードとのうち少なくとも二つのモードを短い周期(例えば10kHz〜100kHz程度の何れかの周期)で切り換える各種切り換え動作を実行することができる。

【0057】

具体的には、第1電圧源E1の出力電圧V1が第2電圧源E2の出力電圧V2よりも大きい場合には、例えば、第5モードと第6モードとを切り換える切り換え動作を実行することができ、第1電圧源E1の出力電圧V1が第2電圧源E2の出力電圧V2よりも小さい場合には、例えば、第4モードと第5モードとを切り換える切り換え動作を実行することができる。第1電圧源E1の出力電圧V1と第2電圧源E2の出力電圧V2とが等しい場合には、例えば、第4モードと第6モードとを切り換える切り換え動作を実行するか、或いは、第5モードのみを実行することができる。なお、第1電圧源E1の出力電圧V1と第2電圧源E2の出力電圧V2とがほぼ等しい場合(電圧V1と電圧V2との差の絶対値が所定範囲内にある場合)に、第4モードと第6モードとを切り換える切り換え動作を実行するか、或いは、第5モードのみを実行してもよい。

【0058】

なお、第1電圧源E1の出力電圧V1、第2電圧源E2の出力電圧V2は、図示を省略した電圧計にて測定することができる。

【0059】

以上説明したように、本発明の実施の形態に係るDC−DCコンバータ10では、第1電圧源E1と第2電圧源E2との間で双方向に出力電圧V1,V2の昇降圧を行うことができる。また、第1電圧源E1と第2電圧源E2との間で双方向に電力を供給することができる。さらに、スイッチング素子として、例えば、第1モード(図2(a)参照)及び第4モード(図3(a)参照)で第1スイッチング素子SW1に、第2モード(図2(b)参照)で第3スイッチング素子SW3に、第5モード(図3(b)参照)で第4スイッチング素子SW4に、また、第3モード(図2(c)参照)及び第6モード(図3(c)参照)で第2スイッチング素子SW2にそれぞれ電流が通過するだけで済む。つまり、第1モードから第6モードの何れのモードにおいても(力行モード及び回生モードの何れにおいても)、少なくとも一つのスイッチング素子(従来に比べて半分のスイッチング素子)に対して電流を通過させることができ、それだけ導通損を低減でき、これにより電力変換効率を向上させることができる。

【0060】

特に、各モードの切り換え周期が短い程、第1から第4スイッチング素子SW1〜SW4のスイッチングロスが大きくなるため、それだけ前記した作用効果を有効なものとすることができる。

【0061】

なお、第1から第4スイッチング素子SW1〜SW4に用いることができる半導体スイッチとして、例えば、IGBT、MOSFET、GTOを用いることができる。ここで、MOSFETは200V程度以下、IGBTは2kV程度以下のシステムで使用されることが多い。また、第1から第4スイッチング素子SW1〜SW4としてMOSFETを用いる場合には、逆並列接続されているダイオードに電流が流れている時に当該MOSFETをオンとする同期整流により当該MOSFETでの導通損失を低減することが可能である。

【0062】

図4は、第1から第4スイッチング素子SW1〜SW4に用いることができる半導体スイッチの例を示す図である。図4(a)は、第1及び第2スイッチング素子SW1,SW2として逆導通形のIGBT素子を用いたい例(図中右側)を示している。図4(b)は、第3スイッチング素子SW3と第4スイッチング素子SW4との接続構成を逆阻止形のIGBTのみで構成した例(図中右側)を示している。図4(c)は、第3スイッチング素子SW3と第4スイッチング素子SW4との接続構成を逆導通形のIGBTとダイオードとで構成した例(図中右側)を示している。図4(d)は、第3スイッチング素子SW3と第4スイッチング素子SW4との接続構成を逆導通形のIGBTで構成した例(図中右側)を示している。なお、図4(c)及び図4(d)に示す接続例については、以下の第1実施例及び第2実施例で説明する。

【0063】

図4に示す例では、半導体スイッチをIGBTとしているが、半導体スイッチをMOSFETとしてもよいし、GTOとしてもよい。

【0064】

また、第1から第4スイッチング素子SW1〜SW4は、例えば、二つの逆導通形の半導体素子を直列接続して一体的に形成した2in1モジュールを用いることができる。

【0065】

図5は、第1から第4スイッチング素子SW1〜SW4に用いることができる2in1モジュールの例を示す図である。図5に示す例では、2in1モジュールMを逆導通形のIGBT素子で構成している。但し、それに限定されるものではなく、例えば、2in1モジュールを逆導通形のMOSFET素子で構成してもよいし、逆導通形のGTO素子で構成してよい。

【0066】

DC−DCコンバータ回路10において、2in1モジュールを適用できる回路を構成することが可能な実施例として、次の第1実施例及び第2実施例を例示できる。

【0067】

[第1実施例]

図6は、2in1モジュールを適用できる回路を構成することが可能な第1実施例の回路図である。なお、図6に示す各接続点A〜Dは、図1に示す各接続点A〜Dに対応している。また、図6において、電圧源等は図示を省略してある。これらのことは、後述する図7の回路についても同様である。

【0068】

第1実施例では、図6に示すように、第3スイッチング素子SW3は、一方向にのみ電流をオン,オフ制御可能な第3半導体スイッチS3と、第3ダイオードD3と、第5ダイオードD5とで構成されている。

【0069】

第4スイッチング素子SW4は、一方向にのみ電流をオン,オフ制御可能な第4半導体スイッチS4と、第4ダイオードD4と、第6ダイオードD6とで構成されている。

【0070】

第3ダイオードD3は、第3半導体スイッチS3が電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように第3半導体スイッチS3に並列接続されている。

【0071】

第4ダイオードD4は、第4半導体スイッチS4が電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように第4半導体スイッチS4に並列接続されている。

【0072】

第5ダイオードD5は、第3半導体スイッチS3に並列接続された第3ダイオードD3のカソード側と第1スイッチング素子SW1に含まれる第1ダイオードD1のカソード側(接続点B参照)との間に、第3ダイオードD3と逆方向に電流を流すことができるように接続されている。

【0073】

第6ダイオードD6は、第4半導体スイッチS4に並列接続された第4ダイオードD4のカソード側と第2スイッチング素子SW2に含まれる第2ダイオードD2のカソード側(接続点C参照)との間に、第4ダイオードD4と逆方向に電流を流すことができるように接続されている。

【0074】

そして、第3半導体スイッチS3に並列接続された第3ダイオードD3のアノード側が、第2スイッチング素子SW3に含まれる第2ダイオードD2のカソード側(接続点C参照)に接続されている。第4半導体スイッチS4に並列接続された第4ダイオードD4のアノード側が、第1スイッチング素子SW1に含まれる第1ダイオードD1のカソード側(接続点B参照)に接続されている。

【0075】

この第1実施例では、第4半導体スイッチS4と第4ダイオードD4とからなる半導体素子を上アームの第1逆導通形の半導体素子H1とし、第1半導体スイッチS1と第1ダイオードD1とからなる半導体素子(第1スイッチング素子SW1)を下アームの第2逆導通形の半導体素子H2とすることができる。

【0076】

これより、DC−DCコンバータ回路10において、第1逆導通形の半導体素子H1と第2逆導通形の半導体素子H2とを直列接続して一体的に形成した2in1モジュールM1を用いることができる。

【0077】

また、第3半導体スイッチS3と第3ダイオードD3とからなる半導体素子を上アームの第3逆導通形の半導体素子H3とし、第2半導体スイッチS2と第2ダイオードD2とからなる半導体素子(第2スイッチング素子SW2)を下アームの第4逆導通形の半導体素子H4とすることができる。

【0078】

これにより、DC−DCコンバータ回路10において、第3逆導通形の半導体素子H3と第4逆導通形の半導体素子H4とを直列接続して一体的に形成した2in1モジュールM2を用いることができる。

【0079】

このように、2in1モジュールM1,M2を用いることができるので、使い勝手のよい回路構成を実現することが可能となる。

【0080】

[第2実施例]

図7は、2in1モジュールを適用できる回路を構成することが可能な第2実施例の回路図である。

【0081】

第2実施例では、図7に示すように、第3スイッチング素子SW3は、一方向にのみ電流をオン,オフ制御可能な第3半導体スイッチS3と、第3ダイオードD3とで構成されている。

【0082】

第4スイッチング素子SW4は、一方向にのみ電流をオン,オフ制御可能な第4半導体スイッチS4と、第4ダイオードD4とで構成されている。

【0083】

第3ダイオードD3は、第4半導体スイッチS4が電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように第4半導体スイッチS4に並列接続されている。

【0084】

第4ダイオードD4は、第3半導体スイッチS3が電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように第3半導体スイッチS3に並列接続されている。

【0085】

そして、第4半導体スイッチS4に並列接続された第3ダイオードD3のアノード側が、第1スイッチング素子SW1に含まれる第1ダイオードD1のカソード側(接続点B参照)に接続されている。第3半導体スイッチS3に並列接続された第4ダイオードD4のアノード側が、第2スイッチング素子SW2に含まれる第2ダイオードD2のカソード側(接続点C参照)に接続されている。また、第3ダイオードD3及び第4ダイオードD4のカソード側同士が接続されている。

【0086】

この第2実施例では、第4半導体スイッチS4と第3ダイオードD3とからなる半導体素子を上アームの第1逆導通形の半導体素子H1とし、第1半導体スイッチS1と第1ダイオードD1とからなる半導体素子(第1スイッチング素子SW1)を下アームの第2逆導通形の半導体素子H2とすることができる。

【0087】

これにより、DC−DCコンバータ回路10において、第1逆導通形の半導体素子H1と第2逆導通形の半導体素子H2とを直列接続して一体的に形成した2in1モジュールM1を用いることができる。

【0088】

また、第3半導体スイッチS3と第4ダイオードD4とからなる半導体素子を上アームの第3逆導通形の半導体素子H3とし、第2半導体スイッチS2と第2ダイオードD2とからなる半導体素子(第2スイッチング素子SW2)を下アームの第4逆導通形の半導体素子H4とすることができる。

【0089】

これにより、DC−DCコンバータ回路10において、第3逆導通形の半導体素子H3と第4逆導通形の半導体素子H4とを直列接続して一体的に形成した2in1モジュールM2を用いることができる。

【0090】

このように、2in1モジュールM1,M2を用いることができるので、使い勝手のよい回路構成を実現することが可能となる。

【0091】

しかも、第1実施例に比べて、第5ダイオードD5及び第6ダイオードD6を設けなくてもよいので、それだけ簡素化した回路構成を実現することができる。

【0092】

次に、第1から第4スイッチング素子SW1〜SW4の制御装置20による制御例について説明する。

【0093】

本実施の形態では、過電流による第1から第4スイッチング素子SW1〜SW4の破壊を防止する観点から、DC−DCコンバータ回路10は、制御装置20による次のスイッチング動作の制御例を行う保護機能を備えている。

【0094】

図8は、第1から第4スイッチング素子SW1〜SW4に対するスイッチング動作の第1から第3制御例により禁止する第7から第9電流経路R7〜R9を示す図である。図8(a)は、第7電流経路R7を示しており、図8(b)は、第8電流経路R8を示しており、図8(c)は、第9電流経路R9を示している。

【0095】

[第1制御例]

図8(a)に示すように、第1電圧源E1から第1スイッチング素子SW1、第2電圧源E2及び第2スイッチング素子SW2を経て第1電圧源E1に戻る第7電流経路(電圧源短絡経路)R7が形成されると、第1スイッチング素子SW1及び第2スイッチング素子SW2が過電流により破壊されることがある。

【0096】

このため、第1制御例では、制御装置20は、第1スイッチング素子SW1と第2スイッチング素子SW2との双方が同時にオン状態とならないように、第1半導体スイッチS1及び第2半導体スイッチS2の制御電圧を制御する構成とされている。

【0097】

こうすることで、第1電圧源E1から第1スイッチング素子SW1、第2電圧源E2及び第2スイッチング素子SW2を経て第1電圧源E1に戻る第7電流経路R7の形成を回避でき、過電流による第1スイッチング素子SW1及び第2スイッチング素子SW2の破壊を防止することができる。

【0098】

[第2制御例]

また、図8(b)に示すように、第2電圧源E2から第4スイッチング素子SW4及び第1スイッチング素子SW1を経て第2電圧源E2に戻る第8電流経路(電圧源短絡経路)R8が形成されると、第1スイッチング素子SW1及び第4スイッチング素子SW4が過電流により破壊されることがある。

【0099】

このため、第2制御例では、制御装置20は、前記の制御構成に代えて、或いは、加えて、第1スイッチング素子SW1と第4スイッチング素子SW4との双方が同時にオン状態とならないように、第1半導体スイッチS1及び第4半導体スイッチS4の制御電圧を制御する構成とされている。

【0100】

こうすることで、第2電圧源E2から第4スイッチング素子SW4及び第1スイッチング素子SW1を経て第2電圧源E2に戻る第8電流経路R8の形成を回避でき、過電流による第1スイッチング素子SW1及び第4スイッチング素子SW4の破壊を防止することができる。

【0101】

[第3制御例]

また、図8(c)に示すように、第1電圧源E1から第3スイッチング素子SW3及び第2スイッチング素子SW2を経て第1電圧源E1に戻る第9電流経路(電圧源短絡経路)R9が形成されると、第2スイッチング素子SW2及び第3スイッチング素子SW3が過電流により破壊されることがある。

【0102】

このため、第2制御例では、制御装置20は、前記の制御構成に代えて、或いは、加えて、第2スイッチング素子SW2と第3スイッチング素子SW3との双方が同時にオン状態とならないように、第2半導体スイッチS2及び第3半導体スイッチS3の制御電圧を制御する構成とされている。

【0103】

こうすることで、1電圧源E1から第3スイッチング素子SW3及び第2スイッチング素子SW2を経て第1電圧源E1に戻る第9電流経路R9の形成を回避でき、過電流による第2スイッチング素子SW2及び第3スイッチング素子SW3の破壊を防止することができる。

【符号の説明】

【0104】

10 DC−DCコンバータ回路

20 制御装置

D1 第1ダイオード

D2 第2ダイオード

D3 第3ダイオード

D4 第4ダイオード

D5 第5ダイオード

D6 第6ダイオード

E1 第1電圧源

E2 第2電圧源

L インダクタ

S1 第1半導体スイッチ

S2 第2半導体スイッチ

S3 第3半導体スイッチ

S4 第4半導体スイッチ

SW1 第1スイッチング素子

SW2 第2スイッチング素子

SW3 第3スイッチング素子

SW4 第4スイッチング素子

【特許請求の範囲】

【請求項1】

一方向に電流をオン,オフ制御可能な第1半導体スイッチ、及び、前記第1半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第1半導体スイッチに並列接続された第1ダイオードを含む第1スイッチング素子と、

一方向に電流をオン,オフ制御可能な第2半導体スイッチ、及び、前記第2半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第2半導体スイッチに並列接続された第2ダイオードを含む第2スイッチング素子と、

一端が前記第1スイッチング素子に含まれる前記第1ダイオードのアノード側に接続され、かつ、他端が前記第2スイッチング素子に含まれる前記第2ダイオードのアノード側に接続されたインダクタと、

前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側から前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側への一方向に電流を流すことができるように設けられた第3スイッチング素子と、

前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側から前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側への一方向に電流を流すことができるように設けられた第4スイッチング素子と

を備え、

前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側と前記第2スイッチング素子に含まれる前記第2ダイオードのアノード側との間に、前記第1スイッチング素子側が陽極になるように第1電圧源が接続され、

前記第1スイッチング素子に含まれる前記第1ダイオードのアノード側と前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側との間に、前記第2スイッチング素子側が陽極になるように第2電圧源が接続されることを特徴とするDC−DCコンバータ回路。

【請求項2】

請求項1に記載のDC−DCコンバータ回路であって、

前記第3スイッチング素子は、一方向に電流をオン,オフ制御可能な第3半導体スイッチと、第3ダイオードと、第5ダイオードとを含んでおり、

前記第4スイッチング素子は、一方向に電流をオン,オフ制御可能な第4半導体スイッチと、第4ダイオードと、第6ダイオードとを含んでおり、

前記第3ダイオードは、前記第3半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第3半導体スイッチに並列接続されており、

前記第4ダイオードは、前記第4半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第4半導体スイッチに並列接続されており、

前記第5ダイオードは、前記第3半導体スイッチに並列接続された前記第3ダイオードのカソード側と前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側との間に、前記第3ダイオードと逆方向に電流を流すことができるように接続されており、

前記第6ダイオードは、前記第4半導体スイッチに並列接続された前記第4ダイオードのカソード側と前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側との間に、前記第4ダイオードと逆方向に電流を流すことができるように接続されており、

前記第3半導体スイッチに並列接続された前記第3ダイオードのアノード側が、前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側に接続されており、

前記第4半導体スイッチに並列接続された前記第4ダイオードのアノード側が、前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側に接続されていることを特徴とするDC−DCコンバータ回路。

【請求項3】

請求項1に記載のDC−DCコンバータ回路であって、

前記第3スイッチング素子は、一方向に電流をオン,オフ制御可能な第3半導体スイッチと、第3ダイオードとを含んでおり、

前記第4スイッチング素子は、一方向に電流をオン,オフ制御可能な第4半導体スイッチと、第4ダイオードとを含んでおり、

前記第3ダイオードは、前記第4半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第4半導体スイッチに並列接続されており、

前記第4ダイオードは、前記第3半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第3半導体スイッチに並列接続されており、

前記第4半導体スイッチに並列接続された前記第3ダイオードのアノード側が、前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側に接続されており、

前記第3半導体スイッチに並列接続された前記第4ダイオードのアノード側が、前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側に接続されており、

前記第3ダイオード及び前記第4ダイオードのカソード側同士が接続されていることを特徴とするDC−DCコンバータ回路。

【請求項4】

請求項1から請求項3までの何れか一つに記載のDC−DCコンバータ回路であって、

前記第1スイッチング素子と前記第2スイッチング素子との双方が同時にオン状態とならないように制御する手段を備えることを特徴とするDC−DCコンバータ回路。

【請求項5】

請求項1から請求項4までの何れか一つに記載のDC−DCコンバータ回路であって、

前記第1スイッチング素子と前記第4スイッチング素子との双方が同時にオン状態とならないように制御する手段を備えることを特徴とするDC−DCコンバータ回路。

【請求項6】

請求項1から請求項5までの何れか一つに記載のDC−DCコンバータ回路であって、

前記第2スイッチング素子と前記第3スイッチング素子との双方が同時にオン状態とならないように制御する手段を備えることを特徴とするDC−DCコンバータ回路。

【請求項1】

一方向に電流をオン,オフ制御可能な第1半導体スイッチ、及び、前記第1半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第1半導体スイッチに並列接続された第1ダイオードを含む第1スイッチング素子と、

一方向に電流をオン,オフ制御可能な第2半導体スイッチ、及び、前記第2半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第2半導体スイッチに並列接続された第2ダイオードを含む第2スイッチング素子と、

一端が前記第1スイッチング素子に含まれる前記第1ダイオードのアノード側に接続され、かつ、他端が前記第2スイッチング素子に含まれる前記第2ダイオードのアノード側に接続されたインダクタと、

前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側から前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側への一方向に電流を流すことができるように設けられた第3スイッチング素子と、

前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側から前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側への一方向に電流を流すことができるように設けられた第4スイッチング素子と

を備え、

前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側と前記第2スイッチング素子に含まれる前記第2ダイオードのアノード側との間に、前記第1スイッチング素子側が陽極になるように第1電圧源が接続され、

前記第1スイッチング素子に含まれる前記第1ダイオードのアノード側と前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側との間に、前記第2スイッチング素子側が陽極になるように第2電圧源が接続されることを特徴とするDC−DCコンバータ回路。

【請求項2】

請求項1に記載のDC−DCコンバータ回路であって、

前記第3スイッチング素子は、一方向に電流をオン,オフ制御可能な第3半導体スイッチと、第3ダイオードと、第5ダイオードとを含んでおり、

前記第4スイッチング素子は、一方向に電流をオン,オフ制御可能な第4半導体スイッチと、第4ダイオードと、第6ダイオードとを含んでおり、

前記第3ダイオードは、前記第3半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第3半導体スイッチに並列接続されており、

前記第4ダイオードは、前記第4半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第4半導体スイッチに並列接続されており、

前記第5ダイオードは、前記第3半導体スイッチに並列接続された前記第3ダイオードのカソード側と前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側との間に、前記第3ダイオードと逆方向に電流を流すことができるように接続されており、

前記第6ダイオードは、前記第4半導体スイッチに並列接続された前記第4ダイオードのカソード側と前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側との間に、前記第4ダイオードと逆方向に電流を流すことができるように接続されており、

前記第3半導体スイッチに並列接続された前記第3ダイオードのアノード側が、前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側に接続されており、

前記第4半導体スイッチに並列接続された前記第4ダイオードのアノード側が、前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側に接続されていることを特徴とするDC−DCコンバータ回路。

【請求項3】

請求項1に記載のDC−DCコンバータ回路であって、

前記第3スイッチング素子は、一方向に電流をオン,オフ制御可能な第3半導体スイッチと、第3ダイオードとを含んでおり、

前記第4スイッチング素子は、一方向に電流をオン,オフ制御可能な第4半導体スイッチと、第4ダイオードとを含んでおり、

前記第3ダイオードは、前記第4半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第4半導体スイッチに並列接続されており、

前記第4ダイオードは、前記第3半導体スイッチが電流をオン,オフ制御できる方向とは逆の方向に電流を流せるように前記第3半導体スイッチに並列接続されており、

前記第4半導体スイッチに並列接続された前記第3ダイオードのアノード側が、前記第1スイッチング素子に含まれる前記第1ダイオードのカソード側に接続されており、

前記第3半導体スイッチに並列接続された前記第4ダイオードのアノード側が、前記第2スイッチング素子に含まれる前記第2ダイオードのカソード側に接続されており、

前記第3ダイオード及び前記第4ダイオードのカソード側同士が接続されていることを特徴とするDC−DCコンバータ回路。

【請求項4】

請求項1から請求項3までの何れか一つに記載のDC−DCコンバータ回路であって、

前記第1スイッチング素子と前記第2スイッチング素子との双方が同時にオン状態とならないように制御する手段を備えることを特徴とするDC−DCコンバータ回路。

【請求項5】

請求項1から請求項4までの何れか一つに記載のDC−DCコンバータ回路であって、

前記第1スイッチング素子と前記第4スイッチング素子との双方が同時にオン状態とならないように制御する手段を備えることを特徴とするDC−DCコンバータ回路。

【請求項6】

請求項1から請求項5までの何れか一つに記載のDC−DCコンバータ回路であって、

前記第2スイッチング素子と前記第3スイッチング素子との双方が同時にオン状態とならないように制御する手段を備えることを特徴とするDC−DCコンバータ回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2011−35999(P2011−35999A)

【公開日】平成23年2月17日(2011.2.17)

【国際特許分類】

【出願番号】特願2009−178196(P2009−178196)

【出願日】平成21年7月30日(2009.7.30)

【出願人】(000006781)ヤンマー株式会社 (3,810)

【Fターム(参考)】

【公開日】平成23年2月17日(2011.2.17)

【国際特許分類】

【出願日】平成21年7月30日(2009.7.30)

【出願人】(000006781)ヤンマー株式会社 (3,810)

【Fターム(参考)】

[ Back to top ]