DC−DCコンバータ

【課題】DC−DCコンバータから出力される高レンジの駆動電流を低損失で検出する。

【解決手段】DC−DCコンバータは、OTA(601)と容量(603)から構成され、インダクタ(10)の両端電圧を積分する第1の積分回路、OTA(602)と容量(604)から構成され、第1の積分回路の出力電圧を積分する第2の積分回路、第2の積分回路の出力電圧を保持する保持部(607)、保持部(607)の出力電圧に基づいてインダクタ(10)の充放電制御を行う制御部(50)を備えている。

【解決手段】DC−DCコンバータは、OTA(601)と容量(603)から構成され、インダクタ(10)の両端電圧を積分する第1の積分回路、OTA(602)と容量(604)から構成され、第1の積分回路の出力電圧を積分する第2の積分回路、第2の積分回路の出力電圧を保持する保持部(607)、保持部(607)の出力電圧に基づいてインダクタ(10)の充放電制御を行う制御部(50)を備えている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、DC−DCコンバータに関し、特に、電流不連続モードで動作する昇圧及び昇降圧コンバータに適した負荷電流検出に関するものである。

【背景技術】

【0002】

近年、携帯機器等の表示装置として有機ELパネルが多用されている。有機ELパネルは比較的高い電圧で駆動する必要があるため、駆動回路としてDC−DCコンバータ、特に、昇圧コンバータがよく用いられる。昇圧コンバータは、バッテリー等から供給される数V程度の低い入力電圧から10V以上の電圧を生成するものである。そして、有機ELパネルの特徴を十分に発揮させるためには、駆動電流を精度良く検出し、その検出結果に基づいてて駆動回路の電圧制御を行う必要がある。

【0003】

一般に、黒ラスタ表示時には有機ELパネルにはほとんど電流は流れていないが、画面の輝度を確保するために印加電圧を通常よりも高く設定することが行われる。しかし、有機ELパネルに過大な電流が流れ続けるとパネル寿命が著しく低下してしまうため、過電流が検出された場合には印加電圧を低下させるように制御することが好ましい。従来、有機ELパネルに過電流が流れるのを防止するために、信号ラインに挿入した検出抵抗の両端に生じる電圧から駆動電流を検出し、その検出結果に応じて有機ELパネルの駆動電圧及び駆動電流を制御する技術が知られている(例えば、特許文献1参照)。

【特許文献1】特開2001−110565号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかし、上記手法では、検出抵抗によって駆動電圧に損失が生じてしまう。損失低減のために検出抵抗の抵抗値を小さくすると、黒ラスタ表示のような軽負荷の場合に検出精度が確保できなくなるといった問題が生じる。逆に、軽負荷時の検出精度を向上させるために検出抵抗の抵抗値を大きくすると、重負荷時に多大な損失が発生してしまう。このため、有機ELパネルの駆動回路では、一般に、抵抗値が比較的小さな検出抵抗を設けて、重負荷時の駆動電流のみを検出するようになっている。

【0005】

上記問題に鑑み、本発明は、主に駆動回路として用いられるDC−DCコンバータについて、高レンジの駆動電流を低損失で検出することを課題とする。

【課題を解決するための手段】

【0006】

上記課題を解決するために本発明が講じた手段は、インダクタを備えたDC−DCコンバータとして、前記インダクタの両端電圧を積分する第1の積分回路と、前記第1の積分回路の出力電圧を積分する第2の積分回路と、前記第2の積分回路の出力電圧を保持する保持部と、前記保持部の出力電圧に基づいて前記インダクタの充放電制御を行う制御部とを備えたものとする。

【0007】

これによると、制御部の制御によりインダクタに充電された電気エネルギーに対応する電圧が第1及び第2の積分回路によって二重積分され、当該積分結果が保持部に保持され、当該保持電圧に基づいて制御部によってインダクタの充放電制御が行われる。当該二重積分によって得られる電圧は本DC−DCコンバータから出力される駆動電流に比例しており、これにより、特に検出抵抗を用いなくとも駆動電流を検出することができる。

【0008】

具体的には、前記第1の積分回路は、積分電荷を蓄積する第1の容量を有するものであり、前記第2の積分回路は、積分電荷を蓄積する第2の容量を有するものである。そして、上記のDC−DCコンバータは、前記第1の容量に並列に設けられた第1のスイッチと、前記第2の容量に並列に設けられた第2のスイッチと、前記インダクタの出力電圧と当該DC−DCコンバータの出力電圧とを受け、前記インダクタの出力電圧が当該DC−DCコンバータの出力電圧よりも小さいとき、前記第1のスイッチを導通状態にする一方、それ以外のとき、前記第1のスイッチを非導通状態にするスイッチ制御部とをさらに備えている。ここで、前記制御部は、前記インダクタの充電制御を行うとき、前記第2のスイッチを導通状態にする一方、前記インダクタの放電制御を行うとき、前記第2のスイッチを非導通状態にするものである。

【0009】

より具体的には、前記第1の積分回路は、前記インダクタの入力電圧と出力電圧との差分に応じた電流を出力する演算相互コンダクタンス増幅器を有するものである。また、前記第1の容量は、前記演算相互コンダクタンス増幅器から出力された電流によって充電されるものである。

【0010】

また、より具体的には、前記第1の積分回路は、前記インダクタの出力電圧を電源電圧とし、前記第1の容量に接続された第1の電流源と、前記インダクタの入力電圧によってバイアス制御され、前記第1の電流源から電流を引き抜く第2の電流源とを有するものである。

【0011】

一方、本発明が講じた手段は、インダクタを備えたDC−DCコンバータとして、前記インダクタの入力電圧を積分する第1の積分回路と、前記第1の積分回路の出力電圧を積分する第2の積分回路と、前記第2の積分回路の出力電圧を保持する保持部と、前記保持部の出力電圧に基づいて前記インダクタの充放電制御を行う制御部とを備えたものとする。

【0012】

これによると、インダクタの入力電圧が第1の積分回路で積分され、当該積分結果がさらに第2の積分回路によって積分され、結局、インダクタに充電されることとなる電気エネルギーに対応する電圧が第1及び第2の積分回路によって二重積分され、当該積分結果が保持部に保持され、当該保持電圧に基づいて制御部によってインダクタの充放電制御が行われる。当該二重積分によって得られる電圧は本DC−DCコンバータから出力される駆動電流に比例しており、これにより、特に検出抵抗を用いなくとも駆動電流を検出することができる。

【0013】

具体的には、前記第1の積分回路は、積分電荷を蓄積する第1の容量を有するものであり、前記第2の積分回路は、積分電荷を蓄積する第2の容量を有するものである。そして、上記のDC−DCコンバータは、前記第1の容量に並列に設けられた第1のスイッチと、前記第2の容量に並列に設けられた第2のスイッチと、前記第1の積分回路の積分動作の有効及び無効を切り替える第3のスイッチと、前記インダクタの出力電圧と当該DC−DCコンバータの出力電圧と前記制御部の出力とを受け、前記インダクタの出力電圧が当該DC−DCコンバータの出力電圧よりも小さく、かつ、前記制御部によって前記インダクタの放電制御が行われているとき、前記第1のスイッチを導通状態にする一方、それ以外のとき、前記第1のスイッチを非導通状態にするスイッチ制御部とをさらに備えている。ここで、前記制御部は、前記インダクタの充電制御を行うとき、前記第2のスイッチを導通状態にするとともに前記第3のスイッチを前記第1の容量が充電される第1の状態にする一方、前記インダクタの放電制御を行うとき、前記第2のスイッチを非導通状態にするとともに前記第3のスイッチを前記第1の容量の充電が停止する第2の状態にするものである。

【0014】

より具体的には、前記第1の積分回路は、前記インダクタの入力電圧と所定電圧との差分に応じた電流を出力する演算相互コンダクタンス増幅器を有するものである。また、前記第1の容量は、前記演算相互コンダクタンス増幅器から出力された電流によって充電されるものである。

【0015】

さらに具体的には、前記第3のスイッチは、前記演算相互コンダクタンス増幅器の反転入力端と非反転入力端との間に設けられたものである。そして、前記第1の状態は、前記反転入力端と前記非反転入力端とを開放する状態であり、前記第2の状態は、前記反転入力端と前記非反転入力端とを短絡する状態である。

【0016】

また、さらに具体的には、前記第3のスイッチは、前記演算相互コンダクタンス増幅器の出力端と前記第1の容量との間に設けられたものである。そして、前記第1の状態は、導通状態であり、前記第2の状態は、非導通状態である。

【0017】

また、具体的には、前記第2の積分回路は、前記第1の容量の両端電圧に応じた電流を出力する演算相互コンダクタンス増幅器を有するものであり、前記第2の容量は、前記演算相互コンダクタンス増幅器から出力された電流によって充電されるものである。

【0018】

また、好ましくは、前記保持部は、前記制御部及びスイッチ制御部のいずれか一方の制御によって初期化されるものとする。

【発明の効果】

【0019】

以上のように本発明によると、DC−DCコンバータについて、高レンジの駆動電流を低損失で検出することができる。

【発明を実施するための最良の形態】

【0020】

以下、本発明を実施するための最良の形態について、図面を参照しながら説明する。

【0021】

(第1の実施形態)

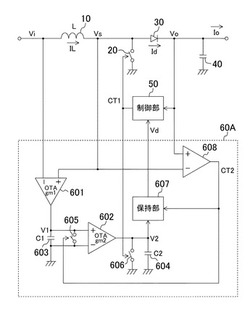

図1は、第1の実施形態に係るDC−DCコンバータの構成を示す。本DC−DCコンバータは、インダクタ10、スイッチ20、ダイオード30、容量40、制御部50、及び検出部60Aを備えた昇圧コンバータである。

【0022】

インダクタ10は、バッテリー等の入力電圧Viを受け、スイッチ20の開閉動作に応じて充放電を繰り返す。この充放電電流はダイオード30によって整流され、容量40で平滑化されて出力電圧Voとなる。制御部50は、出力電圧Vo及び検出部60Aから出力された検出電圧Vdに応じて制御信号CT1の論理レベルを変化させて適応的にスイッチ20の開閉動作を制御する。詳しくは後述するが、検出電圧Vdは本DC−DCコンバータの出力電流(駆動電流)Ioを間接的に検出したものである。これにより、本DC−DCコンバータでは、出力電圧Vo及び出力電流Ioに基づいてフィードバック制御をすることができるようになっている。

【0023】

検出部60Aは、演算相互コンダクタンス増幅器(OTA)601及び602、容量603及び604、スイッチ605及び606、保持部607、及びスイッチ制御部としての比較器608を備えている。OTA601は、インダクタ10の両端電圧、すなわち、入力電圧Vi及びスイッチ電圧(インダクタ10の出力電圧)Vsの差分に応じた電流を出力し、容量603を充電する。すなわち、OTA601と容量603とで積分回路が構成されている。また、OTA602は、容量602の両端電圧に応じた電流を出力し、容量604を充電する。すなわち、OTA602と容量604とで積分回路が構成されている。

【0024】

比較器608は、スイッチ電圧Vs及び出力電圧Voを受け、これら電圧の大小関係に応じて制御信号CT2を出力する。具体的には、比較器608は、スイッチ電圧Vsが出力電圧Voよりも小さい(又は以下)のとき、制御信号CT2をHレベルにする。一方、これ以外のとき、制御信号CT2をLレベルにする。

【0025】

スイッチ605は、容量603に並列に設けられており、制御信号CT2に従って開閉動作をする。具体的には、スイッチ605は、制御信号CT2がHレベルのときに導通状態となり、Lレベルのときに非導通状態となる。スイッチ605が導通状態にあるとき、容量603がリフレッシュされるとともにOTA602の差動入力がゼロとなる。これにより、OTA602の出力電流もまたゼロとなり、容量604の充電が停止する。

【0026】

スイッチ606は、容量604に並列に設けられており、制御信号CT1に従って開閉動作をする。具体的には、スイッチ606は、制御信号CT1がHレベルのときに導通状態となり、Lレベルのときに非導通状態となる。スイッチ606が導通状態にあるとき、容量604がリフレッシュされるとともに保持部607の入力がゼロとなる。

【0027】

保持部607は、容量604の電圧を保持し、検出電圧Vdとして出力する。保持部607の保持電圧は、制御信号CT2がHレベルとなるごとに初期化される。

【0028】

次に、図2のタイミングチャートを参照しながら本DC−DCコンバータの動作について説明する。ここで、図1に示したように、インダクタ10のインダクタンスをL、インダクタ10に流れる電流をIL、ダイオード30に流れる電流をId、容量603の電圧をV1、容量604の電圧をV2、OTA601の相互コンダクタンスをgm1、及びOTA602の相互コンダクタンスをgm2とする。

【0029】

時刻t0において、制御信号CT1はHレベルとなる。これにより、スイッチ20は導通状態となり、インダクタ10に入力電圧Viが印加される。すなわち、インダクタ10の充電制御が開始される。この結果、スイッチ20を流れるインダクタ電流ILは次式(1)に従って直線的に増加する。

IL=Vi/L*t…(1)

【0030】

また、スイッチ606は導通状態となり、容量604はリフレッシュされ、電圧V2はゼロ(グランドレベル)となる。また、スイッチ電圧Vsはほぼゼロであるため、制御信号CT2はHレベルとなる。これにより、スイッチ605は導通状態となり、容量603はリフレッシュされ、電圧V1はゼロとなる。

【0031】

次に、時刻t1において、制御信号CT1はLレベルとなる。これにより、スイッチ20が非導通状態となり、インダクタ10にはスイッチ電圧Vsと入力電圧Viとの差分電圧(Vi−Vs)が印加される。すなわち、インダクタ10の放電制御が開始される。この結果、ダイオード30を流れる電流Id(=インダクタ電流IL)は次式(2)に従って直線的に減少する。電流Idは容量40によって平滑化され、出力電圧Voが生成される。

IL=Id=ΔI−(Vs−Vi)/L*t…(2)

【0032】

また、時刻t1において、スイッチ電圧Vsは高電位となり、制御信号CT2はLレベルとなる。これにより、スイッチ605は非導通状態となり、容量603は(Vs−Vi)*gm1で表される大きさの電流で充電され、電圧V1は次式(3)で表される。

V1=1/C1*∫((Vs−Vi)*gm1)dt

=(Vs−Vi)/C1*gm1*t…(3)

ここで、差分電圧(Vs−Vi)がほぼ一定であれば、電圧V1は図2に示したように直線的に増加する。

【0033】

また、スイッチ606は非導通状態となり、容量604はV1*gm2で表される大きさの電流で充電され、電圧V2は次式(4)で表される。

V2=1/C2*∫(V1*gm2)dt

=1/C1/C2*∬((Vs−Vi)*gm1*gm2)dt2

=(Vs−Vi)/C1/C2*gm1*gm2*t2…(4)

ここで、差分電圧(Vs−Vi)がほぼ一定であれば、電圧V2は図2に示したように2次関数的に増加する。

【0034】

次に、時刻t2において、インダクタ電流IL、すなわち、ダイオード電流Idはゼロとなり、ダイオード30はオフ状態となる。これにより、インダクタ10の両端電圧は減衰振動しながらゼロとなる。同様に、スイッチ電圧Vsもまた減衰振動しながら入力電圧Viとなる。この結果、制御信号CT2はHレベルとなる。これにより、スイッチ605は導通状態となり、容量603はリフレッシュされ、電圧V1はゼロとなる。また、OTA602の差動入力はゼロとなり、容量604の充電は停止する。この時の電圧V2は、ダイオード30の導通期間をΔT(=t2−t1)とすると、次式(5)で表される。

V2=(Vs−Vi)/C1/C2*gm1*gm2*ΔT2…(5)

【0035】

また、制御信号CT2がHレベルとなることにより、保持部607はこの時の電圧V2を保持する。したがって、保持部607から出力される検出電圧Vdは式(5)で表される電圧V2と等しくなる。ここで、駆動電流Ioは、ダイオード電流Idを平滑化(平均化)したものであるから、スイッチ20のスイッチング周期をTとして次式(6)で表される。

Io=ΔI/2/T*ΔT…(6)

式(6)及び式(2)からΔIを消去すると次式(7)が導かれる。

Io=(Vs−Vi)/2/T/L*ΔT2…(7)

ここで、スイッチング周期Tを一定とすると、式(5)及び式(7)から次式(8)が導かれる。

Vd=2*T*L/C1/C2*gm1*gm2*Io…(8)

式(8)から、検出電圧Vdは駆動電流Ioに比例していることがわかる。これは、検出部60Aによって駆動電流Ioが間接的に検出されることを意味する。

【0036】

以後、時刻t3において、制御信号CT1が再びHレベルとなり、上述した時刻t0以降の動作が繰り返される。

【0037】

以上、本実施形態によると、ダイオードの通電期間に、インダクタの両端電圧に応じた電流で第1の容量が充電され、同時に第1の容量に生じる電圧に応じた電流で第2の容量が充電される。これにより、第2の容量に、インダクタから電気エネルギーが放出される期間の2乗に比例する電圧、すなわち、駆動電流に比例する電圧が生じる。したがって、特に検出抵抗を用いることなく、高レンジの駆動電流を低損失で検出することができる。そして、検出された駆動電流及び駆動電圧に基づいて、DC−DCコンバータの出力を適応制御することができる。

【0038】

なお、保持部607は、制御信号CT2に代えて制御信号CT1がHレベルとなるごとに初期化されるようにしてもよい。また、制御信号CT1及びCT2ではなく、図2に示した時刻t2から時刻t3までの期間にHレベルとなる信号によって初期化されるようにしてもよい。

【0039】

(第2の実施形態)

図3は、第2の実施形態に係るDC−DCコンバータの構成を示す。本DC−DCコンバータは、図1に示したDC−DCコンバータにおけるOTA601に代えて電流源611及び612を備えている。以下、第1の実施形態に係るDC−DCコンバータと異なる点についてのみ説明する。

【0040】

電流源611は、スイッチ電圧Vsを電源とする定電流源であり、容量603に接続されている。電流源612は、電流源611と容量603との接続点に接続され、電流源611から電流を引き抜く定電流源である。電流源612は、入力電圧Viによってバイアス制御される。

【0041】

図4は、図3に示したDC−DCコンバータの具体的な回路構成を示す。図4において、6121は入力電圧端に接続された抵抗、6122及び6123は電流ミラー回路を構成するNMOSトランジスタである。抵抗6121に流れる電流と等しい電流がトランジスタ6123に流れる。6111及び6112は電流ミラー回路を構成するPMOSトランジスタである。各トランジスタのソースにはスイッチ電圧Vsが印加される。6113はトランジスタ6111のゲート及びドレインと接地ノードとの間に接続された抵抗である。トランジスタ6123及び6112のドレインはいずれも容量603の一端に接続される。この接続点電位をV1とする。容量603の他端は電圧源613に接続される。なお、電圧源613の電圧V0はトランジスタ6122及び6123が飽和しない電圧レベルに設定される。6021は電圧V1が入力されるバッファ回路である。6022及び6023は直列接続された抵抗である。抵抗6022の一端には電圧V0が印加される。6024は、非反転入力端に抵抗6022及び6023の接続点電位が印加され、出力端に抵抗6023の他端が接続された演算増幅器である。6025は演算増幅器6024の出力端に接続された抵抗である。6026は、容量604及びトランジスタ6025の接続点電位であるV2が入力されるバッファ回路である。6027及び6028は直列接続された抵抗である。抵抗6028にはバッファ回路6021の出力電圧(電圧V1)が印加される。抵抗6029にはバッファ回路6026の出力電圧(電圧V2)が印加される。

【0042】

上記構成のDC−DCコンバータのタイミングチャートは図2に示したとおりである。以下、図2のタイミングチャートを参照しながら図4に示したDC−DCコンバータの動作について説明する。ここで、抵抗6113及び6121の抵抗値をいずれもR1、抵抗6025の抵抗値をR2、抵抗6022、6023、6028及び6029の抵抗値をいずれもR4とする。

【0043】

時刻t1から時刻t2までの間、容量603は(Vs−Vt)/R1−(Vi−Vt)/R1=(Vs−Vi)/R1で表される大きさの電流(ただし、Vtはトランジスタ6112及び6123のソース・ゲート間電圧である。)で充電され、電圧V1は次式(9)で表される。

V1=1/C1*∫((Vs−Vi)/R1)dt+V0

=(Vs−Vi)/C1/R1*t…(9)

【0044】

また、容量604は抵抗6025を流れる電流で充電される。演算増幅器6024の出力端電圧をV4とすると、演算増幅器6024の非反転入力端電圧は(V4+V0)/2となり、反転入力端電圧は(V1+V2)/2となる。いわゆるイマジナリーショートにより演算増幅器6024はこれら電圧が等しくなるように動作し、電圧V4は次式(10)で表される。

V4=V1+V2−V0…(10)

したがって、容量604はV4−V2=(V1−V0)/R2で表される大きさの電流で充電され、電圧V2は次式(11)で表される。

V2=1/C2*∫((V1−V0)/R2)dt

=1/C1/C2*∬((Vs−Vi)/R1/R2)dt2

=(Vs−Vi)/C1/C2/R1/R2*t2…(11)

【0045】

時刻t2から時刻t3までの期間は容量604の充電は停止する。この時の電圧Vdは次式(12)で表される。

Vd=V2=(Vs−Vi)/C1/C2/R1/R2*ΔT2…(12)

式(7)及び式(12)から次式(13)が導かれる。

Vd=2*T*L/C1/C2/R1/R2*Io…(13)

式(13)から、検出電圧Vdは駆動電流Ioに比例していることがわかる。これは、検出部60Bによって駆動電流Ioが間接的に検出されることを意味する。

【0046】

以上、本実施形態によると、第1の実施形態と同様に、特に検出抵抗を用いることなく、高レンジの駆動電流を低損失で検出することができる。そして、検出された駆動電流及び駆動電圧に基づいて、DC−DCコンバータの出力を適応制御することができる。

【0047】

なお、第1及び第2の実施形態において、保持部607は、制御信号CT2に代えて制御信号CT1がHレベルとなるごとに初期化されるようにしてもよい。また、制御信号CT1及びCT2ではなく、図2に示した時刻t2から時刻t3までの期間にHレベルとなる信号によって初期化されるようにしてもよい。

【0048】

(第3の実施形態)

図5は、第3の実施形態に係るDC−DCコンバータの構成を示す。本DC−DCコンバータは、インダクタ10、スイッチ20、ダイオード30、容量40、制御部50、及び検出部60Cを備えた昇圧コンバータである。以下、第1の実施形態と異なる点についてのみ説明する。

【0049】

検出部60Cは、OTA601及び602、容量603及び604、スイッチ605、606及び621、保持部607、比較器608、抵抗622及び623、RSラッチ624及び論理回路625を備えている。比較器608とRSラッチ624と論理回路625とでスイッチ制御部が構成されている。抵抗622及び623は直列接続され、入力電圧端と接地ノードとの間に設けられている。ここで、抵抗622及び623の抵抗値を等しく設定すると、その接続点電圧は入力電圧Viの半分となる。OTA601の反転入力端は接地ノードに接続され、非反転入力端には抵抗622及び623の接続点電圧が印加される。これにより、OTA601は、入力電圧Viに応じた電流を出力し、容量603を充電する。すなわち、抵抗622及び623とOTA601と容量603とで積分回路が構成されている。また、OTA602は、容量602の両端電圧に応じた電流を出力し、容量604を充電する。すなわち、OTA602と容量604とで積分回路が構成されている。

【0050】

スイッチ621は、OTA601の反転入力端と非反転入力端との間に設けられており、制御信号CT1の反転である/CT1に従って開閉動作をする。具体的には、スイッチ621は、制御信号CT2がHレベルのときに非導通状態となり、Lレベルのときに導通状態となる。スイッチ621が非導通状態にあるとき、OTA601は容量603を充電する。一方、スイッチ621が導通状態にあるとき、OTA601の差動入力はゼロとなり、容量603の充電が停止する。すなわち、スイッチ621が非導通状態にあるとき、OTA601を含む積分回路の積分動作が有効となり、スイッチ621が導通状態にあるとき、当該積分動作は無効となる。

【0051】

スイッチ605は、RSラッチ624のQ出力に従って開閉動作をする。RSラッチ624は、セット信号として論理回路625の出力を受け、リセット信号として制御信号CT1を受ける。論理回路625は、制御信号CT1の反転と制御信号CTとの論理積を出力する。したがって、スイッチ605は、制御信号CT2がHレベル、かつ、制御信号CT1がLレベルのときに導通状態となり、制御信号CT1がHレベルとなることによって非導通状態となる。

【0052】

保持部607は、容量604の電圧を保持し、検出電圧Vdとして出力する。保持部607の保持電圧は、制御信号CTがHレベルとなるごとに初期化される。

【0053】

次に、図6のタイミングチャートを参照しながら本DC−DCコンバータの動作について説明する。

【0054】

時刻t0において、制御信号CT1はHレベルとなる。これにより、導通状態となったスイッチ20を流れるインダクタ電流ILは式(1)に従って直線的に増加する。このとき、スイッチ606は導通状態となり、容量604はリフレッシュされ、電圧V2はゼロ(グランドレベル)となる。RSラッチ624はリセットされ、Q出力はLレベルとなり、スイッチ605は非導通状態となる。また、スイッチ621は非導通状態となり、容量603はVi/2*gm1で表される大きさの電流で充電され、電圧V1は次式(14)で表される。

V1=1/C1*∫(Vi/2*gm1)dt

=Vi/2/C1*gm1*t…(14)

ここで、電圧Vi/2は一定であるため、電圧V1は図6に示したように直線的に増加する。

【0055】

次に、時刻t1において、制御信号CT1はLレベルとなる。これにより、スイッチ20が非導通状態となり、ダイオード30を流れる電流Id(=インダクタ電流IL)は式(2)に従って直線的に減少する。このとき、スイッチ621は導通状態となり、OTA601の反転入力端と非反転入力端とが短絡される。これにより、容量603の充電が停止する。また、制御信号CT2がLレベルとなるため、RSラッチ624のQ出力は依然としてLレベルのままであり、スイッチ605は非導通状態を維持する。このときの電圧V1は、式(14)に時刻t0から時刻t1までの期間Tonを代入して、次式(15)で表される。

V1=Vi/2/C1*gm1*Ton…(15)

【0056】

また、時刻t1において、スイッチ606は非導通状態となる。したがって、容量604はV1*gm2で表される大きさの電流で充電され、電圧V2は次式(16)で表される。

V2=1/C2*∫(V1*gm2)dt

=V1/C2*gm2*t…(16)

ここで、電圧V1は一定であるため、電圧V2は図6に示したように直線的に増加する。

【0057】

次に、時刻t2において、制御信号CT2はHレベルとなる。これにより、RSラッチ624はセットされ、Q出力はHレベルとなる。したがって、スイッチ605は導通状態となり、容量603はリフレッシュされ、電圧V1はゼロとなる。また、OTA602の差動入力はゼロとなり、容量604の充電は停止する。このときの電圧Vdは、ダイオード30の導通期間をΔT(=t2−t1)とすると、次式(17)で表される。

Vd=V2=V1/C2*gm2*ΔT

=Vi/2/C1/C2*gm1*gm2*Ton*ΔT…(17)

【0058】

ここで、ΔI=Vi/L*Tonを式(6)に代入してΔIを消去すると次式(18)が導かれる。

Io=Vi/2/L/T*Ton*ΔT…(18)

ここで、スイッチング周期Tを一定とすると、式(17)及び式(18)から次式(19)が導かれる。

Vd=T*L/C1/C2*gm1*gm2*Io…(19)

式(19)から、検出電圧Vdは駆動電流Ioに比例していることがわかる。これは、検出部60Cによって駆動電流Ioが間接的に検出されることを意味する。

【0059】

以後、時刻t3において、制御信号CT1が再びHレベルとなり、上述した時刻t0以降の動作が繰り返される。制御信号CT1がHレベルとなることにより、保持部607は式(17)で表される電圧V2を保持する。

【0060】

図7は、図5に示したDC−DCコンバータの具体的な回路構成を示す。図7において、6011は抵抗622及び623の接続点電位が入力されるバッファ回路である。6012及び6013は直列接続された抵抗である。抵抗6012の一端は接地ノードに接続される。6014は、非反転入力端に抵抗6012及び6013の接続点電位が印加され、出力端に抵抗6013の他端が接続された演算増幅器である。6015は演算増幅器6014の出力端に接続された抵抗である。抵抗6015の他端は容量603の一端に接続されている。この接続点電位をV1とする。6016及び6017は直列接続された抵抗である。抵抗6016にはバッファ回路6011の出力電圧が印加される。抵抗6017にはバッファ回路6021の出力電圧(電圧V1)が印加される。図7においてOTA602に相当する部分は図4を参照して説明したとおりである。なお、図4に示したOTA602に相当する部分とは、抵抗6022の一端が接地ノードに接続されている点が異なる。

【0061】

上記構成のDC−DCコンバータのタイミングチャートは図6に示したとおりである。以下、図6のタイミングチャートを参照しながら図7に示したDC−DCコンバータの動作について説明する。ここで、抵抗6015の抵抗値をR1、抵抗6025の抵抗値をR2、抵抗622及び623の抵抗値をいずれもR3、抵抗6022、6023、6028及び6029の抵抗値をいずれもR4、抵抗6012、6013、6016及び6017の抵抗値をいずれもR5とする。

【0062】

時刻t0から時刻t1までの間、スイッチ621は非導通状態となる。これにより、抵抗622及び623の接続点には入力電圧Viを分圧した電圧Vi/2が発生し、バッファ回路6011に電圧Vi/2が入力される。演算増幅器6014の出力電圧をV5とすると、演算増幅器6014の非反転入力端電圧はV5/2となり、反転入力端電圧は(Vi/2+V1)/2となる。いわゆるイマジナリーショートにより演算増幅器6014はこれら電圧が等しくなるように動作し、電圧V5は次式(20)で表される。

V5=Vi/2+V1…(20)

したがって、容量603は(V5−V1)/R1=Vi/2/R1で表される電流で充電され、電圧V1は次式(21)で表される。

V1=1/C1*∫(Vi/2/R1)dt

=Vi/2/C1/R1*t…(21)

時刻t1における電圧V1は、式(21)にt=Tonを代入して次式(22)で表される。

V1=Vi/2/C1/R1*Ton…(22)

【0063】

次に、時刻t1から時刻t2までの間、スイッチ621は導通状態となり、抵抗622及び623の接続点電圧はほぼゼロとなる。これにより、演算増幅器6014の反転入力端電圧はV1/2となる。いわゆるイマジナリーショートにより演算増幅器6014は非反転入力端電圧がVc/2となるように動作する。これにより、出力端電圧V5=V1となり、電圧V1が維持される。

【0064】

また、この期間、スイッチ606は非導通状態となる。演算増幅器6024の出力端電圧をV4とすると、演算増幅器6024の非反転入力端電圧はV4/2となり、反転入力端電圧は(V1+V2)/2となる。いわゆるイマジナリーショートにより演算増幅器6024はこれら電圧が等しくなるように動作し、電圧V4は次式(23)で表される。

V4=V1+V2…(23)

したがって、容量604は(V4−V2)/R2=V1/R2で表される大きさの電流で充電され、電圧V2は次式(24)で表される。

V2=1/C2*∫(V1/R2)dt

=V1/C2/R2*t…(24)

【0065】

時刻t2から時刻t3までの間、スイッチ605は導通状態となる。これにより、容量603はリフレッシュされ、電圧V1はゼロとなり、演算増幅器6024の反転入力端電圧はV2/2となる。いわゆるイマジナリーショートにより演算増幅器6024は非反転入力端電圧がVc/2となるように動作する。これにより、出力端電圧V4=V2となり、電圧V2が維持される。また、容量604の充電は停止する。このときの電圧Vdは次式(25)で表される。

Vd=V2=V1/C2/R2*ΔT

=Vi/2/C1/C2/R1/R2*Ton*ΔT…(25)

式(18)及び式(25)から次式(16)が導かれる。

Vd=T*L/C1/C2/R1/R2*Io…(26)

式(26)から、検出電圧Vdは駆動電流Ioに比例していることがわかる。これは、検出部60Cによって駆動電流Ioが間接的に検出されることを意味する。

【0066】

以上、本実施形態によると、インダクタが充電されている間、その充電量に応じた電荷が第1の容量に充電され、その後、インダクタが放電している間、第1の容量に発生している電圧に応じた電流で第2の容量が充電される。これにより、第2の容量に、インダクタから電気エネルギーが放出される期間の2乗に比例する電圧、すなわち、駆動電流に比例する電圧が生じる。したがって、特に検出抵抗を用いることなく、高レンジの駆動電流を低損失で検出することができる。そして、検出された駆動電流及び駆動電圧に基づいて、DC−DCコンバータの出力を適応制御することができる。

【0067】

なお、スイッチ621は、OTA601と容量603との間に設けてもよい(図8参照)。この場合、スイッチ621は、制御信号CT1によって開閉動作が制御される。このように変更を加えても上述した効果が奏される。

【0068】

また、保持部607は、制御信号CT1に代えて制御信号CT2がHレベルとなるごとに初期化されるようにしてもよい。また、制御信号CT1及びCT2ではなく、図6に示した時刻t2から時刻t3までの期間にHレベルとなる信号によって初期化されるようにしてもよい。

【0069】

また、上記の各実施形態は昇圧型のDC−DCコンバータに関するものであるが、昇降圧型のDC−DCコンバータについても本発明により上述した効果が奏される。

【産業上の利用可能性】

【0070】

本発明に係るDC−DCコンバータは、低損失で高レンジの駆動電流を検出することができるため、有機ELパネルの駆動回路等として有用である。

【図面の簡単な説明】

【0071】

【図1】第1の実施形態に係るDC−DCコンバータの構成図である。

【図2】図1に示したDC−DCコンバータのタイミングチャートである。

【図3】第2の実施形態に係るDC−DCコンバータの構成図である。

【図4】図3に示したDC−DCコンバータの具体的な回路構成図である。

【図5】第3の実施形態に係るDC−DCコンバータの構成図である。

【図6】図5に示したDC−DCコンバータのタイミングチャートである。

【図7】図5に示したDC−DCコンバータの具体的な回路構成図である。

【図8】図5に示したDC−DCコンバータの変形例である。

【符号の説明】

【0072】

10 インダクタ

50 制御部

601 OTA(第1の演算相互演算コンダクタンス増幅器、第1の積分回路)

602 OTA(第2の演算相互演算コンダクタンス増幅器、第2の積分回路)

603 容量(第1の容量、第1の積分回路)

604 容量(第2の容量、第2の積分回路)

605 スイッチ(第1のスイッチ)

606 スイッチ(第2のスイッチ)

607 保持部

608 比較器(スイッチ制御部)

611 電流源(第1の電流源、第1の積分回路)

612 電流源(第2の電流源、第1の積分回路)

621 スイッチ(第3のスイッチ)

624 RSラッチ(スイッチ制御部)

625 論理回路(スイッチ制御部)

【技術分野】

【0001】

本発明は、DC−DCコンバータに関し、特に、電流不連続モードで動作する昇圧及び昇降圧コンバータに適した負荷電流検出に関するものである。

【背景技術】

【0002】

近年、携帯機器等の表示装置として有機ELパネルが多用されている。有機ELパネルは比較的高い電圧で駆動する必要があるため、駆動回路としてDC−DCコンバータ、特に、昇圧コンバータがよく用いられる。昇圧コンバータは、バッテリー等から供給される数V程度の低い入力電圧から10V以上の電圧を生成するものである。そして、有機ELパネルの特徴を十分に発揮させるためには、駆動電流を精度良く検出し、その検出結果に基づいてて駆動回路の電圧制御を行う必要がある。

【0003】

一般に、黒ラスタ表示時には有機ELパネルにはほとんど電流は流れていないが、画面の輝度を確保するために印加電圧を通常よりも高く設定することが行われる。しかし、有機ELパネルに過大な電流が流れ続けるとパネル寿命が著しく低下してしまうため、過電流が検出された場合には印加電圧を低下させるように制御することが好ましい。従来、有機ELパネルに過電流が流れるのを防止するために、信号ラインに挿入した検出抵抗の両端に生じる電圧から駆動電流を検出し、その検出結果に応じて有機ELパネルの駆動電圧及び駆動電流を制御する技術が知られている(例えば、特許文献1参照)。

【特許文献1】特開2001−110565号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかし、上記手法では、検出抵抗によって駆動電圧に損失が生じてしまう。損失低減のために検出抵抗の抵抗値を小さくすると、黒ラスタ表示のような軽負荷の場合に検出精度が確保できなくなるといった問題が生じる。逆に、軽負荷時の検出精度を向上させるために検出抵抗の抵抗値を大きくすると、重負荷時に多大な損失が発生してしまう。このため、有機ELパネルの駆動回路では、一般に、抵抗値が比較的小さな検出抵抗を設けて、重負荷時の駆動電流のみを検出するようになっている。

【0005】

上記問題に鑑み、本発明は、主に駆動回路として用いられるDC−DCコンバータについて、高レンジの駆動電流を低損失で検出することを課題とする。

【課題を解決するための手段】

【0006】

上記課題を解決するために本発明が講じた手段は、インダクタを備えたDC−DCコンバータとして、前記インダクタの両端電圧を積分する第1の積分回路と、前記第1の積分回路の出力電圧を積分する第2の積分回路と、前記第2の積分回路の出力電圧を保持する保持部と、前記保持部の出力電圧に基づいて前記インダクタの充放電制御を行う制御部とを備えたものとする。

【0007】

これによると、制御部の制御によりインダクタに充電された電気エネルギーに対応する電圧が第1及び第2の積分回路によって二重積分され、当該積分結果が保持部に保持され、当該保持電圧に基づいて制御部によってインダクタの充放電制御が行われる。当該二重積分によって得られる電圧は本DC−DCコンバータから出力される駆動電流に比例しており、これにより、特に検出抵抗を用いなくとも駆動電流を検出することができる。

【0008】

具体的には、前記第1の積分回路は、積分電荷を蓄積する第1の容量を有するものであり、前記第2の積分回路は、積分電荷を蓄積する第2の容量を有するものである。そして、上記のDC−DCコンバータは、前記第1の容量に並列に設けられた第1のスイッチと、前記第2の容量に並列に設けられた第2のスイッチと、前記インダクタの出力電圧と当該DC−DCコンバータの出力電圧とを受け、前記インダクタの出力電圧が当該DC−DCコンバータの出力電圧よりも小さいとき、前記第1のスイッチを導通状態にする一方、それ以外のとき、前記第1のスイッチを非導通状態にするスイッチ制御部とをさらに備えている。ここで、前記制御部は、前記インダクタの充電制御を行うとき、前記第2のスイッチを導通状態にする一方、前記インダクタの放電制御を行うとき、前記第2のスイッチを非導通状態にするものである。

【0009】

より具体的には、前記第1の積分回路は、前記インダクタの入力電圧と出力電圧との差分に応じた電流を出力する演算相互コンダクタンス増幅器を有するものである。また、前記第1の容量は、前記演算相互コンダクタンス増幅器から出力された電流によって充電されるものである。

【0010】

また、より具体的には、前記第1の積分回路は、前記インダクタの出力電圧を電源電圧とし、前記第1の容量に接続された第1の電流源と、前記インダクタの入力電圧によってバイアス制御され、前記第1の電流源から電流を引き抜く第2の電流源とを有するものである。

【0011】

一方、本発明が講じた手段は、インダクタを備えたDC−DCコンバータとして、前記インダクタの入力電圧を積分する第1の積分回路と、前記第1の積分回路の出力電圧を積分する第2の積分回路と、前記第2の積分回路の出力電圧を保持する保持部と、前記保持部の出力電圧に基づいて前記インダクタの充放電制御を行う制御部とを備えたものとする。

【0012】

これによると、インダクタの入力電圧が第1の積分回路で積分され、当該積分結果がさらに第2の積分回路によって積分され、結局、インダクタに充電されることとなる電気エネルギーに対応する電圧が第1及び第2の積分回路によって二重積分され、当該積分結果が保持部に保持され、当該保持電圧に基づいて制御部によってインダクタの充放電制御が行われる。当該二重積分によって得られる電圧は本DC−DCコンバータから出力される駆動電流に比例しており、これにより、特に検出抵抗を用いなくとも駆動電流を検出することができる。

【0013】

具体的には、前記第1の積分回路は、積分電荷を蓄積する第1の容量を有するものであり、前記第2の積分回路は、積分電荷を蓄積する第2の容量を有するものである。そして、上記のDC−DCコンバータは、前記第1の容量に並列に設けられた第1のスイッチと、前記第2の容量に並列に設けられた第2のスイッチと、前記第1の積分回路の積分動作の有効及び無効を切り替える第3のスイッチと、前記インダクタの出力電圧と当該DC−DCコンバータの出力電圧と前記制御部の出力とを受け、前記インダクタの出力電圧が当該DC−DCコンバータの出力電圧よりも小さく、かつ、前記制御部によって前記インダクタの放電制御が行われているとき、前記第1のスイッチを導通状態にする一方、それ以外のとき、前記第1のスイッチを非導通状態にするスイッチ制御部とをさらに備えている。ここで、前記制御部は、前記インダクタの充電制御を行うとき、前記第2のスイッチを導通状態にするとともに前記第3のスイッチを前記第1の容量が充電される第1の状態にする一方、前記インダクタの放電制御を行うとき、前記第2のスイッチを非導通状態にするとともに前記第3のスイッチを前記第1の容量の充電が停止する第2の状態にするものである。

【0014】

より具体的には、前記第1の積分回路は、前記インダクタの入力電圧と所定電圧との差分に応じた電流を出力する演算相互コンダクタンス増幅器を有するものである。また、前記第1の容量は、前記演算相互コンダクタンス増幅器から出力された電流によって充電されるものである。

【0015】

さらに具体的には、前記第3のスイッチは、前記演算相互コンダクタンス増幅器の反転入力端と非反転入力端との間に設けられたものである。そして、前記第1の状態は、前記反転入力端と前記非反転入力端とを開放する状態であり、前記第2の状態は、前記反転入力端と前記非反転入力端とを短絡する状態である。

【0016】

また、さらに具体的には、前記第3のスイッチは、前記演算相互コンダクタンス増幅器の出力端と前記第1の容量との間に設けられたものである。そして、前記第1の状態は、導通状態であり、前記第2の状態は、非導通状態である。

【0017】

また、具体的には、前記第2の積分回路は、前記第1の容量の両端電圧に応じた電流を出力する演算相互コンダクタンス増幅器を有するものであり、前記第2の容量は、前記演算相互コンダクタンス増幅器から出力された電流によって充電されるものである。

【0018】

また、好ましくは、前記保持部は、前記制御部及びスイッチ制御部のいずれか一方の制御によって初期化されるものとする。

【発明の効果】

【0019】

以上のように本発明によると、DC−DCコンバータについて、高レンジの駆動電流を低損失で検出することができる。

【発明を実施するための最良の形態】

【0020】

以下、本発明を実施するための最良の形態について、図面を参照しながら説明する。

【0021】

(第1の実施形態)

図1は、第1の実施形態に係るDC−DCコンバータの構成を示す。本DC−DCコンバータは、インダクタ10、スイッチ20、ダイオード30、容量40、制御部50、及び検出部60Aを備えた昇圧コンバータである。

【0022】

インダクタ10は、バッテリー等の入力電圧Viを受け、スイッチ20の開閉動作に応じて充放電を繰り返す。この充放電電流はダイオード30によって整流され、容量40で平滑化されて出力電圧Voとなる。制御部50は、出力電圧Vo及び検出部60Aから出力された検出電圧Vdに応じて制御信号CT1の論理レベルを変化させて適応的にスイッチ20の開閉動作を制御する。詳しくは後述するが、検出電圧Vdは本DC−DCコンバータの出力電流(駆動電流)Ioを間接的に検出したものである。これにより、本DC−DCコンバータでは、出力電圧Vo及び出力電流Ioに基づいてフィードバック制御をすることができるようになっている。

【0023】

検出部60Aは、演算相互コンダクタンス増幅器(OTA)601及び602、容量603及び604、スイッチ605及び606、保持部607、及びスイッチ制御部としての比較器608を備えている。OTA601は、インダクタ10の両端電圧、すなわち、入力電圧Vi及びスイッチ電圧(インダクタ10の出力電圧)Vsの差分に応じた電流を出力し、容量603を充電する。すなわち、OTA601と容量603とで積分回路が構成されている。また、OTA602は、容量602の両端電圧に応じた電流を出力し、容量604を充電する。すなわち、OTA602と容量604とで積分回路が構成されている。

【0024】

比較器608は、スイッチ電圧Vs及び出力電圧Voを受け、これら電圧の大小関係に応じて制御信号CT2を出力する。具体的には、比較器608は、スイッチ電圧Vsが出力電圧Voよりも小さい(又は以下)のとき、制御信号CT2をHレベルにする。一方、これ以外のとき、制御信号CT2をLレベルにする。

【0025】

スイッチ605は、容量603に並列に設けられており、制御信号CT2に従って開閉動作をする。具体的には、スイッチ605は、制御信号CT2がHレベルのときに導通状態となり、Lレベルのときに非導通状態となる。スイッチ605が導通状態にあるとき、容量603がリフレッシュされるとともにOTA602の差動入力がゼロとなる。これにより、OTA602の出力電流もまたゼロとなり、容量604の充電が停止する。

【0026】

スイッチ606は、容量604に並列に設けられており、制御信号CT1に従って開閉動作をする。具体的には、スイッチ606は、制御信号CT1がHレベルのときに導通状態となり、Lレベルのときに非導通状態となる。スイッチ606が導通状態にあるとき、容量604がリフレッシュされるとともに保持部607の入力がゼロとなる。

【0027】

保持部607は、容量604の電圧を保持し、検出電圧Vdとして出力する。保持部607の保持電圧は、制御信号CT2がHレベルとなるごとに初期化される。

【0028】

次に、図2のタイミングチャートを参照しながら本DC−DCコンバータの動作について説明する。ここで、図1に示したように、インダクタ10のインダクタンスをL、インダクタ10に流れる電流をIL、ダイオード30に流れる電流をId、容量603の電圧をV1、容量604の電圧をV2、OTA601の相互コンダクタンスをgm1、及びOTA602の相互コンダクタンスをgm2とする。

【0029】

時刻t0において、制御信号CT1はHレベルとなる。これにより、スイッチ20は導通状態となり、インダクタ10に入力電圧Viが印加される。すなわち、インダクタ10の充電制御が開始される。この結果、スイッチ20を流れるインダクタ電流ILは次式(1)に従って直線的に増加する。

IL=Vi/L*t…(1)

【0030】

また、スイッチ606は導通状態となり、容量604はリフレッシュされ、電圧V2はゼロ(グランドレベル)となる。また、スイッチ電圧Vsはほぼゼロであるため、制御信号CT2はHレベルとなる。これにより、スイッチ605は導通状態となり、容量603はリフレッシュされ、電圧V1はゼロとなる。

【0031】

次に、時刻t1において、制御信号CT1はLレベルとなる。これにより、スイッチ20が非導通状態となり、インダクタ10にはスイッチ電圧Vsと入力電圧Viとの差分電圧(Vi−Vs)が印加される。すなわち、インダクタ10の放電制御が開始される。この結果、ダイオード30を流れる電流Id(=インダクタ電流IL)は次式(2)に従って直線的に減少する。電流Idは容量40によって平滑化され、出力電圧Voが生成される。

IL=Id=ΔI−(Vs−Vi)/L*t…(2)

【0032】

また、時刻t1において、スイッチ電圧Vsは高電位となり、制御信号CT2はLレベルとなる。これにより、スイッチ605は非導通状態となり、容量603は(Vs−Vi)*gm1で表される大きさの電流で充電され、電圧V1は次式(3)で表される。

V1=1/C1*∫((Vs−Vi)*gm1)dt

=(Vs−Vi)/C1*gm1*t…(3)

ここで、差分電圧(Vs−Vi)がほぼ一定であれば、電圧V1は図2に示したように直線的に増加する。

【0033】

また、スイッチ606は非導通状態となり、容量604はV1*gm2で表される大きさの電流で充電され、電圧V2は次式(4)で表される。

V2=1/C2*∫(V1*gm2)dt

=1/C1/C2*∬((Vs−Vi)*gm1*gm2)dt2

=(Vs−Vi)/C1/C2*gm1*gm2*t2…(4)

ここで、差分電圧(Vs−Vi)がほぼ一定であれば、電圧V2は図2に示したように2次関数的に増加する。

【0034】

次に、時刻t2において、インダクタ電流IL、すなわち、ダイオード電流Idはゼロとなり、ダイオード30はオフ状態となる。これにより、インダクタ10の両端電圧は減衰振動しながらゼロとなる。同様に、スイッチ電圧Vsもまた減衰振動しながら入力電圧Viとなる。この結果、制御信号CT2はHレベルとなる。これにより、スイッチ605は導通状態となり、容量603はリフレッシュされ、電圧V1はゼロとなる。また、OTA602の差動入力はゼロとなり、容量604の充電は停止する。この時の電圧V2は、ダイオード30の導通期間をΔT(=t2−t1)とすると、次式(5)で表される。

V2=(Vs−Vi)/C1/C2*gm1*gm2*ΔT2…(5)

【0035】

また、制御信号CT2がHレベルとなることにより、保持部607はこの時の電圧V2を保持する。したがって、保持部607から出力される検出電圧Vdは式(5)で表される電圧V2と等しくなる。ここで、駆動電流Ioは、ダイオード電流Idを平滑化(平均化)したものであるから、スイッチ20のスイッチング周期をTとして次式(6)で表される。

Io=ΔI/2/T*ΔT…(6)

式(6)及び式(2)からΔIを消去すると次式(7)が導かれる。

Io=(Vs−Vi)/2/T/L*ΔT2…(7)

ここで、スイッチング周期Tを一定とすると、式(5)及び式(7)から次式(8)が導かれる。

Vd=2*T*L/C1/C2*gm1*gm2*Io…(8)

式(8)から、検出電圧Vdは駆動電流Ioに比例していることがわかる。これは、検出部60Aによって駆動電流Ioが間接的に検出されることを意味する。

【0036】

以後、時刻t3において、制御信号CT1が再びHレベルとなり、上述した時刻t0以降の動作が繰り返される。

【0037】

以上、本実施形態によると、ダイオードの通電期間に、インダクタの両端電圧に応じた電流で第1の容量が充電され、同時に第1の容量に生じる電圧に応じた電流で第2の容量が充電される。これにより、第2の容量に、インダクタから電気エネルギーが放出される期間の2乗に比例する電圧、すなわち、駆動電流に比例する電圧が生じる。したがって、特に検出抵抗を用いることなく、高レンジの駆動電流を低損失で検出することができる。そして、検出された駆動電流及び駆動電圧に基づいて、DC−DCコンバータの出力を適応制御することができる。

【0038】

なお、保持部607は、制御信号CT2に代えて制御信号CT1がHレベルとなるごとに初期化されるようにしてもよい。また、制御信号CT1及びCT2ではなく、図2に示した時刻t2から時刻t3までの期間にHレベルとなる信号によって初期化されるようにしてもよい。

【0039】

(第2の実施形態)

図3は、第2の実施形態に係るDC−DCコンバータの構成を示す。本DC−DCコンバータは、図1に示したDC−DCコンバータにおけるOTA601に代えて電流源611及び612を備えている。以下、第1の実施形態に係るDC−DCコンバータと異なる点についてのみ説明する。

【0040】

電流源611は、スイッチ電圧Vsを電源とする定電流源であり、容量603に接続されている。電流源612は、電流源611と容量603との接続点に接続され、電流源611から電流を引き抜く定電流源である。電流源612は、入力電圧Viによってバイアス制御される。

【0041】

図4は、図3に示したDC−DCコンバータの具体的な回路構成を示す。図4において、6121は入力電圧端に接続された抵抗、6122及び6123は電流ミラー回路を構成するNMOSトランジスタである。抵抗6121に流れる電流と等しい電流がトランジスタ6123に流れる。6111及び6112は電流ミラー回路を構成するPMOSトランジスタである。各トランジスタのソースにはスイッチ電圧Vsが印加される。6113はトランジスタ6111のゲート及びドレインと接地ノードとの間に接続された抵抗である。トランジスタ6123及び6112のドレインはいずれも容量603の一端に接続される。この接続点電位をV1とする。容量603の他端は電圧源613に接続される。なお、電圧源613の電圧V0はトランジスタ6122及び6123が飽和しない電圧レベルに設定される。6021は電圧V1が入力されるバッファ回路である。6022及び6023は直列接続された抵抗である。抵抗6022の一端には電圧V0が印加される。6024は、非反転入力端に抵抗6022及び6023の接続点電位が印加され、出力端に抵抗6023の他端が接続された演算増幅器である。6025は演算増幅器6024の出力端に接続された抵抗である。6026は、容量604及びトランジスタ6025の接続点電位であるV2が入力されるバッファ回路である。6027及び6028は直列接続された抵抗である。抵抗6028にはバッファ回路6021の出力電圧(電圧V1)が印加される。抵抗6029にはバッファ回路6026の出力電圧(電圧V2)が印加される。

【0042】

上記構成のDC−DCコンバータのタイミングチャートは図2に示したとおりである。以下、図2のタイミングチャートを参照しながら図4に示したDC−DCコンバータの動作について説明する。ここで、抵抗6113及び6121の抵抗値をいずれもR1、抵抗6025の抵抗値をR2、抵抗6022、6023、6028及び6029の抵抗値をいずれもR4とする。

【0043】

時刻t1から時刻t2までの間、容量603は(Vs−Vt)/R1−(Vi−Vt)/R1=(Vs−Vi)/R1で表される大きさの電流(ただし、Vtはトランジスタ6112及び6123のソース・ゲート間電圧である。)で充電され、電圧V1は次式(9)で表される。

V1=1/C1*∫((Vs−Vi)/R1)dt+V0

=(Vs−Vi)/C1/R1*t…(9)

【0044】

また、容量604は抵抗6025を流れる電流で充電される。演算増幅器6024の出力端電圧をV4とすると、演算増幅器6024の非反転入力端電圧は(V4+V0)/2となり、反転入力端電圧は(V1+V2)/2となる。いわゆるイマジナリーショートにより演算増幅器6024はこれら電圧が等しくなるように動作し、電圧V4は次式(10)で表される。

V4=V1+V2−V0…(10)

したがって、容量604はV4−V2=(V1−V0)/R2で表される大きさの電流で充電され、電圧V2は次式(11)で表される。

V2=1/C2*∫((V1−V0)/R2)dt

=1/C1/C2*∬((Vs−Vi)/R1/R2)dt2

=(Vs−Vi)/C1/C2/R1/R2*t2…(11)

【0045】

時刻t2から時刻t3までの期間は容量604の充電は停止する。この時の電圧Vdは次式(12)で表される。

Vd=V2=(Vs−Vi)/C1/C2/R1/R2*ΔT2…(12)

式(7)及び式(12)から次式(13)が導かれる。

Vd=2*T*L/C1/C2/R1/R2*Io…(13)

式(13)から、検出電圧Vdは駆動電流Ioに比例していることがわかる。これは、検出部60Bによって駆動電流Ioが間接的に検出されることを意味する。

【0046】

以上、本実施形態によると、第1の実施形態と同様に、特に検出抵抗を用いることなく、高レンジの駆動電流を低損失で検出することができる。そして、検出された駆動電流及び駆動電圧に基づいて、DC−DCコンバータの出力を適応制御することができる。

【0047】

なお、第1及び第2の実施形態において、保持部607は、制御信号CT2に代えて制御信号CT1がHレベルとなるごとに初期化されるようにしてもよい。また、制御信号CT1及びCT2ではなく、図2に示した時刻t2から時刻t3までの期間にHレベルとなる信号によって初期化されるようにしてもよい。

【0048】

(第3の実施形態)

図5は、第3の実施形態に係るDC−DCコンバータの構成を示す。本DC−DCコンバータは、インダクタ10、スイッチ20、ダイオード30、容量40、制御部50、及び検出部60Cを備えた昇圧コンバータである。以下、第1の実施形態と異なる点についてのみ説明する。

【0049】

検出部60Cは、OTA601及び602、容量603及び604、スイッチ605、606及び621、保持部607、比較器608、抵抗622及び623、RSラッチ624及び論理回路625を備えている。比較器608とRSラッチ624と論理回路625とでスイッチ制御部が構成されている。抵抗622及び623は直列接続され、入力電圧端と接地ノードとの間に設けられている。ここで、抵抗622及び623の抵抗値を等しく設定すると、その接続点電圧は入力電圧Viの半分となる。OTA601の反転入力端は接地ノードに接続され、非反転入力端には抵抗622及び623の接続点電圧が印加される。これにより、OTA601は、入力電圧Viに応じた電流を出力し、容量603を充電する。すなわち、抵抗622及び623とOTA601と容量603とで積分回路が構成されている。また、OTA602は、容量602の両端電圧に応じた電流を出力し、容量604を充電する。すなわち、OTA602と容量604とで積分回路が構成されている。

【0050】

スイッチ621は、OTA601の反転入力端と非反転入力端との間に設けられており、制御信号CT1の反転である/CT1に従って開閉動作をする。具体的には、スイッチ621は、制御信号CT2がHレベルのときに非導通状態となり、Lレベルのときに導通状態となる。スイッチ621が非導通状態にあるとき、OTA601は容量603を充電する。一方、スイッチ621が導通状態にあるとき、OTA601の差動入力はゼロとなり、容量603の充電が停止する。すなわち、スイッチ621が非導通状態にあるとき、OTA601を含む積分回路の積分動作が有効となり、スイッチ621が導通状態にあるとき、当該積分動作は無効となる。

【0051】

スイッチ605は、RSラッチ624のQ出力に従って開閉動作をする。RSラッチ624は、セット信号として論理回路625の出力を受け、リセット信号として制御信号CT1を受ける。論理回路625は、制御信号CT1の反転と制御信号CTとの論理積を出力する。したがって、スイッチ605は、制御信号CT2がHレベル、かつ、制御信号CT1がLレベルのときに導通状態となり、制御信号CT1がHレベルとなることによって非導通状態となる。

【0052】

保持部607は、容量604の電圧を保持し、検出電圧Vdとして出力する。保持部607の保持電圧は、制御信号CTがHレベルとなるごとに初期化される。

【0053】

次に、図6のタイミングチャートを参照しながら本DC−DCコンバータの動作について説明する。

【0054】

時刻t0において、制御信号CT1はHレベルとなる。これにより、導通状態となったスイッチ20を流れるインダクタ電流ILは式(1)に従って直線的に増加する。このとき、スイッチ606は導通状態となり、容量604はリフレッシュされ、電圧V2はゼロ(グランドレベル)となる。RSラッチ624はリセットされ、Q出力はLレベルとなり、スイッチ605は非導通状態となる。また、スイッチ621は非導通状態となり、容量603はVi/2*gm1で表される大きさの電流で充電され、電圧V1は次式(14)で表される。

V1=1/C1*∫(Vi/2*gm1)dt

=Vi/2/C1*gm1*t…(14)

ここで、電圧Vi/2は一定であるため、電圧V1は図6に示したように直線的に増加する。

【0055】

次に、時刻t1において、制御信号CT1はLレベルとなる。これにより、スイッチ20が非導通状態となり、ダイオード30を流れる電流Id(=インダクタ電流IL)は式(2)に従って直線的に減少する。このとき、スイッチ621は導通状態となり、OTA601の反転入力端と非反転入力端とが短絡される。これにより、容量603の充電が停止する。また、制御信号CT2がLレベルとなるため、RSラッチ624のQ出力は依然としてLレベルのままであり、スイッチ605は非導通状態を維持する。このときの電圧V1は、式(14)に時刻t0から時刻t1までの期間Tonを代入して、次式(15)で表される。

V1=Vi/2/C1*gm1*Ton…(15)

【0056】

また、時刻t1において、スイッチ606は非導通状態となる。したがって、容量604はV1*gm2で表される大きさの電流で充電され、電圧V2は次式(16)で表される。

V2=1/C2*∫(V1*gm2)dt

=V1/C2*gm2*t…(16)

ここで、電圧V1は一定であるため、電圧V2は図6に示したように直線的に増加する。

【0057】

次に、時刻t2において、制御信号CT2はHレベルとなる。これにより、RSラッチ624はセットされ、Q出力はHレベルとなる。したがって、スイッチ605は導通状態となり、容量603はリフレッシュされ、電圧V1はゼロとなる。また、OTA602の差動入力はゼロとなり、容量604の充電は停止する。このときの電圧Vdは、ダイオード30の導通期間をΔT(=t2−t1)とすると、次式(17)で表される。

Vd=V2=V1/C2*gm2*ΔT

=Vi/2/C1/C2*gm1*gm2*Ton*ΔT…(17)

【0058】

ここで、ΔI=Vi/L*Tonを式(6)に代入してΔIを消去すると次式(18)が導かれる。

Io=Vi/2/L/T*Ton*ΔT…(18)

ここで、スイッチング周期Tを一定とすると、式(17)及び式(18)から次式(19)が導かれる。

Vd=T*L/C1/C2*gm1*gm2*Io…(19)

式(19)から、検出電圧Vdは駆動電流Ioに比例していることがわかる。これは、検出部60Cによって駆動電流Ioが間接的に検出されることを意味する。

【0059】

以後、時刻t3において、制御信号CT1が再びHレベルとなり、上述した時刻t0以降の動作が繰り返される。制御信号CT1がHレベルとなることにより、保持部607は式(17)で表される電圧V2を保持する。

【0060】

図7は、図5に示したDC−DCコンバータの具体的な回路構成を示す。図7において、6011は抵抗622及び623の接続点電位が入力されるバッファ回路である。6012及び6013は直列接続された抵抗である。抵抗6012の一端は接地ノードに接続される。6014は、非反転入力端に抵抗6012及び6013の接続点電位が印加され、出力端に抵抗6013の他端が接続された演算増幅器である。6015は演算増幅器6014の出力端に接続された抵抗である。抵抗6015の他端は容量603の一端に接続されている。この接続点電位をV1とする。6016及び6017は直列接続された抵抗である。抵抗6016にはバッファ回路6011の出力電圧が印加される。抵抗6017にはバッファ回路6021の出力電圧(電圧V1)が印加される。図7においてOTA602に相当する部分は図4を参照して説明したとおりである。なお、図4に示したOTA602に相当する部分とは、抵抗6022の一端が接地ノードに接続されている点が異なる。

【0061】

上記構成のDC−DCコンバータのタイミングチャートは図6に示したとおりである。以下、図6のタイミングチャートを参照しながら図7に示したDC−DCコンバータの動作について説明する。ここで、抵抗6015の抵抗値をR1、抵抗6025の抵抗値をR2、抵抗622及び623の抵抗値をいずれもR3、抵抗6022、6023、6028及び6029の抵抗値をいずれもR4、抵抗6012、6013、6016及び6017の抵抗値をいずれもR5とする。

【0062】

時刻t0から時刻t1までの間、スイッチ621は非導通状態となる。これにより、抵抗622及び623の接続点には入力電圧Viを分圧した電圧Vi/2が発生し、バッファ回路6011に電圧Vi/2が入力される。演算増幅器6014の出力電圧をV5とすると、演算増幅器6014の非反転入力端電圧はV5/2となり、反転入力端電圧は(Vi/2+V1)/2となる。いわゆるイマジナリーショートにより演算増幅器6014はこれら電圧が等しくなるように動作し、電圧V5は次式(20)で表される。

V5=Vi/2+V1…(20)

したがって、容量603は(V5−V1)/R1=Vi/2/R1で表される電流で充電され、電圧V1は次式(21)で表される。

V1=1/C1*∫(Vi/2/R1)dt

=Vi/2/C1/R1*t…(21)

時刻t1における電圧V1は、式(21)にt=Tonを代入して次式(22)で表される。

V1=Vi/2/C1/R1*Ton…(22)

【0063】

次に、時刻t1から時刻t2までの間、スイッチ621は導通状態となり、抵抗622及び623の接続点電圧はほぼゼロとなる。これにより、演算増幅器6014の反転入力端電圧はV1/2となる。いわゆるイマジナリーショートにより演算増幅器6014は非反転入力端電圧がVc/2となるように動作する。これにより、出力端電圧V5=V1となり、電圧V1が維持される。

【0064】

また、この期間、スイッチ606は非導通状態となる。演算増幅器6024の出力端電圧をV4とすると、演算増幅器6024の非反転入力端電圧はV4/2となり、反転入力端電圧は(V1+V2)/2となる。いわゆるイマジナリーショートにより演算増幅器6024はこれら電圧が等しくなるように動作し、電圧V4は次式(23)で表される。

V4=V1+V2…(23)

したがって、容量604は(V4−V2)/R2=V1/R2で表される大きさの電流で充電され、電圧V2は次式(24)で表される。

V2=1/C2*∫(V1/R2)dt

=V1/C2/R2*t…(24)

【0065】

時刻t2から時刻t3までの間、スイッチ605は導通状態となる。これにより、容量603はリフレッシュされ、電圧V1はゼロとなり、演算増幅器6024の反転入力端電圧はV2/2となる。いわゆるイマジナリーショートにより演算増幅器6024は非反転入力端電圧がVc/2となるように動作する。これにより、出力端電圧V4=V2となり、電圧V2が維持される。また、容量604の充電は停止する。このときの電圧Vdは次式(25)で表される。

Vd=V2=V1/C2/R2*ΔT

=Vi/2/C1/C2/R1/R2*Ton*ΔT…(25)

式(18)及び式(25)から次式(16)が導かれる。

Vd=T*L/C1/C2/R1/R2*Io…(26)

式(26)から、検出電圧Vdは駆動電流Ioに比例していることがわかる。これは、検出部60Cによって駆動電流Ioが間接的に検出されることを意味する。

【0066】

以上、本実施形態によると、インダクタが充電されている間、その充電量に応じた電荷が第1の容量に充電され、その後、インダクタが放電している間、第1の容量に発生している電圧に応じた電流で第2の容量が充電される。これにより、第2の容量に、インダクタから電気エネルギーが放出される期間の2乗に比例する電圧、すなわち、駆動電流に比例する電圧が生じる。したがって、特に検出抵抗を用いることなく、高レンジの駆動電流を低損失で検出することができる。そして、検出された駆動電流及び駆動電圧に基づいて、DC−DCコンバータの出力を適応制御することができる。

【0067】

なお、スイッチ621は、OTA601と容量603との間に設けてもよい(図8参照)。この場合、スイッチ621は、制御信号CT1によって開閉動作が制御される。このように変更を加えても上述した効果が奏される。

【0068】

また、保持部607は、制御信号CT1に代えて制御信号CT2がHレベルとなるごとに初期化されるようにしてもよい。また、制御信号CT1及びCT2ではなく、図6に示した時刻t2から時刻t3までの期間にHレベルとなる信号によって初期化されるようにしてもよい。

【0069】

また、上記の各実施形態は昇圧型のDC−DCコンバータに関するものであるが、昇降圧型のDC−DCコンバータについても本発明により上述した効果が奏される。

【産業上の利用可能性】

【0070】

本発明に係るDC−DCコンバータは、低損失で高レンジの駆動電流を検出することができるため、有機ELパネルの駆動回路等として有用である。

【図面の簡単な説明】

【0071】

【図1】第1の実施形態に係るDC−DCコンバータの構成図である。

【図2】図1に示したDC−DCコンバータのタイミングチャートである。

【図3】第2の実施形態に係るDC−DCコンバータの構成図である。

【図4】図3に示したDC−DCコンバータの具体的な回路構成図である。

【図5】第3の実施形態に係るDC−DCコンバータの構成図である。

【図6】図5に示したDC−DCコンバータのタイミングチャートである。

【図7】図5に示したDC−DCコンバータの具体的な回路構成図である。

【図8】図5に示したDC−DCコンバータの変形例である。

【符号の説明】

【0072】

10 インダクタ

50 制御部

601 OTA(第1の演算相互演算コンダクタンス増幅器、第1の積分回路)

602 OTA(第2の演算相互演算コンダクタンス増幅器、第2の積分回路)

603 容量(第1の容量、第1の積分回路)

604 容量(第2の容量、第2の積分回路)

605 スイッチ(第1のスイッチ)

606 スイッチ(第2のスイッチ)

607 保持部

608 比較器(スイッチ制御部)

611 電流源(第1の電流源、第1の積分回路)

612 電流源(第2の電流源、第1の積分回路)

621 スイッチ(第3のスイッチ)

624 RSラッチ(スイッチ制御部)

625 論理回路(スイッチ制御部)

【特許請求の範囲】

【請求項1】

インダクタを備えたDC−DCコンバータであって、

前記インダクタの両端電圧を積分する第1の積分回路と、

前記第1の積分回路の出力電圧を積分する第2の積分回路と、

前記第2の積分回路の出力電圧を保持する保持部と、

前記保持部の出力電圧に基づいて前記インダクタの充放電制御を行う制御部とを備えた

ことを特徴とするDC−DCコンバータ。

【請求項2】

請求項1に記載のDC−DCコンバータにおいて、

前記第1の積分回路は、積分電荷を蓄積する第1の容量を有するものであり、

前記第2の積分回路は、積分電荷を蓄積する第2の容量を有するものであり、

当該DC−DCコンバータは、

前記第1の容量に並列に設けられた第1のスイッチと、

前記第2の容量に並列に設けられた第2のスイッチと、

前記インダクタの出力電圧と当該DC−DCコンバータの出力電圧とを受け、前記インダクタの出力電圧が当該DC−DCコンバータの出力電圧よりも小さいとき、前記第1のスイッチを導通状態にする一方、それ以外のとき、前記第1のスイッチを非導通状態にするスイッチ制御部とを備え、

前記制御部は、前記インダクタの充電制御を行うとき、前記第2のスイッチを導通状態にする一方、前記インダクタの放電制御を行うとき、前記第2のスイッチを非導通状態にするものである

ことを特徴とするDC−DCコンバータ。

【請求項3】

請求項2に記載のDC−DCコンバータにおいて、

前記第1の積分回路は、前記インダクタの入力電圧と出力電圧との差分に応じた電流を出力する演算相互コンダクタンス増幅器を有するものであり、

前記第1の容量は、前記演算相互コンダクタンス増幅器から出力された電流によって充電されるものである

ことを特徴とするDC−DCコンバータ。

【請求項4】

請求項2に記載のDC−DCコンバータにおいて、

前記第1の積分回路は、

前記インダクタの出力電圧を電源電圧とし、前記第1の容量に接続された第1の電流源と、

前記インダクタの入力電圧によってバイアス制御され、前記第1の電流源から電流を引き抜く第2の電流源とを有するものである

ことを特徴とするDC−DCコンバータ。

【請求項5】

インダクタを備えたDC−DCコンバータであって、

前記インダクタの入力電圧を積分する第1の積分回路と、

前記第1の積分回路の出力電圧を積分する第2の積分回路と、

前記第2の積分回路の出力電圧を保持する保持部と、

前記保持部の出力電圧に基づいて前記インダクタの充放電制御を行う制御部とを備えた

ことを特徴とするDC−DCコンバータ。

【請求項6】

請求項5に記載のDC−DCコンバータにおいて、

前記第1の積分回路は、積分電荷を蓄積する第1の容量を有するものであり、

前記第2の積分回路は、積分電荷を蓄積する第2の容量を有するものであり、

当該DC−DCコンバータは、

前記第1の容量に並列に設けられた第1のスイッチと、

前記第2の容量に並列に設けられた第2のスイッチと、

前記第1の積分回路の積分動作の有効及び無効を切り替える第3のスイッチと、

前記インダクタの出力電圧と当該DC−DCコンバータの出力電圧と前記制御部の出力とを受け、前記インダクタの出力電圧が当該DC−DCコンバータの出力電圧よりも小さく、かつ、前記制御部によって前記インダクタの放電制御が行われているとき、前記第1のスイッチを導通状態にする一方、それ以外のとき、前記第1のスイッチを非導通状態にするスイッチ制御部とを備え、

前記制御部は、前記インダクタの充電制御を行うとき、前記第2のスイッチを導通状態にするとともに前記第3のスイッチを前記第1の容量が充電される第1の状態にする一方、前記インダクタの放電制御を行うとき、前記第2のスイッチを非導通状態にするとともに前記第3のスイッチを前記第1の容量の充電が停止する第2の状態にするものである

ことを特徴とするDC−DCコンバータ。

【請求項7】

請求項6に記載のDC−DCコンバータにおいて、

前記第1の積分回路は、前記インダクタの入力電圧と所定電圧との差分に応じた電流を出力する演算相互コンダクタンス増幅器を有するものであり、

前記第1の容量は、前記演算相互コンダクタンス増幅器から出力された電流によって充電されるものである

ことを特徴とするDC−DCコンバータ。

【請求項8】

請求項7に記載のDC−DCコンバータにおいて、

前記第3のスイッチは、前記演算相互コンダクタンス増幅器の反転入力端と非反転入力端との間に設けられたものであり、

前記第1の状態は、前記反転入力端と前記非反転入力端とを開放する状態であり、

前記第2の状態は、前記反転入力端と前記非反転入力端とを短絡する状態である

ことを特徴とするDC−DCコンバータ。

【請求項9】

請求項7に記載のDC−DCコンバータにおいて、

前記第3のスイッチは、前記演算相互コンダクタンス増幅器の出力端と前記第1の容量との間に設けられたものであり、

前記第1の状態は、導通状態であり、

前記第2の状態は、非導通状態である

ことを特徴とするDC−DCコンバータ。

【請求項10】

請求項2及び6のいずれか一つに記載のDC−DCコンバータにおいて、

前記第2の積分回路は、前記第1の容量の両端電圧に応じた電流を出力する演算相互コンダクタンス増幅器を有するものであり、

前記第2の容量は、前記演算相互コンダクタンス増幅器から出力された電流によって充電されるものである

ことを特徴とするDC−DCコンバータ。

【請求項11】

請求項2及び6のいずれか一つに記載のDC−DCコンバータにおいて、

前記保持部は、前記制御部及びスイッチ制御部のいずれか一方の制御によって初期化されるものである

ことを特徴とするDC−DCコンバータ。

【請求項1】

インダクタを備えたDC−DCコンバータであって、

前記インダクタの両端電圧を積分する第1の積分回路と、

前記第1の積分回路の出力電圧を積分する第2の積分回路と、

前記第2の積分回路の出力電圧を保持する保持部と、

前記保持部の出力電圧に基づいて前記インダクタの充放電制御を行う制御部とを備えた

ことを特徴とするDC−DCコンバータ。

【請求項2】

請求項1に記載のDC−DCコンバータにおいて、

前記第1の積分回路は、積分電荷を蓄積する第1の容量を有するものであり、

前記第2の積分回路は、積分電荷を蓄積する第2の容量を有するものであり、

当該DC−DCコンバータは、

前記第1の容量に並列に設けられた第1のスイッチと、

前記第2の容量に並列に設けられた第2のスイッチと、

前記インダクタの出力電圧と当該DC−DCコンバータの出力電圧とを受け、前記インダクタの出力電圧が当該DC−DCコンバータの出力電圧よりも小さいとき、前記第1のスイッチを導通状態にする一方、それ以外のとき、前記第1のスイッチを非導通状態にするスイッチ制御部とを備え、

前記制御部は、前記インダクタの充電制御を行うとき、前記第2のスイッチを導通状態にする一方、前記インダクタの放電制御を行うとき、前記第2のスイッチを非導通状態にするものである

ことを特徴とするDC−DCコンバータ。

【請求項3】

請求項2に記載のDC−DCコンバータにおいて、

前記第1の積分回路は、前記インダクタの入力電圧と出力電圧との差分に応じた電流を出力する演算相互コンダクタンス増幅器を有するものであり、

前記第1の容量は、前記演算相互コンダクタンス増幅器から出力された電流によって充電されるものである

ことを特徴とするDC−DCコンバータ。

【請求項4】

請求項2に記載のDC−DCコンバータにおいて、

前記第1の積分回路は、

前記インダクタの出力電圧を電源電圧とし、前記第1の容量に接続された第1の電流源と、

前記インダクタの入力電圧によってバイアス制御され、前記第1の電流源から電流を引き抜く第2の電流源とを有するものである

ことを特徴とするDC−DCコンバータ。

【請求項5】

インダクタを備えたDC−DCコンバータであって、

前記インダクタの入力電圧を積分する第1の積分回路と、

前記第1の積分回路の出力電圧を積分する第2の積分回路と、

前記第2の積分回路の出力電圧を保持する保持部と、

前記保持部の出力電圧に基づいて前記インダクタの充放電制御を行う制御部とを備えた

ことを特徴とするDC−DCコンバータ。

【請求項6】

請求項5に記載のDC−DCコンバータにおいて、

前記第1の積分回路は、積分電荷を蓄積する第1の容量を有するものであり、

前記第2の積分回路は、積分電荷を蓄積する第2の容量を有するものであり、

当該DC−DCコンバータは、

前記第1の容量に並列に設けられた第1のスイッチと、

前記第2の容量に並列に設けられた第2のスイッチと、

前記第1の積分回路の積分動作の有効及び無効を切り替える第3のスイッチと、

前記インダクタの出力電圧と当該DC−DCコンバータの出力電圧と前記制御部の出力とを受け、前記インダクタの出力電圧が当該DC−DCコンバータの出力電圧よりも小さく、かつ、前記制御部によって前記インダクタの放電制御が行われているとき、前記第1のスイッチを導通状態にする一方、それ以外のとき、前記第1のスイッチを非導通状態にするスイッチ制御部とを備え、

前記制御部は、前記インダクタの充電制御を行うとき、前記第2のスイッチを導通状態にするとともに前記第3のスイッチを前記第1の容量が充電される第1の状態にする一方、前記インダクタの放電制御を行うとき、前記第2のスイッチを非導通状態にするとともに前記第3のスイッチを前記第1の容量の充電が停止する第2の状態にするものである

ことを特徴とするDC−DCコンバータ。

【請求項7】

請求項6に記載のDC−DCコンバータにおいて、

前記第1の積分回路は、前記インダクタの入力電圧と所定電圧との差分に応じた電流を出力する演算相互コンダクタンス増幅器を有するものであり、

前記第1の容量は、前記演算相互コンダクタンス増幅器から出力された電流によって充電されるものである

ことを特徴とするDC−DCコンバータ。

【請求項8】

請求項7に記載のDC−DCコンバータにおいて、

前記第3のスイッチは、前記演算相互コンダクタンス増幅器の反転入力端と非反転入力端との間に設けられたものであり、

前記第1の状態は、前記反転入力端と前記非反転入力端とを開放する状態であり、

前記第2の状態は、前記反転入力端と前記非反転入力端とを短絡する状態である

ことを特徴とするDC−DCコンバータ。

【請求項9】

請求項7に記載のDC−DCコンバータにおいて、

前記第3のスイッチは、前記演算相互コンダクタンス増幅器の出力端と前記第1の容量との間に設けられたものであり、

前記第1の状態は、導通状態であり、

前記第2の状態は、非導通状態である

ことを特徴とするDC−DCコンバータ。

【請求項10】

請求項2及び6のいずれか一つに記載のDC−DCコンバータにおいて、

前記第2の積分回路は、前記第1の容量の両端電圧に応じた電流を出力する演算相互コンダクタンス増幅器を有するものであり、

前記第2の容量は、前記演算相互コンダクタンス増幅器から出力された電流によって充電されるものである

ことを特徴とするDC−DCコンバータ。

【請求項11】

請求項2及び6のいずれか一つに記載のDC−DCコンバータにおいて、

前記保持部は、前記制御部及びスイッチ制御部のいずれか一方の制御によって初期化されるものである

ことを特徴とするDC−DCコンバータ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2007−202236(P2007−202236A)

【公開日】平成19年8月9日(2007.8.9)

【国際特許分類】

【出願番号】特願2006−14970(P2006−14970)

【出願日】平成18年1月24日(2006.1.24)

【出願人】(000005821)松下電器産業株式会社 (73,050)

【Fターム(参考)】

【公開日】平成19年8月9日(2007.8.9)

【国際特許分類】

【出願日】平成18年1月24日(2006.1.24)

【出願人】(000005821)松下電器産業株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]