DC−DCコンバータ

【課題】ターンオフ損失だけでなくターンオン損失も低減可能なDC−DCコンバータを提供する。

【解決手段】スナバコンデンサCsは、昇圧用ダイオードD1のアノードと昇圧用スイッチング素子Q1の電流入力端と主リアクトルL1とに接続された一端を有する。第1スナバダイオードDs1は、スナバコンデンサCsの他端に接続されたカソードと、ダイオードD1のカソードに接続されたアノードとを有する。第2スナバダイオードDs2は、第1スナバダイオードDs1のカソードとスナバコンデンサCsの他端とに接続されたアノードを有する。スナバリアクトルLsは、第1スナバダイオードDs1のアノードに接続された一端と、第2スナバダイオードDs2のカソードに接続された他端とを有する。

【解決手段】スナバコンデンサCsは、昇圧用ダイオードD1のアノードと昇圧用スイッチング素子Q1の電流入力端と主リアクトルL1とに接続された一端を有する。第1スナバダイオードDs1は、スナバコンデンサCsの他端に接続されたカソードと、ダイオードD1のカソードに接続されたアノードとを有する。第2スナバダイオードDs2は、第1スナバダイオードDs1のカソードとスナバコンデンサCsの他端とに接続されたアノードを有する。スナバリアクトルLsは、第1スナバダイオードDs1のアノードに接続された一端と、第2スナバダイオードDs2のカソードに接続された他端とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はDC−DCコンバータに関する。

【背景技術】

【0002】

高電圧および大電流を扱う電力用の昇圧型DC−DCコンバータでは、チョッパ回路によるスイッチング周波数を高くすることによって、装置の高効率化や小型化を図ることができる。しかし、高周波数化は、スイッチングを担う電力半導体素子のスイッチング損失を増大させることになるので、スイッチング損失の観点からは装置の高効率化や小型化を妨げる原因となってしまう。なお、かかる問題は電力用かつ昇圧型に限定されるものではない。

【0003】

スイッチング損失を低減させるために、ソフトスイッチング回路が利用される場合がある。特許文献1には、スイッチング素子のターンオフ時のスイッチング損失を低減するためのソフトスイッチング回路が記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−201369号公報

【特許文献2】特開平10−146048号公報

【特許文献3】特開2001−309647号公報

【特許文献4】特開2004−147472号公報

【特許文献5】特開2009−017750号公報

【特許文献6】特開2008−270490号公報

【特許文献7】特開2009−033858号公報

【特許文献8】特開2005−204362号公報

【特許文献9】特開2008−206282号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、特許文献1のソフトスイッチング回路では、ターンオン時のスイッチング損失は低減することはできない。すなわち、スイッチング素子がターンオンする際は、ダイオードのリカバリ電流により、ハードスイッチングしてしまう。

【0006】

本発明は、ターンオフ損失だけでなくターンオン損失も低減可能なDC−DCコンバータを提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の一態様に係るDC−DCコンバータは、主リアクトルと、少なくとも1つの昇圧用スイッチング素子と、少なくとも1つの昇圧用ダイオードと、スナバコンデンサと、第1スナバダイオードと、第2スナバダイオードと、スナバリアクトルと、コンデンサとを含む。前記主リアクトルは、一端および他端を有する。前記少なくとも1つの昇圧用スイッチング素子は、前記主リアクトルの前記他端に接続された電流入力端と、グランド電位に接続される電流出力端と、当該電流入力端と当該電流出力端との間のオンオフを制御するための制御信号が入力される制御端とを有する。前記少なくとも1つの昇圧用ダイオードは、前記少なくとも1つの昇圧用スイッチング素子の前記電流入力端と前記主リアクトルの前記他端とに接続されたアノードを有する。前記スナバコンデンサは、前記少なくとも1つの昇圧用ダイオードの前記アノードと前記少なくとも1つの昇圧用スイッチング素子の前記電流入力端と前記主リアクトルの前記他端とに接続された一端を有する。前記第1スナバダイオードは、前記スナバコンデンサの他端に接続されたカソードと、前記少なくとも1つの昇圧用ダイオードのカソードに接続されたアノードとを有する。前記第2スナバダイオードは、前記第1スナバダイオードのカソードと前記スナバコンデンサの前記他端とに接続されたアノードを有する。前記スナバリアクトルは、前記第1スナバダイオードの前記アノードに接続された一端と、前記第2スナバダイオードのカソードに接続された他端とを有する。前記コンデンサは、前記スナバリアクトルの前記他端と前記第2スナバダイオードの前記カソードとに接続された一端と、前記グランド電位に接続される他端とを有する。

【発明の効果】

【0008】

上記一態様によれば、昇圧動作において、ターンオフ損失だけでなくターンオン損失も低減することができる。また、スイッチング損失の低減により、スイッチング周波数を高くしても、装置の高効率化や小型化を図ることができる。また、ソフトスイッチングにより、電磁ノイズの発生を抑えることができる。また、少ない部品でスナバ回路が構成されているので、大幅な大型化およびコスト増大、さらには大型化による効率低減を抑制可能である。また、当該スナバ回路はそれ自体に複雑な制御を必要としないので、ソフトスイッチングを簡便に実現できる。

【図面の簡単な説明】

【0009】

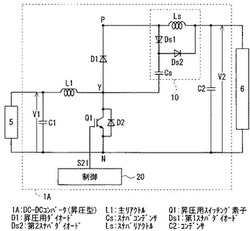

【図1】実施の形態1に係るDC−DCコンバータの構成を概説する回路図である。

【図2】実施の形態1に係るDC−DCコンバータのスイッチングを概説する波形図である。

【図3】実施の形態1に係るDC−DCコンバータの昇圧動作における各種波形を概説する波形図である。

【図4】実施の形態1に係るDC−DCコンバータの昇圧動作を概説する図である。

【図5】実施の形態1に係るDC−DCコンバータの昇圧動作を概説する図である。

【図6】実施の形態1に係るDC−DCコンバータの昇圧動作を概説する図である。

【図7】実施の形態1に係るDC−DCコンバータの昇圧動作を概説する図である。

【図8】実施の形態1に係るDC−DCコンバータの昇圧動作を概説する図である。

【図9】実施の形態1に係るDC−DCコンバータの昇圧動作における各種波形の一例を示す波形図である(ターンオフ)。

【図10】実施の形態1に係るDC−DCコンバータの昇圧動作における各種波形の一例を示す波形図である(ターンオン)。

【図11】実施の形態1に係るDC−DCコンバータの昇圧動作における各種波形の他の一例を示す波形図である(ターンオフ)。

【図12】実施の形態1に係るDC−DCコンバータの昇圧動作における各種波形の他の一例を示す波形図である(ターンオン)。

【図13】実施の形態2に係るDC−DCコンバータの構成を概説する回路図である。

【図14】実施の形態2に係るDC−DCコンバータの降圧動作における各種波形を概説する波形図である。

【図15】実施の形態2に係るDC−DCコンバータの降圧動作を概説する図である。

【図16】実施の形態2に係るDC−DCコンバータの降圧動作を概説する図である。

【図17】実施の形態2に係るDC−DCコンバータの降圧動作を概説する図である。

【図18】実施の形態2に係るDC−DCコンバータの降圧動作を概説する図である。

【図19】実施の形態2に係るDC−DCコンバータの降圧動作を概説する図である。

【図20】実施の形態2に係るDC−DCコンバータの降圧動作における各種波形の一例を示す波形図である(ターンオフ)。

【図21】実施の形態2に係るDC−DCコンバータの降圧動作における各種波形の一例を示す波形図である(ターンオン)。

【図22】実施の形態2に係るDC−DCコンバータの降圧動作における各種波形の他の一例を示す波形図である(ターンオフ)。

【図23】実施の形態2に係るDC−DCコンバータの降圧動作における各種波形の他の一例を示す波形図である(ターンオン)。

【図24】実施の形態3に係るDC−DCコンバータの構成を概説する回路図である。

【図25】実施の形態4に係るDC−DCコンバータの構成を概説する回路図である。

【図26】実施の形態4に係るDC−DCコンバータのスイッチングを概説する波形図である。

【図27】実施の形態5に係るDC−DCコンバータの構成を概説する回路図である。

【図28】実施の形態6に係るDC−DCコンバータの構成を概説する回路図である。

【図29】実施の形態6に係るDC−DCコンバータの構成を概説する回路図である。

【図30】実施の形態7に係るDC−DCコンバータの装置構造を概説する断面図である。

【発明を実施するための形態】

【0010】

<実施の形態1>

図1に実施の形態1に係るDC−DCコンバータ(以下、コンバータと略称する場合もある)1Aの構成を概説する回路図を示す。図1に例示されるようにコンバータ1Aは低電圧側装置5と高電圧側装置6との間に接続されて使用される。換言すれば、コンバータ1Aの低電圧側接続端に低電圧側装置5が接続され、コンバータ1Aの高電圧側接続端に高電圧側装置6が接続される。

【0011】

コンバータ1Aは、昇圧型のコンバータであり、低電圧側接続端の電圧V1を電圧V2(>V1)に昇圧して高電圧側接続端に出力するという昇圧動作を実行可能な構成を有している。換言すれば、コンバータ1Aは、低電圧側装置5によって印加される電圧V1を電圧V2に昇圧し、昇圧した電圧V2を高電圧側装置6へ供給する。

【0012】

なお、昇圧動作において、低電圧側接続端は入力側または1次側とも称され、高電圧側接続端は出力側または2次側とも称される。

【0013】

昇圧動作に対応して、以下では低電圧側装置5が直流電源(DC電源)である場合を例示し、低電圧側装置5をDC電源5とも称することにする。また、高電圧側装置6が各種負荷である場合を例示し、高電圧側装置6を負荷6とも称することにする。

【0014】

また、以下ではコンバータ1Aが相対的に高電圧および大電流を扱う電力用装置として構成される場合を例示するが、コンバータ1Aは例えばエレクトロニクス製品、家電製品等の分野に適合するように構成することも可能である。

【0015】

<コンバータ1Aの構成>

図1に例示のコンバータ1Aは、いわゆる非絶縁型の昇圧チョッパ回路を基本としている。コンバータ1Aは、コンデンサC1と、リアクトルL1と、スイッチング素子Q1と、ダイオードD2と、ダイオードD1と、コンデンサCsと、ダイオードDs1と、ダイオードDs2と、リアクトルLsと、コンデンサC2と、制御装置20とを含んでいる。なお、図中では制御装置20を「制御」と略記しており、後述の各種要素についても図中で名称を略記する場合がある。

【0016】

コンデンサC1は、DC電源5の正極に接続される一端と、DC電源5の負極に接続される他端とを有している。すなわち、コンデンサC1は、コンバータ1Aの利用時に、DC電源5に並列接続される。以下ではコンデンサC1を低電圧側コンデンサC1と称する場合もある。

【0017】

ここではコンデンサC1がコンバータ1Aに含まれる場合を例示するが、コンデンサC1はコンバータ1Aの外部部品として別個に準備しても構わない。また、コンデンサC1を設けない態様も採用可能である。

【0018】

なお、図1の例ではDC電源5の負極の電位がコンバータ1Aのグランド電位Nに選定されている。

【0019】

リアクトルL1は、その一端が低電圧側コンデンサC1の上記一端に接続されている。すなわち、リアクトルL1は、コンバータ1Aの利用時に、DC電源5の正極に接続される。また、リアクトルL1の他端は、スイッチング素子Q1とダイオードD2,D1とコンデンサCsとに接続されている。以下ではリアクトルL1を主リアクトルL1と称する場合もある。

【0020】

スイッチング素子Q1は、電流入力端と、電流出力端と、制御端とを有している。電流入力端は主リアクトルL1の上記他端に接続されている。電流出力端は、低電圧側コンデンサC1の上記他端に接続されており、これによりコンバータ1Aの利用時にはグランド電位Nに接続される。制御端は、制御装置20に接続されており、制御装置20から、電流入力端と電流出力端との間のオンオフを制御するための制御信号S21が入力される。以下ではスイッチング素子Q1を昇圧用スイッチング素子Q1と称する場合もある。

【0021】

ここでは、昇圧用スイッチング素子Q1が絶縁ゲートバイポーラトランジスタ(IGBT)で構成される場合を例示し、当該スイッチング素子Q1をトランジスタQ1とも称することにする。また、スイッチング素子Q1の電流入力端、電流出力端および制御端を、IGBTの端子に対応させて、コレクタ、エミッタおよびゲートとそれぞれ称する場合もある。なお、昇圧用スイッチング素子Q1として他の電力用半導体スイッチング素子を採用することも可能である。

【0022】

ダイオードD2は、昇圧用トランジスタQ1に対して逆並列に接続されている。すなわち、ダイオードD2のアノードはトランジスタQ1のエミッタに接続され、ダイオードD2のカソードはトランジスタQ1のコレクタに接続されている。なお、ダイオードD2とトランジスタQ1とによる逆並列接続構造が、主リアクトルL1の上記他端とグランド電位Nを与える地点との間に接続されている。ダイオードD2は、いわゆるフリーホイールダイオードである。なお、後述の昇圧動作の観点においてはダイオードD2を省略することも可能である。

【0023】

ダイオードD1は、そのアノードが主リアクトルL1の上記他端に接続され、そのカソードがダイオードDs1とリアクトルLsとに接続されている。以下ではダイオードD1を昇圧用ダイオードD1と称する場合もある。

【0024】

なお、ダイオードD1のカソードの側を、グランド電位Nの地点との対比において、高電位側Pと称する場合もある。また、ダイオードD1とトランジスタQ1との接続点を、グランド電位Nの地点および高電位側Pとの対比において、中間点Yと称する場合もある。

【0025】

コンデンサCsは、その一端がリアクトルL1の上記他端と、トランジスタQ1のコレクタと、ダイオードD2のカソードと、ダイオードD1のアノードとに接続されている。コンデンサCsの他端は、ダイオードDs1,Ds2に接続されている。以下ではコンデンサCsをスナバコンデンサCsと称する場合もある。

【0026】

ダイオードDs1は、そのカソードがスナバコンデンサCsの上記他端に接続されている。ダイオードDs1のアノードは、昇圧用ダイオードD1のカソードおよびリアクトルLsに接続されている。以下ではダイオードDs1を第1スナバダイオードDs1と称する場合もある。

【0027】

ダイオードDs2は、そのアノードが第1スナバダイオードDs1のカソードとスナバコンデンサCsの上記他端とに接続されている。ダイオードDs2のカソードは、リアクトルLsおよびコンデンサC2に接続されている。以下ではダイオードDs2を第2スナバダイオードDs2と称する場合もある。

【0028】

リアクトルLsは、その一端が第1スナバダイオードDs1のアノードと昇圧用ダイオードD1のカソードとに接続され、その他端が第2スナバダイオードDs2のカソードとコンデンサC2とに接続されている。以下ではリアクトルLs2をスナバリアクトルLsと称する場合もある。

【0029】

ここで、コンデンサCsと、ダイオードDs1,Ds2と、リアクトルLsとが、スナバ回路10を構成している。当該スナバ回路10の採用により、昇圧用トランジスタQ1のターンオフ時およびターンオン時におけるソフトスイッチングが実現される(後述する)。

【0030】

コンデンサC2は、その一端がスナバリアクトルLsの上記他端と第2スナバダイオードDs2のカソードとに接続されている。コンデンサC2の他端は、昇圧用トランジスタQ1のエミッタおよびダイオードD2のアノードに接続されている。これにより、コンデンサC2の他端はコンバータ1Aの利用時にグランド電位Nに設定される。以下ではコンデンサC2を高電圧側コンデンサC2と称する場合もある。高電圧側コンデンサC2に負荷6が並列接続される。

【0031】

制御装置20は、コンバータ1Aの各種処理を担う。制御装置20は、例えば、マイクロプロセッサ(MPU、CPU、マイクロコンピュータとも称される)と、当該マイクロプロセッサがアクセス可能に設けられたメモリとを含んで具現可能である。この例の場合、マイクロプロセッサが、メモリに予め格納されているプログラムに記述された処理ステップ(換言すれば処理手順)を実行することにより、各種処理が行われる。換言すれば、制御装置20が、各種処理に対応した各種手段として機能する。

【0032】

なお、上記マイクロプロセッサは例えばマルチプロセッサまたはマルチコアの構成を採用することも可能である。また、上記メモリは、例えばROM(Read Only Memory)、RAM(Random Access Memory)、書き換え可能な不揮発性メモリ(EPROM(Erasable Programmable ROM)等)の1つまたは複数を含んで構成可能である。メモリは、上記のようにプログラムを格納する他に、各種データ等を格納し、また、プログラムを実行するための作業領域を提供する。

【0033】

かかる構成例によれば制御装置20による各種処理はソフトウェアによって具現化されるが、かかる各種処理の一部または全部をハードウェアによって実現することも可能である。

【0034】

ここでは制御装置20がコンバータ1Aに含まれる場合を例示するが、制御装置20はコンバータ1Aの外部部品として別個に準備しても構わない。

【0035】

制御装置20は例えば、昇圧用トランジスタQ1の動作を制御する手段として機能する。より具体的に当該手段は、トランジスタQ1のゲートに対する電圧印加を制御することによってトランジスタQ1のオンオフを制御する。この場合、当該手段から出力されるゲート電圧がトランジスタQ1のスイッチング制御信号S21にあたる。

【0036】

図2に制御信号S21の波形図、換言すればトランジスタQ1の動作を概説する波形図を示す。図2に例示の矩形パルスのデューティ比は制御装置20によって制御され、これによりトランジスタQ1がパルス幅変調(PWM)によってオンオフ制御される。デューティ比は昇圧電圧V2の設定値に応じて決定される。換言すれば、デューティ比の設定によって昇圧電圧V2の値が制御される。なお、制御信号S21の波形は図2に例示される矩形波に限定されるものではない。

【0037】

<コンバータ1Aの昇圧動作>

図3〜図10も参照して、コンバータ1Aの昇圧動作を説明する。

【0038】

図3は昇圧動作における各種波形を概説する図であり、図3の上段は主リアクトルL1に流れる電流(リアクトル電流)の概略波形を示し、図3の下段は昇圧用トランジスタQ1のコレクタ電流Icおよびコレクタ−エミッタ間電圧Vceの概略波形を示している。

【0039】

図4〜図8は昇圧動作における各種タイミングでの電流の流れを概説している。図4〜図8中の回路図は基本的には図1と同じであるが、制御装置20およびダイオードD2の図示を省略している。

【0040】

図9は昇圧用トランジスタQ1がターンオフする際の各種波形の一例を示す波形図である。図9の下段はトランジスタQ1のコレクタ電流Icおよびコレクタ−エミッタ間電圧Vceを示し、図9の上段はターンオフ時の電力(換言すればスイッチング損失)Poffを示している。図9には比較のためにスナバ回路10(図1参照)を有さない場合(ハードスイッチング)の波形も示している。図10は昇圧用トランジスタQ1がターンオンする際の各種波形の一例を示す波形図であり、図9と同様に図示されている。なお、図9および図10の波形はシミュレーション結果の一例である。

【0041】

<トランジスタQ1がオン状態(i)(図3参照)>

図4に示されるようにDC電源5の正極から主リアクトルL1とトランジスタQ1とを通ってDC電流5の負極へ至る経路に、電流が流れる。これにより主リアクトルL1はエネルギーを蓄積していく。

【0042】

また、当該オン状態(i)ではスナバコンデンサCsが、スナバリアクトルLsと第1スナバダイオードDs1とを介して、高電圧側接続端の電圧V2によって、完全に充電されている。

【0043】

<トランジスタQ1がオン状態からオフ状態への過渡状態(ii)(図3参照)>

主リアクトルL1を流れる電流は、図5に示されるように、スナバコンデンサCsと第2スナバダイオードDs2と高電圧側コンデンサC2とを通る。ここで、スナバ回路10を有さないハードスイッチングの場合、当該電流はダイオードD1を通る経路を流れる。これに対し、スナバ回路10を有するコンバータ1Aの場合、スナバコンデンサCsが低インピーダンス経路として働くので、上記経路を辿って電流が流れる。

【0044】

当該過渡状態(ii)では、トランジスタQ1の電流Icがターンオフする一方で、スナバコンデンサCsが放電するのでトランジスタQ1の電圧Vceは徐々に増加する(図3および図9下段参照)。これにより、ターンオフ損失Poff(図9下段のグラフにおいて電流Icと電圧Vceとの重なり部分の面積に相関する)が減少する。図9上段のグラフによれば、コンバータ1Aによるソフトスイッチングの方がハードスイッチングに比べて、ターンオフ損失Poffが大幅に削減されることが分かる。

【0045】

このようにトランジスタQ1がオフした際にスナバコンデンサCsから第2スナバダイオードDs2を経由して高電圧側コンデンサC1が充電されるので、電圧Vceの立ち上がりを緩やかにすることができる。すなわちソフトスイッチングが実現される。かかるソフトスイッチングによればスイッチングエネルギーを、ハードスイッチングに比べて数分の1あるいはそれ以下にすることが可能である。

【0046】

<トランジスタQ1がオフ状態(iii)(図3参照)>

スナバコンデンサCsの放電後、主リアクトルL1に流れる電流は、図6に示されるように、ダイオードD1と第1スナバダイオードDs1と第2スナバダイオードDs2とを通って、高電圧側コンデンサC2へ流れる。なお、スナバダイオードDs1,Ds2に高い順方向降下電圧(VF)を持った高速回復仕様のダイオードを採用した場合、主リアクトルL1に流れる電流は主にダイオードD1とスナバリアクトルLsとに流れる。

【0047】

<トランジスタQ1がオフ状態からオン状態への過渡状態(iv)(図3参照)>

図7に示されるように主リアクトルL1に流れる電流がダイオードD1からトランジスタQ1へシフトすると、スナバリアクトルLsに流れる電流に変化が起こる。スナバリアクトルLsの電流変化と、この時点でスナバコンデンサCsは放電した状態にあるという状況とによって、トランジスタQ1の電圧Icが流れ始めると直ぐトランジスタQ1の電圧Vceは非常に低いレベルへ下降する(V=Ls×di/dt効果、換言すれば自己誘導による逆起電力の発生による)。

【0048】

そして、図8に示されるように高電圧側接続端の側から、換言すれば高電圧側コンデンサC2からスナバリアクトルLsと第1スナバダイオードDs1とを通って電流が流れ始め、これによりスナバコンデンサCsが充電される。

【0049】

したがって、ダイオードD1の逆回復段階までトランジスタQ1の電圧Vceが高電圧側接続端の電圧V2に留まっているハードスイッチングとは異なり、スナバ回路10によるソフトスイッチングによればターンオン損失Pon(図10下段のグラフにおいて電流Icと電圧Vceとの重なり部分の面積に相関する)が減少する。図10上段のグラフによれば、コンバータ1Aによるソフトスイッチングの方がハードスイッチングに比べて、ターンオン損失Ponが大幅に削減されることが分かる。

【0050】

なお、図11および図12に他の波形例(シミュレーション)を例示する。図11は昇圧用トランジスタQ1がターンオフする際の各種波形の他の一例である。図11の上段はスナバ回路10の採用によるソフトスイッチングの場合を示し、図11の下段はスナバ回路10の不採用によるハードスイッチングの場合を示している。また、図12は、トランジスタQ1がターンオンする際の各種波形の他の一例であり、図11と同様に図示されている。なお、図11および図12のソフトスイッチング波形が図9および図10と異なるのは、コンバータ1Aの各種素子の定数等を変えていることに因る。

【0051】

<効果>

上記のようにコンバータ1Aによれば、昇圧動作において、ターンオフ損失だけでなくターンオン損失も低減することができる。図11および図12の例によれば、ターンオフ損失とターンオン損失との合算について約50%近い低減効果が確認できる。

【0052】

なお、特許文献1においてゼロ電圧スイッチング用補助回路が、コンバータ1Aのスナバ回路10に相当すると考えられるが、両回路は配設位置が全く異なる。

【0053】

また、コンバータ1Aによれば、スイッチング損失の低減に伴って、スイッチング周波数を高くしても、装置の高効率化や小型化を図ることができる。つまり、高周波数化と高効率化と小型化とを同時的に推進することが可能になる。

【0054】

また、ソフトスイッチングにより、電磁ノイズの発生を抑えることができる。

【0055】

また、スナバ回路10は部品点数が少ないので、スナバ回路10を採用しても大幅な大型化およびコスト増大、さらには大型化による効率低減を抑制可能である。

【0056】

また、スナバ回路10はそれ自体に複雑な制御を必要としないので、ソフトスイッチングを簡便に実現できる。

【0057】

<実施の形態2>

図13に実施の形態2に係るコンバータ1Bの構成を概説する回路図を示す。コンバータ1Bは、いわゆる双方向昇降圧型(双方向型とも称される)のコンバータである。すなわち、コンバータ1Bは、低電圧側接続端の電圧V1を電圧V2に昇圧して高電圧側接続端に出力するという昇圧動作と、高電圧側接続端の電圧V2を電圧V1に降圧して低電圧側接続端に出力するという降圧動作との両方を実行可能な構成を有している。換言すれば、昇圧動作においてコンバータ1Bは、低電圧側装置5によって印加される電圧V1を電圧V2に昇圧し、昇圧した電圧V2を高電圧側装置6へ供給する。他方、降圧動作においてコンバータ1Bは、高電圧側装置6によって印加される電圧V2を電圧V1に降圧し、降圧した電圧V1を低電圧側装置5へ供給する。

【0058】

なお、昇圧動作で入力側または1次側と称される低電圧側接続端は、降圧動作では出力側または2次側にあたる。また、昇圧動作で出力側または2次側と称される高電圧側接続端は、降圧動作では入力側または1次側にあたる。

【0059】

実施の形態2では、低電圧側装置5がDC電源、特に充電池(二次電池とも称される)である場合を例示し、低電圧側装置5を充電池5とも称することにする。また、高電圧側装置6が、コンバータ1Bに接続されたインバータと、当該インバータに接続されたモータジェネレータ(電動発電機とも称される)とを含んだ装置である場合を例示し、高電圧側装置6をインバータ/モータジェネレータ6とも称することにする。当該例示の構成は、例えば電車、電気自動車、ハイブリッド自動車等の車両に搭載されている。

【0060】

当該例示の構成によれば、充電池5から出力されたDC電圧は、コンバータ1Bによって昇圧され、インバータで交流電圧によって変換され、モータジェネレータをモータとして回転させる。これによりモータジェネレータに接続された車輪が回転し、車両が力行する。

【0061】

これに対し、車両の制動時には、モータジェネレータがジェネレータとして働く。このため、モータジェネレータによって発電された交流電圧は、インバータによってDC電圧に変換され、コンバータ1Bによって降圧され、充電池5に充電される。つまり、モータジェネレータから電力が回生される。

【0062】

なお、以下ではコンバータ1Bが実施の形態1と同様に電力用装置として構成される場合を例示するが、コンバータ1Bの利用分野はこれに限定されるものではない。

【0063】

<コンバータ1Bの構成>

図13に例示のコンバータ1Bは、図1に例示したコンバータ1Aにスイッチング素子Q2を追加した構成を有している。コンバータ1Bの他の構成は基本的にコンバータ1Aと同様である。

【0064】

スイッチング素子Q2は、電流入力端と、電流出力端と、制御端とを有している。電流入力端は、ダイオードD1のカソードと、第1スナバダイオードDs1のアノードと、スナバリアクトルLsの上記一端とに接続されている。電流出力端は、ダイオードD1のアノードと、主リアクトルL1の上記他端と、スイッチング素子Q1の電流入力端(トランジスタQ1のコレクタ)と、ダイオードD2のカソードとに接続されている。なお、スイッチング素子Q2はダイオードD1に対して逆並列に接続されている。制御端は、制御装置20に接続されており、制御装置20から、電流入力端と電流出力端との間のオンオフを制御するための制御信号S22が入力される。なお、以下ではスイッチング素子Q2を降圧用スイッチング素子Q2と称する場合もある。

【0065】

ここでは、降圧用スイッチング素子Q2がIGBTで構成される場合を例示し、当該スイッチング素子Q2をトランジスタQ2とも称することにする。また、スイッチング素子Q2の電流入力端、電流出力端および制御端を、IGBTの端子に対応させて、コレクタ、エミッタおよびゲートとそれぞれ称する場合もある。なお、降圧用スイッチング素子Q2として他の電力用半導体スイッチング素子を採用することも可能である。

【0066】

なお、以下では、ダイオードD2を降圧用ダイオードD2と称し、ダイオードD1を昇圧用ダイオードD1と称する場合もある。

【0067】

降圧用トランジスタQ2の追加により、制御装置20は降圧用トランジスタQ2の動作を制御する手段としても機能する。より具体的に当該手段は、トランジスタQ2のゲートに対する電圧印加を制御することによってトランジスタQ2のオンオフを制御する。この場合、当該手段から出力されるゲート電圧がトランジスタQ2のスイッチング制御信号S22にあたる。制御信号S22は例えば図2の制御信号S21と同様の波形を有している。

【0068】

<コンバータ1Bの昇圧動作>

降圧用トランジスタQ2をオフにした状態でコンバータ1A(図1参照)と同様に駆動することにより、コンバータ1Bに昇圧動作を行わせることが可能である。このため、コンバータ1Bの昇圧動作は実施の形態1での説明を援用するに留め、ここでは繰り返しの説明を省略する。

【0069】

<コンバータ1Bの降圧動作>

昇圧用トランジスタQ1をオフにした状態で降圧用トランジスタQ2を駆動することにより、コンバータ1Bに降圧動作を行わせることが可能である。以下、図14〜図21も参照して、コンバータ1Bの降圧動作を説明する。

【0070】

図14は降圧動作における各種波形を概説する図であり、図14の上段は主リアクトルL1に流れる電流(リアクトル電流)の概略波形を示し、図14の下段は降圧用トランジスタQ2のコレクタ電流Icおよびコレクタ−エミッタ間電圧Vceの概略波形を示している。

【0071】

図15〜図19は降圧動作における各種タイミングでの電流の流れを概説している。図15〜図19中の回路図は基本的には図13と同じであるが、制御装置20と昇圧用トランジスタQ1と昇圧用ダイオードD1の図示を省略している。

【0072】

図20は降圧用トランジスタQ2がターンオフする際の各種波形の一例を示す波形図であり、図21は降圧用トランジスタQ2がターンオンする際の各種波形の一例を示す波形図である。図20および図21は既述の図9および図10と同様に図示されている。

【0073】

<トランジスタQ2がオン状態(i)(図14参照)>

図15に示されるように、インバータ/モータジェネレータ6から(換言すれば高電圧側コンデンサC2から)スナバリアクトルLsと降圧用トランジスタQ2と主リアクトルL1とを通って充電池5の正極へ至る経路に、電流が流れる。これにより主リアクトルL1はエネルギーを蓄積していく。

【0074】

また、当該オン状態(i)ではスナバコンデンサCsが、スナバリアクトルLsと第2スナバダイオードDs2とを介して、放電する。

【0075】

<トランジスタQ2がオン状態からオフ状態への過渡状態(ii)(図14参照)>

主リアクトルL1とスナバリアクトルLsとを流れる電流は、図16に示されるように、第1スナバダイオードDs1とスナバコンデンサCsとを通る。ここで、スナバ回路10を有さないハードスイッチングの場合、当該電流は降圧用ダイオードD2を通る経路を流れる。これに対し、スナバ回路10を有するコンバータ1Bの場合、降圧用ダイオードD2が導通可能になる前にスナバコンデンサCsが高電圧側接続端の電圧V2に充電されるので、上記経路を辿って電流が流れる。

【0076】

当該過渡状態(ii)では、トランジスタQ2の電流Icがターンオフする一方で、スナバコンデンサCsが充電されるのでトランジスタQ2の電圧Vceは徐々に増加する(図14および図20下段参照)。これにより、ターンオフ損失Poff(図20下段のグラフにおいて電流Icと電圧Vceとの重なり部分の面積に相関する)が減少する。図20上段のグラフによれば、コンバータ1Bによるソフトスイッチングの方がハードスイッチングに比べて、ターンオフ損失Poffが大幅に削減されることが分かる。

【0077】

<トランジスタQ2がオフ状態(iii)(図14参照)>

スナバコンデンサCsの充電後、主リアクトルL1に流れる電流は、図17に示されるように、降圧用ダイオードD2を通って充電池5へ(換言すれば低電圧側接続端の側へ)流れ続ける。

【0078】

スナバコンデンサCsの充電中に主リアクトルL1に蓄積されたエネルギーは、スナバリアクトルLsと第1スナバダイオードDs1と第2スナバダイオードとを通る経路に電流を環流させる。

【0079】

<トランジスタQ2がオフ状態からオン状態への過渡状態(iv)(図14参照)>

図18に示されるように主リアクトルL1に流れる電流がダイオードD2からトランジスタQ2へシフトすると、スナバリアクトルLsに流れる電流に変化が起こる。スナバリアクトルLsの電流変化と、この時点でスナバコンデンサCsは充電された状態にあるという状況とによって、トランジスタQ2の電圧Icが流れ始めると直ぐトランジスタQ2の電圧Vceは非常に低いレベルへ下降する(V=Ls×di/dt効果、換言すれば自己誘導による逆起電力の発生による)。

【0080】

そして、図19に示されるように完全に充電されたスナバコンデンサCsから、スナバリアクトルLsと第2スナバダイオードDs2とを通って電流が流れ始め、これによりスナバコンデンサCsが放電する。

【0081】

したがって、ダイオードD2の逆回復段階までトランジスタQ2の電圧Vceが高電圧側接続端の電圧V2に留まっているハードスイッチングとは異なり、スナバ回路10によるソフトスイッチングによればターンオン損失Pon(図21下段のグラフにおいて電流Icと電圧Vceとの重なり部分の面積に相関する)が減少する。図21上段のグラフによれば、コンバータ1Bによるソフトスイッチングの方がハードスイッチングに比べて、ターンオン損失Ponが大幅に削減されることが分かる。

【0082】

なお、図22および図23に他の波形例(シミュレーション)を例示する。図22は降圧用トランジスタQ2がターンオフする際の各種波形の他の一例であり、図23はトランジスタQ1がターンオンする際の各種波形の他の一例である。図22および図23は既述の図11および図12と同様に図示されている。なお、図22および図23のソフトスイッチング波形が図20および図21と異なるのは、コンバータ1Bの各種素子の定数等を変えていることに因る。

【0083】

<効果>

コンバータ1Bによれば、昇圧動作だけでなく、降圧動作においてもターンオフ損失とターンオン損失との両方を低減することができる。図22および図23の例によれば、ターンオフ損失とターンオン損失との合算について約40%近い低減効果が確認できる。また、コンバータ1Bによれば、上記コンバータ1Aが奏するその他の効果も得ることができる。

【0084】

<実施の形態3>

図24に実施の形態3に係るコンバータ1Cの構成を概説する回路図を示す。図24に例示のコンバータ1Cは、実施の形態2に係る双方向昇降圧型コンバータ1B(図13参照)から昇圧用トランジスタQ1を削除した構成を有している。すなわち、コンバータ1Cは降圧型に特化されている。コンバータ1Cの他の構成は基本的にコンバータ1Bと同様である。なお、降圧動作の観点においては昇圧用ダイオードD1を省略することも可能である。

【0085】

なお、実施の形態3では、低電圧側装置5が各種負荷や充電池であり、高電圧側装置6がDC電源(交流ジェネレータとインバータとを組み合わせた装置等であってもよい)である場合が例示される。

【0086】

コンバータ1Cによれば、降圧動作において、ターンオフ損失とターンオン損失との両方を低減することができる。また、コンバータ1Cによれば、上記コンバータ1Bが奏するその他の効果も得ることができる。

【0087】

<実施の形態4>

図25に実施の形態4に係るコンバータ1Dの構成を概説する回路図を示す。図25に例示のコンバータ1Dは、実施の形態2に係る双方向昇降圧型コンバータ1B(図13参照)においてトランジスタQ1,Q2およびダイオードD1,D2のそれぞれを複数個設けた構成を有している。コンバータ1Dの他の構成は基本的にコンバータ1Bと同様である。

【0088】

より具体的には、複数の昇圧用トランジスタQ1は同じ向きで並列接続されており、いずれのトランジスタQ1も電流入力端が主リアクトルL1の上記他端に接続され、電流出力端がグランド電位Nの地点に接続されている。

【0089】

また、複数の降圧用トランジスタQ2は同じ向きで並列接続されており、いずれのトランジスタQ2も電流入力端がスナバリアクトルLsの上記一端および第1スナバダイオードDs1のアノードに接続され、電流出力端が主リアクトルL1の上記他端に接続されている。

【0090】

また、複数の昇圧用ダイオードD1は、同じ向きで並列接続されているとともに、複数の降圧用トランジスタQ2に対して逆並列に接続されている。

【0091】

また、複数の降圧用ダイオードD2は、同じ向きで並列接続されているとともに、複数の昇圧用トランジスタQ1に対して逆並列に接続されている。

【0092】

ここでは、コンバータ1Dの各トランジスタQ1の素子容量(換言すれば素子性能)は、コンバータ1B(図13参照)の単一のトランジスタQ1の素子容量よりも小さく設定されている。例えば、コンバータ1Dの各トランジスタQ1の素子容量は、コンバータ1Bの単一のトランジスタQ1の素子容量を等分割した程度に設定される。かかる点はトランジスタQ2およびダイオードD1,D2についても同様である。

【0093】

トランジスタQ1,Q2の個数に対応して、制御装置20はこれらのトランジスタQ1,Q2の動作を制御する。より具体的には、制御装置20は、昇圧動作では、全ての降圧用トランジスタQ2をオフに制御するとともに、複数の昇圧用トランジスタQ1をタイミングをずらして順番にオンさせる手段として機能する。他方、降圧動作において制御装置20は、全ての昇圧用トランジスタQ1をオフに制御するとともに、複数の降圧用トランジスタQ2をタイミングをずらし順番にオンさせる手段として機能する。

【0094】

図26に昇圧用トランジスタQ1のスイッチング制御信号S21の波形図、換言すればトランジスタQ1の動作を概説する波形図を示す。図26には、2つの昇圧用トランジスタQ1(符号Q1a,Q1bで区別することにする)が設けられ、トランジスタQ1a用の制御信号S21として制御信号S21aが用いられ、トランジスタQ1b用の制御信号S21として制御信号S21bが用いられる場合を例示している。図26に示されるように、制御信号S21a,21bはオン期間のタイミングがずれており、昇圧動作では当該制御信号S21a,21bによってトランジスタQ1a,Q1bのオンオフのタイミングをずらすことが可能である。3つ以上の昇圧用トランジスタQ1および複数の降圧用トランジスタQ2も同様に駆動される。

【0095】

コンバータ1Dによれば、コンバータ1A〜1Cが奏する効果を得ることができるとともに、コンバータ1A〜1Cよりも更に高周波数駆動が可能になる。

【0096】

なお、コンバータ1Dをコンバータ1A,1Cの構成に倣って昇圧型または降圧型に変形してもよい。また、トランジスタQ1,Q2の一方をコンバータ1A〜1Cと同様に単一のトランジスタで構成してもよい。また、ダイオードD1,D2の一方または両方をコンバータ1A〜1Cと同様に単一のダイオードで構成してもよい。また、複数のトランジスタQ1を同じタイミングで一括駆動してもよく、複数のトランジスタQ2についても同様である。

【0097】

<実施の形態5>

図27に実施の形態5に係るコンバータ1Eの構成を概説する回路図を示す。図27に例示のコンバータ1Eは、実施の形態2に係る双方向昇降圧型コンバータ1B(図13参照)の一部が多重化された構成を有している。

【0098】

より具体的には、同じ構成を有した2個の単位回路40が並列接続されることによって多重化されている。図27に例示の単位回路40は、実施の形態2に係る双方向昇降圧型コンバータ1B(図13参照)における主リアクトルL1とトランジスタQ1,Q2とダイオードD1,D2とスナバ回路10とによって構成されている。

【0099】

そして図27の例では、2つの単位回路40は、主リアクトルL1の上記一端どうし、高電位側Pの地点どうし、グランド電位Nの地点どうし、スナバリアクトルLsと第2スナバダイオードDs2との接続点どうしが等電位に接続されることによって、多重化されている。かかる構成例ではコンデンサC1,C2は2つの単位回路40によって共用されている。

【0100】

合計2つの昇圧用トランジスタQ1は、昇圧動作において、タイミングをずらして順番にオンさせてもよいし、あるいは、同じタイミングで一括してオンさせてもよい。合計2つの降圧用トランジスタQ2についても同様である。

【0101】

コンバータ1Eによれば、コンバータ1A〜1Dが奏する効果を得ることができるとともに、リップル電流を抑制することができる。また、リップル電流の抑制はコンデンサC1,C2の容量削減を可能にするので、コンデンサC1,C2の小型化、更には装置の小型化を図ることができる。

【0102】

なお、3個以上の単位回路40を多重化してもよい。また、単位回路40をコンバータ1A,1Cの構成に倣って昇圧型または降圧型に変形してもよい。また、トランジスタQ1,Q2の一方または両方をコンバータ1Dの構成に倣って複数のトランジスタに変更してもよい。また、ダイオードD1,D2の一方または両方をコンバータ1Dの構成に倣って複数のダイオードに変更してもよい。

【0103】

<実施の形態6>

図28に実施の形態6に係るコンバータ1Fの構成を概説する回路図を示す。図28に例示のコンバータ1Fは、実施の形態4に係る双方向昇降圧型コンバータ1D(図25参照)に昇圧用検出手段51および降圧用検出手段52を追加した構成を有している。コンバータ1Fの他の構成は基本的にコンバータ1Dと同様である。

【0104】

昇圧用検出手段51は、複数の昇圧用トランジスタQ1の動作状態に関する情報を検出し、検出結果S51を制御装置20へ送信する。また、降圧用検出手段52は、複数の降圧用トランジスタQ2の動作状態に関する情報を検出し、検出結果S52を制御装置20へ出力する。

【0105】

昇圧用検出手段51は、昇圧用トランジスタQ1のそれぞれにセンサ等を取り付けることによって全部のトランジスタQ1について情報検出を行うように構成されてもよいし、あるいは、一部の昇圧用トランジスタQ1についてのみ代表的に情報検出を行うように構成されてもよい。降圧用検出手段52についても同様である。

【0106】

制御装置20は、検出手段51,52による検出結果S51,S52を取得し、当該検出結果S51,S52に基づいてトランジスタQ1,Q2の動作を、予め規定された最適状態になるように制御する手段として機能する。

【0107】

スナバ回路10自体に複雑な制御を必要としないことはコンバータ1Fにおいても同様である。このため、検出結果に基づいてスイッチングトランジスタと共にスナバ回路も制御する構成に比べて、コンバータ1Fは制御方式が簡易である。また、制御方式が簡易であることは制御時間の短縮化、換言すればリアルタイム制御を可能にする。

【0108】

ここで、上記のように昇圧用検出手段51による検出対象は全部のトランジスタQ1であってもよいし、一部のトランジスタQ1であってもよい。但し、全てのトランジスタQ1の動作状態を検出することにより、各トランジスタQ1を検出結果に応じて個別に制御することが可能になる。かかる詳細な個別制御によれば、例えば複数のトランジスタQ1を平均的に動作させることができ、高効率化や高寿命化に寄与する。なお、かかる効果を奏する動作状態が上記最適状態の例である。かかる点は降圧用検出手段52についても同様である。

【0109】

例えば検出結果S51に基づくトランジスタQ1の動作制御には、複数の昇圧用トランジスタQ1の中から駆動させるトランジスタQ1を検出結果S51に基づいて選択する処理が含まれる。これによれば、トランジスタQ1の選択を動作中にリアルタイムで行うので、複数のトランジスタQ1を平均的、安定的に動作させることができ、更には高効率化や高寿命化に寄与する。なお、かかる効果を奏する動作状態も上記最適状態の例である。また、トランジスタQ1の選択処理によれば、製造時にトランジスタQ1の特性の選別、換言すれば特性ばらつきのランク付けおよびその管理を行う必要が無くなるので、製造工程数、製造コスト等を削減することができる。かかる点は降圧用トランジスタQ2の選択処理についても同様である。

【0110】

検出手段51,52が検出する上記情報として、トランジスタQ1,Q2のコレクタ電流が例示される。電流は例えば既知の各種手段によって測定可能であるので、かかる例では検出手段51,52にそのような電流測定手段を設ければよい。コレクタ電流に基づいた制御によれば、例えば、低電流時にはテイル電流が延びる傾向があるので、スイッチング周波数を上げてこれを抑制することが可能になる。また、大電流時にはサージ電流の懸念があるので、スイッチング周波数を下げてこれを抑制することが可能になる。これらの制御も上記最適状態を得るための制御例である。

【0111】

また、検出手段51,52が検出する上記情報として、トランジスタQ1,Q2の温度が例示される。温度は例えば既知の各種手段によって測定可能であるので、かかる例では検出手段51,52にそのような温度測定手段を設ければよい。素子温度に基づいた制御によれば、例えば、最大接合温度に到達しないようにトランジスタQ1,Q2の動作を制御することが可能になる。また、各トランジスタを発熱の観点からバランスよく選択することが可能になる。これらは高寿命化に寄与する。これらの制御も上記最適状態を得るための制御例である。

【0112】

また、検出手段51,52を、トランジスタQ1,Q2のコレクタ電流と、トランジスタQ1,Q2の温度との両方を検出するように構成してもよい。これによれば、電流と温度とのいずれかのみを検出する場合に比べて、最適化を高精度に行うことが可能になる。その結果、高効率化、ノイズ低減、損失低減等を図ることができる。

【0113】

また、例えばトランジスタQ1の動作制御には、駆動させるトランジスタQ1のゲート抵抗(すなわちスイッチング素子Q1の制御端への入力抵抗)を制御する処理が含まれる。

【0114】

ゲート抵抗制御は例えば図29の構成によって行うことが可能である。なお、図29は1つのトランジスタQ1について簡略的に例示している。図29の例において、トランジスタQ1のゲートには可変抵抗手段53が接続されており、当該可変抵抗手段53の抵抗値は制御装置20からの制御信号S23によって設定可能である。かかる構成例によれば、制御装置20が、検出手段51からの検出結果S51に基づいて可変抵抗手段53の抵抗値を制御することが可能である。なお、可変抵抗手段53は例えば、抵抗値を変更可能な既知の各種構成を採用可能である。降圧用トランジスタQ2のゲート抵抗の制御についても同様である。

【0115】

例えば、トランジスタQ1,Q2のターンオフ直後においてゲート抵抗を相対的に高くすることによって、ターンオフ時の電流変化が緩やかになり、その結果、スイッチングサージ電圧を抑制することができる。また、サージ電圧の抑制によって、放射ノイズを抑制することができる。また、例えば、ゲート抵抗を上記増大の後に相対的に低くしてトランジスタQ1,Q2のターンオフ速度を上げることにより、スイッチング損失を低減することができる。なお、これらの効果を奏する動作状態が上記最適状態の例である。

【0116】

なお、検出手段51,52はコンバータ1A等と組み合わせることも可能であり、コンバータ1A等が奏する効果も得ることができる。

【0117】

<実施の形態7>

実施の形態7では上記各種のコンバータの装置構造を説明する。図30に、実施の形態7に係るコンバータ1Gの断面図を例示する。なお、図面の煩雑化を避けるため図30では一部の要素についてハッチングを省略している。コンバータ1Gは、ここでは実施の形態2に係るコンバータ1B(図13)に相当するものとして説明するが、以下の説明は他のコンバータ1A(図1参照)等にも当てはまる。

【0118】

図30の例によればコンバータ1Gは、放熱板101と、ケース102と、ふた103とを含んでいる。

【0119】

放熱板101は例えば銅等の金属で構成されている。放熱板101は各種要素が実装されるベース板としての役割もある。

【0120】

ケース102は、放熱板101の周縁部に立設し放熱板102と共に凹状容器を形成する部分を有している。図30の例では、ケース102は上記凹状容器の内側へ、換言すれば放熱板101の中央部側へ突出した部分も有している。ケース102は例えばポリフェニレンスルファイド(PPS)等の絶縁性材料で構成されている。

【0121】

ケース103には、端子や電極等を構成する種々の導電性部品111〜114が設けられている。なお、これらの部品111〜114は図30に図示される個数に限定されるものではない。例えば端子111は不図示の位置にも設けられており、複数の端子111が低電圧側接続端および高電圧側接続端に対応する。

【0122】

ふた103は、放熱板102とは反対側においてケース103に取り付けられている。ふた103は例えばPPS等の絶縁性材料で構成されている。

【0123】

コンバータ1Gは、さらに、絶縁性基板121と、電力用半導体チップ122,123と、コンデンサ124とをケース102内(換言すれば上記凹状容器内)に含んでいる。

【0124】

絶縁性基板121は、例えばセラミック等の絶縁性材料で構成されており、はんだ等によって放熱板101上に接合されている。

【0125】

電力用半導体チップ122,123は、はんだ等によって絶縁性基板121上に接合されている。電力用半導体チップ122,123には電力用半導体素子(コンバータ1B(図13参照)の例によればトランジスタQ1,Q2およびダイオードD1,D2,Ds1,Ds2)が作り込まれている。電力用半導体チップ122,123は図30の例ではワイヤによって電気的結線がなされて所定の電気回路を構成している。

【0126】

コンデンサ124は、スナバコンデンサCsであり、放熱板101に接触させて配置されている。スナバコンデンサ124はコンバータ1Gの動作時に発熱するので、かかる配置態様によればスナバコンデンサ124の発熱を放熱板101へ効率良く伝達し放熱させることができる。このため、スナバコンデンサ124の容量を低減することができ、さらに容量低減によって小型化を図ることができる。

【0127】

コンデンサ124の端子125は、はんだ付けと、溶接と、超音波接合と、ネジ締めとのうちの少なくとも1つの接続手法によって、ケース102に設けられた電極114に接続されている。接続手法はコンデンサ124の端子125とケース電極114との位置、姿勢等に応じて適宜選択すればよく、適切な接続手法によってコンデンサ124とケース電極114との接続を効率良く行うことができる。また、適切な接続手法によれば、接続箇所の高寿命化、換言すればコンバータ1Gの高寿命化を図ることができる。

【0128】

電力用半導体チップ122,123等は充填材126によって封止されている。充填材126として例えばシリコン樹脂やエポキシ樹脂等が用いられる。

【0129】

なお、図30には図示されていないが、コンデンサC1,C2とリアクトルL1,Lsとのうちの一部または全部をケース102の内部に配置してもよいし、あるいはケース102の外部に配置してもよい。

【0130】

上記のようにトランジスタQ1,Q2と、スナバコンデンサCs(図30ではコンデンサ124)と、スナバダイオードDs1,Ds2とが単一のケース102内に集約されている。このため、各素子を繋ぐ配線を短縮化して配線インダクタンスを低減することができる。また、配線インダクタンスの低減によって、サージを低減することができる。

【0131】

コンバータ1Gは、さらに、制御基板131と、シールド板132とをケース102内に含んでいる。

【0132】

制御基板131は、制御装置20(図13等参照)が形成された基板であり、図30の例では電極112に接続されている。

【0133】

シールド板132は、制御基板131と電力用半導体チップ122,123との間に配置され、制御装置20と電力用半導体チップ122,123との間の電気的(または電磁的)干渉を遮蔽する。シールド板132は例えば導電性材料によって構成されている。

【0134】

なお、制御基板131はケース102の外部に配置される場合もあり、これに伴ってシールド板132もケース102の外部に配置される場合もある。

【符号の説明】

【0135】

1A〜1G DC−DCコンバータ、20 制御装置、40 単位回路、51,52 検出手段、53 可変抵抗手段、101 放熱板、102 ケース、114 電極、C1 低電圧側コンデンサ、C2 高電圧側コンデンサ、Cs,124 スナバコンデンサ、D1 昇圧用ダイオード、D2 降圧用ダイオード、Ds1 第1スナバダイオード、Ds2 第2スナバダイオード、L1 主リアクトル、Ls スナバリアクトル、Q1 昇圧用スイッチング素子、Q2 降圧用スイッチング素子、S21,S22 制御信号、S51,S52 検出結果。

【技術分野】

【0001】

本発明はDC−DCコンバータに関する。

【背景技術】

【0002】

高電圧および大電流を扱う電力用の昇圧型DC−DCコンバータでは、チョッパ回路によるスイッチング周波数を高くすることによって、装置の高効率化や小型化を図ることができる。しかし、高周波数化は、スイッチングを担う電力半導体素子のスイッチング損失を増大させることになるので、スイッチング損失の観点からは装置の高効率化や小型化を妨げる原因となってしまう。なお、かかる問題は電力用かつ昇圧型に限定されるものではない。

【0003】

スイッチング損失を低減させるために、ソフトスイッチング回路が利用される場合がある。特許文献1には、スイッチング素子のターンオフ時のスイッチング損失を低減するためのソフトスイッチング回路が記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−201369号公報

【特許文献2】特開平10−146048号公報

【特許文献3】特開2001−309647号公報

【特許文献4】特開2004−147472号公報

【特許文献5】特開2009−017750号公報

【特許文献6】特開2008−270490号公報

【特許文献7】特開2009−033858号公報

【特許文献8】特開2005−204362号公報

【特許文献9】特開2008−206282号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、特許文献1のソフトスイッチング回路では、ターンオン時のスイッチング損失は低減することはできない。すなわち、スイッチング素子がターンオンする際は、ダイオードのリカバリ電流により、ハードスイッチングしてしまう。

【0006】

本発明は、ターンオフ損失だけでなくターンオン損失も低減可能なDC−DCコンバータを提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の一態様に係るDC−DCコンバータは、主リアクトルと、少なくとも1つの昇圧用スイッチング素子と、少なくとも1つの昇圧用ダイオードと、スナバコンデンサと、第1スナバダイオードと、第2スナバダイオードと、スナバリアクトルと、コンデンサとを含む。前記主リアクトルは、一端および他端を有する。前記少なくとも1つの昇圧用スイッチング素子は、前記主リアクトルの前記他端に接続された電流入力端と、グランド電位に接続される電流出力端と、当該電流入力端と当該電流出力端との間のオンオフを制御するための制御信号が入力される制御端とを有する。前記少なくとも1つの昇圧用ダイオードは、前記少なくとも1つの昇圧用スイッチング素子の前記電流入力端と前記主リアクトルの前記他端とに接続されたアノードを有する。前記スナバコンデンサは、前記少なくとも1つの昇圧用ダイオードの前記アノードと前記少なくとも1つの昇圧用スイッチング素子の前記電流入力端と前記主リアクトルの前記他端とに接続された一端を有する。前記第1スナバダイオードは、前記スナバコンデンサの他端に接続されたカソードと、前記少なくとも1つの昇圧用ダイオードのカソードに接続されたアノードとを有する。前記第2スナバダイオードは、前記第1スナバダイオードのカソードと前記スナバコンデンサの前記他端とに接続されたアノードを有する。前記スナバリアクトルは、前記第1スナバダイオードの前記アノードに接続された一端と、前記第2スナバダイオードのカソードに接続された他端とを有する。前記コンデンサは、前記スナバリアクトルの前記他端と前記第2スナバダイオードの前記カソードとに接続された一端と、前記グランド電位に接続される他端とを有する。

【発明の効果】

【0008】

上記一態様によれば、昇圧動作において、ターンオフ損失だけでなくターンオン損失も低減することができる。また、スイッチング損失の低減により、スイッチング周波数を高くしても、装置の高効率化や小型化を図ることができる。また、ソフトスイッチングにより、電磁ノイズの発生を抑えることができる。また、少ない部品でスナバ回路が構成されているので、大幅な大型化およびコスト増大、さらには大型化による効率低減を抑制可能である。また、当該スナバ回路はそれ自体に複雑な制御を必要としないので、ソフトスイッチングを簡便に実現できる。

【図面の簡単な説明】

【0009】

【図1】実施の形態1に係るDC−DCコンバータの構成を概説する回路図である。

【図2】実施の形態1に係るDC−DCコンバータのスイッチングを概説する波形図である。

【図3】実施の形態1に係るDC−DCコンバータの昇圧動作における各種波形を概説する波形図である。

【図4】実施の形態1に係るDC−DCコンバータの昇圧動作を概説する図である。

【図5】実施の形態1に係るDC−DCコンバータの昇圧動作を概説する図である。

【図6】実施の形態1に係るDC−DCコンバータの昇圧動作を概説する図である。

【図7】実施の形態1に係るDC−DCコンバータの昇圧動作を概説する図である。

【図8】実施の形態1に係るDC−DCコンバータの昇圧動作を概説する図である。

【図9】実施の形態1に係るDC−DCコンバータの昇圧動作における各種波形の一例を示す波形図である(ターンオフ)。

【図10】実施の形態1に係るDC−DCコンバータの昇圧動作における各種波形の一例を示す波形図である(ターンオン)。

【図11】実施の形態1に係るDC−DCコンバータの昇圧動作における各種波形の他の一例を示す波形図である(ターンオフ)。

【図12】実施の形態1に係るDC−DCコンバータの昇圧動作における各種波形の他の一例を示す波形図である(ターンオン)。

【図13】実施の形態2に係るDC−DCコンバータの構成を概説する回路図である。

【図14】実施の形態2に係るDC−DCコンバータの降圧動作における各種波形を概説する波形図である。

【図15】実施の形態2に係るDC−DCコンバータの降圧動作を概説する図である。

【図16】実施の形態2に係るDC−DCコンバータの降圧動作を概説する図である。

【図17】実施の形態2に係るDC−DCコンバータの降圧動作を概説する図である。

【図18】実施の形態2に係るDC−DCコンバータの降圧動作を概説する図である。

【図19】実施の形態2に係るDC−DCコンバータの降圧動作を概説する図である。

【図20】実施の形態2に係るDC−DCコンバータの降圧動作における各種波形の一例を示す波形図である(ターンオフ)。

【図21】実施の形態2に係るDC−DCコンバータの降圧動作における各種波形の一例を示す波形図である(ターンオン)。

【図22】実施の形態2に係るDC−DCコンバータの降圧動作における各種波形の他の一例を示す波形図である(ターンオフ)。

【図23】実施の形態2に係るDC−DCコンバータの降圧動作における各種波形の他の一例を示す波形図である(ターンオン)。

【図24】実施の形態3に係るDC−DCコンバータの構成を概説する回路図である。

【図25】実施の形態4に係るDC−DCコンバータの構成を概説する回路図である。

【図26】実施の形態4に係るDC−DCコンバータのスイッチングを概説する波形図である。

【図27】実施の形態5に係るDC−DCコンバータの構成を概説する回路図である。

【図28】実施の形態6に係るDC−DCコンバータの構成を概説する回路図である。

【図29】実施の形態6に係るDC−DCコンバータの構成を概説する回路図である。

【図30】実施の形態7に係るDC−DCコンバータの装置構造を概説する断面図である。

【発明を実施するための形態】

【0010】

<実施の形態1>

図1に実施の形態1に係るDC−DCコンバータ(以下、コンバータと略称する場合もある)1Aの構成を概説する回路図を示す。図1に例示されるようにコンバータ1Aは低電圧側装置5と高電圧側装置6との間に接続されて使用される。換言すれば、コンバータ1Aの低電圧側接続端に低電圧側装置5が接続され、コンバータ1Aの高電圧側接続端に高電圧側装置6が接続される。

【0011】

コンバータ1Aは、昇圧型のコンバータであり、低電圧側接続端の電圧V1を電圧V2(>V1)に昇圧して高電圧側接続端に出力するという昇圧動作を実行可能な構成を有している。換言すれば、コンバータ1Aは、低電圧側装置5によって印加される電圧V1を電圧V2に昇圧し、昇圧した電圧V2を高電圧側装置6へ供給する。

【0012】

なお、昇圧動作において、低電圧側接続端は入力側または1次側とも称され、高電圧側接続端は出力側または2次側とも称される。

【0013】

昇圧動作に対応して、以下では低電圧側装置5が直流電源(DC電源)である場合を例示し、低電圧側装置5をDC電源5とも称することにする。また、高電圧側装置6が各種負荷である場合を例示し、高電圧側装置6を負荷6とも称することにする。

【0014】

また、以下ではコンバータ1Aが相対的に高電圧および大電流を扱う電力用装置として構成される場合を例示するが、コンバータ1Aは例えばエレクトロニクス製品、家電製品等の分野に適合するように構成することも可能である。

【0015】

<コンバータ1Aの構成>

図1に例示のコンバータ1Aは、いわゆる非絶縁型の昇圧チョッパ回路を基本としている。コンバータ1Aは、コンデンサC1と、リアクトルL1と、スイッチング素子Q1と、ダイオードD2と、ダイオードD1と、コンデンサCsと、ダイオードDs1と、ダイオードDs2と、リアクトルLsと、コンデンサC2と、制御装置20とを含んでいる。なお、図中では制御装置20を「制御」と略記しており、後述の各種要素についても図中で名称を略記する場合がある。

【0016】

コンデンサC1は、DC電源5の正極に接続される一端と、DC電源5の負極に接続される他端とを有している。すなわち、コンデンサC1は、コンバータ1Aの利用時に、DC電源5に並列接続される。以下ではコンデンサC1を低電圧側コンデンサC1と称する場合もある。

【0017】

ここではコンデンサC1がコンバータ1Aに含まれる場合を例示するが、コンデンサC1はコンバータ1Aの外部部品として別個に準備しても構わない。また、コンデンサC1を設けない態様も採用可能である。

【0018】

なお、図1の例ではDC電源5の負極の電位がコンバータ1Aのグランド電位Nに選定されている。

【0019】

リアクトルL1は、その一端が低電圧側コンデンサC1の上記一端に接続されている。すなわち、リアクトルL1は、コンバータ1Aの利用時に、DC電源5の正極に接続される。また、リアクトルL1の他端は、スイッチング素子Q1とダイオードD2,D1とコンデンサCsとに接続されている。以下ではリアクトルL1を主リアクトルL1と称する場合もある。

【0020】

スイッチング素子Q1は、電流入力端と、電流出力端と、制御端とを有している。電流入力端は主リアクトルL1の上記他端に接続されている。電流出力端は、低電圧側コンデンサC1の上記他端に接続されており、これによりコンバータ1Aの利用時にはグランド電位Nに接続される。制御端は、制御装置20に接続されており、制御装置20から、電流入力端と電流出力端との間のオンオフを制御するための制御信号S21が入力される。以下ではスイッチング素子Q1を昇圧用スイッチング素子Q1と称する場合もある。

【0021】

ここでは、昇圧用スイッチング素子Q1が絶縁ゲートバイポーラトランジスタ(IGBT)で構成される場合を例示し、当該スイッチング素子Q1をトランジスタQ1とも称することにする。また、スイッチング素子Q1の電流入力端、電流出力端および制御端を、IGBTの端子に対応させて、コレクタ、エミッタおよびゲートとそれぞれ称する場合もある。なお、昇圧用スイッチング素子Q1として他の電力用半導体スイッチング素子を採用することも可能である。

【0022】

ダイオードD2は、昇圧用トランジスタQ1に対して逆並列に接続されている。すなわち、ダイオードD2のアノードはトランジスタQ1のエミッタに接続され、ダイオードD2のカソードはトランジスタQ1のコレクタに接続されている。なお、ダイオードD2とトランジスタQ1とによる逆並列接続構造が、主リアクトルL1の上記他端とグランド電位Nを与える地点との間に接続されている。ダイオードD2は、いわゆるフリーホイールダイオードである。なお、後述の昇圧動作の観点においてはダイオードD2を省略することも可能である。

【0023】

ダイオードD1は、そのアノードが主リアクトルL1の上記他端に接続され、そのカソードがダイオードDs1とリアクトルLsとに接続されている。以下ではダイオードD1を昇圧用ダイオードD1と称する場合もある。

【0024】

なお、ダイオードD1のカソードの側を、グランド電位Nの地点との対比において、高電位側Pと称する場合もある。また、ダイオードD1とトランジスタQ1との接続点を、グランド電位Nの地点および高電位側Pとの対比において、中間点Yと称する場合もある。

【0025】

コンデンサCsは、その一端がリアクトルL1の上記他端と、トランジスタQ1のコレクタと、ダイオードD2のカソードと、ダイオードD1のアノードとに接続されている。コンデンサCsの他端は、ダイオードDs1,Ds2に接続されている。以下ではコンデンサCsをスナバコンデンサCsと称する場合もある。

【0026】

ダイオードDs1は、そのカソードがスナバコンデンサCsの上記他端に接続されている。ダイオードDs1のアノードは、昇圧用ダイオードD1のカソードおよびリアクトルLsに接続されている。以下ではダイオードDs1を第1スナバダイオードDs1と称する場合もある。

【0027】

ダイオードDs2は、そのアノードが第1スナバダイオードDs1のカソードとスナバコンデンサCsの上記他端とに接続されている。ダイオードDs2のカソードは、リアクトルLsおよびコンデンサC2に接続されている。以下ではダイオードDs2を第2スナバダイオードDs2と称する場合もある。

【0028】

リアクトルLsは、その一端が第1スナバダイオードDs1のアノードと昇圧用ダイオードD1のカソードとに接続され、その他端が第2スナバダイオードDs2のカソードとコンデンサC2とに接続されている。以下ではリアクトルLs2をスナバリアクトルLsと称する場合もある。

【0029】

ここで、コンデンサCsと、ダイオードDs1,Ds2と、リアクトルLsとが、スナバ回路10を構成している。当該スナバ回路10の採用により、昇圧用トランジスタQ1のターンオフ時およびターンオン時におけるソフトスイッチングが実現される(後述する)。

【0030】

コンデンサC2は、その一端がスナバリアクトルLsの上記他端と第2スナバダイオードDs2のカソードとに接続されている。コンデンサC2の他端は、昇圧用トランジスタQ1のエミッタおよびダイオードD2のアノードに接続されている。これにより、コンデンサC2の他端はコンバータ1Aの利用時にグランド電位Nに設定される。以下ではコンデンサC2を高電圧側コンデンサC2と称する場合もある。高電圧側コンデンサC2に負荷6が並列接続される。

【0031】

制御装置20は、コンバータ1Aの各種処理を担う。制御装置20は、例えば、マイクロプロセッサ(MPU、CPU、マイクロコンピュータとも称される)と、当該マイクロプロセッサがアクセス可能に設けられたメモリとを含んで具現可能である。この例の場合、マイクロプロセッサが、メモリに予め格納されているプログラムに記述された処理ステップ(換言すれば処理手順)を実行することにより、各種処理が行われる。換言すれば、制御装置20が、各種処理に対応した各種手段として機能する。

【0032】

なお、上記マイクロプロセッサは例えばマルチプロセッサまたはマルチコアの構成を採用することも可能である。また、上記メモリは、例えばROM(Read Only Memory)、RAM(Random Access Memory)、書き換え可能な不揮発性メモリ(EPROM(Erasable Programmable ROM)等)の1つまたは複数を含んで構成可能である。メモリは、上記のようにプログラムを格納する他に、各種データ等を格納し、また、プログラムを実行するための作業領域を提供する。

【0033】

かかる構成例によれば制御装置20による各種処理はソフトウェアによって具現化されるが、かかる各種処理の一部または全部をハードウェアによって実現することも可能である。

【0034】

ここでは制御装置20がコンバータ1Aに含まれる場合を例示するが、制御装置20はコンバータ1Aの外部部品として別個に準備しても構わない。

【0035】

制御装置20は例えば、昇圧用トランジスタQ1の動作を制御する手段として機能する。より具体的に当該手段は、トランジスタQ1のゲートに対する電圧印加を制御することによってトランジスタQ1のオンオフを制御する。この場合、当該手段から出力されるゲート電圧がトランジスタQ1のスイッチング制御信号S21にあたる。

【0036】

図2に制御信号S21の波形図、換言すればトランジスタQ1の動作を概説する波形図を示す。図2に例示の矩形パルスのデューティ比は制御装置20によって制御され、これによりトランジスタQ1がパルス幅変調(PWM)によってオンオフ制御される。デューティ比は昇圧電圧V2の設定値に応じて決定される。換言すれば、デューティ比の設定によって昇圧電圧V2の値が制御される。なお、制御信号S21の波形は図2に例示される矩形波に限定されるものではない。

【0037】

<コンバータ1Aの昇圧動作>

図3〜図10も参照して、コンバータ1Aの昇圧動作を説明する。

【0038】

図3は昇圧動作における各種波形を概説する図であり、図3の上段は主リアクトルL1に流れる電流(リアクトル電流)の概略波形を示し、図3の下段は昇圧用トランジスタQ1のコレクタ電流Icおよびコレクタ−エミッタ間電圧Vceの概略波形を示している。

【0039】

図4〜図8は昇圧動作における各種タイミングでの電流の流れを概説している。図4〜図8中の回路図は基本的には図1と同じであるが、制御装置20およびダイオードD2の図示を省略している。

【0040】

図9は昇圧用トランジスタQ1がターンオフする際の各種波形の一例を示す波形図である。図9の下段はトランジスタQ1のコレクタ電流Icおよびコレクタ−エミッタ間電圧Vceを示し、図9の上段はターンオフ時の電力(換言すればスイッチング損失)Poffを示している。図9には比較のためにスナバ回路10(図1参照)を有さない場合(ハードスイッチング)の波形も示している。図10は昇圧用トランジスタQ1がターンオンする際の各種波形の一例を示す波形図であり、図9と同様に図示されている。なお、図9および図10の波形はシミュレーション結果の一例である。

【0041】

<トランジスタQ1がオン状態(i)(図3参照)>

図4に示されるようにDC電源5の正極から主リアクトルL1とトランジスタQ1とを通ってDC電流5の負極へ至る経路に、電流が流れる。これにより主リアクトルL1はエネルギーを蓄積していく。

【0042】

また、当該オン状態(i)ではスナバコンデンサCsが、スナバリアクトルLsと第1スナバダイオードDs1とを介して、高電圧側接続端の電圧V2によって、完全に充電されている。

【0043】

<トランジスタQ1がオン状態からオフ状態への過渡状態(ii)(図3参照)>

主リアクトルL1を流れる電流は、図5に示されるように、スナバコンデンサCsと第2スナバダイオードDs2と高電圧側コンデンサC2とを通る。ここで、スナバ回路10を有さないハードスイッチングの場合、当該電流はダイオードD1を通る経路を流れる。これに対し、スナバ回路10を有するコンバータ1Aの場合、スナバコンデンサCsが低インピーダンス経路として働くので、上記経路を辿って電流が流れる。

【0044】

当該過渡状態(ii)では、トランジスタQ1の電流Icがターンオフする一方で、スナバコンデンサCsが放電するのでトランジスタQ1の電圧Vceは徐々に増加する(図3および図9下段参照)。これにより、ターンオフ損失Poff(図9下段のグラフにおいて電流Icと電圧Vceとの重なり部分の面積に相関する)が減少する。図9上段のグラフによれば、コンバータ1Aによるソフトスイッチングの方がハードスイッチングに比べて、ターンオフ損失Poffが大幅に削減されることが分かる。

【0045】

このようにトランジスタQ1がオフした際にスナバコンデンサCsから第2スナバダイオードDs2を経由して高電圧側コンデンサC1が充電されるので、電圧Vceの立ち上がりを緩やかにすることができる。すなわちソフトスイッチングが実現される。かかるソフトスイッチングによればスイッチングエネルギーを、ハードスイッチングに比べて数分の1あるいはそれ以下にすることが可能である。

【0046】

<トランジスタQ1がオフ状態(iii)(図3参照)>

スナバコンデンサCsの放電後、主リアクトルL1に流れる電流は、図6に示されるように、ダイオードD1と第1スナバダイオードDs1と第2スナバダイオードDs2とを通って、高電圧側コンデンサC2へ流れる。なお、スナバダイオードDs1,Ds2に高い順方向降下電圧(VF)を持った高速回復仕様のダイオードを採用した場合、主リアクトルL1に流れる電流は主にダイオードD1とスナバリアクトルLsとに流れる。

【0047】

<トランジスタQ1がオフ状態からオン状態への過渡状態(iv)(図3参照)>

図7に示されるように主リアクトルL1に流れる電流がダイオードD1からトランジスタQ1へシフトすると、スナバリアクトルLsに流れる電流に変化が起こる。スナバリアクトルLsの電流変化と、この時点でスナバコンデンサCsは放電した状態にあるという状況とによって、トランジスタQ1の電圧Icが流れ始めると直ぐトランジスタQ1の電圧Vceは非常に低いレベルへ下降する(V=Ls×di/dt効果、換言すれば自己誘導による逆起電力の発生による)。

【0048】

そして、図8に示されるように高電圧側接続端の側から、換言すれば高電圧側コンデンサC2からスナバリアクトルLsと第1スナバダイオードDs1とを通って電流が流れ始め、これによりスナバコンデンサCsが充電される。

【0049】

したがって、ダイオードD1の逆回復段階までトランジスタQ1の電圧Vceが高電圧側接続端の電圧V2に留まっているハードスイッチングとは異なり、スナバ回路10によるソフトスイッチングによればターンオン損失Pon(図10下段のグラフにおいて電流Icと電圧Vceとの重なり部分の面積に相関する)が減少する。図10上段のグラフによれば、コンバータ1Aによるソフトスイッチングの方がハードスイッチングに比べて、ターンオン損失Ponが大幅に削減されることが分かる。

【0050】

なお、図11および図12に他の波形例(シミュレーション)を例示する。図11は昇圧用トランジスタQ1がターンオフする際の各種波形の他の一例である。図11の上段はスナバ回路10の採用によるソフトスイッチングの場合を示し、図11の下段はスナバ回路10の不採用によるハードスイッチングの場合を示している。また、図12は、トランジスタQ1がターンオンする際の各種波形の他の一例であり、図11と同様に図示されている。なお、図11および図12のソフトスイッチング波形が図9および図10と異なるのは、コンバータ1Aの各種素子の定数等を変えていることに因る。

【0051】

<効果>

上記のようにコンバータ1Aによれば、昇圧動作において、ターンオフ損失だけでなくターンオン損失も低減することができる。図11および図12の例によれば、ターンオフ損失とターンオン損失との合算について約50%近い低減効果が確認できる。

【0052】

なお、特許文献1においてゼロ電圧スイッチング用補助回路が、コンバータ1Aのスナバ回路10に相当すると考えられるが、両回路は配設位置が全く異なる。

【0053】

また、コンバータ1Aによれば、スイッチング損失の低減に伴って、スイッチング周波数を高くしても、装置の高効率化や小型化を図ることができる。つまり、高周波数化と高効率化と小型化とを同時的に推進することが可能になる。

【0054】

また、ソフトスイッチングにより、電磁ノイズの発生を抑えることができる。

【0055】

また、スナバ回路10は部品点数が少ないので、スナバ回路10を採用しても大幅な大型化およびコスト増大、さらには大型化による効率低減を抑制可能である。

【0056】

また、スナバ回路10はそれ自体に複雑な制御を必要としないので、ソフトスイッチングを簡便に実現できる。

【0057】

<実施の形態2>

図13に実施の形態2に係るコンバータ1Bの構成を概説する回路図を示す。コンバータ1Bは、いわゆる双方向昇降圧型(双方向型とも称される)のコンバータである。すなわち、コンバータ1Bは、低電圧側接続端の電圧V1を電圧V2に昇圧して高電圧側接続端に出力するという昇圧動作と、高電圧側接続端の電圧V2を電圧V1に降圧して低電圧側接続端に出力するという降圧動作との両方を実行可能な構成を有している。換言すれば、昇圧動作においてコンバータ1Bは、低電圧側装置5によって印加される電圧V1を電圧V2に昇圧し、昇圧した電圧V2を高電圧側装置6へ供給する。他方、降圧動作においてコンバータ1Bは、高電圧側装置6によって印加される電圧V2を電圧V1に降圧し、降圧した電圧V1を低電圧側装置5へ供給する。

【0058】

なお、昇圧動作で入力側または1次側と称される低電圧側接続端は、降圧動作では出力側または2次側にあたる。また、昇圧動作で出力側または2次側と称される高電圧側接続端は、降圧動作では入力側または1次側にあたる。

【0059】

実施の形態2では、低電圧側装置5がDC電源、特に充電池(二次電池とも称される)である場合を例示し、低電圧側装置5を充電池5とも称することにする。また、高電圧側装置6が、コンバータ1Bに接続されたインバータと、当該インバータに接続されたモータジェネレータ(電動発電機とも称される)とを含んだ装置である場合を例示し、高電圧側装置6をインバータ/モータジェネレータ6とも称することにする。当該例示の構成は、例えば電車、電気自動車、ハイブリッド自動車等の車両に搭載されている。

【0060】

当該例示の構成によれば、充電池5から出力されたDC電圧は、コンバータ1Bによって昇圧され、インバータで交流電圧によって変換され、モータジェネレータをモータとして回転させる。これによりモータジェネレータに接続された車輪が回転し、車両が力行する。

【0061】

これに対し、車両の制動時には、モータジェネレータがジェネレータとして働く。このため、モータジェネレータによって発電された交流電圧は、インバータによってDC電圧に変換され、コンバータ1Bによって降圧され、充電池5に充電される。つまり、モータジェネレータから電力が回生される。

【0062】

なお、以下ではコンバータ1Bが実施の形態1と同様に電力用装置として構成される場合を例示するが、コンバータ1Bの利用分野はこれに限定されるものではない。

【0063】

<コンバータ1Bの構成>

図13に例示のコンバータ1Bは、図1に例示したコンバータ1Aにスイッチング素子Q2を追加した構成を有している。コンバータ1Bの他の構成は基本的にコンバータ1Aと同様である。

【0064】

スイッチング素子Q2は、電流入力端と、電流出力端と、制御端とを有している。電流入力端は、ダイオードD1のカソードと、第1スナバダイオードDs1のアノードと、スナバリアクトルLsの上記一端とに接続されている。電流出力端は、ダイオードD1のアノードと、主リアクトルL1の上記他端と、スイッチング素子Q1の電流入力端(トランジスタQ1のコレクタ)と、ダイオードD2のカソードとに接続されている。なお、スイッチング素子Q2はダイオードD1に対して逆並列に接続されている。制御端は、制御装置20に接続されており、制御装置20から、電流入力端と電流出力端との間のオンオフを制御するための制御信号S22が入力される。なお、以下ではスイッチング素子Q2を降圧用スイッチング素子Q2と称する場合もある。

【0065】

ここでは、降圧用スイッチング素子Q2がIGBTで構成される場合を例示し、当該スイッチング素子Q2をトランジスタQ2とも称することにする。また、スイッチング素子Q2の電流入力端、電流出力端および制御端を、IGBTの端子に対応させて、コレクタ、エミッタおよびゲートとそれぞれ称する場合もある。なお、降圧用スイッチング素子Q2として他の電力用半導体スイッチング素子を採用することも可能である。

【0066】

なお、以下では、ダイオードD2を降圧用ダイオードD2と称し、ダイオードD1を昇圧用ダイオードD1と称する場合もある。

【0067】

降圧用トランジスタQ2の追加により、制御装置20は降圧用トランジスタQ2の動作を制御する手段としても機能する。より具体的に当該手段は、トランジスタQ2のゲートに対する電圧印加を制御することによってトランジスタQ2のオンオフを制御する。この場合、当該手段から出力されるゲート電圧がトランジスタQ2のスイッチング制御信号S22にあたる。制御信号S22は例えば図2の制御信号S21と同様の波形を有している。

【0068】

<コンバータ1Bの昇圧動作>

降圧用トランジスタQ2をオフにした状態でコンバータ1A(図1参照)と同様に駆動することにより、コンバータ1Bに昇圧動作を行わせることが可能である。このため、コンバータ1Bの昇圧動作は実施の形態1での説明を援用するに留め、ここでは繰り返しの説明を省略する。

【0069】

<コンバータ1Bの降圧動作>

昇圧用トランジスタQ1をオフにした状態で降圧用トランジスタQ2を駆動することにより、コンバータ1Bに降圧動作を行わせることが可能である。以下、図14〜図21も参照して、コンバータ1Bの降圧動作を説明する。

【0070】

図14は降圧動作における各種波形を概説する図であり、図14の上段は主リアクトルL1に流れる電流(リアクトル電流)の概略波形を示し、図14の下段は降圧用トランジスタQ2のコレクタ電流Icおよびコレクタ−エミッタ間電圧Vceの概略波形を示している。

【0071】

図15〜図19は降圧動作における各種タイミングでの電流の流れを概説している。図15〜図19中の回路図は基本的には図13と同じであるが、制御装置20と昇圧用トランジスタQ1と昇圧用ダイオードD1の図示を省略している。

【0072】

図20は降圧用トランジスタQ2がターンオフする際の各種波形の一例を示す波形図であり、図21は降圧用トランジスタQ2がターンオンする際の各種波形の一例を示す波形図である。図20および図21は既述の図9および図10と同様に図示されている。

【0073】

<トランジスタQ2がオン状態(i)(図14参照)>

図15に示されるように、インバータ/モータジェネレータ6から(換言すれば高電圧側コンデンサC2から)スナバリアクトルLsと降圧用トランジスタQ2と主リアクトルL1とを通って充電池5の正極へ至る経路に、電流が流れる。これにより主リアクトルL1はエネルギーを蓄積していく。

【0074】

また、当該オン状態(i)ではスナバコンデンサCsが、スナバリアクトルLsと第2スナバダイオードDs2とを介して、放電する。

【0075】

<トランジスタQ2がオン状態からオフ状態への過渡状態(ii)(図14参照)>

主リアクトルL1とスナバリアクトルLsとを流れる電流は、図16に示されるように、第1スナバダイオードDs1とスナバコンデンサCsとを通る。ここで、スナバ回路10を有さないハードスイッチングの場合、当該電流は降圧用ダイオードD2を通る経路を流れる。これに対し、スナバ回路10を有するコンバータ1Bの場合、降圧用ダイオードD2が導通可能になる前にスナバコンデンサCsが高電圧側接続端の電圧V2に充電されるので、上記経路を辿って電流が流れる。

【0076】

当該過渡状態(ii)では、トランジスタQ2の電流Icがターンオフする一方で、スナバコンデンサCsが充電されるのでトランジスタQ2の電圧Vceは徐々に増加する(図14および図20下段参照)。これにより、ターンオフ損失Poff(図20下段のグラフにおいて電流Icと電圧Vceとの重なり部分の面積に相関する)が減少する。図20上段のグラフによれば、コンバータ1Bによるソフトスイッチングの方がハードスイッチングに比べて、ターンオフ損失Poffが大幅に削減されることが分かる。

【0077】

<トランジスタQ2がオフ状態(iii)(図14参照)>

スナバコンデンサCsの充電後、主リアクトルL1に流れる電流は、図17に示されるように、降圧用ダイオードD2を通って充電池5へ(換言すれば低電圧側接続端の側へ)流れ続ける。

【0078】

スナバコンデンサCsの充電中に主リアクトルL1に蓄積されたエネルギーは、スナバリアクトルLsと第1スナバダイオードDs1と第2スナバダイオードとを通る経路に電流を環流させる。

【0079】

<トランジスタQ2がオフ状態からオン状態への過渡状態(iv)(図14参照)>

図18に示されるように主リアクトルL1に流れる電流がダイオードD2からトランジスタQ2へシフトすると、スナバリアクトルLsに流れる電流に変化が起こる。スナバリアクトルLsの電流変化と、この時点でスナバコンデンサCsは充電された状態にあるという状況とによって、トランジスタQ2の電圧Icが流れ始めると直ぐトランジスタQ2の電圧Vceは非常に低いレベルへ下降する(V=Ls×di/dt効果、換言すれば自己誘導による逆起電力の発生による)。

【0080】

そして、図19に示されるように完全に充電されたスナバコンデンサCsから、スナバリアクトルLsと第2スナバダイオードDs2とを通って電流が流れ始め、これによりスナバコンデンサCsが放電する。

【0081】

したがって、ダイオードD2の逆回復段階までトランジスタQ2の電圧Vceが高電圧側接続端の電圧V2に留まっているハードスイッチングとは異なり、スナバ回路10によるソフトスイッチングによればターンオン損失Pon(図21下段のグラフにおいて電流Icと電圧Vceとの重なり部分の面積に相関する)が減少する。図21上段のグラフによれば、コンバータ1Bによるソフトスイッチングの方がハードスイッチングに比べて、ターンオン損失Ponが大幅に削減されることが分かる。

【0082】

なお、図22および図23に他の波形例(シミュレーション)を例示する。図22は降圧用トランジスタQ2がターンオフする際の各種波形の他の一例であり、図23はトランジスタQ1がターンオンする際の各種波形の他の一例である。図22および図23は既述の図11および図12と同様に図示されている。なお、図22および図23のソフトスイッチング波形が図20および図21と異なるのは、コンバータ1Bの各種素子の定数等を変えていることに因る。

【0083】

<効果>

コンバータ1Bによれば、昇圧動作だけでなく、降圧動作においてもターンオフ損失とターンオン損失との両方を低減することができる。図22および図23の例によれば、ターンオフ損失とターンオン損失との合算について約40%近い低減効果が確認できる。また、コンバータ1Bによれば、上記コンバータ1Aが奏するその他の効果も得ることができる。

【0084】

<実施の形態3>

図24に実施の形態3に係るコンバータ1Cの構成を概説する回路図を示す。図24に例示のコンバータ1Cは、実施の形態2に係る双方向昇降圧型コンバータ1B(図13参照)から昇圧用トランジスタQ1を削除した構成を有している。すなわち、コンバータ1Cは降圧型に特化されている。コンバータ1Cの他の構成は基本的にコンバータ1Bと同様である。なお、降圧動作の観点においては昇圧用ダイオードD1を省略することも可能である。

【0085】

なお、実施の形態3では、低電圧側装置5が各種負荷や充電池であり、高電圧側装置6がDC電源(交流ジェネレータとインバータとを組み合わせた装置等であってもよい)である場合が例示される。

【0086】

コンバータ1Cによれば、降圧動作において、ターンオフ損失とターンオン損失との両方を低減することができる。また、コンバータ1Cによれば、上記コンバータ1Bが奏するその他の効果も得ることができる。

【0087】

<実施の形態4>

図25に実施の形態4に係るコンバータ1Dの構成を概説する回路図を示す。図25に例示のコンバータ1Dは、実施の形態2に係る双方向昇降圧型コンバータ1B(図13参照)においてトランジスタQ1,Q2およびダイオードD1,D2のそれぞれを複数個設けた構成を有している。コンバータ1Dの他の構成は基本的にコンバータ1Bと同様である。

【0088】

より具体的には、複数の昇圧用トランジスタQ1は同じ向きで並列接続されており、いずれのトランジスタQ1も電流入力端が主リアクトルL1の上記他端に接続され、電流出力端がグランド電位Nの地点に接続されている。

【0089】

また、複数の降圧用トランジスタQ2は同じ向きで並列接続されており、いずれのトランジスタQ2も電流入力端がスナバリアクトルLsの上記一端および第1スナバダイオードDs1のアノードに接続され、電流出力端が主リアクトルL1の上記他端に接続されている。

【0090】

また、複数の昇圧用ダイオードD1は、同じ向きで並列接続されているとともに、複数の降圧用トランジスタQ2に対して逆並列に接続されている。

【0091】

また、複数の降圧用ダイオードD2は、同じ向きで並列接続されているとともに、複数の昇圧用トランジスタQ1に対して逆並列に接続されている。

【0092】

ここでは、コンバータ1Dの各トランジスタQ1の素子容量(換言すれば素子性能)は、コンバータ1B(図13参照)の単一のトランジスタQ1の素子容量よりも小さく設定されている。例えば、コンバータ1Dの各トランジスタQ1の素子容量は、コンバータ1Bの単一のトランジスタQ1の素子容量を等分割した程度に設定される。かかる点はトランジスタQ2およびダイオードD1,D2についても同様である。

【0093】

トランジスタQ1,Q2の個数に対応して、制御装置20はこれらのトランジスタQ1,Q2の動作を制御する。より具体的には、制御装置20は、昇圧動作では、全ての降圧用トランジスタQ2をオフに制御するとともに、複数の昇圧用トランジスタQ1をタイミングをずらして順番にオンさせる手段として機能する。他方、降圧動作において制御装置20は、全ての昇圧用トランジスタQ1をオフに制御するとともに、複数の降圧用トランジスタQ2をタイミングをずらし順番にオンさせる手段として機能する。

【0094】

図26に昇圧用トランジスタQ1のスイッチング制御信号S21の波形図、換言すればトランジスタQ1の動作を概説する波形図を示す。図26には、2つの昇圧用トランジスタQ1(符号Q1a,Q1bで区別することにする)が設けられ、トランジスタQ1a用の制御信号S21として制御信号S21aが用いられ、トランジスタQ1b用の制御信号S21として制御信号S21bが用いられる場合を例示している。図26に示されるように、制御信号S21a,21bはオン期間のタイミングがずれており、昇圧動作では当該制御信号S21a,21bによってトランジスタQ1a,Q1bのオンオフのタイミングをずらすことが可能である。3つ以上の昇圧用トランジスタQ1および複数の降圧用トランジスタQ2も同様に駆動される。

【0095】

コンバータ1Dによれば、コンバータ1A〜1Cが奏する効果を得ることができるとともに、コンバータ1A〜1Cよりも更に高周波数駆動が可能になる。

【0096】

なお、コンバータ1Dをコンバータ1A,1Cの構成に倣って昇圧型または降圧型に変形してもよい。また、トランジスタQ1,Q2の一方をコンバータ1A〜1Cと同様に単一のトランジスタで構成してもよい。また、ダイオードD1,D2の一方または両方をコンバータ1A〜1Cと同様に単一のダイオードで構成してもよい。また、複数のトランジスタQ1を同じタイミングで一括駆動してもよく、複数のトランジスタQ2についても同様である。

【0097】

<実施の形態5>

図27に実施の形態5に係るコンバータ1Eの構成を概説する回路図を示す。図27に例示のコンバータ1Eは、実施の形態2に係る双方向昇降圧型コンバータ1B(図13参照)の一部が多重化された構成を有している。

【0098】

より具体的には、同じ構成を有した2個の単位回路40が並列接続されることによって多重化されている。図27に例示の単位回路40は、実施の形態2に係る双方向昇降圧型コンバータ1B(図13参照)における主リアクトルL1とトランジスタQ1,Q2とダイオードD1,D2とスナバ回路10とによって構成されている。

【0099】

そして図27の例では、2つの単位回路40は、主リアクトルL1の上記一端どうし、高電位側Pの地点どうし、グランド電位Nの地点どうし、スナバリアクトルLsと第2スナバダイオードDs2との接続点どうしが等電位に接続されることによって、多重化されている。かかる構成例ではコンデンサC1,C2は2つの単位回路40によって共用されている。

【0100】

合計2つの昇圧用トランジスタQ1は、昇圧動作において、タイミングをずらして順番にオンさせてもよいし、あるいは、同じタイミングで一括してオンさせてもよい。合計2つの降圧用トランジスタQ2についても同様である。

【0101】

コンバータ1Eによれば、コンバータ1A〜1Dが奏する効果を得ることができるとともに、リップル電流を抑制することができる。また、リップル電流の抑制はコンデンサC1,C2の容量削減を可能にするので、コンデンサC1,C2の小型化、更には装置の小型化を図ることができる。

【0102】

なお、3個以上の単位回路40を多重化してもよい。また、単位回路40をコンバータ1A,1Cの構成に倣って昇圧型または降圧型に変形してもよい。また、トランジスタQ1,Q2の一方または両方をコンバータ1Dの構成に倣って複数のトランジスタに変更してもよい。また、ダイオードD1,D2の一方または両方をコンバータ1Dの構成に倣って複数のダイオードに変更してもよい。

【0103】

<実施の形態6>

図28に実施の形態6に係るコンバータ1Fの構成を概説する回路図を示す。図28に例示のコンバータ1Fは、実施の形態4に係る双方向昇降圧型コンバータ1D(図25参照)に昇圧用検出手段51および降圧用検出手段52を追加した構成を有している。コンバータ1Fの他の構成は基本的にコンバータ1Dと同様である。

【0104】

昇圧用検出手段51は、複数の昇圧用トランジスタQ1の動作状態に関する情報を検出し、検出結果S51を制御装置20へ送信する。また、降圧用検出手段52は、複数の降圧用トランジスタQ2の動作状態に関する情報を検出し、検出結果S52を制御装置20へ出力する。

【0105】

昇圧用検出手段51は、昇圧用トランジスタQ1のそれぞれにセンサ等を取り付けることによって全部のトランジスタQ1について情報検出を行うように構成されてもよいし、あるいは、一部の昇圧用トランジスタQ1についてのみ代表的に情報検出を行うように構成されてもよい。降圧用検出手段52についても同様である。

【0106】

制御装置20は、検出手段51,52による検出結果S51,S52を取得し、当該検出結果S51,S52に基づいてトランジスタQ1,Q2の動作を、予め規定された最適状態になるように制御する手段として機能する。

【0107】

スナバ回路10自体に複雑な制御を必要としないことはコンバータ1Fにおいても同様である。このため、検出結果に基づいてスイッチングトランジスタと共にスナバ回路も制御する構成に比べて、コンバータ1Fは制御方式が簡易である。また、制御方式が簡易であることは制御時間の短縮化、換言すればリアルタイム制御を可能にする。

【0108】

ここで、上記のように昇圧用検出手段51による検出対象は全部のトランジスタQ1であってもよいし、一部のトランジスタQ1であってもよい。但し、全てのトランジスタQ1の動作状態を検出することにより、各トランジスタQ1を検出結果に応じて個別に制御することが可能になる。かかる詳細な個別制御によれば、例えば複数のトランジスタQ1を平均的に動作させることができ、高効率化や高寿命化に寄与する。なお、かかる効果を奏する動作状態が上記最適状態の例である。かかる点は降圧用検出手段52についても同様である。

【0109】

例えば検出結果S51に基づくトランジスタQ1の動作制御には、複数の昇圧用トランジスタQ1の中から駆動させるトランジスタQ1を検出結果S51に基づいて選択する処理が含まれる。これによれば、トランジスタQ1の選択を動作中にリアルタイムで行うので、複数のトランジスタQ1を平均的、安定的に動作させることができ、更には高効率化や高寿命化に寄与する。なお、かかる効果を奏する動作状態も上記最適状態の例である。また、トランジスタQ1の選択処理によれば、製造時にトランジスタQ1の特性の選別、換言すれば特性ばらつきのランク付けおよびその管理を行う必要が無くなるので、製造工程数、製造コスト等を削減することができる。かかる点は降圧用トランジスタQ2の選択処理についても同様である。

【0110】

検出手段51,52が検出する上記情報として、トランジスタQ1,Q2のコレクタ電流が例示される。電流は例えば既知の各種手段によって測定可能であるので、かかる例では検出手段51,52にそのような電流測定手段を設ければよい。コレクタ電流に基づいた制御によれば、例えば、低電流時にはテイル電流が延びる傾向があるので、スイッチング周波数を上げてこれを抑制することが可能になる。また、大電流時にはサージ電流の懸念があるので、スイッチング周波数を下げてこれを抑制することが可能になる。これらの制御も上記最適状態を得るための制御例である。

【0111】

また、検出手段51,52が検出する上記情報として、トランジスタQ1,Q2の温度が例示される。温度は例えば既知の各種手段によって測定可能であるので、かかる例では検出手段51,52にそのような温度測定手段を設ければよい。素子温度に基づいた制御によれば、例えば、最大接合温度に到達しないようにトランジスタQ1,Q2の動作を制御することが可能になる。また、各トランジスタを発熱の観点からバランスよく選択することが可能になる。これらは高寿命化に寄与する。これらの制御も上記最適状態を得るための制御例である。

【0112】

また、検出手段51,52を、トランジスタQ1,Q2のコレクタ電流と、トランジスタQ1,Q2の温度との両方を検出するように構成してもよい。これによれば、電流と温度とのいずれかのみを検出する場合に比べて、最適化を高精度に行うことが可能になる。その結果、高効率化、ノイズ低減、損失低減等を図ることができる。

【0113】

また、例えばトランジスタQ1の動作制御には、駆動させるトランジスタQ1のゲート抵抗(すなわちスイッチング素子Q1の制御端への入力抵抗)を制御する処理が含まれる。

【0114】

ゲート抵抗制御は例えば図29の構成によって行うことが可能である。なお、図29は1つのトランジスタQ1について簡略的に例示している。図29の例において、トランジスタQ1のゲートには可変抵抗手段53が接続されており、当該可変抵抗手段53の抵抗値は制御装置20からの制御信号S23によって設定可能である。かかる構成例によれば、制御装置20が、検出手段51からの検出結果S51に基づいて可変抵抗手段53の抵抗値を制御することが可能である。なお、可変抵抗手段53は例えば、抵抗値を変更可能な既知の各種構成を採用可能である。降圧用トランジスタQ2のゲート抵抗の制御についても同様である。

【0115】

例えば、トランジスタQ1,Q2のターンオフ直後においてゲート抵抗を相対的に高くすることによって、ターンオフ時の電流変化が緩やかになり、その結果、スイッチングサージ電圧を抑制することができる。また、サージ電圧の抑制によって、放射ノイズを抑制することができる。また、例えば、ゲート抵抗を上記増大の後に相対的に低くしてトランジスタQ1,Q2のターンオフ速度を上げることにより、スイッチング損失を低減することができる。なお、これらの効果を奏する動作状態が上記最適状態の例である。

【0116】

なお、検出手段51,52はコンバータ1A等と組み合わせることも可能であり、コンバータ1A等が奏する効果も得ることができる。

【0117】

<実施の形態7>

実施の形態7では上記各種のコンバータの装置構造を説明する。図30に、実施の形態7に係るコンバータ1Gの断面図を例示する。なお、図面の煩雑化を避けるため図30では一部の要素についてハッチングを省略している。コンバータ1Gは、ここでは実施の形態2に係るコンバータ1B(図13)に相当するものとして説明するが、以下の説明は他のコンバータ1A(図1参照)等にも当てはまる。

【0118】

図30の例によればコンバータ1Gは、放熱板101と、ケース102と、ふた103とを含んでいる。

【0119】

放熱板101は例えば銅等の金属で構成されている。放熱板101は各種要素が実装されるベース板としての役割もある。

【0120】

ケース102は、放熱板101の周縁部に立設し放熱板102と共に凹状容器を形成する部分を有している。図30の例では、ケース102は上記凹状容器の内側へ、換言すれば放熱板101の中央部側へ突出した部分も有している。ケース102は例えばポリフェニレンスルファイド(PPS)等の絶縁性材料で構成されている。

【0121】

ケース103には、端子や電極等を構成する種々の導電性部品111〜114が設けられている。なお、これらの部品111〜114は図30に図示される個数に限定されるものではない。例えば端子111は不図示の位置にも設けられており、複数の端子111が低電圧側接続端および高電圧側接続端に対応する。

【0122】

ふた103は、放熱板102とは反対側においてケース103に取り付けられている。ふた103は例えばPPS等の絶縁性材料で構成されている。

【0123】

コンバータ1Gは、さらに、絶縁性基板121と、電力用半導体チップ122,123と、コンデンサ124とをケース102内(換言すれば上記凹状容器内)に含んでいる。

【0124】

絶縁性基板121は、例えばセラミック等の絶縁性材料で構成されており、はんだ等によって放熱板101上に接合されている。

【0125】

電力用半導体チップ122,123は、はんだ等によって絶縁性基板121上に接合されている。電力用半導体チップ122,123には電力用半導体素子(コンバータ1B(図13参照)の例によればトランジスタQ1,Q2およびダイオードD1,D2,Ds1,Ds2)が作り込まれている。電力用半導体チップ122,123は図30の例ではワイヤによって電気的結線がなされて所定の電気回路を構成している。

【0126】

コンデンサ124は、スナバコンデンサCsであり、放熱板101に接触させて配置されている。スナバコンデンサ124はコンバータ1Gの動作時に発熱するので、かかる配置態様によればスナバコンデンサ124の発熱を放熱板101へ効率良く伝達し放熱させることができる。このため、スナバコンデンサ124の容量を低減することができ、さらに容量低減によって小型化を図ることができる。

【0127】

コンデンサ124の端子125は、はんだ付けと、溶接と、超音波接合と、ネジ締めとのうちの少なくとも1つの接続手法によって、ケース102に設けられた電極114に接続されている。接続手法はコンデンサ124の端子125とケース電極114との位置、姿勢等に応じて適宜選択すればよく、適切な接続手法によってコンデンサ124とケース電極114との接続を効率良く行うことができる。また、適切な接続手法によれば、接続箇所の高寿命化、換言すればコンバータ1Gの高寿命化を図ることができる。

【0128】

電力用半導体チップ122,123等は充填材126によって封止されている。充填材126として例えばシリコン樹脂やエポキシ樹脂等が用いられる。

【0129】

なお、図30には図示されていないが、コンデンサC1,C2とリアクトルL1,Lsとのうちの一部または全部をケース102の内部に配置してもよいし、あるいはケース102の外部に配置してもよい。

【0130】

上記のようにトランジスタQ1,Q2と、スナバコンデンサCs(図30ではコンデンサ124)と、スナバダイオードDs1,Ds2とが単一のケース102内に集約されている。このため、各素子を繋ぐ配線を短縮化して配線インダクタンスを低減することができる。また、配線インダクタンスの低減によって、サージを低減することができる。

【0131】

コンバータ1Gは、さらに、制御基板131と、シールド板132とをケース102内に含んでいる。

【0132】

制御基板131は、制御装置20(図13等参照)が形成された基板であり、図30の例では電極112に接続されている。

【0133】

シールド板132は、制御基板131と電力用半導体チップ122,123との間に配置され、制御装置20と電力用半導体チップ122,123との間の電気的(または電磁的)干渉を遮蔽する。シールド板132は例えば導電性材料によって構成されている。

【0134】

なお、制御基板131はケース102の外部に配置される場合もあり、これに伴ってシールド板132もケース102の外部に配置される場合もある。

【符号の説明】

【0135】

1A〜1G DC−DCコンバータ、20 制御装置、40 単位回路、51,52 検出手段、53 可変抵抗手段、101 放熱板、102 ケース、114 電極、C1 低電圧側コンデンサ、C2 高電圧側コンデンサ、Cs,124 スナバコンデンサ、D1 昇圧用ダイオード、D2 降圧用ダイオード、Ds1 第1スナバダイオード、Ds2 第2スナバダイオード、L1 主リアクトル、Ls スナバリアクトル、Q1 昇圧用スイッチング素子、Q2 降圧用スイッチング素子、S21,S22 制御信号、S51,S52 検出結果。

【特許請求の範囲】

【請求項1】

一端および他端を有する主リアクトルと、

前記主リアクトルの前記他端に接続された電流入力端と、グランド電位に接続される電流出力端と、当該電流入力端と当該電流出力端との間のオンオフを制御するための制御信号が入力される制御端とを有する、少なくとも1つの昇圧用スイッチング素子と、

前記少なくとも1つの昇圧用スイッチング素子の前記電流入力端と前記主リアクトルの前記他端とに接続されたアノードを有する少なくとも1つの昇圧用ダイオードと、

前記少なくとも1つの昇圧用ダイオードの前記アノードと前記少なくとも1つの昇圧用スイッチング素子の前記電流入力端と前記主リアクトルの前記他端とに接続された一端を有するスナバコンデンサと、

前記スナバコンデンサの他端に接続されたカソードと、前記少なくとも1つの昇圧用ダイオードのカソードに接続されたアノードとを有する第1スナバダイオードと、

前記第1スナバダイオードのカソードと前記スナバコンデンサの前記他端とに接続されたアノードを有する第2スナバダイオードと、

前記第1スナバダイオードの前記アノードに接続された一端と、前記第2スナバダイオードのカソードに接続された他端とを有するスナバリアクトルと、

前記スナバリアクトルの前記他端と前記第2スナバダイオードの前記カソードとに接続された一端と、前記グランド電位に接続される他端とを有するコンデンサと

を備えるDC−DCコンバータ。

【請求項2】

請求項1に記載のDC−DCコンバータであって、

前記少なくとも1つの昇圧用スイッチング素子は、同じ向きで並列接続された複数の昇圧用スイッチング素子であり、

当該DC−DCコンバータは、前記複数の昇圧用スイッチング素子をタイミングをずらして順番にオンさせる手段をさらに備える、

DC−DCコンバータ。

【請求項3】

請求項1または請求項2に記載のDC−DCコンバータであって、

同じ構成を有し並列接続されることによって多重化された複数の単位回路を備え、

前記複数の単位回路のそれぞれが、前記主リアクトルと、前記少なくとも1つの昇圧用スイッチング素子と、前記少なくとも1つの昇圧用ダイオードと、前記スナバコンデンサと、前記第1スナバダイオードと、前記第2スナバダイオードと、前記スナバリアクトルとを含む、

DC−DCコンバータ。

【請求項4】

請求項1ないし請求項3のうちのいずれか1項に記載のDC−DCコンバータであって、

前記少なくとも1つの昇圧用スイッチング素子のうちの一部または全部の素子の動作状態に関する情報を検出する昇圧用検出手段と、

前記昇圧用検出手段による検出結果に基づいて前記少なくとも1つの昇圧用スイッチング素子の動作を制御する手段と

をさらに備えるDC−DCコンバータ。

【請求項5】

請求項4に記載のDC−DCコンバータであって、

前記少なくとも1つの昇圧用スイッチング素子は、同じ向きで並列接続された複数の昇圧用スイッチング素子であり、

前記昇圧用検出手段は、前記複数の昇圧用スイッチング素子のそれぞれの動作状態に関する情報を検出する、

DC−DCコンバータ。

【請求項6】

請求項5に記載のDC−DCコンバータであって、

前記少なくとも1つの昇圧用スイッチング素子の動作を制御する前記手段は、前記昇圧用検出手段による前記検出結果に基づいて、前記複数の昇圧用スイッチング素子の中から駆動させる素子を選択する、DC−DCコンバータ。

【請求項7】

請求項4ないし請求項6のうちのいずれか1項に記載のDC−DCコンバータであって、

前記昇圧用検出手段が検出する前記情報は、

前記少なくとも1つの昇圧用スイッチング素子に流れる電流と、

前記少なくとも1つの昇圧用スイッチング素子の温度と

のうちの少なくとも一方を含む、DC−DCコンバータ。

【請求項8】

請求項4ないし請求項7のうちのいずれか1項に記載のDC−DCコンバータであって、

前記少なくとも1つの昇圧用スイッチング素子の動作を制御する前記手段は、前記少なくとも1つの昇圧用スイッチング素子の前記制御端への入力抵抗を制御することによって、前記少なくとも1つの昇圧用スイッチング素子の動作を制御する、DC−DCコンバータ。

【請求項9】

請求項1ないし請求項8のうちのいずれか1項に記載のDC−DCコンバータであって、

前記少なくとも1つの昇圧用スイッチング素子と、前記少なくとも1つの昇圧用ダイオードと、前記スナバコンデンサと、前記第1スナバダイオードと、前記第2スナバダイオードとが、単一のケース内に集約されている、DC−DCコンバータ。

【請求項10】

請求項9に記載のDC−DCコンバータであって、

前記スナバコンデンサに接触している放熱板をさらに備えるDC−DCコンバータ。

【請求項11】

請求項10に記載のDC−DCコンバータであって、

前記スナバコンデンサは、はんだ付けと、溶接と、超音波接合と、ネジ締めとのうちの少なくとも1つの接続手法によって、前記ケースの電極に接続されている、DC−DCコンバータ。

【請求項12】

請求項1ないし請求項11のうちのいずれか1項に記載のDC−DCコンバータであって、

前記少なくとも1つの昇圧用ダイオードの前記カソードに接続された電流入力端と、前記少なくとも1つの昇圧用ダイオードの前記アノードに接続された電流出力端と、当該電流入力端と当該電流出力端との間のオンオフを制御するための制御信号が入力される制御端とを有する、少なくとも1つの降圧用スイッチング素子と、

前記少なくとも1つの昇圧用スイッチング素子の前記電流入力端および前記電流出力端にそれぞれ接続されたカソードおよびアノードを有する、少なくとも1つの降圧用ダイオードと

をさらに備えるDC−DCコンバータ。

【請求項13】

一端および他端を有する主リアクトルと、

前記主リアクトルの前記他端に接続された電流出力端と、電流入力端と、当該電流入力端と当該電流出力端との間のオンオフを制御するための制御信号が入力される制御端とを有する、少なくとも1つの降圧用スイッチング素子と、

前記少なくとも1つの降圧用スイッチング素子の前記電流出力端と前記主リアクトルの前記他端とに接続されたカソードと、グランド電位に接続されるアノードとを有する、少なくとも1つの降圧用ダイオードと、

前記少なくとも1つの降圧用ダイオードの前記カソードと前記少なくとも1つの降圧用スイッチング素子の前記電流出力端と前記主リアクトルの前記他端とに接続された一端を有するスナバコンデンサと、

前記スナバコンデンサの他端に接続されたカソードと、前記少なくとも1つの降圧用スイッチング素子の前記電流入力端に接続されたアノードとを有する第1スナバダイオードと、

前記第1スナバダイオードのカソードと前記スナバコンデンサの前記他端とに接続されたアノードを有する第2スナバダイオードと、

前記第1スナバダイオードの前記アノードに接続された一端と、前記第2スナバダイオードのカソードに接続された他端とを有するスナバリアクトルと、

前記スナバリアクトルの前記他端と前記第2スナバダイオードの前記カソードとに接続された一端と、前記グランド電位に接続される他端とを有するコンデンサと

を備えるDC−DCコンバータ。

【請求項14】

請求項12または請求項13に記載のDC−DCコンバータであって、

前記少なくとも1つの降圧用スイッチング素子は、同じ向きで並列接続された複数の降圧用スイッチング素子であり、

当該DC−DCコンバータは、前記複数の降圧用スイッチング素子をタイミングをずらして順番にオンさせる手段をさらに備える、

DC−DCコンバータ。

【請求項15】

請求項3を引用する請求項12に記載のDC−DCコンバータであって、

前記複数の単位回路のそれぞれが、前記少なくとも1つの降圧用スイッチング素子と、前記少なくとも1つの降圧用ダイオードとをさらに含む、DC−DCコンバータ。

【請求項16】

請求項13に記載のDC−DCコンバータであって、

同じ構成を有し並列接続されることによって多重化された複数の単位回路を備え、

前記複数の単位回路のそれぞれが、前記主リアクトルと、前記少なくとも1つの降圧用スイッチング素子と、前記少なくとも1つの降圧用ダイオードと、前記スナバコンデンサと、前記第1スナバダイオードと、前記第2スナバダイオードと、前記スナバリアクトルとを含む、

DC−DCコンバータ。

【請求項17】

請求項12ないし請求項16のうちのいずれか1項に記載のDC−DCコンバータであって、

前記少なくとも1つの降圧用スイッチング素子のうちの一部または全部の素子の動作状態に関する情報を検出する降圧用検出手段と、

前記降圧用検出手段による検出結果に基づいて前記少なくとも1つの降圧用スイッチング素子の動作を制御する手段と

をさらに備えるDC−DCコンバータ。

【請求項18】

請求項17に記載のDC−DCコンバータであって、

前記少なくとも1つの降圧用スイッチング素子は、同じ向きで並列接続された複数の降圧用スイッチング素子であり、

前記降圧用検出手段は、前記複数の降圧用スイッチング素子のそれぞれの動作状態に関する情報を検出する、

DC−DCコンバータ。

【請求項19】

請求項18に記載のDC−DCコンバータであって、

前記少なくとも1つの降圧用スイッチング素子の動作を制御する前記手段は、前記降圧用検出手段による前記検出結果に基づいて、前記複数の降圧用スイッチング素子の中から駆動させる素子を選択する、DC−DCコンバータ。

【請求項20】

請求項17ないし請求項19のうちのいずれか1項に記載のDC−DCコンバータであって、

前記降圧用検出手段が検出する前記情報は、

前記少なくとも1つの降圧用スイッチング素子に流れる電流と、

前記少なくとも1つの降圧用スイッチング素子の温度と

のうちの少なくとも一方を含む、DC−DCコンバータ。

【請求項21】

請求項17ないし請求項20のうちのいずれか1項に記載のDC−DCコンバータであって、

前記少なくとも1つの降圧用スイッチング素子の動作を制御する前記手段は、前記少なくとも1つの降圧用スイッチング素子の前記制御端への入力抵抗を制御することによって、前記少なくとも1つの降圧用スイッチング素子の動作を制御する、DC−DCコンバータ。

【請求項22】

請求項9を引用する請求項12に記載のDC−DCコンバータであって、

前記少なくとも1つの降圧用スイッチング素子と、前記少なくとも1つの降圧用ダイオードとがさらに前記単一のケース内に集約されている、DC−DCコンバータ。

【請求項23】

請求項13に記載のDC−DCコンバータであって、

前記少なくとも1つの降圧用スイッチング素子と、前記少なくとも1つの降圧用ダイオードと、前記スナバコンデンサと、前記第1スナバダイオードと、前記第2スナバダイオードとが、単一のケース内に集約されている、DC−DCコンバータ。

【請求項24】

請求項23に記載のDC−DCコンバータであって、

前記スナバコンデンサに接触している放熱板をさらに備えるDC−DCコンバータ。

【請求項25】

請求項24に記載のDC−DCコンバータであって、

前記スナバコンデンサは、はんだ付けと、溶接と、超音波接合と、ネジ締めとのうちの少なくとも1つの接続手法によって、前記ケースの電極に接続されている、DC−DCコンバータ。

【請求項1】

一端および他端を有する主リアクトルと、

前記主リアクトルの前記他端に接続された電流入力端と、グランド電位に接続される電流出力端と、当該電流入力端と当該電流出力端との間のオンオフを制御するための制御信号が入力される制御端とを有する、少なくとも1つの昇圧用スイッチング素子と、

前記少なくとも1つの昇圧用スイッチング素子の前記電流入力端と前記主リアクトルの前記他端とに接続されたアノードを有する少なくとも1つの昇圧用ダイオードと、

前記少なくとも1つの昇圧用ダイオードの前記アノードと前記少なくとも1つの昇圧用スイッチング素子の前記電流入力端と前記主リアクトルの前記他端とに接続された一端を有するスナバコンデンサと、

前記スナバコンデンサの他端に接続されたカソードと、前記少なくとも1つの昇圧用ダイオードのカソードに接続されたアノードとを有する第1スナバダイオードと、

前記第1スナバダイオードのカソードと前記スナバコンデンサの前記他端とに接続されたアノードを有する第2スナバダイオードと、

前記第1スナバダイオードの前記アノードに接続された一端と、前記第2スナバダイオードのカソードに接続された他端とを有するスナバリアクトルと、

前記スナバリアクトルの前記他端と前記第2スナバダイオードの前記カソードとに接続された一端と、前記グランド電位に接続される他端とを有するコンデンサと

を備えるDC−DCコンバータ。

【請求項2】

請求項1に記載のDC−DCコンバータであって、

前記少なくとも1つの昇圧用スイッチング素子は、同じ向きで並列接続された複数の昇圧用スイッチング素子であり、

当該DC−DCコンバータは、前記複数の昇圧用スイッチング素子をタイミングをずらして順番にオンさせる手段をさらに備える、

DC−DCコンバータ。

【請求項3】

請求項1または請求項2に記載のDC−DCコンバータであって、

同じ構成を有し並列接続されることによって多重化された複数の単位回路を備え、

前記複数の単位回路のそれぞれが、前記主リアクトルと、前記少なくとも1つの昇圧用スイッチング素子と、前記少なくとも1つの昇圧用ダイオードと、前記スナバコンデンサと、前記第1スナバダイオードと、前記第2スナバダイオードと、前記スナバリアクトルとを含む、

DC−DCコンバータ。

【請求項4】

請求項1ないし請求項3のうちのいずれか1項に記載のDC−DCコンバータであって、

前記少なくとも1つの昇圧用スイッチング素子のうちの一部または全部の素子の動作状態に関する情報を検出する昇圧用検出手段と、

前記昇圧用検出手段による検出結果に基づいて前記少なくとも1つの昇圧用スイッチング素子の動作を制御する手段と

をさらに備えるDC−DCコンバータ。

【請求項5】

請求項4に記載のDC−DCコンバータであって、

前記少なくとも1つの昇圧用スイッチング素子は、同じ向きで並列接続された複数の昇圧用スイッチング素子であり、

前記昇圧用検出手段は、前記複数の昇圧用スイッチング素子のそれぞれの動作状態に関する情報を検出する、

DC−DCコンバータ。

【請求項6】

請求項5に記載のDC−DCコンバータであって、

前記少なくとも1つの昇圧用スイッチング素子の動作を制御する前記手段は、前記昇圧用検出手段による前記検出結果に基づいて、前記複数の昇圧用スイッチング素子の中から駆動させる素子を選択する、DC−DCコンバータ。

【請求項7】

請求項4ないし請求項6のうちのいずれか1項に記載のDC−DCコンバータであって、

前記昇圧用検出手段が検出する前記情報は、

前記少なくとも1つの昇圧用スイッチング素子に流れる電流と、

前記少なくとも1つの昇圧用スイッチング素子の温度と

のうちの少なくとも一方を含む、DC−DCコンバータ。

【請求項8】

請求項4ないし請求項7のうちのいずれか1項に記載のDC−DCコンバータであって、

前記少なくとも1つの昇圧用スイッチング素子の動作を制御する前記手段は、前記少なくとも1つの昇圧用スイッチング素子の前記制御端への入力抵抗を制御することによって、前記少なくとも1つの昇圧用スイッチング素子の動作を制御する、DC−DCコンバータ。

【請求項9】

請求項1ないし請求項8のうちのいずれか1項に記載のDC−DCコンバータであって、

前記少なくとも1つの昇圧用スイッチング素子と、前記少なくとも1つの昇圧用ダイオードと、前記スナバコンデンサと、前記第1スナバダイオードと、前記第2スナバダイオードとが、単一のケース内に集約されている、DC−DCコンバータ。

【請求項10】

請求項9に記載のDC−DCコンバータであって、

前記スナバコンデンサに接触している放熱板をさらに備えるDC−DCコンバータ。

【請求項11】

請求項10に記載のDC−DCコンバータであって、

前記スナバコンデンサは、はんだ付けと、溶接と、超音波接合と、ネジ締めとのうちの少なくとも1つの接続手法によって、前記ケースの電極に接続されている、DC−DCコンバータ。

【請求項12】

請求項1ないし請求項11のうちのいずれか1項に記載のDC−DCコンバータであって、

前記少なくとも1つの昇圧用ダイオードの前記カソードに接続された電流入力端と、前記少なくとも1つの昇圧用ダイオードの前記アノードに接続された電流出力端と、当該電流入力端と当該電流出力端との間のオンオフを制御するための制御信号が入力される制御端とを有する、少なくとも1つの降圧用スイッチング素子と、

前記少なくとも1つの昇圧用スイッチング素子の前記電流入力端および前記電流出力端にそれぞれ接続されたカソードおよびアノードを有する、少なくとも1つの降圧用ダイオードと

をさらに備えるDC−DCコンバータ。

【請求項13】

一端および他端を有する主リアクトルと、

前記主リアクトルの前記他端に接続された電流出力端と、電流入力端と、当該電流入力端と当該電流出力端との間のオンオフを制御するための制御信号が入力される制御端とを有する、少なくとも1つの降圧用スイッチング素子と、

前記少なくとも1つの降圧用スイッチング素子の前記電流出力端と前記主リアクトルの前記他端とに接続されたカソードと、グランド電位に接続されるアノードとを有する、少なくとも1つの降圧用ダイオードと、

前記少なくとも1つの降圧用ダイオードの前記カソードと前記少なくとも1つの降圧用スイッチング素子の前記電流出力端と前記主リアクトルの前記他端とに接続された一端を有するスナバコンデンサと、

前記スナバコンデンサの他端に接続されたカソードと、前記少なくとも1つの降圧用スイッチング素子の前記電流入力端に接続されたアノードとを有する第1スナバダイオードと、

前記第1スナバダイオードのカソードと前記スナバコンデンサの前記他端とに接続されたアノードを有する第2スナバダイオードと、

前記第1スナバダイオードの前記アノードに接続された一端と、前記第2スナバダイオードのカソードに接続された他端とを有するスナバリアクトルと、

前記スナバリアクトルの前記他端と前記第2スナバダイオードの前記カソードとに接続された一端と、前記グランド電位に接続される他端とを有するコンデンサと

を備えるDC−DCコンバータ。

【請求項14】

請求項12または請求項13に記載のDC−DCコンバータであって、

前記少なくとも1つの降圧用スイッチング素子は、同じ向きで並列接続された複数の降圧用スイッチング素子であり、

当該DC−DCコンバータは、前記複数の降圧用スイッチング素子をタイミングをずらして順番にオンさせる手段をさらに備える、

DC−DCコンバータ。

【請求項15】

請求項3を引用する請求項12に記載のDC−DCコンバータであって、

前記複数の単位回路のそれぞれが、前記少なくとも1つの降圧用スイッチング素子と、前記少なくとも1つの降圧用ダイオードとをさらに含む、DC−DCコンバータ。

【請求項16】

請求項13に記載のDC−DCコンバータであって、

同じ構成を有し並列接続されることによって多重化された複数の単位回路を備え、

前記複数の単位回路のそれぞれが、前記主リアクトルと、前記少なくとも1つの降圧用スイッチング素子と、前記少なくとも1つの降圧用ダイオードと、前記スナバコンデンサと、前記第1スナバダイオードと、前記第2スナバダイオードと、前記スナバリアクトルとを含む、

DC−DCコンバータ。

【請求項17】

請求項12ないし請求項16のうちのいずれか1項に記載のDC−DCコンバータであって、

前記少なくとも1つの降圧用スイッチング素子のうちの一部または全部の素子の動作状態に関する情報を検出する降圧用検出手段と、

前記降圧用検出手段による検出結果に基づいて前記少なくとも1つの降圧用スイッチング素子の動作を制御する手段と

をさらに備えるDC−DCコンバータ。

【請求項18】

請求項17に記載のDC−DCコンバータであって、

前記少なくとも1つの降圧用スイッチング素子は、同じ向きで並列接続された複数の降圧用スイッチング素子であり、

前記降圧用検出手段は、前記複数の降圧用スイッチング素子のそれぞれの動作状態に関する情報を検出する、

DC−DCコンバータ。

【請求項19】

請求項18に記載のDC−DCコンバータであって、

前記少なくとも1つの降圧用スイッチング素子の動作を制御する前記手段は、前記降圧用検出手段による前記検出結果に基づいて、前記複数の降圧用スイッチング素子の中から駆動させる素子を選択する、DC−DCコンバータ。

【請求項20】

請求項17ないし請求項19のうちのいずれか1項に記載のDC−DCコンバータであって、

前記降圧用検出手段が検出する前記情報は、

前記少なくとも1つの降圧用スイッチング素子に流れる電流と、

前記少なくとも1つの降圧用スイッチング素子の温度と

のうちの少なくとも一方を含む、DC−DCコンバータ。

【請求項21】

請求項17ないし請求項20のうちのいずれか1項に記載のDC−DCコンバータであって、

前記少なくとも1つの降圧用スイッチング素子の動作を制御する前記手段は、前記少なくとも1つの降圧用スイッチング素子の前記制御端への入力抵抗を制御することによって、前記少なくとも1つの降圧用スイッチング素子の動作を制御する、DC−DCコンバータ。

【請求項22】

請求項9を引用する請求項12に記載のDC−DCコンバータであって、

前記少なくとも1つの降圧用スイッチング素子と、前記少なくとも1つの降圧用ダイオードとがさらに前記単一のケース内に集約されている、DC−DCコンバータ。

【請求項23】

請求項13に記載のDC−DCコンバータであって、

前記少なくとも1つの降圧用スイッチング素子と、前記少なくとも1つの降圧用ダイオードと、前記スナバコンデンサと、前記第1スナバダイオードと、前記第2スナバダイオードとが、単一のケース内に集約されている、DC−DCコンバータ。

【請求項24】

請求項23に記載のDC−DCコンバータであって、

前記スナバコンデンサに接触している放熱板をさらに備えるDC−DCコンバータ。

【請求項25】

請求項24に記載のDC−DCコンバータであって、

前記スナバコンデンサは、はんだ付けと、溶接と、超音波接合と、ネジ締めとのうちの少なくとも1つの接続手法によって、前記ケースの電極に接続されている、DC−DCコンバータ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【公開番号】特開2012−70505(P2012−70505A)

【公開日】平成24年4月5日(2012.4.5)

【国際特許分類】

【出願番号】特願2010−211840(P2010−211840)

【出願日】平成22年9月22日(2010.9.22)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成24年4月5日(2012.4.5)

【国際特許分類】

【出願日】平成22年9月22日(2010.9.22)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]