DC−DCコンバータ

【課題】スイッチングICのスイッチング制御により発生したスイッチングノイズが共通のグランド電極パターンを介してグランドラインから漏洩することを抑制できるDC−DCコンバータを提供する。

【解決手段】DC−DCコンバータ10の絶縁性基板11には、表面にインダクタL1、内部にスイッチング制御IC13、裏面にグランド電極パターン12が設けられている。グランド電極パターン12は、隔離した第1パターン121および第2パターン122と、これらを接続するブリッジパターン123からなる。第1パターン121および第2パターン122には、インダクタL1またはスイッチング制御IC13が接続されている。ブリッジパターン123は、インダクタL1に対向し、幅が第1パターン121および第2パターン122よりも幅が狭くしてある。

【解決手段】DC−DCコンバータ10の絶縁性基板11には、表面にインダクタL1、内部にスイッチング制御IC13、裏面にグランド電極パターン12が設けられている。グランド電極パターン12は、隔離した第1パターン121および第2パターン122と、これらを接続するブリッジパターン123からなる。第1パターン121および第2パターン122には、インダクタL1またはスイッチング制御IC13が接続されている。ブリッジパターン123は、インダクタL1に対向し、幅が第1パターン121および第2パターン122よりも幅が狭くしてある。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、絶縁体基板にインダクタおよびスイッチング制御ICを設けたDC−DCコンバータに関する。

【背景技術】

【0002】

携帯電話機または多機能型携帯端末などでは、マルチバンドの周波数帯域に対応するために複数種類の電圧が求められており、非絶縁型DC−DCコンバータが用いられている。DC−DCコンバータは、コイル、コンデンサおよびスイッチングICなどから構成されているが、これまでに、絶縁体基板内部にコイルパターンを形成し、絶縁体基板表面にキャパシタおよびスイッチングICなどを実装して構成されたものがある。

【0003】

この構成の場合、DC−DCコンバータは、絶縁体基板表面にスイッチングICを実装していることから基板厚み方向に大きくなるため、薄型化が進む携帯電話機等においては、より小型化(薄型化)したDC−DCコンバータが望まれている。そこで、絶縁体基板内にスイッチングICを内蔵し、コイルおよびコンデンサなどを基板表面に実装する構成とすることで、DC−DCコンバータの低背化を実現したものが提案されている。

【0004】

また、DC−DCコンバータでは、スイッチングICがスイッチングを行う際に高周波のノイズ(スイッチングノイズ)が発生するといった問題があり、ノイズに対する対策を行う必要がある。特許文献1には、電子部品からの電磁ノイズがある環境下でも安定した動作を実現するための電子部品の実装に用いられるプリント配線板が開示されている。電磁ノイズはコイルまたはコンデンサなどから構成されるフィルタによって大部分の除去が可能であるが、フィルタの実装スペースがないという問題があることから、特許文献1では、電子部品のリードを取付ける穴の周囲に磁性体を塗布している。これによって、電子部品に直列にコイルを挿入するのと同等の効果が得られるようにして、電磁ノイズを除去している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平6−152079号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、DC−DCコンバータは、通常、コイルおよびスイッチングICなどの共通電極として、絶縁体基板の裏面にグランド電極パターンが形成されている。各素子が共通のグランド電極パターンに接続されているため、コイルおよびスイッチングICで発生したスイッチングノイズがグランドラインから漏洩するといった問題がある。斯かる問題は特許文献1に記載の発明では解決できない。

【0007】

そこで、本発明の目的は、スイッチングICのスイッチング制御により発生したスイッチングノイズが共通のグランド電極パターンを介してグランドラインから漏洩することを抑制できるDC−DCコンバータを提供することにある。

【課題を解決するための手段】

【0008】

本発明に係るDC−DCコンバータは、複数の絶縁体層を有する絶縁性基板と、該絶縁性基板に設けられた入力端子および出力端子と、前記絶縁性基板の第1の層に設けられ、前記入力端子および前記出力端子の間に接続されている磁性材料を含む第1インダクタと、前記絶縁性基板の内部に設けられ、かつ、前記入力端子および前記出力端子の間に接続されていて、スイッチング素子をオンオフ制御するスイッチング制御部と、前記絶縁性基板の第2の層に設けられたグランド電極パターンと、を備え、前記グランド電極パターンは、前記入力端子に接続している第1電極パターンと、前記出力端子に接続し、前記第1電極パターンから隔離している第2電極パターンと、所定方向に沿って形成され、前記第1および第2電極パターンを接続している接続電極パターンと、を有し、前記接続電極パターンは、前記第1インダクタに対向し、かつ、前記所定方向に直交する方向の幅が前記第1および第2電極パターンよりも短くしてあることを特徴とする。

【0009】

この構成では、第1および第2電極パターンを繋ぐ接続電極パターンの幅が細く形成されているため、接続電極パターンのインダクタンス成分が第1および第2電極パターンより大きくなる。また、接続電極パターンには対向している第1インダクタが、ビーズ(フェライトビーズ)として作用して、接続電極パターンはビーズインダクタとして機能する。これにより、第1インダクタの磁性材料がノイズ電流により励起される磁束を吸収し、磁性材料の磁気抵抗により損失が生じて、ノイズ電流が抑制される。これにより、第1または第2電極パターンからグランド電極パターンへ流れ込んだノイズ電流がグランド電極パターンから漏洩することを抑制できる。

【0010】

本発明に係るDC−DCコンバータにおいて、前記絶縁性基板の第1の層に設けられ、第1端が前記入力端子または前記出力端子に接続され、第2端が前記第1電極パターンまたは前記2電極パターンに接続されているキャパシタをさらに備える構成でもよい。

【0011】

この構成では、一の絶縁性基板にインダクタおよびキャパシタを実装したDC−DCコンバータのモジュールを形成することができる。

【0012】

本発明に係るDC−DCコンバータは、多出力型DC−DCコンバータであって、前記第2の層を挟んで前記第1の層とは反対方向の前記絶縁性基板の第3の層に設けられ、前記入力端子または前記出力端子に接続されている第2インダクタ、をさらに備え、前記第2インダクタは、磁性材料を含み、前記接続電極パターンを挟んで前記第1インダクタに対向している構成でもよい。

【0013】

この構成では、接続電極パターンが第1および第2インダクタに挟まれた構成であるので、ノイズ電流が接続電極パターンを通る際に、二つの第1および第2インダクタの磁性材料がノイズ電流により励起される磁束を吸収するため、より効果的にノイズ電流を抑制できる。

【発明の効果】

【0014】

本発明によれば、グランド電極パターンにおいてインダクタに対向する接続電極パターンを細くし、接続電極パターンに第1インダクタを対向させることで、接続電極パターンに流れるノイズ電流を抑制することができる。その結果、グランド電極パターンからのノイズ電流の漏洩を抑制できる。

【図面の簡単な説明】

【0015】

【図1】実施形態1に係るDC−DCコンバータの構成を示す模式図。

【図2】(A)は、DC-DCコンバータの断面図において各素子の接続態様を示す模式図、(B)はDC-DCコンバータの等価回路を示す図。

【図3】(A)は、実施形態2に係るDC-DCコンバータの断面図において各素子の接続態様を示す模式図、(B)はDC-DCコンバータの等価回路を示す図。

【図4】DC-DCコンバータの別の構成例を示す模式図。

【図5】実施形態3に係るDC−DCコンバータの構成を示す模式図。

【図6】DC-DCコンバータの等価回路を示す図。

【図7】実施形態1,2に係るDC−DCコンバータの別の構成例を示す模式図。

【発明を実施するための形態】

【0016】

(実施形態1)

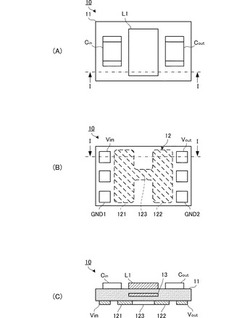

図1は、実施形態1に係るDC−DCコンバータの構成を示す模式図である。図1(A)はDC-DCコンバータの上面図である。図1(B)はDC-DCコンバータの下面図である。図1(C)は、図1(A)および図1(B)のI−I線における正面断面図である。

【0017】

DC-DCコンバータ10は、複数の絶縁体層が積層されてなる絶縁性基板11を備えている。絶縁性基板11は長辺を有する矩形状の表裏面を有している。絶縁性基板11の表面(第1の層)は磁性体部品などが実装される面である。また、絶縁性基板11の裏面はメイン基板などの回路基板に実装される面である。

【0018】

絶縁性基板11の表面には、インダクタL1、キャパシタCin,Coutが実装されている。インダクタL1は、コイルパターンが印刷された磁性体グリーンシート(磁性材料)が積層されて焼結されてなるチップインダクタであって、表面の略中央に設けられている。キャパシタCin,Coutは、インダクタL1を挟んで対向するように長手方向に沿って設けられている。なお、各素子の配線については後に詳述する。

【0019】

また、絶縁性基板11の内層にはスイッチング制御IC13が設けられている。スイッチング制御IC13は、MOS−FET(以下、単にFETという)を備え、インダクタL1に流れる電流を断続する。

【0020】

絶縁性基板11の裏面(第2の層)の四隅近傍には、入力端子電極Vin、出力端子電極Voutおよびグランド端子電極GND1,GND2が形成されている。入力端子電極Vinおよび出力端子電極Voutは、長手方向に沿って形成されている。グランド端子電極GND1,GND2は、長手方向に直交する方向(以下、短手方向という)において入力端子電極Vinおよび出力端子電極Voutと対向するよう、長手方向に沿って形成されている。

【0021】

また、長手方向において、入力端子電極Vinおよびグランド端子電極GND1と、出力端子電極Voutおよびグランド端子電極GND2との間には、グランド電極パターン12が形成されている。グランド端子電極GND1,GND2は、グランド電極パターン12と導通している。グランド電極パターン12は、絶縁性基板11の裏面に形成され、レジスト膜で被覆されていてもよいし、絶縁性基板11の内層に形成されていてもよい。

【0022】

グランド電極パターン12は、第1パターン121、第2パターン122およびブリッジパターン123から構成され、H形状を有している。第1パターン121は、絶縁性基板11の厚み方向においてキャパシタCinに対向する領域に形成されている。第2パターン122は、絶縁性基板11の厚み方向においてキャパシタCoutに対向する領域に形成されている。第1パターン121および第2パターン122は相似形状であって、短手方向の長さが長手方向の長さより長く、長手方向に沿って隔離して形成されている。ブリッジパターン123は、絶縁性基板11の厚み方向においてインダクタL1に対向する領域に、長手方向(所定方向)に長く形成されていて、第1パターン121および第2パターン122を接続している。ブリッジパターン123は、短手方向の長さ(幅)が第1パターン121および第2パターン122よりも短く形成されている。

【0023】

このように、グランド電極パターン12の第1パターン121および第2パターン122は、これらよりも幅(短手方向の長さ)が狭いブリッジパターン123により接続されている。従って、ブリッジパターン123のインダクタンス成分は、第1パターン121および第2パターン122よりも大きくなっている。第1パターン121は上述したグランド端子電極GND1と導通し、第2パターン122はグランド端子電極GND2と導通している。すなわち、DC−DCコンバータ10におけるグランド端子電極GND1,GNDD2間のグランドラインにはブリッジパターン123が存在する。このブリッジパターン123が、後述するビーズインダクタとして機能することになる。

【0024】

次に、DC-DCコンバータ10の各素子の配線について説明する。図2(A)は、DC-DCコンバータ10の断面図において各素子の接続態様を示す模式図であり、図2(B)はDC-DCコンバータ10の等価回路を示す図である。

【0025】

スイッチング制御IC13は、入力端子Inと、出力端子Outと、グランド端子G1,G2とを備えている。入力端子Inには、入力端子電極Vinへ繋がる入力ラインが接続されている。入力端子電極Vinには、一端(第1端)が第2パターン122に接続されているキャパシタCinの他端(第2端)が接続されている。キャパシタCinは、ノイズ成分の除去等を行い、スイッチング制御IC13に安定した入力電圧の供給を可能としている。

【0026】

スイッチング制御IC13の出力端子Outは、インダクタL1を介して出力端子電極Voutに接続している。出力端子電極Voutには、一端がグランド端子電極GND2に接続しているキャパシタCoutの他端が接続されている。

【0027】

スイッチング制御IC13のグランド端子G1は、グランド端子電極GND2に接続している。より具体的には、グランド端子G1は第2パターン122を介してグランド端子電極GND2に接続している。また、グランド端子G2は、グランド端子電極GND1に接続している。より具体的には、グランド端子G2は第1パターン121を介してグランド端子電極GND1に接続している。

【0028】

スイッチング制御IC13は、p型FET131、n型FET132、および、FET131,132のスイッチング制御を行うドライバ133を備えている。FET131は、ドレインをスイッチング制御IC13の入力端子In、ソースを出力端子Out、ゲートをドライバ133に接続している。FET132は、ドレインを出力端子Out、ソースをグランド端子G1、ゲートをドライバ133に接続している。ドライバ133は、グランド側をグランド端子G2に接続している。このドライバ133は、FET131,132のスイッチング制御を行う。

【0029】

グランド端子G1は第1パターン121に接続し、グランド端子G2は第2パターン122に接続している。換言すれば、ドライバ133は第1パターン121に接続し、FET132のソースは第2パターン122に接続している。第1パターン121および第2パターン122はブリッジパターン123を介して接続されているため、図2(B)に示すように、ドライバ133およびFET132のソース間には、ブリッジパターン123のインダクタンス成分であるインダクタLeが構成される。

【0030】

このように構成されたDC−DCコンバータ10は、FET131をオン、FET132をオフすることでインダクタL1に電流を流して励磁させ、エネルギーを蓄積する。その後、DC−DCコンバータ10は、FET131をオフ、FET132をオンして、蓄積したエネルギーを転流させる。この動作を繰り返して、DC−DCコンバータ10は、入力電圧よりも低い電圧を出力端子電極Voutから出力する。

【0031】

以下に、DC-DCコンバータ10がスイッチング制御IC13で発生したスイッチングノイズを抑制する原理について説明する。

【0032】

一般にDC-DCコンバータを小型化した場合、接地配線を十分に長くできず、回路に生じたノイズ成分を抑圧できないといった問題がある。例えば、グランド電極パターンが矩形状である場合、スイッチング制御IC13で発生したスイッチングノイズが、共通のグランド電極パターンを介して出力端子電極Voutへ接続される出力ラインに重畳されるといった問題がある。本実施形態の場合、発生したスイッチングノイズは、スイッチング制御IC13のグランド端子G2から第2パターン122、ブリッジパターン123および第1パターン121を通り、入力ラインへ重畳されるおそれがある。

【0033】

そこで、本実施形態に係るグランド電極パターン12は、図1に示すように、磁性体部品であるインダクタL1に対向する領域に形成されたブリッジパターン123の幅(絶縁性基板11の短手方向の長さ)を細くし、等価的インダクタLeが構成されるようにしてある。DC-DCコンバータ10を小型化した場合、絶縁性基板11の厚みが薄くなるため、絶縁性基板11の表面に実装したインダクタL1の磁性体と、細く形成されたブリッジパターン123とが近接する。このとき、インダクタL1の磁性体が、ブリッジパターン123が構成する等価的インダクタLeのビーズ(フェライトビーズ)として作用する。

【0034】

すなわち、ブリッジパターン123にスイッチングノイズ電流が流れた場合、インダクタL1の磁性体はスイッチングノイズ電流によりブリッジパターン123に励起される磁束を吸収し、磁性体内の磁気抵抗により損失が生じて、スイッチングノイズが抑制される。この結果、本実施形態に係るDC-DCコンバータ10は、実際にビーズインダクタを実装することなく、グランド電極パターン12の形状を変更するだけで、スイッチングノイズがグランド電極パターン12を介して漏洩することを抑制することができる。

【0035】

(実施形態2)

以下に、本発明に係る実施形態2について説明する。実施形態1では、降圧型DC−DCコンバータ10について例示したが、実施形態2では昇圧型DC−DCコンバータの例を示す。実施形態2に係るDC-DCコンバータの構成(実装する磁性体部品など)については実施形態1と同様であるため説明は省略する。

【0036】

図3(A)は、実施形態2に係るDC-DCコンバータの断面図において各素子の接続態様を示す模式図であり、図3(B)はDC-DCコンバータの等価回路を示す図である。

【0037】

スイッチング制御IC21は、入力端子Inと、出力端子Outと、グランド端子Gとを備えている。入力端子Inは、インダクタL1を介して入力端子電極Vinへ接続されている。入力端子電極Vinには、一端が第1パターン121に接続されているキャパシタCinの他端が接続されている。キャパシタCinは入力電圧のノイズ成分の除去等を行う。

【0038】

スイッチング制御IC21の出力端子Outは出力端子電極Voutに接続している。出力端子電極Voutには、一端がグランド端子電極GND2に接続しているキャパシタCoutの他端が接続されている。

【0039】

スイッチング制御IC21のグランド端子Gは、グランド端子電極GND2に接続している。より具体的には、グランド端子Gは第2パターン122を介してグランド端子電極GND2に接続している。

【0040】

スイッチング制御IC21は、p型FET211、n型FET212、および、FET211,212のスイッチング制御を行うドライバ213を備えている。FET211,212のゲートは、ドライバ213に接続している。また、ドライバ213は、スイッチング制御IC21のグランド端子Gに接続している。

【0041】

FET211は、ドレインをスイッチング制御IC13の入力端子In、ソースをスイッチング制御IC21のグランド端子Gに接続している。FET212は、ドレインをスイッチング制御IC21の入力端子In、ソースを出力端子Outに接続している。グランド端子Gは第2パターン122に接続していて、第2パターン122は、ブリッジパターン123を介して第1パターン121と接続している。このため、図3(B)に示すように、グランド端子Gおよびグランド端子電極GND1間には、ブリッジパターン123のインダクタンス成分である等価的インダクタLeが構成される。

【0042】

このように構成されたDC−DCコンバータ20は、FET211のオン時にインダクタL1に蓄積されたエネルギーが、FET212のオン、FET212のオフ時に誘導電圧として入力電圧に加算され、キャパシタCoutによって平滑化される。これにより、DC-DCコンバータ20は入力電圧よりも高い出力電圧を出力する。

【0043】

また、本実施形態の場合、スイッチング制御IC21で発生したスイッチングノイズは、スイッチング制御IC21のグランド端子Gから第2パターン122、ブリッジパターン123および第1パターン121を流れる。このとき、実施形態1で説明したように、インダクタL1がブリッジパターン123に近接に対向しているため、インダクタL1の磁性体がブリッジパターン123に対してビーズインダクタのビーズとして作用して、ブリッジパターン123を流れるスイッチングノイズが抑制される。この結果、グランド電極パターン12を介して入力ラインにノイズが漏洩することが抑制される。

【0044】

なお、実施形態1,2に係るDC-DCコンバータは、キャパシタCin,Coutが絶縁性基板11の表面に実装されている構成としているが、キャパシタCin,Coutは、図4に示すように、絶縁性基板11以外、例えば、絶縁性基板11を実装する基板に設けるようにしてもよい。図4は、DC-DCコンバータの別の構成例を示す模式図である。図4(A)はDC-DCコンバータの上面図である。図4(B)はDC-DCコンバータの下面図である。図4(C)は、図4(A)および図4(B)のIV−IV線における正面断面図である。

【0045】

DC−DCコンバータ15が備える絶縁性基板16の表面には、インダクタL1が実装され、絶縁性基板16の内層には、スイッチング制御IC13が設けられている。キャパシタCin,Coutは、DC−DCコンバータ15が実装される基板18に実装されている。

【0046】

絶縁性基板16の裏面には、入力端子電極Vin、出力端子電極Voutおよびグランド電極パターン17が形成されている。入力端子電極Vinおよび出力端子電極Voutは、実施形態1と同様の位置に形成されている。キャパシタCinは入力端子電極Vinに接続され、キャパシタCoutは出力端子電極Voutに接続されている。

【0047】

グランド電極パターン17は、入力端子電極Vinおよび出力端子電極Voutを除く絶縁性基板16の裏面のほぼ全域に形成されている。グランド電極パターン17は、第1パターン171、第2パターン172およびブリッジパターン173からなり、ブリッジパターン173がインダクタL1と対向するよう形成されている。

【0048】

また、ブリッジパターン173は、絶縁性基板16の短手方向の長さが第1パターン171および第2パターン172よりも短く形成されている。第1パターン171および第2パターン172は、実施形態1との対比において面積が大きく形成してある。このため、図4に示す変形例は、ブリッジパターン173によりスイッチングノイズを抑制でき、さらに、グランド電極パターンの大きさが実施形態1よりも大きいため、シールド効果が大きくなり、実施形態1よりもノイズ成分をより抑圧できる。

【0049】

なお、実施形態1,2において、降圧型および昇圧型DC−DCコンバータについて説明したが、昇降圧型のDC−DCコンバータであってもよい。

【0050】

(実施形態3)

以下に、本発明に係る実施形態3について説明する。本実施形態に係るDC−DCコンバータは、多出力型DC−DCコンバータであり、以下では2出力型DC−DCコンバータを例に挙げて説明する。

【0051】

図5は、実施形態3に係るDC−DCコンバータの構成を示す模式図である。図5(A)は、実施形態3に係るDC−DCコンバータの上面図、図5(B)は、図5(A)のVA−VA線における正面断面図、図5(C)は、図5(A)のVB−VB線における正面断面図である。

【0052】

DC-DCコンバータ30は絶縁性基板31を備えている。絶縁性基板31の表面には、実施形態1と同様に、インダクタL1およびキャパシタCin,Cout1が実装されている。

【0053】

絶縁性基板31の内層には、スイッチング制御IC32が設けられている。スイッチング制御IC32は、インダクタL1に流れる電流を断続する。

【0054】

また、絶縁性基板31の内層であって、スイッチング制御IC32および絶縁性基板31の裏面の間には、図1(B)で説明した、第1パターン121、第2パターン122およびブリッジパターン123からなるグランド電極パターンが形成されている。さらに、絶縁性基板31の内層(第3の層)であって、絶縁性基板31の裏面側にグランド電極パターン12と対向する位置にインダクタL2が設けられている。インダクタL2は、インダクタL1と同様、コイルパターンが印刷された磁性体グリーンシートが積層され焼結されてなるチップインダクタである。このインダクタL2と同層(またはそれに近い層)には、キャパシタCout2が設けられている。

【0055】

絶縁性基板31の裏面には、入力端子電極Vin、出力端子電極Vout1,Vout2およびグランド端子電極GND3,GND4が形成されている。グランド端子電極GND3には、図示しないスルーホールを介して第1パターン121が導通している。また、グランド端子電極GND4には第2パターン122が導通している。

【0056】

次に、DC-DCコンバータ10の各素子の配線について説明する。図6は、DC-DCコンバータ30の等価回路を示す図である。

【0057】

スイッチング制御IC32は、2つの入力端子In1,In2と、2つの出力端子Out1,Out2と、グランド端子G1,G2,G3,G4とを備えている。

【0058】

入力端子In1,In2には、入力端子電極Vinへ繋がる入力ラインが接続されている。入力端子電極Vinには、一端が第1パターン121に接続されているキャパシタCinの他端が接続されている。

【0059】

スイッチング制御IC32の出力端子Out1は、インダクタL1を介して出力端子電極Vout1に接続されている。出力端子電極Vout1には、一端がグランド端子電極GND4に接続しているキャパシタCout1の他端が接続されている。また、出力端子Out2には、インダクタL2を介して出力端子電極Vout2に接続している。出力端子電極Vout2は、一端がグランド端子電極GND4に接続しているキャパシタCout2の他端が接続されている。

【0060】

スイッチング制御IC32のグランド端子G1,G2は、グランド端子電極GND4に接続している。より具体的には、グランド端子G1,G2は第2パターン122を介してグランド端子電極GND4に接続している。

【0061】

また、グランド端子G3,G4は、グランド端子電極GND3に接続している。より具体的には、グランド端子G3,G4は第1パターン121を介してグランド端子電極GND3に接続している。

【0062】

スイッチング制御IC32は、p型FET321,324、n型FET322,325および、スイッチング制御を行うドライバ323,326を備えている。FET321は、ドレインを入力端子In1、ソースを出力端子Out1、ゲートをドライバ323にそれぞれ接続している。FET322は、ドレインを出力端子Out1、ソースをグランド端子G1、ゲートをドライバ323に接続している。ドライバ323は、グランド側がグランド端子G4に接続されている。

【0063】

FET324は、ドレインを入力端子In2、ソースを出力端子Out2、ゲートをドライバ326に接続している。FET325は、ドレインを出力端子Out2、ソースをグランド端子G2、ゲートをドライバ326に接続している。ドライバ326は、グランド側をグランド端子G3に接続している。

【0064】

グランド端子G1は第2パターン122に接続し、グランド端子G4は第1パターン121に接続している。従って、実施形態1と同様に、グランド端子G1,G4のグランドラインには、ブリッジパターン123のインダクタンス成分である等価的インダクタL3が接続されていることになる。

【0065】

DC−DCコンバータ30のブリッジパターン123は、絶縁性基板31の上下方向(厚み方向)において、インダクタL1,L2により挟まれている。このため、インダクタL1,L2の磁性体が、ブリッジパターン123が構成するインダクタL3のビーズとして作用する。実施形態1では、ブリッジパターン123の表面側のみに磁性体が近接しているのに対し、実施形態3では、ブリッジパターン123の表面側および裏面側に磁性体が近接している。従って、実施形態3に係るDC−DCコンバータ30は、ドライバ313,316などで発生したスイッチングノイズがブリッジパターン123を通る際に、インダクタL1,L2の二つの磁性体がスイッチングノイズ電流により励起される磁束を吸収するため、実施形態1との対比において、より高いスイッチングノイズ電流の抑制効果が得られる。

【0066】

なお、本実施の形態では、降圧型の多出力型DC−DCコンバータについて説明したが、昇圧型又は昇降圧型の多出力型DC−DCコンバータであってもよい。また、降圧型DC−DCコンバータと昇圧型DC−DCコンバータとが混在する多出力型DC−DCコンバータであってもよい。また、DC−DCコンバータ30は、3出力型またはそれ以上の多出力型DC−DCコンバータであってもよい。また、グランド電極パターン12,17はH形状としているが、ブリッジパターン123,173の幅が他の電極パターンより細ければよい。例えば、ブリッジパターン123,173はミアンダ状に形成されていてもよい。

【0067】

図7は、実施形態1,2に係るDC−DCコンバータの別の構成例を示す模式図である。実施形態1,2では、インダクタL1などの磁性体部品は、絶縁性基板11の表面に実装されているが、図7(A)に示すように、絶縁性基板11の内層に実装された構成であってもよい。また、表面にインダクタL1など実装した場合、樹脂などによりインダクタL1などをモールドした構成としてもよい。

【0068】

また、インダクタL1などを絶縁性基板11の内層に実装する場合、図7(B)に示すように、インダクタL1とキャパシタCin,Coutとを異なる層に実装してもよい。図7(B)の場合、インダクタL1は絶縁性基板11の最下層に実装している。キャパシタCin,Coutは、グランド電極パターン41,42が形成された絶縁性基板11の内層に実装している。なお、図7(B)の場合、スイッチング制御IC13は絶縁性基板11内部であればどの層に実装されていてもよい。

【符号の説明】

【0069】

10,20,30−DC−DCコンバータ

11,31−絶縁性基板

12−グランド電極パターン

13−スイッチング制御IC(スイッチング制御部)

121−第1パターン(第1電極パターン)

122−第2パターン(第2電極パターン)

123−ブリッジパターン(接続電極パターン)

131,132−FET(スイッチング素子)

L1−インダクタ(第1インダクタ)

L2−インダクタ(第2インダクタ)

Cin,Cout−キャパシタ

Vin−入力電極端子

Vout−出力電極端子

【技術分野】

【0001】

本発明は、絶縁体基板にインダクタおよびスイッチング制御ICを設けたDC−DCコンバータに関する。

【背景技術】

【0002】

携帯電話機または多機能型携帯端末などでは、マルチバンドの周波数帯域に対応するために複数種類の電圧が求められており、非絶縁型DC−DCコンバータが用いられている。DC−DCコンバータは、コイル、コンデンサおよびスイッチングICなどから構成されているが、これまでに、絶縁体基板内部にコイルパターンを形成し、絶縁体基板表面にキャパシタおよびスイッチングICなどを実装して構成されたものがある。

【0003】

この構成の場合、DC−DCコンバータは、絶縁体基板表面にスイッチングICを実装していることから基板厚み方向に大きくなるため、薄型化が進む携帯電話機等においては、より小型化(薄型化)したDC−DCコンバータが望まれている。そこで、絶縁体基板内にスイッチングICを内蔵し、コイルおよびコンデンサなどを基板表面に実装する構成とすることで、DC−DCコンバータの低背化を実現したものが提案されている。

【0004】

また、DC−DCコンバータでは、スイッチングICがスイッチングを行う際に高周波のノイズ(スイッチングノイズ)が発生するといった問題があり、ノイズに対する対策を行う必要がある。特許文献1には、電子部品からの電磁ノイズがある環境下でも安定した動作を実現するための電子部品の実装に用いられるプリント配線板が開示されている。電磁ノイズはコイルまたはコンデンサなどから構成されるフィルタによって大部分の除去が可能であるが、フィルタの実装スペースがないという問題があることから、特許文献1では、電子部品のリードを取付ける穴の周囲に磁性体を塗布している。これによって、電子部品に直列にコイルを挿入するのと同等の効果が得られるようにして、電磁ノイズを除去している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平6−152079号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、DC−DCコンバータは、通常、コイルおよびスイッチングICなどの共通電極として、絶縁体基板の裏面にグランド電極パターンが形成されている。各素子が共通のグランド電極パターンに接続されているため、コイルおよびスイッチングICで発生したスイッチングノイズがグランドラインから漏洩するといった問題がある。斯かる問題は特許文献1に記載の発明では解決できない。

【0007】

そこで、本発明の目的は、スイッチングICのスイッチング制御により発生したスイッチングノイズが共通のグランド電極パターンを介してグランドラインから漏洩することを抑制できるDC−DCコンバータを提供することにある。

【課題を解決するための手段】

【0008】

本発明に係るDC−DCコンバータは、複数の絶縁体層を有する絶縁性基板と、該絶縁性基板に設けられた入力端子および出力端子と、前記絶縁性基板の第1の層に設けられ、前記入力端子および前記出力端子の間に接続されている磁性材料を含む第1インダクタと、前記絶縁性基板の内部に設けられ、かつ、前記入力端子および前記出力端子の間に接続されていて、スイッチング素子をオンオフ制御するスイッチング制御部と、前記絶縁性基板の第2の層に設けられたグランド電極パターンと、を備え、前記グランド電極パターンは、前記入力端子に接続している第1電極パターンと、前記出力端子に接続し、前記第1電極パターンから隔離している第2電極パターンと、所定方向に沿って形成され、前記第1および第2電極パターンを接続している接続電極パターンと、を有し、前記接続電極パターンは、前記第1インダクタに対向し、かつ、前記所定方向に直交する方向の幅が前記第1および第2電極パターンよりも短くしてあることを特徴とする。

【0009】

この構成では、第1および第2電極パターンを繋ぐ接続電極パターンの幅が細く形成されているため、接続電極パターンのインダクタンス成分が第1および第2電極パターンより大きくなる。また、接続電極パターンには対向している第1インダクタが、ビーズ(フェライトビーズ)として作用して、接続電極パターンはビーズインダクタとして機能する。これにより、第1インダクタの磁性材料がノイズ電流により励起される磁束を吸収し、磁性材料の磁気抵抗により損失が生じて、ノイズ電流が抑制される。これにより、第1または第2電極パターンからグランド電極パターンへ流れ込んだノイズ電流がグランド電極パターンから漏洩することを抑制できる。

【0010】

本発明に係るDC−DCコンバータにおいて、前記絶縁性基板の第1の層に設けられ、第1端が前記入力端子または前記出力端子に接続され、第2端が前記第1電極パターンまたは前記2電極パターンに接続されているキャパシタをさらに備える構成でもよい。

【0011】

この構成では、一の絶縁性基板にインダクタおよびキャパシタを実装したDC−DCコンバータのモジュールを形成することができる。

【0012】

本発明に係るDC−DCコンバータは、多出力型DC−DCコンバータであって、前記第2の層を挟んで前記第1の層とは反対方向の前記絶縁性基板の第3の層に設けられ、前記入力端子または前記出力端子に接続されている第2インダクタ、をさらに備え、前記第2インダクタは、磁性材料を含み、前記接続電極パターンを挟んで前記第1インダクタに対向している構成でもよい。

【0013】

この構成では、接続電極パターンが第1および第2インダクタに挟まれた構成であるので、ノイズ電流が接続電極パターンを通る際に、二つの第1および第2インダクタの磁性材料がノイズ電流により励起される磁束を吸収するため、より効果的にノイズ電流を抑制できる。

【発明の効果】

【0014】

本発明によれば、グランド電極パターンにおいてインダクタに対向する接続電極パターンを細くし、接続電極パターンに第1インダクタを対向させることで、接続電極パターンに流れるノイズ電流を抑制することができる。その結果、グランド電極パターンからのノイズ電流の漏洩を抑制できる。

【図面の簡単な説明】

【0015】

【図1】実施形態1に係るDC−DCコンバータの構成を示す模式図。

【図2】(A)は、DC-DCコンバータの断面図において各素子の接続態様を示す模式図、(B)はDC-DCコンバータの等価回路を示す図。

【図3】(A)は、実施形態2に係るDC-DCコンバータの断面図において各素子の接続態様を示す模式図、(B)はDC-DCコンバータの等価回路を示す図。

【図4】DC-DCコンバータの別の構成例を示す模式図。

【図5】実施形態3に係るDC−DCコンバータの構成を示す模式図。

【図6】DC-DCコンバータの等価回路を示す図。

【図7】実施形態1,2に係るDC−DCコンバータの別の構成例を示す模式図。

【発明を実施するための形態】

【0016】

(実施形態1)

図1は、実施形態1に係るDC−DCコンバータの構成を示す模式図である。図1(A)はDC-DCコンバータの上面図である。図1(B)はDC-DCコンバータの下面図である。図1(C)は、図1(A)および図1(B)のI−I線における正面断面図である。

【0017】

DC-DCコンバータ10は、複数の絶縁体層が積層されてなる絶縁性基板11を備えている。絶縁性基板11は長辺を有する矩形状の表裏面を有している。絶縁性基板11の表面(第1の層)は磁性体部品などが実装される面である。また、絶縁性基板11の裏面はメイン基板などの回路基板に実装される面である。

【0018】

絶縁性基板11の表面には、インダクタL1、キャパシタCin,Coutが実装されている。インダクタL1は、コイルパターンが印刷された磁性体グリーンシート(磁性材料)が積層されて焼結されてなるチップインダクタであって、表面の略中央に設けられている。キャパシタCin,Coutは、インダクタL1を挟んで対向するように長手方向に沿って設けられている。なお、各素子の配線については後に詳述する。

【0019】

また、絶縁性基板11の内層にはスイッチング制御IC13が設けられている。スイッチング制御IC13は、MOS−FET(以下、単にFETという)を備え、インダクタL1に流れる電流を断続する。

【0020】

絶縁性基板11の裏面(第2の層)の四隅近傍には、入力端子電極Vin、出力端子電極Voutおよびグランド端子電極GND1,GND2が形成されている。入力端子電極Vinおよび出力端子電極Voutは、長手方向に沿って形成されている。グランド端子電極GND1,GND2は、長手方向に直交する方向(以下、短手方向という)において入力端子電極Vinおよび出力端子電極Voutと対向するよう、長手方向に沿って形成されている。

【0021】

また、長手方向において、入力端子電極Vinおよびグランド端子電極GND1と、出力端子電極Voutおよびグランド端子電極GND2との間には、グランド電極パターン12が形成されている。グランド端子電極GND1,GND2は、グランド電極パターン12と導通している。グランド電極パターン12は、絶縁性基板11の裏面に形成され、レジスト膜で被覆されていてもよいし、絶縁性基板11の内層に形成されていてもよい。

【0022】

グランド電極パターン12は、第1パターン121、第2パターン122およびブリッジパターン123から構成され、H形状を有している。第1パターン121は、絶縁性基板11の厚み方向においてキャパシタCinに対向する領域に形成されている。第2パターン122は、絶縁性基板11の厚み方向においてキャパシタCoutに対向する領域に形成されている。第1パターン121および第2パターン122は相似形状であって、短手方向の長さが長手方向の長さより長く、長手方向に沿って隔離して形成されている。ブリッジパターン123は、絶縁性基板11の厚み方向においてインダクタL1に対向する領域に、長手方向(所定方向)に長く形成されていて、第1パターン121および第2パターン122を接続している。ブリッジパターン123は、短手方向の長さ(幅)が第1パターン121および第2パターン122よりも短く形成されている。

【0023】

このように、グランド電極パターン12の第1パターン121および第2パターン122は、これらよりも幅(短手方向の長さ)が狭いブリッジパターン123により接続されている。従って、ブリッジパターン123のインダクタンス成分は、第1パターン121および第2パターン122よりも大きくなっている。第1パターン121は上述したグランド端子電極GND1と導通し、第2パターン122はグランド端子電極GND2と導通している。すなわち、DC−DCコンバータ10におけるグランド端子電極GND1,GNDD2間のグランドラインにはブリッジパターン123が存在する。このブリッジパターン123が、後述するビーズインダクタとして機能することになる。

【0024】

次に、DC-DCコンバータ10の各素子の配線について説明する。図2(A)は、DC-DCコンバータ10の断面図において各素子の接続態様を示す模式図であり、図2(B)はDC-DCコンバータ10の等価回路を示す図である。

【0025】

スイッチング制御IC13は、入力端子Inと、出力端子Outと、グランド端子G1,G2とを備えている。入力端子Inには、入力端子電極Vinへ繋がる入力ラインが接続されている。入力端子電極Vinには、一端(第1端)が第2パターン122に接続されているキャパシタCinの他端(第2端)が接続されている。キャパシタCinは、ノイズ成分の除去等を行い、スイッチング制御IC13に安定した入力電圧の供給を可能としている。

【0026】

スイッチング制御IC13の出力端子Outは、インダクタL1を介して出力端子電極Voutに接続している。出力端子電極Voutには、一端がグランド端子電極GND2に接続しているキャパシタCoutの他端が接続されている。

【0027】

スイッチング制御IC13のグランド端子G1は、グランド端子電極GND2に接続している。より具体的には、グランド端子G1は第2パターン122を介してグランド端子電極GND2に接続している。また、グランド端子G2は、グランド端子電極GND1に接続している。より具体的には、グランド端子G2は第1パターン121を介してグランド端子電極GND1に接続している。

【0028】

スイッチング制御IC13は、p型FET131、n型FET132、および、FET131,132のスイッチング制御を行うドライバ133を備えている。FET131は、ドレインをスイッチング制御IC13の入力端子In、ソースを出力端子Out、ゲートをドライバ133に接続している。FET132は、ドレインを出力端子Out、ソースをグランド端子G1、ゲートをドライバ133に接続している。ドライバ133は、グランド側をグランド端子G2に接続している。このドライバ133は、FET131,132のスイッチング制御を行う。

【0029】

グランド端子G1は第1パターン121に接続し、グランド端子G2は第2パターン122に接続している。換言すれば、ドライバ133は第1パターン121に接続し、FET132のソースは第2パターン122に接続している。第1パターン121および第2パターン122はブリッジパターン123を介して接続されているため、図2(B)に示すように、ドライバ133およびFET132のソース間には、ブリッジパターン123のインダクタンス成分であるインダクタLeが構成される。

【0030】

このように構成されたDC−DCコンバータ10は、FET131をオン、FET132をオフすることでインダクタL1に電流を流して励磁させ、エネルギーを蓄積する。その後、DC−DCコンバータ10は、FET131をオフ、FET132をオンして、蓄積したエネルギーを転流させる。この動作を繰り返して、DC−DCコンバータ10は、入力電圧よりも低い電圧を出力端子電極Voutから出力する。

【0031】

以下に、DC-DCコンバータ10がスイッチング制御IC13で発生したスイッチングノイズを抑制する原理について説明する。

【0032】

一般にDC-DCコンバータを小型化した場合、接地配線を十分に長くできず、回路に生じたノイズ成分を抑圧できないといった問題がある。例えば、グランド電極パターンが矩形状である場合、スイッチング制御IC13で発生したスイッチングノイズが、共通のグランド電極パターンを介して出力端子電極Voutへ接続される出力ラインに重畳されるといった問題がある。本実施形態の場合、発生したスイッチングノイズは、スイッチング制御IC13のグランド端子G2から第2パターン122、ブリッジパターン123および第1パターン121を通り、入力ラインへ重畳されるおそれがある。

【0033】

そこで、本実施形態に係るグランド電極パターン12は、図1に示すように、磁性体部品であるインダクタL1に対向する領域に形成されたブリッジパターン123の幅(絶縁性基板11の短手方向の長さ)を細くし、等価的インダクタLeが構成されるようにしてある。DC-DCコンバータ10を小型化した場合、絶縁性基板11の厚みが薄くなるため、絶縁性基板11の表面に実装したインダクタL1の磁性体と、細く形成されたブリッジパターン123とが近接する。このとき、インダクタL1の磁性体が、ブリッジパターン123が構成する等価的インダクタLeのビーズ(フェライトビーズ)として作用する。

【0034】

すなわち、ブリッジパターン123にスイッチングノイズ電流が流れた場合、インダクタL1の磁性体はスイッチングノイズ電流によりブリッジパターン123に励起される磁束を吸収し、磁性体内の磁気抵抗により損失が生じて、スイッチングノイズが抑制される。この結果、本実施形態に係るDC-DCコンバータ10は、実際にビーズインダクタを実装することなく、グランド電極パターン12の形状を変更するだけで、スイッチングノイズがグランド電極パターン12を介して漏洩することを抑制することができる。

【0035】

(実施形態2)

以下に、本発明に係る実施形態2について説明する。実施形態1では、降圧型DC−DCコンバータ10について例示したが、実施形態2では昇圧型DC−DCコンバータの例を示す。実施形態2に係るDC-DCコンバータの構成(実装する磁性体部品など)については実施形態1と同様であるため説明は省略する。

【0036】

図3(A)は、実施形態2に係るDC-DCコンバータの断面図において各素子の接続態様を示す模式図であり、図3(B)はDC-DCコンバータの等価回路を示す図である。

【0037】

スイッチング制御IC21は、入力端子Inと、出力端子Outと、グランド端子Gとを備えている。入力端子Inは、インダクタL1を介して入力端子電極Vinへ接続されている。入力端子電極Vinには、一端が第1パターン121に接続されているキャパシタCinの他端が接続されている。キャパシタCinは入力電圧のノイズ成分の除去等を行う。

【0038】

スイッチング制御IC21の出力端子Outは出力端子電極Voutに接続している。出力端子電極Voutには、一端がグランド端子電極GND2に接続しているキャパシタCoutの他端が接続されている。

【0039】

スイッチング制御IC21のグランド端子Gは、グランド端子電極GND2に接続している。より具体的には、グランド端子Gは第2パターン122を介してグランド端子電極GND2に接続している。

【0040】

スイッチング制御IC21は、p型FET211、n型FET212、および、FET211,212のスイッチング制御を行うドライバ213を備えている。FET211,212のゲートは、ドライバ213に接続している。また、ドライバ213は、スイッチング制御IC21のグランド端子Gに接続している。

【0041】

FET211は、ドレインをスイッチング制御IC13の入力端子In、ソースをスイッチング制御IC21のグランド端子Gに接続している。FET212は、ドレインをスイッチング制御IC21の入力端子In、ソースを出力端子Outに接続している。グランド端子Gは第2パターン122に接続していて、第2パターン122は、ブリッジパターン123を介して第1パターン121と接続している。このため、図3(B)に示すように、グランド端子Gおよびグランド端子電極GND1間には、ブリッジパターン123のインダクタンス成分である等価的インダクタLeが構成される。

【0042】

このように構成されたDC−DCコンバータ20は、FET211のオン時にインダクタL1に蓄積されたエネルギーが、FET212のオン、FET212のオフ時に誘導電圧として入力電圧に加算され、キャパシタCoutによって平滑化される。これにより、DC-DCコンバータ20は入力電圧よりも高い出力電圧を出力する。

【0043】

また、本実施形態の場合、スイッチング制御IC21で発生したスイッチングノイズは、スイッチング制御IC21のグランド端子Gから第2パターン122、ブリッジパターン123および第1パターン121を流れる。このとき、実施形態1で説明したように、インダクタL1がブリッジパターン123に近接に対向しているため、インダクタL1の磁性体がブリッジパターン123に対してビーズインダクタのビーズとして作用して、ブリッジパターン123を流れるスイッチングノイズが抑制される。この結果、グランド電極パターン12を介して入力ラインにノイズが漏洩することが抑制される。

【0044】

なお、実施形態1,2に係るDC-DCコンバータは、キャパシタCin,Coutが絶縁性基板11の表面に実装されている構成としているが、キャパシタCin,Coutは、図4に示すように、絶縁性基板11以外、例えば、絶縁性基板11を実装する基板に設けるようにしてもよい。図4は、DC-DCコンバータの別の構成例を示す模式図である。図4(A)はDC-DCコンバータの上面図である。図4(B)はDC-DCコンバータの下面図である。図4(C)は、図4(A)および図4(B)のIV−IV線における正面断面図である。

【0045】

DC−DCコンバータ15が備える絶縁性基板16の表面には、インダクタL1が実装され、絶縁性基板16の内層には、スイッチング制御IC13が設けられている。キャパシタCin,Coutは、DC−DCコンバータ15が実装される基板18に実装されている。

【0046】

絶縁性基板16の裏面には、入力端子電極Vin、出力端子電極Voutおよびグランド電極パターン17が形成されている。入力端子電極Vinおよび出力端子電極Voutは、実施形態1と同様の位置に形成されている。キャパシタCinは入力端子電極Vinに接続され、キャパシタCoutは出力端子電極Voutに接続されている。

【0047】

グランド電極パターン17は、入力端子電極Vinおよび出力端子電極Voutを除く絶縁性基板16の裏面のほぼ全域に形成されている。グランド電極パターン17は、第1パターン171、第2パターン172およびブリッジパターン173からなり、ブリッジパターン173がインダクタL1と対向するよう形成されている。

【0048】

また、ブリッジパターン173は、絶縁性基板16の短手方向の長さが第1パターン171および第2パターン172よりも短く形成されている。第1パターン171および第2パターン172は、実施形態1との対比において面積が大きく形成してある。このため、図4に示す変形例は、ブリッジパターン173によりスイッチングノイズを抑制でき、さらに、グランド電極パターンの大きさが実施形態1よりも大きいため、シールド効果が大きくなり、実施形態1よりもノイズ成分をより抑圧できる。

【0049】

なお、実施形態1,2において、降圧型および昇圧型DC−DCコンバータについて説明したが、昇降圧型のDC−DCコンバータであってもよい。

【0050】

(実施形態3)

以下に、本発明に係る実施形態3について説明する。本実施形態に係るDC−DCコンバータは、多出力型DC−DCコンバータであり、以下では2出力型DC−DCコンバータを例に挙げて説明する。

【0051】

図5は、実施形態3に係るDC−DCコンバータの構成を示す模式図である。図5(A)は、実施形態3に係るDC−DCコンバータの上面図、図5(B)は、図5(A)のVA−VA線における正面断面図、図5(C)は、図5(A)のVB−VB線における正面断面図である。

【0052】

DC-DCコンバータ30は絶縁性基板31を備えている。絶縁性基板31の表面には、実施形態1と同様に、インダクタL1およびキャパシタCin,Cout1が実装されている。

【0053】

絶縁性基板31の内層には、スイッチング制御IC32が設けられている。スイッチング制御IC32は、インダクタL1に流れる電流を断続する。

【0054】

また、絶縁性基板31の内層であって、スイッチング制御IC32および絶縁性基板31の裏面の間には、図1(B)で説明した、第1パターン121、第2パターン122およびブリッジパターン123からなるグランド電極パターンが形成されている。さらに、絶縁性基板31の内層(第3の層)であって、絶縁性基板31の裏面側にグランド電極パターン12と対向する位置にインダクタL2が設けられている。インダクタL2は、インダクタL1と同様、コイルパターンが印刷された磁性体グリーンシートが積層され焼結されてなるチップインダクタである。このインダクタL2と同層(またはそれに近い層)には、キャパシタCout2が設けられている。

【0055】

絶縁性基板31の裏面には、入力端子電極Vin、出力端子電極Vout1,Vout2およびグランド端子電極GND3,GND4が形成されている。グランド端子電極GND3には、図示しないスルーホールを介して第1パターン121が導通している。また、グランド端子電極GND4には第2パターン122が導通している。

【0056】

次に、DC-DCコンバータ10の各素子の配線について説明する。図6は、DC-DCコンバータ30の等価回路を示す図である。

【0057】

スイッチング制御IC32は、2つの入力端子In1,In2と、2つの出力端子Out1,Out2と、グランド端子G1,G2,G3,G4とを備えている。

【0058】

入力端子In1,In2には、入力端子電極Vinへ繋がる入力ラインが接続されている。入力端子電極Vinには、一端が第1パターン121に接続されているキャパシタCinの他端が接続されている。

【0059】

スイッチング制御IC32の出力端子Out1は、インダクタL1を介して出力端子電極Vout1に接続されている。出力端子電極Vout1には、一端がグランド端子電極GND4に接続しているキャパシタCout1の他端が接続されている。また、出力端子Out2には、インダクタL2を介して出力端子電極Vout2に接続している。出力端子電極Vout2は、一端がグランド端子電極GND4に接続しているキャパシタCout2の他端が接続されている。

【0060】

スイッチング制御IC32のグランド端子G1,G2は、グランド端子電極GND4に接続している。より具体的には、グランド端子G1,G2は第2パターン122を介してグランド端子電極GND4に接続している。

【0061】

また、グランド端子G3,G4は、グランド端子電極GND3に接続している。より具体的には、グランド端子G3,G4は第1パターン121を介してグランド端子電極GND3に接続している。

【0062】

スイッチング制御IC32は、p型FET321,324、n型FET322,325および、スイッチング制御を行うドライバ323,326を備えている。FET321は、ドレインを入力端子In1、ソースを出力端子Out1、ゲートをドライバ323にそれぞれ接続している。FET322は、ドレインを出力端子Out1、ソースをグランド端子G1、ゲートをドライバ323に接続している。ドライバ323は、グランド側がグランド端子G4に接続されている。

【0063】

FET324は、ドレインを入力端子In2、ソースを出力端子Out2、ゲートをドライバ326に接続している。FET325は、ドレインを出力端子Out2、ソースをグランド端子G2、ゲートをドライバ326に接続している。ドライバ326は、グランド側をグランド端子G3に接続している。

【0064】

グランド端子G1は第2パターン122に接続し、グランド端子G4は第1パターン121に接続している。従って、実施形態1と同様に、グランド端子G1,G4のグランドラインには、ブリッジパターン123のインダクタンス成分である等価的インダクタL3が接続されていることになる。

【0065】

DC−DCコンバータ30のブリッジパターン123は、絶縁性基板31の上下方向(厚み方向)において、インダクタL1,L2により挟まれている。このため、インダクタL1,L2の磁性体が、ブリッジパターン123が構成するインダクタL3のビーズとして作用する。実施形態1では、ブリッジパターン123の表面側のみに磁性体が近接しているのに対し、実施形態3では、ブリッジパターン123の表面側および裏面側に磁性体が近接している。従って、実施形態3に係るDC−DCコンバータ30は、ドライバ313,316などで発生したスイッチングノイズがブリッジパターン123を通る際に、インダクタL1,L2の二つの磁性体がスイッチングノイズ電流により励起される磁束を吸収するため、実施形態1との対比において、より高いスイッチングノイズ電流の抑制効果が得られる。

【0066】

なお、本実施の形態では、降圧型の多出力型DC−DCコンバータについて説明したが、昇圧型又は昇降圧型の多出力型DC−DCコンバータであってもよい。また、降圧型DC−DCコンバータと昇圧型DC−DCコンバータとが混在する多出力型DC−DCコンバータであってもよい。また、DC−DCコンバータ30は、3出力型またはそれ以上の多出力型DC−DCコンバータであってもよい。また、グランド電極パターン12,17はH形状としているが、ブリッジパターン123,173の幅が他の電極パターンより細ければよい。例えば、ブリッジパターン123,173はミアンダ状に形成されていてもよい。

【0067】

図7は、実施形態1,2に係るDC−DCコンバータの別の構成例を示す模式図である。実施形態1,2では、インダクタL1などの磁性体部品は、絶縁性基板11の表面に実装されているが、図7(A)に示すように、絶縁性基板11の内層に実装された構成であってもよい。また、表面にインダクタL1など実装した場合、樹脂などによりインダクタL1などをモールドした構成としてもよい。

【0068】

また、インダクタL1などを絶縁性基板11の内層に実装する場合、図7(B)に示すように、インダクタL1とキャパシタCin,Coutとを異なる層に実装してもよい。図7(B)の場合、インダクタL1は絶縁性基板11の最下層に実装している。キャパシタCin,Coutは、グランド電極パターン41,42が形成された絶縁性基板11の内層に実装している。なお、図7(B)の場合、スイッチング制御IC13は絶縁性基板11内部であればどの層に実装されていてもよい。

【符号の説明】

【0069】

10,20,30−DC−DCコンバータ

11,31−絶縁性基板

12−グランド電極パターン

13−スイッチング制御IC(スイッチング制御部)

121−第1パターン(第1電極パターン)

122−第2パターン(第2電極パターン)

123−ブリッジパターン(接続電極パターン)

131,132−FET(スイッチング素子)

L1−インダクタ(第1インダクタ)

L2−インダクタ(第2インダクタ)

Cin,Cout−キャパシタ

Vin−入力電極端子

Vout−出力電極端子

【特許請求の範囲】

【請求項1】

複数の絶縁体層を有する絶縁性基板と、

該絶縁性基板に設けられた入力端子および出力端子と、

前記絶縁性基板の第1の層に設けられ、前記入力端子および前記出力端子の間に接続されている磁性材料を含む第1インダクタと、

前記絶縁性基板の内部に設けられ、かつ、前記入力端子および前記出力端子の間に接続されていて、スイッチング素子をオンオフ制御するスイッチング制御部と、

前記絶縁性基板の第2の層に設けられたグランド電極パターンと、

を備え、

前記グランド電極パターンは、

前記入力端子に接続している第1電極パターンと、

前記出力端子に接続し、前記第1電極パターンから隔離している第2電極パターンと、

所定方向に沿って形成され、前記第1および第2電極パターンを接続している接続電極パターンと、

を有し、

前記接続電極パターンは、

前記第1インダクタに対向し、かつ、前記所定方向に直交する方向の幅が前記第1および第2電極パターンよりも短くしてある、DC−DCコンバータ。

【請求項2】

前記絶縁性基板の第1の層に設けられ、第1端が前記入力端子または前記出力端子に接続され、第2端が前記第1電極パターンまたは前記第2電極パターンに接続されているキャパシタ、

をさらに備える請求項1に記載のDC−DCコンバータ。

【請求項3】

多出力型DC−DCコンバータであって、

前記第2の層を挟んで前記第1の層とは反対方向の前記絶縁性基板の第3の層に設けられ、前記入力端子または前記出力端子に接続されている第2インダクタ、

をさらに備え、

前記第2インダクタは、

磁性材料を含み、前記接続電極パターンを挟んで前記第1インダクタに対向している、

請求項1または2に記載のDC−DCコンバータ。

【請求項1】

複数の絶縁体層を有する絶縁性基板と、

該絶縁性基板に設けられた入力端子および出力端子と、

前記絶縁性基板の第1の層に設けられ、前記入力端子および前記出力端子の間に接続されている磁性材料を含む第1インダクタと、

前記絶縁性基板の内部に設けられ、かつ、前記入力端子および前記出力端子の間に接続されていて、スイッチング素子をオンオフ制御するスイッチング制御部と、

前記絶縁性基板の第2の層に設けられたグランド電極パターンと、

を備え、

前記グランド電極パターンは、

前記入力端子に接続している第1電極パターンと、

前記出力端子に接続し、前記第1電極パターンから隔離している第2電極パターンと、

所定方向に沿って形成され、前記第1および第2電極パターンを接続している接続電極パターンと、

を有し、

前記接続電極パターンは、

前記第1インダクタに対向し、かつ、前記所定方向に直交する方向の幅が前記第1および第2電極パターンよりも短くしてある、DC−DCコンバータ。

【請求項2】

前記絶縁性基板の第1の層に設けられ、第1端が前記入力端子または前記出力端子に接続され、第2端が前記第1電極パターンまたは前記第2電極パターンに接続されているキャパシタ、

をさらに備える請求項1に記載のDC−DCコンバータ。

【請求項3】

多出力型DC−DCコンバータであって、

前記第2の層を挟んで前記第1の層とは反対方向の前記絶縁性基板の第3の層に設けられ、前記入力端子または前記出力端子に接続されている第2インダクタ、

をさらに備え、

前記第2インダクタは、

磁性材料を含み、前記接続電極パターンを挟んで前記第1インダクタに対向している、

請求項1または2に記載のDC−DCコンバータ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−46509(P2013−46509A)

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願番号】特願2011−183464(P2011−183464)

【出願日】平成23年8月25日(2011.8.25)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願日】平成23年8月25日(2011.8.25)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]