DCーDCコンバータ

【課題】軽負荷時における電力効率を高めることができる、DC−DCコンバータを提供すること。

【解決手段】同期整流型のDC−DCコンバータにおいて、制御回路が、逆流が検出された場合に、負荷電流に応じたパルス幅と、予め定められた最低パルス幅とのうちのパルス幅が長い信号に基づいて、スイッチング素子を切り換える。

【解決手段】同期整流型のDC−DCコンバータにおいて、制御回路が、逆流が検出された場合に、負荷電流に応じたパルス幅と、予め定められた最低パルス幅とのうちのパルス幅が長い信号に基づいて、スイッチング素子を切り換える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、DC−DCコンバータに関する。

【背景技術】

【0002】

デジタルカメラセット等の電気機器では、モータ、メモリ、スピーカ、及びバックライト等を駆動するために、様々な電源電圧が必要とされる。入力電圧を所望する電圧に変換するために、同期整流型のDC−DCコンバータが用いられる。現在のデジタルカメラ等の市場では、低消費電力及び長時間動作が要求されている。長時間動作を実現するために、DC−DCコンバータに対して、電力効率の向上が求められている。その結果、従来は問題にされていなかった無負荷時若しくは軽負荷時においても、高い電力効率が求められるようになっている。

【0003】

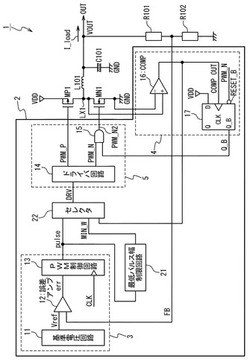

関連技術として、特許文献1(特開2010−239778号公報)に記載されたスイッチング電源装置が挙げられる。図1は、特許文献1に記載された降圧型同期整流方式のスイッチング電源装置を示す構成図である。このスイッチング電源装置は、メイントランジスタMP11、同期整流トランジスタMN11、インダクタL1、キャパシタC1、電源制御回路114、Pchドライバ115及びNchドライバ116Aを備えている。このスイッチング電源装置では、Pchドライバ115によってメイントランジスタMP11がオンになったとき(同期整流トランジスタMN11がオフになったとき)、電流が、電源11から、メイントランジスタMP11及びインダクタL1を介して、キャパシタC1へ流れ、キャパシタC1が充電される。また、Nchドライバ16Aによって同期整流トランジスタMN11がオン状態になったとき(メイントランジスタMP11がオフ)、インダクタL1に蓄積されたエネルギーにより、電流が、同期整流トランジスタMN11から、インダクタL1を介してキャパシタC1に流れ、キャパシタC1が充電される。後者のとき、負荷電流が小さいと、インダクタL1を流れる電流の方向が逆転する(逆流する)ことがある。逆流により、エネルギーが失われ、電力効率が低下する。そこで、ノードLX1の電圧V_LX1の変化が、Nchドライバ116Aによって検出され、電流の方向が逆転するとき、同期整流トランジスタMN11がオフにされる。

【0004】

図2は、上述のNchドライバ116Aの動作波形を示す図である。電源制御回路114が、制御信号PRDRV_Nを「L」から「H」に切り換えると(制御信号PRDRV_Pが「L」から「H」に変化してメイントランジスタMP11がオフになると)、駆動信号DRV_Nが「L」から「H」に変化し、同期整流トランジスタMN11がオフ状態からオン状態に変化し、同期整流トランジスタMN11からインダクタL1を介してキャパシタC1に電流が流れる。これにより、ノードLX1の電圧V_LX1は、接地電位(GND)よりも低い負の電位になる。この後、時間経過により、インダクタL1の電流は減少し、ノードLX1の電位は上昇する。インダクタL1の電流がゼロになると、ノードLX1の電圧V_LX1もゼロになる。その後インダクタL1から同期整流トランジスタMN11の方向に逆電流が流れ始める。この逆電流を防止するため、電圧V_LX1が0になると、Nchドライバ116Aにより、同期整流トランジスタMN11がオフ状態になるように制御される。これにより、逆電流による電力効率の低下を防ぐことができる。

【先行技術文献】

【非特許文献】

【0005】

【特許文献1】特開2010−239778号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

引用文献1に記載されたスイッチング電源装置によれば、軽負荷時において、逆電流の発生を防止することにより、電力効率の低下が抑制される。しかしながら、通常、メイントランジスタMP11及び同期整流トランジスタの状態(オン状態又はオフ状態)は、PWM(Pulse Width Modulation)制御により切り換えられる。軽負荷時には、メイントランジスタMP11のオン時間が短くなる。その結果、一度のスイッチングによる出力電圧の上昇も少なくなる。出力電圧を保つ為には、絶えずスイッチングを行わなければならない。しかし、絶えずスイッチングが行なわれると、回路の動作割合が上がることになる。電力効率は、入力電力に対する出力電力の割合(出力電力/入力電力)により求めることができる。入力電力は、回路動作電流の全体に入力電圧をかけて導くことができる。回路の動作割合が上がることにより、入力電力の値が大きくなり、電力効率が小さくなってしまう。

【0007】

従って、本発明の課題は、軽負荷時における電力効率を高めることができる、DC−DCコンバータを提供することにある。

【課題を解決するための手段】

【0008】

以下に、(発明を実施するための形態)で使用される番号を用いて、課題を解決するための手段を説明する。これらの番号は、(特許請求の範囲)の記載と(発明を実施するための形態)との対応関係を明らかにするために付加されたものである。ただし、それらの番号を、(特許請求の範囲)に記載されている発明の技術的範囲の解釈に用いてはならない。

【0009】

本発明に係る降圧DC−DCコンバータ(1)は、電源と第1ノードとを接続するように設けられた、第1スイッチング素子(MP1)と、前記第1ノードと接地との間を接続するように設けられた、第2スイッチング素子(MN1)と、前記第1ノードと出力端との間に設けられた、インダクタンス素子(L101)と、前記出力端と接地との間に設けられた、コンデンサ(C101)と、前記出力端の出力電圧を制御する、制御回路(2)とを具備する。前記制御回路(2)は、前記出力端から負荷に流れる負荷電流が小さいほど、前記第1スイッチング素子(MP1)のオン期間が小さくなるように、前記第1スイッチング素子(MP1)のオン期間を決定し、前記決定したオン期間に対応するパルス幅を有するパルス信号を生成する、パルス信号生成回路(3)と、予め定められた最低パルス幅を有するパルス信号を最低パルス信号として生成する、最低パルス幅制限回路(21)と、前記パルス信号と前記最低パルス信号とのうちのいずれかを選択パルス信号として選択する、セレクタ(22)と、前記選択パルス信号に基づいて、前記第1スイッチング素子(MP1)及び前記第2スイッチング素子(MN1)を、一方のスイッチング素子がオン状態になっているときに他方のスイッチング素子がオフ状態になるように、切り換える、ドライバ部(5)と、前記出力端から前記第1ノードに流れる逆電流を検出する、逆電流検出回路(4)とを備える。前記ドライバ部(5)は、前記逆電流が検出された場合に、前記第2スイッチング素子をオフ状態になるように制御する。前記セレクタ(22)は、前記逆電流が検出されない場合に、前記パルス信号を選択し、前記逆電流が検出された場合に、前記最低パルス信号と前記パルス信号とのうちのパルス幅が短い信号を選択する。

【0010】

本発明に係る昇圧DC−DCコンバータ(1)は、電源と第2ノード(LX)との間に設けられた、インダクタンス素子(L101)と、前記第2ノードと出力端との間に設けられた、第1スイッチング素子(MP1)と、前記第2ノードと接地との間を接続するように設けられた、第2スイッチング素子(MN1)と、前記出力端と接地との間に設けられた、コンデンサ(C101)と、前記出力端の出力電圧を制御する、制御回路(2)とを具備する。前記制御回路(2)は、前記出力端から負荷に流れる負荷電流が小さいほど、前記第1スイッチング素子のオン期間が小さくなるように、前記第1スイッチング素子のオン期間を決定し、前記決定したオン期間に対応するパルス幅を有するパルス信号を生成する、パルス信号生成回路(3)と、予め定められた最低パルス幅を有するパルス信号を最低パルス信号として生成する、最低パルス幅制限回路(21)と、前記パルス信号と前記最低パルス信号とのうちのいずれかを選択パルス信号として選択する、セレクタ(22)と、前記選択パルス信号に基づいて、前記第1スイッチング素子及び前記第2スイッチング素子を、一方のスイッチング素子がオン状態になっているときに他方のスイッチング素子がオフ状態になるように、切り換える、ドライバ部(5)と、前記出力端から前記第2ノードに流れる逆電流を検出する、逆電流検出回路(4)とを備える。前記ドライバ部(4)は、前記逆電流が検出された場合に、前記第1スイッチング素子をオフ状態になるように制御する。前記セレクタ(22)は、前記逆電流が検出されない場合に、前記パルス信号を選択し、前記逆電流が検出された場合に、前記最低パルス信号と前記パルス信号とのうちのパルス幅が短い信号を選択する。

【発明の効果】

【0011】

本発明によれば、軽負荷時における電力効率を高めることができる、DC−DCコンバータが提供される。

【図面の簡単な説明】

【0012】

【図1】特許文献1に記載された降圧型同期整流方式のスイッチング電源装置を示す構成図である。

【図2】Nchドライバの動作波形を示す図である。

【図3】第1の実施形態に係るDC−DCコンバータを示すブロック図である。

【図4】DC−DCコンバータの動作方法を示すタイミングチャートである。

【図5】第2の実施形態に係る昇圧DC−DCコンバータを示すブロック図である。

【図6】第2の実施形態に係るDC−DCコンバータの動作方法を示すタイミングチャートである。

【図7】第3の実施形態に係る昇降圧DC−DCコンバータを示すブロック図である。

【発明を実施するための形態】

【0013】

以下に、図面を参照しつつ、本発明の実施形態を説明する。

【0014】

(第1の実施形態)

図3は、本実施形態に係るDC−DCコンバータ1を示すブロック図である。本実施形態に係るDC−DCコンバータ1は、同期整流型の降圧コンバータである。図3に示されるように、DC−DCコンバータ1は、第1トランジスタMP1、第2トランジスタMN1、インダクタンス素子L101、コンデンサC101、及び制御回路2を備えている。

【0015】

第1トランジスタMP1は、Pチャネル型トランジスタであり、電源VDDと第1ノードLX1との間に設けられている。また、第2トランジスタMN1は、Nチャネル型トランジスタであり、第1ノードLX1とグランドGNDとの間に設けられている。インダクタンス素子L101は、第1ノードLX1と出力端OUTとの間に設けられている。コンデンサC101は、出力端OUTとグランドGNDとの間に設けられている。また、出力端OUTとグランドGNDとの間には、出力電圧を分圧する、抵抗素子R101及びR102が直列に接続されている。

【0016】

制御回路2は、第1トランジスタMP1及び第2トランジスタMN1のオン/オフを切り換えることにより、出力電圧を制御する機能を有している。図3に示されるように、制御回路2は、パルス信号生成回路3、逆電流検出回路4、ドライバ部5、最低パルス幅制限回路21及びセレクタ22を備えている。

【0017】

逆電流検出回路4は、出力端OUTから、第1ノードLX、及び第2トランジスタMN1を介してグランドGNDに流れる逆電流を検出する機能を有している。逆電流検出回路4は、コンパレータ16、及びD−フリップフロップ回路17を有している。コンパレータ16は、第1ノードLXにおける電圧とグランド電圧とを比較し、第1ノードLXにおける電圧の方がグランド電圧よりも大きい場合に、逆電流を検出し、比較結果信号COMP_OUTとしてハイレベルの信号を生成する。D−フリップフロップ回路17は、比較結果信号COMP_OUTとしてハイレベルの信号を取得すると、後述するPWM_N信号がローレベルになるまでの間、制御信号Q_Bとしてローレベルの信号を出力する。

【0018】

パルス信号生成回路3は、出力端OUTから負荷に流れる負荷電流が小さいほど、第1トランジスタMP1のオン期間が小さくなるように、第1トランジスタMP1のオン期間を決定し、決定したオン期間に対応するパルス幅を有するパルス信号pulseを生成する回路である。パルス信号生成回路3は、基準電圧回路11、誤差アンプ12、及びPWM制御回路13を有している。基準電圧回路11は、目標電圧に対応する基準電圧Vrefを生成する。誤差アンプ12は、一方の入力端で抵抗素子R101と抵抗素子R102との間に接続されており、他方の入力端で基準電圧回路11に接続されている。誤差アンプ12は、抵抗素子R101と抵抗素子R102との間の電圧(以下、フィードバック電圧FB)を基準電圧Vrefと比較し、フィードバック電圧FBが基準電圧Vrefよりも小さい場合に、フィードバック電圧FBと基準電圧Vrefとの差を示すエラー信号errを生成する。PWM制御回路13は、エラー信号errに基づいて、フィードバック電圧FBと基準電圧Vrefとの差が大きいほど長くなるようにパルス幅を決定し、クロック信号と同期させてパルス信号pulseを生成する。

【0019】

最低パルス幅制限回路は、予め定められたパルス幅を有する、最低パルス信号MIN_Wを生成する機能を有している。最低パルス幅制限回路は、パルス信号pulseを取得し、パルス信号pulseに同期させて、最低パルス信号MIN_Wを生成する。

【0020】

セレクタ22は、逆流が生じていない場合、パルス信号pulseを選択信号DRVとして選択する。また、逆流が生じている場合、最低パルス信号MIN_Wとパルス信号pulseとのうちのパルス幅が大きい信号を、選択信号DRVとして選択する機能を有している。セレクタ22は、初期時には、パルス信号pulseを選択信号DRVとして選択する。そして、セレクタ22は、COMP_OUT信号がハイレベルに切り替わったとき(逆電流が検出されたとき)、後述するPWM_N2信号がハイレベルになるまで、パルス信号pulseと最低パルス信号MIN_Wのうちのパルス幅が長い方の信号を、選択信号DRVとして選択する。

【0021】

ドライバ部5は、第1トランジスタMP1及び第2トランジスタMN1を制御する機能を有している。ドライバ部5は、ドライバ回路14、及びAND回路15を有している。ドライバ回路14は、選択信号DRVと同じ信号を、制御信号PWM_Pとして生成し、第1トランジスタMP1のゲートに供給する。また、ドライバ回路14は、選択信号DRVと同じ信号を、制御信号PWM_Nとして生成し、AND回路15に供給する。AND回路15は、一方の入力端で制御信号PWM_Nを受け取り、他方の入力端で制御信号Q_Bを取得する。AND回路15は、出力信号として、制御信号PWM_N2を生成し、第2トランジスタMN1のゲートに供給する。このような構成によれば、逆流が起きていない場合、制御信号Q_Bとしてハイレベルの信号がAND回路15に供給されるので、AND回路15は、制御信号PWM_N2として制御信号PWM_Nと同じ信号を、第2トランジスタMN1のゲートに供給する。その結果、第2トランジスタMN1のオン/オフは、制御信号PWM_N2(選択信号DRV)に基づいて切り換えられる。一方、逆流が起きた場合、制御信号Q_Bとしてローレベルの信号がAND回路15に供給される。その結果、制御信号PWM_Nに関係なく、AND回路15は、制御信号PWM_N2としてローレベルの信号を第2トランジスタMN1のゲートに供給する。その結果、第2トランジスタMN1は、制御信号PWM_N2(選択信号DRV)に関係なく、オフ状態になるように制御される。

【0022】

続いて、本実施形態に係るDC−DCコンバータの動作方法を説明する。

【0023】

図4は、DC−DCコンバータ1の動作方法を示すタイミングチャートである。図4には、フィードバック電圧FB、第1ノードLX1の電圧、負荷電流I_load、比較結果信号COMP_OUT、制御信号Q_B、パルス信号pulse、最低パルス信号MIN_W、選択信号DRV、制御信号PWM_P、制御信号PWM_N、及び制御信号PWM_N2の波形が示されている。

【0024】

図4に示される例では、時刻t1以前において、負荷電流I_loadが臨界電流よりも大きく、時刻t1よりも後においては、負荷電流I_loadが臨界電流よりも小さい。尚、臨界電流とは、逆流が起きるかおきないかの境目を示す電流である。

【0025】

時刻t1以前においては、既述のように、負荷電流I_loadが臨界電流よりも大きい。負荷電流I_loadが大きい為、パルス信号生成回路3は、パルス信号pulseとして、負荷電流I_loadが小さいときよりもパルス幅が大きい信号を生成する。また、負荷電流I_loadが臨界電流よりも大きいので、逆流は生じない。そのため、比較結果信号COMP_OUTはローレベルとなり、セレクタ22は、選択信号DRVとして、パルス信号pulseを選択する。また、制御信号Q_Bとしてハイレベルの信号が出力されるため、AND回路15は、制御信号PWM_Nを制御信号PWM_N2として第2トランジスタMN1のゲートに供給する。これにより、第1トランジスタMP1及び第2トランジスタMN1の状態は、パルス信号pulseに基づいて、切り換えられる。すなわち、パルス信号pulseがローレベルになっているとき、第1トランジスタMP1はオン状態になり、第2トランジスタMN1はオフ状態になる。第1トランジスタMP1がオン状態になっている間(パルス信号pulseがローレベルである間)、出力電圧は上昇し、フィードバック電圧FBも上昇する。

【0026】

一方、時刻t1よりも後では、既述のように、負荷電流I_loadが臨界電流よりも小さくなっている。負荷電流I_loadが小さい為、パルス信号生成回路3は、パルス信号pulseとして、パルス幅が小さい信号を生成する。また、負荷電流は、逆流が発生するような大きさになっている。すなわち、時刻t1において、選択信号DRVがローレベルからハイレベルに切り替わると、第1トランジスタMP1がオン状態からオフ状態に切り替わり、第2トランジスタMN1がオフ状態からオン状態に切り替わる。その結果、第1ノードLX1の電圧は、グランド電圧よりも低い電圧に切り替わる。その後、第1ノードLX1の電圧は上昇し、グランド電圧を超える。図4に示される例では、時刻t3に、第1ノードLXの電圧がグランド電圧を超えている。第1ノードLX1の電圧がグランド電圧を超えると、コンパレータ16が、逆電流を検出し、比較結果信号COMP_OUTとしてハイレベルの信号を生成する。これにより、D−フリップフロップ回路17が、制御信号PWM_Nがローレベルに切り替わるまで、制御信号Q_Bとしてローレベルの信号を出力する。その結果、AND回路15が、ローレベルの信号を制御信号PWM_N2として第2トランジスタMN1のゲートに供給し、第2トランジスタMN1がオフ状態になるように制御される。第2トランジスタMN1がオフ状態になるので、逆電流が防止される。

【0027】

また、セレクタ22は、時刻t2において、比較結果信号COMP_OUTとしてハイレベルの信号を取得すると、選択信号DRVとして、最低パルス信号MIN_Wとパルス信号pulseのうち、パルス幅が大きい方の信号を選択する。図4に示される例では、最低パルス信号MIN_Wのパルス幅の方がパルス信号pulseよりも大きいので、最低パルス信号MIN_Wが選択信号DRVとして選択される。その結果、ドライバ回路14は、最低パルス信号MIN_Wを制御信号PWM_Pとして第1トランジスタMP1のゲートに供給する。これにより、第1トランジスタMP1は、パルス信号pulseが選択された場合よりも長い期間、オン状態になるように制御される。図4に示される例では、時刻t3〜時刻t4までの間、第1トランジスタMP1がオン状態になり、フィードバック電圧FBが上昇している。その結果、フィードバック電圧FBは、パルス信号pulseが選択された場合よりも大きく上昇する。フィードバック電圧FBが大きく上昇するので、次にフィードバック電圧FBが基準電圧Vrefを下回るまでの期間が長くなり、次に第1トランジスタMP1が切り換えられるまで(時刻t5)までの期間が長くなる。

【0028】

以上説明したように、本実施形態によれば、逆流が生じるような軽負荷時には、セレクタ22が、パルス信号pulseと最低パルス信号MIN_Wのうちのパルス幅が大きい方の信号を選択する。そのため、軽負荷時であっても、第1トランジスタMP1は、最低パルス信号MIN_Wのパルス幅以上の期間、オン状態になる。出力電圧の増加量が大きくなり、次にフィードバック電圧FBが基準電圧Vrefを下回るまでの期間が長くなる。スイッチング動作は、フィードバック電圧FBが基準電圧Vrefを下回るまで行われないため、確実に間欠動作を行うことが可能となる。回路が連続動作しないので、消費電力の増加を抑えることができ、電力効率を改善することができる。

【0029】

(第2の実施形態)

続いて、第2の実施形態について説明する。第1の実施形態では、降圧DC−DCコンバータについて説明した。これに対し、本実施形態では、昇圧DC−DCコンバータについて説明する。

【0030】

図5は、本実施形態に係る昇圧DC−DCコンバータ1を示すブロック図である。本実施形態においても、第1の実施形態と同様に、DC−DCコンバータ1は、第1トランジスタMP1、第2トランジスタMN1、インダクタンス素子L101、コンデンサC101、及び制御回路2を備えている。但し、インダクタンス素子L101は、電源VDDと第2ノードLX2との間に設けられている。また、第1トランジスタMP1は、第2ノードLX2と出力端OUTとの間に設けられている。更に、逆電流検出回路4、及びドライバ部5の構成が変更されている。その他の点については、第1の実施形態と同様である。

【0031】

図5に示されるように、逆電流検出回路4は、第1の実施形態と同様に、コンパレータ16及びD−フリップフロップ回路17を有している。但し、コンパレータ16は、出力端OUTの電圧(出力電圧)と第2ノードLX2の電圧とを比較し、出力電圧が第2ノードLXの電圧よりも小さい場合に、逆電流を検出し、比較結果信号COMP_OUTとしてハイレベルの信号を出力する。D−フリップフロップ回路17は、比較結果信号COMP_OUTとしてハイレベルの信号を取得すると、制御信号PWM_Nがローレベルになるまで、制御信号Qとしてハイレベルの信号を出力する。

【0032】

ドライバ部5は、ドライバ回路14及びOR回路18を備えている。ドライバ回路14は、選択信号DRVと同じ信号を制御信号PWM_PとしてOR回路18に供給する。また、ドライバ回路14は、選択信号DRVと同じ信号を制御信号PWM_Nとして第2トランジスタMN1のゲートに供給する。OR回路18は、一方の入力端で制御信号PWM_Pを取得し、他方の入力端で制御信号Qを取得する。OR回路18の出力信号は、PWM_P2として、第1トランジスタMP1のゲートに供給される。

【0033】

続いて、本実施形態に係るDC−DCコンバータの動作方法について説明する。図6は、本実施形態に係るDC−DCコンバータの動作方法を示すタイミングチャートである。図6に示されるように、時刻t1以前においては、負荷電流I_loadが臨界電流を超えており、時刻t1より後は、負荷電流I_loadが臨界電流を下回っている。

【0034】

時刻t1以前においては、負荷電流I_loadが臨界電流を超えているので、逆流は生じない。従って、コンパレータ16は、比較結果信号COMP_OUTとして、ローレベルの信号を生成する。そのため、セレクタ22は、パルス信号pulseを選択信号DRVとして選択する。また、D−フリップフロップ回路17は、制御信号Qとして、ローレベルの信号を出力する。その結果、ドライバ部5において、OR回路18は、制御信号PWM_Pを制御信号PWM_P2として第1トランジスタMP1のゲートに供給する。すなわち、時刻t1以前においては、パルス信号pulseに基づいて、第1トランジスタMP1及び第2トランジスタMN1の状態が切り換えられる。

【0035】

一方、時刻t1より後では、負荷電流I_loadが臨界電流よりも小さくなっている。負荷電流I_loadが小さいので、パルス信号生成回路3は、パルス信号pulseとしてパルス幅が小さい信号を出力する。また、逆流が生じた段階(時刻t3)において、コンパレータ16が逆流を検出し、比較結果信号COMP_OUTとしてハイレベルの信号を出力する。D−フリップフロップ回路17は、比較結果信号COMP_OUTとしてハイレベルの信号を取得すると、制御信号Qとしてハイレベルの信号を出力する。これにより、OR回路18が制御信号PWM_P2としてハイレベルの信号を第1トランジスタMP1のゲートに印加し、第1トランジスタMP1がオフ状態になるように制御される。これにより、逆流が防止される。

【0036】

また、比較結果信号COMP_OUTとしてハイレベルの信号が生成されるので、セレクタ22は、パルス信号pulseと最低パルス信号MIN_Wのうちのパルス幅が大きい方の信号を選択信号DRVとして選択する。図6に示される例では、最低パルス信号MIN_Wが選択信号DRVとして選択されている。これにより、時刻t1以降では、最低パルス信号MIN_Wのパルス幅に対応する期間、第2トランジスタMN1がオン状態になり、出力電圧及びフィードバック電圧FBが上昇する。図6に示される例では、時刻t3から時刻t4までの期間、第2トランジスタMN1がオン状態になり、出力電圧及びフィードバック電圧FBが上昇している。その結果、第1の実施形態と同様に、出力電圧の増加量が大きくなり、次にフィードバック電圧FBが基準電圧Vrefを下回るまでの期間が長くなる。軽負荷時における回路の連続動作が防止され、消費電力の増加が抑制され、電力効率が改善される。

【0037】

(第3の実施形態)

続いて、第3の実施形態について説明する。本実施形態では、第1の実施形態に係る降圧DC−DCコンバータと第2の実施形態に係る昇圧DC−DCコンバータが組み合わされた昇降圧DC−DCコンバータについて説明する。図7は、本実施形態に係る昇降圧DC−DCコンバータを示すブロック図である。

【0038】

図7に示されるように、本実施形態に係る昇降圧DC−DCコンバータは、降圧DC−DCコンバータ1−1と、降圧DC−DCコンバータ1−2とを備えている。昇圧DC−DCコンバータ1−1の構成は、第1の実施形態と同様であり、降圧DC−DCコンバータ1−2の構成は、第2の実施形態と同様である。また、降圧DC−DCコンバータ1−1及び降圧DC−DCコンバータ1−2において、基準電圧回路11、誤差アンプ12、及びインダクタンス素子L101は、共通に用いられている。

【0039】

詳細には、降圧DC−DCコンバータ1−1の第1トランジスタMP1は、電源VDDと第1ノードLX1との間に設けられている。また、降圧DC−DCコンバータ1−1の第2トランジスタMN1は、第1ノードLX1とグランドGNDとの間に設けられている。インダクタンス素子L101は、第1ノードLX1と第2ノードLX2との間に設けられている。昇圧DC−DCコンバータ1−2の第1トランジスタMP2は、第2ノードLX2と出力端OUTとの間に設けられている。降圧DC−DCコンバータ1−2の第2トランジスタMN2は、第2ノードLX2とグランドGNDとの間に設けられている。

【0040】

本実施形態において、降圧時には、昇圧DC−DCコンバータ1−2において、第1トランジスタMP1がオン状態となり、第2トランジスタMN1がオフ状態になるように制御される。そして、降圧DC−DCコンバータ1−1が第1の実施形態と同様に動作する。また、昇圧時には、降圧DC−DCコンバータ1−1において、第1トランジスタMP1がオン状態となり、第2トランジスタMN1がオフ状態になるように制御される。そして、昇圧DC−DCコンバータ1−2が第2の実施形態と同様に動作する。これにより、既述の実施形態と同様に、軽負荷時における回路の連続動作が防止され、消費電力の増加が抑制され、電力効率が改善される。

【符号の説明】

【0041】

1 DC−DCコンバータ

2 制御回路

3 パルス信号生成回路

4 逆電流検出回路

5 ドライバ部

11 基準電圧回路

12 誤差アンプ

13 PWM制御回路

14 ドライバ回路

15 AND回路

16 コンパレータ

17 D−フリップフロップ回路

18 OR回路

19 昇降圧DC−DCコンバータ

21 最低パルス幅制限回路

22 セレクタ

111 電源

112 出力端子

113 負荷

114 電源制御回路

115 Pchドライバ

116A Nchドライバ

【技術分野】

【0001】

本発明は、DC−DCコンバータに関する。

【背景技術】

【0002】

デジタルカメラセット等の電気機器では、モータ、メモリ、スピーカ、及びバックライト等を駆動するために、様々な電源電圧が必要とされる。入力電圧を所望する電圧に変換するために、同期整流型のDC−DCコンバータが用いられる。現在のデジタルカメラ等の市場では、低消費電力及び長時間動作が要求されている。長時間動作を実現するために、DC−DCコンバータに対して、電力効率の向上が求められている。その結果、従来は問題にされていなかった無負荷時若しくは軽負荷時においても、高い電力効率が求められるようになっている。

【0003】

関連技術として、特許文献1(特開2010−239778号公報)に記載されたスイッチング電源装置が挙げられる。図1は、特許文献1に記載された降圧型同期整流方式のスイッチング電源装置を示す構成図である。このスイッチング電源装置は、メイントランジスタMP11、同期整流トランジスタMN11、インダクタL1、キャパシタC1、電源制御回路114、Pchドライバ115及びNchドライバ116Aを備えている。このスイッチング電源装置では、Pchドライバ115によってメイントランジスタMP11がオンになったとき(同期整流トランジスタMN11がオフになったとき)、電流が、電源11から、メイントランジスタMP11及びインダクタL1を介して、キャパシタC1へ流れ、キャパシタC1が充電される。また、Nchドライバ16Aによって同期整流トランジスタMN11がオン状態になったとき(メイントランジスタMP11がオフ)、インダクタL1に蓄積されたエネルギーにより、電流が、同期整流トランジスタMN11から、インダクタL1を介してキャパシタC1に流れ、キャパシタC1が充電される。後者のとき、負荷電流が小さいと、インダクタL1を流れる電流の方向が逆転する(逆流する)ことがある。逆流により、エネルギーが失われ、電力効率が低下する。そこで、ノードLX1の電圧V_LX1の変化が、Nchドライバ116Aによって検出され、電流の方向が逆転するとき、同期整流トランジスタMN11がオフにされる。

【0004】

図2は、上述のNchドライバ116Aの動作波形を示す図である。電源制御回路114が、制御信号PRDRV_Nを「L」から「H」に切り換えると(制御信号PRDRV_Pが「L」から「H」に変化してメイントランジスタMP11がオフになると)、駆動信号DRV_Nが「L」から「H」に変化し、同期整流トランジスタMN11がオフ状態からオン状態に変化し、同期整流トランジスタMN11からインダクタL1を介してキャパシタC1に電流が流れる。これにより、ノードLX1の電圧V_LX1は、接地電位(GND)よりも低い負の電位になる。この後、時間経過により、インダクタL1の電流は減少し、ノードLX1の電位は上昇する。インダクタL1の電流がゼロになると、ノードLX1の電圧V_LX1もゼロになる。その後インダクタL1から同期整流トランジスタMN11の方向に逆電流が流れ始める。この逆電流を防止するため、電圧V_LX1が0になると、Nchドライバ116Aにより、同期整流トランジスタMN11がオフ状態になるように制御される。これにより、逆電流による電力効率の低下を防ぐことができる。

【先行技術文献】

【非特許文献】

【0005】

【特許文献1】特開2010−239778号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

引用文献1に記載されたスイッチング電源装置によれば、軽負荷時において、逆電流の発生を防止することにより、電力効率の低下が抑制される。しかしながら、通常、メイントランジスタMP11及び同期整流トランジスタの状態(オン状態又はオフ状態)は、PWM(Pulse Width Modulation)制御により切り換えられる。軽負荷時には、メイントランジスタMP11のオン時間が短くなる。その結果、一度のスイッチングによる出力電圧の上昇も少なくなる。出力電圧を保つ為には、絶えずスイッチングを行わなければならない。しかし、絶えずスイッチングが行なわれると、回路の動作割合が上がることになる。電力効率は、入力電力に対する出力電力の割合(出力電力/入力電力)により求めることができる。入力電力は、回路動作電流の全体に入力電圧をかけて導くことができる。回路の動作割合が上がることにより、入力電力の値が大きくなり、電力効率が小さくなってしまう。

【0007】

従って、本発明の課題は、軽負荷時における電力効率を高めることができる、DC−DCコンバータを提供することにある。

【課題を解決するための手段】

【0008】

以下に、(発明を実施するための形態)で使用される番号を用いて、課題を解決するための手段を説明する。これらの番号は、(特許請求の範囲)の記載と(発明を実施するための形態)との対応関係を明らかにするために付加されたものである。ただし、それらの番号を、(特許請求の範囲)に記載されている発明の技術的範囲の解釈に用いてはならない。

【0009】

本発明に係る降圧DC−DCコンバータ(1)は、電源と第1ノードとを接続するように設けられた、第1スイッチング素子(MP1)と、前記第1ノードと接地との間を接続するように設けられた、第2スイッチング素子(MN1)と、前記第1ノードと出力端との間に設けられた、インダクタンス素子(L101)と、前記出力端と接地との間に設けられた、コンデンサ(C101)と、前記出力端の出力電圧を制御する、制御回路(2)とを具備する。前記制御回路(2)は、前記出力端から負荷に流れる負荷電流が小さいほど、前記第1スイッチング素子(MP1)のオン期間が小さくなるように、前記第1スイッチング素子(MP1)のオン期間を決定し、前記決定したオン期間に対応するパルス幅を有するパルス信号を生成する、パルス信号生成回路(3)と、予め定められた最低パルス幅を有するパルス信号を最低パルス信号として生成する、最低パルス幅制限回路(21)と、前記パルス信号と前記最低パルス信号とのうちのいずれかを選択パルス信号として選択する、セレクタ(22)と、前記選択パルス信号に基づいて、前記第1スイッチング素子(MP1)及び前記第2スイッチング素子(MN1)を、一方のスイッチング素子がオン状態になっているときに他方のスイッチング素子がオフ状態になるように、切り換える、ドライバ部(5)と、前記出力端から前記第1ノードに流れる逆電流を検出する、逆電流検出回路(4)とを備える。前記ドライバ部(5)は、前記逆電流が検出された場合に、前記第2スイッチング素子をオフ状態になるように制御する。前記セレクタ(22)は、前記逆電流が検出されない場合に、前記パルス信号を選択し、前記逆電流が検出された場合に、前記最低パルス信号と前記パルス信号とのうちのパルス幅が短い信号を選択する。

【0010】

本発明に係る昇圧DC−DCコンバータ(1)は、電源と第2ノード(LX)との間に設けられた、インダクタンス素子(L101)と、前記第2ノードと出力端との間に設けられた、第1スイッチング素子(MP1)と、前記第2ノードと接地との間を接続するように設けられた、第2スイッチング素子(MN1)と、前記出力端と接地との間に設けられた、コンデンサ(C101)と、前記出力端の出力電圧を制御する、制御回路(2)とを具備する。前記制御回路(2)は、前記出力端から負荷に流れる負荷電流が小さいほど、前記第1スイッチング素子のオン期間が小さくなるように、前記第1スイッチング素子のオン期間を決定し、前記決定したオン期間に対応するパルス幅を有するパルス信号を生成する、パルス信号生成回路(3)と、予め定められた最低パルス幅を有するパルス信号を最低パルス信号として生成する、最低パルス幅制限回路(21)と、前記パルス信号と前記最低パルス信号とのうちのいずれかを選択パルス信号として選択する、セレクタ(22)と、前記選択パルス信号に基づいて、前記第1スイッチング素子及び前記第2スイッチング素子を、一方のスイッチング素子がオン状態になっているときに他方のスイッチング素子がオフ状態になるように、切り換える、ドライバ部(5)と、前記出力端から前記第2ノードに流れる逆電流を検出する、逆電流検出回路(4)とを備える。前記ドライバ部(4)は、前記逆電流が検出された場合に、前記第1スイッチング素子をオフ状態になるように制御する。前記セレクタ(22)は、前記逆電流が検出されない場合に、前記パルス信号を選択し、前記逆電流が検出された場合に、前記最低パルス信号と前記パルス信号とのうちのパルス幅が短い信号を選択する。

【発明の効果】

【0011】

本発明によれば、軽負荷時における電力効率を高めることができる、DC−DCコンバータが提供される。

【図面の簡単な説明】

【0012】

【図1】特許文献1に記載された降圧型同期整流方式のスイッチング電源装置を示す構成図である。

【図2】Nchドライバの動作波形を示す図である。

【図3】第1の実施形態に係るDC−DCコンバータを示すブロック図である。

【図4】DC−DCコンバータの動作方法を示すタイミングチャートである。

【図5】第2の実施形態に係る昇圧DC−DCコンバータを示すブロック図である。

【図6】第2の実施形態に係るDC−DCコンバータの動作方法を示すタイミングチャートである。

【図7】第3の実施形態に係る昇降圧DC−DCコンバータを示すブロック図である。

【発明を実施するための形態】

【0013】

以下に、図面を参照しつつ、本発明の実施形態を説明する。

【0014】

(第1の実施形態)

図3は、本実施形態に係るDC−DCコンバータ1を示すブロック図である。本実施形態に係るDC−DCコンバータ1は、同期整流型の降圧コンバータである。図3に示されるように、DC−DCコンバータ1は、第1トランジスタMP1、第2トランジスタMN1、インダクタンス素子L101、コンデンサC101、及び制御回路2を備えている。

【0015】

第1トランジスタMP1は、Pチャネル型トランジスタであり、電源VDDと第1ノードLX1との間に設けられている。また、第2トランジスタMN1は、Nチャネル型トランジスタであり、第1ノードLX1とグランドGNDとの間に設けられている。インダクタンス素子L101は、第1ノードLX1と出力端OUTとの間に設けられている。コンデンサC101は、出力端OUTとグランドGNDとの間に設けられている。また、出力端OUTとグランドGNDとの間には、出力電圧を分圧する、抵抗素子R101及びR102が直列に接続されている。

【0016】

制御回路2は、第1トランジスタMP1及び第2トランジスタMN1のオン/オフを切り換えることにより、出力電圧を制御する機能を有している。図3に示されるように、制御回路2は、パルス信号生成回路3、逆電流検出回路4、ドライバ部5、最低パルス幅制限回路21及びセレクタ22を備えている。

【0017】

逆電流検出回路4は、出力端OUTから、第1ノードLX、及び第2トランジスタMN1を介してグランドGNDに流れる逆電流を検出する機能を有している。逆電流検出回路4は、コンパレータ16、及びD−フリップフロップ回路17を有している。コンパレータ16は、第1ノードLXにおける電圧とグランド電圧とを比較し、第1ノードLXにおける電圧の方がグランド電圧よりも大きい場合に、逆電流を検出し、比較結果信号COMP_OUTとしてハイレベルの信号を生成する。D−フリップフロップ回路17は、比較結果信号COMP_OUTとしてハイレベルの信号を取得すると、後述するPWM_N信号がローレベルになるまでの間、制御信号Q_Bとしてローレベルの信号を出力する。

【0018】

パルス信号生成回路3は、出力端OUTから負荷に流れる負荷電流が小さいほど、第1トランジスタMP1のオン期間が小さくなるように、第1トランジスタMP1のオン期間を決定し、決定したオン期間に対応するパルス幅を有するパルス信号pulseを生成する回路である。パルス信号生成回路3は、基準電圧回路11、誤差アンプ12、及びPWM制御回路13を有している。基準電圧回路11は、目標電圧に対応する基準電圧Vrefを生成する。誤差アンプ12は、一方の入力端で抵抗素子R101と抵抗素子R102との間に接続されており、他方の入力端で基準電圧回路11に接続されている。誤差アンプ12は、抵抗素子R101と抵抗素子R102との間の電圧(以下、フィードバック電圧FB)を基準電圧Vrefと比較し、フィードバック電圧FBが基準電圧Vrefよりも小さい場合に、フィードバック電圧FBと基準電圧Vrefとの差を示すエラー信号errを生成する。PWM制御回路13は、エラー信号errに基づいて、フィードバック電圧FBと基準電圧Vrefとの差が大きいほど長くなるようにパルス幅を決定し、クロック信号と同期させてパルス信号pulseを生成する。

【0019】

最低パルス幅制限回路は、予め定められたパルス幅を有する、最低パルス信号MIN_Wを生成する機能を有している。最低パルス幅制限回路は、パルス信号pulseを取得し、パルス信号pulseに同期させて、最低パルス信号MIN_Wを生成する。

【0020】

セレクタ22は、逆流が生じていない場合、パルス信号pulseを選択信号DRVとして選択する。また、逆流が生じている場合、最低パルス信号MIN_Wとパルス信号pulseとのうちのパルス幅が大きい信号を、選択信号DRVとして選択する機能を有している。セレクタ22は、初期時には、パルス信号pulseを選択信号DRVとして選択する。そして、セレクタ22は、COMP_OUT信号がハイレベルに切り替わったとき(逆電流が検出されたとき)、後述するPWM_N2信号がハイレベルになるまで、パルス信号pulseと最低パルス信号MIN_Wのうちのパルス幅が長い方の信号を、選択信号DRVとして選択する。

【0021】

ドライバ部5は、第1トランジスタMP1及び第2トランジスタMN1を制御する機能を有している。ドライバ部5は、ドライバ回路14、及びAND回路15を有している。ドライバ回路14は、選択信号DRVと同じ信号を、制御信号PWM_Pとして生成し、第1トランジスタMP1のゲートに供給する。また、ドライバ回路14は、選択信号DRVと同じ信号を、制御信号PWM_Nとして生成し、AND回路15に供給する。AND回路15は、一方の入力端で制御信号PWM_Nを受け取り、他方の入力端で制御信号Q_Bを取得する。AND回路15は、出力信号として、制御信号PWM_N2を生成し、第2トランジスタMN1のゲートに供給する。このような構成によれば、逆流が起きていない場合、制御信号Q_Bとしてハイレベルの信号がAND回路15に供給されるので、AND回路15は、制御信号PWM_N2として制御信号PWM_Nと同じ信号を、第2トランジスタMN1のゲートに供給する。その結果、第2トランジスタMN1のオン/オフは、制御信号PWM_N2(選択信号DRV)に基づいて切り換えられる。一方、逆流が起きた場合、制御信号Q_Bとしてローレベルの信号がAND回路15に供給される。その結果、制御信号PWM_Nに関係なく、AND回路15は、制御信号PWM_N2としてローレベルの信号を第2トランジスタMN1のゲートに供給する。その結果、第2トランジスタMN1は、制御信号PWM_N2(選択信号DRV)に関係なく、オフ状態になるように制御される。

【0022】

続いて、本実施形態に係るDC−DCコンバータの動作方法を説明する。

【0023】

図4は、DC−DCコンバータ1の動作方法を示すタイミングチャートである。図4には、フィードバック電圧FB、第1ノードLX1の電圧、負荷電流I_load、比較結果信号COMP_OUT、制御信号Q_B、パルス信号pulse、最低パルス信号MIN_W、選択信号DRV、制御信号PWM_P、制御信号PWM_N、及び制御信号PWM_N2の波形が示されている。

【0024】

図4に示される例では、時刻t1以前において、負荷電流I_loadが臨界電流よりも大きく、時刻t1よりも後においては、負荷電流I_loadが臨界電流よりも小さい。尚、臨界電流とは、逆流が起きるかおきないかの境目を示す電流である。

【0025】

時刻t1以前においては、既述のように、負荷電流I_loadが臨界電流よりも大きい。負荷電流I_loadが大きい為、パルス信号生成回路3は、パルス信号pulseとして、負荷電流I_loadが小さいときよりもパルス幅が大きい信号を生成する。また、負荷電流I_loadが臨界電流よりも大きいので、逆流は生じない。そのため、比較結果信号COMP_OUTはローレベルとなり、セレクタ22は、選択信号DRVとして、パルス信号pulseを選択する。また、制御信号Q_Bとしてハイレベルの信号が出力されるため、AND回路15は、制御信号PWM_Nを制御信号PWM_N2として第2トランジスタMN1のゲートに供給する。これにより、第1トランジスタMP1及び第2トランジスタMN1の状態は、パルス信号pulseに基づいて、切り換えられる。すなわち、パルス信号pulseがローレベルになっているとき、第1トランジスタMP1はオン状態になり、第2トランジスタMN1はオフ状態になる。第1トランジスタMP1がオン状態になっている間(パルス信号pulseがローレベルである間)、出力電圧は上昇し、フィードバック電圧FBも上昇する。

【0026】

一方、時刻t1よりも後では、既述のように、負荷電流I_loadが臨界電流よりも小さくなっている。負荷電流I_loadが小さい為、パルス信号生成回路3は、パルス信号pulseとして、パルス幅が小さい信号を生成する。また、負荷電流は、逆流が発生するような大きさになっている。すなわち、時刻t1において、選択信号DRVがローレベルからハイレベルに切り替わると、第1トランジスタMP1がオン状態からオフ状態に切り替わり、第2トランジスタMN1がオフ状態からオン状態に切り替わる。その結果、第1ノードLX1の電圧は、グランド電圧よりも低い電圧に切り替わる。その後、第1ノードLX1の電圧は上昇し、グランド電圧を超える。図4に示される例では、時刻t3に、第1ノードLXの電圧がグランド電圧を超えている。第1ノードLX1の電圧がグランド電圧を超えると、コンパレータ16が、逆電流を検出し、比較結果信号COMP_OUTとしてハイレベルの信号を生成する。これにより、D−フリップフロップ回路17が、制御信号PWM_Nがローレベルに切り替わるまで、制御信号Q_Bとしてローレベルの信号を出力する。その結果、AND回路15が、ローレベルの信号を制御信号PWM_N2として第2トランジスタMN1のゲートに供給し、第2トランジスタMN1がオフ状態になるように制御される。第2トランジスタMN1がオフ状態になるので、逆電流が防止される。

【0027】

また、セレクタ22は、時刻t2において、比較結果信号COMP_OUTとしてハイレベルの信号を取得すると、選択信号DRVとして、最低パルス信号MIN_Wとパルス信号pulseのうち、パルス幅が大きい方の信号を選択する。図4に示される例では、最低パルス信号MIN_Wのパルス幅の方がパルス信号pulseよりも大きいので、最低パルス信号MIN_Wが選択信号DRVとして選択される。その結果、ドライバ回路14は、最低パルス信号MIN_Wを制御信号PWM_Pとして第1トランジスタMP1のゲートに供給する。これにより、第1トランジスタMP1は、パルス信号pulseが選択された場合よりも長い期間、オン状態になるように制御される。図4に示される例では、時刻t3〜時刻t4までの間、第1トランジスタMP1がオン状態になり、フィードバック電圧FBが上昇している。その結果、フィードバック電圧FBは、パルス信号pulseが選択された場合よりも大きく上昇する。フィードバック電圧FBが大きく上昇するので、次にフィードバック電圧FBが基準電圧Vrefを下回るまでの期間が長くなり、次に第1トランジスタMP1が切り換えられるまで(時刻t5)までの期間が長くなる。

【0028】

以上説明したように、本実施形態によれば、逆流が生じるような軽負荷時には、セレクタ22が、パルス信号pulseと最低パルス信号MIN_Wのうちのパルス幅が大きい方の信号を選択する。そのため、軽負荷時であっても、第1トランジスタMP1は、最低パルス信号MIN_Wのパルス幅以上の期間、オン状態になる。出力電圧の増加量が大きくなり、次にフィードバック電圧FBが基準電圧Vrefを下回るまでの期間が長くなる。スイッチング動作は、フィードバック電圧FBが基準電圧Vrefを下回るまで行われないため、確実に間欠動作を行うことが可能となる。回路が連続動作しないので、消費電力の増加を抑えることができ、電力効率を改善することができる。

【0029】

(第2の実施形態)

続いて、第2の実施形態について説明する。第1の実施形態では、降圧DC−DCコンバータについて説明した。これに対し、本実施形態では、昇圧DC−DCコンバータについて説明する。

【0030】

図5は、本実施形態に係る昇圧DC−DCコンバータ1を示すブロック図である。本実施形態においても、第1の実施形態と同様に、DC−DCコンバータ1は、第1トランジスタMP1、第2トランジスタMN1、インダクタンス素子L101、コンデンサC101、及び制御回路2を備えている。但し、インダクタンス素子L101は、電源VDDと第2ノードLX2との間に設けられている。また、第1トランジスタMP1は、第2ノードLX2と出力端OUTとの間に設けられている。更に、逆電流検出回路4、及びドライバ部5の構成が変更されている。その他の点については、第1の実施形態と同様である。

【0031】

図5に示されるように、逆電流検出回路4は、第1の実施形態と同様に、コンパレータ16及びD−フリップフロップ回路17を有している。但し、コンパレータ16は、出力端OUTの電圧(出力電圧)と第2ノードLX2の電圧とを比較し、出力電圧が第2ノードLXの電圧よりも小さい場合に、逆電流を検出し、比較結果信号COMP_OUTとしてハイレベルの信号を出力する。D−フリップフロップ回路17は、比較結果信号COMP_OUTとしてハイレベルの信号を取得すると、制御信号PWM_Nがローレベルになるまで、制御信号Qとしてハイレベルの信号を出力する。

【0032】

ドライバ部5は、ドライバ回路14及びOR回路18を備えている。ドライバ回路14は、選択信号DRVと同じ信号を制御信号PWM_PとしてOR回路18に供給する。また、ドライバ回路14は、選択信号DRVと同じ信号を制御信号PWM_Nとして第2トランジスタMN1のゲートに供給する。OR回路18は、一方の入力端で制御信号PWM_Pを取得し、他方の入力端で制御信号Qを取得する。OR回路18の出力信号は、PWM_P2として、第1トランジスタMP1のゲートに供給される。

【0033】

続いて、本実施形態に係るDC−DCコンバータの動作方法について説明する。図6は、本実施形態に係るDC−DCコンバータの動作方法を示すタイミングチャートである。図6に示されるように、時刻t1以前においては、負荷電流I_loadが臨界電流を超えており、時刻t1より後は、負荷電流I_loadが臨界電流を下回っている。

【0034】

時刻t1以前においては、負荷電流I_loadが臨界電流を超えているので、逆流は生じない。従って、コンパレータ16は、比較結果信号COMP_OUTとして、ローレベルの信号を生成する。そのため、セレクタ22は、パルス信号pulseを選択信号DRVとして選択する。また、D−フリップフロップ回路17は、制御信号Qとして、ローレベルの信号を出力する。その結果、ドライバ部5において、OR回路18は、制御信号PWM_Pを制御信号PWM_P2として第1トランジスタMP1のゲートに供給する。すなわち、時刻t1以前においては、パルス信号pulseに基づいて、第1トランジスタMP1及び第2トランジスタMN1の状態が切り換えられる。

【0035】

一方、時刻t1より後では、負荷電流I_loadが臨界電流よりも小さくなっている。負荷電流I_loadが小さいので、パルス信号生成回路3は、パルス信号pulseとしてパルス幅が小さい信号を出力する。また、逆流が生じた段階(時刻t3)において、コンパレータ16が逆流を検出し、比較結果信号COMP_OUTとしてハイレベルの信号を出力する。D−フリップフロップ回路17は、比較結果信号COMP_OUTとしてハイレベルの信号を取得すると、制御信号Qとしてハイレベルの信号を出力する。これにより、OR回路18が制御信号PWM_P2としてハイレベルの信号を第1トランジスタMP1のゲートに印加し、第1トランジスタMP1がオフ状態になるように制御される。これにより、逆流が防止される。

【0036】

また、比較結果信号COMP_OUTとしてハイレベルの信号が生成されるので、セレクタ22は、パルス信号pulseと最低パルス信号MIN_Wのうちのパルス幅が大きい方の信号を選択信号DRVとして選択する。図6に示される例では、最低パルス信号MIN_Wが選択信号DRVとして選択されている。これにより、時刻t1以降では、最低パルス信号MIN_Wのパルス幅に対応する期間、第2トランジスタMN1がオン状態になり、出力電圧及びフィードバック電圧FBが上昇する。図6に示される例では、時刻t3から時刻t4までの期間、第2トランジスタMN1がオン状態になり、出力電圧及びフィードバック電圧FBが上昇している。その結果、第1の実施形態と同様に、出力電圧の増加量が大きくなり、次にフィードバック電圧FBが基準電圧Vrefを下回るまでの期間が長くなる。軽負荷時における回路の連続動作が防止され、消費電力の増加が抑制され、電力効率が改善される。

【0037】

(第3の実施形態)

続いて、第3の実施形態について説明する。本実施形態では、第1の実施形態に係る降圧DC−DCコンバータと第2の実施形態に係る昇圧DC−DCコンバータが組み合わされた昇降圧DC−DCコンバータについて説明する。図7は、本実施形態に係る昇降圧DC−DCコンバータを示すブロック図である。

【0038】

図7に示されるように、本実施形態に係る昇降圧DC−DCコンバータは、降圧DC−DCコンバータ1−1と、降圧DC−DCコンバータ1−2とを備えている。昇圧DC−DCコンバータ1−1の構成は、第1の実施形態と同様であり、降圧DC−DCコンバータ1−2の構成は、第2の実施形態と同様である。また、降圧DC−DCコンバータ1−1及び降圧DC−DCコンバータ1−2において、基準電圧回路11、誤差アンプ12、及びインダクタンス素子L101は、共通に用いられている。

【0039】

詳細には、降圧DC−DCコンバータ1−1の第1トランジスタMP1は、電源VDDと第1ノードLX1との間に設けられている。また、降圧DC−DCコンバータ1−1の第2トランジスタMN1は、第1ノードLX1とグランドGNDとの間に設けられている。インダクタンス素子L101は、第1ノードLX1と第2ノードLX2との間に設けられている。昇圧DC−DCコンバータ1−2の第1トランジスタMP2は、第2ノードLX2と出力端OUTとの間に設けられている。降圧DC−DCコンバータ1−2の第2トランジスタMN2は、第2ノードLX2とグランドGNDとの間に設けられている。

【0040】

本実施形態において、降圧時には、昇圧DC−DCコンバータ1−2において、第1トランジスタMP1がオン状態となり、第2トランジスタMN1がオフ状態になるように制御される。そして、降圧DC−DCコンバータ1−1が第1の実施形態と同様に動作する。また、昇圧時には、降圧DC−DCコンバータ1−1において、第1トランジスタMP1がオン状態となり、第2トランジスタMN1がオフ状態になるように制御される。そして、昇圧DC−DCコンバータ1−2が第2の実施形態と同様に動作する。これにより、既述の実施形態と同様に、軽負荷時における回路の連続動作が防止され、消費電力の増加が抑制され、電力効率が改善される。

【符号の説明】

【0041】

1 DC−DCコンバータ

2 制御回路

3 パルス信号生成回路

4 逆電流検出回路

5 ドライバ部

11 基準電圧回路

12 誤差アンプ

13 PWM制御回路

14 ドライバ回路

15 AND回路

16 コンパレータ

17 D−フリップフロップ回路

18 OR回路

19 昇降圧DC−DCコンバータ

21 最低パルス幅制限回路

22 セレクタ

111 電源

112 出力端子

113 負荷

114 電源制御回路

115 Pchドライバ

116A Nchドライバ

【特許請求の範囲】

【請求項1】

電源と第1ノードとを接続するように設けられた、第1スイッチング素子と、

前記第1ノードと接地との間を接続するように設けられた、第2スイッチング素子と、

前記第1ノードと出力端との間に設けられた、インダクタンス素子と、

前記出力端と接地との間に設けられた、コンデンサと、

前記出力端の出力電圧を制御する、制御回路と、

を具備し、

前記制御回路は、

前記出力端から負荷に流れる負荷電流が小さいほど、前記第1スイッチング素子のオン期間が小さくなるように、前記第1スイッチング素子のオン期間を決定し、前記決定したオン期間に対応するパルス幅を有するパルス信号を生成する、パルス信号生成回路と、

予め定められた最低パルス幅を有するパルス信号を最低パルス信号として生成する、最低パルス幅制限回路と、

前記パルス信号と前記最低パルス信号とのうちのいずれかを選択パルス信号として選択する、セレクタと、

前記選択パルス信号に基づいて、前記第1スイッチング素子及び前記第2スイッチング素子を、一方のスイッチング素子がオン状態になっているときに他方のスイッチング素子がオフ状態になるように、切り換える、ドライバ部と、

前記出力端から前記第1ノードに流れる逆電流を検出する、逆電流検出回路とを備え、

前記ドライバ部は、前記逆電流が検出された場合に、前記第2スイッチング素子をオフ状態になるように制御し、

前記セレクタは、前記逆電流が検出されない場合に、前記パルス信号を選択し、前記逆電流が検出された場合に、前記最低パルス信号と前記パルス信号とのうちのパルス幅が大きい信号を選択する

降圧DC−DCコンバータ。

【請求項2】

請求項1に記載された降圧DC−DCコンバータであって、

前記パルス信号生成回路は、

基準電圧を生成する基準電圧回路と、

前記出力電圧に対応する電圧を前記基準電圧と比較し、前記基準電圧と前記出力電圧との差を示すエラー信号を生成する、誤差アンプと、

前記エラー信号に基づいて、前記第1スイッチング素子のオン期間を決定し、前記パルス信号を生成する

降圧DC−DCコンバータ。

【請求項3】

請求項1又は2に記載された降圧DC−DCコンバータであって、

前記逆電流検出回路は、前記第1ノードの電圧と接地電圧とを比較し、比較結果を示す比較結果信号を生成する、コンパレータを備えている

降圧DC−DCコンバータ。

【請求項4】

電源と第2ノードとの間に設けられた、インダクタンス素子と、

前記第2ノードと出力端との間に設けられた、第1スイッチング素子と、

前記第2ノードと接地との間を接続するように設けられた、第2スイッチング素子と、

前記出力端と接地との間に設けられた、コンデンサと、

前記出力端の出力電圧を制御する、制御回路と、

を具備し、

前記制御回路は、

前記出力端から負荷に流れる負荷電流が小さいほど、前記第2スイッチング素子のオン期間が小さくなるように、前記第2スイッチング素子のオン期間を決定し、前記決定したオン期間に対応するパルス幅を有するパルス信号を生成する、パルス信号生成回路と、

予め定められた最低パルス幅を有するパルス信号を最低パルス信号として生成する、最低パルス幅制限回路と、

前記パルス信号と前記最低パルス信号とのうちのいずれかを選択パルス信号として選択する、セレクタと、

前記選択パルス信号に基づいて、前記第1スイッチング素子及び前記第2スイッチング素子を、一方のスイッチング素子がオン状態になっているときに他方のスイッチング素子がオフ状態になるように、切り換える、ドライバ部と、

前記出力端から前記第2ノードに流れる逆電流を検出する、逆電流検出回路とを備え、

前記ドライバ部は、前記逆電流が検出された場合に、前記第1スイッチング素子をオフ状態になるように制御し、

前記セレクタは、前記逆電流が検出されない場合に、前記パルス信号を選択し、前記逆電流が検出された場合に、前記最低パルス信号と前記パルス信号とのうちのパルス幅が大きい信号を選択する

昇圧DC−DCコンバータ。

【請求項5】

請求項4に記載された昇圧DC−DCコンバータであって、

前記パルス信号生成回路は、

基準電圧を生成する基準電圧回路と、

前記出力電圧に対応する電圧を前記基準電圧と比較し、前記基準電圧と前記出力電圧との差を示すエラー信号を生成する、誤差アンプと、

前記エラー信号に基づいて、前記第1スイッチング素子のオン期間を決定し、前記パルス信号を生成する

昇圧DC−DCコンバータ。

【請求項6】

請求項4又は5に記載された昇圧DC−DCコンバータであって、

前記逆電流検出回路は、前記第2ノードの電圧と出力端の電圧とを比較し、比較結果を示す比較結果信号を生成する、コンパレータを備えている

昇圧DC−DCコンバータ。

【請求項7】

降圧DC−DCコンバータと、

昇圧DC−DCコンバータと、

を具備し、

前記降圧DC−DCコンバータは、

電源と第1ノードとを接続するように設けられた、降圧第1スイッチング素子と、

前記第1ノードと接地との間を接続するように設けられた、降圧第2スイッチング素子と、

前記第1ノードと出力端との間に設けられた、インダクタンス素子と、

前記出力端と接地との間に設けられた、コンデンサと、

前記出力端の出力電圧を制御する、降圧制御回路と、

を備え、

前記降圧制御回路は、

前記出力端から負荷に流れる負荷電流が小さいほど、前記降圧第1スイッチング素子のオン期間が小さくなるように、前記降圧第1スイッチング素子のオン期間を決定し、前記決定したオン期間に対応する降圧パルス幅を有する降圧パルス信号を生成する、降圧パルス信号生成回路と、

予め定められた最低パルス幅を有するパルス信号を降圧最低パルス信号として生成する、降圧最低パルス幅制限回路と、

前記降圧パルス信号と前記降圧最低パルス信号とのうちのいずれかを降圧選択パルス信号として選択する、降圧セレクタと、

前記降圧選択パルス信号に基づいて、前記降圧第1スイッチング素子及び前記降圧第2スイッチング素子を、一方のスイッチング素子がオン状態になっているときに他方のスイッチング素子がオフ状態になるように、切り換える、降圧ドライバ部と、

前記出力端から前記第1ノードに流れる逆電流を検出する、降圧逆電流検出回路とを備え、

前記降圧ドライバ部は、前記逆電流が検出された場合に、前記降圧第2スイッチング素子をオフ状態になるように制御し、

前記降圧セレクタは、前記逆電流が検出されない場合に、前記降圧パルス信号を選択し、前記逆電流が検出された場合に、前記降圧最低パルス信号と前記降圧パルス信号とのうちのパルス幅が短い信号を選択し、

前記昇圧DC−DCコンバータは、

電源と第2ノードとの間に設けられ、前記降圧DC−DCコンバータと共通に用いられる前記インダクタンス素子と、

前記第2ノードと出力端との間に設けられた、昇圧第1スイッチング素子と、

前記第2ノードと接地との間を接続するように設けられた、昇圧第2スイッチング素子と、

前記出力端と接地との間に設けられ、前記降圧DC−DCコンバータと共通に用いられるコンデンサと、

前記出力端の出力電圧を制御する、昇圧制御回路と、

を具備し、

前記昇圧制御回路は、

前記出力端から負荷に流れる負荷電流が小さいほど、前記昇圧第2スイッチング素子のオン期間が小さくなるように、前記昇圧第1スイッチング素子のオン期間を決定し、前記決定したオン期間に対応するパルス幅を有する昇圧パルス信号を生成する、昇圧パルス信号生成回路と、

予め定められた最低パルス幅を有するパルス信号を昇圧最低パルス信号として生成する、昇圧最低パルス幅制限回路と、

前記昇圧パルス信号と前記昇圧最低パルス信号とのうちのいずれかを昇圧選択パルス信号として選択する、昇圧セレクタと、

前記昇圧選択パルス信号に基づいて、前記昇圧第1スイッチング素子及び前記昇圧第2スイッチング素子を、一方のスイッチング素子がオン状態になっているときに他方のスイッチング素子がオフ状態になるように、切り換える、昇圧ドライバ部と、

前記出力端から前記第2ノードに流れる逆電流を検出する、昇圧逆電流検出回路とを備え、

前記昇圧ドライバ部は、前記逆電流が検出された場合に、前記昇圧第1スイッチング素子をオフ状態になるように制御し、

前記昇圧セレクタは、前記逆電流が検出されない場合に、前記昇圧パルス信号を選択し、前記逆電流が検出された場合に、前記昇圧最低パルス信号と前記パルス信号とのうちのパルス幅が大きい信号を選択する

昇降圧DC−DCコンバータ。

【請求項1】

電源と第1ノードとを接続するように設けられた、第1スイッチング素子と、

前記第1ノードと接地との間を接続するように設けられた、第2スイッチング素子と、

前記第1ノードと出力端との間に設けられた、インダクタンス素子と、

前記出力端と接地との間に設けられた、コンデンサと、

前記出力端の出力電圧を制御する、制御回路と、

を具備し、

前記制御回路は、

前記出力端から負荷に流れる負荷電流が小さいほど、前記第1スイッチング素子のオン期間が小さくなるように、前記第1スイッチング素子のオン期間を決定し、前記決定したオン期間に対応するパルス幅を有するパルス信号を生成する、パルス信号生成回路と、

予め定められた最低パルス幅を有するパルス信号を最低パルス信号として生成する、最低パルス幅制限回路と、

前記パルス信号と前記最低パルス信号とのうちのいずれかを選択パルス信号として選択する、セレクタと、

前記選択パルス信号に基づいて、前記第1スイッチング素子及び前記第2スイッチング素子を、一方のスイッチング素子がオン状態になっているときに他方のスイッチング素子がオフ状態になるように、切り換える、ドライバ部と、

前記出力端から前記第1ノードに流れる逆電流を検出する、逆電流検出回路とを備え、

前記ドライバ部は、前記逆電流が検出された場合に、前記第2スイッチング素子をオフ状態になるように制御し、

前記セレクタは、前記逆電流が検出されない場合に、前記パルス信号を選択し、前記逆電流が検出された場合に、前記最低パルス信号と前記パルス信号とのうちのパルス幅が大きい信号を選択する

降圧DC−DCコンバータ。

【請求項2】

請求項1に記載された降圧DC−DCコンバータであって、

前記パルス信号生成回路は、

基準電圧を生成する基準電圧回路と、

前記出力電圧に対応する電圧を前記基準電圧と比較し、前記基準電圧と前記出力電圧との差を示すエラー信号を生成する、誤差アンプと、

前記エラー信号に基づいて、前記第1スイッチング素子のオン期間を決定し、前記パルス信号を生成する

降圧DC−DCコンバータ。

【請求項3】

請求項1又は2に記載された降圧DC−DCコンバータであって、

前記逆電流検出回路は、前記第1ノードの電圧と接地電圧とを比較し、比較結果を示す比較結果信号を生成する、コンパレータを備えている

降圧DC−DCコンバータ。

【請求項4】

電源と第2ノードとの間に設けられた、インダクタンス素子と、

前記第2ノードと出力端との間に設けられた、第1スイッチング素子と、

前記第2ノードと接地との間を接続するように設けられた、第2スイッチング素子と、

前記出力端と接地との間に設けられた、コンデンサと、

前記出力端の出力電圧を制御する、制御回路と、

を具備し、

前記制御回路は、

前記出力端から負荷に流れる負荷電流が小さいほど、前記第2スイッチング素子のオン期間が小さくなるように、前記第2スイッチング素子のオン期間を決定し、前記決定したオン期間に対応するパルス幅を有するパルス信号を生成する、パルス信号生成回路と、

予め定められた最低パルス幅を有するパルス信号を最低パルス信号として生成する、最低パルス幅制限回路と、

前記パルス信号と前記最低パルス信号とのうちのいずれかを選択パルス信号として選択する、セレクタと、

前記選択パルス信号に基づいて、前記第1スイッチング素子及び前記第2スイッチング素子を、一方のスイッチング素子がオン状態になっているときに他方のスイッチング素子がオフ状態になるように、切り換える、ドライバ部と、

前記出力端から前記第2ノードに流れる逆電流を検出する、逆電流検出回路とを備え、

前記ドライバ部は、前記逆電流が検出された場合に、前記第1スイッチング素子をオフ状態になるように制御し、

前記セレクタは、前記逆電流が検出されない場合に、前記パルス信号を選択し、前記逆電流が検出された場合に、前記最低パルス信号と前記パルス信号とのうちのパルス幅が大きい信号を選択する

昇圧DC−DCコンバータ。

【請求項5】

請求項4に記載された昇圧DC−DCコンバータであって、

前記パルス信号生成回路は、

基準電圧を生成する基準電圧回路と、

前記出力電圧に対応する電圧を前記基準電圧と比較し、前記基準電圧と前記出力電圧との差を示すエラー信号を生成する、誤差アンプと、

前記エラー信号に基づいて、前記第1スイッチング素子のオン期間を決定し、前記パルス信号を生成する

昇圧DC−DCコンバータ。

【請求項6】

請求項4又は5に記載された昇圧DC−DCコンバータであって、

前記逆電流検出回路は、前記第2ノードの電圧と出力端の電圧とを比較し、比較結果を示す比較結果信号を生成する、コンパレータを備えている

昇圧DC−DCコンバータ。

【請求項7】

降圧DC−DCコンバータと、

昇圧DC−DCコンバータと、

を具備し、

前記降圧DC−DCコンバータは、

電源と第1ノードとを接続するように設けられた、降圧第1スイッチング素子と、

前記第1ノードと接地との間を接続するように設けられた、降圧第2スイッチング素子と、

前記第1ノードと出力端との間に設けられた、インダクタンス素子と、

前記出力端と接地との間に設けられた、コンデンサと、

前記出力端の出力電圧を制御する、降圧制御回路と、

を備え、

前記降圧制御回路は、

前記出力端から負荷に流れる負荷電流が小さいほど、前記降圧第1スイッチング素子のオン期間が小さくなるように、前記降圧第1スイッチング素子のオン期間を決定し、前記決定したオン期間に対応する降圧パルス幅を有する降圧パルス信号を生成する、降圧パルス信号生成回路と、

予め定められた最低パルス幅を有するパルス信号を降圧最低パルス信号として生成する、降圧最低パルス幅制限回路と、

前記降圧パルス信号と前記降圧最低パルス信号とのうちのいずれかを降圧選択パルス信号として選択する、降圧セレクタと、

前記降圧選択パルス信号に基づいて、前記降圧第1スイッチング素子及び前記降圧第2スイッチング素子を、一方のスイッチング素子がオン状態になっているときに他方のスイッチング素子がオフ状態になるように、切り換える、降圧ドライバ部と、

前記出力端から前記第1ノードに流れる逆電流を検出する、降圧逆電流検出回路とを備え、

前記降圧ドライバ部は、前記逆電流が検出された場合に、前記降圧第2スイッチング素子をオフ状態になるように制御し、

前記降圧セレクタは、前記逆電流が検出されない場合に、前記降圧パルス信号を選択し、前記逆電流が検出された場合に、前記降圧最低パルス信号と前記降圧パルス信号とのうちのパルス幅が短い信号を選択し、

前記昇圧DC−DCコンバータは、

電源と第2ノードとの間に設けられ、前記降圧DC−DCコンバータと共通に用いられる前記インダクタンス素子と、

前記第2ノードと出力端との間に設けられた、昇圧第1スイッチング素子と、

前記第2ノードと接地との間を接続するように設けられた、昇圧第2スイッチング素子と、

前記出力端と接地との間に設けられ、前記降圧DC−DCコンバータと共通に用いられるコンデンサと、

前記出力端の出力電圧を制御する、昇圧制御回路と、

を具備し、

前記昇圧制御回路は、

前記出力端から負荷に流れる負荷電流が小さいほど、前記昇圧第2スイッチング素子のオン期間が小さくなるように、前記昇圧第1スイッチング素子のオン期間を決定し、前記決定したオン期間に対応するパルス幅を有する昇圧パルス信号を生成する、昇圧パルス信号生成回路と、

予め定められた最低パルス幅を有するパルス信号を昇圧最低パルス信号として生成する、昇圧最低パルス幅制限回路と、

前記昇圧パルス信号と前記昇圧最低パルス信号とのうちのいずれかを昇圧選択パルス信号として選択する、昇圧セレクタと、

前記昇圧選択パルス信号に基づいて、前記昇圧第1スイッチング素子及び前記昇圧第2スイッチング素子を、一方のスイッチング素子がオン状態になっているときに他方のスイッチング素子がオフ状態になるように、切り換える、昇圧ドライバ部と、

前記出力端から前記第2ノードに流れる逆電流を検出する、昇圧逆電流検出回路とを備え、

前記昇圧ドライバ部は、前記逆電流が検出された場合に、前記昇圧第1スイッチング素子をオフ状態になるように制御し、

前記昇圧セレクタは、前記逆電流が検出されない場合に、前記昇圧パルス信号を選択し、前記逆電流が検出された場合に、前記昇圧最低パルス信号と前記パルス信号とのうちのパルス幅が大きい信号を選択する

昇降圧DC−DCコンバータ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−110795(P2013−110795A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−251953(P2011−251953)

【出願日】平成23年11月17日(2011.11.17)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月17日(2011.11.17)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]