DC/DCコンバータとその出力制御方法

【課題】カレントモード制御方式であっても負荷変動の影響を受けにくく、総合ゲインが常に一定の周波数特性が得られるようにする。

【解決手段】 負荷(10)のモニタ電圧値について基準電圧値との電圧差分値を演算し(101)、この電圧差分値に電圧フィードバックの比例定数を乗算し(102)、モニタ電流値に積分定数を乗算し(104)、この積分定数が乗算されたモニタ電流値と電圧差分値とを乗算し(105)、この乗算結果に1つ前の値を加算し(106,107)、この加算結果に電圧フィードバックの比例定数が乗算された電圧差分値を加算して基準電流値を取得し(103)、モニタ電流値について基準電流値との電流差分値を演算し(108)、電流差分値に電流フィードバックの比例定数を乗算して(109)DC−DCコンバータの出力制御値を得る。

【解決手段】 負荷(10)のモニタ電圧値について基準電圧値との電圧差分値を演算し(101)、この電圧差分値に電圧フィードバックの比例定数を乗算し(102)、モニタ電流値に積分定数を乗算し(104)、この積分定数が乗算されたモニタ電流値と電圧差分値とを乗算し(105)、この乗算結果に1つ前の値を加算し(106,107)、この加算結果に電圧フィードバックの比例定数が乗算された電圧差分値を加算して基準電流値を取得し(103)、モニタ電流値について基準電流値との電流差分値を演算し(108)、電流差分値に電流フィードバックの比例定数を乗算して(109)DC−DCコンバータの出力制御値を得る。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、無負荷の大きな装置に用いられるカレントモード制御方式のDC/DCコンバータとその出力制御方法に関する。

【背景技術】

【0002】

例えば固体化レーダー送信装置用電源、CPU用電源のような、無負荷の大きな装置にあっては、安定したマルチフェーズで処理可能なカレントモード制御方式のDC/DCコンバータがよく用いられる。このカレントモード制御方式は、インダクタ電流をマイナーループとしており、伝達関数が1次遅れであるため、高速化が容易であり、入力電圧の影響を受けない優れた制御方式である。

【0003】

例えば、非特許文献1の記載によれば、カレントモード制御方式におけるコンバータの伝達関数Gc(s)は(1)式で表される。

【数1】

【0004】

ここで、Roは負荷抵抗、Riは電流センス抵抗で、Ro/RiがDCゲインとなる。ωzはゼロ角周波数、ωpは極角周波数である。

【数2】

【0005】

ここで、Coは出力コンデンサ容量、ESRは出力コンデンサの等価直列抵抗、Roは負荷抵抗である。

【0006】

しかしながら、上記カレントモード制御方式では、ゲインが負荷抵抗に依存し、極角周波数が負荷抵抗と出力コンデンサによって決まるため、負荷変動の影響を大きく受けてしまうという問題がある。

【先行技術文献】

【非特許文献】

【0007】

【非特許文献1】An Accurate Control Loop Model for Current-Mode Step-down Controllers-Maxim, APPLICATION NOTE 3440 "An Accurate Control Loop Model for Current-mode Step-Down Controllers", http://www.maxim-ic.com/app-index.mvp/id/3440

【発明の概要】

【発明が解決しようとする課題】

【0008】

以上述べたように、カレントモード制御方式のDC/DCコンバータでは、ゲインが負荷抵抗に依存し、極角周波数が負荷抵抗と出力コンデンサによって決まるため、負荷変動の影響を大きく受けてしまうという問題がある。

【0009】

本実施形態は上記の課題に鑑みてなされたもので、カレントモード制御方式であっても負荷変動の影響を受けにくく、総合ゲインが常に一定の周波数特性が得られるDC−DCコンバータ及びその出力制御方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本実施形態によれば、スイッチング手段により直流電圧を断続出力し、この断続出力を整流平滑手段により整流平滑して負荷に出力するDC−DCコンバータにおいて、電流検出手段により前記負荷への出力電流を検出してモニタ電流値を取得すると共に、電圧検出手段により前記負荷への出力電圧を検出してモニタ電圧値を取得し、前記モニタ電流値及びモニタ電圧値それぞれに基づいて出力制御値を演算し、この演算結果に基づいて前記スイッチング手段をスイッチング駆動する構成であって、前記出力制御値の演算は、第1の演算手段により前記モニタ電圧値について基準電圧値との電圧差分値を演算し、第1の乗算手段により前記電圧差分値に電圧フィードバックの比例定数を乗算し、第2の乗算手段により前記モニタ電流値に積分定数を乗算し、第3の乗算手段により前記第2の乗算手段の乗算結果と前記電圧差分値とを乗算し、遅延加算手段により前記第3の乗算手段の乗算結果に1つ前の値を加算し、加算手段により前記遅延加算手段の加算結果に前記第1の乗算手段の乗算結果を加算して基準電流値を取得し、第2の演算手段により前記モニタ電流値について前記基準電流値との電流差分値を演算し、第4の乗算手段により前記電流差分値に電流フィードバックの比例定数を乗算して前記出力制御値を取得することを特徴とするものである。

【図面の簡単な説明】

【0011】

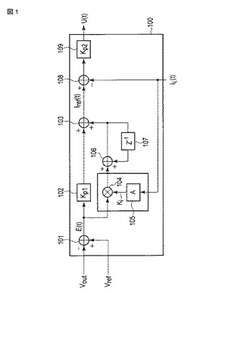

【図1】本実施形態に係るDC/DCコンバータのカレントモード制御回路の構成を示す回路図。

【図2】図1に示す制御回路を降圧型DC/DCコンバータに組み込んだ構成を示すブロック回路図。

【図3】図2に示す回路のコンバータゲイン、制御ゲイン及び総合ゲインを示すボード線図。

【発明を実施するための形態】

【0012】

以下、図面を参照して本実施形態に係る目標追跡システムを説明する。

【0013】

図1は本実施形態に係るDC/DCコンバータのカレントモード制御回路の構成を示す回路図、図2は図1に示す制御回路を組み込んだ降圧型DC/DCコンバータの構成を示すブロック回路図である。

【0014】

まず、図2において、直流電圧源1の電圧出力は、FETまたはトランジスタ等による第1及び第2のスイッチ素子2,3それぞれのオン・オフによって、ダイオード4に逆バイアスとして周期的に与えられる。このダイオード4に断続的に発生する電圧はインダクタ5及びキャパシタ7による平滑回路によって平滑され、直流電圧V0となって負荷回路10に出力される。

【0015】

ここで、上記インダクタ5の出力ラインには、負荷電流(インダクタ電流)IL を検出するための電流センサ6が設けられ、キャパシタ7の出力端には抵抗8,9による電圧モニタ回路が接続されている。電流センサ6で得られたモニタ電流IL 及び電圧モニタ回路で得られたモニタ電圧VMはそれぞれA/D(アナログ/デジタル)コンバータ11,12でデジタル変換された後、本実施形態の制御回路100に送られる。

【0016】

この制御回路100は、上記電流モニタ結果IL(t)及び電圧モニタ結果VM(t)から、安定化出力を得るための最適なPWM(Pulse-width modulation:パルス幅変調)制御信号U(t)を生成する。このPWM制御信号U(t)はPWM回路13に送られる。このPWM回路13は、上記スイッチ素子2,3を駆動する駆動回路14,15にPWM制御信号に基づくオン・オフ指令信号を与えるもので、駆動回路14,15はそれぞれオン・オフ指令の発生タイミングでスイッチ素子2,3のオン期間、オフ期間を決定し駆動する。

【0017】

上記制御回路100では、図1に示すように、電圧モニタ回路からのモニタ電圧VMは、同時に入力される基準電圧Vrefと共に減算器101に送られ、これによって両者の差分値が演算される。この差分値演算結果E(t) は乗算器102において電圧フィードバックの比例定数KP1が乗算されて加算器103に送られる。また、上記差分値演算結果E(t) は乗算器104に送られる。

【0018】

一方、上記電流センサ6からのモニタ電流IL(t)は、乗算器105にて積分定数Aが乗算され、その乗算結果Kiは電圧フィードバック値として乗算器104に送られて差分値演算結果E(t)と乗算される。この乗算結果は加算器106に送られ、Z-1遅延器107のZ変換によって得られるZ-1すなわち、加算器106の1つ前のデータが加算されて加算器103に送られ、上記乗算器102の出力に加算される。加算器103の加算結果は基準電流Iref(t)として減算器108に送られ、モニタ電流IL(t)との差分値が演算される。この差分値演算結果は乗算器109において電流フィードバックの比例定数KP2が乗算される。この乗算結果は上記PWM制御信号U(t) としてPWM回路13に送られる。

【0019】

尚、上記構成においては、電圧フィードバックループがPI(比例・積分)制御、電流フィードバックループがP(比例)制御のカレントモード制御方式を採用しているが、電圧フィードバックループがP制御やPID(比例・積分・微分)制御でもかまわない。また、電流フィードバックループがPI制御やPID制御でもかまわない。

【0020】

また、PWM回路13は、メインの回路方式によっては周波数変調回路(PFM)や位相変調回路等も利用可能である。また、演算結果のオーバーフローを防止するためのリミッタ回路を設けてもよい。

【0021】

上記構成による制御回路100について、さらに具体的な処理動作を説明する。

【0022】

まず、図1に示す回路において、PWM制御信号U(t)について式をたてる。

【数3】

【0023】

【数4】

【0024】

ここで、fsをサンプリング周波数、カットオフ周波数をfcとすると、KIは

【数5】

【0025】

が成立する。そこで、fcを(3)式と一致させれば、コンバータと制御回路の総合伝達関数は負荷に依存しなくなる。負荷抵抗Roは直接測定できないため、出力電圧と出力電流をモニタし、計算すれば求められるが、余分な回路が増えてしまう。インダクタンス電流は出力電流に比例しているため、カレントモードで検出する値に定数aを掛けることにより出力電流が得られる。

【数6】

【0026】

(7)式のTsはサンプリング周期である。また、出力電圧は通常定電圧であるため、定数として使用すると、計算がより簡素化され高速な演算が可能となる。積分定数部分をAとすると、

【数7】

【0027】

が得られ、図1で示したブロック図のKIの部分が得られる。

【0028】

(5)式、(8)式より、

【数8】

【0029】

となり、積和演算のみで出力U(t)が得られるため、DSP(デジタル・シグナル・プロセッサ)等の高速の演算器が使用できる。

【0030】

図3はコンバータゲイン、制御ゲイン、および総合ゲインの周波数特性を示すボード線図である。図では軽い負荷時と重い負荷時のコンバータゲイン、制御ゲイン、および総合ゲインを表している。図に示されるように、コンバータゲインは負荷が変動すると、ゲインが変わるが、それに応じて制御ゲインを変えることにより、総合ゲインは常に一定であることを表している。

【0031】

以上より、インダクタンス電流にて定数Aを掛けそれを積分定数とすることにより、カレントモード制御方式の欠点であった負荷変動の影響を無くすことができ、しかも高速に処理することが可能であるため、応答性の改善が図れる。

【0032】

尚、上記実施形態はそのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合わせでもよい。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。さらに、異なる実施形態にわたる構成要素を適宜組み合わせてもよい。

【符号の説明】

【0033】

1…直流電圧源、2,3…スイッチ素子、4…ダイオード、5…インダクタ、6…電流センサ、7…キャパシタ、8,9…抵抗、10…負荷回路、11,12…A/Dコンバータ、13…PWM回路、14,15…駆動回路、100…制御回路、101…減算器、102…乗算器、103…加算器、104…乗算器、105…乗算器、106…加算器、107…Z-1遅延器、108…減算器、109…乗算器。

【技術分野】

【0001】

本発明は、無負荷の大きな装置に用いられるカレントモード制御方式のDC/DCコンバータとその出力制御方法に関する。

【背景技術】

【0002】

例えば固体化レーダー送信装置用電源、CPU用電源のような、無負荷の大きな装置にあっては、安定したマルチフェーズで処理可能なカレントモード制御方式のDC/DCコンバータがよく用いられる。このカレントモード制御方式は、インダクタ電流をマイナーループとしており、伝達関数が1次遅れであるため、高速化が容易であり、入力電圧の影響を受けない優れた制御方式である。

【0003】

例えば、非特許文献1の記載によれば、カレントモード制御方式におけるコンバータの伝達関数Gc(s)は(1)式で表される。

【数1】

【0004】

ここで、Roは負荷抵抗、Riは電流センス抵抗で、Ro/RiがDCゲインとなる。ωzはゼロ角周波数、ωpは極角周波数である。

【数2】

【0005】

ここで、Coは出力コンデンサ容量、ESRは出力コンデンサの等価直列抵抗、Roは負荷抵抗である。

【0006】

しかしながら、上記カレントモード制御方式では、ゲインが負荷抵抗に依存し、極角周波数が負荷抵抗と出力コンデンサによって決まるため、負荷変動の影響を大きく受けてしまうという問題がある。

【先行技術文献】

【非特許文献】

【0007】

【非特許文献1】An Accurate Control Loop Model for Current-Mode Step-down Controllers-Maxim, APPLICATION NOTE 3440 "An Accurate Control Loop Model for Current-mode Step-Down Controllers", http://www.maxim-ic.com/app-index.mvp/id/3440

【発明の概要】

【発明が解決しようとする課題】

【0008】

以上述べたように、カレントモード制御方式のDC/DCコンバータでは、ゲインが負荷抵抗に依存し、極角周波数が負荷抵抗と出力コンデンサによって決まるため、負荷変動の影響を大きく受けてしまうという問題がある。

【0009】

本実施形態は上記の課題に鑑みてなされたもので、カレントモード制御方式であっても負荷変動の影響を受けにくく、総合ゲインが常に一定の周波数特性が得られるDC−DCコンバータ及びその出力制御方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本実施形態によれば、スイッチング手段により直流電圧を断続出力し、この断続出力を整流平滑手段により整流平滑して負荷に出力するDC−DCコンバータにおいて、電流検出手段により前記負荷への出力電流を検出してモニタ電流値を取得すると共に、電圧検出手段により前記負荷への出力電圧を検出してモニタ電圧値を取得し、前記モニタ電流値及びモニタ電圧値それぞれに基づいて出力制御値を演算し、この演算結果に基づいて前記スイッチング手段をスイッチング駆動する構成であって、前記出力制御値の演算は、第1の演算手段により前記モニタ電圧値について基準電圧値との電圧差分値を演算し、第1の乗算手段により前記電圧差分値に電圧フィードバックの比例定数を乗算し、第2の乗算手段により前記モニタ電流値に積分定数を乗算し、第3の乗算手段により前記第2の乗算手段の乗算結果と前記電圧差分値とを乗算し、遅延加算手段により前記第3の乗算手段の乗算結果に1つ前の値を加算し、加算手段により前記遅延加算手段の加算結果に前記第1の乗算手段の乗算結果を加算して基準電流値を取得し、第2の演算手段により前記モニタ電流値について前記基準電流値との電流差分値を演算し、第4の乗算手段により前記電流差分値に電流フィードバックの比例定数を乗算して前記出力制御値を取得することを特徴とするものである。

【図面の簡単な説明】

【0011】

【図1】本実施形態に係るDC/DCコンバータのカレントモード制御回路の構成を示す回路図。

【図2】図1に示す制御回路を降圧型DC/DCコンバータに組み込んだ構成を示すブロック回路図。

【図3】図2に示す回路のコンバータゲイン、制御ゲイン及び総合ゲインを示すボード線図。

【発明を実施するための形態】

【0012】

以下、図面を参照して本実施形態に係る目標追跡システムを説明する。

【0013】

図1は本実施形態に係るDC/DCコンバータのカレントモード制御回路の構成を示す回路図、図2は図1に示す制御回路を組み込んだ降圧型DC/DCコンバータの構成を示すブロック回路図である。

【0014】

まず、図2において、直流電圧源1の電圧出力は、FETまたはトランジスタ等による第1及び第2のスイッチ素子2,3それぞれのオン・オフによって、ダイオード4に逆バイアスとして周期的に与えられる。このダイオード4に断続的に発生する電圧はインダクタ5及びキャパシタ7による平滑回路によって平滑され、直流電圧V0となって負荷回路10に出力される。

【0015】

ここで、上記インダクタ5の出力ラインには、負荷電流(インダクタ電流)IL を検出するための電流センサ6が設けられ、キャパシタ7の出力端には抵抗8,9による電圧モニタ回路が接続されている。電流センサ6で得られたモニタ電流IL 及び電圧モニタ回路で得られたモニタ電圧VMはそれぞれA/D(アナログ/デジタル)コンバータ11,12でデジタル変換された後、本実施形態の制御回路100に送られる。

【0016】

この制御回路100は、上記電流モニタ結果IL(t)及び電圧モニタ結果VM(t)から、安定化出力を得るための最適なPWM(Pulse-width modulation:パルス幅変調)制御信号U(t)を生成する。このPWM制御信号U(t)はPWM回路13に送られる。このPWM回路13は、上記スイッチ素子2,3を駆動する駆動回路14,15にPWM制御信号に基づくオン・オフ指令信号を与えるもので、駆動回路14,15はそれぞれオン・オフ指令の発生タイミングでスイッチ素子2,3のオン期間、オフ期間を決定し駆動する。

【0017】

上記制御回路100では、図1に示すように、電圧モニタ回路からのモニタ電圧VMは、同時に入力される基準電圧Vrefと共に減算器101に送られ、これによって両者の差分値が演算される。この差分値演算結果E(t) は乗算器102において電圧フィードバックの比例定数KP1が乗算されて加算器103に送られる。また、上記差分値演算結果E(t) は乗算器104に送られる。

【0018】

一方、上記電流センサ6からのモニタ電流IL(t)は、乗算器105にて積分定数Aが乗算され、その乗算結果Kiは電圧フィードバック値として乗算器104に送られて差分値演算結果E(t)と乗算される。この乗算結果は加算器106に送られ、Z-1遅延器107のZ変換によって得られるZ-1すなわち、加算器106の1つ前のデータが加算されて加算器103に送られ、上記乗算器102の出力に加算される。加算器103の加算結果は基準電流Iref(t)として減算器108に送られ、モニタ電流IL(t)との差分値が演算される。この差分値演算結果は乗算器109において電流フィードバックの比例定数KP2が乗算される。この乗算結果は上記PWM制御信号U(t) としてPWM回路13に送られる。

【0019】

尚、上記構成においては、電圧フィードバックループがPI(比例・積分)制御、電流フィードバックループがP(比例)制御のカレントモード制御方式を採用しているが、電圧フィードバックループがP制御やPID(比例・積分・微分)制御でもかまわない。また、電流フィードバックループがPI制御やPID制御でもかまわない。

【0020】

また、PWM回路13は、メインの回路方式によっては周波数変調回路(PFM)や位相変調回路等も利用可能である。また、演算結果のオーバーフローを防止するためのリミッタ回路を設けてもよい。

【0021】

上記構成による制御回路100について、さらに具体的な処理動作を説明する。

【0022】

まず、図1に示す回路において、PWM制御信号U(t)について式をたてる。

【数3】

【0023】

【数4】

【0024】

ここで、fsをサンプリング周波数、カットオフ周波数をfcとすると、KIは

【数5】

【0025】

が成立する。そこで、fcを(3)式と一致させれば、コンバータと制御回路の総合伝達関数は負荷に依存しなくなる。負荷抵抗Roは直接測定できないため、出力電圧と出力電流をモニタし、計算すれば求められるが、余分な回路が増えてしまう。インダクタンス電流は出力電流に比例しているため、カレントモードで検出する値に定数aを掛けることにより出力電流が得られる。

【数6】

【0026】

(7)式のTsはサンプリング周期である。また、出力電圧は通常定電圧であるため、定数として使用すると、計算がより簡素化され高速な演算が可能となる。積分定数部分をAとすると、

【数7】

【0027】

が得られ、図1で示したブロック図のKIの部分が得られる。

【0028】

(5)式、(8)式より、

【数8】

【0029】

となり、積和演算のみで出力U(t)が得られるため、DSP(デジタル・シグナル・プロセッサ)等の高速の演算器が使用できる。

【0030】

図3はコンバータゲイン、制御ゲイン、および総合ゲインの周波数特性を示すボード線図である。図では軽い負荷時と重い負荷時のコンバータゲイン、制御ゲイン、および総合ゲインを表している。図に示されるように、コンバータゲインは負荷が変動すると、ゲインが変わるが、それに応じて制御ゲインを変えることにより、総合ゲインは常に一定であることを表している。

【0031】

以上より、インダクタンス電流にて定数Aを掛けそれを積分定数とすることにより、カレントモード制御方式の欠点であった負荷変動の影響を無くすことができ、しかも高速に処理することが可能であるため、応答性の改善が図れる。

【0032】

尚、上記実施形態はそのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合わせでもよい。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。さらに、異なる実施形態にわたる構成要素を適宜組み合わせてもよい。

【符号の説明】

【0033】

1…直流電圧源、2,3…スイッチ素子、4…ダイオード、5…インダクタ、6…電流センサ、7…キャパシタ、8,9…抵抗、10…負荷回路、11,12…A/Dコンバータ、13…PWM回路、14,15…駆動回路、100…制御回路、101…減算器、102…乗算器、103…加算器、104…乗算器、105…乗算器、106…加算器、107…Z-1遅延器、108…減算器、109…乗算器。

【特許請求の範囲】

【請求項1】

直流電圧を断続出力するスイッチング手段と、

前記スイッチング手段の断続出力を整流平滑して負荷に出力する整流平滑手段と、

前記負荷への出力電流を検出してモニタ電流値を得る電流検出手段と、

前記負荷への出力電圧を検出してモニタ電圧値を得る電圧検出手段と、

前記モニタ電流値及びモニタ電圧値それぞれに基づいて出力制御値を演算する制御手段と、

前記制御手段の演算結果に基づいて前記スイッチング手段をスイッチング駆動する駆動手段と

を具備し、

前記制御手段は、

前記モニタ電圧値について基準電圧値との電圧差分値を演算する第1の演算手段と、

前記電圧差分値に電圧フィードバックの比例定数を乗算する第1の乗算手段と、

前記モニタ電流値に積分定数を乗算する第2の乗算手段と、

前記第2の乗算手段の乗算結果と前記電圧差分値とを乗算する第3の乗算手段と、

前記第3の乗算手段の乗算結果に1つ前の値を加算する遅延加算手段と、

前記遅延加算手段の加算結果に前記第1の乗算手段の乗算結果を加算して基準電流値を得る加算手段と、

前記モニタ電流値について前記基準電流値との電流差分値を演算する第2の演算手段と、

前記電流差分値に電流フィードバックの比例定数を乗算して前記出力制御値を得る第4の乗算手段と

を備えることを特徴とするDC−DCコンバータ。

【請求項2】

スイッチング手段による直流電圧の断続出力を整流平滑して負荷に出力する際に、前記負荷への出力電流及び出力電圧をそれぞれ検出してモニタ電流値及びモニタ電圧値を取得し、記負荷への出力電圧を検出してモニタ電圧値を取得し、前記モニタ電流値及びモニタ電圧値それぞれに基づいて出力制御値を演算し、その演算結果に基づいて前記スイッチング手段をスイッチング駆動するDC−DCコンバータに用いられ、

前記モニタ電圧値について基準電圧値との電圧差分値を演算し、

前記電圧差分値に電圧フィードバックの比例定数を乗算し、

前記モニタ電流値に積分定数を乗算し、

この積分定数が乗算されたモニタ電流値と前記電圧差分値とを乗算し、

この乗算結果に1つ前の値を加算し、

この加算結果に前記電圧フィードバックの比例定数が乗算された電圧差分値を加算して基準電流値を取得し、

前記モニタ電流値について前記基準電流値との電流差分値を演算し、

前記電流差分値に電流フィードバックの比例定数を乗算して前記出力制御値を得ることを特徴とするDC−DCコンバータの出力制御方法。

【請求項1】

直流電圧を断続出力するスイッチング手段と、

前記スイッチング手段の断続出力を整流平滑して負荷に出力する整流平滑手段と、

前記負荷への出力電流を検出してモニタ電流値を得る電流検出手段と、

前記負荷への出力電圧を検出してモニタ電圧値を得る電圧検出手段と、

前記モニタ電流値及びモニタ電圧値それぞれに基づいて出力制御値を演算する制御手段と、

前記制御手段の演算結果に基づいて前記スイッチング手段をスイッチング駆動する駆動手段と

を具備し、

前記制御手段は、

前記モニタ電圧値について基準電圧値との電圧差分値を演算する第1の演算手段と、

前記電圧差分値に電圧フィードバックの比例定数を乗算する第1の乗算手段と、

前記モニタ電流値に積分定数を乗算する第2の乗算手段と、

前記第2の乗算手段の乗算結果と前記電圧差分値とを乗算する第3の乗算手段と、

前記第3の乗算手段の乗算結果に1つ前の値を加算する遅延加算手段と、

前記遅延加算手段の加算結果に前記第1の乗算手段の乗算結果を加算して基準電流値を得る加算手段と、

前記モニタ電流値について前記基準電流値との電流差分値を演算する第2の演算手段と、

前記電流差分値に電流フィードバックの比例定数を乗算して前記出力制御値を得る第4の乗算手段と

を備えることを特徴とするDC−DCコンバータ。

【請求項2】

スイッチング手段による直流電圧の断続出力を整流平滑して負荷に出力する際に、前記負荷への出力電流及び出力電圧をそれぞれ検出してモニタ電流値及びモニタ電圧値を取得し、記負荷への出力電圧を検出してモニタ電圧値を取得し、前記モニタ電流値及びモニタ電圧値それぞれに基づいて出力制御値を演算し、その演算結果に基づいて前記スイッチング手段をスイッチング駆動するDC−DCコンバータに用いられ、

前記モニタ電圧値について基準電圧値との電圧差分値を演算し、

前記電圧差分値に電圧フィードバックの比例定数を乗算し、

前記モニタ電流値に積分定数を乗算し、

この積分定数が乗算されたモニタ電流値と前記電圧差分値とを乗算し、

この乗算結果に1つ前の値を加算し、

この加算結果に前記電圧フィードバックの比例定数が乗算された電圧差分値を加算して基準電流値を取得し、

前記モニタ電流値について前記基準電流値との電流差分値を演算し、

前記電流差分値に電流フィードバックの比例定数を乗算して前記出力制御値を得ることを特徴とするDC−DCコンバータの出力制御方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−110935(P2013−110935A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−256363(P2011−256363)

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]