DC/DCコンバータの制御回路、それを用いたDC/DCコンバータ、発光装置および電子機器

【課題】DC/DCコンバータの制御回路の面積を低減する。

【解決手段】充電回路30は、キャパシタC2を充電する。放電回路32は、オン状態においてキャパシタC2を放電する。コンパレータ38は、キャパシタC2の電圧VC2に応じてレベルが変化する解除信号S1を生成する。ロジック部40は、異常検出信号S2がアサートされるとフェイル信号S3をアサートし、その後、解除信号S1が第1レベルに遷移するタイミングにおいて、異常検出信号S2がネゲートされていると、フェイル信号S3をネゲートし、そのタイミングにおいて、異常検出信号S2がアサートされていると、フェイル信号S3をアサートし続ける。またロジック部40は、解除信号S1に応じて放電回路32を制御する。反転アンプ46は、キャパシタC2の電圧VC2を反転することによりソフトスタート電圧Vssを生成する。

【解決手段】充電回路30は、キャパシタC2を充電する。放電回路32は、オン状態においてキャパシタC2を放電する。コンパレータ38は、キャパシタC2の電圧VC2に応じてレベルが変化する解除信号S1を生成する。ロジック部40は、異常検出信号S2がアサートされるとフェイル信号S3をアサートし、その後、解除信号S1が第1レベルに遷移するタイミングにおいて、異常検出信号S2がネゲートされていると、フェイル信号S3をネゲートし、そのタイミングにおいて、異常検出信号S2がアサートされていると、フェイル信号S3をアサートし続ける。またロジック部40は、解除信号S1に応じて放電回路32を制御する。反転アンプ46は、キャパシタC2の電圧VC2を反転することによりソフトスタート電圧Vssを生成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、DC/DCコンバータの制御回路に関する。

【背景技術】

【0002】

電池電圧などの直流電圧を昇圧もしくは降圧するために、DC/DCコンバータが利用される。DC/DCコンバータの制御回路は、制御回路は、DC/DCコンバータにおいて生ずる異常、たとえば過電圧状態、過電流状態、温度異常状態などを検出し、異常状態において回路保護を行う。制御回路は、異常状態を監視するタイマー回路を備えており、所定の判定期間ごとに、異常状態が持続しているか否かを判定する。また制御回路は、その起動時において突入電流を防止するために、時間とともに緩やかに上昇するソフトスタート電圧を生成するソフトスタート回路を備える。制御回路は、DC/DCコンバータの出力電圧を、ソフトスタート電圧に追従させて増大させる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平9−121535号公報

【特許文献2】特開平7−336999号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

異常検出用のタイマー回路およびソフトスタート回路は、それぞれが外付けのキャパシタを必要とするため部品点数が多くなる。また制御回路には、外付けのキャパシタを接続するための2つのピン(パッド)が必要となるため、チップサイズ、パッケージサイズが大きくなってしまう。

【0005】

本発明はこうした課題に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、DC/DCコンバータの制御回路のサイズの低減にある。

【課題を解決するための手段】

【0006】

本発明のある態様は、DC/DCコンバータの制御回路に関する。制御回路は、その第1端子の電位が固定されたキャパシタと、キャパシタを充電する充電回路と、オン、オフが切りかえ可能であり、オン状態においてキャパシタを放電する放電回路と、キャパシタの電圧が所定の上側しきい値電圧に達してから所定の下側しきい値電圧に低下するまでの期間、第1レベルをとり、キャパシタの電圧が、下側しきい値電圧に低下してから、上側しきい値電圧に達するまでの期間、第2レベルをとる解除信号を生成するコンパレータと、解除信号と、異常状態が検出されるとアサートされる異常検出信号と、を受け、異常検出信号がアサートされるとフェイル信号をアサートし、その後、解除信号が第1レベルに遷移するタイミングにおいて、異常検出信号がネゲートされていると、フェイル信号をネゲートし、そのタイミングにおいて、異常検出信号がアサートされていると、フェイル信号をアサートし続け、かつ解除信号が第1レベルのとき放電回路をオンし、解除信号が第2レベルのとき放電回路をオフするロジック部と、キャパシタの電圧を反転することによりソフトスタート電圧を生成する反転アンプと、を備える。

【0007】

この態様によると、異常検出用のタイマー回路において生成されるスロープ電圧を、異常状態からの解放後においてソフトスタート電圧として利用することができる。その結果、タイマー回路とソフトスタート回路を兼用することができ、サイズを低減できる。

【0008】

ロジック部は、そのセット端子に異常検出信号が入力され、そのリセット端子に解除信号が入力されたセット優先のSRフリップフロップを含んでもよい。

【0009】

ロジック部はさらに、SRフリップフロップの反転出力信号と解除信号の論理和を生成し、放電回路を制御するORゲートを含んでもよい。

【0010】

本発明の別の態様は、DC/DCコンバータである。このDC/DCコンバータは、上述の制御回路を備える。

【0011】

本発明のさらに別の態様は、発光装置である。この発光装置は、発光素子と、発光素子に駆動電圧を供給する上述のDC/DCコンバータと、を備える。

【0012】

本発明のさらに別の態様は、電子機器である。この電子機器は、液晶パネルと、液晶パネルのバックライトとして設けられた上述の発光装置と、を備える。

【0013】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0014】

本発明のある態様によれば、回路面積を削減できる。

【図面の簡単な説明】

【0015】

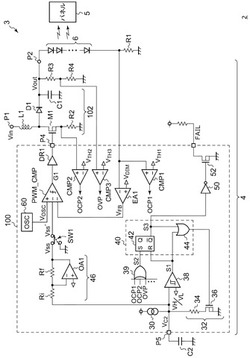

【図1】実施の形態に係る駆動回路を備える電子機器の構成を示す回路図である。

【図2】図1の駆動回路の動作を示すタイムチャートである。

【発明を実施するための形態】

【0016】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0017】

本明細書において、「部材Aが、部材Bと接続された状態」とは、部材Aと部材Bが物理的に直接的に接続される場合のほか、部材Aと部材Bが、電気的な接続状態に影響を及ぼさない他の部材を介して間接的に接続される場合も含む。

同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、電気的な接続状態に影響を及ぼさない他の部材を介して間接的に接続される場合も含む。

【0018】

図1は、実施の形態に係るDC/DCコンバータを備える電子機器2の構成を示す回路図である。

【0019】

電子機器2は、ノートPC、デジタルカメラ、デジタルビデオカメラ、携帯電話端末、PDA(Personal Digital Assistant)などの電池駆動型の機器であり、発光装置3とLCD(Liquid Crystal Display)パネル5を備える。発光装置3はLCDパネル5のバックライトとして設けられる。

【0020】

発光装置3は、発光素子であるLEDストリング6と、その駆動回路4を備える。

【0021】

LEDストリング6は、直列に接続された複数のLEDを含む。駆動回路4は、昇圧型のDC/DCコンバータを含み、入力端子P1に入力された入力電圧(たとえば電池電圧)Vinを昇圧して、出力端子P2から出力電圧(駆動電圧)Voutを出力する。LEDストリング6の一端(アノード)は、出力端子P2に接続される。

【0022】

駆動回路(DC/DCコンバータ)4は、制御IC100および出力回路102を備える。出力回路102は、インダクタL1、整流ダイオードD1、スイッチングトランジスタM1、出力キャパシタC1を含む。出力回路102のトポロジーは一般的であるため、説明を省略する。

【0023】

制御IC100のスイッチング端子P4は、スイッチングトランジスタM1のゲートと接続される。制御IC100は、LEDストリング6の点灯に必要な出力電圧Voutが得られ、かつLEDストリング6に目標輝度に応じた駆動電流が流れるように、フィードバックによりスイッチングトランジスタM1のオン、オフのデューティ比を調節する。なおスイッチングトランジスタM1は制御IC100に内蔵されてもよい。

【0024】

第1検出抵抗R1は、LEDストリング6の経路上、具体的にはLEDストリング6のカソードと接地端子の間に設けられる。誤差増幅器EA1は、第1検出抵抗R1に生ずる電圧降下VR1と制御電圧VDIMの誤差を増幅し、誤差電圧VFBを生成する。オシレータ60は、三角波もしくはノコギリ波の周期電圧VOSCを生成する。PWMコンパレータPMW_CMPは、周期電圧VOSC、後述するソフトスタート電圧Vssおよび誤差電圧VFBを受ける。PWMコンパレータPWM_CMPは、ソフトスタート電圧Vssと誤差電圧VFBのうち、低い方と、周期電圧VOSCを比較する。PWMコンパレータPWM_CMPの出力(ゲートパルス信号G1)のデューティ比は、第1検出抵抗R1の電圧降下VR1が制御電圧VDIMと一致するように調節される。ドライバDR1は、ゲートパルス信号G1にもとづき、DC/DCコンバータのスイッチングトランジスタM1を駆動する。なお、パルス幅変調器に代えて、パルス周波数変調器を用いてもよい。

【0025】

第1コンパレータCMP1は、第1検出抵抗R1の電圧降下VR1が第1しきい値電圧VTH1を超えると、第1過電流検出信号OCP1をアサートする。第2検出抵抗R2は、DC/DCコンバータのスイッチングトランジスタM1の経路上に設けられる。第2コンパレータCMP2は、第2検出抵抗R2の電圧降下VR2が第2しきい値電圧VTH2を超えると第2過電流検出信号OCP2をアサートする。

【0026】

抵抗R3、R4は、駆動電圧Voutを分圧する。過電圧検出用の第3コンパレータCMP3は、抵抗R3、R4により分圧された電圧Vout’を、所定のしきい値電圧VTH3と比較する。第3コンパレータCMP3は、Vout’>VTH3となると、過電圧検出信号OVPをアサートする。

【0027】

ドライバDR1は、検出信号OCP1、OCP2、OVPの少なくともひとつがアサートされると、直ちにゲートパルス信号G1をローレベルに固定し、スイッチングトランジスタM1をオフすることによりDC/DCのスイッチング動作を停止する。

【0028】

キャパシタC2は、キャパシタ端子P5に外付けされる。キャパシタC2の一端(第1端子)は接地されて電位が固定される。充電回路30は、キャパシタC2を充電する。放電回路32は、オン、オフが切りかえ可能であり、オン状態においてキャパシタC2を放電する。放電回路32は、放電経路に直列に設けられた抵抗34およびトランジスタ36を含む。トランジスタ36がオンのとき、放電回路32はオン状態、トランジスタ36がオフのとき、放電回路32はオフ状態となる。

【0029】

コンパレータ38は、いわゆるヒステリシスコンパレータの機能を有し、キャパシタC2の電圧VC2を所定の上側しきい値電圧VHおよび所定の下側しきい値電圧VLと比較し、比較結果に応じた解除信号S1を生成する。解除信号S1は、キャパシタC2の電圧VC2が上側しきい値電圧VHに達してから所定の下側しきい値電圧VLに低下するまでの期間、第1レベル(ハイレベルとする)をとり、キャパシタC2の電圧VC2が、下側しきい値電圧VLに低下してから、上側しきい値電圧VHに達するまでの期間、第2レベル(ローレベル)をとる。

【0030】

解除信号S1は、放電回路32のオン、オフ状態の切りかえに利用されるとともに、解除信号S1のポジティブエッジは、異常状態を再判定するタイミングとして利用される。ロジック部40は、解除信号S1と、異常検出信号S2を受ける。異常検出信号S2は、発光装置3において何らかの異常状態が検出されるとアサートされる信号であり、たとえば、ORゲート39によって、上述した検出信号OCP1、OCP2、OVP等の論理和をとることにより生成される。これらの検出信号に加えて、または代えて、ORゲート39は、外部から供給される電源電圧の低電圧状態を示すUVLO(Under Voltage Lock Out)信号、温度異常を示すTHD(Thermal ShutDown)信号などを受けてもよい。

【0031】

ロジック部40は、異常検出信号S2がアサートされるとフェイル信号S3をアサート(ローレベル)する。その後、解除信号S1が第1レベル(ハイレベル)に遷移するタイミングにおいて、異常検出信号S2がネゲートされていると、ロジック部40はフェイル信号S3をネゲート(ハイレベル)する。解除信号S1がハイレベルに遷移する再判定タイミングにおいて、異常検出信号S2がアサートされていると、ロジック部40はフェイル信号S3をネゲートせずに、アサートし続ける。

【0032】

またロジック部40は、解除信号S1が第1レベル(ハイレベル)のとき放電回路32をオンし、解除信号S1が第2レベル(ローレベル)のとき放電回路32をオフする。

【0033】

ロジック部40は、SRフリップフロップ42、ORゲート44を含む。SRフリップフロップ42のセット端子(S)には、異常検出信号S2が入力され、そのリセット端子(R)には解除信号S1が入力される。SRフリップフロップ42は、セット優先論理で構成されており、セット端子とリセット端子の信号が両方ハイレベルのときには、セット端子が優先される。

【0034】

SRフリップフロップ42の反転出力信号#Q(#は論理反転を示す)は、フェイル信号S3に相当する。ORゲート44は、フェイル信号S3と解除信号S1の論理和を生成し、放電回路32を制御する。

【0035】

反転アンプ46は、抵抗Ri、Rfおよび演算増幅器OA1を含み、キャパシタC2の電圧VC2を反転することによりソフトスタート電圧Vssを生成する。スイッチSW1は、反転アンプ46の出力端子と、PWMコンパレータPWM_CMPの間に設けられる。スイッチSW1はソフトスタート期間以降、オン状態となり、ソフトスタート電圧VssがPWMコンパレータPWM_CMPの反転入力端子に供給される。ソフトスタート期間より前の期間、スイッチSW1はオフ状態となる。スイッチSW1は、オフ状態においてPWMコンパレータPWM_CMPの反転入力端子の電位がフローティングとならないように構成される。スイッチSW1は、たとえばフェイル信号S3がハイレベルの期間、オンしてもよい。

【0036】

出力回路50は、フェイル信号S3を、制御IC100の外部のプロセッサ(不図示)に出力する。出力回路50は、インバータ52およびトランジスタ54を含む。インバータ52は、フェイル信号S3を反転する。トランジスタ54は、オープンドレイン形式の出力回路を構成する。

【0037】

以上が駆動回路4の構成である。続いてその動作を説明する。図2は、図1の駆動回路4の動作を示すタイムチャートである。時刻t0に、異常検出信号S2がアサートされると、SRフリップフロップ42の反転出力#Qがローレベルに遷移し、フェイル信号S3がアサート(ローレベル)される。

【0038】

フェイル信号S3がローレベルとなると、トランジスタ36がオフし、放電回路32がオフ状態となり、充電回路30によってキャパシタC2が充電され、キャパシタ電圧VC2が上昇する。時刻t1にキャパシタ電圧VC2が上側しきい値電圧VHに達すると、解除信号S1がハイレベルに遷移する。

【0039】

時刻t1に解除信号S1がハイレベルに遷移しても、異常検出信号S2がアサートされているため、セット優先論理によってSRフリップフロップ42はリセットされず、フェイル信号S3はローレベルを維持し続ける。解除信号S1がハイレベルに遷移すると、トランジスタ36がオンし、キャパシタC2が放電され、キャパシタ電圧VC2が低下し始める。キャパシタ電圧VC2が下側しきい値電圧VLまで低下すると、解除信号S1がローレベルに遷移し(t2)、再びキャパシタC2が充電される。時刻t3にキャパシタ電圧VC2が上側しきい値電圧VHに達すると、解除信号S1がハイレベルとなる。

【0040】

制御IC100は、同様の処理を繰り返す。時刻t4に異常検出信号S2がネゲートされる。時刻t4に解除信号S1がハイレベルに遷移すると、SRフリップフロップ42がリセットされ、フェイル信号S3がハイレベルに遷移する。フェイル信号S3がハイレベルに遷移すると、スイッチSW1がオンする。

【0041】

スイッチSW1がオンすると、反転アンプ46の出力電圧Vssが、PWMコンパレータPMW_CMPへと供給される。その結果、ゲートパルス信号G1のデューティ比が時間とともに増加し、出力電圧Voutが緩やかに上昇する。

【0042】

以上が駆動回路4の動作である。

制御IC100によれば、単一のキャパシタC2を充放電することにより、周期信号である解除信号S1と、ソフトスタート電圧Vssを生成することができる。これにより、従来2つ必要であったキャパシタがひとつに削減できるため、回路面積を削減することができる。

【0043】

また、キャパシタC2に発生する電圧VC2の下りのスロープを反転してソフトスタート電圧Vssを生成しているため、フェイル信号S3がネゲートされると、直ちにソフトスタート電圧Vssを生成し始めることができる。

【0044】

以上、本発明について、実施の形態をもとに説明した。この実施の形態は例示であり、それらの各構成要素や各処理プロセス、それらの組み合わせには、さまざまな変形例が存在しうる。以下、こうした変形例について説明する。

【0045】

実施の形態では、LEDストリング6の経路上に設けられた第1検出抵抗R1の電圧降下VR1を目標値VDIMと一致させることにより、駆動電流を安定化させる構成を説明したが、本発明はそれに限定されない。たとえばLEDストリング6の経路上に、安定した駆動電流を生成する定電流源(電流ドライバ)を設けてもよい。

【0046】

実施の形態ではインダクタを用いた非絶縁型のスイッチング電源を説明したが、本発明はトランスを用いた絶縁型のスイッチング電源にも適用可能である。

【0047】

実施の形態では、発光装置3のアプリケーションとして電子機器を説明したが、用途は特に限定されず、照明などにも利用できる。

【0048】

また、本実施の形態において、ハイレベル、ローレベルの論理信号の設定は一例であって、インバータなどによって適宜反転させることにより自由に変更することが可能である。

【0049】

実施の形態にもとづき、具体的な語句を用いて本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【符号の説明】

【0050】

2…電子機器、3…発光装置、4…駆動回路、5…LCDパネル、6…LEDストリング、C2…キャパシタ、30…充電回路、32…放電回路、34…抵抗、36…トランジスタ、38…コンパレータ、40…ロジック部、42…SRフリップフロップ、44…ORゲート、46…反転アンプ、50…出力回路、52…インバータ、54…トランジスタ、SW1…スイッチ、100…制御IC、102…出力回路、EA1…誤差増幅器、DR1…第1ドライバ、CMP1…第1コンパレータ、CMP2…第2コンパレータ、CMP3…第3コンパレータ、R1…第1検出抵抗、R2…第2検出抵抗、L1…インダクタ、C1…出力キャパシタ、D1…整流ダイオード、M1…スイッチングトランジスタ、OCP1…第1過電流検出信号、OCP2…第2過電流検出信号、OVP…過電圧検出信号、S1…解除信号、S2…異常検出信号、S3…フェイル信号。

【技術分野】

【0001】

本発明は、DC/DCコンバータの制御回路に関する。

【背景技術】

【0002】

電池電圧などの直流電圧を昇圧もしくは降圧するために、DC/DCコンバータが利用される。DC/DCコンバータの制御回路は、制御回路は、DC/DCコンバータにおいて生ずる異常、たとえば過電圧状態、過電流状態、温度異常状態などを検出し、異常状態において回路保護を行う。制御回路は、異常状態を監視するタイマー回路を備えており、所定の判定期間ごとに、異常状態が持続しているか否かを判定する。また制御回路は、その起動時において突入電流を防止するために、時間とともに緩やかに上昇するソフトスタート電圧を生成するソフトスタート回路を備える。制御回路は、DC/DCコンバータの出力電圧を、ソフトスタート電圧に追従させて増大させる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平9−121535号公報

【特許文献2】特開平7−336999号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

異常検出用のタイマー回路およびソフトスタート回路は、それぞれが外付けのキャパシタを必要とするため部品点数が多くなる。また制御回路には、外付けのキャパシタを接続するための2つのピン(パッド)が必要となるため、チップサイズ、パッケージサイズが大きくなってしまう。

【0005】

本発明はこうした課題に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、DC/DCコンバータの制御回路のサイズの低減にある。

【課題を解決するための手段】

【0006】

本発明のある態様は、DC/DCコンバータの制御回路に関する。制御回路は、その第1端子の電位が固定されたキャパシタと、キャパシタを充電する充電回路と、オン、オフが切りかえ可能であり、オン状態においてキャパシタを放電する放電回路と、キャパシタの電圧が所定の上側しきい値電圧に達してから所定の下側しきい値電圧に低下するまでの期間、第1レベルをとり、キャパシタの電圧が、下側しきい値電圧に低下してから、上側しきい値電圧に達するまでの期間、第2レベルをとる解除信号を生成するコンパレータと、解除信号と、異常状態が検出されるとアサートされる異常検出信号と、を受け、異常検出信号がアサートされるとフェイル信号をアサートし、その後、解除信号が第1レベルに遷移するタイミングにおいて、異常検出信号がネゲートされていると、フェイル信号をネゲートし、そのタイミングにおいて、異常検出信号がアサートされていると、フェイル信号をアサートし続け、かつ解除信号が第1レベルのとき放電回路をオンし、解除信号が第2レベルのとき放電回路をオフするロジック部と、キャパシタの電圧を反転することによりソフトスタート電圧を生成する反転アンプと、を備える。

【0007】

この態様によると、異常検出用のタイマー回路において生成されるスロープ電圧を、異常状態からの解放後においてソフトスタート電圧として利用することができる。その結果、タイマー回路とソフトスタート回路を兼用することができ、サイズを低減できる。

【0008】

ロジック部は、そのセット端子に異常検出信号が入力され、そのリセット端子に解除信号が入力されたセット優先のSRフリップフロップを含んでもよい。

【0009】

ロジック部はさらに、SRフリップフロップの反転出力信号と解除信号の論理和を生成し、放電回路を制御するORゲートを含んでもよい。

【0010】

本発明の別の態様は、DC/DCコンバータである。このDC/DCコンバータは、上述の制御回路を備える。

【0011】

本発明のさらに別の態様は、発光装置である。この発光装置は、発光素子と、発光素子に駆動電圧を供給する上述のDC/DCコンバータと、を備える。

【0012】

本発明のさらに別の態様は、電子機器である。この電子機器は、液晶パネルと、液晶パネルのバックライトとして設けられた上述の発光装置と、を備える。

【0013】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0014】

本発明のある態様によれば、回路面積を削減できる。

【図面の簡単な説明】

【0015】

【図1】実施の形態に係る駆動回路を備える電子機器の構成を示す回路図である。

【図2】図1の駆動回路の動作を示すタイムチャートである。

【発明を実施するための形態】

【0016】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0017】

本明細書において、「部材Aが、部材Bと接続された状態」とは、部材Aと部材Bが物理的に直接的に接続される場合のほか、部材Aと部材Bが、電気的な接続状態に影響を及ぼさない他の部材を介して間接的に接続される場合も含む。

同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、電気的な接続状態に影響を及ぼさない他の部材を介して間接的に接続される場合も含む。

【0018】

図1は、実施の形態に係るDC/DCコンバータを備える電子機器2の構成を示す回路図である。

【0019】

電子機器2は、ノートPC、デジタルカメラ、デジタルビデオカメラ、携帯電話端末、PDA(Personal Digital Assistant)などの電池駆動型の機器であり、発光装置3とLCD(Liquid Crystal Display)パネル5を備える。発光装置3はLCDパネル5のバックライトとして設けられる。

【0020】

発光装置3は、発光素子であるLEDストリング6と、その駆動回路4を備える。

【0021】

LEDストリング6は、直列に接続された複数のLEDを含む。駆動回路4は、昇圧型のDC/DCコンバータを含み、入力端子P1に入力された入力電圧(たとえば電池電圧)Vinを昇圧して、出力端子P2から出力電圧(駆動電圧)Voutを出力する。LEDストリング6の一端(アノード)は、出力端子P2に接続される。

【0022】

駆動回路(DC/DCコンバータ)4は、制御IC100および出力回路102を備える。出力回路102は、インダクタL1、整流ダイオードD1、スイッチングトランジスタM1、出力キャパシタC1を含む。出力回路102のトポロジーは一般的であるため、説明を省略する。

【0023】

制御IC100のスイッチング端子P4は、スイッチングトランジスタM1のゲートと接続される。制御IC100は、LEDストリング6の点灯に必要な出力電圧Voutが得られ、かつLEDストリング6に目標輝度に応じた駆動電流が流れるように、フィードバックによりスイッチングトランジスタM1のオン、オフのデューティ比を調節する。なおスイッチングトランジスタM1は制御IC100に内蔵されてもよい。

【0024】

第1検出抵抗R1は、LEDストリング6の経路上、具体的にはLEDストリング6のカソードと接地端子の間に設けられる。誤差増幅器EA1は、第1検出抵抗R1に生ずる電圧降下VR1と制御電圧VDIMの誤差を増幅し、誤差電圧VFBを生成する。オシレータ60は、三角波もしくはノコギリ波の周期電圧VOSCを生成する。PWMコンパレータPMW_CMPは、周期電圧VOSC、後述するソフトスタート電圧Vssおよび誤差電圧VFBを受ける。PWMコンパレータPWM_CMPは、ソフトスタート電圧Vssと誤差電圧VFBのうち、低い方と、周期電圧VOSCを比較する。PWMコンパレータPWM_CMPの出力(ゲートパルス信号G1)のデューティ比は、第1検出抵抗R1の電圧降下VR1が制御電圧VDIMと一致するように調節される。ドライバDR1は、ゲートパルス信号G1にもとづき、DC/DCコンバータのスイッチングトランジスタM1を駆動する。なお、パルス幅変調器に代えて、パルス周波数変調器を用いてもよい。

【0025】

第1コンパレータCMP1は、第1検出抵抗R1の電圧降下VR1が第1しきい値電圧VTH1を超えると、第1過電流検出信号OCP1をアサートする。第2検出抵抗R2は、DC/DCコンバータのスイッチングトランジスタM1の経路上に設けられる。第2コンパレータCMP2は、第2検出抵抗R2の電圧降下VR2が第2しきい値電圧VTH2を超えると第2過電流検出信号OCP2をアサートする。

【0026】

抵抗R3、R4は、駆動電圧Voutを分圧する。過電圧検出用の第3コンパレータCMP3は、抵抗R3、R4により分圧された電圧Vout’を、所定のしきい値電圧VTH3と比較する。第3コンパレータCMP3は、Vout’>VTH3となると、過電圧検出信号OVPをアサートする。

【0027】

ドライバDR1は、検出信号OCP1、OCP2、OVPの少なくともひとつがアサートされると、直ちにゲートパルス信号G1をローレベルに固定し、スイッチングトランジスタM1をオフすることによりDC/DCのスイッチング動作を停止する。

【0028】

キャパシタC2は、キャパシタ端子P5に外付けされる。キャパシタC2の一端(第1端子)は接地されて電位が固定される。充電回路30は、キャパシタC2を充電する。放電回路32は、オン、オフが切りかえ可能であり、オン状態においてキャパシタC2を放電する。放電回路32は、放電経路に直列に設けられた抵抗34およびトランジスタ36を含む。トランジスタ36がオンのとき、放電回路32はオン状態、トランジスタ36がオフのとき、放電回路32はオフ状態となる。

【0029】

コンパレータ38は、いわゆるヒステリシスコンパレータの機能を有し、キャパシタC2の電圧VC2を所定の上側しきい値電圧VHおよび所定の下側しきい値電圧VLと比較し、比較結果に応じた解除信号S1を生成する。解除信号S1は、キャパシタC2の電圧VC2が上側しきい値電圧VHに達してから所定の下側しきい値電圧VLに低下するまでの期間、第1レベル(ハイレベルとする)をとり、キャパシタC2の電圧VC2が、下側しきい値電圧VLに低下してから、上側しきい値電圧VHに達するまでの期間、第2レベル(ローレベル)をとる。

【0030】

解除信号S1は、放電回路32のオン、オフ状態の切りかえに利用されるとともに、解除信号S1のポジティブエッジは、異常状態を再判定するタイミングとして利用される。ロジック部40は、解除信号S1と、異常検出信号S2を受ける。異常検出信号S2は、発光装置3において何らかの異常状態が検出されるとアサートされる信号であり、たとえば、ORゲート39によって、上述した検出信号OCP1、OCP2、OVP等の論理和をとることにより生成される。これらの検出信号に加えて、または代えて、ORゲート39は、外部から供給される電源電圧の低電圧状態を示すUVLO(Under Voltage Lock Out)信号、温度異常を示すTHD(Thermal ShutDown)信号などを受けてもよい。

【0031】

ロジック部40は、異常検出信号S2がアサートされるとフェイル信号S3をアサート(ローレベル)する。その後、解除信号S1が第1レベル(ハイレベル)に遷移するタイミングにおいて、異常検出信号S2がネゲートされていると、ロジック部40はフェイル信号S3をネゲート(ハイレベル)する。解除信号S1がハイレベルに遷移する再判定タイミングにおいて、異常検出信号S2がアサートされていると、ロジック部40はフェイル信号S3をネゲートせずに、アサートし続ける。

【0032】

またロジック部40は、解除信号S1が第1レベル(ハイレベル)のとき放電回路32をオンし、解除信号S1が第2レベル(ローレベル)のとき放電回路32をオフする。

【0033】

ロジック部40は、SRフリップフロップ42、ORゲート44を含む。SRフリップフロップ42のセット端子(S)には、異常検出信号S2が入力され、そのリセット端子(R)には解除信号S1が入力される。SRフリップフロップ42は、セット優先論理で構成されており、セット端子とリセット端子の信号が両方ハイレベルのときには、セット端子が優先される。

【0034】

SRフリップフロップ42の反転出力信号#Q(#は論理反転を示す)は、フェイル信号S3に相当する。ORゲート44は、フェイル信号S3と解除信号S1の論理和を生成し、放電回路32を制御する。

【0035】

反転アンプ46は、抵抗Ri、Rfおよび演算増幅器OA1を含み、キャパシタC2の電圧VC2を反転することによりソフトスタート電圧Vssを生成する。スイッチSW1は、反転アンプ46の出力端子と、PWMコンパレータPWM_CMPの間に設けられる。スイッチSW1はソフトスタート期間以降、オン状態となり、ソフトスタート電圧VssがPWMコンパレータPWM_CMPの反転入力端子に供給される。ソフトスタート期間より前の期間、スイッチSW1はオフ状態となる。スイッチSW1は、オフ状態においてPWMコンパレータPWM_CMPの反転入力端子の電位がフローティングとならないように構成される。スイッチSW1は、たとえばフェイル信号S3がハイレベルの期間、オンしてもよい。

【0036】

出力回路50は、フェイル信号S3を、制御IC100の外部のプロセッサ(不図示)に出力する。出力回路50は、インバータ52およびトランジスタ54を含む。インバータ52は、フェイル信号S3を反転する。トランジスタ54は、オープンドレイン形式の出力回路を構成する。

【0037】

以上が駆動回路4の構成である。続いてその動作を説明する。図2は、図1の駆動回路4の動作を示すタイムチャートである。時刻t0に、異常検出信号S2がアサートされると、SRフリップフロップ42の反転出力#Qがローレベルに遷移し、フェイル信号S3がアサート(ローレベル)される。

【0038】

フェイル信号S3がローレベルとなると、トランジスタ36がオフし、放電回路32がオフ状態となり、充電回路30によってキャパシタC2が充電され、キャパシタ電圧VC2が上昇する。時刻t1にキャパシタ電圧VC2が上側しきい値電圧VHに達すると、解除信号S1がハイレベルに遷移する。

【0039】

時刻t1に解除信号S1がハイレベルに遷移しても、異常検出信号S2がアサートされているため、セット優先論理によってSRフリップフロップ42はリセットされず、フェイル信号S3はローレベルを維持し続ける。解除信号S1がハイレベルに遷移すると、トランジスタ36がオンし、キャパシタC2が放電され、キャパシタ電圧VC2が低下し始める。キャパシタ電圧VC2が下側しきい値電圧VLまで低下すると、解除信号S1がローレベルに遷移し(t2)、再びキャパシタC2が充電される。時刻t3にキャパシタ電圧VC2が上側しきい値電圧VHに達すると、解除信号S1がハイレベルとなる。

【0040】

制御IC100は、同様の処理を繰り返す。時刻t4に異常検出信号S2がネゲートされる。時刻t4に解除信号S1がハイレベルに遷移すると、SRフリップフロップ42がリセットされ、フェイル信号S3がハイレベルに遷移する。フェイル信号S3がハイレベルに遷移すると、スイッチSW1がオンする。

【0041】

スイッチSW1がオンすると、反転アンプ46の出力電圧Vssが、PWMコンパレータPMW_CMPへと供給される。その結果、ゲートパルス信号G1のデューティ比が時間とともに増加し、出力電圧Voutが緩やかに上昇する。

【0042】

以上が駆動回路4の動作である。

制御IC100によれば、単一のキャパシタC2を充放電することにより、周期信号である解除信号S1と、ソフトスタート電圧Vssを生成することができる。これにより、従来2つ必要であったキャパシタがひとつに削減できるため、回路面積を削減することができる。

【0043】

また、キャパシタC2に発生する電圧VC2の下りのスロープを反転してソフトスタート電圧Vssを生成しているため、フェイル信号S3がネゲートされると、直ちにソフトスタート電圧Vssを生成し始めることができる。

【0044】

以上、本発明について、実施の形態をもとに説明した。この実施の形態は例示であり、それらの各構成要素や各処理プロセス、それらの組み合わせには、さまざまな変形例が存在しうる。以下、こうした変形例について説明する。

【0045】

実施の形態では、LEDストリング6の経路上に設けられた第1検出抵抗R1の電圧降下VR1を目標値VDIMと一致させることにより、駆動電流を安定化させる構成を説明したが、本発明はそれに限定されない。たとえばLEDストリング6の経路上に、安定した駆動電流を生成する定電流源(電流ドライバ)を設けてもよい。

【0046】

実施の形態ではインダクタを用いた非絶縁型のスイッチング電源を説明したが、本発明はトランスを用いた絶縁型のスイッチング電源にも適用可能である。

【0047】

実施の形態では、発光装置3のアプリケーションとして電子機器を説明したが、用途は特に限定されず、照明などにも利用できる。

【0048】

また、本実施の形態において、ハイレベル、ローレベルの論理信号の設定は一例であって、インバータなどによって適宜反転させることにより自由に変更することが可能である。

【0049】

実施の形態にもとづき、具体的な語句を用いて本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【符号の説明】

【0050】

2…電子機器、3…発光装置、4…駆動回路、5…LCDパネル、6…LEDストリング、C2…キャパシタ、30…充電回路、32…放電回路、34…抵抗、36…トランジスタ、38…コンパレータ、40…ロジック部、42…SRフリップフロップ、44…ORゲート、46…反転アンプ、50…出力回路、52…インバータ、54…トランジスタ、SW1…スイッチ、100…制御IC、102…出力回路、EA1…誤差増幅器、DR1…第1ドライバ、CMP1…第1コンパレータ、CMP2…第2コンパレータ、CMP3…第3コンパレータ、R1…第1検出抵抗、R2…第2検出抵抗、L1…インダクタ、C1…出力キャパシタ、D1…整流ダイオード、M1…スイッチングトランジスタ、OCP1…第1過電流検出信号、OCP2…第2過電流検出信号、OVP…過電圧検出信号、S1…解除信号、S2…異常検出信号、S3…フェイル信号。

【特許請求の範囲】

【請求項1】

DC/DCコンバータの制御回路であって、

その第1端子の電位が固定されたキャパシタと、

前記キャパシタを充電する充電回路と、

オン、オフが切りかえ可能であり、オン状態において前記キャパシタを放電する放電回路と、

前記キャパシタの電圧が所定の上側しきい値電圧に達してから所定の下側しきい値電圧に低下するまでの期間、第1レベルをとり、前記キャパシタの電圧が、前記下側しきい値電圧に低下してから、前記上側しきい値電圧に達するまでの期間、第2レベルをとる解除信号を生成するコンパレータと、

前記解除信号と、異常状態が検出されるとアサートされる異常検出信号と、を受け、前記異常検出信号がアサートされるとフェイル信号をアサートし、その後、前記解除信号が前記第1レベルに遷移するタイミングにおいて、前記異常検出信号がネゲートされていると、前記フェイル信号をネゲートし、そのタイミングにおいて、前記異常検出信号がアサートされていると、前記フェイル信号をアサートし続け、かつ前記解除信号が前記第1レベルのとき前記放電回路をオンし、前記解除信号が前記第2レベルのとき前記放電回路をオフするロジック部と、

前記キャパシタの電圧を反転することによりソフトスタート電圧を生成する反転アンプと、

を備えることを特徴とする制御回路。

【請求項2】

前記反転アンプの出力端子側の前記ソフトスタート電圧の経路上に設けられたスイッチをさらに備えることを特徴とする請求項1に記載の制御回路。

【請求項3】

前記スイッチは、前記フェイル信号がアサートされる期間オフ、前記フェイル信号がネゲートされる期間オンすることを特徴とする請求項2に記載の制御回路。

【請求項4】

前記ロジック部は、そのセット端子に前記異常検出信号が入力され、そのリセット端子に前記解除信号が入力されたセット優先のSRフリップフロップを含むことを特徴とする請求項1から3のいずれかに記載の制御回路。

【請求項5】

前記ロジック部はさらに、

前記SRフリップフロップの反転出力信号と前記解除信号の論理和を生成し、前記放電回路を制御するORゲートを含むことを特徴とする請求項4に記載の制御回路。

【請求項6】

請求項1から5のいずれかに記載の制御回路を備えることを特徴とするDC/DCコンバータ。

【請求項7】

発光素子と、

前記発光素子に駆動電圧を供給する請求項6に記載のDC/DCコンバータと、

を備えることを特徴とする発光装置。

【請求項8】

液晶パネルと、

前記液晶パネルのバックライトとして設けられた請求項7に記載の発光装置と、

を備えることを特徴とする電子機器。

【請求項1】

DC/DCコンバータの制御回路であって、

その第1端子の電位が固定されたキャパシタと、

前記キャパシタを充電する充電回路と、

オン、オフが切りかえ可能であり、オン状態において前記キャパシタを放電する放電回路と、

前記キャパシタの電圧が所定の上側しきい値電圧に達してから所定の下側しきい値電圧に低下するまでの期間、第1レベルをとり、前記キャパシタの電圧が、前記下側しきい値電圧に低下してから、前記上側しきい値電圧に達するまでの期間、第2レベルをとる解除信号を生成するコンパレータと、

前記解除信号と、異常状態が検出されるとアサートされる異常検出信号と、を受け、前記異常検出信号がアサートされるとフェイル信号をアサートし、その後、前記解除信号が前記第1レベルに遷移するタイミングにおいて、前記異常検出信号がネゲートされていると、前記フェイル信号をネゲートし、そのタイミングにおいて、前記異常検出信号がアサートされていると、前記フェイル信号をアサートし続け、かつ前記解除信号が前記第1レベルのとき前記放電回路をオンし、前記解除信号が前記第2レベルのとき前記放電回路をオフするロジック部と、

前記キャパシタの電圧を反転することによりソフトスタート電圧を生成する反転アンプと、

を備えることを特徴とする制御回路。

【請求項2】

前記反転アンプの出力端子側の前記ソフトスタート電圧の経路上に設けられたスイッチをさらに備えることを特徴とする請求項1に記載の制御回路。

【請求項3】

前記スイッチは、前記フェイル信号がアサートされる期間オフ、前記フェイル信号がネゲートされる期間オンすることを特徴とする請求項2に記載の制御回路。

【請求項4】

前記ロジック部は、そのセット端子に前記異常検出信号が入力され、そのリセット端子に前記解除信号が入力されたセット優先のSRフリップフロップを含むことを特徴とする請求項1から3のいずれかに記載の制御回路。

【請求項5】

前記ロジック部はさらに、

前記SRフリップフロップの反転出力信号と前記解除信号の論理和を生成し、前記放電回路を制御するORゲートを含むことを特徴とする請求項4に記載の制御回路。

【請求項6】

請求項1から5のいずれかに記載の制御回路を備えることを特徴とするDC/DCコンバータ。

【請求項7】

発光素子と、

前記発光素子に駆動電圧を供給する請求項6に記載のDC/DCコンバータと、

を備えることを特徴とする発光装置。

【請求項8】

液晶パネルと、

前記液晶パネルのバックライトとして設けられた請求項7に記載の発光装置と、

を備えることを特徴とする電子機器。

【図1】

【図2】

【図2】

【公開番号】特開2012−60743(P2012−60743A)

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願番号】特願2010−200203(P2010−200203)

【出願日】平成22年9月7日(2010.9.7)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願日】平成22年9月7日(2010.9.7)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]