DC/DCコンバータ

【課題】軽負荷時において、同期整流スイッチに逆電流を流すことなく、簡素な構成で同期整流スイッチの切り替え動作を行うことが可能なDC‐DCコンバータを提供する。

【解決手段】軽負荷時に同期整流オフとする同期整流オフ選択回路11とスイッチQ1のオフ期間Toffを生成するToff期間生成部12を備え、軽負荷時のスイッチQ1とQ2との接続点電位をパルス成型回路13でパルス変換後カウンタ14でカウントし、時間差比較/不連続検出信号生成部15でToff期間中にカウンタ信号の発生を検出し、カウンタ信号があった場合は1パルス・ラッチ回路17を介して次のスイッチング周期は同期整流オフを継続させてスイッチQ2の同期整流をオフにするスイッチ制御部10aを備える。

【解決手段】軽負荷時に同期整流オフとする同期整流オフ選択回路11とスイッチQ1のオフ期間Toffを生成するToff期間生成部12を備え、軽負荷時のスイッチQ1とQ2との接続点電位をパルス成型回路13でパルス変換後カウンタ14でカウントし、時間差比較/不連続検出信号生成部15でToff期間中にカウンタ信号の発生を検出し、カウンタ信号があった場合は1パルス・ラッチ回路17を介して次のスイッチング周期は同期整流オフを継続させてスイッチQ2の同期整流をオフにするスイッチ制御部10aを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はDC−DCコンバータに関し、特に、逆電流を防止する同期整流方式のDC−DCコンバータに関する。

【背景技術】

【0002】

同期整流方式のDC−DCコンバータにおいて、負荷電流が小さいときの電力変換効率を改善する方法が広く知られている。

一つは、DC−DCコンバータのスイッチング素子に流れる電流を検出するか、または負荷電流を直接検出する方法である。もう一つの方法は、同期整流素子の端子間電圧を検出する方法である。ここで 図6は、同期整流素子の端子間電圧を検出する方法の従来のDC−DCコンバータを示す回路図である。

【0003】

図6に示すDC−DCコンバータ100は、同期整流型のDC−DCコンバータであって、PWM発振器20、スイッチ制御部10と、PMOSトランジスタQ1とNMOSトランジスタQ2(以下それぞれ、スイッチQ1,スイッチQ2とする)との直列接続回路で構成されるスイッチング部3と、インダクタ5と出力コンデンサC2とで構成される平滑回路4と、出力電圧を所定の電圧に安定化するための制御回路1とを有している。平滑回路4の出力部はDC−DCコンバータ100の負荷回路8(図では電流源)に接続されている。

【0004】

スイッチ制御部10は、スイッチング部3に接続され、直流入力電源VDDの電源電圧を降圧して所定の直流電圧を得るために、PWM発振器20からのPWM信号に基づきスイッチング回路3のオンオフ動作を制御する。また、スイッチング部3の出力部には、平滑回路4を介して負荷回路8が接続され、制御回路1を介してスイッチ制御部10によりスイッチQ1,スイッチQ2が所定のスイッチング期間内で交互にON/OFF制御されることによって、負荷8に所定の大きさの出力電圧V2を供給する。

【0005】

図7は、図6におけるDC−DCコンバータの各部の動作波形を示す図である。

このDC−DCコンバータ100において、インダクタ5に流れるインダクタ電流IL(図7中(a)に示す波形)は、スイッチQ1のON期間(スイッチQ2はOFFしている)では、スイッチQ1に流れる電流IQ1(図7中(b)に示す波形)と等しくなり、スイッチQ2のON期間(スイッチQ1はOFFしている)では、スイッチQ2に流れる電流IQ2(図7中(c)に示す波形)と等しくなる。

【0006】

再び図6に戻って説明する。

定常状態において、インダクタ電流ILの平均値は出力電流Ioと等しくなるが、そのリップル電流の大きさは、直流入力電源VDDからの入力電圧VDDと出力電圧V2とが同条件なら、出力電流Ioの値によらず略一定になるため、出力電流Ioが小さくなると、出力端子側からスイッチQ1とスイッチQ2との接続点に向かって流れる電流(以下、「逆電流」という)、すなわちIL<0となる期間が生じて、電力変換効率が低下する。

【0007】

この効率の低下を防止するために、逆電流が流れたことを検出して、スイッチQ2をOFFさせる方法が知られている(特許文献1)。

【0008】

図6に示すスイッチ制御部10は、反転入力端子がノードV1に接続され、非反転入力端子がGNDに接続されるコンパレータCPを有し、コンパレータCPの出力はアンド回路ANDの一方の端子に接続され、他方の端子はPWM発振器20の信号が入力されている。

【0009】

このような構成は、DC−DCコンバータ100の出力段のMOSFETをICに内蔵する場合によく用いられる。

DC−DCコンバータ100は、コンパレータCPにより平滑回路4のインダクタ5を流れるインダクタ電流ILの向きを、ノードV1の電位を検出することにより判断し、ノードV1の電位がGND電位よりも大きいとき、スイッチQ2をOFFすることにより、インダクタ電流ILが出力端子側からノードV1に向かって流れ、GNDに流れ込むことを防止して効率の低下を防止している。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2000−92824号公報

【発明の開示】

【発明が解決しようとする課題】

【0011】

しかしながら、従来のDC‐DCコンバータ100では、インダクタ5の電流不連続時の自由振動により逆電流が流れたり、正常方向の電流に戻ったりする振動期間を生じるため、スイッチQ2はPWM信号の1周期内において複数回のオンオフ動作を繰り返すことになる。すなわち、スイッチQ2のスイッチング回数の増加によるスイッチング損失及びゲート駆動電力も増加してしまい変換効率を低下させる原因にもなる。

【0012】

本発明の課題は、逆電流を流すことなく、簡素な構成で同期整流スイッチの切り替え動作を行うことが可能なDC‐DCコンバータを提供することにある。

【課題を解決するための手段】

【0013】

上記課題を解決するために、本発明に係るDC‐DCコンバータは、第1の電位を供給する第1の電源から、第1の電位よりも低い第2の電位を出力する同期整流方式のDC−DCコンバータにおいて、第1の電位を供給する第1の電源とグランド間に直列に設けられた第1のスイッチ素子と第2のスイッチ素子からなる一対のスイッチ素子と、制御信号に応じて、前記第1及び第2のスイッチ素子を相補的にオンオフ制御する制御回路と、第1のスイッチ素子と前記第2のスイッチ素子との接続点の電位を平滑化する平滑回路とを有し、制御回路は、第2の電位を検出して、検出した電位と第1の基準電位とを比較して誤差信号を得て、誤差信号を基に第2の電位が所定の電圧になるように第1及び第2のスイッチ素子をオンオフ制御する機能を備え、 さらに、制御回路は、第2の電位出力の負荷電流が軽負荷となり、誤差信号が第2の基準電位を越えた場合に、第2のスイッチ素子をオフ状態にするように構成され、 第2の電位出力の負荷電流が軽負荷の時に、第1のスイッチ素子と第2のスイッチ素子との接続点の電位を第3の基準電位と第4の基準電位とで比較する比較器と、第1のスイッチ素子がオフ状態の時に、比較器からの出力信号をカウントするカウンタを有し、カウンタのカウント数がゼロになったことを検出して第2のスイッチ素子の駆動回路動作を無効から有効にすることを特徴とする。

また、平滑回路は、インダクタとコンデンサとの直列回路から構成され、インダクタとコンデンサの接続点が第2の電位を出力する端子に接続され、比較器は、第1のスイッチ素子と第2のスイッチ素子との接続点の電位に生じる振動電圧波形をパルス信号に変換出力し、第1のスイッチ素子のオフ期間にカウンタ回路でパルス信号をカウントすることを特徴とする。

また、第2の電位の設定電圧に合わせて、第3の基準電位と第4の基準電位とを可変することを特徴とする。

【発明の効果】

【0014】

本発明によれば、第2の電位出力の負荷電流が軽負荷から重負荷に変わる時に、第1のスイッチ素子と第2のスイッチ素子との接続点の電位を第3と第4の基準電位とで比較してパルス信号に変換出力し、第1のスイッチ素子のオフ期間にカウンタ回路でパルス信号がゼロになったことを検出することで、平滑回路に流れる電流の向きを測定せずに、第2のスイッチ素子のオンオフ動作による同期整流のオフ状態を有効にすることができる。

【図面の簡単な説明】

【0015】

【図1】本発明の実施例に係るDC‐DCコンバータの制御回路の構成を示す図である。

【図2】本発明の実施例に係るDC‐DCコンバータの動作を示すタイミングチャートである。

【図3】本発明の実施例に係る同期整流オフ選択回路である。

【図4】本発明の実施例に係る出力電流Ioとフィードバック信号FB電圧との関係を示した特性図である。

【図5】本発明の実施例に係るパルス成型回路の構成図である。

【図6】従来のDC‐DCコンバータの構成を示す図である。

【図7】従来のDC‐DCコンバータの動作を示すタイミングチャートである。

【発明を実施するための形態】

【0016】

以下、本発明の実施の形態に係るDC-DCコンバータを、図面を参照しながら詳細に説明する。

【0017】

本発明においては、同期整流方式のDC−DCコンバータにおいて、軽負荷時の平滑回路のインダクタに流れる電流が臨界電流以下になると自由振動をおこして出力から同期整流の第2のスイッチ素子を介して逆電流が流れることを防止するものである。

まず、軽負荷時の平滑回路のインダクタに流れる電流が臨界電流以下になる前に、DC−DCコンバータの制御回路の誤差信号電圧を基に軽負荷であることを判断して同期整流のスイッチ素子の動作をオフ状態にする。

次に、軽負荷状態から定格負荷ないし重負荷の方に変化したときには、平滑回路に流れる電流の向きを測定せずに、第1のスイッチ素子と第2のスイッチ素子との接続点の電位を第3と第4の基準電位とで比較してパルス信号に変換出力し、第1のスイッチ素子のオフ期間にカウンタ回路でパルス信号がゼロになったことを検出することで、第2のスイッチ素子の同期整流の機能をオフ状態からオン状態にすることができる。

【実施例】

【0018】

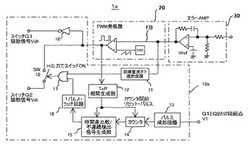

図1は、本発明の実施例に係るDC-DCコンバータの制御回路の構成を示す図である。

なお、図1においては、図6に示す従来のDC-DCコンバータと同一部分には同一符号を付しその説明を省略し、図6に示す従来のDC-DCコンバータと異なる部分を説明する。

【0019】

本発明の実施例に係るDC-DCコンバータは、図6に示した従来のDC-DCコンバータに、制御回路1aのスイッチ制御部10aが変更されている。

【0020】

図1に示す制御回路1aは、PWM発振器20、エラーAMP30、スイッチ制御部10aから構成され、PWM発振器20のPWM信号とエラーAMP30の出力信号を基に、スイッチ制御部10aを介してスイッチQ1,スイッチQ2のオンオフ駆動信号を出力する。

スイッチ制御部10aは、同期整流オフ選択回路11、Toff期間生成部12、パルス成型回路13、カウンタ14、時間差比較/不連続検出信号生成部15、1パルス・ラッチ16、OR回路17、INV回路18、スイッチSW19から構成されている。

スイッチ制御部10aは、エラーAMP30のフィードバック信号FBから軽負荷を検出してスイッチQ2の同期整流をオフにし、スイッチQ1、Q2の接続点電位V1を検出して軽負荷に発生する自由振動電圧をパルスに成型後、スイッチQ1のオフ期間中のカウンタ回路でのパルスカウントがゼロになったことを検出することで、スイッチQ2の同期整流をオフ状態からオン状態に戻す。

【0021】

図1に示すように同期整流オフ選択回路11は、エラーAMP30の出力であるフィードバック信号FBを入力し、フィードバック信号FBの電圧が基準電圧Vlightよりも低い場合にHレベル信号をOR回路17の一方の端子へ出力する。この同期整流オフ選択回路11については、後に詳細に説明する。

Toff期間生成部12は、PWM発振器20の出力信号を基にToff期間の信号を生成し、カウンタ14へカウンタ・リセット信号及び、時間差比較/不連続検出信号生成部15へToff期間の信号を送出する。

パルス生成回路13は、スイッチQ1,スイッチQ2との接続点V1の電位v1信号を入力して、V1の電位に生じる振動電圧波形をパルス信号に変換出力してカウンタ14へ出力する。このパルス生成回路13については、後に詳細に説明する。

カウンタ14は、Toff期間生成部12からのカウンタ・リセット信号によりリセットされて、パルス生成回路からのパルス信号を待受けする。

時間差比較/不連続検出信号生成部15は、Toff期間生成部12からのToff期間内にカウンタ14からパルスが入力されるか否かを検出し、パルスを検出すると出力信号を1パルス・ラッチ回路16へ出力する。1パルス・ラッチ回路16はPWM発振器20の出力信号の1周期分T、前述の時間差比較/不連続検出信号生成部15からの信号によりLレベル信号をOR回路17の他方の端子へ出力する。

【0022】

OR回路17は、1パルス・ラッチ回路16または同期整流オフ選択回路11から送られてくるLレベル信号に応じて、NMOS駆動信号Vdlを、スイッチ(SW)19を介してオフ信号へ切り替える。

これにより、軽負荷時の場合にはスイッチQ2はオン動作しないモードになる。

【0023】

次に、このように構成される実施例に係るDC-DCコンバータの動作を、図2に示すタイミングチャートを参照しながら説明する。

図2に示したタイミングチャートでは、同期整流オフ選択回路11からの切替信号が、一旦軽負荷と判定された信号を出力した後、カウンタ14がパルス成型回路信号のパルスをカウントする毎に不連続検出信号をLレベル出力し、スイッチ(SW)19をオフする状態を示している。

【0024】

図2のタイミングチャートにおけるインダクタ5に流れる電流IL波形(1)は、周期T期間の時刻t1〜t2にスイッチQ1からのオン電流が流れ、時刻t2〜t3間に回生電流が流れる。時刻t3にて電流は不連続となり、時刻t4まで流れない。

図2(2)に示すスイッチQ1とスイッチQ2との接続点V1の電位v1波形は、時刻t1〜t2にスイッチQ1からのオン電圧が印加され、時刻t2〜t3間にスイッチQ2のボディダイオードを介して回生電流が流れる。ここで、時刻t3〜t4期間はインダクタ5による自由振動電圧が生じる。

【0025】

図2(3)に示すToff期間生成部12のToff期間生成は、制御回路1aのPWM信号からToff期間波形を生成する。また、(4)に示すToff期間生成部の(A)に示す波形は、スイッチQ1のオン時の立ち上がりにターンオン検出を行い、ワンショットパルスを出力する。同様に(5)に示すToff期間生成部の(B)に示す波形は、スイッチQ1のオン時の立ち下がりにターンオフ検出を行い、ワンショットパルスを出力する。

前述のターンオン検出及びターンオフ検出でのワンショットパルスは、各々カウンタ14及び時間差比較/不連続検出信号生成部15に出力され、カウンタ14のカウンタリセット・パルス及び、カウント開始、また時間差比較/不連続検出信号生成部15のToff期間信号となる。

すなわち、カウンタ14は前述のターンオフ検出でカウントを開始し、前述のターンオン検出でカウントをリセットする。

【0026】

図2(7)に示すパルス生成回路信号は、時刻t3〜t4期間にv1波形の自由振動電圧波形を基準電圧Vth(H)と基準電圧Vth(L)とで比較して生成されたパルスである。時刻aにてv1波形の自由振動電圧が基準電圧Vth(H)を超えるとHレベルを出力し、時刻bにてv1波形の自由振動電圧が基準電圧Vth(L)未満になるとLレベルを出力する。以降、時刻b〜fにおいても同様に出力する。

すなわち、インダクタ5に流れる電流IL波形が不連続となるとv1波形の自由振動電圧波形を介してパルスとして出力される。

このパルス生成回路の構成例の詳細は、後述する。

【0027】

時間差比較/不連続検出信号生成部15は、Toff期間の時刻とパルス生成回路の出力とを比較して、インダクタ5に流れる電流IL波形の不連続検出信号の有無を検出し、不連続検出信号が有った時点でLレベルを1パルス・ラッチ回路16へ出力する。図2(8)では、時刻aにてパルス生成回路のパルスを検出してLレベルになっている。ここで、 時間差比較/不連続検出信号生成部15はToff期間の開始とともにリセットされ、出力はHレベルに戻る。

【0028】

1パルス・ラッチ回路16は、時間差比較/不連続検出信号生成部15の信号を時刻t1あるいは時刻t4で取り込みラッチしてOR回路17の他方の入力端子へ出力する。OR回路17は、Lレベル信号をスイッチ(SW)19に出力して、オフとする。図2(9)では、オフ状態が継続している様を示している。すなわち、時刻t3〜t4間に不連続検出信号が発生した場合、次のスイッチング周期におけるスイッチQ2による同期整流動作を停止させる。

【0029】

図3は本発明の実施例に係る制御部の同期整流オフ選択回路11を示したものである。同期整流オフ選択回路11は、コンパレータCPoffと基準電圧Vlightからなり、コンパレータCPoffの非反転端子はエラーAMP2の出力に接続され、フィードバック電圧FBが入力される。反転端子には基準電圧Vlightの正極が接続され、基準電圧Vlightの負極はグランドに接地されている。

【0030】

図4は本発明の実施例に係る出力電流Ioとフィードバック信号FB電圧との関係を示した特性図である。図4に示す特性図を参照しながら同期整流オフ選択回路11の動作について説明する。

図4は、出力電流Ioに対する誤差増幅器エラーAMPのフィードバック信号FB電圧の変化を示した特性図である。フィードバック信号FB電圧は出力電流Ioに対して比例する関係にあることがわかる。

すなわち、インダクタ5に流れるILの不連続電流ポイントとなる出力電流Ioがわかれば、フィードバック信号FB電圧でも検出することが可能である。

この特性を利用して、同期整流オフ選択回路11は、インダクタ5に流れるILの不連続電流ポイントとなるフィードバック信号FB電圧値を基準電圧Vlightとして事前に設定することで、コンパレータCPoffの非反転端子電圧とを比較して、不連続電流状態か否かを検出する。コンパレータCPoffの非反転端子電圧が基準電圧Vlight未満の場合にはLレベルを出力する。これにより、同期整流動作はオフが選択されることになる。

【0031】

図5は本発明の実施例に係る制御部のパルス成型回路の構成図である。図5に示すパルス成型回路は、フリップフロップ回路FF1とコンパレータCP(H)、CP(L)と基準電圧Vth(H)、Vth(L)と抵抗R11,R12からなる。

スイッチQ1とスイッチQ2との接続点V1とグランド間に抵抗R11とR12との直列回路が接続されている。抵抗R11とR12の接続端子には、コンパレータCP(H)の非反転端子とコンパレータCP(L)の反転端子とが接続されている。コンパレータCP(H)の反転端子には、基準電圧Vth(H)の正電極が接続され、負電極はグランドに接地されている。また、コンパレータCP(L)の非反転端子には基準電圧Vth(L)の正電極が接続され、負電極はグランドに接地されている。

コンパレータCP(H)の出力端子はフリップフロップ回路FF1のセット端子Sに接続され、コンパレータCP(L)の出力端子はフリップフロップ回路FF1のリセット端子Rに接続され、フリップフロップ回路FF1の出力Qは、パルス成型信号として出力される。また、基準電圧Vth(H)とVth(L)の電圧関係は、Vth(H)>Vth(L)の設定がされている。

【0032】

パルス成型回路の動作について、以下に詳細を述べる。

コンパレータCP(H)及びCP(L)はスイッチQ1とスイッチQ2の接続点V1の電位v1を抵抗R11とR12とで分圧した電圧V1pと基準電圧Vth(H)とVth(L)と各々比較する。

図2の(2)V1波形と(7)パルス成型回路信号で示されるように、時刻t3〜t4においてインダクタ5の自由振動波形が発生すると、時刻aにて電圧V1pは基準電圧Vth(H)を超えるのでコンパレータCP(H)はHレベルを出力し、フリップフロップ回路FF1はセットさせてHレベル信号を出力する。また、時刻bにおいて電圧V1pは基準電圧Vth(L)より低下するのでコンパレータCP(L)はHレベルを出力し、フリップフロップ回路FF1はリセットされてLレベル信号を出力する。すなわち、v1波形の自由振動電圧(V1p)は、基準電圧Vth(H)とVth(L)をもとにパルス成型されることになる。

【0033】

以上のように、スイッチ制御部10aは、エラーAMP30のフィードバック信号FB電圧から軽負荷を検出してスイッチQ2の同期整流をオフにする。また、スイッチQ1、Q2の接続点V1の電位v1を検出して、軽負荷に発生する自由振動電圧をパルス信号に成型後、スイッチQ1のオフ期間にカウンタ回路で前述のパルスがゼロになったことを検出することで、スイッチQ2の同期整流をオフ状態からオン状態に戻す。これにより、インダクタ5の電流ILのピーク電流もしくは平均値をシャント抵抗或いはセンスMOSFET等で直接検出しないで軽負荷/重負荷を判断し、かつ軽負荷時に逆電流を流すことなく、簡素な構成で同期整流スイッチの切り替え動作を行うことが可能なDC‐DCコンバータを提供することができる。

【産業上の利用可能性】

【0034】

本発明は、軽負荷時の効率が要求されるDC‐DCコンバータに適用可能である。

【符号の説明】

【0035】

Q1 スイッチ(PMOSトランジスタ)

Q2 スイッチ(NMOSトランジスタ)

FF1 フリップフロップ回路

CP、CPoff、CP(H)、CP(L) コンパレータ

R11,R12 抵抗

Vref、Vlight、Vth(H)、Vth(L) 基準電圧

1 、1a 制御回路

3 スイッチング部

4 平滑回路

5 インダクタ

8 負荷回路

10、10a スイッチ制御部

11 同期整流オフ選択回路

12 Toff期間生成回路

13 パルス成型回路

14 カウンタ

15 時間差比較/不連続検出信号部

16 1パルス・ラッチ

17 OR回路

18 インバータ回路

19 スイッチ(SW)

20 PWM発振器

30 エラーAMP

【技術分野】

【0001】

本発明はDC−DCコンバータに関し、特に、逆電流を防止する同期整流方式のDC−DCコンバータに関する。

【背景技術】

【0002】

同期整流方式のDC−DCコンバータにおいて、負荷電流が小さいときの電力変換効率を改善する方法が広く知られている。

一つは、DC−DCコンバータのスイッチング素子に流れる電流を検出するか、または負荷電流を直接検出する方法である。もう一つの方法は、同期整流素子の端子間電圧を検出する方法である。ここで 図6は、同期整流素子の端子間電圧を検出する方法の従来のDC−DCコンバータを示す回路図である。

【0003】

図6に示すDC−DCコンバータ100は、同期整流型のDC−DCコンバータであって、PWM発振器20、スイッチ制御部10と、PMOSトランジスタQ1とNMOSトランジスタQ2(以下それぞれ、スイッチQ1,スイッチQ2とする)との直列接続回路で構成されるスイッチング部3と、インダクタ5と出力コンデンサC2とで構成される平滑回路4と、出力電圧を所定の電圧に安定化するための制御回路1とを有している。平滑回路4の出力部はDC−DCコンバータ100の負荷回路8(図では電流源)に接続されている。

【0004】

スイッチ制御部10は、スイッチング部3に接続され、直流入力電源VDDの電源電圧を降圧して所定の直流電圧を得るために、PWM発振器20からのPWM信号に基づきスイッチング回路3のオンオフ動作を制御する。また、スイッチング部3の出力部には、平滑回路4を介して負荷回路8が接続され、制御回路1を介してスイッチ制御部10によりスイッチQ1,スイッチQ2が所定のスイッチング期間内で交互にON/OFF制御されることによって、負荷8に所定の大きさの出力電圧V2を供給する。

【0005】

図7は、図6におけるDC−DCコンバータの各部の動作波形を示す図である。

このDC−DCコンバータ100において、インダクタ5に流れるインダクタ電流IL(図7中(a)に示す波形)は、スイッチQ1のON期間(スイッチQ2はOFFしている)では、スイッチQ1に流れる電流IQ1(図7中(b)に示す波形)と等しくなり、スイッチQ2のON期間(スイッチQ1はOFFしている)では、スイッチQ2に流れる電流IQ2(図7中(c)に示す波形)と等しくなる。

【0006】

再び図6に戻って説明する。

定常状態において、インダクタ電流ILの平均値は出力電流Ioと等しくなるが、そのリップル電流の大きさは、直流入力電源VDDからの入力電圧VDDと出力電圧V2とが同条件なら、出力電流Ioの値によらず略一定になるため、出力電流Ioが小さくなると、出力端子側からスイッチQ1とスイッチQ2との接続点に向かって流れる電流(以下、「逆電流」という)、すなわちIL<0となる期間が生じて、電力変換効率が低下する。

【0007】

この効率の低下を防止するために、逆電流が流れたことを検出して、スイッチQ2をOFFさせる方法が知られている(特許文献1)。

【0008】

図6に示すスイッチ制御部10は、反転入力端子がノードV1に接続され、非反転入力端子がGNDに接続されるコンパレータCPを有し、コンパレータCPの出力はアンド回路ANDの一方の端子に接続され、他方の端子はPWM発振器20の信号が入力されている。

【0009】

このような構成は、DC−DCコンバータ100の出力段のMOSFETをICに内蔵する場合によく用いられる。

DC−DCコンバータ100は、コンパレータCPにより平滑回路4のインダクタ5を流れるインダクタ電流ILの向きを、ノードV1の電位を検出することにより判断し、ノードV1の電位がGND電位よりも大きいとき、スイッチQ2をOFFすることにより、インダクタ電流ILが出力端子側からノードV1に向かって流れ、GNDに流れ込むことを防止して効率の低下を防止している。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2000−92824号公報

【発明の開示】

【発明が解決しようとする課題】

【0011】

しかしながら、従来のDC‐DCコンバータ100では、インダクタ5の電流不連続時の自由振動により逆電流が流れたり、正常方向の電流に戻ったりする振動期間を生じるため、スイッチQ2はPWM信号の1周期内において複数回のオンオフ動作を繰り返すことになる。すなわち、スイッチQ2のスイッチング回数の増加によるスイッチング損失及びゲート駆動電力も増加してしまい変換効率を低下させる原因にもなる。

【0012】

本発明の課題は、逆電流を流すことなく、簡素な構成で同期整流スイッチの切り替え動作を行うことが可能なDC‐DCコンバータを提供することにある。

【課題を解決するための手段】

【0013】

上記課題を解決するために、本発明に係るDC‐DCコンバータは、第1の電位を供給する第1の電源から、第1の電位よりも低い第2の電位を出力する同期整流方式のDC−DCコンバータにおいて、第1の電位を供給する第1の電源とグランド間に直列に設けられた第1のスイッチ素子と第2のスイッチ素子からなる一対のスイッチ素子と、制御信号に応じて、前記第1及び第2のスイッチ素子を相補的にオンオフ制御する制御回路と、第1のスイッチ素子と前記第2のスイッチ素子との接続点の電位を平滑化する平滑回路とを有し、制御回路は、第2の電位を検出して、検出した電位と第1の基準電位とを比較して誤差信号を得て、誤差信号を基に第2の電位が所定の電圧になるように第1及び第2のスイッチ素子をオンオフ制御する機能を備え、 さらに、制御回路は、第2の電位出力の負荷電流が軽負荷となり、誤差信号が第2の基準電位を越えた場合に、第2のスイッチ素子をオフ状態にするように構成され、 第2の電位出力の負荷電流が軽負荷の時に、第1のスイッチ素子と第2のスイッチ素子との接続点の電位を第3の基準電位と第4の基準電位とで比較する比較器と、第1のスイッチ素子がオフ状態の時に、比較器からの出力信号をカウントするカウンタを有し、カウンタのカウント数がゼロになったことを検出して第2のスイッチ素子の駆動回路動作を無効から有効にすることを特徴とする。

また、平滑回路は、インダクタとコンデンサとの直列回路から構成され、インダクタとコンデンサの接続点が第2の電位を出力する端子に接続され、比較器は、第1のスイッチ素子と第2のスイッチ素子との接続点の電位に生じる振動電圧波形をパルス信号に変換出力し、第1のスイッチ素子のオフ期間にカウンタ回路でパルス信号をカウントすることを特徴とする。

また、第2の電位の設定電圧に合わせて、第3の基準電位と第4の基準電位とを可変することを特徴とする。

【発明の効果】

【0014】

本発明によれば、第2の電位出力の負荷電流が軽負荷から重負荷に変わる時に、第1のスイッチ素子と第2のスイッチ素子との接続点の電位を第3と第4の基準電位とで比較してパルス信号に変換出力し、第1のスイッチ素子のオフ期間にカウンタ回路でパルス信号がゼロになったことを検出することで、平滑回路に流れる電流の向きを測定せずに、第2のスイッチ素子のオンオフ動作による同期整流のオフ状態を有効にすることができる。

【図面の簡単な説明】

【0015】

【図1】本発明の実施例に係るDC‐DCコンバータの制御回路の構成を示す図である。

【図2】本発明の実施例に係るDC‐DCコンバータの動作を示すタイミングチャートである。

【図3】本発明の実施例に係る同期整流オフ選択回路である。

【図4】本発明の実施例に係る出力電流Ioとフィードバック信号FB電圧との関係を示した特性図である。

【図5】本発明の実施例に係るパルス成型回路の構成図である。

【図6】従来のDC‐DCコンバータの構成を示す図である。

【図7】従来のDC‐DCコンバータの動作を示すタイミングチャートである。

【発明を実施するための形態】

【0016】

以下、本発明の実施の形態に係るDC-DCコンバータを、図面を参照しながら詳細に説明する。

【0017】

本発明においては、同期整流方式のDC−DCコンバータにおいて、軽負荷時の平滑回路のインダクタに流れる電流が臨界電流以下になると自由振動をおこして出力から同期整流の第2のスイッチ素子を介して逆電流が流れることを防止するものである。

まず、軽負荷時の平滑回路のインダクタに流れる電流が臨界電流以下になる前に、DC−DCコンバータの制御回路の誤差信号電圧を基に軽負荷であることを判断して同期整流のスイッチ素子の動作をオフ状態にする。

次に、軽負荷状態から定格負荷ないし重負荷の方に変化したときには、平滑回路に流れる電流の向きを測定せずに、第1のスイッチ素子と第2のスイッチ素子との接続点の電位を第3と第4の基準電位とで比較してパルス信号に変換出力し、第1のスイッチ素子のオフ期間にカウンタ回路でパルス信号がゼロになったことを検出することで、第2のスイッチ素子の同期整流の機能をオフ状態からオン状態にすることができる。

【実施例】

【0018】

図1は、本発明の実施例に係るDC-DCコンバータの制御回路の構成を示す図である。

なお、図1においては、図6に示す従来のDC-DCコンバータと同一部分には同一符号を付しその説明を省略し、図6に示す従来のDC-DCコンバータと異なる部分を説明する。

【0019】

本発明の実施例に係るDC-DCコンバータは、図6に示した従来のDC-DCコンバータに、制御回路1aのスイッチ制御部10aが変更されている。

【0020】

図1に示す制御回路1aは、PWM発振器20、エラーAMP30、スイッチ制御部10aから構成され、PWM発振器20のPWM信号とエラーAMP30の出力信号を基に、スイッチ制御部10aを介してスイッチQ1,スイッチQ2のオンオフ駆動信号を出力する。

スイッチ制御部10aは、同期整流オフ選択回路11、Toff期間生成部12、パルス成型回路13、カウンタ14、時間差比較/不連続検出信号生成部15、1パルス・ラッチ16、OR回路17、INV回路18、スイッチSW19から構成されている。

スイッチ制御部10aは、エラーAMP30のフィードバック信号FBから軽負荷を検出してスイッチQ2の同期整流をオフにし、スイッチQ1、Q2の接続点電位V1を検出して軽負荷に発生する自由振動電圧をパルスに成型後、スイッチQ1のオフ期間中のカウンタ回路でのパルスカウントがゼロになったことを検出することで、スイッチQ2の同期整流をオフ状態からオン状態に戻す。

【0021】

図1に示すように同期整流オフ選択回路11は、エラーAMP30の出力であるフィードバック信号FBを入力し、フィードバック信号FBの電圧が基準電圧Vlightよりも低い場合にHレベル信号をOR回路17の一方の端子へ出力する。この同期整流オフ選択回路11については、後に詳細に説明する。

Toff期間生成部12は、PWM発振器20の出力信号を基にToff期間の信号を生成し、カウンタ14へカウンタ・リセット信号及び、時間差比較/不連続検出信号生成部15へToff期間の信号を送出する。

パルス生成回路13は、スイッチQ1,スイッチQ2との接続点V1の電位v1信号を入力して、V1の電位に生じる振動電圧波形をパルス信号に変換出力してカウンタ14へ出力する。このパルス生成回路13については、後に詳細に説明する。

カウンタ14は、Toff期間生成部12からのカウンタ・リセット信号によりリセットされて、パルス生成回路からのパルス信号を待受けする。

時間差比較/不連続検出信号生成部15は、Toff期間生成部12からのToff期間内にカウンタ14からパルスが入力されるか否かを検出し、パルスを検出すると出力信号を1パルス・ラッチ回路16へ出力する。1パルス・ラッチ回路16はPWM発振器20の出力信号の1周期分T、前述の時間差比較/不連続検出信号生成部15からの信号によりLレベル信号をOR回路17の他方の端子へ出力する。

【0022】

OR回路17は、1パルス・ラッチ回路16または同期整流オフ選択回路11から送られてくるLレベル信号に応じて、NMOS駆動信号Vdlを、スイッチ(SW)19を介してオフ信号へ切り替える。

これにより、軽負荷時の場合にはスイッチQ2はオン動作しないモードになる。

【0023】

次に、このように構成される実施例に係るDC-DCコンバータの動作を、図2に示すタイミングチャートを参照しながら説明する。

図2に示したタイミングチャートでは、同期整流オフ選択回路11からの切替信号が、一旦軽負荷と判定された信号を出力した後、カウンタ14がパルス成型回路信号のパルスをカウントする毎に不連続検出信号をLレベル出力し、スイッチ(SW)19をオフする状態を示している。

【0024】

図2のタイミングチャートにおけるインダクタ5に流れる電流IL波形(1)は、周期T期間の時刻t1〜t2にスイッチQ1からのオン電流が流れ、時刻t2〜t3間に回生電流が流れる。時刻t3にて電流は不連続となり、時刻t4まで流れない。

図2(2)に示すスイッチQ1とスイッチQ2との接続点V1の電位v1波形は、時刻t1〜t2にスイッチQ1からのオン電圧が印加され、時刻t2〜t3間にスイッチQ2のボディダイオードを介して回生電流が流れる。ここで、時刻t3〜t4期間はインダクタ5による自由振動電圧が生じる。

【0025】

図2(3)に示すToff期間生成部12のToff期間生成は、制御回路1aのPWM信号からToff期間波形を生成する。また、(4)に示すToff期間生成部の(A)に示す波形は、スイッチQ1のオン時の立ち上がりにターンオン検出を行い、ワンショットパルスを出力する。同様に(5)に示すToff期間生成部の(B)に示す波形は、スイッチQ1のオン時の立ち下がりにターンオフ検出を行い、ワンショットパルスを出力する。

前述のターンオン検出及びターンオフ検出でのワンショットパルスは、各々カウンタ14及び時間差比較/不連続検出信号生成部15に出力され、カウンタ14のカウンタリセット・パルス及び、カウント開始、また時間差比較/不連続検出信号生成部15のToff期間信号となる。

すなわち、カウンタ14は前述のターンオフ検出でカウントを開始し、前述のターンオン検出でカウントをリセットする。

【0026】

図2(7)に示すパルス生成回路信号は、時刻t3〜t4期間にv1波形の自由振動電圧波形を基準電圧Vth(H)と基準電圧Vth(L)とで比較して生成されたパルスである。時刻aにてv1波形の自由振動電圧が基準電圧Vth(H)を超えるとHレベルを出力し、時刻bにてv1波形の自由振動電圧が基準電圧Vth(L)未満になるとLレベルを出力する。以降、時刻b〜fにおいても同様に出力する。

すなわち、インダクタ5に流れる電流IL波形が不連続となるとv1波形の自由振動電圧波形を介してパルスとして出力される。

このパルス生成回路の構成例の詳細は、後述する。

【0027】

時間差比較/不連続検出信号生成部15は、Toff期間の時刻とパルス生成回路の出力とを比較して、インダクタ5に流れる電流IL波形の不連続検出信号の有無を検出し、不連続検出信号が有った時点でLレベルを1パルス・ラッチ回路16へ出力する。図2(8)では、時刻aにてパルス生成回路のパルスを検出してLレベルになっている。ここで、 時間差比較/不連続検出信号生成部15はToff期間の開始とともにリセットされ、出力はHレベルに戻る。

【0028】

1パルス・ラッチ回路16は、時間差比較/不連続検出信号生成部15の信号を時刻t1あるいは時刻t4で取り込みラッチしてOR回路17の他方の入力端子へ出力する。OR回路17は、Lレベル信号をスイッチ(SW)19に出力して、オフとする。図2(9)では、オフ状態が継続している様を示している。すなわち、時刻t3〜t4間に不連続検出信号が発生した場合、次のスイッチング周期におけるスイッチQ2による同期整流動作を停止させる。

【0029】

図3は本発明の実施例に係る制御部の同期整流オフ選択回路11を示したものである。同期整流オフ選択回路11は、コンパレータCPoffと基準電圧Vlightからなり、コンパレータCPoffの非反転端子はエラーAMP2の出力に接続され、フィードバック電圧FBが入力される。反転端子には基準電圧Vlightの正極が接続され、基準電圧Vlightの負極はグランドに接地されている。

【0030】

図4は本発明の実施例に係る出力電流Ioとフィードバック信号FB電圧との関係を示した特性図である。図4に示す特性図を参照しながら同期整流オフ選択回路11の動作について説明する。

図4は、出力電流Ioに対する誤差増幅器エラーAMPのフィードバック信号FB電圧の変化を示した特性図である。フィードバック信号FB電圧は出力電流Ioに対して比例する関係にあることがわかる。

すなわち、インダクタ5に流れるILの不連続電流ポイントとなる出力電流Ioがわかれば、フィードバック信号FB電圧でも検出することが可能である。

この特性を利用して、同期整流オフ選択回路11は、インダクタ5に流れるILの不連続電流ポイントとなるフィードバック信号FB電圧値を基準電圧Vlightとして事前に設定することで、コンパレータCPoffの非反転端子電圧とを比較して、不連続電流状態か否かを検出する。コンパレータCPoffの非反転端子電圧が基準電圧Vlight未満の場合にはLレベルを出力する。これにより、同期整流動作はオフが選択されることになる。

【0031】

図5は本発明の実施例に係る制御部のパルス成型回路の構成図である。図5に示すパルス成型回路は、フリップフロップ回路FF1とコンパレータCP(H)、CP(L)と基準電圧Vth(H)、Vth(L)と抵抗R11,R12からなる。

スイッチQ1とスイッチQ2との接続点V1とグランド間に抵抗R11とR12との直列回路が接続されている。抵抗R11とR12の接続端子には、コンパレータCP(H)の非反転端子とコンパレータCP(L)の反転端子とが接続されている。コンパレータCP(H)の反転端子には、基準電圧Vth(H)の正電極が接続され、負電極はグランドに接地されている。また、コンパレータCP(L)の非反転端子には基準電圧Vth(L)の正電極が接続され、負電極はグランドに接地されている。

コンパレータCP(H)の出力端子はフリップフロップ回路FF1のセット端子Sに接続され、コンパレータCP(L)の出力端子はフリップフロップ回路FF1のリセット端子Rに接続され、フリップフロップ回路FF1の出力Qは、パルス成型信号として出力される。また、基準電圧Vth(H)とVth(L)の電圧関係は、Vth(H)>Vth(L)の設定がされている。

【0032】

パルス成型回路の動作について、以下に詳細を述べる。

コンパレータCP(H)及びCP(L)はスイッチQ1とスイッチQ2の接続点V1の電位v1を抵抗R11とR12とで分圧した電圧V1pと基準電圧Vth(H)とVth(L)と各々比較する。

図2の(2)V1波形と(7)パルス成型回路信号で示されるように、時刻t3〜t4においてインダクタ5の自由振動波形が発生すると、時刻aにて電圧V1pは基準電圧Vth(H)を超えるのでコンパレータCP(H)はHレベルを出力し、フリップフロップ回路FF1はセットさせてHレベル信号を出力する。また、時刻bにおいて電圧V1pは基準電圧Vth(L)より低下するのでコンパレータCP(L)はHレベルを出力し、フリップフロップ回路FF1はリセットされてLレベル信号を出力する。すなわち、v1波形の自由振動電圧(V1p)は、基準電圧Vth(H)とVth(L)をもとにパルス成型されることになる。

【0033】

以上のように、スイッチ制御部10aは、エラーAMP30のフィードバック信号FB電圧から軽負荷を検出してスイッチQ2の同期整流をオフにする。また、スイッチQ1、Q2の接続点V1の電位v1を検出して、軽負荷に発生する自由振動電圧をパルス信号に成型後、スイッチQ1のオフ期間にカウンタ回路で前述のパルスがゼロになったことを検出することで、スイッチQ2の同期整流をオフ状態からオン状態に戻す。これにより、インダクタ5の電流ILのピーク電流もしくは平均値をシャント抵抗或いはセンスMOSFET等で直接検出しないで軽負荷/重負荷を判断し、かつ軽負荷時に逆電流を流すことなく、簡素な構成で同期整流スイッチの切り替え動作を行うことが可能なDC‐DCコンバータを提供することができる。

【産業上の利用可能性】

【0034】

本発明は、軽負荷時の効率が要求されるDC‐DCコンバータに適用可能である。

【符号の説明】

【0035】

Q1 スイッチ(PMOSトランジスタ)

Q2 スイッチ(NMOSトランジスタ)

FF1 フリップフロップ回路

CP、CPoff、CP(H)、CP(L) コンパレータ

R11,R12 抵抗

Vref、Vlight、Vth(H)、Vth(L) 基準電圧

1 、1a 制御回路

3 スイッチング部

4 平滑回路

5 インダクタ

8 負荷回路

10、10a スイッチ制御部

11 同期整流オフ選択回路

12 Toff期間生成回路

13 パルス成型回路

14 カウンタ

15 時間差比較/不連続検出信号部

16 1パルス・ラッチ

17 OR回路

18 インバータ回路

19 スイッチ(SW)

20 PWM発振器

30 エラーAMP

【特許請求の範囲】

【請求項1】

第1の電位を供給する第1の電源から、前記第1の電位よりも低い第2の電位を出力する同期整流方式のDC−DCコンバータにおいて、

前記第1の電位を供給する前記第1の電源とグランド間に直列に設けられた第1のスイッチ素子と第2のスイッチ素子からなる一対のスイッチ素子と、

制御信号に応じて、前記第1及び第2のスイッチ素子を相補的にオンオフ制御する制御回路と、

前記第1のスイッチ素子と前記第2のスイッチ素子との接続点の電位を平滑化する平滑回路とを有し、

前記制御回路は、前記第2の電位を検出して、検出した電位と第1の基準電位とを比較して誤差信号を得て、前記誤差信号を基に前記第2の電位が所定の電圧になるように前記第1及び第2のスイッチ素子をオンオフ制御する機能を備え、

さらに、前記制御回路は、第2の電位出力の負荷電流が軽負荷となり、前記誤差信号が第2の基準電位を越えた場合に、前記第2のスイッチ素子をオフ状態にするように構成され、

前記第2の電位出力の負荷電流が軽負荷の時に、前記第1のスイッチ素子と前記第2のスイッチ素子との接続点の電位を第3の基準電位と第4の基準電位とで比較する比較器と、第1のスイッチ素子がオフ状態の時に、前記比較器からの出力信号をカウントするカウンタを有し、

前記カウンタのカウント数がゼロになったことを検出して第2のスイッチ素子の駆動回路動作を無効から有効にすることを特徴とするDC−DCコンバータ。

【請求項2】

前記平滑回路は、インダクタとコンデンサとの直列回路から構成され、前記インダクタと前記コンデンサの接続点が前記第2の電位を出力する端子に接続され、

前記比較器は、前記第1のスイッチ素子と前記第2のスイッチ素子との接続点の電位に生じる振動電圧波形をパルス信号に変換出力し、

前記第1のスイッチ素子のオフ期間に前記カウンタ回路で前記パルス信号をカウントすることを特徴とする請求項1記載のDC−DCコンバータ。

【請求項3】

前記第2の電位の設定電圧に合わせて、前記第3の基準電位と第4の基準電位とを可変することを特徴とする請求項1記載のDC−DCコンバータ。

【請求項4】

前記第1及び第2のスイッチ素子と、前記平滑回路と、前記制御回路と、前記比較器と、前記カウンタとを基板上に集約して、一つのモールド樹脂で覆われた集積回路としたことを特徴とする請求項2記載のDC−DCコンバータ。

【請求項1】

第1の電位を供給する第1の電源から、前記第1の電位よりも低い第2の電位を出力する同期整流方式のDC−DCコンバータにおいて、

前記第1の電位を供給する前記第1の電源とグランド間に直列に設けられた第1のスイッチ素子と第2のスイッチ素子からなる一対のスイッチ素子と、

制御信号に応じて、前記第1及び第2のスイッチ素子を相補的にオンオフ制御する制御回路と、

前記第1のスイッチ素子と前記第2のスイッチ素子との接続点の電位を平滑化する平滑回路とを有し、

前記制御回路は、前記第2の電位を検出して、検出した電位と第1の基準電位とを比較して誤差信号を得て、前記誤差信号を基に前記第2の電位が所定の電圧になるように前記第1及び第2のスイッチ素子をオンオフ制御する機能を備え、

さらに、前記制御回路は、第2の電位出力の負荷電流が軽負荷となり、前記誤差信号が第2の基準電位を越えた場合に、前記第2のスイッチ素子をオフ状態にするように構成され、

前記第2の電位出力の負荷電流が軽負荷の時に、前記第1のスイッチ素子と前記第2のスイッチ素子との接続点の電位を第3の基準電位と第4の基準電位とで比較する比較器と、第1のスイッチ素子がオフ状態の時に、前記比較器からの出力信号をカウントするカウンタを有し、

前記カウンタのカウント数がゼロになったことを検出して第2のスイッチ素子の駆動回路動作を無効から有効にすることを特徴とするDC−DCコンバータ。

【請求項2】

前記平滑回路は、インダクタとコンデンサとの直列回路から構成され、前記インダクタと前記コンデンサの接続点が前記第2の電位を出力する端子に接続され、

前記比較器は、前記第1のスイッチ素子と前記第2のスイッチ素子との接続点の電位に生じる振動電圧波形をパルス信号に変換出力し、

前記第1のスイッチ素子のオフ期間に前記カウンタ回路で前記パルス信号をカウントすることを特徴とする請求項1記載のDC−DCコンバータ。

【請求項3】

前記第2の電位の設定電圧に合わせて、前記第3の基準電位と第4の基準電位とを可変することを特徴とする請求項1記載のDC−DCコンバータ。

【請求項4】

前記第1及び第2のスイッチ素子と、前記平滑回路と、前記制御回路と、前記比較器と、前記カウンタとを基板上に集約して、一つのモールド樹脂で覆われた集積回路としたことを特徴とする請求項2記載のDC−DCコンバータ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−110943(P2013−110943A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−256543(P2011−256543)

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

[ Back to top ]