DC/DC電圧変換装置

【課題】従来のDC/DC電圧変換装置と比較して効率の改善と出力電力容量の増大を達成しつつ、力行動作時と回生動作時の何れも、一次側電圧と二次側電圧の間を昇圧にも降圧にも調整可能であって、更に、小型化、軽量化を確保したDC/DC電圧変換装置を提供することを目的とする。

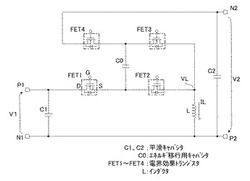

【解決手段】ワイドバンドギャップの半導体材料からなる電界効果トランジスタFET1〜FET4、インダクタL、エネルギ移行用キャパシタC0、平滑キャパシタC1、C2を備えた変換主回路2、およびFET1とFET4およびFET2とFET3をそれぞれ組として各組の一対のFETをオンオフが互いに反対となる相補の関係を持つように、かつ可聴周波数の上限以上のスイッチング周波数でFET1〜FET4をオンオフして各FETのオンデューティを制御することにより、一次側と二次側との間で双方向に電力を授受して昇降圧の直流電圧変換を行う制御ユニットを備えた。

【解決手段】ワイドバンドギャップの半導体材料からなる電界効果トランジスタFET1〜FET4、インダクタL、エネルギ移行用キャパシタC0、平滑キャパシタC1、C2を備えた変換主回路2、およびFET1とFET4およびFET2とFET3をそれぞれ組として各組の一対のFETをオンオフが互いに反対となる相補の関係を持つように、かつ可聴周波数の上限以上のスイッチング周波数でFET1〜FET4をオンオフして各FETのオンデューティを制御することにより、一次側と二次側との間で双方向に電力を授受して昇降圧の直流電圧変換を行う制御ユニットを備えた。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一次側と二次側の間で双方向に電力を授受させつつ、直流電圧を昇圧あるいは降圧した直流電圧に変換するDC/DC電圧変換装置に関するものである。

【背景技術】

【0002】

従来から、直列接続した半導体スイッチ素子のスイッチオン、スイッチオフ動作を利用して、インダクタへのエネルギの蓄積、放出とエネルギ移行用キャパシタの充電、放電との動作を組み合わせ、直流から直流への電圧変換を行う装置が用いられている(特許文献1、非特許文献1)。

これは、半導体スイッチ素子およびこれと逆並列に整流素子を接続したパワーデバイスを、同時には半数のパワーデバイスのみオン状態(半導体スイッチ素子ならばスイッチオン、整流素子ならば順バイアス)とするものであって、個々のパワーデバイスの耐電圧を低く設定することができる。このため、耐電圧が高いことに起因して各パワーデバイスの導通損失が増加してしまうのを抑えつつ、DC/DC電圧変換装置の取り扱い電圧を高電圧に設定可能である。

【0003】

ここで、商用交流電源(AC100V、AC200V)を整流した後の電圧を変換するDC/DC電圧変換装置や、およそ100Vから1,000Vの範囲の電圧を変換する出力電力容量が4kW程度以上のDC/DC電圧変換装置には、パワーデバイスとして主に半導体スイッチ素子にはSi(珪素)を材料としたIGBT(絶縁ゲート バイポーラ トランジスタ:Insulated Gate Bipolar Transistor)が、また、整流素子には同じくSiを材料としたPINダイオードが用いられている。

このようなDC/DC電圧変換装置は、直流を交流に変換するインバータと組み合わせてシステムが構成される場合があり、例えば、図31に示すハイブリッド自動車や電気自動車の電気駆動システム、図32に示す太陽光発電用の電力変換システム、エアーコンディショナ等の電力変換システムが挙げられる。

【0004】

図31の電気駆動システムは、DC/DC電圧変換装置1の一次側端子P1、N1にニッケル水素電池やリチウムイオン電池、燃料電池などの直流電源となる電池41を、二次側端子P2、N2にインバータ51a、51bを接続している。更に、インバータ51aには回転電機52aが、インバータ51bには回転電機52bがそれぞれ接続されている。回転電機52a、52bは車両の駆動力源となる。

DC/DC電圧変換装置1は、一次側の電池41の電圧をDC/DC電圧変換して二次側のインバータ51a、51bに供給する。インバータ51aは回転電機52aと、インバータ51bは回転電機52bとそれぞれ交流電力を授受する。

【0005】

図32の太陽光発電用電力変換システムは、DC/DC電圧変換装置1の一次側端子P1、N1に太陽電池42を、また、二次側端子P2、N2にインバータ51cを接続している。インバータ51cは、フィルタ6を介して商用交流電源7に接続しており、DC/DC電圧変換装置1は一次側の太陽電池42の発電電圧をDC/DC電圧変換して二次側のインバータ51cに供給する。インバータ51cは、直流電圧を所定の商用交流電圧の振幅、周波数にDC/AC変換して商用電力系統に供給する。

これらシステムに用いられるDC/DC電圧変換装置は、電源の状態(例えば、太陽光発電システムの太陽電池の光の照射量)や負荷の状態(例えば、ハイブリッド自動車の電気駆動システムの回転電機の回転速度)に応じて、変換する電圧の比率を調整し、その出力電圧をコントロールしている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開昭62−53171号公報

【非特許文献】

【0007】

【非特許文献1】三菱電機技報 Vol.61 1987年 No.2

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、上記した従来のDC/DC電圧変換装置において、次のような3つの課題があった。

第1に、一次側から二次側へ電力を送り込む力行動作時には、二次側電圧を一次側電圧よりも高く調整する昇圧動作はできるものの、二次側電圧を一次側電圧よりも低く調整する降圧動作は不可であり、昇降圧動作を同時には行えなかった。また、二次側から一次側へ電力を回収する回生動作時にも、一次側電圧を二次側電圧よりも低く調整する降圧動作(一次側から見れば昇圧動作)はできるものの、一次側電圧を二次側電圧よりも高く調整する昇圧動作は不可であり、昇降圧動作を同時には行えなかった。

これは、例えば、一次側に充電可能な電池を接続し、二次側に発電動作をおこなう電気機器を接続して、二次側から一次側に電力を送って電池を充電しようとする場合に、二次側の電気機器の発電電圧が比較的高くなければ一次側の電池を充電する際の損失が大きくなり、エネルギの利用効率が低下してしまうという不都合を生じる。

【0009】

第2に、高い出力電力容量を得ようとすれば、各要素の発生損失やその冷却手段等の関係から装置が大型重量化するという課題があった。発生損失が大きい要素として、パワーデバイスが挙げられる。パワーデバイスである半導体スイッチ素子と整流素子の発生損失には、それぞれ次の成分がある。

半導体スイッチ素子には、スイッチオンでの電流導通時のオン抵抗分による導通損失とスイッチング損失が生じる。スイッチング損失は、スイッチオフからスイッチオンへの切替わり(ターンオン)、スイッチオンからスイッチオフへの切替わり(ターンオフ)時の過渡的な立上り、立下り変化における半導体スイッチ素子の両端の電圧と導通電流の積の時間積分である。

【0010】

また、整流素子には、順方向導通時のオン抵抗分による導通損失と逆回復時の逆回復損失が生じる。逆回復損失は、逆回復動作での過渡的な立上り、立下り変化における整流素子の両端電圧と逆回復電流の積の時間積分である。

このように、半導体スイッチ素子のスイッチング損失と整流素子の逆回復損失はスイッチングのタイミングで生じるものであり、スイッチング周波数に比例し、このスイッチング周波数の増大は、パワーデバイスの損失増大に結びつき冷却手段を大型化する。

スイッチング周波数が一定の場合、スイッチング損失を下げるためには、スイッチングの速度を速くすれば良いものの、これはパワーデバイスに導通する電流の変化速度を高めることから、パワーデバイスの電流導通路の配索導体に寄生するインダクタンス成分Lsによって大きなサージ電圧が生じることになり、パワーデバイスやキャパシタに高電圧がかかり、損傷する懸念がある。

【0011】

第3に、DC/DC電圧変換装置全体の容積や重量において、金属材料を用いる冷却ヒートシンクやインダクタが多くを占めているため、装置が大型重量化するという課題がある。

DC/DC電圧変換装置が高い出力電力容量を得ようとすれば、パワーデバイスの発生損失の増加に連れてパワーデバイスの半導体接合部温度が上昇するのを和らげるために、冷却ヒートシンクを大型化する必要がある。

また、出力電力容量が増すとインダクタの導通電流も増えるのに対し、大電流にてもインダクタのコアが磁気飽和せず所望のインダクタンス値を得るためには磁路の断面積を増すようコアを大型化し、また、インダクタの巻線の発熱増加を抑えるためには巻線の断面積を増して巻線の抵抗を下げる必要がある。

これら冷却ヒートシンクやインダクタは金属材料を多量に用いるが故に、樹脂材料と比較して相対的に比重が高く、重量が嵩むことへの影響が大きい。

【0012】

この発明は、以上のような従来の課題を同時に解決するためになされたものであり、従来のDC/DC電圧変換装置と比較して効率の改善と出力電力容量の増大を達成しつつ、力行動作時と回生動作時の何れも、一次側電圧と二次側電圧の間を昇圧にも降圧にも調整可能であって、更に、小型化、軽量化を確保したDC/DC電圧変換装置を提供することを目的とする。

【課題を解決するための手段】

【0013】

この発明に係るDC/DC電圧変換装置は、変換主回路と制御ユニットとを備え、一次側と二次側との間で双方向に電力を授受して昇降圧の直流電圧変換を行うDC/DC電圧変換装置であって、

主変換回路は、一次側の正極側端子と負極側端子との間に接続され一次側の電圧を平滑する一次側平滑キャパシタと、二次側の正極側端子と負極側端子との間に接続され二次側の電圧を平滑する二次側平滑キャパシタと、エネルギの蓄積、放出を行うエネルギ移行用キャパシタおよびインダクタと、オンオフのスイッチング動作と逆方向導通動作とが可能な半導体ユニットを2n(nは2以上の整数)個互いに直列に接続して一次側の正極側端子と二次側の負極側端子との間に接続してなるパワーモジュールとを備え、

一次側の負極側端子は二次側の正極側端子に接続され、

制御ユニットは、2n個の半導体ユニットを2個で一対となるn個の組に分け、各組を構成する一対の半導体ユニットのオンオフが互いに反対となる相補の関係を持つように、かつ、インダクタに流れる電流の交流成分が半導体ユニットをオンオフ制御するスイッチング周波数のn倍となるように制御し、

エネルギ移行用キャパシタは、半導体ユニットの内、一次側の正極側端子に直接接続される半導体ユニットと二次側の負極側端子に直接接続される半導体ユニットとを除いて、各組の一対の半導体ユニットにおける、一次側の正極側端子に最も近い端子と二次側の負極側端子に最も近い端子との間に接続し、

インダクタは、一対の半導体ユニットであって互いに直接接続されるものの当該接続点と一次側の負極側端子との間に接続するようにしたものである。

【発明の効果】

【0014】

この発明に係るDC/DC電圧変換装置は、以上のように、特にその制御ユニットが、2n個の半導体ユニットを2個で一対となるn個の組に分け、各組を構成する一対の半導体ユニットのオンオフが互いに反対となる相補の関係を持つように、かつ、インダクタに流れる電流の交流成分が半導体ユニットをオンオフ制御するスイッチング周波数のn倍となるように制御する。

従って、インダクタに流れる電流の周波数がスイッチング周波数の2倍以上に増大し、その交流成分(リップル成分)が低減するか、または、その必要なインダクタンスを低減することができ、いずれにしろ、インダクタの損失低減、小型化、それに伴う冷却ヒートシンクの小型化が実現する。

また、一次側から二次側に電力を供給する力行動作時と二次側から一次側に電力を供給する回生動作時のいずれの場合にも、二次側電圧と一次側電圧の間を昇圧、降圧の双方に直流電圧変換する事が可能となる。

【図面の簡単な説明】

【0015】

【図1】本発明によるDC/DC電圧変換装置のシステムの全体構成図である。

【図2】本発明によるDC/DC電圧変換装置の電力の流れを示す説明図である。

【図3】本発明による実施の形態1の変換主回路の接続構成を示す図である。

【図4】本発明による実施の形態1の力行降圧時(オンデューティ50%未満)の動作を説明する波形図である。

【図5】本発明による実施の形態1の力行昇圧時(オンデューティ50%以上)の動作を説明する波形図である。

【図6】本発明による実施の形態1の回生降圧時(オンデューティ50%未満)の動作を説明する波形図である。

【図7】本発明による実施の形態1の回生昇圧時(オンデューティ50%以上)の動作を説明する波形図である。

【図8】本発明による実施の形態1のキャパシタのインピーダンスの周波数特性を示す図である。

【図9】本発明による実施の形態1の制御ユニットと変換主回路の構成を示すブロック図である。

【図10】本発明によるオンデューティとDC/DC電圧変換比との関係を示す特性図である。

【図11】本発明による実施の形態1の変換主回路の図3とは異なる接続構成を示す図である。

【図12】本発明による実施の形態1の変換主回路の図3、図11とは異なる接続構成を示す図である。

【図13】本発明による実施の形態2の制御ユニットと変換主回路の構成を示すブロック図である。

【図14】本発明による実施の形態2のゲート駆動回路の詳細な構成を示すブロック図である。

【図15】本発明による実施の形態2のスイッチオフ回路の選択方法を説明する図である。

【図16】本発明による実施の形態2の電界効果トランジスタのターンオフ動作を説明する波形図である。

【図17】本発明による実施の形態3の変換主回路の接続構成を示す図である。

【図18】本発明による実施の形態3の制御ユニットの構成を示すブロック図である。

【図19】本発明による実施の形態3のスイッチング周波数とインダクタ、キャパシタ、半導体ユニットの発熱量との関係を示す説明図である。

【図20】本発明による実施の形態3の周波数調整器の詳細な構成を示すブロック図である。

【図21】本発明による実施の形態3の選択処理手段の処理を説明するフロー図である。

【図22】本発明による実施の形態4の変換主回路の接続構成を示す図である。

【図23】本発明による実施の形態4の力行降圧時(オンデューティ100/3%未満)の動作を説明する波形図である。

【図24】本発明による実施の形態4の力行降圧時(オンデューティ100/3%以上50%未満)の動作を説明する波形図である。

【図25】本発明による実施の形態4の力行昇圧時(オンデューティ50%以上100×(2/3)%未満)の動作を説明する波形図である。

【図26】本発明による実施の形態4の力行昇圧時(オンデューティ100×(2/3)%以上)の動作を説明する波形図である。

【図27】本発明による実施の形態4の回生降圧時(オンデューティ100/3%未満)の動作を説明する波形図である。

【図28】本発明による実施の形態4の回生降圧時(オンデューティ100/3%以上50%未満)の動作を説明する波形図である。

【図29】本発明による実施の形態4の回生昇圧時(オンデューティ50%以上100×(2/3)%未満)の動作を説明する波形図である。

【図30】本発明による実施の形態4の回生昇圧時(オンデューティ100×(2/3)%以上)の動作を説明する波形図である。

【図31】DC/DC電圧変換装置を用いた自動車用電気駆動システムの構成図である。

【図32】DC/DC電圧変換装置を用いた太陽光発電用の電力変換システムの構成図である。

【発明を実施するための形態】

【0016】

実施の形態1.

以下、本発明の実施の形態1のDC/DC電圧変換装置につき、図1から図12を用いて説明する。

図1は、本実施例によるシステムの全体構成を示すブロック図である。DC/DC電圧変換装置1は、変換主回路2と制御ユニット3とから構成されている。DC/DC電圧変換装置1は、電力経路の接続端子として変換主回路2の一次側に正極側端子P1、負極側端子N1、二次側に正極側端子P2、負極側端子N2を備えている。

図2は、本実施例によるDC/DC電圧変換装置1の一次側と二次側との間の電圧変換と電力の流れを模式的に図示したものである。DC/DC電圧変換装置1の一次側には端子P1、N1に直流電源4が、二次側には端子P2、N2に電気機器5が接続される。

図2において、直流電源4は、リチウムイオン電池やニッケル水素電池、鉛電池といった二次電池の他、太陽電池、燃料電池などの電源に電気二重層キャパシタや二次電池を組み合わせたものなどが想定される。電気機器5は、電気負荷を含んで発電装置や蓄電装置と組み合わさって成る機器である。

【0017】

DC/DC電圧変換装置1は、一次側端子電圧V1と二次側端子電圧V2について、その電圧がV1≦V2の関係、V1>V2の関係のいずれに対しても電流を双方向に導通可能なよう電圧変換を行い、相互に電力をやり取りする。

ここで、直流電源4が放電動作であり電気機器5が電力消費動作の場合、DC/DC電圧変換装置1は、図2(a)に示すように、電圧を昇圧して一次側から二次側の方向へ電力を送り込む場合と、図2(b)に示すように、電圧を降圧して電力を送り込む場合とがある。

また、直流電源4が充電動作であり電気機器5が電力供給動作の場合、DC/DC電圧変換装置1は、図2(c)に示すように、電圧を昇圧(一次側電圧V1を基準として二次側電圧V2はV1≦V2の関係)して二次側から一次側の方向へ電力を送り込む場合と、図2(d)に示すように、電圧を降圧(一次側電圧V1を基準として二次側電圧V2はV1>V2の関係)して電力を送り込む場合とがある。

この時、電圧の変換は制御ユニット3から出力されるゲート駆動信号8に従い、変換主回路2に備わる、後述する半導体ユニット内の半導体スイッチ素子のオン、オフを制御することによってなされる。

【0018】

ここで、DC/DC電圧変換装置1の動作内容について図3から図10を用いて説明する。図3は、変換主回路2の回路配線を示す図であり、4個の半導体ユニットを直列に接続し、一次側から二次側へ電圧を昇圧あるいは降圧して電力供給を、また、二次側から一次側へ電圧を降圧あるいは昇圧して電力供給を行う。

変換主回路2は、一次側端子電圧V1を平滑化する一次側平滑キャパシタC1と、二次側端子電圧V2を平滑化する二次側平滑キャパシタC2と、エネルギの蓄積、放出を行う、インダクタLおよびエネルギ移行用キャパシタC0と、4個の半導体ユニットを備えている。

【0019】

第1〜第4の半導体ユニットは、この図3の例では、寄生ダイオードを内部に含む電界効果トランジスタFET4、FET3、FET2、FET1を採用している。なお、これら電界効果トランジスタは、そのバンドギャップがシリコンのそれより大きいワイドバンドギャップ半導体で形成したものを採用しているが、この点については、後段で詳述するものとする。

【0020】

続けて、変換主回路2の接続の詳細について説明する。

平滑キャパシタC1の両端子は、変換主回路2の一次側の正極側端子P1、負極側端子N1に接続されており、負極側端子N1は変換主回路2の二次側の正極側端子P2とも接続されている。

正極側端子P1は、平滑キャパシタC1の一方の端子とFET1のドレイン端子に接続され、平滑キャパシタC1の他方の端子は負極側端子N1に接続される。

また、平滑キャパシタC2の両端子は、変換主回路2の二次側の正極側端子P2、負極側端子N2に接続されている。

【0021】

FET4のソース端子は変換主回路2の二次側の負極側端子N2に、ドレイン端子はFET3のソース端子に、FET3のドレイン端子はFET2のソース端子に、FET2のドレイン端子はFET1のソース端子に、それぞれ接続されている。

エネルギ移行用キャパシタC0は、一方の端子をFET4とFET3との接続点に、他方の端子をFET2とFET1との接続点に接続されている。

【0022】

なお、後段の動作説明で触れているように、この例では、FET1とFET4およびFET2とFET3とがそれぞれ組となり、各組をなす一対のFETは、いわゆる相補の関係を持つようにオンオフ制御される。従って、エネルギ移行用キャパシタC0は、一次側の正極側端子P1に直接接続されるFET1と二次側の負極側端子N2に直接接続されるFET4とを除いた、一対のFET2、FET3における、一次側の正極側端子P1に最も近い端子であるFET2のドレイン端子と二次側の負極側端子N2に最も近い端子であるFET3のソース端子との間に接続されているとも言える。

【0023】

インダクタLは、図3に示すように、一方の端子を変換主回路2の一次側の負極側端子N1に接続され、他方の端子を、上記した一対のFETであって互いに直接接続されているFET3とFET2との接続点に接続されている。

【0024】

図3には示されない制御ユニット3からは、ゲート駆動信号8として電界効果トランジスタをオン、オフ制御するための信号がFET4、FET3、FET2、FET1に対応して、それぞれGate4、Gate3、Gate2、Gate1信号としてFET4からFET1のゲート電極(G)に接続されている。FET4はGate4信号の、FET3はGate3信号の、FET2はGate2信号の、FET1はGate1信号の電圧変化にしたがって、スイッチング動作する。

【0025】

次に、変換主回路2の動作について説明する。

上述のように、DC/DC電圧変換装置1は、一次側から二次側へ、あるいは、二次側から一次側へ、電力を双方向に授受させつつ、一次側に対して二次側が昇圧動作、降圧動作のいずれにもなるよう電圧変換する。この昇圧動作、降圧動作は、電界効果トランジスタのオン、オフ動作のタイミングをゲート駆動信号8であるGate4、Gate3、Gate2、Gate1で調整することによって制御される。

このゲート駆動信号8による電圧変換の制御について、力行動作時と回生動作時とに分けて説明する。

【0026】

力行動作時:

1)オンデューティが50%未満で降圧動作の場合:

一次側から二次側へ電力を供給する力行動作時であって、二次側電圧V2<一次側電圧V1の降圧を行うオンデューティ50%未満の動作について説明する。

但し、オンデューティはGate1信号とGate2信号に対する値を言っており、Gate3信号とGate4信号はそれぞれGate2信号、Gate1信号と相補であるから、Gate3信号とGate4信号のオンデューティは、100%−(Gate2信号、Gate1信号のオンデューティ)の関係となる。

【0027】

図4に力行動作時の降圧動作でゲート駆動信号のオンデューティが50%未満の場合の波形を示す。図4で(a)は、ゲート駆動信号、(b)はインダクタ電流IL、(c)はスイッチングモードとその切替わりタイミングを示している。

インダクタ電流ILは、インダクタLをFET2側の接続端子から負極側端子N1側の接続端子の方向に流れる極性を正とする。

図4(a)において、Gate1信号がハイの場合にFET1が、Gate2信号がハイの場合にFET2がオンし、ドレインからソースに向けて電流が流れる。

【0028】

Gate3信号がハイの場合にFET3が、Gate4信号がハイの場合にFET4がオンするが、力行動作時には電流がソースからドレインに向けてFET3、FET4に内在する寄生ダイオードの替わりにトランジスタ部分を流れる。

この結果、当該部分での電圧降下が少なく、発生する損失がその分低減し効率が向上するという利点がある。この利点は、本願発明になる制御方式にあって、半導体ユニットに電界効果トランジスタFETを採用した場合に得られる効果である。

【0029】

ここで、Gate1信号とGate4信号は、互いにハイ、ローの論理が相反する相補信号であり、Gate1信号がハイの時にはGate4信号はロー、Gate1信号がローの時にはGate4信号はハイとなる。但し、ハイとローの論理の切替わり時は電界効果トランジスタのスイッチング動作の応答遅れにより双方が同時にオンとならないよう阻止時間(デッドタイム)を設ける。

同様に、Gate2信号とGate3信号は、互いにハイ、ローの論理が相反する相補信号であり、Gate1信号とGate2信号は位相差が180度である。即ち、ゲート駆動信号8は、相補信号として対を成す信号が二通り有って、互いの位相差が等間隔となっている。

【0030】

この時、Gate1からGate4のゲート駆動信号のハイ、ローの論理の組合わせは、スイッチングモードB、C、Dの三種に分類され B→D→C→D→B の順に切替わる。

【0031】

スイッチングモードBでは、FET1とFET3がオン、FET2とFET4がオフであって、

電流が、正極側端子P1→FET1→エネルギ移行用キャパシタC0→FET3→インダクタL→負極側端子N1の経路に流れ、エネルギがインダクタLとエネルギ移行用キャパシタC0に蓄えられる。電気機器5には、後述する動作で蓄電された平滑キャパシタC2の両端電圧が印加され、平滑キャパシタC2からエネルギが供給される。

FET1、FET3がオンして電流が導通することから、エネルギ移行用キャパシタC0のFET1側接続端子の電位はおよそV1、FET3側接続端子の電位はおよそインダクタLのFET3側接続端子の電圧VLとなる。インダクタLの他方は負極側端子N1に接続しており、電位は0(基準電位)である。

よって、インダクタLのFET3側接続端子の電圧VL=V1−Vc0 となる。但しVc0はエネルギ移行用キャパシタC0の両端電圧である。

【0032】

スイッチングモードDでは、FET3とFET4がオン、FET1とFET2がオフであって、

負極側端子N2→FET4→FET3→インダクタL→正極側端子P2→電気機器5→負極側端子N2の経路に電流が流れ、インダクタLに蓄積されたエネルギが放出される。

また、基準電位である一次側の負極側端子N1の電位に対して二次側の負極側端子N2は−V2であり、また、FET3とFET4に電流が導通し、ここでの電圧降下が僅かであるため、電圧VLは、およそ−V2となる。インダクタLのFET3側接続端子の電圧VLと正極側端子P2側接続端子の電圧の差は−V2で負となり、インダクタ電流ILはIL<0の方向へ向けて減少する。

【0033】

スイッチングモードCでは、FET2とFET4がオン、FET1とFET3がオフであって、

電流が、負極側端子N2→FET4→エネルギ移行用キャパシタC0→FET2→インダクタL→正極側端子P2→電気機器5→負極側端子N2の経路に電流が流れ、エネルギがインダクタLに蓄えられ、エネルギ移行用キャパシタC0から放出される。また、同時に平滑キャパシタC2にも電流が流れてエネルギが蓄えられる。

FET2、FET4がオンして電流が導通することから、エネルギ移行用キャパシタC0のFET2側接続端子の電位はおよそVL、FET4側接続端子の電位はおよそ−V2となる。よって、インダクタLのFET3側接続端子の電圧VL=−V2+Vc0 となる。

【0034】

ここで、Gate1信号とGate2信号のオンデューティは等しいため、スイッチングモードB、Cにおける電圧VLは時間平均的に等しく、V1−Vc0=−V2+Vc0の関係となる。よって、エネルギ移行用キャパシタC0の両端電圧Vc0は、一次側端子電圧V1と二次側端子電圧V2の和の1/2倍の、(V1+V2)/2となる。

【0035】

上記を整理すると、インダクタLのFET3側接続端子の電圧VLは、

スイッチングモードBでは、VL=V1−Vc0=(V1−V2)/2、

スイッチングモードCでは、VL=−V2+Vc0=(V1−V2)/2、

スイッチングモードDでは、VL=−V2

となる。

これより、インダクタLの両端の電位差と、FET1、FET2のスイッチオン時間ton、スイッチオフ時間toffは、次の関係で表される。

【0036】

スイッチングモードB、C:L・ILrpl=ton・(V1−V2)/2 ・(1a)

スイッチングモードD:L・ILrpl=−toff・(−V2) ・・(1b)

但し、Lは、インダクタLのインダクタンス、ILrplは、インダクタLに流れるリップル電流成分(交流電流成分)の振幅を示す。

【0037】

式(1a)と式(1b)の左辺同士が等しいことから、次の関係が成り立つ。

【0038】

ton・(V1−V2)/2=toff・V2 ・・・(2)

【0039】

上の式(2)を一次側端子電圧V1と二次側端子電圧V2について整理すると次のようになる。

【0040】

(V2/V1)=ton/(ton+toff+toff)=(ton/T)/(1−ton/T) ・・・(3)

但し、ton+toff=T/2

【0041】

上の式(3)で周期Tは、スイッチングモードB→D→C→D→Bの順に切替わって一周する期間を示しており、T/2=ton+toffである。

また、式(3)の左辺、V2/V1は、DC/DC電圧変換装置1の一次側電圧V1と二次側電圧V2との比率であり、DC/DC電圧変換比である。

図4に示される、ゲート駆動信号のオンデューティが50%未満の動作では、ton/T<0.5であり、式(3)に当てはめると、DC/DC電圧変換比は、1未満となる。よって、V2<V1の降圧動作である。

【0042】

これらから、スイッチングモードB、Cでは、インダクタLのFET3側接続端子の電圧VL=(V1−V2)/2>0、インダクタLの負極側端子N1側の接続端子の電圧が0である。よって、インダクタLの両端間の電位差は正となり、インダクタ電流ILは正の方向へ増加する。

【0043】

以上のように、スイッチングモードB→D→C→D→Bの切替わりにおいて、

スイッチングモードB、Cでは、インダクタ電流ILは、IL≧0の状態から更に正の方向に向けて変化し、

スイッチングモードDでは、インダクタ電流ILは、IL<0の状態に向けて変化する。

このことから、電界効果トランジスタのスイッチング周期Tに亘ってインダクタ電流ILの増加、減少はT/2周期で2回繰り返されることとなる。即ち、電界効果トランジスタのスイッチング周波数に対してインダクタLには2倍の周波数の交流電流が導通することとなる。

【0044】

2)オンデューティが50%以上で昇圧動作の場合:

次に、力行動作時であって、二次側電圧V2≧一次側電圧V1の昇圧を行うオンデューティ50%以上の動作について説明する。

図5は、当該時の動作波形を示しており、(a)はゲート駆動信号、(b)はインダクタ電流IL、(c)はスイッチングモードとその切替わりタイミングである。

図5(a)において、図4(a)と同様に、Gate1信号がハイの場合にFET1が、Gate2信号がハイの場合にFET2がオンし、ドレインからソースに向けて電流が流れる。

Gate3信号がハイの場合にFET3が、Gate4信号がハイの場合にFET4がオンするが、力行動作時には電流がソースからドレインに向けてFET3、FET4に内在する寄生ダイオードの替わりにトランジスタ部分を流れる。

【0045】

また、Gate1信号とGate4信号、Gate2信号とGate3信号はそれぞれ相補信号であり、ハイとローの論理の切替わり時に電界効果トランジスタのスイッチング動作の応答遅れにより双方が同時にオンとならないよう阻止時間(デッドタイム)を設ける。Gate1信号とGate2信号は位相差が180度である。

【0046】

この時、Gate1からGate4のゲート駆動信号のハイ、ローの論理の組合わせは、スイッチングモードA、B、Cの三種に分類され A→B→A→C→A の順に切替わる。

【0047】

先ず、スイッチングモードAでは、FET1とFET2がオン、FET3とFET4がオフであって、

電流が、正極側端子P1→FET1→FET2→インダクタL→負極側端子N1の経路に流れ、インダクタLにエネルギが蓄積される。

電圧VLは、FET1とFET2に電流が導通し、およそV1となることから、インダクタLのFET2側接続端子の電圧VLと負極側端子N1側の接続端子の電圧との差は、(V1−0)で正となり、インダクタ電流ILは正の方向へ増加する。

【0048】

スイッチングモードBでは、FET1とFET3がオン、FET2とFET4がオフであって、

電流が、正極側端子P1→FET1→エネルギ移行用キャパシタC0→FET3→インダクタL→負極側端子N1の経路に流れ、エネルギがエネルギ移行用キャパシタC0に蓄えられる。電気機器5には、後述する動作で蓄電された平滑キャパシタC2の両端電圧が印加され、平滑キャパシタC2からエネルギが供給される。

FET1、FET3がオンして電流が導通することから、エネルギ移行用キャパシタC0のFET1側接続端子の電位は、およそV1、FET3側接続端子の電位は、およそVLとなる。

よって、インダクタLのFET3側接続端子の電圧VL=V1−Vc0となる。

【0049】

スイッチングモードCでは、FET2とFET4がオン、FET1とFET3がオフであって

電流が、二次側の負極側端子N2→FET4→エネルギ移行用キャパシタC0→FET2→インダクタL→正極側端子P2→電気機器5→負極側端子N2の経路に流れ、エネルギがインダクタLとエネルギ移行用キャパシタC0から放出される。また、同時に平滑キャパシタC2にも電流が流れてエネルギが蓄えられる。

FET2、FET4がオンして電流が導通することから、エネルギ移行用キャパシタC0のFET2側接続端子の電位は、およそVL、FET4側接続端子の電位は、およそ−V2となる。

よって、インダクタLのFET3側接続端子の電圧VL=−V2+Vc0となる。

【0050】

また、上述のオンデューティが50%未満の動作と同様に、Gate1信号とGate2信号のオンデューティは等しいため、スイッチングモードB、Cにおける電圧VLは、時間平均的に等しく V1−Vc0=−V2+Vc0 の関係となる。よって、エネルギ移行用キャパシタC0の両端電圧Vc0は、一次側端子電圧V1と二次側端子電圧V2の和の1/2倍の、(V1+V2)/2となる。

【0051】

上記を整理すると、インダクタLのFET3側接続端子の電圧VLは、

スイッチングモードAでは、VL=V1、

スイッチングモードBでは、VL=V1−Vc0=(V1−V2)/2、

スイッチングモードCでは、VL=−V2+Vc0=(V1−V2)/2

となる。

これより、インダクタLの両端の電位差と、FET1、FET2のスイッチオン時間ton、スイッチオフ時間toffは、次の関係で表される。

【0052】

スイッチングモードA:L・ILrpl=V1・(ton−toff)/2・・(4a)

スイッチングモードB、C:L・ILrpl=−toff・(V1−V2)/2

・・(4b)

【0053】

式(4a)と式(4b)の左辺同士が等しいことから、次の関係が成り立つ。

【0054】

V1・(ton−toff)/2=−toff・(V1−V2)/2 ・・(5)

【0055】

上の式(5)を一次側端子電圧V1と二次側端子電圧V2について整理すると次のようになる。

【0056】

(V2/V1)=ton/toff=(ton/T)/(1−ton/T)・・(6)

但し、ton+toff=T

【0057】

上の式(6)で、周期Tは、スイッチングモードA→B→A→C→Aの順に切替わって一周する期間を示しており、T=ton+toffである。

式(6)は、式(3)と等しいものであり、即ち、オンデューティが50%未満であっても50%以上であっても無関係にオンデューティの変化に合わせて連続的にDC/DC電圧変換比は調整される。

なお、図5に示されるゲート駆動信号のオンデューティが50%以上の動作では、ton/T≧0.5であり、式(6)に当てはめると、DC/DC電圧変換比は、1以上となる。よって、V2≧V1の昇圧動作である。

【0058】

これらから、スイッチングモードB、Cでは、インダクタLのFET3側接続端子の電圧VL=(V1−V2)/2<0、インダクタLの負極側端子N1側接続端子の電圧が0である。よって、インダクタLの両端間の電位差は負となり、インダクタ電流ILは負の方向へ減少する。

【0059】

以上のように、スイッチングモードA→B→A→C→Aの切替わりにおいて、

スイッチングモードAでは、インダクタ電流ILは、IL≧0の状態から更に正の方向に増加するよう変化し、

スイッチングモードB、Cでは、インダクタ電流ILは、IL<0の状態に向けて変化する。

このことから、電界効果トランジスタのスイッチング周期Tに亘ってインダクタ電流ILの増加、減少はT/2周期で2回繰り返されることとなる。即ち、ゲート駆動信号のオンデューティが50%以上である場合についても、電界効果トランジスタのスイッチング周波数に対してインダクタLには2倍の周波数の交流電流が導通することとなる。

【0060】

回生動作時:

1)オンデューティが50%未満で降圧動作の場合:

二次側から一次側へ電力を供給する回生動作時であって、一次側電圧V1>二次側電圧V2の降圧を行うオンデューティ50%未満の動作について説明する。なお、二次側電圧V2を基にすれば、(V1/V2)>1の関係の昇圧となる。

回生動作時の降圧動作では図2(d)に示すように、二次側電圧V2<一次側電圧V1の関係で、DC/DC電圧変換装置1の二次側に接続した電気機器5が発生する電力をV2からV1へDC/DC電圧変換して直流電源4で回収する。

図6に、降圧動作時でゲート駆動信号のオンデューティが50%未満の波形を図示する。図6で(a)は、ゲート駆動信号、(b)はインダクタ電流IL、(c)はスイッチングモードとその切替わりタイミングを示している。

【0061】

図6(a)において、Gate3信号がハイの場合にFET3が、Gate4信号がハイの場合にFET4がオンし、ドレインからソースに向けて電流が流れる。Gate1信号がハイの場合にFET1が、Gate2信号がハイの場合にFET2がオンするが、回生動作時には電流がソースからドレインに向けてFET1、FET2に内在する寄生ダイオードの替わりにトランジスタ部分を流れる。

図6(a)のゲート駆動信号と図6(c)のスイッチングモードとその切替わりタイミングは、力行動作時の降圧動作でゲート駆動信号のオンデューティが50%未満での、図4(a)、図4(c)と同じである。

即ち、力行動作時も回生動作時もゲート駆動信号は同じ波形であり、Gate1からGate4のゲート駆動信号のハイ、ローの論理の組合わせは、スイッチングモードB→D→C→D→Bの順に切替わる。

【0062】

スイッチングモードDでは、FET3とFET4がオン、FET1とFET2がオフであって、

電流が、正極側端子P2→インダクタL→FET3→FET4→負極側端子N2の経路に流れ、インダクタLにエネルギが蓄積される。その電流導通の方向から、インダクタ電流ILの極性は負である。

また、FET3とFET4がオンして電流が導通することから、電圧VLは、およそ−V2となる。

よって、インダクタLのFET3側接続端子の電圧と正極側端子P2側の接続端子の電圧との差は、(−V2−0)で負となり、インダクタ電流ILは、IL<0の状態から負方向へ増加する。

【0063】

スイッチングモードBでは、FET1とFET3がオン、FET2とFET4がオフであって、

電流が、インダクタL→FET3→エネルギ移行用キャパシタC0→FET1→正極側端子P1→直流電源4→負極側端子N1の経路に流れ、エネルギがインダクタLとエネルギ移行用キャパシタC0から放出される。また、平滑キャパシタC2には、電気機器5の発電電圧V2が印加され、平滑キャパシタC2にエネルギが供給される。

FET1、FET3がオンして電流が導通することから、エネルギ移行用キャパシタC0のFET1側接続端子の電位は、およそV1、FET3側接続端子の電位は、およそVLとなる。

よって、インダクタLのFET3側接続端子の電圧VL=V1−Vc0となる。

【0064】

スイッチングモードCでは、FET2とFET4がオン、FET1とFET3がオフであって、

電流が、正極側端子P2→インダクタL→FET2→エネルギ移行用キャパシタC0→FET4→負極側端子N2の経路に流れ、エネルギがインダクタLから放出され、エネルギ移行用キャパシタC0に蓄えられる。

FET2、FET4がオンして電流が導通することから、エネルギ移行用キャパシタC0のFET2側接続端子の電位は、およそVL、FET4側接続端子の電位は、およそ−V2となる。

よって、インダクタLのFET3側接続端子の電圧VL=−V2+Vc0となる。

【0065】

ここで、Gate3信号とGate4信号のオンデューティは等しいため、スイッチングモードB、Cにおける電圧VLは時間平均的に等しく、V1−Vc0=−V2+Vc0の関係となる。

よって、力行動作時と同様にエネルギ移行用キャパシタC0の両端電圧Vc0は、一次側端子電圧V1と二次側端子電圧V2の和の1/2倍の、(V1+V2)/2となる。

【0066】

上記を整理すると、インダクタLのFET3側接続端子の電圧VLは、

スイッチングモードBでは、VL=V1−Vc0=(V1−V2)/2、

スイッチングモードCでは、VL=−V2+Vc0=(V1−V2)/2、

スイッチングモードDでは、VL=−V2

となる。

これより、インダクタLの両端の電位差とFET1、FET2のスイッチオン時間ton、スイッチオフ時間toffは、力行動作時の降圧動作でゲート駆動信号のオンデューティが50%未満における関係を示す式(1a)、(1b)と同じとなる。

このため、同様に、式(2)、式(3)の関係が成り立つ。

即ち、DC/DC電圧変換装置1の電圧変換比(V2/V1)は、式(3)で示される。

【0067】

図6のゲート駆動信号のオンデューティが50%未満の動作では、ton/T<0.5であり、式(3)に当てはめるとDC/DC電圧変換比は、1未満となる。よって、V2<V1の降圧動作である。

即ち、一次側端子電圧V1は、二次側端子電圧V2より高い電圧へ変換される。

【0068】

これらから、スイッチングモードB、Cでは、インダクタLのFET3側接続端子の電圧VL=(V1−V2)/2 > 0、インダクタLの負極側端子N1側の接続端子の電圧が0である。よって、インダクタLの両端間の電位差は正となり、インダクタ電流ILは正の方向に向けて減少する。即ち、回生動作時でインダクタ電流IL<0の状態から、IL≧0の状態に向けてILは変化する。

【0069】

以上のように、スイッチングモードB→D→C→D→B の切替わりにおいて、

スイッチングモードB、Cでは、インダクタ電流ILは、IL≧0の状態に向けて変化し、

スイッチングモードDでは、インダクタ電流ILは、IL<0の状態から更に負の方向に増加するよう変化する。

このことから、電界効果トランジスタのスイッチング周期Tに亘ってインダクタ電流ILの増加、減少はT/2周期で2回繰り返されることとなる。即ち、力行動作時と同様に電界効果トランジスタのスイッチング周波数に対してインダクタLには2倍の周波数の交流電流が導通することとなる。

【0070】

2)オンデューティが50%以上で昇圧動作の場合:

次に、二次側から一次側へ電力を供給する回生動作時であって、一次側電圧V1≦二次側電圧V2の昇圧を行うオンデューティ50%以上の動作について説明する。なお、二次側電圧V2を基にすれば、(V1/V2)≦1の関係の降圧となる。

図7は、当該時の動作波形を示しており、(a)はゲート駆動信号、(b)はインダクタ電流IL、(c)はスイッチングモードとその切替わりタイミングである。

図7(a)において、Gate3信号がハイの場合にFET3が、Gate4信号がハイの場合にFET4がオンし、ドレインからソースに向けて電流が流れる。

Gate1信号がハイの場合にFET1が、Gate2信号がハイの場合にFET2がオンするが、回生動作時には電流がソースからドレインに向けてFET1、FET2に内在する寄生ダイオードの替わりにトランジスタ部分を流れる。

【0071】

図7(a)のゲート駆動信号と図7(c)のスイッチングモードとその切替わりタイミングは、力行動作時の昇圧動作でゲート駆動信号のオンデューティが50%以上での図5(a)、図5(c)と同じである。

即ち、力行動作時も回生動作時もゲート駆動信号は同じ波形であり、Gate1からGate4のゲート駆動信号のハイ、ローの論理の組合わせは、スイッチングモードA→B→A→C→A の順に切替わる。

【0072】

先ず、スイッチングモードCでは、FET2とFET4がオン、FET1とFET3がオフであって、

電流が、正極側端子P2→インダクタL→FET2→エネルギ移行用キャパシタC0→FET4→負極側端子N2の経路に流れ、エネルギがインダクタLとエネルギ移行用キャパシタC0に蓄えられる。

FET2、FET4がオンして電流が導通することから、エネルギ移行用キャパシタC0のFET2側接続端子の電位は、およそVL、FET4側接続端子の電位は、およそ−V2となる。

よって、インダクタLのFET2側接続端子の電圧VL=−V2+Vc0となる。

【0073】

スイッチングモードBでは、FET1とFET3がオン、FET2とFET4がオフであって、

電流が、インダクタL→FET3→エネルギ移行用キャパシタC0→FET1→正極側端子P1→直流電源4→負極側端子N1の経路に流れ、エネルギがインダクタLに蓄えられ、エネルギ移行用キャパシタC0から放出される。

FET1、FET3がオンして電流が導通することから、エネルギ移行用キャパシタC0のFET1側接続端子の電位は、およそV1、FET3側接続端子の電位は、およそVLとなる。

よって、インダクタLのFET3側接続端子の電圧VL=V1−Vc0となる。

【0074】

スイッチングモードAでは、FET1とFET2がオン、FET3とFET4がオフであって、

電流が、インダクタL→FET2→FET1→正極側端子P1→直流電源4→負極側端子N1の経路に流れ、エネルギがインダクタLから放出される。

電圧VLは、FET1とFET2に電流が導通し、およそV1となることから、インダクタLのFET2側接続端子の電圧VLと負極側端子N1側の接続端子の電圧との差は、(V1−0)=V1で正となり、インダクタ電流ILは、IL<0の状態から正の方向へ向けて変化する。

【0075】

また、上述の回生動作時の1)項 オンデューティが50%未満の動作と同様に、Gate3信号とGate4信号のオンデューティは等しいため、スイッチングモードB、Cにおける電圧VLは、時間平均的に等しく、V1−Vc0=−V2+Vc0の関係となる。

よって、降圧動作時と同様に、エネルギ移行用キャパシタC0の両端電圧Vc0は、一次側端子電圧V1と二次側端子電圧V2の和の1/2倍の、(V1+V2)/2となる。

【0076】

上記を整理すると、インダクタLのFET3側接続端子の電圧VLは、

スイッチングモードAでは、VL=V1、

スイッチングモードBでは、VL=V1−Vc0=(V1−V2)/2、

スイッチングモードCでは、VL=−V2+Vc0=(V1−V2)/2

となる。

これより、インダクタLの両端の電位差とFET1、FET2のスイッチオン時間ton、スイッチオフ時間toffの関係は、力行動作時の昇圧動作でゲート駆動信号のオンデューティが50%以上での関係を示す式(4a)、(4b)と同じとなる。このため、同様に式(5)、式(6)の関係が成り立つ。

即ち、DC/DC電圧変換装置1の電圧変換比(V2/V1)は、式(6)で示される。

【0077】

図7のゲート駆動信号のオンデューティが50%以上の動作では、ton/T≧0.5であり、式(6)に当てはめるとDC/DC電圧変換比は、1以上となる。よって、V2≧V1である。即ち、二次側端子電圧V2は一次側端子電圧V1よりも高い電圧の昇圧動作となる。

【0078】

これらから、スイッチングモードB、Cでは、インダクタLのFET3側接続端子の電圧VL=(V1−V2)/2<0、インダクタLの負極側端子N1側接続端子の電圧が0である。よって、インダクタLの両端間の電位差は負となり、インダクタ電流ILは負の方向に増加する。即ち、回生動作時でインダクタ電流IL<0の状態から、更に負の方向へ増加するよう変化する。

【0079】

上述のように、スイッチングモードA→B→A→C→A の切替わりにおいて、

スイッチングモードAでは、インダクタ電流ILは、IL≧0の状態に向けて変化し、

スイッチングモードB、Cでは、インダクタ電流ILは、IL<0の状態から更に負の方向に増加するよう変化する。

このことから、電界効果トランジスタのスイッチング周期Tに亘ってインダクタ電流ILの増加、減少はT/2周期で2回繰り返されることとなる。即ち、ゲート駆動信号のオンデューティが50%以上である場合についても、電界効果トランジスタのスイッチング周波数に対してインダクタLには2倍の周波数の交流電流が導通することとなる。

【0080】

以上で説明した動作内容の通り、力行動作時と回生動作時のいずれの場合も電界効果トランジスタのスイッチング周波数に対してインダクタLには2倍の周波数の交流電流が導通する。

そして、本発明のDC/DC電圧変換装置1の電界効果トランジスタは、可聴周波数の上限である20kHz以上のスイッチング周波数で動作する。

なお、この実施の形態において、スイッチング周波数を可聴周波数の上限以上に設定するとしているのは、後段でも詳述するが、スイッチング素子等にいわゆるワイドバンドギャップ半導体を採用することで、この高いスイッチング周波数の設定が可能となるとともに、この種の装置で従来から問題となっていた、インダクタやキャパシタからの耳障りな騒音の発生を確実に防止出来る等の利点が得られるからである。

【0081】

ところで、従来のDC/DC電圧変換装置では、半導体ユニットにSiを材料としたIGBTとPINダイオードを用いているため、実用的な半導体接合部温度の上限が175℃程度となる制約がある。この上限温度を超えると、Siを材料とする半導体ユニットは、漏れ電流が増加するなど物性が変化し破損する。従って、DC/DC電圧変換装置の出力電力容量は、半導体ユニットの半導体接合部温度が上昇したとしても、上限の175℃未満に収まるよう設定されなければならない。ここで、半導体ユニットの半導体接合部温度は、半導体ユニットの発生損失による発熱特性と、半導体ユニットを冷却するための冷却構造や冷媒の温度によって定まる放熱特性とのバランスに従う。

【0082】

これに対し、本願発明のDC/DC電圧変換装置におけるFET1、FET2、FET3、FET4には、そのバンドギャップがSiのそれより大きいワイドバンドギャップの半導体材料による電界効果トランジスタを用いているため、DC/DC電圧変換装置1が取り扱い可能な出力電力容量は、従来技術に基づくものよりも格段に拡大し、電力密度が向上している。

これは、ワイドバンドギャップの材料の半導体接合部温度の上限がSi材料の半導体接合部温度の上限よりも引き上げられることに因る。この理由について述べる。

【0083】

従来技術での半導体材料として良く用いられるSiはバンドギャップ値が1.12eVであった。これに対し、ワイドバンドギャップと総称されている材料として代表的なものには、炭化珪素4H−SiC(バンドギャップ:3.25eV)、窒化ガリウムGaN(バンドギャップ:3.39eV)、ダイヤモンド(バンドギャップ:5.47eV)が挙げられる。

【0084】

Si材料とワイドバンドギャップ材料とを比較すると、結晶内の電子の状態を表すバンド構造の上で、バンドギャップが大きい(広い)ほど、電子が価電子帯から伝導帯に遷移するために多くのエネルギが必要となるが、ワイドバンドギャップの場合はSiに比べて、より多くの熱エネルギを与えて励起させない限り、電子が伝導帯へ飛び移れない。この性質をパワーデバイスのPN接合部の漏れ電流に当てはめると考えると、半導体ユニットがオフしている際にワイドバンドギャップの半導体材料は、Si材料にて漏れ電流が流れ始める温度よりも、更に高温になってようやく漏れ電流が流れ始めることにあたる。言い換えると、ワイドバンドギャップ材料の半導体ユニットは、Si材料の半導体ユニットよりも、半導体として正常に動作する半導体接合部温度の上限が高くなる。バンドギャップ値が、例えば、2.0eV以上であれば、Siのバンドギャップ値1.12eVと比較してバンドギャップ値が約80%以上大きくなるため、半導体接合部温度上限の差は有意に表れる。

【0085】

DC/DC電圧変換装置の取扱い電力を増すと、半導体ユニットに生じる損失が増えて半導体接合部温度が上昇するが、バンドギャップ値が2.0eV以上の材料の半導体ユニットを用いることにより、特性の劣化が少なく抑えられて、耐熱性能は向上する。

従って、本発明のDC/DC電圧変換装置1は、従来のSi材料による半導体ユニットを用いた場合と比較して、半導体接合部が更に高温となるまで動作させることが可能であり、出力電力容量が拡大し電力密度が向上する。

【0086】

一方で、半導体接合部温度の上限が高くなることを利用して、冷却ヒートシンクが要する冷却性能を下げることもできる。冷却性能を下げれば、冷却ヒートシンクも小型となるため、高出力容量であっても小型で軽量なDC/DC電圧変換装置を実現可能である。

【0087】

また、半導体スイッチ素子である電界効果トランジスタを可聴周波数上限の20kHz以上でスイッチング動作させるため、インダクタLには40kHz以上の周波数の交流電流が導通し、従来のものよりも更にインダクタLの容積と重量を低減できる。以下、この点について説明する。

【0088】

上記で変換主回路2の動作を説明したように、インダクタLのリップル電流成分はインダクタLの巻線の端子間電位差の極性が周期的に切替わることで生じており、この端子間電位差の極性は、半導体スイッチ素子のスイッチング動作に連動している。即ち、半導体スイッチ素子を高い周波数でスイッチング動作させるほど、巻線の端子間電位差の極性が短い周期で切替わることとなる。これは、インダクタLのリップル電流成分の増加→減少→増加→減少の繰返しが短時間で行われることにあたるため、この繰返しの中でのインダクタ電流ILの増加量、減少量は低下する、つまり、リップル電流成分の振幅が低減されることになる。

【0089】

このため、インダクタLに導通する交流電流が減ることとなり、直流電流と交流電流が重畳した合計の電流量も減少する。

そこで、インダクタLのインダクタンス値の大小によって、リップル電流成分の振幅が大小変化することから、交流電流の振幅をそのまま低減させる代わりにインダクタンス値を下げてインダクタの磁路の断面積を減らし、インダクタLを従来よりも小型、軽量に構成できる。

この時、リップル電流成分の振幅をILrpl、インダクタンス値をLc、インダクタ巻線の端子間電位差をΔV、半導体スイッチ素子のスイッチング周期をTとすると、リップル電流成分の周期はT/2となり、次の関係で表される。

【0090】

Lc・ILrpl=ΔV・(T/4) ・・・(7)

【0091】

いま、半導体スイッチ素子のスイッチング周波数が5kHz(T=200μs)、インダクタLのリップル電流成分周波数が10kHz、端子間電位差ΔV=350V、インダクタンス値Lc=350μHである場合に、式(7)より、リップル電流成分振幅ILrpl=50Aとなる。

ここで、スイッチング周波数を可聴周波数上限の20kHz(T=50μs)に上げると、インダクタLのリップル電流成分周波数は40kHz、端子間電位差ΔV=350Vの場合に、式(7)よりLc・ILrpl=4375×10^−6となる。

【0092】

インダクタンス値Lc=350μHのままとすれば、ILrpl=12.5Aとなり、前述の50Aに比べて25%に低下するが、ILrpl=50Aを保てば、L=87.5μHと、インダクタンス値Lcが25%に低減する。

インダクタンス値Lcを低減することは、インダクタ巻線の巻数、インダクタコアの実効断面積を下げることにつながり、巻線部分、コア部分の容積が低減、即ち、インダクタLの容積が減ることになる。

【0093】

インダクタの巻線には主に銅が、コアには鉄を主成分とする電磁鋼板や軟磁性材、フェライト、あるいは鉄、アルミ、ニッケルの合金が用いられる。これら金属の比重は、銅が8.95g/cc、鉄が7.87g/ccであり、樹脂(プラスチック)の比重に比べて数倍以上に高い。その構成材料の内でも、金属が主体の構造物であるインダクタLを小型、軽量とする本発明のDC/DC電圧変換装置1は、高出力容量であっても優れて軽量に実現できる。

【0094】

ところで、本発明のDC/DC電圧変換装置1は、およそ100Vから1,000Vの範囲の電圧を取り扱い、可聴周波数上限の20kHz以上でスイッチングすると共に、高い出力電力容量かつ小型、軽量であることが要求される。

ところが、従来技術のDC/DC電圧変換装置では、Si材料の半導体スイッチ素子を用いており、可聴周波数上限の20kHz以上でスイッチング動作させることは極めて困難であった。

半導体スイッチ素子としてSi材料のものであっても、電界効果トランジスタであればユニポーラデバイスであって動作反応時間が短い特性を持っており、可聴周波数の上限以上の周波数でのスイッチング動作が可能となる。しかし、DC/DC電圧変換装置に求められる高い出力電力容量に適合して低損失であるには、半導体スイッチ素子の耐電圧が100V程度以下のものしか実用化されていない。よって、Siを材料とした電界効果トランジスタは本発明のDC/DC電圧変換装置1の用途に対して使用できなかった。

【0095】

また、従来のようにSiを材料とした半導体スイッチ素子としてIGBTを用いる場合は、100Vから1,000Vの電圧範囲を取り扱うための素子耐電圧として適合するものの、可聴周波数の上限以上の周波数でのスイッチング動作には使用できなかった。上記の電圧範囲に合致した素子耐電圧を持つIGBTは、耐電圧を得るためにデバイス構造内のドリフト層が厚くなってしまう。IGBTはバイポーラデバイスであることから、ターンオフ動作時に厚いドリフト層内の少数キャリアの消滅に時間を要してしまい、動作反応時間が長いという短所がある。この動作反応時間の長さから、可聴周波数の上限以上の高い周波数でのスイッチング動作には適用困難である。

【0096】

これに対し、本発明のDC/DC電圧変換装置1は、半導体ユニットとしてバンドギャップが、例えば、2.0eV以上のワイドバンドギャップの半導体材料を使った電界効果トランジスタあるいは整流ダイオードを用いるが故に、およそ100Vから1,000Vの範囲の電圧を取り扱い、かつ、可聴周波数上限の20kHz以上でのスイッチング動作が可能であって、高い出力電力容量で小型、軽量に実現できる。

これは、ワイドバンドギャップの半導体がSiを材料とする半導体よりも絶縁破壊電界強度が高く、飽和ドリフト速度が速いという特性に基づいている。

Siを材料とする半導体では絶縁破壊強度は、0.3MV/cm、飽和ドリフト速度は1×10^7cm/sであるのに対し、ワイドバンドギャップの半導体では、絶縁破壊強度は、4H−SiCが3MV/cm、GaNが3MV/cm、ダイヤモンドが2MV/cm、飽和ドリフト速度は、4H−SiCが2.2×10^7cm/s、GaNが2.4×10^7cm/s、ダイヤモンドが2.5×10^7cm/sである。

【0097】

絶縁破壊強度が高いほど半導体ユニットとして必要な耐電圧を得るに際しての、半導体ユニットの構造でドリフト領域に当てられる層の厚みを薄くすることができる。また、飽和ドリフト速度が速いことによってドリフト領域内を電子が素早く移動できる。即ち、ワイドバンドギャップの半導体の特長として、電子が薄いドリフト層を素早く移動することから動作反応時間が短く、可聴周波数の上限以上の高い周波数でのスイッチング動作が可能であるという点が挙げられる。

【0098】

また、本発明のDC/DC電圧変換装置1は、半導体スイッチ素子を可聴周波数の上限以上の周波数でスイッチング動作させ、インダクタLのリップル電流成分の周波数がスイッチング周波数の2倍となることから、特に、インダクタLとエネルギ移行用キャパシタC0、平滑キャパシタC1、C2で顕著であった耳障りな可聴騒音の発生を解消できる。よって、従来では外部への騒音伝播を抑えるための振動吸収部材を取り付けたり、インダクタのコア材料として低磁歪のものを採用するなどのコストアップや容積アップ、重くなるといった悪影響をもたらす処置を採らなくても良い。

【0099】

また、本発明のDC/DC電圧変換装置1は、従来のものよりも高い周波数で半導体スイッチ素子をスイッチング動作させることから、エネルギ移行用キャパシタC0、平滑キャパシタC1、C2に必要な静電容量を低減し、また、発生する損失も低減して小型で軽量に構成することが可能となる。

このことを、図8を用いて説明する。図8は、横軸を周波数の対数値、縦軸をインピーダンスの対数値としてキャパシタのインピーダンス特性を見た図である。

【0100】

図において、一点鎖線は静電容量Caの特性、実線は静電容量Cbの特性を示し、静電容量の大小関係は Cb<Caであって Caの方が静電容量が大きい。インピーダンスは、低い周波数域から周波数が増すに連れて低下していく。これは低い周波数域ではキャパシタ素子の容量成分がインピーダンスを決める主成分となるためである。インピーダンスは、周波数の増加に連れて、ある周波数で極小値となり、この極小値となる周波数を超えて更に周波数が増すと、傾きが反転してインピーダンスが増加する特性となる。これは、高い周波数となるとキャパシタ素子の電流経路となるリード部分の誘導成分がインピーダンスを決める主成分となるためである。

【0101】

ここで、キャパシタ素子の容量成分がインピーダンスの主成分となる低い周波数域では、静電容量が少ない容量Cbの方が容量Caよりもインピーダンスが大きくなる。一方、誘導成分がインピーダンスの主成分となる高い周波数域では静電容量が多い容量Caの方が容量Cbよりもインピーダンスが大きくなる。

いま、従来のDC/DC電圧変換装置にて半導体スイッチ素子を10kHzでスイッチングし、キャパシタに流れる交流電流の周波数も同じ周波数である場合のインピーダンスをZaΩとする。本発明のDC/DC電圧変換装置にて、キャパシタのインピーダンス特性が極小値となる周波数までの範囲内かつ可聴周波数の上限20kHzでスイッチングすれば、従来の通り、10kHzでスイッチングする場合よりもインピーダンスが低減する。

【0102】

そこで、静電容量をCaからCbへ減少させても尚、20kHzでのインピーダンスZbが、Zb<ZaとなるようCbを選定すれば、静電容量の低減によるキャパシタの小型化、軽量化と、インピーダンスの低減を両立可能となる。

また、インピーダンスがZaからZbへ低減することにより、キャパシタに交流電流が流れる際に生じる損失が減少するため、キャパシタの発熱による温度上昇が緩和されて好ましい。発熱による温度上昇は、キャパシタに用いられる樹脂材料の劣化を促進することから、キャパシタを用いたDC/DC電圧変換装置の耐久性を短縮する要因となる。本発明のDC/DC電圧変換装置は、キャパシタの小型化、軽量化と耐久信頼性の確保を容易とする効果を得られる。

【0103】

続いて、図9を参照して、制御ユニット3の動作について説明する。図9は、制御ユニット3と変換主回路2の構成を説明するブロック図である。

制御ユニット3は、外部から、変換主回路2の一次側端子電圧V1、二次側端子電圧V2、インダクタ電流IL、および、図示しない外部装置からのDC/DC電圧変換比指示を入力して内部で制御演算を行い、変換主回路2内のFET4、FET3、FET2、FET1のスイッチング動作を制御するゲート駆動信号8を出力する。

【0104】

制御ユニット3に入力する一次側端子電圧V1、二次側端子電圧V2、インダクタ電流IL、DC/DC電圧変換比指示は、変換制御部10に入力する。変換制御部10は、二次側端子電圧V2と一次側端子電圧V1との比から、実際に動作中の変換主回路2の電圧変換比を算出するとともに、外部装置からのDC/DC電圧変換比指示と突き合わせて公知の比例積分(PI)演算等を用いた負帰還制御演算を行ってFET1とFET2のオンデューティの目標量Ldutyを算出する。Ldutyは、デューティの下限を0%、上限を100%とする範囲で、例えば、0%の際にLduty=0.0、100%の際にLduty=1.0として間を直線補間した量として表す。

【0105】

また、インダクタ電流ILは、上記の電圧変換比の負帰還制御演算ループに内包される制御演算ループとして、インダクタ電流の目標量IL_refとインダクタ電流ILを突き合わせて行う負帰還制御演算の入力量として用いられる。

このインダクタ電流の負帰還マイナー制御演算を適用すれば、外周のDC/DC電圧変換比の負帰還制御系の制御帯域を高周波数に設定可能となり、半導体スイッチ素子にワイドバンドギャップ半導体を適用して従来よりも高い周波数でスイッチングするのと相俟って、DC/DC電圧変換比指示への変換比制御の追従応答性が向上する。

【0106】

次に、LdutyはゲートPWM生成部11に入力する。ゲートPWM生成部11は、Ldutyの値に対応して、パルス幅変調(PWM:Pulse Width Modulation)し、図4(a)、図5(a)、図6(a)、図7(a)に示されるゲート駆動信号8(Gate1、Gate2、Gate3、Gate4)の原信号となる矩形状のゲートPWM信号Gpwm1、Gpwm2、Gpwm3、Gpwm4を生成出力する。これは、例えば、三角波比較法を用いて周波数が半導体スイッチ素子のスイッチング周波数、振幅が1.0の三角波とLdutyとの大小比較を行って生成される。

【0107】

ゲートPWM信号Gpwm1、Gpwm2、Gpwm3、Gpwm4は、ゲート駆動回路12に入力する。ゲート駆動回路12は、ゲートPWM信号の論理に応じて半導体スイッチ素子をオン、オフ動作させるゲート駆動信号8を出力する。ゲート駆動回路12は、ゲートPWM生成部11との間でゲートPWM信号を受け渡しする必要から、信号を絶縁して受信する。これは、FET4、FET3、FET2、FET1のソース電位がそれぞれ個別の値となり、またFET4、FET3、FET2、FET1のオン、オフを切替えるために、それぞれの電界効果トランジスタのソース電位を基準として、ゲートの電位を操作する必要がある一方、ゲートPWM生成部11は、同一の基準電位でゲートPWM信号を生成出力するためである。

【0108】

また、上述のように、ソース電位が個別である各電界効果トランジスタを動作させるよう、ゲート駆動回路12は、ゲート駆動回路(1)121、ゲート駆動回路(2)122、ゲート駆動回路(3)123、ゲート駆動回路(4)124に分かれる。

各ゲート駆動回路は、対応する電界効果トランジスタのソース電位と信号接続しており、ゲート駆動信号8の電圧を電源電圧VDとするかソース電位とするかを切替えることで、スイッチオン、スイッチオフを制御する。電源電圧VDも各電界効果トランジスタに応じて個別に供給する必要から、4通りの相互に絶縁された電源電圧VD1、VD2、VD3、VD4をゲート電源回路13で作り、それぞれゲート駆動回路(1)121、ゲート駆動回路(2)122、ゲート駆動回路(3)123、ゲート駆動回路(4)124に供給する。

【0109】

ゲート駆動回路(1)121はGate1信号を出力しFET1を、ゲート駆動回路(2)122はGate2信号を出力しFET2を、ゲート駆動回路(3)123はGate3信号を出力しFET3を、ゲート駆動回路(4)124はGate4信号を出力しFET4をそれぞれスイッチング動作する。

【0110】

FET1とFET2のオンデューティとDC/DC電圧変換比の関係は、式(3)、式(6)にしたがって図10に示される特性となる。DC/DC電圧変換装置1は、上述のように図示しない外部装置からのDC/DC電圧変換比指示に追従すべく制御ユニット3で演算を行い、定常的には、図10の特性線上での指示されたDC/DC電圧変換比に対応するオンデューティでのゲート駆動信号8を出力して変換主回路2内の半導体スイッチ素子のスイッチオン、スイッチオフを制御する。

オンデューティが50%の場合にDC/DC電圧変換装置1の一次側端子電圧V1と二次側端子電圧V2は等しくなる。オンデューティが50%以上で昇圧動作となり、大きくなるに連れ、電圧変換比V2/V1も大きくなる。

オンデューティが50%未満で降圧動作となり、小さくなるに連れ、電圧変換比V2/V1も小さくなる。

【0111】

以上に説明したように、本実施の形態1によれば、半導体ユニットとして、そのバンドギャップがSiのそれより大きいワイドバンドギャップの半導体材料からなる電界効果トランジスタを用いてDC/DC電圧変換装置を構成しているため、可聴周波数上限の20kHz以上でのスイッチング動作が可能であって、かつ、半導体ユニットの半導体接合部温度の上限が、従来のSi材料によるものよりも大幅に引き上げられる。

また、本発明の変換主回路構成とすることで、インダクタLのリップル電流成分周波数は半導体スイッチ素子のスイッチング周波数の2倍とできる。

このことから、DC/DC電圧変換装置の出力電力容量を増加して半導体ユニットで生じる損失が増えたとしても、半導体ユニットの耐熱温度が高くなるため、ヒートシンクによる放熱とパワーデバイスの発熱との釣り合い関係が不整合とならない。一方、冷却ヒートシンクが要する冷却性能を下げることで、冷却ヒートシンクを小型、軽量とできる。装置の小型化に伴い、運搬や運搬時の梱包に関しても簡便となる。

【0112】

更に、インダクタLのリップル電流成分の周波数が高くなるため、インダクタLのインダクタンスを下げることが可能となり、インダクタの容積と重量が従来技術に基づくものに比べ格段に低減する。

従って、取り扱い可能な出力電力容量を拡大し、電力密度が向上しつつも、小型で軽量なDC/DC電圧変換装置を実現可能である。

また、特に、インダクタLとエネルギ移行用キャパシタC0、平滑キャパシタC1、C2で顕著であった耳障りな可聴騒音の発生も解消できる。

【0113】

なお、本発明の範囲内で、図11に示すよう変換主回路2の半導体ユニットへ、ワイドバンドギャップの半導体材料による電界効果トランジスタの替わりに、Si材料であって可聴周波数の上限周波数以上で動作可能なよう特性の調整を施したIGBT、および、これと逆並列に接続したワイドバンドギャップの半導体材料による整流素子を適用したものであっても良い。

図11において、半導体スイッチ素子は、IGBT1、IGBT2、IGBT3、IGBT4である。ワイドバンドギャップ材料による整流素子は、Di1、Di2、Di3、Di4である。IGBT1とDi1、IGBT2とDi2、IGBT3とDi3、IGBT4とDi4が対となって逆並列に接続し、電流を双方向に導通可能な半導体ユニットとなす。

【0114】

このように構成すれば、半導体スイッチ素子であるIGBTの半導体接合部温度を上限の175℃未満に抑えなければいけないものの、整流素子としてワイドバンドギャップの半導体材料を適用することから、逆回復時間が短く逆回復電流を低減できる。

よって、Si材料によるIGBTを用いたとしてもIGBTのスイッチングの応答速度を速めることができ、スイッチング損失を低減可能なことから、IGBTの温度上昇に余裕が生じ、DC/DC電圧変換装置が取り扱い可能な出力電力容量が拡大して電力密度が向上する。

【0115】

また、図12に示すよう変換主回路2の半導体ユニットへ、共にワイドバンドギャップの半導体材料から成る電界効果トランジスタ、および、これと逆並列に接続した整流素子を適用したものであっても良い。

図12において、半導体スイッチ素子は、FET1、FET2、FET3、FET4である。整流素子は、Di1、Di2、Di3、Di4である。ワイドバンドギャップの半導体材料から成る整流素子は、主にショットキーバリアダイオードとして実装される。

【0116】

このように構成すれば、特性が優れた整流素子を適用するため、整流素子に流れる電流の転流時に、しばらくの間、逆方向に電流が流れてしまうリカバリ動作時間を短縮できる。よって、スイッチング毎の動作状態の整定が短時間に行われる。したがって、スイッチング周波数をさらに向上させて、インダクタンス値Lcを低減し、インダクタLの容積を減らして、さらに、小型で軽量なDC/DC電圧変換装置を実現可能である。

【0117】

なお、以上の説明では、半導体ユニットのスイッチング周波数を可聴周波数の上限以上としたが、このスイッチング周波数の2倍となるインダクタに流れる交流成分の周波数が可聴周波数の上限値以上となる条件を満たすものとしても、特に、その騒音が問題となるインダクタの発生音が可聴周波数の上限以上となることから、耳障りな可聴騒音の発生は、以上で説明した場合と同様に防止することができる。

更には、インダクタの騒音が特に問題とならない環境で使用される場合等では、インダクタに流れる交流成分の周波数が可聴周波数の上限値以上となる条件に拘らず、スイッチング周波数を従来並に留める設定とすれば、標準的で比較的安価なスイッチング素子を使用することが出来、装置を低コストで実現できるとともに、一次側から二次側に電力を供給する力行動作時と二次側から一次側に電力を供給する回生動作時のいずれの場合にも、二次側電圧と一次側電圧の間を昇圧、降圧の双方に直流電圧変換する事が可能となるという、この発明特有の効果を享受することが出来る。

【0118】

実施の形態2.

以下、本発明の実施の形態2におけるDC/DC電圧変換装置を、図13から図16を用いて説明する。

本実施の形態のDC/DC電圧変換装置は、制御ユニット3内のゲートPWM生成部11とゲート駆動回路12の構成と動作、および変換主回路2内の電界効果トランジスタのターンオフ時の動作を除いて、先の実施の形態1のDC/DC電圧変換装置の場合と同じであり、以下では、実施の形態1と同じ構成、動作、作用の箇所については適宜説明を省略する。

【0119】

先ず、図13を参照して説明する。図13は、本実施例による制御ユニット3と変換主回路2の構成を説明するブロック図である。制御ユニット3は、外部から変換主回路2の一次側端子電圧V1、二次側端子電圧V2、インダクタ電流IL、および、図示しない外部装置からのDC/DC電圧変換比指示を入力して内部で制御演算を行い、変換主回路2内のスイッチング素子を制御するゲート駆動信号8を出力する。実施の形態1で示したタイミングと論理のゲート駆動信号8によって、変換主回路2内のスイッチング素子がスイッチオン、スイッチオフ動作して所望のDC/DC電圧変換が行われる。

制御ユニット3に入力する一次側端子電圧V1、二次側端子電圧V2、インダクタ電流IL、DC/DC電圧変換比指示は、変換制御部10に入力し、電圧変換比の負帰還制御演算が行われてFET1とFET2のオンデューティの目標量Ldutyが出力される。

【0120】

続いて、ゲートPWM生成部11aは、Ldutyを入力し、Ldutyの値に対応してゲートPWM信号Gpwm1、Gpwm2、Gpwm3、Gpwm4を生成しゲート駆動回路12aへ出力する。

また、Ldutyの大小によって、ゲート駆動回路12aのスイッチオフ回路(1)とスイッチオフ回路(2)のいずれかを選択する切替え信号DCselをゲート駆動回路12aへ出力する。

【0121】

ゲート駆動回路12aの詳細な構成は図14に示される。図14は、ゲート駆動回路12aを構成する4つの個別の駆動回路ブロック121a、122a、123a、124aの内の一つを代表して駆動回路ブロック12xaとして示している。上記の個別の駆動回路ブロック121a、122a、123a、124aは同じ構成、動作であって、駆動回路ブロック121aはFET1に、122aはFET2に、123aはFET3に、124aはFET4に対応している。

駆動回路ブロック12xaは、スイッチオン回路24、スイッチオフ回路(1)25、スイッチオフ回路(2)26のいずれかを動作させてゲート駆動信号8を生成し出力する。スイッチオン回路24は、小信号用の電界効果トランジスタ等の半導体スイッチ241と回路抵抗242とから成る。

【0122】

同様に、スイッチオフ回路(1)25は、半導体スイッチ251と回路抵抗252、スイッチオフ回路(2)26は、半導体スイッチ261と回路抵抗262とから成る。ここで、(回路抵抗252の抵抗値)<(回路抵抗262の抵抗値)の関係を持たせている。

【0123】

ゲートPWM信号Gpwmがゲート駆動回路12aに入力すると、内部で信号バッファ21、22に伝送される。信号バッファ21は、ゲートPWM信号Gpwmの論理がスイッチオン論理の場合に閉、スイッチオフ論理の場合に開とするよう半導体スイッチ241を制御する増幅回路である。

Gpwmがスイッチオン論理の場合に半導体スイッチ241が閉となって、ゲート駆動信号8(Gate)の電圧は電源電圧VDとなる。よって、対応する変換主回路2内の電界効果トランジスタがスイッチオンする。

【0124】

信号バッファ22は、ゲートPWM信号Gpwmの論理がスイッチオン論理の場合に開、スイッチオフ論理の場合に閉とするよう半導体スイッチ251、261を制御する増幅回路である。

Gpwmがスイッチオフ論理の場合に半導体スイッチ251か半導体スイッチ261の何れかが閉となって、ゲート駆動信号8(Gate)の電圧はソース電位と等しくなる。よって、対応する変換主回路2内の電界効果トランジスタがスイッチオフする。

【0125】

ここで、半導体スイッチ251と半導体スイッチ261の何れを閉とするかは、オフ信号調整手段としての回路切替え器23で選択される。

信号バッファ22の出力と切替え信号DCselとが回路切替え器23に入力し、スイッチオフ回路(1)25とスイッチオフ回路(2)26のどちらを動作させるかを選択して、選択した側のスイッチオフ回路内の半導体スイッチを閉とするよう制御信号を伝送する。

【0126】

回路切替え器23でのスイッチオフ回路の選択は、図15に示す形態で行われる。

図15は、オンデューティに対応して二種類のスイッチオフ回路のいずれを選択するかを模式的に示す説明図である。図15にて、スイッチオフ回路の切替えはオンデューティに関してオンデューティ幅ΔDのヒステリシスをもって行われる。

即ち、スイッチオフ回路(1)25が選択されている状態で、オンデューティがDa %(第2の閾値)以上となればスイッチオフ回路(2)26を選択するよう切替える。また、スイッチオフ回路(2)26が選択されている状態で、オンデューティが(Da−ΔD)%(第1の閾値)未満となればスイッチオフ回路(1)25を選択するよう切替える。

即ち、オンデューティが高く、Da%以上の場合に高い回路抵抗値でのスイッチオフ回路で動作させ、オンデューティが低く、(Da−ΔD)%未満の場合に低い回路抵抗値でのスイッチオフ回路で動作させる。

実施の形態1で説明したように、オンデューティが50%以上では昇圧動作であり、オンデューティが高いほどDC/DC電圧変換比は大きく、DC/DC電圧変換装置の二次側電圧V2は高くなる。

【0127】

なお、後段でも触れるが、回路切替え器23は、(回路抵抗252の抵抗値)<(回路抵抗262の抵抗値)の関係に基づき、半導体スイッチへのゲート信号8を立ち下げ該半導体スイッチをオフさせるときの立ち下げ峻度を、スイッチオフ回路(1)25を選択することで当該立ち下げ峻度として第1の設定値を選択するケースと、スイッチオフ回路(2)26を選択することで当該立ち下げ峻度として上記第1の設定値より小さい第2の設定値を選択するケースとの切替えを行うものである。

【0128】

以上のように動作すれば、DC/DC電圧変換装置1の二次側電圧が高電圧の際に、電界効果トランジスタがターンオフ動作する場合に発生するサージ電圧を低減し、電界効果トランジスタのドレイン−ソース(D−S)間でのサージ電圧を加味した最大電圧が過大となるのを防止できる。このことについて、図16を用いて更に詳細に説明する。

【0129】

図16は、電界効果トランジスタのターンオフ時の動作波形を示すものであり、横軸は時間の経過を表している。図16(a)は、低い回路抵抗値のスイッチオフ回路で動作した場合、図16(b)は、高い回路抵抗値のスイッチオフ回路で動作した場合である。

なお、図中の各記号は、

Vgs:ゲート−ソース(G−S)間の電圧、

Ig:ゲート駆動信号8の動作電流、

Vds:ドレイン−ソース(D−S)間電圧、

Id:ドレインに流れ込む電流、

Vth:閾値電圧、

Nfet:変換主回路の電界効果トランジスタの直列数

である。

【0130】

ターンオフ動作の過程は、図16(a)においては時刻ta1からta4までの変化で、また、図16(b)においては時刻tb1からtb4までの変化で表される。

図16(a)において、先ず、時刻ta1でゲート駆動信号8の論理がスイッチオンからスイッチオフに切替わる。Vgsは、ゲート−ソ−ス間容量Cgsを放電し、時刻ta2でVthに達する。時刻ta2から電圧Vdsが増加し始めることより、ドレイン−ソ−ス間容量Cdsの両端電圧は増加し充電される。同時に、ゲート−ドレイン間容量Cgdも充電される。時刻ta2から時刻ta3の間、Cgsの放電は一旦休止し、電圧Vgsの減少は止んでVthに一定となる。この間でゲート駆動信号8の動作電流Igは大きくなりΔigp1となる。時刻ta3では電圧Vdsはほぼ増加し切る。

【0131】

時刻ta3でCgdの充電がほぼ終了すると、Cgsの放電が再開して電流Idは減少していく。時刻ta4で、Idは減少し切って、ターンオフ動作が終了する。

ここで、電流Idの変化速度dId/dtと配索導体部分の寄生インダクタンスLsとの積より、誘起電圧が生じてサージ電圧ΔVsg1となる。ターンオフの過渡的な動作が終了すると電圧Vds=(2・V2)/Nfet に収束する。これは電圧V2が印加される部分をNfet個の内の半数の電界効果トランジスタで受け持っている状態である。半数で受け持つのは、電界効果トランジスタのスイッチオンとスイッチオフの関係が相補となる組み合わせとして動作しているためである。

ターンオフ動作の過渡状態で電圧Vdsにはサージ電圧が重畳されて、最大値がVds_max=(2・V2)/Nfet+ΔVsg1に達する。このVds_maxが過大であれば、パワーデバイスやキャパシタの耐電圧を超過し損傷する懸念が強まる。

【0132】

一方、高い回路抵抗値を用いた、ゲート信号の立ち下がり峻度が小さく緩やかとなるスイッチオフ回路で動作した場合は図16(b)のようになる。

図16(b)で時刻tb1、tb2、tb3、tb4に亘る動作の内容は図16(a)と同じであり、時刻tbxは時刻taxと対応している。しかし、回路抵抗値の相違より、時刻tb2から時刻tb3の間のゲート駆動信号8の動作電流Igは、図16(a)のΔigp1より小さいΔigp2となる。これは、閾値電圧Vthに対して高い回路抵抗値で動作電流Igを流すためである。

【0133】

よって、時刻tb3から時刻tb4にかけてCgsの放電が再開して電流Idが減少していく際の電流Idの変化速度dId/dtは、図16(a)の波形と比較して緩やかなものとなる。従って、配索導体部分の寄生インダクタンスLsとの積で表されるサージ電圧ΔVsg2は、図16(a)でのΔVsg1よりも低くなり、過渡状態での電圧Vdsの最大値Vds_max=(2・V2)/NFET+ΔVsg2 も低くなる。

【0134】

以上のことから、本実施の形態2のDC/DC電圧変換装置1は、オンデューティに応じてゲート駆動回路12a内のスイッチオフ回路を切替えることによって、二次側電圧V2が高電圧の場合に電界効果トランジスタのドレイン−ソース間に重畳するサージ電圧を低く抑える。このため、ドレイン−ソース間電圧が過大となって半導体ユニットやキャパシタの耐電圧を超過し、損傷してしまわぬよう動作できる。

【0135】

なお、スイッチオフの動作速度を速めればサージ電圧は電流Idの変化速度dId/dtに比例する関係より、サージ電圧は増える方向となる。

本実施の形態2では、オンデューティが高い際にスイッチオフの動作速度を遅くする動作となるため、二次側電圧V2が高電圧であって半導体ユニットやキャパシタの耐電圧を超過する懸念が高まる動作範囲でのみ、サージ電圧が低減するようスイッチオフ回路を切替える。従って、二次側端子電圧V2が高電圧ではない動作範囲でスイッチオフの動作速度を速くでき、スイッチング損失が少なく高効率となる利点が得られる。

【0136】

実施の形態3.

以下、本発明の実施の形態3におけるDC/DC電圧変換装置を、図17から図21を用いて説明する。

本実施の形態のDC/DC電圧変換装置は、エネルギ移行用キャパシタC0とインダクタLと半導体ユニットである電界効果トランジスタの温度に基づいて、電界効果トランジスタのスイッチング周波数を調整するよう構成されていることを除いて、先の実施の形態1のDC/DC電圧変換装置の場合と同じである。以下では、実施の形態1と同じ構成、動作、作用の箇所については適宜説明を省略する。

【0137】

先ず、図17は、本実施の形態による変換主回路2の構成を示す図である。変換主回路2内のFET1には、半導体チップの近傍、あるいは半導体チップの構成面に温度検出用ダイオード271が形成されており、FET1の半導体チップ温度を検出する。また、同様にFET3の半導体チップの近傍、あるいは半導体チップの構成面に温度検出用ダイオード273が形成されており、FET3の半導体チップ温度を検出する。

インダクタL、エネルギ移行用キャパシタC0には、それぞれの温度を検出するインダクタ温度検出器28、キャパシタ温度検出器29が取り付けられており、各温度を検出する。

【0138】

図18は、本実施例による制御ユニット3の構成を示すブロック図である。制御ユニット3には、外部から変換主回路2の一次側端子電圧V1、二次側端子電圧V2、インダクタ電流IL、図示しない外部装置からのDC/DC電圧変換比指示、および、上記変換主回路2の温度検出用ダイオード271、273、インダクタ温度検出器28、キャパシタ温度検出器29からの信号が入力される。

【0139】

詳細には、インダクタ温度検出器28の信号は、インダクタ温度算出回路31に入力し、インダクタ温度TmLを出力する。キャパシタ温度検出器29の信号は、キャパシタ温度算出回路32に入力し、キャパシタ温度TmCを出力する。

また、温度検出用ダイオード271、273の信号は、半導体チップ温度算出回路33に入力し、FET1かFET3のいずれか高い方の半導体チップ温度Tmjを出力する。

温度検出用ダイオードは、所定の順バイアス電流を流しているという状態の下で、そのPN接合部の温度によってアノードAt−カソードKt間の電圧VFが変化するという性質を持っている。半導体チップ温度算出回路33は、この性質を用いてFET1、FET3の半導体チップ温度を算出する。

なお、便宜上FET2、FET4の半導体チップ温度は検出しない様態で説明しているが、必ずしもこの通りではなく、全ての電界効果トランジスタの半導体チップ温度を検出するものであっても、また、いずれか一つのみの半導体チップ温度を検出するものであっても良い。

【0140】

続いて、各温度TmL、TmC、Tmjは、スイッチング周波数調整手段である周波数調整器34に入力する。周波数調整器34は、これら入力した各温度に基づいて、電界効果トランジスタFET1、FET2、FET3、FET4のスイッチング周波数の適正値を選択する。

この適正値の選択は、インダクタLの温度あるいはエネルギ移行用キャパシタC0の温度が高温となり、規定動作温度範囲の上限に近付く場合に、スイッチング周波数を漸増させるよう調整することで行われる。

【0141】

このことを、図19を用いて説明する。図19(a)は、スイッチング周波数fcとインダクタL、エネルギ移行用キャパシタC0の発熱量との関係を説明する模式図である。図19(a)に示すように、スイッチング周波数fcが低いほど発熱量は多く、スイッチング周波数fcが高いほど発熱量は少なくなる。これは、実施の形態1にて説明したように、スイッチング周波数が高いほど、リップル電流成分である交流電流の振幅が低減して損失、即ち、発熱量が低減することに因る。同様に、エネルギ移行用キャパシタC0の発熱量が低減するのも交流電流の振幅が低減するためである。インダクタL、エネルギ移行用キャパシタC0の発熱量がスイッチング周波数fcの増加に連れて累乗根で減少するのは、発熱量が主に交流電流の累乗に依存した値となるためである。

【0142】

図19(b)は、スイッチング周波数fcと半導体ユニットの発熱量との関係を説明する模式図である。図19(b)に示すように、スイッチング周波数fcが低いほど発熱量は少なく、スイッチング周波数fcが高いほど発熱量は多くなる。これは、スイッチング周波数が高いほど、所定時間当たりのスイッチング回数が増えることから、半導体スイッチ素子に生じるスイッチング損失と整流素子に生じる逆回復損失が増加するためである。なお、電界効果トランジスタは、半導体スイッチ素子と整流素子とが一体となった双方向導通デバイスである。

この図19(a)と図19(b)の特性から、スイッチング周波数fcが低いほどインダクタL、エネルギ移行用キャパシタC0は高温となり易く、スイッチング周波数fcが高いほど半導体スイッチ素子と整流素子は高温となり易い。

【0143】

この特性から、周波数調整器34は以下のように動作する。図20は、周波数調整器34の詳細な構成を示すブロック図である。図において、341は周波数調整テーブルL、342は周波数調整テーブルC、343は周波数調整テーブルjである。また、344は選択処理手段である。

インダクタ温度算出回路31からのインダクタ温度TmLは周波数調整テーブルL341に入力し、テーブル参照によってTmLに適したスイッチング周波数候補fclを出力する。このテーブルでは、インダクタLの動作温度範囲Tl_minからTl_maxの範囲で閾値Tl_Fより低温時は初期値fc0を、閾値Tl_F以上の高温時はTl_maxに対応してfcl_maxとなるまでの間で漸増する設定としている。これは、図19(a)のスイッチング周波数が高い場合にインダクタLの発熱量が減少する特性に合わせて、高温時にはスイッチング周波数を漸増したいとするものである。

ここで、初期値fc0は、可聴周波数の上限以上の周波数であり、インダクタL、エネルギ移行用キャパシタC0、半導体ユニットの何れも高温でなく、過熱の懸念なしに通常の動作を行う場合のスイッチング周波数の基本設定値である。

【0144】

同様に、キャパシタ温度算出回路32からのキャパシタ温度TmCは、周波数調整テーブルC342に入力し、テーブル参照にてTmCに適したスイッチング周波数候補fccを出力する。このテーブルでは、キャパシタCの動作温度範囲Tc_minからTc_maxの範囲で閾値Tc_Fより低温時は初期値fc0を、閾値Tc_F以上の高温時はTc_maxに対応してfcc_maxとなるまでの間で漸増する設定としている。これも上記のインダクタLでの場合と同様に、スイッチング周波数が高い場合にエネルギ移行用キャパシタC0の発熱量が減少する特性に合わせて、高温時にはスイッチング周波数を漸増したいとするものである。

【0145】

また、半導体チップ温度算出回路33からの、温度検出した内で最も高い半導体チップ温度Tmjを、周波数調整テーブルj343に入力し、テーブル参照にてTmjに適したスイッチング周波数候補fcjを出力する。このテーブルでは、半導体ユニットの動作温度範囲Tj_minからTj_maxの範囲で閾値Tj_Fより低温時は初期値fcj_maxを、閾値Tj_F以上の高温時はTj_maxに対応してfcj_minとなるまでの間で漸減する設定としている。

これは、図19(b)のスイッチング周波数が低い場合に、半導体ユニットの発熱量が減少する特性に合わせて、高温時にはスイッチング周波数を漸減したいとするものである。

【0146】

続いて、選択処理手段344は、スイッチング周波数候補fcl、fcc、fcjを入力し、図21に示す処理フローにしたがってスイッチング周波数指示値fc_refを選択し出力する。

図21の処理フローで、先ず、ステップS101にてスイッチング周波数暫定指示値fc_tmpへfclとfccのいずれか大きい方の値を設定する。次に、ステップS102でスイッチング周波数暫定指示値fc_tmpとスイッチング周波数候補fcjとの大小関係を比較して、fc_tmp≦fcjならばステップS104へ進む。反対に、fc_tmp>fcjならばステップS103へ進む。ステップS103ではスイッチング周波数暫定指示値fc_tmpへfcjを設定する。

次に、ステップS104で暫定指示値fc_tmpをスイッチング周波数指示値fc_refへ設定する。このfc_refが選択処理手段344より出力される。

【0147】

これらの動作で、ステップS102での分岐とステップS103のスイッチング周波数暫定指示値fc_tmpへのfcjの設定は、インダクタL、あるいは、エネルギ移行用キャパシタC0が高温となってスイッチング周波数を漸増したい場合でも、半導体ユニットの半導体チップ温度もまた高温であってスイッチング周波数を漸減したければ、後者を優先してスイッチング周波数指示値に選択するという動作を表している。

【0148】

次に、選択処理手段344からのスイッチング周波数指示値fc_refは、周波数調整器34の出力としてゲートPWM生成部11bに入力する。ゲートPWM生成部11bは、図9に示す実施の形態1のゲートPWM生成部11と同様に、Ldutyの値に対応してパルス幅変調し、ゲート駆動信号8(Gate1、Gate2、Gate3、Gate4)の原信号となる矩形状のゲートPWM信号Gpwm1、Gpwm2、Gpwm3、Gpwm4を生成出力する。

この時、搬送波の周波数、即ち、スイッチング周波数を上記スイッチング周波数指示値fc_refに設定してゲートPWM信号を生成する。

上記に説明した内容を除く制御ユニット3の構成と動作は、実施の形態1で説明した制御ユニット3のものと同じであるため、説明を省略する。

【0149】

以上のように、本実施の形態3のDC/DC電圧変換装置1によれば、変換主回路のエネルギ移行用キャパシタとインダクタと半導体ユニットの温度に基づいて、半導体ユニットのスイッチング周波数を調整する。このため、半導体ユニットと比較して相対的に耐熱性が低い樹脂材料を用いてエネルギ移行用キャパシタやインダクタを構成したとしても、エネルギ移行用キャパシタやインダクタが高温となった際に、半導体ユニットの半導体チップ温度の上昇が問題とならない範囲でスイッチング周波数を漸増し、キャパシタやインダクタが過熱して損傷しないよう保護することが可能となる。

【0150】

実施の形態4.

以下、本発明の実施の形態4におけるDC/DC電圧変換装置を、図22から図30を用いて説明する。

本実施例では、DC/DC電圧変換装置が、実施の形態1で説明した形態のものと異なり、同時刻のスイッチオン、オフの状態が相補の関係となる2個で一組となる双方向に電流を導通可能な半導体ユニットを3組有する変換主回路2を備えている。

半導体ユニットが3組である変換主回路2を図22に示す。図22の変換主回路2は、半導体ユニットである電界効果トランジスタFET1、FET2、FET3、FET4、FET5、FET6、一次側平滑キャパシタC1、二次側平滑キャパシタC2、エネルギ移行用キャパシタC0a、C0b、およびインダクタLを備えている。

また、全ての半導体ユニットは、直列に接続されている。ここで、インダクタLのFET4側接続端子の電圧をVLと表す。

【0151】

続けて、変換主回路2の接続の詳細について説明する。

平滑キャパシタC1の両端子は、変換主回路2の一次側の正極側端子P1、負極側端子N1に接続されており、負極側端子N1は変換主回路2の二次側の正極側端子P2とも接続されている。

正極側端子P1は、平滑キャパシタC1の一方の端子とFET1のドレイン端子に接続され、平滑キャパシタC1の他方の端子は負極側端子N1に接続される。

また、平滑キャパシタC2の両端子は、変換主回路2の二次側の正極側端子P2、負極側端子N2に接続されている。

【0152】

FET6のソース端子は変換主回路2の二次側の負極側端子N2に、ドレイン端子はFET5のソース端子に、FET5のドレイン端子はFET4のソース端子に、FET4のドレイン端子はFET3のソース端子に、FET3のドレイン端子はFET2のソース端子に、FET2のドレイン端子はFET1のソース端子に、それぞれ接続されている。

エネルギ移行用キャパシタC0aは、一方の端子をFET5とFET4との接続点に、他方の端子をFET3とFET2との接続点に接続されている。また、エネルギ移行用キャパシタC0bは、一方の端子をFET6とFET5との接続点に、他方の端子をFET2とFET1との接続点に接続されている。

【0153】

なお、後段の動作説明で触れているように、この例では、FET1とFET6、FET2とFET5、FET3とFET4がそれぞれ組となり、各組をなす一対のFETは、いわゆる相補の関係を持つようにオンオフ制御される。

【0154】

インダクタLは、図22に示すように、一方の端子を変換主回路2の一次側の負極側端子N1に接続され、他方の端子を、上記した一対のFETであって互いに直接接続されているFET4とFET3との接続点に接続されている。

【0155】

図22には示されない制御ユニット3からは、ゲート駆動信号8として電界効果トランジスタをオン、オフ制御するための信号がFET6、FET5、FET4、FET3、FET2、FET1に対応して、それぞれGate6、Gate5、Gate4、Gate3、Gate2、Gate1信号としてFET6からFET1のゲート電極(G)に接続されている。FET6はGate6信号の、FET5はGate5信号の、FET4はGate4信号の、FET3はGate3信号の、FET2はGate2信号の、FET1はGate1信号の電圧変化にしたがって、スイッチング動作する。

【0156】

電界効果トランジスタは、制御ユニット3からのゲート駆動信号8にしたがってスイッチオン、スイッチオフの動作が制御される。制御ユニット3は、実施の形態1の図9と相似であって、変換制御部10が算出したオンデューティの目標量LdutyがゲートPWM生成部11に入力する。ゲートPWM生成部11は、Ldutyの値に対応してパルス幅変調し、図23(a)、図24(a)、図25(a)、図26(a)、図27(a)、図28(a)、図29(a)、図30(a)に示されるゲート駆動信号8(Gate1、Gate2、Gate3、Gate4、Gate5、Gate6)の原信号となる矩形状のゲートPWM信号Gpwm1、Gpwm2、Gpwm3、Gpwm4、Gpwm5、Gpwm6を生成出力する。

【0157】

ここで、図23は、力行動作時の降圧動作でゲート駆動信号のオンデューティが100/3%未満の場合の波形を図示する。(a)はゲート駆動信号、(b)はインダクタ電流IL、(c)はスイッチングモードとその切替わりタイミングを示している。

同様に、図24は、力行動作時の降圧動作でゲート駆動信号のオンデューティが100/3%以上で50%未満の場合、図25は、力行動作時の昇圧動作でゲート駆動信号のオンデューティが50%以上で100×(2/3)%未満の場合、図26は、力行動作時の昇圧動作でゲート駆動信号のオンデューティが100×(2/3)%以上の場合の波形を図示する。それぞれ、(a)はゲート駆動信号、(b)はインダクタ電流IL、(c)はスイッチングモードとその切替わりタイミングを示している。

インダクタ電流ILは、インダクタLをFET4側接続端子から負極側端子N1側接続端子の方向に流れる極性を正とする。

【0158】

ゲートPWM信号Gpwm1、Gpwm2、Gpwm3、Gpwm4、Gpwm5、Gpwm6は、ゲート駆動回路12に入力する。ゲート駆動回路12は、ゲートPWM信号の論理に応じて半導体スイッチ素子をオン、オフ動作させるゲート駆動信号8を出力する。

Gpwm1はFET1、Gpwm2はFET2、Gpwm3はFET3、Gpwm4はFET4、Gpwm5はFET5、Gpwm6はFET6にそれぞれ対応し、電界効果トランジスタのスイッチング動作を制御する。

【0159】

また、図示しないものの、ソース電位が個別である各電界効果トランジスタを動作させるよう、ゲート駆動回路12はゲート駆動回路(1)121、ゲート駆動回路(2)122、ゲート駆動回路(3)123、ゲート駆動回路(4)124、ゲート駆動回路(5)125、ゲート駆動回路(6)126に分かれる。

ゲート電源回路13は、6通りの相互に絶縁された電源電圧VD1、VD2、VD3、VD4、VD5、VD6を作り、それぞれのゲート駆動回路121から126に供給する。

【0160】

次に、このゲート駆動信号8による電圧変換の制御について、力行動作時と回生動作時とに分けて説明する。

力行動作時:

1)オンデューティが100/3%未満で降圧動作の場合:

一次側から二次側へ電力を供給する力行動作時であって、二次側電圧V2<一次側電圧V1の降圧を行うオンデューティが100/3%未満の動作について説明する。

図23(a)において、Gate1信号がハイの場合にFET1が、Gate2信号がハイの場合にFET2が、Gate3信号がハイの場合にFET3がオンし、ドレインからソースに向けて電流が流れる。また、Gate4信号がハイの場合にFET4が、Gate5信号がハイの場合にFET5が、Gate6信号がハイの場合にFET6がオンするが、力行動作時には電流がソースからドレインに向けてFET4、FET5、FET6に内在する寄生ダイオードの替わりにトランジスタ部分を流れる。

【0161】

ここで、Gate1信号とGate6信号、Gate2信号とGate5信号、Gate3信号とGate4信号とは、互いにハイ、ローの論理が相反する相補信号である。図23(a)に示す通り、ゲート駆動信号8は、相補信号として対を成す信号が3通り有って、互いの位相差が等間隔となっている。

この時、Gate1からGate6のゲート駆動信号のハイ、ローの論理の組合わせは、スイッチングモードE、F、G、Hの4種に分類され H→E→G→E→F→E→H の順に切替わる。

【0162】

スイッチングモードFでは、FET1、FET4、FET5がオン、FET2、FET3、FET6がオフであって、

電流が、正極側端子P1→FET1→エネルギ移行用キャパシタC0b→FET5→FET4→インダクタL→負極側端子N1の経路に流れ、エネルギがエネルギ移行用キャパシタC0bに蓄えられる。電気機器5には、平滑キャパシタC2の両端電圧が印加され、平滑キャパシタC2からエネルギが供給される。

また、FET1、FET4、FET5がオンであって電流が導通することから、エネルギ移行用キャパシタC0bのFET5側接続端子の電位はおよそVL、FET1側接続端子の電位はおよそV1となる。

よって、インダクタLのFET4側接続端子の電圧VLは、VL=V1−Vc0bとなる。ここでVc0bは、エネルギ移行用キャパシタC0bの両端電圧である。

【0163】

スイッチングモードHでは、FET3、FET5、FET6がオン、FET1、FET2、FET4がオフであって、

電流が、負極側端子N2→FET6→FET5→エネルギ移行用キャパシタC0a→FET3→インダクタL→正極側端子P2→電気機器5→負極側端子N2の経路に流れ、エネルギがエネルギ移行用キャパシタC0aから放出する。

また、FET3、FET5、FET6がオンであって電流が導通することから、エネルギ移行用キャパシタC0aのFET3側接続端子の電位はおよそVL、FET5側接続端子の電位はおよそ−V2となる。

よって、インダクタLのFET4側接続端子の電圧VLは、VL=−V2+Vc0aとなる。ここで、Vc0aは、エネルギ移行用キャパシタC0aの両端電圧である。

【0164】

スイッチングモードEでは、FET4、FET5、FET6がオン、FET1、FET2、FET3がオフであって、

電流が、負極側端子N2→FET6→FET5→FET4→インダクタL→正極側端子P2→電気機器5→負極側端子N2の経路に流れ、インダクタLに蓄積されたエネルギが放出される。

また、FET4、FET5、FET6がオンであって電流が導通することから、電圧VLはおよそ−V2となる。インダクタLのFET4側接続端子の電圧VLと負極側端子N1側の接続端子の電圧との差は、(−V2−0)で負となり、インダクタ電流ILは、IL≧0の状態で、負の方向へ向けて減少する。

【0165】

スイッチングモードGでは、FET2、FET4、FET6がオン、FET1、FET3、FET5がオフであって、

電流が、負極側端子N2→FET6→エネルギ移行用キャパシタC0b→FET2→エネルギ移行用キャパシタC0a→FET4→インダクタL→正極側端子P2→電気機器5→負極側端子N2の経路に流れ、エネルギはエネルギ移行用キャパシタC0aに蓄えられ、エネルギ移行用キャパシタC0bから放出される。

また、FET2、FET4、FET6がオンであって電流が導通することから、エネルギ移行用キャパシタC0aのFET4側接続端子の電位はおよそVL、FET2側接続端子の電位はエネルギ移行用キャパシタC0bのFET2側接続端子の電位とほぼ等しくなる。また、エネルギ移行用キャパシタC0bのFET6側接続端子の電位はおよそ−V2となる。

よって、インダクタLのFET4側接続端子の電圧VLは、VL=(−V2+Vc0b−Vc0a)となる。

【0166】

ここで、Gate1信号、Gate2信号、Gate3信号のオンデューティは等しい。その動作より、スイッチングモードF、G、Hにおける電圧VLは時間平均的に等しく、V1−Vc0b=−V2+Vc0b−Vc0a=−V2+Vc0aの関係となる。よって、Vc0b=(2/3)・(V1+V2)、Vc0a=(1/3)・(V1+V2) となる。

このことから、インダクタLの両端の電位差と、FET1、FET2、FET3のスイッチオン時間ton、スイッチオフ時間toffは、次の関係で表される。

【0167】

スイッチングモードF、G、H: L・ILrpl=ton・(V1−2・V2)/3

・・(8a)

スイッチングモードE: L・ILrpl=−toff・(−V2) ・・(8b)

【0168】

式(8a)と式(8b)との左辺同士が等しいことから、次の関係が成り立つ。

【0169】

ton・(V1−2・V2)/3=−toff・(−V2) ・・(9)

【0170】

上の式(9)を一次側端子電圧V1と二次側端子電圧V2について整理すると次のようになる。

【0171】

(V2/V1)=ton/(3・toff+2・ton)=ton/((2/3)・T+toff)

= (ton/T)/(1−ton/T) ・・(10)

但し、ton+toff=T/3

【0172】

上の式(10)で、周期Tは、スイッチングモードH→E→G→E→F→E→H の順に切替わって一周する期間を示しており、T/3=ton+toffである。式(10)の左辺(V2/V1)はDC/DC電圧変換比である。

図23に示されるゲート駆動信号のオンデューティが100/3%未満の動作では、(ton/T)<(1/3)であり、式(10)に当てはめると、DC/DC電圧変換比は、1/2未満となる。よって、V2<(V1/2)である。

【0173】

これらから、スイッチングモードF、G、Hでは、インダクタLのFET4側接続端子の電圧VLはVL=(V1−2・V2)/3>0、インダクタLの負極側端子N1側の接続端子の電圧が0である。

よって、インダクタLの両端間の電位差は正となり、インダクタ電流ILは正の方向へ増加する。また、上述の通りスイッチングモードEでは、インダクタ電流ILは、IL≧0の状態で、負の方向へ向けて変化する。

【0174】

以上のように、スイッチングモードH→E→G→E→F→E→Hの切替わりにおいて、

スイッチングモードF、G、Hでは、インダクタ電流ILは、IL≧0の状態から更に正の方向へ増加するよう変化し、

スイッチングモードEでは、インダクタ電流ILは、IL<0の状態に向けて変化する。

このことから、電界効果トランジスタのスイッチング周期Tに亘ってインダクタ電流ILの増加、減少はT/3周期で3回繰り返されることとなる。

従って、電界効果トランジスタのスイッチング周波数に対してインダクタLには3倍の周波数の交流電流が導通することとなる。

【0175】

2)オンデューティが100/3%以上かつ50%未満で降圧動作の場合:

次に、ゲート駆動信号のオンデューティが100/3%以上かつ50%未満で降圧動作時である場合について説明する。

図24(a)において、Gate1信号がハイの場合にFET1が、Gate2信号がハイの場合にFET2が、Gate3信号がハイの場合にFET3がオンし、ドレインからソースに向けて電流が流れる。

また、Gate4信号がハイの場合にFET4が、Gate5信号がハイの場合にFET5が、Gate6信号がハイの場合にFET6がオンするが、力行動作時には電流がソースからドレインに向けてFET4、FET5、FET6に内在する寄生ダイオードの替わりにトランジスタ部分を流れる。

【0176】

Gate1信号とGate6信号、Gate2信号とGate5信号、Gate3信号とGate4信号は、互いにハイ、ローの論理が相反する相補信号であり、ゲート駆動信号8は相補信号として対を成す信号が3通り有って、互いの位相差が等間隔となっている。

この時、Gate1からGate6のゲート駆動信号のハイ、ローの論理の組合わせは、スイッチングモードF、G、H、I、J、Kの6種に分類され、G→J→H→K→F→I→Gの順に切替わる。

【0177】

スイッチングモードF、G、Hでの各電界効果トランジスタの状態、電流の導通経路、インダクタLのFET4側接続端子の電圧VLは、上述の力行動作時の1)項 オンデューティが100/3%未満である場合と同じであるため、説明を省略する。

【0178】

スイッチングモードIでは、FET1、FET2、FET4がオン、FET3、FET5、FET6がオフであって、

電流が、正極側端子P1→FET1→FET2→エネルギ移行用キャパシタC0a→FET4→インダクタL→負極側端子N1の経路に流れ、エネルギ移行用キャパシタC0aにエネルギが蓄えられる。

電気機器5には平滑キャパシタC2の両端電圧が印加され、平滑キャパシタC2からエネルギが供給される。

FET1、FET2、FET4がオンして電流が導通することから、エネルギ移行用キャパシタC0aのFET2側接続端子の電位はおよそV1、FET4側接続端子の電位はおよそVLとなる。よって、インダクタLのFET4側接続端子の電圧VLは、VL=V1−Vc0aとなる。インダクタLの負極側端子N1側接続端子の電圧は0であり、インダクタLのFET4側接続端子の電圧VLと負極側端子N1側の接続端子の電圧の差は、(V1−Vc0a)である。

【0179】

スイッチングモードJでは、FET2、FET3、FET6がオン、FET1、FET4、FET5がオフであって、

電流が、負極側端子N2→FET6→エネルギ移行用キャパシタC0b→FET2→FET3→インダクタL→正極側端子P2→電気機器5→負極側端子N2の経路に流れ、エネルギ移行用キャパシタC0bからはエネルギが放出される。また、同時に平滑キャパシタC2にも電流が流れてエネルギが蓄えられる。

FET2、FET3、FET6がオンして電流が導通することから、インダクタLのFET4側接続端子の電圧VLは、エネルギ移行用キャパシタC0bのFET2と接続する高電位側端子の電位と等しくなる。また、エネルギ移行用キャパシタC0bのFET6と接続する低電位側端子の電位は、負極側端子N2の電圧−V2と等しくなる。よって、インダクタLのFET4側接続端子の電圧VLはVL=−V2+Vc0bとなり、インダクタLの電圧VLと負極側端子N1側の接続端子の電圧との差は、(−V2+Vc0b−0)である。

【0180】

スイッチングモードKでは、FET1、FET3、FET5がオン、FET2、FET4、FET6がオフであって、

電流が、正極側端子P1→FET1→エネルギ移行用キャパシタC0b→FET5→エネルギ移行用キャパシタC0a→FET3→インダクタL→負極側端子N1の経路に流れ、エネルギがエネルギ移行用キャパシタC0aから放出され、エネルギ移行用キャパシタC0bに蓄えられる。電気機器5には、平滑キャパシタC2の両端電圧が印加され、平滑キャパシタC2からエネルギが供給される。

【0181】

FET1、FET3、FET5がオンして電流が導通することから、エネルギ移行用キャパシタC0aのFET5側接続端子の電位は、エネルギ移行用キャパシタC0bのFET5側接続端子の電位と等しくなる。

また、エネルギ移行用キャパシタC0aのFET3側接続端子の電位は、およそVLとなる。エネルギ移行用キャパシタC0bのFET1側接続端子の電位は、およそV1となる。

よって、インダクタLのFET3側接続端子の電圧VLは、VL=(V1−Vc0b+Vc0a)となる。

よって、インダクタLのFET3側接続端子の電圧VLと負極側端子N1側の接続端子の電圧との差は、(V1−Vc0b+Vc0a)である。

【0182】

ここで、Gate1信号、Gate2信号、Gate3信号のオンデューティは等しい。その動作より、スイッチングモードF、G、Hにおける電圧VLは時間平均的に等しく、V1−Vc0b=−V2+Vc0b−Vc0a=−V2+Vc0aの関係となる。これから、Vc0b=2・Vc0aである。

また、スイッチングモードI、J、Kにおける電圧VLは時間平均的に等しく、V1−Vc0a=(−V2+Vc0b)=(V1−Vc0b+Vc0a)の関係となる。これらより、ゲート駆動信号のオンデューティが100/3%未満である場合と同様に、Vc0b=(2/3)・(V1+V2)、Vc0a=(1/3)・(V1+V2) となる。

このことから、インダクタLの両端の電位差、FET1、FET2、FET3のスイッチオン時間ton、スイッチオフ時間toffは、次の関係で表される。

【0183】

スイッチングモードF、G、H:

L・ILrpl=(T/3−ton+T/3)・(V1−2・V2)/3

=(2・T/3−ton)・(V1−2・V2)/3 ・・(11a)

スイッチングモードI、J、K:

L・ILrpl=−(ton−T/3)・(2・V1−V2)/3 ・・(11b)

但し、ton+toff=T

【0184】

式(11a)と式(11b)の左辺同士が等しいことから、次の関係が成り立つ。

【0185】

(2・T/3−ton)・(V1−2・V2)/3

=−(ton−T/3)・(2・V1−V2)/3 ・・(12)

【0186】

上の式(12)を一次側端子電圧V1と二次側端子電圧V2について整理すると次のようになる。

【0187】

(V2/V1)=ton/(T−ton)=(ton/T)/(1−ton/T)

・・(13)

但し、ton+toff=T

【0188】

上の式(13)で、周期Tは、スイッチングモードG→J→H→K→F→I→Gの順に切替わって一周する期間を示しており、T=ton+toffである。式(13)の左辺(V2/V1)はDC/DC電圧変換比である。

図24に示されるゲート駆動信号のオンデューティが100/3%以上かつ50%未満の動作では、(1/3)≦(ton/T)<(1/2)であり、式(13)に当てはめると、DC/DC電圧変換比は、1/2以上で1未満となる。よって、(V1/2)≦V2<V1である。

【0189】

これらから、スイッチングモードF、G、Hでは、インダクタLのFET4側接続端子の電圧VLは0から(−V1/3)の範囲、インダクタLの負極側端子N1側の接続端子の電圧が0である。よって、インダクタLの両端間の電位差は負となり、インダクタ電流ILは、IL≧0の状態で、負の方向へ向けて変化する。

また、スイッチングモードI、J、Kでは、インダクタLのFET4側接続端子の電圧VLはV1/2からV1/3の範囲、インダクタLの負極側端子N1側の接続端子の電圧が0である。よって、インダクタLの両端間の電位差は正となり、インダクタ電流ILは正の方向に増加する。

【0190】

以上のように、スイッチングモードG→J→H→K→F→I→Gの切替わりにおいて、

スイッチングモードF、G、Hでは、インダクタ電流ILは、IL≧0の状態からIL<0の状態に向けて変化し、

スイッチングモードI、J、Kでは、インダクタ電流ILは、更に正の方向へ増加するよう変化する。

このことから、電界効果トランジスタのスイッチング周期Tに亘ってインダクタ電流ILの増加、減少はT/3周期で3回繰り返されることとなる。従って、電界効果トランジスタのスイッチング周波数に対してインダクタLには3倍の周波数の交流電流が導通することとなる。

【0191】

3)オンデューティが50%以上かつ100×(2/3)%未満で昇圧動作の場合:

次に、力行動作時でゲート駆動信号のオンデューティが50%以上かつ100×(2/3)%未満である場合について説明する。

図25(a)において、Gate1信号がハイの場合にFET1が、Gate2信号がハイの場合にFET2が、Gate3信号がハイの場合にFET3がオンし、ドレインからソースに向けて電流が流れる。

また、Gate4信号がハイの場合にFET4が、Gate5信号がハイの場合にFET5が、Gate6信号がハイの場合にFET6がオンするが、力行動作時には電流がソースからドレインに向けてFET4、FET5、FET6に内在する寄生ダイオードの替わりにトランジスタ部分を流れる。

【0192】

上述の力行動作時の2)項 オンデューティが100/3%以上かつ50%未満で降圧動作の場合と同様に、

Gate1信号とGate6信号、Gate2信号とGate5信号、Gate3信号とGate4信号は、互いにハイ、ローの論理が相反する相補信号であり、ゲート駆動信号8は相補信号として対を成す信号が3通り有って、互いの位相差が等間隔となっている。

この時、Gate1からGate6のゲート駆動信号のハイ、ローの論理の組合わせは、スイッチングモードF、G、H、I、J、Kの6種に分類され、G→J→H→K→F→I→Gの順に切替わる。

【0193】

スイッチングモードF、G、H、I、J、Kでの各電界効果トランジスタの状態、電流の導通経路、インダクタLのFET4側接続端子の電圧VLは、上述の力行動作時の2)項 オンデューティが100/3%以上かつ50%未満で降圧動作の場合と同じであるため、説明を省略する。

これらより、インダクタLの両端の電位差、FET1、FET2、FET3のスイッチオン時間ton、スイッチオフ時間toffの関係は、同様に、式(11a)、式(11b)、式(12)で表される。よって、一次側端子電圧V1と二次側端子電圧V2について、DC/DC電圧変換比(V2/V1)は式(13)のように表される。

【0194】

上の式(13)で、周期Tは、スイッチングモードG→J→H→K→F→I→Gの順に切替わって一周する期間を示しており、T=ton+toffである。

図25に示されるゲート駆動信号の50%以上かつ100×(2/3)%未満の動作では、(1/2)≦(ton/T)<(2/3)であり、式(13)に当てはめると、DC/DC電圧変換比は、1以上で2未満となる。よって、V1≦V2<(2・V1)である。

【0195】

これらから、スイッチングモードF、G、Hでは、インダクタLのFET4側接続端子の電圧VLは(−V1/3)から(−V1)の範囲、インダクタLの負極側端子N1側の接続端子の電圧が0である。よって、インダクタLの両端間の電位差は負となり、インダクタ電流ILは、IL≧0の状態で、負の方向へ向けて変化する。

また、スイッチングモードI、J、Kでは、インダクタLのFET4側接続端子の電圧VLは(V1/3)から0の範囲、インダクタLの負極側端子N1側の接続端子の電圧が0である。よって、インダクタLの両端間の電位差は正となり、インダクタ電流ILは正の方向に増加する。

【0196】

以上のように、上述の力行動作時の2)項 オンデューティが100/3%以上かつ50%未満で降圧動作の場合と同じく、スイッチングモードG→J→H→K→F→I→Gの切替わりにおいて、

スイッチングモードF、G、Hでは、インダクタ電流ILは、IL≧0の状態からIL<0の状態に向けて変化し、

スイッチングモードI、J、Kでは、インダクタ電流ILは、更に正の方向へ増加するよう変化する。

このことから、電界効果トランジスタのスイッチング周期Tに亘ってインダクタ電流ILの増加、減少はT/3周期で3回繰り返されることとなる。

従って、電界効果トランジスタのスイッチング周波数に対してインダクタLには3倍の周波数の交流電流が導通することとなる。

【0197】

4)オンデューティが100×(2/3)%以上で昇圧動作の場合:

次に、力行動作時でゲート駆動信号のオンデューティが100×(2/3)%以上である場合について説明する。

図26(a)において、Gate1信号がハイの場合にFET1が、Gate2信号がハイの場合にFET2が、Gate3信号がハイの場合にFET3がオンし、ドレインからソースに向けて電流が流れる。

また、Gate4信号がハイの場合にFET4が、Gate5信号がハイの場合にFET5が、Gate6信号がハイの場合にFET6がオンするが、力行動作時には電流がソースからドレインに向けてFET4、FET5、FET6に内在する寄生ダイオードの替わりにトランジスタ部分を流れる。

【0198】

Gate1信号とGate6信号、Gate2信号とGate5信号、Gate3信号とGate4信号とは、互いにハイ、ローの論理が相反する相補信号であり、ゲート駆動信号8は相補信号として対を成す信号が3通り有って、互いの位相差が等間隔となっている。

この時、Gate1からGate6のゲート駆動信号のハイ、ローの論理の組合わせは、スイッチングモードI、J、K、Mの4種に分類され M→K→M→I→M→J→M の順に切替わる。

【0199】

スイッチングモードI、J、Kでの各電界効果トランジスタの状態、電流の導通経路、インダクタLのFET4側接続端子の電圧VLは、上述の力行動作時の2)項 オンデューティが100/3%以上かつ50%未満で降圧動作の場合と同じであるため、説明を省略する。

【0200】

スイッチングモードMでは、FET1、FET2、FET3がオン、FET4、FET5、FET6がオフであって、

電流が、正極側端子P1→FET1→FET2→FET3→インダクタL→負極側端子N1の経路に流れ、インダクタLにエネルギが蓄えられる。

また、FET1、FET2、FET3がオンして電流が導通することより、電圧VLはおよそV1となる。インダクタLのFET3側接続端子の電圧VLと負極側端子N1側の接続端子の電圧との差は、(V1−0)で正となり、インダクタ電流ILは更に正の方向に増加する。

電気機器5には、平滑キャパシタC2の両端電圧が印加され、平滑キャパシタC2からエネルギが供給される。

【0201】

ここで、Gate1信号、Gate2信号、Gate3信号のオンデューティは等しい。その動作より、スイッチングモードI、J、Kにおける電圧VLは時間平均的に等しく (V1−Vc0a)=(−V2+Vc0b)=(V1−Vc0b+Vc0a) の関係となる。

よって、ゲート駆動信号のオンデューティが100/3%以上で50%未満である場合と同様に、Vc0b=(2/3)・(V1+V2)、Vc0a=(1/3)・(V1+V2) となる。

このことから、インダクタLの両端の電位差、FET1、FET2、FET3のスイッチオン時間ton、スイッチオフ時間toffは、次の関係で表される。

【0202】

スイッチングモードM: L・ILrpl=(T/3−toff)・V1・・(14a)

スイッチングモードI、J、K:L・ILrpl=−toff・(2・V1−V2)/3 ・・(14b)但し、ton+toff=T

【0203】

式(14a)と式(14b)の左辺同士が等しいことから、次の関係が成り立つ。

【0204】

(T/3−toff)・V1=−toff・(2・V1−V2)/3 ・・(15)

【0205】

上の式(15)を一次側端子電圧V1と二次側端子電圧V2について整理すると次のようになる。

【0206】

(V2/V1)=(T−toff)/toff=ton/(T−ton)

=(ton/T)/(1−ton/T) ・・(16)

但し、ton+toff=T

【0207】

上の式(16)で周期Tは、スイッチングモードM→K→M→I→M→J→Mの順に切替わって一周する期間を示しており、T=ton+toffである。式(16)の左辺(V2/V1)はDC/DC電圧変換比である。

図26に示されるゲート駆動信号のオンデューティが100×(2/3)%以上の動作では、(2/3)≦(ton/T)であり、式(16)に当てはめると、DC/DC電圧変換比は2以上となる。よって、(2・V1)≦V2である。

【0208】

これらから、スイッチングモードI、J、Kでは、インダクタLのFET4側接続端子の電圧VLは、VL=(2・V1−V2)/3<0である。インダクタLの負極側端子N1側の接続端子の電圧は0である。

よって、インダクタLの両端間の電位差は負となり、インダクタ電流ILは、IL≧0の状態で、負の方向へ向けて変化する。

また、上述の通りスイッチングモードMではインダクタ電流ILは更に正の方向に増加する。

【0209】

以上のように、スイッチングモードM→K→M→I→M→J→Mの切替わりにおいて、

スイッチングモードI、J、Kでは、インダクタ電流ILは、IL≧0の状態からIL<0の状態に向けて変化し、

スイッチングモードMでは、インダクタ電流ILは、IL≧0の状態から更に正の方向に増加する。

このことから、電界効果トランジスタのスイッチング周期Tに亘ってインダクタ電流ILの増加、減少はT/3周期で3回繰り返されることとなる。

従って、電界効果トランジスタのスイッチング周波数に対してインダクタLには3倍の周波数の交流電流が導通することとなる。

また、式(10)、式(13)、式(16)は等しいものであり、即ち、オンデューティが何れの値であっても無関係にオンデューティの変化に合わせて連続的にDC/DC電圧変換比は調整される。

【0210】

次に、回生動作時について説明する。

回生動作時:

本実施の形態においても、実施の形態1で説明した力行時と回生時との動作の対称性を持つ。本実施の形態での回生時の動作はDC/DC電圧変換装置1の二次側に接続した電気機器5が発生する電力をV2からV1へDC/DC電圧変換して直流電源4で回収する。

この際、降圧動作では電圧V1>電圧V2の関係で、昇圧動作では電圧V1≦電圧V2の関係で、DC/DC電圧変換を行う。

ゲート駆動信号8の波形は、図27(a)、図28(a)、図29(a)、図30(a)に示されるものであって、力行動作時と同じである。即ち、

図27(a)は、ゲート駆動信号のオンデューティが100/3%未満の場合、

図28(a)は、ゲート駆動信号のオンデューティが100/3%以上かつ50%未満の場合、

図29(a)は、ゲート駆動信号のオンデューティが50%以上かつ100×(2/3)%未満の場合、

図30(a)は、ゲート駆動信号のオンデューティが100×(2/3)%以上の場合のゲート駆動信号の波形となる。

【0211】

1)オンデューティが100/3%未満で降圧動作の場合:

二次側から一次側へ電力を供給する回生動作時であって、二次側電圧V2<一次側電圧V1の降圧を行うオンデューティが100/3%未満の動作について説明する。尚、二次側電圧V2を基にすれば、V1/V2>1の関係の昇圧となる。

図27(a)において、Gate4信号がハイの場合にFET4が、Gate5信号がハイの場合にFET5が、Gate6信号がハイの場合にFET6がオンし、ドレインからソースに向けて電流が流れる。

また、Gate1信号がハイの場合にFET1が、Gate2信号がハイの場合にFET2が、Gate3信号がハイの場合にFET3がオンするが、回生動作時には電流がソースからドレインに向けてFET1、FET2、FET3に内在する寄生ダイオードの替わりにトランジスタ部分を流れる。

【0212】

Gate1からGate6のゲート駆動信号のハイ、ローの論理の組合わせは、ゲート駆動信号のオンデューティが100/3%未満では図27(c)の、ゲート駆動信号のオンデューティが100/3%以上かつ50%未満では図28(c)の、ゲート駆動信号のオンデューティが50%以上かつ100×(2/3)%未満では図29(c)の、ゲート駆動信号のオンデューティが100×(2/3)%以上では図30(c)の通りとなる。

即ち、スイッチングモードは E、F、G、H、I、J、K、Mの8通りとなる。

【0213】

スイッチングモードEでは、

電流が、正極側端子P2→インダクタL→FET4→FET5→FET6→負極側端子N2→電気機器5→正極側端子P2の経路に流れ、インダクタLにエネルギが蓄えられる。また、FET4、FET5、FET6がオンして電流が導通することから、電圧VLはおよそ−V2となる。また、二次側の正極側端子P2は一次側の負極側端子N1と接続しているため、インダクタLのFET4側接続端子の電圧VLと正極側端子P2側の接続端子の電圧との差は(−V2−0)で負となり、インダクタ電流ILは、IL<0の状態で更に負の方向に増加する。

【0214】

スイッチングモードFでは、

電流が、負極側端子N1→インダクタL→FET4→FET5→エネルギ移行用キャパシタC0b→FET1→正極側端子P1→直流電源4→負極側端子N1の経路に流れ、エネルギがエネルギ移行用キャパシタC0bから放出される。平滑キャパシタC2には電気機器5の両端電圧が印加され、電気機器5からの発電エネルギが供給される。

また、FET1、FET4、FET5がオンであって電流が導通することから、エネルギ移行用キャパシタC0bのFET5側接続端子の電位はおよそVL、FET1側接続端子の電位はおよそV1となる。

よって、インダクタLのFET4側接続端子の電圧VLは、VL=V1−Vc0bとなる。

【0215】

スイッチングモードGでは、

正極側端子P2→インダクタL→FET4→エネルギ移行用キャパシタC0a→FET2→エネルギ移行用キャパシタC0b→FET6→負極側端子N2→電気機器5→正極側端子P2の経路に流れ、エネルギはエネルギ移行用キャパシタC0aから放出され、エネルギ移行用キャパシタC0bに蓄えられる。

また、FET2、FET4、FET6がオンして電流が導通することから、電圧VLはおよそ(−V2+Vc0b−Vc0a)となる。

【0216】

スイッチングモードHでは、

電流が、正極側端子P2→インダクタL→FET3→エネルギ移行用キャパシタC0a→FET5→FET6→負極側端子N2→電気機器5→正極側端子P2の経路に流れ、エネルギがエネルギ移行用キャパシタC0aに蓄えられる。

また、FET3、FET5、FET6がオンして電流が導通することから、電圧VLはおよそ(−V2+Vc0a)となる。

【0217】

スイッチングモードIでは、

電流が、インダクタL→FET4→エネルギ移行用キャパシタC0a→FET2→FET1→正極側端子P1→直流電源4→負極側端子N1→インダクタLの経路に流れ、エネルギ移行用キャパシタC0aからエネルギが放出される。

また、FET1、FET2、FET4がオンして電流が導通することから、電圧VLはおよそ、(V1−Vc0a)となる。

【0218】

スイッチングモードJでは、

電流が、正極側端子P2→インダクタL→FET3→FET2→エネルギ移行用キャパシタC0b→FET6→負極側端子N2→電気機器5→正極側端子P2の経路に流れ、エネルギがエネルギ移行用キャパシタC0bに蓄えられる。

また、FET2、FET3、FET6がオンして電流が導通することから、電圧VLはおよそ(−V2+Vc0b)となる。

【0219】

スイッチングモードKでは、

電流が、インダクタL→FET3→エネルギ移行用キャパシタC0a→FET5→エネルギ移行用キャパシタC0b→FET1→正極側端子P1→直流電源4→負極側端子N1→インダクタLの経路に流れ、

エネルギがエネルギ移行用キャパシタC0bから放出しエネルギ移行用キャパシタC0aに蓄えられる。

また、FET1、FET3、FET5がオンして電流が導通することから、電圧VLはおよそ(V1−Vc0b+Vc0a)となる。

【0220】

スイッチングモードMでは、

電流が、インダクタL→FET3→FET2→FET1→正極側端子P1→直流電源4→負極側端子N1→インダクタLの経路に流れ、エネルギがインダクタLから放出される。

また、FET1、FET2、FET3がオンして電流が導通することから、電圧VLはおよそ、V1となる。

インダクタLのFET3側接続端子の電圧VLと負極側端子N1側の接続端子の電圧との差は(V1−0)で正となり、インダクタ電流ILは、IL<0の状態で正の方向に向けて変化する。

【0221】

続いて、ゲート駆動信号のオンデューティの各範囲と、対応するスイッチングモードの切替わりについて説明する。

1)オンデューティが100/3%未満で降圧動作の場合:

ゲート駆動信号のオンデューティが100/3%未満では図27(c)に示されるように、スイッチングモードH→E→G→E→F→E→Hの順に切替わって、周期Tで一周する。

力行動作時と同様に、スイッチングモードF、G、Hにおける電圧VLは時間平均的に等しく、(V1−Vc0b)=(−V2+Vc0b−Vc0a)=(−V2+Vc0a)の関係となる。よって、Vc0b=(2/3)・(V1+V2)、Vc0a=(1/3)・(V1+V2) となる。

インダクタLの両端の電位差、FET1、FET2、FET3のスイッチオン時間ton、スイッチオフ時間toff、一次側端子電圧V1、二次側端子電圧V2には、式(8a)、式(8b)、式(9)の関係が成り立つ。

【0222】

従って、DC/DC電圧変換装置1の電圧変換比(V2/V1)は、式(10)で示されるものとなる。

ゲート駆動信号のオンデューティが100/3%未満の動作では、(ton/T)<(1/3)であり、式(10)に当てはめるとDC/DC電圧変換比は1/2未満となる。よって、V2<(V1/2)である。即ち、二次側端子電圧V2は、一次側端子電圧V1の1/2倍よりも低い電圧へ降圧される。

【0223】

これらから、スイッチングモードF、G、Hでは、インダクタLのFET4側接続端子の電圧VL=(V1−2・V2)/3>0、インダクタLの負極側端子N1側接続端子の電圧が0である。よって、インダクタLの両端間の電位差は正となり、インダクタ電流ILは正の方向へ向けて変化する。

スイッチングモードEでは、上述のように、IL<0の状態で更に負の方向に増加する。

以上のように、スイッチングモードH→E→G→E→F→E→Hの切替わりにおいて、

スイッチングモードF、G、Hでは、インダクタ電流ILは、IL<0の状態からIL≧0の状態に向けて変化し、

スイッチングモードEでは、インダクタ電流ILは、IL<0の状態から、更に負の方向に向けて増加する。

このことから、電界効果トランジスタのスイッチング周期Tに亘ってインダクタ電流ILの増加、減少はT/3周期で3回繰り返され、インダクタLには電界効果トランジスタのスイッチング周波数に対して3倍の周波数の交流電流が導通することとなる。

【0224】

2)オンデューティが100/3%以上かつ50%未満で降圧動作の場合:

次に、ゲート駆動信号のオンデューティが100/3%以上で50%未満である場合は、図28(c)に示されるように、スイッチングモードG→J→H→K→F→I→Gの順に切替わって、周期Tで一周する。

力行動作時と同様に、スイッチングモードF、G、Hにおける電圧VLは時間平均的に等しく、(V1−Vc0b)=(−V2+Vc0b−Vc0a)=(−V2+Vc0a) となる。

また、スイッチングモードI、J、Kにおける電圧VLも時間平均的に等しく、 (V1−Vc0a)=(−V2+Vc0b)=(V1−Vc0b+Vc0a)の関係となる。これらより、ゲート駆動信号のオンデューティが100/3%未満である場合と同様に、エネルギ移行用キャパシタの両端の電圧は、Vc0b=(2/3)・(V1+V2)、Vc0a=(1/3)・(V1+V2)となる。

これより、 インダクタLの両端の電位差、FET1、FET2、FET3のスイッチオン時間ton、スイッチオフ時間toff、一次側接続端子電圧V1、二次側接続端子電圧V2には式(11a)、式(11b)、式(12)の関係が成り立つ。

【0225】

従って、DC/DC電圧変換装置1の電圧変換比(V2/V1)は、式(13)で示されるものとなる。

ゲート駆動信号のオンデューティが100/3%以上で50%未満である動作では、(1/3)≦(ton/T)<(1/2)であり、式(13)に当てはめるとDC/DC電圧変換比は、1/2以上で1未満となる。よって、(V1/2)≦V2<V1である。即ち、二次側端子電圧V2は一次側端子電圧V1の(1/2)倍以上で1倍未満の電圧へ降圧される。

【0226】

これらから、スイッチングモードF、G、Hでは、インダクタLのFET4側接続端子の電圧VLは0から(−V1/3)の範囲であり、インダクタLの負極側端子N1側の接続端子の電圧が0である。よって、インダクタLの両端間の電位差は負となり、インダクタ電流ILは更に負の方向へ増加する。

スイッチングモードI、J、Kでは、インダクタLのFET4側接続端子の電圧VLは(V1/2)から(V1/3)の範囲であり、インダクタLの負極側端子N1側の接続端子の電圧が0である。よって、インダクタLの両端間の電位差は正となり、インダクタ電流ILは、IL<0の状態で正の方向へ向けて変化する。

【0227】

以上のように、スイッチングモードG→J→H→K→F→I→Gの切替わりにおいて、

スイッチングモードF、G、Hでは、インダクタ電流ILは、IL<0の状態から、更に負の方向に向けて増加し、

スイッチングモードI、J、Kでは、インダクタ電流ILは、IL<0の状態から、IL≧0の状態に向けて変化する。

このことから、電界効果トランジスタのスイッチング周期Tに亘ってインダクタ電流ILの増加、減少はT/3周期で3回繰り返され、インダクタLには電界効果トランジスタのスイッチング周波数に対して3倍の周波数の交流電流が導通することとなる。

【0228】

3)オンデューティが50%以上かつ100×(2/3)%未満で昇圧動作の場合:

次に、ゲート駆動信号のオンデューティが50%以上かつ100×(2/3)%未満である場合は、図29(c)に示されるように、スイッチングモードG→J→H→K→F→I→Gの順に切替わって、周期Tで一周する。

上述の回生動作時の2)項 オンデューティが100/3%以上かつ50%未満で降圧動作の場合と同様に、スイッチングモードF、G、Hにおける電圧VLは時間平均的に等しく、(V1−Vc0b)=(−V2+Vc0b−Vc0a)=(−V2+Vc0a)となる。

また、スイッチングモードI、J、Kにおける電圧VLも時間平均的に等しく、(V1−Vc0a)=(−V2+Vc0b)=(V1−Vc0b+Vc0a)の関係となる。これらより、ゲート駆動信号のオンデューティが100/3%未満である場合と同様に、エネルギ移行用キャパシタの両端の電圧は、Vc0b=(2/3)・(V1+V2)、

Vc0a=(1/3)・(V1+V2) となる。

よって、インダクタLの両端の電位差、FET1、FET2、FET3のスイッチオン時間ton、スイッチオフ時間toff、一次側接続端子電圧V1、二次側接続端子電圧V2についても同様に、式(11a)、式(11b)、式(12)の関係が成り立つ。

【0229】

従って、DC/DC電圧変換装置1の電圧変換比(V2/V1)は式(13)で示され、

ゲート駆動信号のオンデューティが50%以上かつ100×(2/3)%未満である動作では、(1/2)≦(ton/T)<(2/3)であり、式(13)に当てはめるとDC/DC電圧変換比は、1以上で2未満となる。よって、V1≦V2<(2・V1)である。即ち、二次側端子電圧V2は一次側端子電圧V1の1倍より高く2倍未満の電圧へ昇圧される。

【0230】

これらから、スイッチングモードF、G、Hでは、インダクタLのFET4側接続端子の電圧VLは(−V1/3)から(−V1)の範囲であり、インダクタLの負極側端子N1側の接続端子の電圧が0である。よって、インダクタLの両端間の電位差は負となり、インダクタ電流ILは更に負の方向へ増加する。

スイッチングモードI、J、Kでは、インダクタLのFET4側接続端子の電圧VLは0から(V1/3)の範囲であり、インダクタLの負極側端子N1側の接続端子の電圧が0である。よって、インダクタLの両端間の電位差は正となり、インダクタ電流ILは、IL<0の状態で正の方向へ向けて変化する。

【0231】

以上のように、上述の回生動作時の2)項 オンデューティが100/3%以上かつ50%未満で降圧動作の場合と同じく、スイッチングモードG→J→H→K→F→I→Gの切替わりにおいて、

スイッチングモードF、G、Hでは、インダクタ電流ILは、IL<0の状態から、更に負の方向に向けて増加し、

スイッチングモードI、J、Kでは、インダクタ電流ILは、IL<0の状態から、IL≧0の状態に向けて変化する。

このことから、電界効果トランジスタのスイッチング周期Tに亘ってインダクタ電流ILの増加、減少はT/3周期で3回繰り返され、インダクタLには電界効果トランジスタのスイッチング周波数に対して3倍の周波数の交流電流が導通することとなる。

【0232】

4)オンデューティが100×(2/3)%以上で昇圧動作の場合:

更に、ゲート駆動信号のオンデューティが100×(2/3)%以上である場合は、図30(c)に示されるように、スイッチングモードM→K→M→I→M→J→Mの順に切替わって、周期Tで一周する。

力行動作時と同様に、スイッチングモードI、J、Kにおける電圧VLは時間平均的に等しく、(V1−Vc0a)=(−V2+Vc0b)=(V1−Vc0b+Vc0a) の関係となる。

よって、Vc0b=(2/3)・(V1+V2)、

Vc0a=(1/3)・(V1+V2) となる。

インダクタLの両端の電位差、FET1、FET2、FET3のスイッチオン時間ton、スイッチオフ時間toff、一次側端子電圧V1、二次側端子電圧V2には、力行動作時と同様に、式(14a)、式(14b)、式(15)の関係が成り立つ。

【0233】

従って、DC/DC電圧変換装置1の電圧変換比(V2/V1)は、式(16)で示されるものとなる。

ゲート駆動信号のオンデューティが100×(2/3)%以上の動作では、(2/3)≦(ton/T)であり、式(16)に当てはめるとDC/DC電圧変換比は2以上となる。よって、(2×V1)≦V2である。即ち、二次側端子電圧V2は、一次側端子電圧V1の2倍より高い電圧へ昇圧される。

【0234】

これらから、スイッチングモードI、J、Kでは、インダクタLのFET4側接続端子の電圧VLはVL≦0、インダクタLの負極側端子N1側の接続端子の電圧が0である。よって、インダクタLの両端間の電位差は負となり、インダクタ電流ILは更に負の方向へ増加する。

スイッチングモードMでは、上述のようにインダクタ電流ILは、IL<0の状態からIL≧0の状態へ向けて変化する。

【0235】

以上のように、スイッチングモードM→K→M→I→M→J→Mの切替わりにおいて、

スイッチングモードI、J、Kでは、インダクタ電流ILは、更に負の方向へ増加し、

スイッチングモードMでは、インダクタ電流ILは、IL<0の状態から、IL≧0の状態へ向けて変化する。

このことから、電界効果トランジスタのスイッチング周期Tに亘ってインダクタ電流ILの増加、減少はT/3周期で3回繰り返され、インダクタLには、電界効果トランジスタのスイッチング周波数に対して3倍の周波数の交流電流が導通することとなる。

【0236】

以上で説明した動作内容の通り、本実施の形態4のDC/DC電圧変換装置は、力行動作時と回生動作時のいずれの場合も電界効果トランジスタのスイッチング周波数に対してインダクタLには3倍の周波数の交流電流が導通する。

従って、実施の形態1でのDC/DC電圧変換装置と比較して、インダクタLのリップル電流成分の周波数が更に高くなるため、インダクタLのインダクタンスを下げることが可能となり、インダクタの容積と重量が従来技術に基づくものに比べ格段に低減する。

【0237】

また、実施の形態1の変形例として説明したように、インダクタLに流れる交流成分の周波数を、可聴周波数の上限以上と設定する場合等も、電界効果トランジスタのスイッチング周波数を実施の形態1の場合より低い値に設定してもよいので、そのスイッチング損失等を実施の形態1の場合より低減させることができるという利点がある。

【0238】

更に、この他にも実施の形態1と同様の効果を得ることができる。即ち、電界効果トランジスタには、ワイドバンドギャップの半導体材料によるものを適用することから、DC/DC電圧変換装置の出力電力容量を増加して半導体ユニットで生じる損失が増えたとしても、半導体ユニットの耐熱温度が高くなることから、取り扱い可能な出力電力容量を拡大し、電力密度が向上しつつも、小型で軽量なDC/DC電圧変換装置を実現可能である。

また、インダクタLとエネルギ移行用キャパシタC0a、C0b、平滑キャパシタC1、C2で顕著であった耳障りな可聴騒音の発生を解消または低減できる。

【0239】

以上のように、本発明に関する実施例を実施の形態1から実施の形態4によって説明したが、これらは本発明の好適な実施事例を例示したものに過ぎない。

例えば、可聴周波数の上限を20kHzとしたが、DC/DC電圧変換装置の可聴騒音の問題を解消するという目的のもとで、指標とする可聴周波数の上限は、また別な値へ設定され得る。

本発明は、これら実施の形態の構成、動作に限定されるものでなく、本発明の範囲内にある限り、別な構成、動作へ変更を加えて実施してもよい。

【符号の説明】

【0240】

1 DC/DC電圧変換装置、2 変換主回路、3 制御ユニット、4 直流電源、

5 電気機器、8 ゲート駆動信号、11,11a,11b ゲートPWM生成部、

12,12a ゲート駆動回路、23 回路切替え器、25,26 スイッチオフ回路、271,273 温度検出用ダイオード、28 インダクタ温度検出器、

29 キャパシタ温度検出器、C1,C2 平滑キャパシタ、

C0,C0a,C0b エネルギ移行用キャパシタ、

FET1〜FET6 電界効果トランジスタ、L インダクタ。

【技術分野】

【0001】

本発明は、一次側と二次側の間で双方向に電力を授受させつつ、直流電圧を昇圧あるいは降圧した直流電圧に変換するDC/DC電圧変換装置に関するものである。

【背景技術】

【0002】

従来から、直列接続した半導体スイッチ素子のスイッチオン、スイッチオフ動作を利用して、インダクタへのエネルギの蓄積、放出とエネルギ移行用キャパシタの充電、放電との動作を組み合わせ、直流から直流への電圧変換を行う装置が用いられている(特許文献1、非特許文献1)。

これは、半導体スイッチ素子およびこれと逆並列に整流素子を接続したパワーデバイスを、同時には半数のパワーデバイスのみオン状態(半導体スイッチ素子ならばスイッチオン、整流素子ならば順バイアス)とするものであって、個々のパワーデバイスの耐電圧を低く設定することができる。このため、耐電圧が高いことに起因して各パワーデバイスの導通損失が増加してしまうのを抑えつつ、DC/DC電圧変換装置の取り扱い電圧を高電圧に設定可能である。

【0003】

ここで、商用交流電源(AC100V、AC200V)を整流した後の電圧を変換するDC/DC電圧変換装置や、およそ100Vから1,000Vの範囲の電圧を変換する出力電力容量が4kW程度以上のDC/DC電圧変換装置には、パワーデバイスとして主に半導体スイッチ素子にはSi(珪素)を材料としたIGBT(絶縁ゲート バイポーラ トランジスタ:Insulated Gate Bipolar Transistor)が、また、整流素子には同じくSiを材料としたPINダイオードが用いられている。

このようなDC/DC電圧変換装置は、直流を交流に変換するインバータと組み合わせてシステムが構成される場合があり、例えば、図31に示すハイブリッド自動車や電気自動車の電気駆動システム、図32に示す太陽光発電用の電力変換システム、エアーコンディショナ等の電力変換システムが挙げられる。

【0004】

図31の電気駆動システムは、DC/DC電圧変換装置1の一次側端子P1、N1にニッケル水素電池やリチウムイオン電池、燃料電池などの直流電源となる電池41を、二次側端子P2、N2にインバータ51a、51bを接続している。更に、インバータ51aには回転電機52aが、インバータ51bには回転電機52bがそれぞれ接続されている。回転電機52a、52bは車両の駆動力源となる。

DC/DC電圧変換装置1は、一次側の電池41の電圧をDC/DC電圧変換して二次側のインバータ51a、51bに供給する。インバータ51aは回転電機52aと、インバータ51bは回転電機52bとそれぞれ交流電力を授受する。

【0005】

図32の太陽光発電用電力変換システムは、DC/DC電圧変換装置1の一次側端子P1、N1に太陽電池42を、また、二次側端子P2、N2にインバータ51cを接続している。インバータ51cは、フィルタ6を介して商用交流電源7に接続しており、DC/DC電圧変換装置1は一次側の太陽電池42の発電電圧をDC/DC電圧変換して二次側のインバータ51cに供給する。インバータ51cは、直流電圧を所定の商用交流電圧の振幅、周波数にDC/AC変換して商用電力系統に供給する。

これらシステムに用いられるDC/DC電圧変換装置は、電源の状態(例えば、太陽光発電システムの太陽電池の光の照射量)や負荷の状態(例えば、ハイブリッド自動車の電気駆動システムの回転電機の回転速度)に応じて、変換する電圧の比率を調整し、その出力電圧をコントロールしている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開昭62−53171号公報

【非特許文献】

【0007】

【非特許文献1】三菱電機技報 Vol.61 1987年 No.2

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、上記した従来のDC/DC電圧変換装置において、次のような3つの課題があった。

第1に、一次側から二次側へ電力を送り込む力行動作時には、二次側電圧を一次側電圧よりも高く調整する昇圧動作はできるものの、二次側電圧を一次側電圧よりも低く調整する降圧動作は不可であり、昇降圧動作を同時には行えなかった。また、二次側から一次側へ電力を回収する回生動作時にも、一次側電圧を二次側電圧よりも低く調整する降圧動作(一次側から見れば昇圧動作)はできるものの、一次側電圧を二次側電圧よりも高く調整する昇圧動作は不可であり、昇降圧動作を同時には行えなかった。

これは、例えば、一次側に充電可能な電池を接続し、二次側に発電動作をおこなう電気機器を接続して、二次側から一次側に電力を送って電池を充電しようとする場合に、二次側の電気機器の発電電圧が比較的高くなければ一次側の電池を充電する際の損失が大きくなり、エネルギの利用効率が低下してしまうという不都合を生じる。

【0009】

第2に、高い出力電力容量を得ようとすれば、各要素の発生損失やその冷却手段等の関係から装置が大型重量化するという課題があった。発生損失が大きい要素として、パワーデバイスが挙げられる。パワーデバイスである半導体スイッチ素子と整流素子の発生損失には、それぞれ次の成分がある。

半導体スイッチ素子には、スイッチオンでの電流導通時のオン抵抗分による導通損失とスイッチング損失が生じる。スイッチング損失は、スイッチオフからスイッチオンへの切替わり(ターンオン)、スイッチオンからスイッチオフへの切替わり(ターンオフ)時の過渡的な立上り、立下り変化における半導体スイッチ素子の両端の電圧と導通電流の積の時間積分である。

【0010】

また、整流素子には、順方向導通時のオン抵抗分による導通損失と逆回復時の逆回復損失が生じる。逆回復損失は、逆回復動作での過渡的な立上り、立下り変化における整流素子の両端電圧と逆回復電流の積の時間積分である。

このように、半導体スイッチ素子のスイッチング損失と整流素子の逆回復損失はスイッチングのタイミングで生じるものであり、スイッチング周波数に比例し、このスイッチング周波数の増大は、パワーデバイスの損失増大に結びつき冷却手段を大型化する。

スイッチング周波数が一定の場合、スイッチング損失を下げるためには、スイッチングの速度を速くすれば良いものの、これはパワーデバイスに導通する電流の変化速度を高めることから、パワーデバイスの電流導通路の配索導体に寄生するインダクタンス成分Lsによって大きなサージ電圧が生じることになり、パワーデバイスやキャパシタに高電圧がかかり、損傷する懸念がある。

【0011】

第3に、DC/DC電圧変換装置全体の容積や重量において、金属材料を用いる冷却ヒートシンクやインダクタが多くを占めているため、装置が大型重量化するという課題がある。

DC/DC電圧変換装置が高い出力電力容量を得ようとすれば、パワーデバイスの発生損失の増加に連れてパワーデバイスの半導体接合部温度が上昇するのを和らげるために、冷却ヒートシンクを大型化する必要がある。

また、出力電力容量が増すとインダクタの導通電流も増えるのに対し、大電流にてもインダクタのコアが磁気飽和せず所望のインダクタンス値を得るためには磁路の断面積を増すようコアを大型化し、また、インダクタの巻線の発熱増加を抑えるためには巻線の断面積を増して巻線の抵抗を下げる必要がある。

これら冷却ヒートシンクやインダクタは金属材料を多量に用いるが故に、樹脂材料と比較して相対的に比重が高く、重量が嵩むことへの影響が大きい。

【0012】

この発明は、以上のような従来の課題を同時に解決するためになされたものであり、従来のDC/DC電圧変換装置と比較して効率の改善と出力電力容量の増大を達成しつつ、力行動作時と回生動作時の何れも、一次側電圧と二次側電圧の間を昇圧にも降圧にも調整可能であって、更に、小型化、軽量化を確保したDC/DC電圧変換装置を提供することを目的とする。

【課題を解決するための手段】

【0013】

この発明に係るDC/DC電圧変換装置は、変換主回路と制御ユニットとを備え、一次側と二次側との間で双方向に電力を授受して昇降圧の直流電圧変換を行うDC/DC電圧変換装置であって、

主変換回路は、一次側の正極側端子と負極側端子との間に接続され一次側の電圧を平滑する一次側平滑キャパシタと、二次側の正極側端子と負極側端子との間に接続され二次側の電圧を平滑する二次側平滑キャパシタと、エネルギの蓄積、放出を行うエネルギ移行用キャパシタおよびインダクタと、オンオフのスイッチング動作と逆方向導通動作とが可能な半導体ユニットを2n(nは2以上の整数)個互いに直列に接続して一次側の正極側端子と二次側の負極側端子との間に接続してなるパワーモジュールとを備え、

一次側の負極側端子は二次側の正極側端子に接続され、

制御ユニットは、2n個の半導体ユニットを2個で一対となるn個の組に分け、各組を構成する一対の半導体ユニットのオンオフが互いに反対となる相補の関係を持つように、かつ、インダクタに流れる電流の交流成分が半導体ユニットをオンオフ制御するスイッチング周波数のn倍となるように制御し、

エネルギ移行用キャパシタは、半導体ユニットの内、一次側の正極側端子に直接接続される半導体ユニットと二次側の負極側端子に直接接続される半導体ユニットとを除いて、各組の一対の半導体ユニットにおける、一次側の正極側端子に最も近い端子と二次側の負極側端子に最も近い端子との間に接続し、

インダクタは、一対の半導体ユニットであって互いに直接接続されるものの当該接続点と一次側の負極側端子との間に接続するようにしたものである。

【発明の効果】

【0014】

この発明に係るDC/DC電圧変換装置は、以上のように、特にその制御ユニットが、2n個の半導体ユニットを2個で一対となるn個の組に分け、各組を構成する一対の半導体ユニットのオンオフが互いに反対となる相補の関係を持つように、かつ、インダクタに流れる電流の交流成分が半導体ユニットをオンオフ制御するスイッチング周波数のn倍となるように制御する。

従って、インダクタに流れる電流の周波数がスイッチング周波数の2倍以上に増大し、その交流成分(リップル成分)が低減するか、または、その必要なインダクタンスを低減することができ、いずれにしろ、インダクタの損失低減、小型化、それに伴う冷却ヒートシンクの小型化が実現する。

また、一次側から二次側に電力を供給する力行動作時と二次側から一次側に電力を供給する回生動作時のいずれの場合にも、二次側電圧と一次側電圧の間を昇圧、降圧の双方に直流電圧変換する事が可能となる。

【図面の簡単な説明】

【0015】

【図1】本発明によるDC/DC電圧変換装置のシステムの全体構成図である。

【図2】本発明によるDC/DC電圧変換装置の電力の流れを示す説明図である。

【図3】本発明による実施の形態1の変換主回路の接続構成を示す図である。

【図4】本発明による実施の形態1の力行降圧時(オンデューティ50%未満)の動作を説明する波形図である。

【図5】本発明による実施の形態1の力行昇圧時(オンデューティ50%以上)の動作を説明する波形図である。

【図6】本発明による実施の形態1の回生降圧時(オンデューティ50%未満)の動作を説明する波形図である。

【図7】本発明による実施の形態1の回生昇圧時(オンデューティ50%以上)の動作を説明する波形図である。

【図8】本発明による実施の形態1のキャパシタのインピーダンスの周波数特性を示す図である。

【図9】本発明による実施の形態1の制御ユニットと変換主回路の構成を示すブロック図である。

【図10】本発明によるオンデューティとDC/DC電圧変換比との関係を示す特性図である。

【図11】本発明による実施の形態1の変換主回路の図3とは異なる接続構成を示す図である。

【図12】本発明による実施の形態1の変換主回路の図3、図11とは異なる接続構成を示す図である。

【図13】本発明による実施の形態2の制御ユニットと変換主回路の構成を示すブロック図である。

【図14】本発明による実施の形態2のゲート駆動回路の詳細な構成を示すブロック図である。

【図15】本発明による実施の形態2のスイッチオフ回路の選択方法を説明する図である。

【図16】本発明による実施の形態2の電界効果トランジスタのターンオフ動作を説明する波形図である。

【図17】本発明による実施の形態3の変換主回路の接続構成を示す図である。

【図18】本発明による実施の形態3の制御ユニットの構成を示すブロック図である。

【図19】本発明による実施の形態3のスイッチング周波数とインダクタ、キャパシタ、半導体ユニットの発熱量との関係を示す説明図である。

【図20】本発明による実施の形態3の周波数調整器の詳細な構成を示すブロック図である。

【図21】本発明による実施の形態3の選択処理手段の処理を説明するフロー図である。

【図22】本発明による実施の形態4の変換主回路の接続構成を示す図である。

【図23】本発明による実施の形態4の力行降圧時(オンデューティ100/3%未満)の動作を説明する波形図である。

【図24】本発明による実施の形態4の力行降圧時(オンデューティ100/3%以上50%未満)の動作を説明する波形図である。

【図25】本発明による実施の形態4の力行昇圧時(オンデューティ50%以上100×(2/3)%未満)の動作を説明する波形図である。

【図26】本発明による実施の形態4の力行昇圧時(オンデューティ100×(2/3)%以上)の動作を説明する波形図である。

【図27】本発明による実施の形態4の回生降圧時(オンデューティ100/3%未満)の動作を説明する波形図である。

【図28】本発明による実施の形態4の回生降圧時(オンデューティ100/3%以上50%未満)の動作を説明する波形図である。

【図29】本発明による実施の形態4の回生昇圧時(オンデューティ50%以上100×(2/3)%未満)の動作を説明する波形図である。

【図30】本発明による実施の形態4の回生昇圧時(オンデューティ100×(2/3)%以上)の動作を説明する波形図である。

【図31】DC/DC電圧変換装置を用いた自動車用電気駆動システムの構成図である。

【図32】DC/DC電圧変換装置を用いた太陽光発電用の電力変換システムの構成図である。

【発明を実施するための形態】

【0016】

実施の形態1.

以下、本発明の実施の形態1のDC/DC電圧変換装置につき、図1から図12を用いて説明する。

図1は、本実施例によるシステムの全体構成を示すブロック図である。DC/DC電圧変換装置1は、変換主回路2と制御ユニット3とから構成されている。DC/DC電圧変換装置1は、電力経路の接続端子として変換主回路2の一次側に正極側端子P1、負極側端子N1、二次側に正極側端子P2、負極側端子N2を備えている。

図2は、本実施例によるDC/DC電圧変換装置1の一次側と二次側との間の電圧変換と電力の流れを模式的に図示したものである。DC/DC電圧変換装置1の一次側には端子P1、N1に直流電源4が、二次側には端子P2、N2に電気機器5が接続される。

図2において、直流電源4は、リチウムイオン電池やニッケル水素電池、鉛電池といった二次電池の他、太陽電池、燃料電池などの電源に電気二重層キャパシタや二次電池を組み合わせたものなどが想定される。電気機器5は、電気負荷を含んで発電装置や蓄電装置と組み合わさって成る機器である。

【0017】

DC/DC電圧変換装置1は、一次側端子電圧V1と二次側端子電圧V2について、その電圧がV1≦V2の関係、V1>V2の関係のいずれに対しても電流を双方向に導通可能なよう電圧変換を行い、相互に電力をやり取りする。

ここで、直流電源4が放電動作であり電気機器5が電力消費動作の場合、DC/DC電圧変換装置1は、図2(a)に示すように、電圧を昇圧して一次側から二次側の方向へ電力を送り込む場合と、図2(b)に示すように、電圧を降圧して電力を送り込む場合とがある。

また、直流電源4が充電動作であり電気機器5が電力供給動作の場合、DC/DC電圧変換装置1は、図2(c)に示すように、電圧を昇圧(一次側電圧V1を基準として二次側電圧V2はV1≦V2の関係)して二次側から一次側の方向へ電力を送り込む場合と、図2(d)に示すように、電圧を降圧(一次側電圧V1を基準として二次側電圧V2はV1>V2の関係)して電力を送り込む場合とがある。

この時、電圧の変換は制御ユニット3から出力されるゲート駆動信号8に従い、変換主回路2に備わる、後述する半導体ユニット内の半導体スイッチ素子のオン、オフを制御することによってなされる。

【0018】

ここで、DC/DC電圧変換装置1の動作内容について図3から図10を用いて説明する。図3は、変換主回路2の回路配線を示す図であり、4個の半導体ユニットを直列に接続し、一次側から二次側へ電圧を昇圧あるいは降圧して電力供給を、また、二次側から一次側へ電圧を降圧あるいは昇圧して電力供給を行う。

変換主回路2は、一次側端子電圧V1を平滑化する一次側平滑キャパシタC1と、二次側端子電圧V2を平滑化する二次側平滑キャパシタC2と、エネルギの蓄積、放出を行う、インダクタLおよびエネルギ移行用キャパシタC0と、4個の半導体ユニットを備えている。

【0019】

第1〜第4の半導体ユニットは、この図3の例では、寄生ダイオードを内部に含む電界効果トランジスタFET4、FET3、FET2、FET1を採用している。なお、これら電界効果トランジスタは、そのバンドギャップがシリコンのそれより大きいワイドバンドギャップ半導体で形成したものを採用しているが、この点については、後段で詳述するものとする。

【0020】

続けて、変換主回路2の接続の詳細について説明する。

平滑キャパシタC1の両端子は、変換主回路2の一次側の正極側端子P1、負極側端子N1に接続されており、負極側端子N1は変換主回路2の二次側の正極側端子P2とも接続されている。

正極側端子P1は、平滑キャパシタC1の一方の端子とFET1のドレイン端子に接続され、平滑キャパシタC1の他方の端子は負極側端子N1に接続される。

また、平滑キャパシタC2の両端子は、変換主回路2の二次側の正極側端子P2、負極側端子N2に接続されている。

【0021】

FET4のソース端子は変換主回路2の二次側の負極側端子N2に、ドレイン端子はFET3のソース端子に、FET3のドレイン端子はFET2のソース端子に、FET2のドレイン端子はFET1のソース端子に、それぞれ接続されている。

エネルギ移行用キャパシタC0は、一方の端子をFET4とFET3との接続点に、他方の端子をFET2とFET1との接続点に接続されている。

【0022】

なお、後段の動作説明で触れているように、この例では、FET1とFET4およびFET2とFET3とがそれぞれ組となり、各組をなす一対のFETは、いわゆる相補の関係を持つようにオンオフ制御される。従って、エネルギ移行用キャパシタC0は、一次側の正極側端子P1に直接接続されるFET1と二次側の負極側端子N2に直接接続されるFET4とを除いた、一対のFET2、FET3における、一次側の正極側端子P1に最も近い端子であるFET2のドレイン端子と二次側の負極側端子N2に最も近い端子であるFET3のソース端子との間に接続されているとも言える。

【0023】

インダクタLは、図3に示すように、一方の端子を変換主回路2の一次側の負極側端子N1に接続され、他方の端子を、上記した一対のFETであって互いに直接接続されているFET3とFET2との接続点に接続されている。

【0024】

図3には示されない制御ユニット3からは、ゲート駆動信号8として電界効果トランジスタをオン、オフ制御するための信号がFET4、FET3、FET2、FET1に対応して、それぞれGate4、Gate3、Gate2、Gate1信号としてFET4からFET1のゲート電極(G)に接続されている。FET4はGate4信号の、FET3はGate3信号の、FET2はGate2信号の、FET1はGate1信号の電圧変化にしたがって、スイッチング動作する。

【0025】

次に、変換主回路2の動作について説明する。

上述のように、DC/DC電圧変換装置1は、一次側から二次側へ、あるいは、二次側から一次側へ、電力を双方向に授受させつつ、一次側に対して二次側が昇圧動作、降圧動作のいずれにもなるよう電圧変換する。この昇圧動作、降圧動作は、電界効果トランジスタのオン、オフ動作のタイミングをゲート駆動信号8であるGate4、Gate3、Gate2、Gate1で調整することによって制御される。

このゲート駆動信号8による電圧変換の制御について、力行動作時と回生動作時とに分けて説明する。

【0026】

力行動作時:

1)オンデューティが50%未満で降圧動作の場合:

一次側から二次側へ電力を供給する力行動作時であって、二次側電圧V2<一次側電圧V1の降圧を行うオンデューティ50%未満の動作について説明する。

但し、オンデューティはGate1信号とGate2信号に対する値を言っており、Gate3信号とGate4信号はそれぞれGate2信号、Gate1信号と相補であるから、Gate3信号とGate4信号のオンデューティは、100%−(Gate2信号、Gate1信号のオンデューティ)の関係となる。

【0027】

図4に力行動作時の降圧動作でゲート駆動信号のオンデューティが50%未満の場合の波形を示す。図4で(a)は、ゲート駆動信号、(b)はインダクタ電流IL、(c)はスイッチングモードとその切替わりタイミングを示している。

インダクタ電流ILは、インダクタLをFET2側の接続端子から負極側端子N1側の接続端子の方向に流れる極性を正とする。

図4(a)において、Gate1信号がハイの場合にFET1が、Gate2信号がハイの場合にFET2がオンし、ドレインからソースに向けて電流が流れる。

【0028】

Gate3信号がハイの場合にFET3が、Gate4信号がハイの場合にFET4がオンするが、力行動作時には電流がソースからドレインに向けてFET3、FET4に内在する寄生ダイオードの替わりにトランジスタ部分を流れる。

この結果、当該部分での電圧降下が少なく、発生する損失がその分低減し効率が向上するという利点がある。この利点は、本願発明になる制御方式にあって、半導体ユニットに電界効果トランジスタFETを採用した場合に得られる効果である。

【0029】

ここで、Gate1信号とGate4信号は、互いにハイ、ローの論理が相反する相補信号であり、Gate1信号がハイの時にはGate4信号はロー、Gate1信号がローの時にはGate4信号はハイとなる。但し、ハイとローの論理の切替わり時は電界効果トランジスタのスイッチング動作の応答遅れにより双方が同時にオンとならないよう阻止時間(デッドタイム)を設ける。

同様に、Gate2信号とGate3信号は、互いにハイ、ローの論理が相反する相補信号であり、Gate1信号とGate2信号は位相差が180度である。即ち、ゲート駆動信号8は、相補信号として対を成す信号が二通り有って、互いの位相差が等間隔となっている。

【0030】

この時、Gate1からGate4のゲート駆動信号のハイ、ローの論理の組合わせは、スイッチングモードB、C、Dの三種に分類され B→D→C→D→B の順に切替わる。

【0031】

スイッチングモードBでは、FET1とFET3がオン、FET2とFET4がオフであって、

電流が、正極側端子P1→FET1→エネルギ移行用キャパシタC0→FET3→インダクタL→負極側端子N1の経路に流れ、エネルギがインダクタLとエネルギ移行用キャパシタC0に蓄えられる。電気機器5には、後述する動作で蓄電された平滑キャパシタC2の両端電圧が印加され、平滑キャパシタC2からエネルギが供給される。