DDR信号をテストするための補助冶具

【課題】マザーボードのDDR信号を容易にテストすることができるテスト補助冶具を提供すること。

【解決手段】本発明に係るDDR信号をテストするための補助冶具は、DDRメモリ用コネクタを有するマザーボードに着脱可能に固定される板体を備え、前記板体には、前記マザーボードのDDRメモリ用コネクタのピンに各々対応する複数のテスト孔が設けられ、前記板体における各々のテスト孔の近傍には、キャラクターが設けられ、前記キャラクターは、各々のテスト孔と組み合わせられるDDRメモリ用コネクタのピンの名称或いは機能をそれぞれ示す。

【解決手段】本発明に係るDDR信号をテストするための補助冶具は、DDRメモリ用コネクタを有するマザーボードに着脱可能に固定される板体を備え、前記板体には、前記マザーボードのDDRメモリ用コネクタのピンに各々対応する複数のテスト孔が設けられ、前記板体における各々のテスト孔の近傍には、キャラクターが設けられ、前記キャラクターは、各々のテスト孔と組み合わせられるDDRメモリ用コネクタのピンの名称或いは機能をそれぞれ示す。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子装置用のテスト補助冶具に関し、特にマザーボードのDDR信号のテストを容易にさせるための補助冶具に関するものである。

【背景技術】

【0002】

ダブルデータレートシンクロナスダイナミックランダムアクセスメモリ(Double Data Rate Synchronous Dynamic Random Access Memory,DDR SDRAM)は、電子製品に用いられる一種の高帯域幅パラレルデータバスであり、コンピュータ及びサーバー等の電子装置に広く用いられている。

【0003】

現在、電子装置のマザーボードを設計した後、一般的にはマザーボードのDDR信号に対してテストを行わなければならない。既存のテスト方法として、テスト者は、先ずテンプレートファイルを参照しながら、マザーボード上において、一つ一つテストポイントを探し出した後、このテストポイントに対して、一つ一つ信号のテストを行う。しかし、マザーボードにおけるDDRメモリ用コネクタのピンは非常に多い(例えば、DDR3は240個のピンを有する)ので、テスト者が多くのDDRメモリ用コネクタのピンからテストポイントを探し出して、DDR信号のテストを行うことは、煩雑で且つ間違え易いため、非常に不便である。

【発明の概要】

【発明が解決しようとする課題】

【0004】

以上の問題点に鑑みて、本発明は、マザーボードのDDR信号を容易にテストすることができる補助冶具を提供することを目的とする。

【課題を解決するための手段】

【0005】

上記の目的を達成するために、本発明に係るDDR信号をテストするための補助冶具は、DDRメモリ用コネクタを有するマザーボードに着脱可能に固定される板体を備え、前記板体には、前記マザーボードのDDRメモリ用コネクタのピンに各々対応する複数のテスト孔が設けられ、前記板体における各々のテスト孔の近傍には、キャラクターが設けられ、前記キャラクターは、各々のテスト孔と組み合わせられるDDRメモリ用コネクタのピンの名称或いは機能をそれぞれ示す。

【発明の効果】

【0006】

従来の技術と異なり、本発明のDDR信号をテストするための補助冶具の板体には、多数のテスト孔が設けられ、さらに各々のテスト孔の近傍にはキャラクターが設けられている。各々のテスト孔は、DDRメモリ用コネクタの一つのピンとそれぞれ組み合わせられるので、使用する際、テスト者は前記キャラクターを介してテストするピンを素早く見付けることができ、テストの効率を高めることができる。

【図面の簡単な説明】

【0007】

【図1】従来のDDRメモリ用コネクタが集積されたマザーボードの斜視図である。

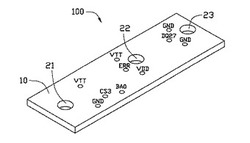

【図2】本発明の実施形態に係るDDR信号を容易にテストするための補助冶具を示す斜視図である。

【発明を実施するための形態】

【0008】

図1及び図2に示すように、本発明の実施形態に係るDDR信号をテストするための補助冶具100は、コンピュータ及びサーバー等の電子装置(図示せず)のマザーボード200のDDR信号を容易にテストするために用いられる。

【0009】

マザーボード200には、少なくとも一つのDDRメモリ用コネクタ(図示せず)が設けられている。以下の実施形態において、当該DDRメモリ用コネクタは、DDR3プログレスバーインサートを提供することに用いられる。また、DDRメモリ用コネクタは、例えば240個のピンを備え、該240個のピンは、全てマザーボード200の表面から露出し、且つ複数の電源ピンV、複数の接地ピンG及び複数の信号ピンSを備える。また、マザーボード200上には、三つの位置決め柱Pがさらに設けられ、この位置決め柱Pは、DDRメモリ用コネクタとマザーボード200とを固定するためのボルトであることができる。

【0010】

DDR信号をテストするための補助冶具100は、板体10を備える。該板体10は、アクリロニトリル・ブタジエン・スチレン共重合体(ABS)等の樹脂材料からなり、且つマザーボード200を被覆するように、マザーボード200に着脱可能に設置される。板体10には、テストしようとするマザーボード200のDDRメモリ用コネクタのピン及び位置決め柱Pの配列位置、形状及び数量に対応して、多くのテスト孔及び位置決め孔が設けられている。本発明の実施形態において、テスト孔の数は240個であり、位置決め孔は21、22、23の三つである。

【0011】

240個のテスト孔は、DDRメモリ用コネクタの各々のピンと互いに係合し、DDRメモリ用コネクタのピンは、該テスト孔を介して板体10を貫通する。また、該240個のテスト孔は、それに組み合わせられるピンに基づいて三種類に分けられる。以下、具体的に説明する。

【0012】

第一種は、信号孔である。当該信号孔の数は、DDRメモリ用コネクタの信号ピンの数に等しく、前記信号ピンと各々対応する。また、板体10における各々の信号孔の近傍には、キャラクターがそれぞれ設けられている。キャラクターには、例えば、CS3、BA0、ERR、DQ27がある。該キャラクターは、各々の信号孔と組み合わせられる信号ピンの名称或いは機能をそれぞれ表示する。テスト者が容易に識別できるように、黒インクによって、キャラクターを板体10の上面における各々信号孔の近傍に印刷することができる。

【0013】

第二種は、接地孔である。当該接地孔の数は、DDRメモリ用コネクタの接地ピンの数に等しく、前記接地ピンと各々対応する。また、板体10における各々の接地孔の近傍には、キャラクター(例えば、GND)が設けられている。該キャラクターは、接地孔と組み合わせられるピンが接地ピンであることを示す。テスト者が容易に識別できるように、青インクによって、キャラクターを板体10の上面における接地孔の近傍に印刷することができる。

【0014】

第三種は、電源孔である。当該電源孔の数は、DDRメモリ用コネクタの電源ピンの数に等しく、前記電源ピンと各々対応する。また、板体10における各々の電源孔の近傍には、キャラクター(例えば、VTT、VDD)が設けられている。キャラクターVTTは、電源孔と組み合わせられるピンが電源ピンであることを示し、VTTに対応する電源孔と組み合わせられる電源ピンの電圧は、約1.5Vである。キャラクターVDDは、電源孔と組み合わせられるピンが電源ピンであることを示し、VDDに対応する電源孔と組み合わせられる電源ピンの電圧は、約0.75Vである。テスト者が容易に識別できるように、赤インクによって、キャラクターを板体10の上面における電源孔の近傍に印刷することができる。

【0015】

位置決め孔21〜23は、マザーボード200の位置決め柱Pとそれぞれ組み合わせられる。板体10をマザーボード200の上面に被覆して固定する場合、三つの位置決め柱Pを位置決め孔21〜23に各々貫通させればよい。

【0016】

以下、本発明のDDR信号をテストするための補助冶具100の使用原理について詳細に説明する。

【0017】

マザーボード200のDDR信号をテストする際、先ず、三つの位置決め柱Pを位置決め孔21〜23に各々貫通させて、板体10をマザーボード200の上に固定させる。この際、DDRメモリ用コネクタの信号ピンは板体10の信号孔から露出し、接地ピンは接地孔から露出し、電源ピンは電源孔から露出する。これにより、DDRメモリ用コネクタの何れか一つの信号ピンをテストする時に、テスト者は、信号ピンの近傍に設けられたキャラクターを介して、テストしようとする信号ピンを素早く見付けることができる。例えば、キャラクターBA0を介して、DDRメモリ用コネクタのバンクアドレス信号ピンを見付けることができる。次いで、テスト者は、一つのプローブを利用して、該バンクアドレス信号ピンに接触し、他のプローブを利用して、当該バンクアドレス信号ピンに最も近い接地ピンに接触することによって、テストを行う。

【0018】

また、本発明のDDR信号をテストするための補助冶具100のテスト孔の数は、本実施形態に記載された240個に限定されず、DDRメモリ用コネクタの具体的なピンの数に基づいてテスト孔の数を設定することができる。

【0019】

また、本実施形態から分かるように、テスト者が接地孔及びそれに対応するキャラクターを介して、接地ピンを識別することができるので、テストする時に、テストする信号ピンに最も近い接地ピンを選択することができる。これにより、接地ピンを探し出す時間を短縮させ、また、テストする信号ピンが接地ピンから遠いため、信号の折り返し経路が長くなることに起因する信号の歪み現象を防止することができる。また、電源孔及びそれに対応するキャラクターの存在は、電源の安定したテストを補助することができる。つまり、テスト者は、該電源孔及びその近傍のキャラクターを介して、対応する電源ピンを素早く見付けることができる。

【0020】

本発明の実施形態によると、DDR信号をテストするための補助冶具100の板体10には、多数のテスト孔が設けられ、さらに各々のテスト孔の近傍にはキャラクターがそれぞれ設けられている。各々のテスト孔は、DDRメモリ用コネクタの各々のピンとそれぞれ組み合わせられるので、使用する際、テスト者は、キャラクターを介してテストするピンを素早く見付けることができ、テストの効率を高めることができる。

【0021】

以上、本発明の好適な実施形態について詳細に説明したが、本発明は前記実施形態に限定されるものではなく、本発明の範囲内で種々の変形又は修正が可能であり、該変形又は修正も又、本発明の特許請求の範囲内に含まれるものであることは、言うまでもない。

【符号の説明】

【0022】

10 板体

21、22、23 位置決め孔

100 DDR信号をテストするための補助冶具

200 マザーボード

【技術分野】

【0001】

本発明は、電子装置用のテスト補助冶具に関し、特にマザーボードのDDR信号のテストを容易にさせるための補助冶具に関するものである。

【背景技術】

【0002】

ダブルデータレートシンクロナスダイナミックランダムアクセスメモリ(Double Data Rate Synchronous Dynamic Random Access Memory,DDR SDRAM)は、電子製品に用いられる一種の高帯域幅パラレルデータバスであり、コンピュータ及びサーバー等の電子装置に広く用いられている。

【0003】

現在、電子装置のマザーボードを設計した後、一般的にはマザーボードのDDR信号に対してテストを行わなければならない。既存のテスト方法として、テスト者は、先ずテンプレートファイルを参照しながら、マザーボード上において、一つ一つテストポイントを探し出した後、このテストポイントに対して、一つ一つ信号のテストを行う。しかし、マザーボードにおけるDDRメモリ用コネクタのピンは非常に多い(例えば、DDR3は240個のピンを有する)ので、テスト者が多くのDDRメモリ用コネクタのピンからテストポイントを探し出して、DDR信号のテストを行うことは、煩雑で且つ間違え易いため、非常に不便である。

【発明の概要】

【発明が解決しようとする課題】

【0004】

以上の問題点に鑑みて、本発明は、マザーボードのDDR信号を容易にテストすることができる補助冶具を提供することを目的とする。

【課題を解決するための手段】

【0005】

上記の目的を達成するために、本発明に係るDDR信号をテストするための補助冶具は、DDRメモリ用コネクタを有するマザーボードに着脱可能に固定される板体を備え、前記板体には、前記マザーボードのDDRメモリ用コネクタのピンに各々対応する複数のテスト孔が設けられ、前記板体における各々のテスト孔の近傍には、キャラクターが設けられ、前記キャラクターは、各々のテスト孔と組み合わせられるDDRメモリ用コネクタのピンの名称或いは機能をそれぞれ示す。

【発明の効果】

【0006】

従来の技術と異なり、本発明のDDR信号をテストするための補助冶具の板体には、多数のテスト孔が設けられ、さらに各々のテスト孔の近傍にはキャラクターが設けられている。各々のテスト孔は、DDRメモリ用コネクタの一つのピンとそれぞれ組み合わせられるので、使用する際、テスト者は前記キャラクターを介してテストするピンを素早く見付けることができ、テストの効率を高めることができる。

【図面の簡単な説明】

【0007】

【図1】従来のDDRメモリ用コネクタが集積されたマザーボードの斜視図である。

【図2】本発明の実施形態に係るDDR信号を容易にテストするための補助冶具を示す斜視図である。

【発明を実施するための形態】

【0008】

図1及び図2に示すように、本発明の実施形態に係るDDR信号をテストするための補助冶具100は、コンピュータ及びサーバー等の電子装置(図示せず)のマザーボード200のDDR信号を容易にテストするために用いられる。

【0009】

マザーボード200には、少なくとも一つのDDRメモリ用コネクタ(図示せず)が設けられている。以下の実施形態において、当該DDRメモリ用コネクタは、DDR3プログレスバーインサートを提供することに用いられる。また、DDRメモリ用コネクタは、例えば240個のピンを備え、該240個のピンは、全てマザーボード200の表面から露出し、且つ複数の電源ピンV、複数の接地ピンG及び複数の信号ピンSを備える。また、マザーボード200上には、三つの位置決め柱Pがさらに設けられ、この位置決め柱Pは、DDRメモリ用コネクタとマザーボード200とを固定するためのボルトであることができる。

【0010】

DDR信号をテストするための補助冶具100は、板体10を備える。該板体10は、アクリロニトリル・ブタジエン・スチレン共重合体(ABS)等の樹脂材料からなり、且つマザーボード200を被覆するように、マザーボード200に着脱可能に設置される。板体10には、テストしようとするマザーボード200のDDRメモリ用コネクタのピン及び位置決め柱Pの配列位置、形状及び数量に対応して、多くのテスト孔及び位置決め孔が設けられている。本発明の実施形態において、テスト孔の数は240個であり、位置決め孔は21、22、23の三つである。

【0011】

240個のテスト孔は、DDRメモリ用コネクタの各々のピンと互いに係合し、DDRメモリ用コネクタのピンは、該テスト孔を介して板体10を貫通する。また、該240個のテスト孔は、それに組み合わせられるピンに基づいて三種類に分けられる。以下、具体的に説明する。

【0012】

第一種は、信号孔である。当該信号孔の数は、DDRメモリ用コネクタの信号ピンの数に等しく、前記信号ピンと各々対応する。また、板体10における各々の信号孔の近傍には、キャラクターがそれぞれ設けられている。キャラクターには、例えば、CS3、BA0、ERR、DQ27がある。該キャラクターは、各々の信号孔と組み合わせられる信号ピンの名称或いは機能をそれぞれ表示する。テスト者が容易に識別できるように、黒インクによって、キャラクターを板体10の上面における各々信号孔の近傍に印刷することができる。

【0013】

第二種は、接地孔である。当該接地孔の数は、DDRメモリ用コネクタの接地ピンの数に等しく、前記接地ピンと各々対応する。また、板体10における各々の接地孔の近傍には、キャラクター(例えば、GND)が設けられている。該キャラクターは、接地孔と組み合わせられるピンが接地ピンであることを示す。テスト者が容易に識別できるように、青インクによって、キャラクターを板体10の上面における接地孔の近傍に印刷することができる。

【0014】

第三種は、電源孔である。当該電源孔の数は、DDRメモリ用コネクタの電源ピンの数に等しく、前記電源ピンと各々対応する。また、板体10における各々の電源孔の近傍には、キャラクター(例えば、VTT、VDD)が設けられている。キャラクターVTTは、電源孔と組み合わせられるピンが電源ピンであることを示し、VTTに対応する電源孔と組み合わせられる電源ピンの電圧は、約1.5Vである。キャラクターVDDは、電源孔と組み合わせられるピンが電源ピンであることを示し、VDDに対応する電源孔と組み合わせられる電源ピンの電圧は、約0.75Vである。テスト者が容易に識別できるように、赤インクによって、キャラクターを板体10の上面における電源孔の近傍に印刷することができる。

【0015】

位置決め孔21〜23は、マザーボード200の位置決め柱Pとそれぞれ組み合わせられる。板体10をマザーボード200の上面に被覆して固定する場合、三つの位置決め柱Pを位置決め孔21〜23に各々貫通させればよい。

【0016】

以下、本発明のDDR信号をテストするための補助冶具100の使用原理について詳細に説明する。

【0017】

マザーボード200のDDR信号をテストする際、先ず、三つの位置決め柱Pを位置決め孔21〜23に各々貫通させて、板体10をマザーボード200の上に固定させる。この際、DDRメモリ用コネクタの信号ピンは板体10の信号孔から露出し、接地ピンは接地孔から露出し、電源ピンは電源孔から露出する。これにより、DDRメモリ用コネクタの何れか一つの信号ピンをテストする時に、テスト者は、信号ピンの近傍に設けられたキャラクターを介して、テストしようとする信号ピンを素早く見付けることができる。例えば、キャラクターBA0を介して、DDRメモリ用コネクタのバンクアドレス信号ピンを見付けることができる。次いで、テスト者は、一つのプローブを利用して、該バンクアドレス信号ピンに接触し、他のプローブを利用して、当該バンクアドレス信号ピンに最も近い接地ピンに接触することによって、テストを行う。

【0018】

また、本発明のDDR信号をテストするための補助冶具100のテスト孔の数は、本実施形態に記載された240個に限定されず、DDRメモリ用コネクタの具体的なピンの数に基づいてテスト孔の数を設定することができる。

【0019】

また、本実施形態から分かるように、テスト者が接地孔及びそれに対応するキャラクターを介して、接地ピンを識別することができるので、テストする時に、テストする信号ピンに最も近い接地ピンを選択することができる。これにより、接地ピンを探し出す時間を短縮させ、また、テストする信号ピンが接地ピンから遠いため、信号の折り返し経路が長くなることに起因する信号の歪み現象を防止することができる。また、電源孔及びそれに対応するキャラクターの存在は、電源の安定したテストを補助することができる。つまり、テスト者は、該電源孔及びその近傍のキャラクターを介して、対応する電源ピンを素早く見付けることができる。

【0020】

本発明の実施形態によると、DDR信号をテストするための補助冶具100の板体10には、多数のテスト孔が設けられ、さらに各々のテスト孔の近傍にはキャラクターがそれぞれ設けられている。各々のテスト孔は、DDRメモリ用コネクタの各々のピンとそれぞれ組み合わせられるので、使用する際、テスト者は、キャラクターを介してテストするピンを素早く見付けることができ、テストの効率を高めることができる。

【0021】

以上、本発明の好適な実施形態について詳細に説明したが、本発明は前記実施形態に限定されるものではなく、本発明の範囲内で種々の変形又は修正が可能であり、該変形又は修正も又、本発明の特許請求の範囲内に含まれるものであることは、言うまでもない。

【符号の説明】

【0022】

10 板体

21、22、23 位置決め孔

100 DDR信号をテストするための補助冶具

200 マザーボード

【特許請求の範囲】

【請求項1】

DDRメモリ用コネクタを有するマザーボードに着脱可能に固定される板体を備えるDDR信号をテストするための補助冶具であって、

前記板体には、前記マザーボードのDDRメモリ用コネクタのピンに各々対応する複数のテスト孔が設けられ、前記板体における各々のテスト孔の近傍には、キャラクターが設けられ、前記キャラクターは、各々のテスト孔と組み合わせられるDDRメモリコネクタのピンの名称或いは機能をそれぞれ示すことを特徴とするDDR信号をテストするための補助冶具。

【請求項2】

前記板体には、前記マザーボードに設けられた位置決め柱とそれぞれ組み合わせられる複数の位置決め孔が設けられ、前記位置決め柱は、前記位置決め孔を貫通することを特徴とする請求項1に記載のDDR信号をテストするための補助冶具。

【請求項3】

前記テスト孔は、複数の信号孔を含み、前記信号孔は、マザーボードのDDRメモリ用コネクタの信号ピンと各々対応することを特徴とする請求項1または2に記載のDDR信号をテストするための補助冶具。

【請求項4】

前記テスト孔は、複数の接地孔をさらに含み、前記接地孔は、マザーボードのDDRメモリ用コネクタの接地ピンと各々対応することを特徴とする請求項1から3のいずれか一項に記載のDDR信号をテストするための補助冶具。

【請求項5】

前記テスト孔は、複数の電源孔をさらに備え、前記電源孔は、マザーボードのDDRメモリ用コネクタの電源ピンと各々対応することを特徴とする請求項1から4のいずれか一項に記載のDDR信号をテストするための補助冶具。

【請求項1】

DDRメモリ用コネクタを有するマザーボードに着脱可能に固定される板体を備えるDDR信号をテストするための補助冶具であって、

前記板体には、前記マザーボードのDDRメモリ用コネクタのピンに各々対応する複数のテスト孔が設けられ、前記板体における各々のテスト孔の近傍には、キャラクターが設けられ、前記キャラクターは、各々のテスト孔と組み合わせられるDDRメモリコネクタのピンの名称或いは機能をそれぞれ示すことを特徴とするDDR信号をテストするための補助冶具。

【請求項2】

前記板体には、前記マザーボードに設けられた位置決め柱とそれぞれ組み合わせられる複数の位置決め孔が設けられ、前記位置決め柱は、前記位置決め孔を貫通することを特徴とする請求項1に記載のDDR信号をテストするための補助冶具。

【請求項3】

前記テスト孔は、複数の信号孔を含み、前記信号孔は、マザーボードのDDRメモリ用コネクタの信号ピンと各々対応することを特徴とする請求項1または2に記載のDDR信号をテストするための補助冶具。

【請求項4】

前記テスト孔は、複数の接地孔をさらに含み、前記接地孔は、マザーボードのDDRメモリ用コネクタの接地ピンと各々対応することを特徴とする請求項1から3のいずれか一項に記載のDDR信号をテストするための補助冶具。

【請求項5】

前記テスト孔は、複数の電源孔をさらに備え、前記電源孔は、マザーボードのDDRメモリ用コネクタの電源ピンと各々対応することを特徴とする請求項1から4のいずれか一項に記載のDDR信号をテストするための補助冶具。

【図1】

【図2】

【図2】

【公開番号】特開2013−108980(P2013−108980A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2012−251158(P2012−251158)

【出願日】平成24年11月15日(2012.11.15)

【出願人】(503023069)鴻富錦精密工業(深▲セン▼)有限公司 (399)

【出願人】(500080546)鴻海精密工業股▲ふん▼有限公司 (1,018)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成24年11月15日(2012.11.15)

【出願人】(503023069)鴻富錦精密工業(深▲セン▼)有限公司 (399)

【出願人】(500080546)鴻海精密工業股▲ふん▼有限公司 (1,018)

【Fターム(参考)】

[ Back to top ]