EL表示装置

【課題】動作性能および信頼性の高いEL表示装置を提供する。

【解決手段】第1のチャネル形成領域と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

【解決手段】第1のチャネル形成領域と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は絶縁表面を有する基板上に薄膜トランジスタ(以下、TFTという)

で構成された回路を有する半導体装置およびその作製方法に関する。特に本発明は、画素

部(画素マトリクス回路)とその周辺に設けられる駆動回路(ドライバー回路)を同一基

板上に設けた液晶表示装置やEL(エレクトロルミネッセンス)表示装置に代表される電

気光学装置(電子装置ともいう)、および電気光学装置を搭載した電気器具(電子機器と

もいう)に関する。

【0002】

尚、本願明細書において半導体装置とは、半導体特性を利用することで機能する装置全

般を指し、上記電気光学装置およびその電気光学装置を用いた電気器具も半導体装置に含

む。

【背景技術】

【0003】

絶縁表面を有する基板上にTFTで形成した大面積集積回路を有する半導体装置の開発

が進んでいる。アクティブマトリクス型液晶表示装置、EL表示装置、および密着型イメ

ージセンサはその代表例として知られている。特に、結晶質シリコン膜(代表的にはポリ

シリコン膜)を活性層にしたTFT(以下、ポリシリコンTFTと記す)は電界効果移動

度が高いことから、いろいろな機能回路を形成することも可能である。

【0004】

例えば、アクティブマトリクス型液晶表示装置には、機能ブロックごとに画像表示を行

う画素部や、CMOS回路を基本としたシフトレジスタ回路、レベルシフタ回路、バッフ

ァ回路、サンプリング回路などの集積回路が一枚の基板上に形成される。また、密着型イ

メージセンサでは、サンプルホールド回路、シフトレジスタ回路、マルチプレクサ回路な

どの集積回路がTFTを用いて形成されている。

【0005】

これらの駆動回路(周辺駆動回路ともいう)はそれぞれにおいて動作条件が必ずしも同

一でないので、当然TFTに要求される特性も少なからず異なっている。画素部において

は、スイッチ素子として機能する画素TFTと補助の保持容量を設けた構成であり、液晶

に電圧を印加して駆動させるものである。ここで、液晶は交流で駆動させる必要があり、

フレーム反転駆動と呼ばれる方式が多く採用されている。従って、要求されるTFTの特

性はオフ電流値(TFTがオフ動作時に流れるドレイン電流値)を十分低くさせておく必

要があった。また、バッファ回路は高い駆動電圧が印加されるため、高電圧がかかっても

壊れない程度に耐圧を高めておく必要があった。また電流駆動能力を高めるために、オン

電流値(TFTがオン動作時に流れるドレイン電流値)を十分確保する必要があった。

【0006】

しかし、ポリシリコンTFTのオフ電流値は高くなりやすいといった問題点がある。ま

た、ICなどで使われるMOSトランジスタと同様にポリシリコンTFTにはオン電流値

の低下といった劣化現象が観測される。主たる原因はホットキャリア注入であり、ドレイ

ン近傍の高電界によって発生したホットキャリアが劣化現象を引き起こすものと考えられ

ている。

【0007】

オフ電流値を低減するためのTFTの構造として、低濃度ドレイン(LDD:Lightly

Doped Drain)構造が知られている。この構造はチャネル形成領域と、高濃度に不純物

が添加されるソース領域またはドレイン領域との間に低濃度の不純物領域を設けたもので

あり、この低濃度不純物領域はLDD領域と呼ばれている。

【0008】

また、ホットキャリア注入によるオン電流値の劣化を防ぐための構造として、いわゆる

GOLD(Gate-drain Overlapped LDD)構造が知られている。この構造は、LDD領

域がゲート絶縁膜を介してゲート配線と重なるように配置されているため、ドレイン近傍

のホットキャリア注入を防ぎ、信頼性を向上させるのに有効である。例えば、「Mutsuko

Hatano,Hajime Akimoto and Takeshi Sakai,IEDM97 TECHNICAL DIGEST,p523-526,

1997」では、シリコンで形成したサイドウォールによるGOLD構造を開示しているが、

他の構造のTFTと比べ、きわめて優れた信頼性が得られることが確認されている。

【0009】

また、アクティブマトリクス型液晶表示装置の画素部には、数十から数百万個の各画素

にTFTが配置され、そのTFTのそれぞれには画素電極が設けられている。液晶を挟ん

だ対向基板側には対向電極が設けられており、液晶を誘電体とした一種のコンデンサを形

成している。そして、各画素に印加する電圧をTFTのスイッチング機能により制御して

、このコンデンサへの電荷を制御することで液晶を駆動し、透過光量を制御して画像を表

示する仕組みになっている。

【0010】

ところが、このコンデンサはオフ電流等に起因するリーク電流により次第にその蓄積容

量が減少するため、透過光量が変化して画像表示のコントラストを低下させる原因となっ

ていた。そこで、従来では容量配線を設けて、液晶を誘電体とするコンデンサとは別のコ

ンデンサ(保持容量という)を並列に設け、液晶を誘電体とするコンデンサが損失する容

量を補っていた。

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかしながら、画素部の画素TFTと、シフトレジスタ回路やバッファ回路などのロジ

ック回路(駆動回路ともいう)のTFT(以下、駆動TFTという)とでは、その要求さ

れる特性は必ずしも同じではない。例えば、画素TFTにおいては、ゲート配線に大きな

逆バイアス(nチャネル型TFTであればマイナス)

電圧が印加されるが、駆動回路のTFTは基本的に逆バイアス電圧が印加されて動作され

ることはない。また、前者の動作速度は後者の1/100以下で良い。

【0012】

また、GOLD構造は確かにオン電流値の劣化を防ぐ効果は高いが、反面、通常のLD

D構造に比べてオフ電流値が大きくなってしまう問題があった。従って、特に画素TFT

にとっては好ましい構造とは言えなかった。逆に通常のLDD構造はオフ電流値を抑える

効果は高いが、ホットキャリア注入には弱いことが知られていた。

【0013】

このように、アクティブマトリクス型液晶表示装置のような複数の集積回路を有する半

導体装置において、全てのTFTを同じ構造で形成することは必ずしも好ましくなかった

。

【0014】

さらに、従来例に示したように画素部に容量配線を用いた保持容量を形成して十分な容

量を確保しようとすると、開口率(一画素の面積に対して画像表示が可能な面積の割合)

を犠牲にしなければならなかった。特に、プロジェクター型表示装置に用いられるような

小型の高精細パネルでは、一個当たりの画素面積も小さいため、容量配線による開口率の

低下は問題となっていた。

【0015】

本発明はこのような課題を解決するための技術であり、半導体装置の各回路に配置され

るTFTの構造を、回路の機能に応じて適切なものとすることにより半導体装置の動作性

能および信頼性を向上させることを目的とする。

【0016】

また、他の目的として画素部を有する半導体装置において、画素に設けられる保持容量

の面積を縮小化し、開口率を向上させるための構造を提供することを目的とする。

【課題を解決するための手段】

【0017】

上記問題点を解決するために本発明の構成は、同一基板上に画素部と駆動回路とを含む

半導体装置において、前記駆動回路を形成するnチャネル型TFTのLDD領域は、一部

または全部が該nチャネル型TFTのゲート配線にゲート絶縁膜を挟んで重なるように形

成され、前記画素部を形成する画素TFTのLDD領域は、該画素TFTのゲート配線に

ゲート絶縁膜を挟んで重ならないように形成されることを特徴とする。

【0018】

また、上記構成に加えて、前記画素部の保持容量を樹脂膜の上に設けられた遮光膜、該

遮光膜の酸化物および画素電極で形成しても良い。こうすることで非常に小さい面積で保

持容量を形成することができるため、画素の開口率を向上させることができる。

【0019】

また、本発明のさらに詳細な構成は、同一基板上に画素部と駆動回路とを含む半導体装

置において、前記駆動回路には、LDD領域の全部がゲート絶縁膜を挟んでゲート配線に

重なるように形成された第1のnチャネル型TFTと、LDD領域の一部がゲート絶縁膜

を挟んでゲート配線に重なるように形成された第2のnチャネル型TFTとが含まれ、前

記画素部には、LDD領域がゲート絶縁膜を挟んでゲート配線に重ならないように形成さ

れた画素TFTが含まれることを特徴とする。勿論、画素部の保持容量を有機樹脂膜の上

に設けられた遮光膜、該遮光膜の酸化物および画素電極で形成しても良い。

【0020】

なお、上記構成において、前記駆動回路を形成するnチャネル型TFTのLDD領域に

は、前記画素TFTのLDD領域に比べて2〜10倍の濃度で周期表の15族に属する元

素を含ませておけば良い。また、前記第1のnチャネル型TFTのLDD領域をチャネル

形成領域とドレイン領域との間に形成し、前記第2のnチャネル型TFTのLDD領域を

チャネル形成領域を挟んで形成しても良い。

【0021】

また、作製工程に関する本発明の構成は、同一基板上に画素部と駆動回路とを含む半導

体装置の作製方法において、前記駆動回路を形成する第1のnチャネル型TFTの活性層

に、チャネル形成領域、ソース領域、ドレイン領域並びに前記ドレイン領域と前記チャネ

ル形成領域との間のLDD領域を形成する工程と、前記駆動回路を形成する第2のnチャ

ネル型TFTの活性層に、チャネル形成領域、ソース領域、ドレイン領域並びに前記ソー

ス領域と前記チャネル形成領域との間のLDD領域及び前記ドレイン領域と前記チャネル

形成領域との間のLDD領域形成する工程と、前記駆動回路を形成するpチャネル型TF

Tの活性層に、チャネル形成領域、ソース領域およびドレイン領域を形成する工程と、前

記画素部を形成する画素TFTの活性層に、チャネル形成領域、ソース領域、ドレイン領

域並びに前記ドレイン領域と前記チャネル形成領域との間のLDD領域を形成する工程と

、を有し、前記第1のnチャネル型TFTのLDD領域は、全部が該第1のnチャネル型

TFTのゲート配線にゲート絶縁膜を挟んで重なって形成され、前記第2のnチャネル型

TFTのLDD領域は、一部が該第1のnチャネル型TFTのゲート配線にゲート絶縁膜

を挟んで重なって形成され、前記画素TFTのLDD領域は、該画素TFTのゲート配線

にゲート絶縁膜を挟んで重ならないように配置されることを特徴とする。

【0022】

また、作製工程に関する他の発明の構成は、同一基板上に画素部と駆動回路とを含む半

導体装置の作製方法において、基板上に活性層を形成する第1工程と、前記活性層に接し

てゲート絶縁膜を形成する第2工程と、前記駆動回路を形成するnチャネル型TFTの活

性層に周期表の15族に属する元素を添加してn-領域を形成する第3工程と、前記ゲー

ト絶縁膜上に導電膜を形成する第4工程と、前記導電膜をパターニングしてpチャネル型

TFTのゲート配線を形成する第5工程と、前記pチャネル型TFTの活性層に、該pチ

ャネル型TFTのゲート配線をマスクとして自己整合的に周期表の13族に属する元素を

添加し、p++領域を形成する第6工程と、前記第5工程でパターニングされなかった導電

膜をパターニングしてnチャネル型TFTのゲート配線を形成する第7工程と、前記nチ

ャネル型TFTの活性層に、周期表の15族に属する元素を添加し、n+領域を形成する

第8工程と、前記nチャネル型TFT及び前記pチャネル型TFTのゲート配線をマスク

として自己整合的に周期表の15族に属する元素を添加し、n--領域を形成する第9工程

と、を有することを特徴とする。

【0023】

また、本発明のさらに詳細な構成は、同一基板上に画素部と駆動回路とを含む半導体装

置の作製方法において、基板上に活性層を形成する第1工程と、前記活性層に接してゲー

ト絶縁膜を形成する第2工程と、前記駆動回路を形成するnチャネル型TFTの活性層に

周期表の15族に属する元素を添加してn-領域を形成する第3工程と、前記ゲート絶縁

膜上に導電膜を形成する第4工程と、前記導電膜をパターニングしてpチャネル型TFT

のゲート配線を形成する第5工程と、前記pチャネル型TFTの活性層に、該pチャネル

型TFTのゲート配線をマスクとして自己整合的に周期表の13族に属する元素を添加し

、p++領域を形成する第6工程と、前記第5工程でパターニングされなかった導電膜をパ

ターニングしてnチャネル型TFTのゲート配線を形成する第7工程と、前記nチャネル

型TFTの活性層に、周期表の15族に属する元素を添加し、n+領域を形成する第8工

程と、前記nチャネル型TFT及び前記pチャネル型TFTのゲート配線をマスクとして

自己整合的に周期表の15族に属する元素を添加し、n--領域を形成する第9工程と、

を有することを特徴とする。

【0024】

なお、この構成において、p++領域、n+領域またはn--領域を形成する工程の順序は

適宜変更しても構わない。どのような順序としても、最終的に形成されるTFTの基本的

な機能は変化せず、本発明の効果を損なうものではない。

【発明の効果】

【0025】

本願発明を用いることで同一基板上に、回路が要求する仕様に応じて適切な性能の回路

を配置することが可能となり、半導体装置(ここでは具体的に電気光学装置)の動作性能

や信頼性を大幅に向上させることができた。

【0026】

また、AM−LCDに代表される電気光学装置の画素部において、小さい面積で大きな

キャパシティを有する保持容量を形成することができる。そのため、対角1インチ以下の

AM−LCDにおいても開口率を低下させることなく、十分な保持容量を確保することが

可能となった。

【0027】

また、そのような電気光学装置を表示媒体として有する半導体装置(ここでは具体的に

電気器具)の動作性能と信頼性も向上させることができた。

【図面の簡単な説明】

【0028】

【図1】画素部と駆動回路の作製工程を示す図。

【図2】画素部と駆動回路の作製工程を示す図。

【図3】画素部と駆動回路の作製工程を示す図。

【図4】保持容量の構成を示す図。

【図5】保持容量の作製工程を示す図。

【図6】画素部と駆動回路の作製工程を示す図。

【図7】画素部と駆動回路の作製工程を示す図。

【図8】画素部と駆動回路の作製工程を示す図。

【図9】アクティブマトリクス型液晶表示装置の断面構造図。

【図10】アクティブマトリクス型液晶表示装置の斜視図。

【図11】画素部の上面図。

【図12】保持容量の構成を示す断面図。

【図13】アクティブマトリクス型液晶表示装置の回路ブロック図。

【図14】結晶質半導体膜の作製工程を示す断面図。

【図15】結晶質半導体膜の作製工程を示す断面図。

【図16】画素部と駆動回路の作製工程を示す図。

【図17】画素部の上面図および断面図。

【図18】画素部と駆動回路の作製工程を示す図。

【図19】画素部と駆動回路の作製工程を示す図。

【図20】画素部と駆動回路の作製工程を示す図。

【図21】画素部と駆動回路の作製工程を示す図。

【図22】画素部と駆動回路の作製工程を示す図。

【図23】画素部と駆動回路の構成を示す図。

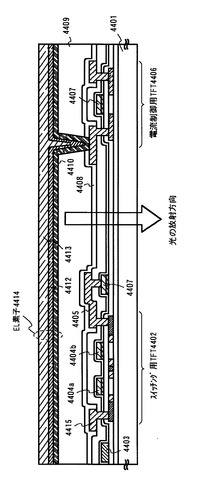

【図24】アクティブマトリクス型EL表示装置の構成を示す図。

【図25】EL表示装置の上面構造及び断面構造を示す図。

【図26】EL表示装置の断面構造を示す図。

【図27】EL表示装置の画素部の上面構造を示す図。

【図28】EL表示装置の断面構造を示す図。

【図29】EL表示装置の画素部の回路構成を示す図。

【図30】電気器具の一例を示す図。

【図31】電気器具の一例を示す図。

【図32】光学エンジンの構成を示す図。

【図33】nチャネル型TFTのID−VG曲線を示す図。

【図34】電界効果移動度の劣化率とLov領域の長さの関係を示す図。

【図35】消費電流と最低動作電圧の経時変化を示す図。

【図36】nチャネル型TFTのID−VG曲線を示す図。

【図37】電界効果移動度の劣化率とLov領域の長さの関係を示す図。

【図38】消費電流と最低動作電圧の経時変化を示す図。

【発明を実施するための形態】

【0029】

本発明の実施の形態について、以下に示す実施例でもって詳細な説明を行うこととする

。

【実施例1】

【0030】

本発明の実施形態を、図1〜図3を用いて説明する。ここでは、画素部とその周辺に設

けられる駆動回路のTFTを同時に作製する方法について説明する。

【0031】

〔活性層、ゲート絶縁膜形成の工程:図1(A)〕 図1(A)において、基板101

には、ガラス基板、石英基板もしくはプラスチック基板(フィルムも含む)を使用するこ

とが望ましい。その他にもシリコン基板や金属基板の表面に絶縁膜を形成したものを基板

としても良い。

【0032】

そして、基板101のTFTが形成される表面には、珪素(シリコン)を含む絶縁膜(

本明細書中では酸化シリコン膜、窒化シリコン膜、または窒化酸化シリコン膜の総称を指

す)からなる下地膜102をプラズマCVD法やスパッタ法で100〜400nmの厚さ

に形成した。なお、本明細書中において窒化酸化シリコン膜とはSiOxNy(但し、0<

x、y<1)で表される絶縁膜であり、珪素、酸素、窒素を所定の割合で含む絶縁膜を指

す。

【0033】

本実施例では、下地膜102として、窒化シリコン膜102を25〜100nm、ここ

では50nmの厚さに、酸化シリコン膜103を50〜300nm、ここでは150nm

の厚さとした2層構造で形成した。下地膜102は基板からの不純物汚染を防ぐために設

けられるものであり、石英基板を用いた場合には必ずしも設けなくても良い。

【0034】

次に下地膜102の上に20〜100nmの厚さの、非晶質シリコン膜を公知の成膜法

で形成した。非晶質シリコン膜は含有水素量にもよるが、好ましくは400〜550℃で

数時間加熱して脱水素処理を行い、含有水素量を5atom%以下として、結晶化の工程を行

うことが望ましい。また、非晶質シリコン膜をスパッタ法や蒸着法などの他の作製方法で

形成しても良いが、膜中に含まれる酸素、窒素などの不純物元素を十分低減させておくこ

とが望ましい。ここでは、下地膜と非晶質シリコン膜とは、同じ成膜法で形成することが

可能であるので両者を連続形成しても良い。下地膜を形成後、一旦大気雰囲気にさらされ

ないようにすることで表面の汚染を防ぐことが可能となり、作製されるTFTの特性バラ

ツキを低減させることができる。

【0035】

非晶質シリコン膜から結晶質シリコン膜を形成する工程は、公知のレーザー結晶化技術

または熱結晶化の技術を用いれば良い。また、シリコンの結晶化を助長する触媒元素を用

いて熱結晶化の方法で結晶質シリコン膜を作製しても良い。その他に、微結晶シリコン膜

を用いても良いし、結晶質シリコン膜を直接堆積成膜しても良い。さらに、単結晶シリコ

ンを基板上に貼りあわせるSOI(Silicon On Insulators)の公知技術を使用して結

晶質シリコン膜を形成しても良い。

【0036】

こうして形成された結晶質シリコン膜の不要な部分をエッチング除去して、島状の半導

体膜(以下、活性層という)104〜106を形成した。結晶質シリコン膜のnチャネル

型TFTが作製される領域には、しきい値電圧を制御するため、あらかじめ1×1015〜

5×1017cm-3程度の濃度でボロン(B)を添加しておいても良い。

【0037】

次に、活性層104〜106を覆って、酸化シリコンまたは窒化シリコンを主成分とす

るゲート絶縁膜107を形成した。ゲート絶縁膜107は、10〜200nm、好ましく

は50〜150nmの厚さに形成すれば良い。例えば、プラズマCVD法でN2OとSi

H4を原料とした窒化酸化シリコン膜を75nm形成し、その後、酸素雰囲気中または酸

素と塩酸の混合雰囲気中、800〜1000℃で熱酸化して115nmのゲート絶縁膜と

しても良い。(図1(A))

【0038】

〔n-領域の形成:図1(B)〕 活性層104、106及び配線を形成する領域の全

面と、活性層105の一部(チャネル形成領域となる領域を含む)にレジストマスク10

8〜111を形成し、n型を付与する不純物元素を添加して低濃度不純物領域112を形

成した。

この低濃度不純物領域112は、後にCMOS回路のnチャネル型TFTに、ゲート絶縁

膜を介してゲート配線と重なるLDD領域(本明細書中ではこのLDD領域をLov領域と

呼ぶ。なお、ovとはoverlapの意味である。)を形成するための不純物領域である。なお

、ここで形成された低濃度不純物領域に含まれるn型を付与する不純物元素の濃度を(n

-)で表すこととする。従って、本明細書中では低濃度不純物領域112をn-領域と言い

換えることができる。

【0039】

ここではフォスフィン(PH3)を質量分離しないでプラズマ励起したイオンドープ法

でリンを添加した。勿論、質量分離を行うイオンインプランテーション法を用いても良い

。この工程では、ゲート絶縁膜107を通してその下の半導体層にリンを添加した。添加

するリン濃度は、2×1016〜5×1019atoms/cm3の範囲にするのが好ましく、ここで

は1×1018atoms/cm3とした。

【0040】

その後、レジストマスク108〜111を除去し、窒素雰囲気中で400〜900℃、

好ましくは550〜800℃で1〜12時間の熱処理を行ない、この工程で添加されたリ

ンを活性化する工程を行なった。また、この活性化をレーザーにより行っても良い。なお

、この工程は省略することも可能であるが、行った方がより高い活性化率を期待できる。

【0041】

〔ゲート配線の形成:図1(C)〕 第1の導電膜113を、タンタル(Ta)、チタ

ン(Ti)、モリブデン(Mo)、タングステン(W)から選ばれた元素またはいずれか

の元素を主成分とする導電性材料で、10〜100nmの厚さに形成した。第1の導電膜

113としては、例えば窒化タンタル(TaN)や窒化タングステン(WN)を用いるこ

とが望ましい。

【0042】

さらに、第1の導電膜113上に第2の導電膜114をTa、Ti、Mo、Wから選ば

れた元素またはいずれかの元素を主成分とする導電性材料で、100〜400nmの厚さ

に形成した。例えば、Taを200nmの厚さに形成すれば良い。また、図示しないが、

第1の導電膜113の下、もしくは第2の導電膜114の上に導電膜113、114(特

に導電膜114)の酸化防止のためにシリコン膜を2〜20nm程度の厚さで形成してお

くことは有効である。

【0043】

〔p−chゲート配線の形成とp++領域の形成:図2(A)〕 レジストマスク115

〜118を形成し、第1の導電膜と第2の導電膜(以下、積層膜として取り扱う)をエッ

チングして、pチャネル型TFTのゲート配線(ゲート電極ともいう)119、ゲート配

線120、121を形成した。なお、ここではnチャネル型TFTとなる領域の上には全

面を覆うように導電膜122、123を残した。

【0044】

そして、レジストマスク115〜118をそのまま残してマスクとし、pチャネル型T

FTが形成される半導体層104の一部に、p型を付与する不純物元素を添加する工程を

行った。ここではボロンをその不純物元素として、ジボラン(B2H6)を用いてイオンド

ープ法(勿論、イオンインプランテーション法でも良い)で添加した。ここでは5×10

20〜3×1021atoms/cm3の濃度にボロンを添加した。なお、ここで形成された不純物領

域に含まれるp型を付与する不純物元素の濃度を(p++)で表すこととする。従って、本

明細書中では不純物領域124、125をp++領域と言い換えることができる。

【0045】

なお、この工程において、レジストマスク115〜118を使用してゲート絶縁膜10

7をエッチング除去して、活性層104の一部を露出させた後、p型を付与する不純物元

素を添加する工程を行っても良い。その場合、加速電圧が低くて済むため、活性層に与え

るダメージも少ないし、スループットも向上する。

【0046】

〔n―chゲート配線の形成:図2(B)〕 次に、レジストマスク115〜118は

除去した後、レジストマスク126〜129を形成し、nチャネル型TFTのゲート配線

130、131を形成した。

このときゲート配線130はn-領域112とゲート絶縁膜107を介して重なるように

形成した。

【0047】

〔n+領域の形成:図2(C)〕 次に、レジストマスク126〜129を除去し、レ

ジストマスク132〜134を形成した。そして、nチャネル型TFTにおいて、ソース

領域またはドレイン領域として機能する不純物領域を形成する工程を行なった。レジスト

マスク134はnチャネル型TFTのゲート配線131を覆う形で形成した。これは、後

の工程において画素部のnチャネル型TFTに、ゲート配線と重ならないようにLDD領

域を形成するためである。

【0048】

そして、n型を付与する不純物元素を添加して不純物領域135〜139を形成した。

ここでも、フォスフィン(PH3)を用いたイオンドープ法(勿論、イオンインプランテ

ーション法でも良い)で行い、この領域のリンの濃度は1×1020〜1×1021atoms/cm

3とした。なお、ここで形成された不純物領域137〜139に含まれるn型を付与する

不純物元素の濃度を(n+)で表すこととする。従って、本明細書中では不純物領域13

7〜139をn+領域と言い換えることができる。また、不純物領域135は既にn-領域

が形成されていたので、厳密には不純物領域136〜139よりも若干高い濃度でリンを

含む。

【0049】

なお、この工程において、レジストマスク132〜134およびゲート配線130をマ

スクとしてゲート絶縁膜107をエッチングし、活性層105、106の一部を露出させ

た後、n型を付与する不純物元素を添加する工程を行っても良い。その場合、加速電圧が

低くて済むため、活性層に与えるダメージも少ないし、スループットも向上する。

【0050】

〔n--領域の形成:図3(A)〕 次に、レジストマスク132〜134を除去し、画

素部のnチャネル型TFTとなる活性層106にn型を付与する不純物元素を添加する工

程を行った。こうして形成された不純物領域140〜143には前記n-領域の1/2〜

1/10の濃度(具体的には1×1016〜5×1018atoms/cm3)でリンが添加されるよ

うにした。なお、ここで形成された不純物領域140〜143に含まれるn型を付与する

不純物元素の濃度を(n--)で表すこととする。従って、本明細書中では不純物領域14

0〜143をn--領域と言い換えることができる。また、この工程ではゲート配線で隠さ

れた不純物領域167を除いて全ての不純物領域にn--の濃度でリンが添加されているが

、非常に低濃度であるため無視して差し支えない。

【0051】

〔熱活性化の工程:図3(B)〕 次に、後に第1の層間絶縁膜の一部となる保護絶縁

膜144を形成した。保護絶縁膜144は窒化シリコン膜、酸化シリコン膜、窒化酸化シ

リコン膜またはそれらを組み合わせた積層膜で形成すれば良い。また、膜厚は100〜4

00nmとすれば良い。

【0052】

その後、それぞれの濃度で添加されたn型またはp型を付与する不純物元素を活性化す

るために熱処理工程を行った。この工程はファーネスアニール法、レーザーアニール法、

またはラピッドサーマルアニール法(RTA法)で行うことができる。ここではファーネ

スアニール法で活性化工程を行った。加熱処理は、窒素雰囲気中において300〜650

℃、好ましくは400〜550℃、ここでは450℃、2時間の熱処理を行った。

【0053】

さらに、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱

処理を行い、活性層を水素化する工程を行った。この工程は加熱励起された水素により半

導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ

水素化(プラズマにより励起された水素を用いる)を行っても良い。

【0054】

〔層間絶縁膜、ソース/ドレイン配線、遮光膜、画素電極、保持容量の形成:図3(C

)〕 活性化工程を終えたら、保護絶縁膜144の上に0.5〜1.5μm厚の層間絶縁

膜145を形成した。前記保護絶縁膜144と層間絶縁膜145とでなる積層膜を第1の

層間絶縁膜とした。

【0055】

その後、それぞれのTFTのソース領域またはドレイン領域に達するコンタクトホール

が形成され、ソース配線146〜148と、ドレイン配線149、150を形成した。図

示していないが、本実施例ではこれらの配線を、Ti膜を100nm、Tiを含むアルミ

ニウム膜300nm、Ti膜150nmをスパッタ法で連続して形成した3層構造の積層

膜とした。なお、ソース配線及びドレイン配線として銅膜と窒化チタン膜との積層膜を用

いても良い。

【0056】

次に、パッシベーション膜151として、窒化シリコン膜、酸化シリコン膜、または窒

化酸化シリコン膜で50〜500nm(代表的には200〜300nm)の厚さで形成し

た。その後、この状態で水素化処理を行うとTFTの特性向上に対して好ましい結果が得

られた。例えば、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時

間の熱処理を行うと良く、あるいはプラズマ水素化法を用いても同様の効果が得られた。

なお、ここで後に画素電極とドレイン配線を接続するためのコンタクトホールを形成する

位置において、パッシベーション膜151に開口部を形成しておいても良い。

【0057】

その後、有機樹脂からなる第2の層間絶縁膜152を約1μmの厚さに形成した。有機

樹脂としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB(ベンゾ

シクロブテン)等を使用することができる。有機樹脂膜を用いることの利点は、成膜方法

が簡単である点や、比誘電率が低いので、寄生容量を低減できる点、平坦性に優れる点な

どが上げられる。なお上述した以外の有機樹脂膜や有機系SiO化合物などを用いることも

できる。ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300℃で焼

成して形成した。

【0058】

次に、画素部となる領域において、第2の層間絶縁膜152上に遮光膜153を形成し

た。遮光膜153はアルミニウム(Al)、チタン(Ti)、タンタル(Ta)から選ば

れた元素またはいずれかを主成分とする膜で100〜300nmの厚さに形成した。そし

て、遮光膜153の表面に陽極酸化法またはプラズマ酸化法により30〜150nm(好

ましくは50〜75nm)の厚さの酸化物(酸化膜)154を形成した。ここでは遮光膜

153としてアルミニウム膜またはアルミニウムを主成分とする膜を用い、酸化物154

として酸化アルミニウム膜(アルミナ膜)を用いた。

【0059】

なお、ここでは遮光膜表面のみに絶縁膜を設ける構成としたが、絶縁膜をプラズマCV

D法、熱CVD法またはスパッタ法などの気相法によって形成しても良い。その場合も膜

厚は30〜150nm(好ましくは50〜75nm)とすることが好ましい。また、酸化

シリコン膜、窒化シリコン膜、窒化酸化シリコン膜、DLC(Diamond like carbon)

膜または有機樹脂膜を用いても良い。さらに、これらを組み合わせた積層膜を用いても良

い。

【0060】

次に、第2の層間絶縁膜152にドレイン配線150に達するコンタクトホールを形成

し、画素電極155を形成した。なお、画素電極156、157はそれぞれ隣接する別の

画素の画素電極である。画素電極155〜157は、透過型液晶表示装置とする場合には

透明導電膜を用い、反射型の液晶表示装置とする場合には金属膜を用いれば良い。ここで

は透過型の液晶表示装置とするために、酸化インジウムと酸化スズとの化合物(ITOと

呼ばれる)膜を100nmの厚さにスパッタ法で形成した。

【0061】

また、この時、画素電極155と遮光膜153とが酸化物154を介して重なった領域

158が保持容量を形成した。

【0062】

こうして同一基板上に、駆動回路を形成するCMOS回路と画素部とを有したアクティ

ブマトリクス基板が完成した。なお、駆動回路を形成するCMOS回路にはnチャネル型

TFT181、pチャネル型TFT182が形成され、画素部にはnチャネル型TFTで

なる画素TFT183が形成された。

【0063】

CMOS回路のpチャネル型TFT181には、チャネル形成領域161並びにp++領

域で形成されたソース領域162及びドレイン領域163が形成された。また、nチャネ

ル型TFT182には、チャネル形成領域164、ソース領域165、ドレイン領域16

6、ゲート絶縁膜を介してゲート配線と全部重なったLDD領域(Lov領域)167が形

成された。この時、ソース領域165、ドレイン領域166はそれぞれn+領域(厳密に

は(n-+n+)領域)で形成され、Lov領域167はn-領域で形成された。

【0064】

また、図3(C)ではできるだけ抵抗成分を減らすためにチャネル形成領域164の片

側のみ(ドレイン領域側のみ)にLov領域を配置しているが、チャネル形成領域164を

挟んで両側に配置しても良い。

【0065】

また、画素TFT183には、チャネル形成領域168、169、ソース領域170、

ドレイン領域171、ゲート絶縁膜を介してゲート配線と重ならないLDD領域(以下、

このLDD領域をLoff領域という。なお、offとはoffsetの意である。)172〜175

、Loff領域173、174に接したn+領域(オフ電流値の低減に効果がある)176が

形成された。この時、ソース領域170、ドレイン領域171はそれぞれn+領域で形成

され、Loff領域172〜175はn--領域で形成される。

【0066】

本発明は、画素部および駆動回路が要求する回路仕様に応じて各回路を形成するTFT

の構造を最適化し、半導体装置の動作性能および信頼性を向上させることができた。具体

的には、nチャネル型TFTは回路仕様に応じてLDD領域の配置を異ならせ、Lov領域

またはLoff領域を使い分けることによって、同一基板上に高速動作またはホットキャリ

ア対策を重視したTFT構造と低オフ電流動作を重視したTFT構造とを実現した。

【0067】

例えば、アクティブマトリクス型液晶表示装置の場合、nチャネル型TFT182は高

速動作を重視するシフトレジスタ回路、分周波回路、信号分割回路、レベルシフタ回路、

バッファ回路などのロジック回路に適している。また、nチャネル型TFT183は低オ

フ電流動作を重視した画素部、サンプリング回路(トランスファーゲートともいう)に適

している。

【0068】

また、チャネル長3〜7μmに対してLov領域の長さ(幅)は0.5〜3.0μm、代

表的には1.0〜1.5μmとすれば良い。また、画素TFT183に設けられるLoff

領域172〜175の長さ(幅)は0.5〜3.5μm、代表的には2.0〜2.5μm

とすれば良い。

【実施例2】

【0069】

本実施例では、アクティブマトリクス基板の画素部のnチャネル型TFT401に接続

される保持容量の他の構成について図4を用いて説明する。なお、図4の断面構造は実施

例1で説明した作製工程に従って、酸化物154を形成するところまで全く同一であるの

で、そこまでの構造は図1〜3で既に説明されている。従って、本実施例では実施例1と

異なる点のみに注目して説明を行うこととする。

【0070】

実施例1の工程に従って遮光膜153、遮光膜153を酸化して得られた酸化物154

を形成したら、有機樹脂膜でなるスペーサー402〜404を形成する。有機樹脂膜とし

ては、ポリイミド、ポリアミド、ポリイミドアミド、アクリル、BCB(ベンゾシクロブ

テン)から選ばれた膜を用いることができる。その後、スペーサー402、第2の層間絶

縁膜152、パッシベーション膜151をエッチングしてコンタクトホールを形成し、実

施例1と同一の材料で画素電極405を形成する。なお、画素電極406、407は隣接

する別の画素の画素電極である。

【0071】

こうして、遮光膜153と画素電極405が酸化物154を介して重なった領域におい

て保持容量408が形成される。このようにスペーサー402〜404を設けることによ

り、遮光膜153と画素電極405〜407との間で発生するショート(短絡)を防止す

ることができる。

【0072】

なお、本実施例の構成は実施例1の構成と組み合わせることが可能である。

【実施例3】

【0073】

本実施例では、アクティブマトリクス基板の画素部のnチャネル型TFTに接続される

保持容量の他の構成について図5を用いて説明する。なお、図5の断面構造は実施例1で

説明した作製工程に従って、遮光膜153を形成するところまで全く同一であるので、そ

こまでの構造は図1〜3で既に説明されている。従って、本実施例では実施例1と異なる

点のみに注目して説明を行うこととする。

【0074】

まず実施例1の工程に従って遮光膜153を形成したら、遮光膜153の端部を覆うよ

うにして有機樹脂膜でなるスペーサー501〜503を形成する。有機樹脂膜としては、

ポリイミド、ポリアミド、ポリイミドアミド、アクリル、BCB(ベンゾシクロブテン)

から選ばれた膜を用いることができる。(図5(A)

)

【0075】

次に、陽極酸化法またはプラズマ酸化法により遮光膜153の露出した表面に酸化物5

04を形成する。なお、スペーサー501〜503と接した部分には酸化物504は形成

されない。(図5(B))

【0076】

次に、スペーサー501、第2の層間絶縁膜152、パッシベーション膜151をエッ

チングしてコンタクトホールを形成し、実施例1と同一の材料で画素電極505を形成す

る。なお、画素電極506、507は隣接する別の画素の画素電極である。

【0077】

こうして、遮光膜153と画素電極505が酸化物504を介して重なった領域におい

て保持容量508が形成される。このようにスペーサー501〜503を設けることによ

り、遮光膜153と画素電極505〜507との間で発生するショート(短絡)を防止す

ることができる。

【0078】

なお、本実施例の構成は実施例1の構成と組み合わせることが可能である。

【実施例4】

【0079】

本実施例では本発明の構成について図6〜図8を用い、画素部とその周辺に設けられる

駆動回路の基本形態であるCMOS回路を同時に形成したアクティブマトリクス基板の作

製方法について説明する。

【0080】

最初に、基板601上に下地膜として窒化酸化シリコン膜602aを50〜500nm

、代表的には100nmの厚さに形成した。窒化酸化シリコン膜602aは、SiH4と

N2OとNH3を原料ガスとして作製されるものであり、含有する窒素濃度を25atomic%

以上50atomic%未満となるようにした。その後、窒素雰囲気中で450〜650℃の熱

処理を施し、窒化酸化シリコン膜602aを緻密化した。

【0081】

さらに窒化酸化シリコン膜602bを100〜500nm、代表的には200nmの厚

さに形成し、連続して非晶質半導体膜(図示せず)を20〜80nmの厚さに形成した。

本実施例では非晶質半導体膜としては非晶質シリコン膜を用いたが、微結晶シリコン膜や

非晶質シリコンゲルマニウム膜を用いても良い。

【0082】

そして特開平7−130652号公報(米国特許番号5,643,826号及び5,9

23,962号に対応)に記載された結晶化手段により非晶質シリコン膜を結晶化し、結

晶質シリコン膜(図示せず)を形成した。同公報記載の技術は、非晶質シリコン膜の結晶

化に際して、結晶化を助長する触媒元素(ニッケル、コバルト、ゲルマニウム、錫、鉛、

パラジウム、鉄、銅から選ばれた一種または複数種の元素、代表的にはニッケル)を用い

る結晶化手段である。具体的には、非晶質シリコン膜表面に触媒元素を保持させた状態で

加熱処理を行い、非晶質シリコン膜を結晶質シリコン膜に変化させるものである。

【0083】

こうして結晶質シリコン膜を形成したら、エキシマレーザー光を照射することにより残

存した非晶質成分の結晶化を行い、全体の結晶性を向上させる。なお、エキシマレーザー

光はパルス発振型でも連続発振型でも良いが、ビーム形を線状に加工して照射することで

大型基板にも対応できる。

【0084】

次に、結晶質シリコン膜をパターニングして、活性層603〜606を形成し、さらに

それらを覆ってゲート絶縁膜607を形成した。ゲート絶縁膜607は、SiH4とN2O

とから作製される窒化酸化シリコン膜であり、ここでは10〜200nm、好ましくは5

0〜150nmの厚さで形成した。(図6(A))

【0085】

次に、活性層603、606の全面と、活性層604、605の一部(チャネル形成領

域を含む)を覆うレジストマスク608〜611を形成した。そして、フォスフィン(P

H3)を用いたイオンドープ法でn型を付与する不純物元素(本実施例ではリン)を添加

して後にLov領域またはLoff領域となるn-領域612〜614を形成した。この工程で

は、ゲート絶縁膜607を通してその下の活性層にリンを添加するために、加速電圧は6

5keVに設定した。活性層に添加されるリンの濃度は、2×1016〜5×1019atoms/

cm3の範囲にするのが好ましく、ここでは1×1018atoms/cm3とした。(図6(B))

【0086】

次に、第1の導電膜615を、スパッタ法により窒化タンタル(TaN)で形成した。

続いて、アルミニウム(Al)を主成分とする第2の導電膜616を、100〜300n

mの厚さに形成した。(図6(C))

【0087】

そして、第2の導電膜をエッチングして配線617を形成した。本実施例の場合、第2

の導電膜がAlであるので、リン酸溶液により下地であるTaN膜との選択比が良好であ

った。さらに、第1の導電層615と配線617の上に第3の導電膜618をタンタル(

Ta)で100〜400nm(本実施例では200nm)の厚さに形成した。なお、この

タンタル膜の上にさらに窒化タンタル膜を形成しても構わない。(図6(D))

【0088】

次に、レジストマスク619〜624を形成し、第1の導電膜と第3の導電膜の一部を

エッチング除去して、低抵抗な接続配線625、pチャネル型TFTのゲート配線626

、画素部のゲート配線627を形成した。なお、導電膜628〜630はnチャネル型T

FTとなる領域上に残しておく。また、この接続配線625は、配線抵抗を極力小さくし

た部分(例えば、外部信号の入出力端子から駆動回路の入出力端子までの配線部分)に形

成する。但し、構造上、配線幅がある程度太くなってしまうので、微細な配線を必要とす

る部分には不向きである。

【0089】

上記第1の導電膜(TaN膜)と第2の導電膜(Ta膜)のエッチングはCF4とO2の

混合ガスにより行うことができた。そして、レジストマスク619〜624をそのまま残

して、pチャネル型TFTが形成される活性層603の一部に、p型を付与する不純物元

素を添加する工程を行った。ここではボロンをその不純物元素として、ジボラン(B2H6

)を用いてイオンドープ法(勿論、イオンインプランテーション法でも良い)で添加した

。ボロンの添加濃度は5×1020〜3×1021atoms/cm3(本実施例では2×1021atoms

/cm3)とした。そして、ボロンが高濃度に添加されたp++領域631、632を形成さし

た。(図7(A)

)

【0090】

なお、この工程において、レジストマスク619〜624をマスクとしてゲート絶縁膜

107をエッチングし、活性層603の一部を露出させた後、ボロンを添加する工程を行

っても良い。その場合、加速電圧が低くて済むため、活性層に与えるダメージも少ないし

、スループットも向上する。

【0091】

次に、レジストマスク619〜624を除去した後、新たにレジストマスク633〜6

38を形成した。これはnチャネル型TFTのゲート配線を形成するためのものであり、

ドライエッチング法によりnチャネル型TFTのゲート配線639〜641が形成された

。このときゲート配線639、640はn-領域612〜614の一部と重なるように形

成した。(図7(B))

【0092】

次に、レジストマスク633〜638を除去した後、新たにレジストマスク642〜6

47を形成した。レジストマスク644、646はnチャネル型TFTのゲート配線64

0、641とn-領域の一部を覆う形で形成した。

【0093】

そして、n型を付与する不純物元素(本実施例ではリン)を1×1020〜1×1021at

oms/cm3(本実施例では5×1020atoms/cm3)の濃度で添加して活性層604〜606に

n+領域647〜653を形成した。(図7(C))

【0094】

なお、この工程において、レジストマスク642〜647を用いてゲート絶縁膜107

をエッチング除去し、活性層604〜606の一部を露出させた後、リンを添加する工程

を行っても良い。その場合、加速電圧が低くて済むため、活性層に与えるダメージも少な

いし、スループットも向上する。

【0095】

次に、レジストマスク642〜646を除去し、画素部のnチャネル型TFTとなる活

性層606にn型を付与する不純物元素(本実施例ではリン)を添加する工程を行った。

こうして前記n-領域の1/2〜1/10の濃度(具体的には1×1016〜5×1018ato

ms/cm3)でリンが添加されたn--領域654〜657を形成した。

【0096】

また、この工程ではゲート配線で隠された不純物領域658〜660を除いて全ての不

純物領域にn--の濃度でリンが添加された。実際、その濃度は非常に低濃度であるため無

視して差し支えない。但し、厳密には659、660で示される領域がn-領域であるの

に対し、661、662で示される領域は(n-+n--)領域となり、前記n-領域659

、660よりも若干高い濃度でリンを含む。(図8(A))

【0097】

次に、100〜400nm厚の保護絶縁膜663をプラズマCVD法でSiH4、N2O

、NH3を原料とした窒化酸化シリコン膜で形成した。この窒化酸化シリコン膜中の含有

水素濃度は1〜30atomic%となるように形成することが望ましかった。保護絶縁膜66

3としては、他にも酸化シリコン膜、窒化シリコン膜またはそれらを組み合わせた積層膜

を用いることができる。

【0098】

その後、それぞれの濃度で添加されたn型またはp型を付与する不純物元素を活性化す

るために熱処理工程を行った。この工程はファーネスアニール法、レーザーアニール法、

またはラピッドサーマルアニール法(RTA法)で行うことができる。ここではファーネ

スアニール法で活性化工程を行った。加熱処理は、窒素雰囲気中において300〜650

℃、好ましくは400〜550℃、ここでは450℃、2時間の熱処理を行った。

【0099】

さらに、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱

処理を行い、活性層を水素化する工程を行った。この工程は熱的に励起された水素により

半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズ

マ水素化(プラズマにより励起された水素を用いる)

を行っても良い。(図8(B))

【0100】

活性化工程を終えたら、保護絶縁膜663の上に0.5〜1.5μm厚の層間絶縁膜6

64を形成した。前記保護絶縁膜663と層間絶縁膜664とでなる積層膜を第1の層間

絶縁膜とした。

【0101】

その後、それぞれのTFTのソース領域またはドレイン領域に達するコンタクトホール

が形成され、ソース配線665〜668と、ドレイン配線669〜672を形成した。な

お、図示されていないがCMOS回路を形成するためにドレイン配線669と670は同

一配線として接続されている。また、入出力端子間、回路間を結ぶ接続配線673、67

4も同時に形成した。なお、図示していないが本実施例ではこの配線を、Ti膜を100

nm、Tiを含むアルミニウム膜300nm、Ti膜150nmをスパッタ法で連続して

形成した3層構造の積層膜とした。

【0102】

次に、パッシベーション膜675として、窒化シリコン膜、酸化シリコン膜、または窒

化酸化シリコン膜で50〜500nm(代表的には200〜300nm)の厚さで形成し

た。パッシベーション膜675はプラズマCVD法でSiH4、N2O、NH3から形成さ

れる窒化酸化シリコン膜、またはSiH4、N2、NH3から作製される窒化シリコン膜で

形成すれば良い。

【0103】

まず、膜の形成に先立ってN2O、N2、NH3等を導入してプラズマ水素化処理により

水素化の工程を行なった。プラズマ処理により励起された水素は第1の層間絶縁膜中に供

給され、基板を200〜400℃に加熱しておけば、その水素を下層側にも拡散させて活

性層を水素化することができた。このパッシベーション膜の作製条件は特に限定されるも

のではないが、緻密な膜とすることが望ましい。

【0104】

また、パッシベーション膜を形成した後に、さらに水素化工程を行っても良い。例えば

、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行

うと良く、あるいはプラズマ水素化法を用いても同様の効果が得られた。なお、ここで後

に画素電極とドレイン配線を接続するためのコンタクトホールを形成する位置において、

パッシベーション膜151に開口部を形成しておいても良い。

【0105】

その後、有機樹脂からなる第2の層間絶縁膜676を約1μmの厚さに形成した。有機

樹脂としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB(ベンゾ

シクロブテン)等を使用することができる。有機樹脂膜を用いることの利点は、成膜方法

が簡単である点や、比誘電率が低いので、寄生容量を低減できる点、平坦性に優れる点な

どが上げられる。なお上述した以外の有機樹脂膜や有機系SiO化合物などを用いることも

できる。ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300℃で焼

成して形成した。

【0106】

次に、画素部となる領域において、第2の層間絶縁膜676上に遮光膜677を形成し

た。遮光膜153はアルミニウム(Al)、チタン(Ti)、タンタル(Ta)から選ば

れた元素またはいずれかを主成分とする膜で100〜300nmの厚さに形成した。なお

、第2の層間絶縁膜676上に酸化シリコン膜等の絶縁膜を5〜50nm形成しておくと

、この上に形成する遮光膜の密着性を高めることができた。また、有機樹脂で形成した第

2の層間絶縁膜676の表面にCF4ガスを用いたプラズマ処理を施すと、表面改質によ

り膜上に形成する遮光膜の密着性を向上させることができた。

【0107】

また、遮光膜だけでなく、他の接続配線を形成することも可能である。例えば、駆動回

路内で回路間をつなぐ接続配線を形成できる。但し、その場合は遮光膜または接続配線を

形成する材料を成膜する前に、予め第2の層間絶縁膜にコンタクトホールを形成しておく

必要がある。

【0108】

次に、遮光膜677の表面に陽極酸化法またはプラズマ酸化法(本実施例では陽極酸化

法)により30〜150nm(好ましくは50〜75nm)の厚さの陽極酸化物678を

形成した。本実施例では遮光膜677としてアルミニウム膜またはアルミニウムを主成分

とする膜を用いたため、陽極酸化物678として酸化アルミニウム膜(アルミナ膜)が形

成された。

【0109】

陽極酸化処理に際して、まず十分にアルカリイオン濃度の小さい酒石酸エチレングリコ

ール溶液を作製した。これは15%の酒石酸アンモニウム水溶液とエチレングリコールと

を2:8で混合した溶液であり、これにアンモニア水を加え、pHが7±0.5となるよ

うに調節した。そして、この溶液中に陰極となる白金電極を設け、遮光膜677が形成さ

れている基板を溶液に浸し、遮光膜677を陽極として、一定(数mA〜数十mA)の直

流電流を流した。溶液中の陰極と陽極との間の電圧は酸化物の成長に従い時間と共に変化

するが、電流が一定となるように電圧を調整し、150Vとなったところで電圧を一定と

して、15分間保持した。このようにして遮光膜677の表面には厚さ50〜75nmの

陽極酸化物678を形成することができた。なお、ここで示した陽極酸化法に係わる数値

は一例にすぎず、作製する素子の大きさ等によって当然最適値は変化しうるものである。

【0110】

また、ここでは遮光膜表面のみに絶縁膜を設ける構成としたが、絶縁膜をプラズマCV

D法、熱CVD法またはスパッタ法などの気相法によって形成しても良い。その場合も膜

厚は30〜150nm(好ましくは50〜75nm)とすることが好ましい。また、酸化

シリコン膜、窒化シリコン膜、窒化酸化シリコン膜、DLC(Diamond like carbon)

膜または有機樹脂膜を用いても良い。さらに、これらを組み合わせた積層膜を用いても良

い。

【0111】

次に、第2の層間絶縁膜676、パッシベーション膜675にドレイン配線672に達

するコンタクトホールを形成し、画素電極679を形成した。なお、画素電極680、6

81はそれぞれ隣接する別の画素の画素電極である。画素電極679〜681は、透過型

液晶表示装置とする場合には透明導電膜を用い、反射型の液晶表示装置とする場合には金

属膜を用いれば良い。ここでは透過型の液晶表示装置とするために、酸化インジウムと酸

化スズとの化合物(ITO)膜を100nmの厚さにスパッタ法で形成した。

【0112】

また、この時、画素電極679と遮光膜677とが陽極酸化物678を介して重なった

領域682が保持容量を形成した。

【0113】

こうして同一基板上に、駆動回路となるCMOS回路と画素部とを有したアクティブマ

トリクス基板が完成した。なお、駆動回路にはpチャネル型TFT801、nチャネル型

TFT802、803が形成され、画素部にはnチャネル型TFTでなる画素TFT80

4が形成された。(図8(C))

【0114】

CMOS回路のpチャネル型TFT801には、チャネル形成領域701、並びにp++

領域で形成されたソース領域702及びドレイン領域703が形成された。

【0115】

また、nチャネル型TFT802には、チャネル形成領域704、ソース領域705、

ドレイン領域706、そしてチャネル形成領域の片側にLov領域707が形成された。こ

の時、ソース領域705、ドレイン領域706はそれぞれ(n-+n+)領域で形成され、

Lov領域707はn-領域で形成された。また、Lov領域707はゲート配線と全部重な

って形成された。

【0116】

また、nチャネル型TFT803には、チャネル形成領域708、ソース領域709、

ドレイン領域710、そしてチャネル形成領域の両側にLov領域711a、712aおよび

Loff領域711b、712bが形成された。この時、ソース領域709、ドレイン領域7

10はそれぞれ(n-+n+)領域、Lov領域711a、712aはn-領域、Loff領域71

1b、712bは(n--+n-)領域で形成された。なお、この構造ではLDD領域の一部

がゲート配線と重なるように配置されたために、Lov領域とLoff領域が実現されている

。

【0117】

また、画素TFT804には、チャネル形成領域713、714、ソース領域715、

ドレイン領域716、Loff領域717〜720、Loff領域718、719に接したn+

領域721が形成された。この時、ソース領域715、ドレイン領域716はそれぞれn

+領域で形成され、Loff領域717〜720はn--領域で形成された。

【0118】

本実施例では、画素部および駆動回路が要求する回路仕様に応じて各回路を形成するT

FTの構造を最適化し、半導体装置の動作性能および信頼性を向上させることができた。

具体的には、nチャネル型TFTは回路仕様に応じてLDD領域の配置を異ならせ、Lov

領域またはLoff領域を使い分けることによって、同一基板上に高速動作またはホットキ

ャリア対策を重視したTFT構造と低オフ電流動作を重視したTFT構造とを実現した。

【0119】

例えば、アクティブマトリクス型液晶表示装置の場合、nチャネル型TFT802は高

速動作を重視するシフトレジスタ回路、分周波回路、信号分割回路、レベルシフタ回路、

バッファ回路などのロジック回路に適している。即ち、チャネル形成領域の片側(ドレイ

ン領域側)のみにLov領域を配置することで、できるだけ抵抗成分を低減させつつホット

キャリア対策を重視した構造となっている。

これは上記回路群の場合、ソース領域とドレイン領域の機能が変わらず、キャリア(電子

)の移動する方向が一定だからである。但し、必要に応じてチャネル形成領域の両側にL

ov領域を配置することもできる。

【0120】

また、nチャネル型TFT803はホットキャリア対策と低オフ電流動作の双方を重視

するサンプリング回路(サンプルホールド回路)に適している。即ち、Lov領域を配置す

ることでホットキャリア対策とし、さらにLoff領域を配置することで低オフ電流動作を

実現した。また、サンプリング回路はソース領域とドレイン領域の機能が反転してキャリ

アの移動方向が180°変わるため、ゲート配線を中心に線対称となるような構造としな

ければならない。なお、場合によってはLov領域のみとすることもありうる。

【0121】

また、nチャネル型TFT804は低オフ電流動作を重視した画素部、サンプリング回

路(サンプルホールド回路)に適している。即ち、オフ電流値を増加させる要因となりう

るLov領域を配置せず、Loff領域のみを配置することで低オフ電流動作を実現している

。また、駆動回路のLDD領域よりも低い濃度のLDD領域をLoff領域として用いるこ

とで、多少オン電流値が低下しても徹底的にオフ電流値を低減する対策を打っている。さ

らに、n+領域721はオフ電流値を低減する上で非常に有効であることが確認されてい

る。

【0122】

また、チャネル長3〜7μmに対してnチャネル型TFT802のLov領域707の長

さ(幅)は0.5〜3.0μm、代表的には1.0〜1.5μmとすれば良い。また、n

チャネル型TFT803のLov領域711a、712aの長さ(幅)は0.5〜3.0μm

、代表的には1.0〜1.5μm、Loff領域711b、712bの長さ(幅)は1.0〜

3.5μm、代表的には1.5〜2.0μmとすれば良い。また、画素TFT804に設

けられるLoff領域717〜720の長さ(幅)は0.5〜3.5μm、代表的には2.

0〜2.5μmとすれば良い。

【0123】

さらに、pチャネル型TFT801は自己整合(セルフアライン)的に形成され、nチ

ャネル型TFT802〜804は非自己整合(ノンセルフアライン)的に形成されている

点も本発明の特徴の一つである。

【0124】

なお、本実施例は実施例1で説明したアクティブマトリクス基板の構成にnチャネル型

TFT803の構成を加えただけであるので、作製工程中の薄膜材料、不純物添加工程の

数値範囲、薄膜の膜厚範囲等の条件は実施例1で説明した条件をそのまま用いることが可

能である。また、本実施例の構成を実施例2又は実施例3の構成と組み合わせることは可

能である。

【実施例5】

【0125】

本実例では、アクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を

作製する工程を説明する。図9に示すように、図8(C)の状態の基板に対し、配向膜9

01を形成する。通常液晶表示素子の配向膜にはポリイミド樹脂が多く用いられている。

対向側の基板902には、透明導電膜903と、配向膜904とを形成した。配向膜を形

成した後、ラビング処理を施して液晶分子がある一定のプレチルト角を持って配向するよ

うにした。そして、画素部と、CMOS回路が形成されたアクティブマトリクス基板と対

向基板とを、公知のセル組み工程によってシール材やスペーサ(共に図示せず)などを介

して貼りあわせる。その後、両基板の間に液晶材料905を注入し、封止剤(図示せず)

によって完全に封止した。液晶材料には公知の液晶材料を用いれば良い。このようにして

図9に示すアクティブマトリクス型液晶表示装置が完成した。

【0126】

次にこのアクティブマトリクス型液晶表示装置の構成を、図10の斜視図および図11

の上面図を用いて説明する。尚、図10と図11は、図6〜図8の断面構造図と対応付け

るため、共通の符号を用いている。また、図11(B)で示すA―A’に沿った断面構造

は、図8(C)に示す画素部の断面図に対応している。

【0127】

アクティブマトリクス基板は、ガラス基板601上に形成された、画素部1001と、

走査(ゲート)線駆動回路1002と、信号(ソース)線駆動回路1003で構成される。

画素部の画素TFT804はnチャネル型TFTであり、周辺に設けられる駆動回路はC

MOS回路を基本として構成されている。走査(ゲート)線駆動回路1002と、信号(

ソース)線駆動回路1003はそれぞれゲート配線641とソース配線668で画素部1

001に接続されている。また、FPC1004が接続された外部入出力端子1005か

ら駆動回路の入出力端子までの接続配線625、673が設けられている。

【0128】

図11は画素部1001の一部分(一画素)を示す上面図である。ここで図11(A)

は活性層、ゲート配線、ソース配線の重ねあわせを示す上面図であり、同図(B)はその

上に遮光膜、画素電極を重ねあわせた状態を示す上面図である。図11(A)において、

ゲート配線641は、図示されていないゲート絶縁膜を介してその下の活性層606と交

差している。また、図示はしていないが、活性層606には、ソース領域、ドレイン領域

、n--領域でなるLoff領域が形成されている。また、1101はソース配線668と活

性層606とのコンタクト部、1102はドレイン配線672と活性層606とのコンタ

クト部である。

【0129】

また、図11(B)において、画素TFTの上には表面に陽極酸化物(ここでは図示し

ないが、図8(C)の陽極酸化物678を指す)が形成された遮光膜677と、各画素ご

とに設けられる画素電極679〜681が形成されている。そして、遮光膜677と画素

電極679とが陽極酸化物を介して重なる領域で保持容量682が形成される。なお、1

103はドレイン配線672と画素電極679とのコンタクト部である。

【0130】

本実施例では保持容量の誘電体として比誘電率が7〜9と高いアルミナ膜を用いたこと

で、必要な容量を形成するための面積を少なくすることが可能である。

さらに、本実施例のように画素TFT上に形成される遮光膜を保持容量の一方の電極とす

ることで、アクティブマトリクス型液晶表示装置の画像表示部の開口率を向上させること

ができた。

【0131】

なお、本実施例のアクティブマトリクス型液晶表示装置は、実施例4で説明した構造と

照らし合わせて説明したが、実施例1〜3のいずれの構成とも自由に組み合わせてアクテ

ィブマトリクス型液晶表示装置を作製することができる。

【実施例6】

【0132】

画素部の各画素に設けられる保持容量は画素電極に接続されていない方の電極(本発明

の場合は遮光膜)を固定電位としておくことで保持容量を形成することができる。その場

合、遮光膜をフローティング状態(電気的に孤立した状態)かコモン電位(データとして

送られる画像信号の中間電位)に設定しておくことが望ましい。

【0133】

そこで本実施例では遮光膜をコモン電位に固定する場合の接続方法について図12を用

いて説明する。図12(A)において、1201は実施例1と同様にして作製された画素

TFTであり、1202が保持容量の一方の電極として機能する遮光膜である。遮光膜1

202は画素部の外側にまで延在し、第2の層間絶縁膜1204、パッシベーション膜1

205に設けられたコンタクトホール1206を介してコモン電位を与える電源線120

3と接続している。

【0134】

このように画素部の外側において、コモン電位を与える電源線と電気的に接続すること

でコモン電位とすることができる。従って、この場合には遮光膜1202を形成する前に

第2の層間絶縁膜1204、パッシベーション膜1205をエッチングする工程が必要と

なる。

【0135】

次に、図12(B)において、1207は実施例1と同様にして作製された画素TFT

であり、1208が保持容量の一方の電極として機能する遮光膜である。遮光膜1208

は画素部の外側にまで延在し、1209で示される領域において導電膜1210と酸化物

1211を介して重なる。この導電膜1210は画素電極1212と同時に形成される導

電膜である。

【0136】

そして、この導電膜1210は第2の層間絶縁膜1213、パッシベーション膜121

4に設けられたコンタクトホール1215を介してコモン電位を与える電源線1216と

接続している。この時、領域1209では遮光膜1208、酸化物1211、導電膜12

10でなるコンデンサが形成される。このコンデンサは交流駆動を行うことによって実質

的に短絡する。即ち、領域1209では静電結合によって、遮光膜1208と導電膜12

10とが電気的に接続されるため、遮光膜1208と電源線1216とは実質的に接続さ

れる。

【0137】

このように図12(B)の構造を採用することで、工程数を増やすことなく遮光膜をコ

モン電位に設定することが可能となる。

【0138】

なお、本実施例の構成は実施例1〜5のいずれの構成とも自由に組み合わせることが可

能である。

【実施例7】

【0139】

図13は、実施例4で示したアクティブマトリクス基板の回路構成の一例を示す。本実

施例のアクティブマトリクス基板は、ソース信号線側駆動回路1301、ゲート信号線側

駆動回路(A)1307、ゲート信号線側駆動回路(B)1311、プリチャージ回路1

312、画素部1306を有している。ソース信号線側駆動回路1301は、シフトレジ

スタ回路1302、レベルシフタ回路1303、バッファ回路1304、サンプリング回

路1305を備えている。また、ゲート信号線側駆動回路(A)1307は、シフトレジ

スタ回路1308、レベルシフタ回路1309、バッファ回路1310を備えている。ゲ

ート信号線側駆動回路(B)1311も同様な構成である。

【0140】

ここでシフトレジスタ回路1302、1308は駆動電圧が5〜16V(代表的には1

0V)であり、回路を形成するCMOS回路に使われるnチャネル型TFTは図8(C)

の802で示される構造が適している。

【0141】

また、レベルシフタ回路1303、1309、バッファ回路1304、1310は、駆

動電圧は14〜16Vと高くなるが、シフトレジスタ回路と同様に、図8(C)のnチャ

ネル型TFT802を含むCMOS回路が適している。なお、ゲート配線をダブルゲート

構造とすることは、回路の信頼性を向上させる上で有効である。

【0142】

また、サンプリング回路1305は駆動電圧が14〜16Vであるが、ソース領域とド

レイン領域が反転する上、オフ電流値を低減する必要があるので、図8(C)のnチャネ

ル型TFT803を含むCMOS回路が適している。なお、実際にサンプリング回路を形

成する時はnチャネル型TFTとpチャネル型TFTとを組み合わせて形成することにな

る。

【0143】

また、画素部1306は駆動電圧が14〜16Vであり、サンプリング回路1305よ

りもさらにオフ電流値が低いことを要求するので、完全なLDD構造(Lov領域を配置し

ない構造)とすることが望ましく、図8(C)のnチャネル型TFT804を画素TFT

として用いることが望ましい。

【0144】

なお、本実施例の構成は、実施例2〜6のいずれの構成とも自由に組み合わせることが

可能である。

【実施例8】

【0145】

本実施例ではTFTの活性層(能動層)となる活性層を形成する工程について図14を

用いて説明する。まず、基板(本実施例ではガラス基板)1401上に200nm厚の窒

化酸化シリコン膜でなる下地膜1402と50nm厚の非晶質半導体膜(本実施例では非

晶質シリコン膜)1403を大気解放しないで連続的に形成する。

【0146】

次に、重量換算で10ppmの触媒元素(本実施例ではニッケル)を含む水溶液(酢酸

ニッケル水溶液)をスピンコート法で塗布して、触媒元素含有層1404を非晶質半導体

膜1403の全面に形成する。ここで使用可能な触媒元素は、ニッケル(Ni)以外にも

、ゲルマニウム(Ge)、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)

、コバルト(Co)、白金(Pt)、銅(Cu)、金(Au)、といった元素がある。(

図14(A))

【0147】

また、本実施例ではスピンコート法でニッケルを添加する方法を用いたが、蒸着法やス

パッタ法などにより触媒元素でなる薄膜(本実施例の場合はニッケル膜)を非晶質半導体

膜上に形成する手段をとっても良い。

【0148】

次に、結晶化の工程に先立って400〜500℃で1時間程度の熱処理工程を行い、水

素を膜中から脱離させた後、500〜650℃(好ましくは550〜570℃)で4〜1

2時間(好ましくは4〜6時間)の熱処理を行う。本実施例では、550℃で4時間の熱

処理を行い、結晶質半導体膜(本実施例では結晶質シリコン膜)1405を形成する。(

図14(B))

【0149】

次に、結晶化の工程で用いたニッケルを結晶質シリコン膜から除去するゲッタリング工

程を行う。まず、結晶質半導体膜1405の表面にマスク絶縁膜1406を150nmの

厚さに形成し、パターニングにより開口部1407を形成する。そして、露出した結晶質

半導体膜に対して周期表の15族に属する元素(本実施例ではリン)を添加する工程を行

う。この工程により1×1019〜1×1020atoms/cm3の濃度でリンを含むゲッタリング

領域1408が形成される。(図14(C))

【0150】

次に、窒素雰囲気中で450〜650℃(好ましくは500〜550℃)、4〜24時

間(好ましくは6〜12時間)の熱処理工程を行う。この熱処理工程により結晶質半導体

膜中のニッケルは矢印の方向に移動し、リンのゲッタリング作用によってゲッタリング領

域1408に捕獲される。即ち、結晶質半導体膜中からニッケルが除去されるため、結晶

質半導体膜1409に含まれるニッケル濃度は、1×1017atms/cm3以下、好ましくは1

×1016atms/cm3以下にまで低減することができる。(図14(D))

【0151】

そして、マスク絶縁膜1406を除去した後、ゲッタリング領域1408を完全に取り

除くようにしてパターニングを行い、活性層1410を得る。なお、図14(E)では活

性層1410を一つしか図示していないが、基板上に複数の活性層を同時に形成すること

は言うまでもない。

【0152】

以上のようにして形成された活性層1410は、結晶化を助長する触媒元素(ここでは

ニッケル)を用いることによって、非常に結晶性の良い結晶質半導体膜で形成されている

。また、結晶化のあとは触媒元素をリンのゲッタリング作用により除去しており、活性層

1410中に残存する触媒元素の濃度は、1×1017atms/cm3以下、好ましくは1×10

16atms/cm3以下である。

【0153】

なお、本実施例の構成は、実施例1〜7のいずれの構成とも自由に組み合わせることが

可能である。

【実施例9】

【0154】

本実施例ではTFTの活性層(能動層)となる活性層を形成する工程について図15を

用いて説明する。具体的には特開平10−247735号公報(米国出願番号09/03

4,041号に対応)に記載された技術を用いる。

【0155】

まず、基板(本実施例ではガラス基板)1501上に200nm厚の窒化酸化シリコン

膜でなる下地膜1502と50nm厚の非晶質半導体膜(本実施例では非晶質シリコン膜

)1503を大気解放しないで連続的に形成する。次に、酸化シリコン膜でなるマスク絶

縁膜1504を200nmの厚さに形成し、開口部1505を形成する。

【0156】

次に、重量換算で100ppmの触媒元素(本実施例ではニッケル)を含む水溶液(酢

酸ニッケル水溶液)をスピンコート法で塗布して、触媒元素含有層1506を形成する。

この時、触媒元素含有層1506は、開口部1505が形成された領域において、選択的

に非晶質半導体膜1503に接触する。ここで使用可能な触媒元素は、ニッケル(Ni)

以外にも、ゲルマニウム(Ge)、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛

(Pb)、コバルト(Co)、白金(Pt)、銅(Cu)、金(Au)、といった元素が

ある。(図15(A))

【0157】

また、本実施例ではスピンコート法でニッケルを添加する方法を用いたが、蒸着法やス

パッタ法などにより触媒元素でなる薄膜(本実施例の場合はニッケル膜)を非晶質半導体

膜上に形成する手段をとっても良い。

【0158】

次に、結晶化の工程に先立って400〜500℃で1時間程度の熱処理工程を行い、水

素を膜中から脱離させた後、500〜650℃(好ましくは550〜600℃)で6〜1

6時間(好ましくは8〜14時間)の熱処理を行う。本実施例では、570℃で14時間

の熱処理を行う。その結果、開口部1505を起点として概略基板と平行な方向(矢印で

示した方向)に結晶化が進行し、巨視的な結晶成長方向が揃った結晶質半導体膜(本実施

例では結晶質シリコン膜)1507が形成される。(図15(B))

【0159】

次に、結晶化の工程で用いたニッケルを結晶質シリコン膜から除去するゲッタリング工

程を行う。本実施例では、先ほど形成したマスク絶縁膜1504をそのままマスクとして

周期表の15族に属する元素(本実施例ではリン)を添加する工程を行い、開口部150

5で露出した結晶質半導体膜に1×1019〜1×1020atoms/cm3の濃度でリンを含むゲ

ッタリング領域1508を形成する。(図15(C))

【0160】

次に、窒素雰囲気中で450〜650℃(好ましくは500〜550℃)、4〜24時

間(好ましくは6〜12時間)の熱処理工程を行う。この熱処理工程により結晶質半導体

膜中のニッケルは矢印の方向に移動し、リンのゲッタリング作用によってゲッタリング領

域1508に捕獲される。即ち、結晶質半導体膜中からニッケルが除去されるため、結晶

質半導体膜1509に含まれるニッケル濃度は、1×1017atms/cm3以下、好ましくは1

×1016atms/cm3以下にまで低減することができる。(図15(D))

【0161】

そして、マスク絶縁膜1504を除去した後、ゲッタリング領域1508を完全に取り

除くようにしてパターニングを行い、活性層1510を得る。なお、図15(E)では活

性層1510を一つしか図示していないが、基板上に複数の活性層を同時に形成すること

は言うまでもない。

【0162】

以上のようにして形成された活性層1510は、結晶化を助長する触媒元素(ここでは

ニッケル)を選択的に添加して結晶化することによって、非常に結晶性の良い結晶質半導

体膜で形成されている。具体的には、棒状または柱状の結晶が、特定の方向性を持って並

んだ結晶構造を有している。また、結晶化のあとは触媒元素をリンのゲッタリング作用に

より除去しており、活性層1510中に残存する触媒元素の濃度は、1×1017atms/cm3

以下、好ましくは1×1016atms/cm3以下である。

【0163】

なお、本実施例の構成は、実施例1〜7のいずれの構成とも自由に組み合わせることが

可能である。

【実施例10】

【0164】

実施例8、9では半導体膜を結晶化するために用いた触媒元素をゲッタリングするため

にリンを用いたが、本実施例では他の元素を用いて上記触媒元素をゲッタリングする場合

について説明する。

【0165】

まず、実施例8または実施例9工程に従って、結晶質半導体膜を得る。但し、本実施例

で用いることのできる基板は、700℃以上に耐えうる耐熱性基板、代表的には石英基板

、金属基板、シリコン基板である。また、本実施例では結晶化に用いる触媒元素(ニッケ

ルを例にとる)の濃度を極力低いものとする。具体的には、非晶質半導体膜上に重量換算

で0.5〜3ppmのニッケル含有層を形成し、結晶化のための熱処理を行う。これにより

形成された結晶質半導体膜中に含まれるニッケル濃度は、1×1017〜1×1019atoms/

cm3(代表的には5×1017〜1×1018atoms/cm3)となる。

【0166】

そして、結晶質半導体膜を形成したら、ハロゲン元素を含む酸化性雰囲気中で熱処理を

行う。温度は800〜1150℃(好ましくは900〜1000℃)とし、処理時間は1

0分〜4時間(好ましくは30分〜1時間)とする。

【0167】

本実施例では、酸素雰囲気中に対して3〜10体積%の塩化水素を含ませた雰囲気中に

おいて、950℃30分の熱処理を行う。この工程により結晶質半導体膜中のニッケルは

揮発性の塩化化合物(塩化ニッケル)となって処理雰囲気中に離脱する。即ち、ハロゲン

元素のゲッタリング作用によってニッケルを除去することが可能となる。但し、結晶質半

導体膜中に存在するニッケル濃度が高すぎると、ニッケルの偏析部で酸化が異常に進行す

るという問題を生じる。そのため、結晶化の段階で用いるニッケルの濃度を極力低くする

必要がある。

【0168】

こうして形成された結晶質半導体膜中にに残存するニッケルの濃度は、1×1017atms

/cm3以下、好ましくは1×1016atms/cm3以下となる。この後は、結晶質半導体膜をパタ

ーニングして、活性層を形成することで、TFTの活性層として用いることが可能である

。

【0169】

なお、本実施例の構成は実施例1〜9のいずれの構成とも自由に組み合わせることが可

能である。即ち、実施例8、9に示したリンによるゲッタリング工程と併用することも可

能である。

【実施例11】

【0170】

本実施例では本発明に用いる結晶質半導体膜(結晶質シリコン膜を例にとる)

の結晶性を改善するための工程について説明する。まず、実施例8〜10のいずれかの工

程に従って活性層を形成する。但し、本実施例ではTFTを形成する基板として800〜

1150℃の温度に耐えうる基板を用いる材料を用いる必要がある。そのような基板とし

ては、石英基板、金属基板、シリコン基板、セラミックス基板(セラミックスガラス基板

も含む)が挙げられる。

【0171】

そして、その上に窒化酸化シリコン膜、酸化シリコン膜、または窒化シリコン膜と酸化

シリコン膜とを積層した積層膜でなるゲート絶縁膜を形成する。ゲート絶縁膜の膜厚は2

0〜120nm(代表的には60〜80nm)とする。本実施例ではSiH4ガスとN2Oガス

との混合ガスを用いて800℃の成膜温度で酸化シリコン膜を形成する。

【0172】

ゲート絶縁膜を形成したら、酸化性雰囲気中で熱処理を行う。温度は800〜1150

℃(好ましくは900〜1000℃)とし、処理時間は10分〜4時間(好ましくは30

分〜1時間)とする。なお、この場合、ドライ酸化法が最も好ましいが、ウェット酸化法

であっても良い。また、酸化性雰囲気は100%酸素雰囲気でも良いし、実施例10のよ

うにハロゲン元素を含ませても良い。

【0173】

この熱処理により活性層とゲート絶縁膜との界面付近で活性層が酸化され、熱酸化膜が

形成される。その結果、上記界面の準位が低減され、非常に良好な界面特性を示すように

なる。さらに、活性層は酸化されることで膜厚が減り、その酸化の際に発生する余剰シリ

コンによって膜中の欠陥が大幅に低減され、非常に欠陥密度の小さい良好な結晶性を有す

る半導体膜となる。

【0174】

本実施例を実施する場合、最終的な活性層の膜厚が20〜60nm、ゲート絶縁膜の膜

厚が50〜150nm(代表的には80〜120nm)となるように調節する。また、欠

陥密度の低減効果を十分に引き出すためには、活性層が少なくとも50nmは酸化される

ようにすることが好ましい。

【0175】

次に、実施例1と同様にn型不純物元素を添加し、後にLov領域となるn-領域を形成

する。さらに、n型不純物元素を活性化するために不活性雰囲気中で700〜950℃(

好ましくは750〜800℃)の熱処理を行う。本実施例では窒素雰囲気中にて800℃

1時間の熱処理を行う。この後は、実施例1の図1(C)以降もしくは実施例4の図6(

C)以降の工程に従えば良い。

【0176】

本実施例のような工程を経た活性層の結晶構造は結晶格子に連続性を持つ特異な結晶構

造となる。その特徴について以下に説明する。

【0177】

上記作製工程に従って形成した活性層は、微視的に見れば複数の針状又は棒状の結晶(

以下、棒状結晶と略記する)が集まって並んだ結晶構造を有する。このことはTEM(透

過型電子顕微鏡法)による観察で容易に確認できた。

【0178】

また、電子線回折及びエックス線(X線)回折を利用すると活性層の表面(チャネルを

形成する部分)が、結晶軸に多少のずれが含まれているものの主たる配向面として{11

0}面を有することを確認できた。本出願人がスポット径約1.5μmの電子線回折写真を詳

細に観察した結果、{110}面に対応する回折斑点がきれいに現れているが、各斑点は

同心円上に分布を持っていることが確認された。

【0179】

また、本出願人は個々の棒状結晶が接して形成する結晶粒界をHR−TEM(高分解能

透過型電子顕微鏡法)により観察し、結晶粒界において結晶格子に連続性があることを確

認した。これは観察される格子縞が結晶粒界において連続的に繋がっていることから容易

に確認できた。

【0180】

なお、結晶粒界における結晶格子の連続性は、その結晶粒界が「平面状粒界」と呼ばれ

る粒界であることに起因する。本明細書における平面状粒界の定義は、「Characterizati

on of High-Efficiency Cast-Si Solar Cell Wafers by MBIC Measurement ;Ryuichi Sh

imokawa and Yutaka Hayashi,Japanese Journal of Applied Physics vol.27,No.5,pp

.751-758,1988」に記載された「Planar boundary 」である。

【0181】

上記論文によれば、平面状粒界には双晶粒界、特殊な積層欠陥、特殊なtwist 粒界など

が含まれる。この平面状粒界は電気的に不活性であるという特徴を持つ。即ち、結晶粒界

でありながらキャリアの移動を阻害するトラップとして機能しないため、実質的に存在し

ないと見なすことができる。

【0182】

特に結晶軸(結晶面に垂直な軸)が〈110〉軸である場合、{211}双晶粒界はΣ

3の対応粒界とも呼ばれる。Σ値は対応粒界の整合性の程度を示す指針となるパラメータ

であり、Σ値が小さいほど整合性の良い粒界であることが知られている。

【0183】

本出願人が本実施例を実施して得た結晶質珪素膜を詳細にTEMを用いて観察した結果

、結晶粒界の殆ど(90%以上、典型的には95%以上)がΣ3の対応粒界、即ち{21

1}双晶粒界であることが判明した。

【0184】

二つの結晶粒の間に形成された結晶粒界において、両方の結晶の面方位が{110}で

ある場合、{111}面に対応する格子縞がなす角をθとすると、θ=70.5°の時にΣ3

の対応粒界となることが知られている。

【0185】

本実施例の結晶質珪素膜は、結晶粒界において隣接する結晶粒の各格子縞がまさに約70

.5°の角度で連続しており、その事からこの結晶粒界は{211}双晶粒界であるという

結論に辿り着いた。

【0186】

なお、θ= 38.9 °の時にはΣ9の対応粒界となるが、この様な他の結晶粒界も存在し

た。

【0187】

この様な結晶構造(正確には結晶粒界の構造)は、結晶粒界において異なる二つの結晶

粒が極めて整合性よく接合していることを示している。即ち、結晶粒界において結晶格子

が連続的に連なり、結晶欠陥等に起因するトラップ準位を非常に作りにくい構成となって

いる。従って、この様な結晶構造を有する半導体薄膜は実質的に結晶粒界が存在しない見

なすことができる。

【0188】

またさらに、700〜1150℃という高い温度での熱処理工程(本実施例における熱

酸化工程またはゲッタリング工程にあたる)によって結晶粒内に存在する欠陥が殆ど消滅

していることがTEM観察によって確認されている。これはこの熱処理工程の前後で欠陥

数が大幅に低減されていることからも明らかである。

【0189】

この欠陥数の差は電子スピン共鳴分析(Electron Spin Resonance :ESR)

によってスピン密度の差となって現れる。現状では本実施例の作製工程に従って作製され

た結晶質珪素膜のスピン密度は少なくとも 5×1017spins/cm3以下(好ましくは 3×1017s

pins/cm3以下)であることが判明している。ただし、この測定値は現存する測定装置の検

出限界に近いので、実際のスピン密度はさらに低いと予想される。

【0190】

以上の事から、本実施例を実施することで得られた結晶質シリコン膜は結晶粒内及び結

晶粒界が実質的に存在しないため、単結晶シリコン膜又は実質的な単結晶シリコン膜と考

えて良い。

【0191】

(TFTの電気特性に関する知見)

本実施例の活性層を用いたTFTは、MOSFETに匹敵する電気特性を示した。本出

願人が試作したTFT(但し、活性層の膜厚は30nm、ゲート絶縁膜の膜厚は100nm)

からは次に示す様なデータが得られている。

【0192】

(1)スイッチング性能(オン/オフ動作切り換えの俊敏性)の指標となるサブスレッ

ショルド係数が、Nチャネル型TFTおよびPチャネル型TFTともに60〜100mV/decade

(代表的には60〜85mV/decade )と小さい。

(2)TFTの動作速度の指標となる電界効果移動度(μFE)が、Nチャネル型TFT

で 200〜650cm2/Vs (代表的には 300〜500cm2/Vs )、Pチャネル型TFTで100〜300cm

2/Vs(代表的には 150〜200cm2/Vs)と大きい。

(3)TFTの駆動電圧の指標となるしきい値電圧(Vth)が、Nチャネル型TFTで

-0.5〜1.5 V、Pチャネル型TFTで-1.5〜0.5 Vと小さい。

【0193】

以上の様に、極めて優れたスイッチング特性および高速動作特性が実現可能であること

が確認されている。なお、本実施例の構成は、実施例1〜10のいずれの構成とも自由に

組み合わせることが可能である。但し、非晶質半導体膜の結晶化に、実施例8〜10で示

したような結晶化を助長する触媒元素を用いていることが重要である。

【実施例12】

【0194】

本実施例では、実施例8、9に示したいずれかの手段により結晶化した結晶質半導体膜

(結晶質シリコン膜を例にとる)から、結晶化に用いた触媒元素(本実施例ではニッケル

を例にとる)をゲッタリングする手段について説明する。なお、説明には図16を用いる

。

【0195】

まず、実施例1と同様の工程に従って、図2(B)の状態を得る。次に、図2(C)の

工程と同様にリンを添加する。その際、本実施例では図2(C)のレジストマスク132

の代わりに図16(A)に示すようなレジストマスク1601を用いる。即ち、図2(C

)ではpチャネル型TFTとなる領域を全て隠すようにレジストマスクを設けていたが、

図16(A)ではp++領域の端部を隠さないようにレジストマスクを形成する。

【0196】

この状態で図2(C)の工程と同様の条件でリンを添加する。その結果、pチャネル型

TFTのp++領域124、125の端部にもリンが添加され、(p+++n+)領域160

2、1603が形成される。このとき、p++領域に含まれるp型を付与する不純物元素の

濃度が、n+領域に含まれるリンよりも十分高濃度に添加されていれば、その部分はp++

領域のまま維持できる。

【0197】

次に、レジストマスク1601,133、134を除去した後、実施例1の図3(A)

と同様の濃度でリンの添加工程を行う。この工程によりn--領域140〜143が形成さ

れる。(図16(B))

【0198】

次に、実施例1の図3(B)と同様に、添加された不純物元素(リンまたはボロン)の

活性化工程を行う。本実施例ではこの活性化工程をファーネスアニールまたはランプアニ

ールによって行うことが好ましい。ファーネスアニールを用いる場合、450〜650℃

、好ましくは500〜550℃、ここでは500℃、4時間の熱処理を行うことにする。

(図16(C))

【0199】

本実施例の場合、nチャネル型TFTおよびpチャネル型TFTの双方のソース領域ま

たはドレイン領域に、必ずn+領域に相当する濃度のリンが含まれた領域を有する。その

ため、熱活性化のための熱処理工程において、リンによるニッケルのゲッタリング効果を

得ることができる。即ち、チャネル形成領域から矢印で示す方向へニッケルが移動し、ソ

ース領域またはドレイン領域に含まれるリンの作用によってゲッタリングされる。

【0200】

このように本実施例を実施すると、活性層に添加された不純物元素の活性化工程と、結

晶化に用いた触媒元素のゲッタリング工程とを兼ねることができ、工程の簡略化に有効で

ある。

【0201】

また、ゲッタリングのためのn+領域を形成するのはpチャネル型TFTのソース領域

及びドレイン領域の一部である。従って、pチャネル型TFTのソース領域及びドレイン

領域全体に高濃度にP型を付与する不純物元素を添加する必要がない。即ち、P型を付与

する不純物元素を添加する工程を短縮化でき、スループットを向上させることができる。

さらに、ソース領域及びドレイン領域の抵抗を下げることができる。

【0202】

なお、本実施例の構成は、実施例1〜11のいずれの構成とも自由に組み合わせること

が可能である。但し、非晶質半導体膜の結晶化に際して、結晶化を助長する触媒元素を用

いている場合に有効な技術である。

【実施例13】

【0203】

本実施例では、画素部の構成を実施例5(図11参照)とは異なるものとした場合につ

いて図17を用いて説明する。なお、基本的な構造は実施例4、5で説明した構造と同じ

であるので同一の部分に関しては同じ符号を用いることとする。

【0204】

図17(A)は本実施例の画素部の断面図であり、ゲート配線(但し活性層と重なる部

分を除く)1700を、第1の導電膜1701、第2の導電膜1702および第3の導電

膜1703を積層して形成する点に特徴がある。このゲート配線1700は実施例4で説

明した接続配線625の形成と同時に形成される。従って、第1の導電膜は窒化タンタル

、第2の導電膜はアルミニウムを主成分とする膜、第3の導電膜はタンタル膜である。

【0205】

そして、この時の上面図は図17(B)に示すようなものとなる。即ち、ゲート配線の

うち活性層と重なる部分(この部分はゲート電極と呼んでもよい)1704a、1704b

は第1および第3の導電膜の積層構造でなる。一方、ゲート配線1700はゲート配線1

704a、1704bよりも配線幅が太く、且つ、図17(A)に示すような三層構造で形

成される。即ち、ゲート配線の中でも単に配線として用いる部分はできるだけ配線抵抗を

小さくするために、本実施例のような構造とすることが好ましい。

【0206】

なお、本実施例の構成は実施例1〜12のいずれの構成とも自由に組み合わせることが

可能である。

【実施例14】

【0207】

本実施例では、実施例4とは異なる工程順序でTFTを作製する場合について図18を

用いて説明する。なお、途中の工程までは実施例4と同様であるので、同じ工程について

は同一の符号を用いることとする。また、添加する不純物元素も実施例4と同様の不純物

元素を例にとる。

【0208】

まず、実施例4の工程に従って図7(B)の状態を得る。本実施例ではその状態を図1

8(A)に示す。次に、レジストマスク633〜638を除去して、n--領域を形成する

ためのリンの添加工程を行う。条件は実施例4の図8(A)の工程と同様で良い。図18

(B)において、1801〜1803で示される領域は、n-領域にn--領域に相当する

リンが添加された領域であり、1804〜1806は画素TFTのLoff領域となるn--

領域である。(図18(B))

【0209】

次に、レジストマスク1807〜1811を形成し、図7(C)と同様の条件でリンを

添加する。この工程により高濃度にリンが添加された領域1812〜1818が形成され

る。(図18(C))

【0210】

この後は、実施例4の工程に従って図8(B)以降の工程を行えば、図8(C)で説明

した構造の画素部を得ることができる。本実施例を用いた場合、CMOS回路を形成する

pチャネル型TFTのソース領域およびドレイン領域にn+領域に相当する濃度のリンが

添加されない構成となる。そのため、p++添加工程に必要なボロン濃度が低くて済み、ス

ループットが向上する。また、図18(C)

の工程でnチャネル型TFTのp++領域の端部にもリンが添加されるようにすれば、実施

例12のゲッタリング工程を行うことが可能である。

【0211】

また、ソース領域またはドレイン領域を形成するn+領域またはp++領域を形成する際

、不純物元素を添加する前に、ゲート絶縁膜をエッチングして活性層の一部を露出させ、

露出させた部分に不純物元素を添加しても良い。その場合、加速電圧が低くて済むため、

活性層に与えるダメージも少ないし、スループットも向上する。

【0212】

なお、本実施例を実施した場合、工程順序の変化により、最終的に活性層に形成された

不純物領域に含まれる不純物元素の濃度が実施例4とは異なる場合もありうる。しかしな

がら、各不純物領域の実質的な機能は変わらないので、本実施例を実施した場合の最終的

な構造の説明は、図8(C)の構造の説明をそのまま参照することができる。また、本実

施例の構成を、実施例1または実施例4に適用することは可能であり、他の実施例2、3

、5〜13の構成と自由に組み合わせることも可能である。

【実施例15】

【0213】

本実施例では、実施例4とは異なる工程順序でTFTを作製する場合について図19を

用いて説明する。なお、途中の工程までは実施例4と同様であるので、同じ工程について

は同一の符号を用いることとする。また、添加する不純物元素も実施例4と同様の不純物

元素を例にとる。

【0214】

まず、実施例4の工程に従って図6(D)の状態を得る。そして、次にnチャネル型T

FTのゲート配線およびその他の接続配線を形成する。図19(A)において、1901

、1902は接続配線、1903〜1905はnチャネル型TFTのゲート配線、190

6は後にpチャネル型TFTのゲート配線を形成するための導電膜である。

【0215】

次に、レジストマスク1907〜1911を形成し、実施例4の図7(C)の工程と同

様の条件でリンを添加する。こうして、高濃度にリンを含む不純物領域1912〜191

8が形成される。(図19(A))

【0216】

次に、レジストマスク1907〜1911を除去した後、レジストマスク1919〜1

924を形成し、pチャネル型TFTのゲート配線1925を形成する。そして、図7(

A)と同様の条件でボロンを添加し、p++領域1926、1927を形成する。(図19

(B))

【0217】

次に、レジストマスク1919〜1924を除去した後、図8(A)と同様の条件でリ

ンを添加する。この添加工程により(n-+n--)領域1930、1931およびn--領

域1932〜1935が形成される。(図19(C))

【0218】

この後は、実施例4の工程に従って図8(B)以降の工程を行えば、図8(C)で説明

した構造の画素部を得ることができる。本実施例を用いた場合、CMOS回路を形成する

pチャネル型TFTのソース領域およびドレイン領域にn+領域に相当する濃度のリンが

添加されない構成となる。そのため、p++添加工程に必要なボロン濃度が低くて済み、ス

ループットが向上する。

【0219】

また、ソース領域またはドレイン領域を形成するn+領域またはp++領域を形成する際

、不純物元素を添加する前に、ゲート絶縁膜をエッチングして活性層の一部を露出させ、

露出させた部分に不純物元素を添加しても良い。その場合、加速電圧が低くて済むため、

活性層に与えるダメージも少ないし、スループットも向上する。

【0220】

なお、本実施例を実施した場合、工程順序の変化により、最終的に活性層に形成された

不純物領域に含まれる不純物元素の濃度が実施例4とは異なる場合もありうる。しかしな

がら、各不純物領域の実質的な機能は変わらないので、本実施例を実施した場合の最終的

な構造の説明は、図8(C)の構造の説明をそのまま参照することができる。また、本実

施例の構成を、実施例1または実施例4に適用することは可能であり、他の実施例2、3

、5〜11、13の構成と自由に組み合わせることも可能である。

【実施例16】

【0221】

本実施例では、実施例4とは異なる工程順序でTFTを作製する場合について図20を

用いて説明する。なお、途中の工程までは実施例4と同様であるので、同じ工程について

は同一の符号を用いることとする。また、添加する不純物元素も実施例4と同様の不純物

元素を例にとる。

【0222】

まず、実施例4の工程に従って図6(D)の状態を得て、実施例15の工程に従って図

19(A)に示す状態を得る。本実施例ではこの状態を図20(A)に示す。なお、図2

0(A)に用いた符号は図19(A)と同一の符号である。

【0223】

次に、レジストマスク1907〜1911を除去した後、図8(A)と同様の条件でリ

ンを添加する。この添加工程により(n-+n--)領域2001、2002およびn--領

域2003〜2006が形成される。(図20(B))

【0224】

次に、レジストマスク2007〜2012を形成し、pチャネル型TFTのゲート配線

2013を形成する。そして、図7(A)と同様の条件でボロンを添加し、p++領域20

14、2015を形成する。(図20(C))

【0225】

この後は、実施例4の工程に従って図8(B)以降の工程を行えば、図8(C)で説明

した構造の画素部を得ることができる。本実施例を用いた場合、CMOS回路を形成する

pチャネル型TFTのソース領域およびドレイン領域に全くリンが添加されない構成とな

る。そのため、p++添加工程に必要なボロン濃度が低くて済み、スループットが向上する

。

【0226】

また、ソース領域またはドレイン領域を形成するn+領域またはp++領域を形成する際

、不純物元素を添加する前に、ゲート絶縁膜をエッチングして活性層の一部を露出させ、

露出させた部分に不純物元素を添加しても良い。その場合、加速電圧が低くて済むため、

活性層に与えるダメージも少ないし、スループットも向上する。

【0227】

なお、本実施例を実施した場合、工程順序の変化により、最終的に活性層に形成された

不純物領域に含まれる不純物元素の濃度が実施例4とは異なる場合もありうる。しかしな

がら、各不純物領域の実質的な機能は変わらないので、本実施例を実施した場合の最終的

な構造の説明は、図8(C)の構造の説明をそのまま参照することができる。また、本実

施例の構成を、実施例1または実施例4に適用することは可能であり、他の実施例2、3

、5〜11、13の構成と自由に組み合わせることも可能である。

【実施例17】

【0228】

本実施例では、実施例4とは異なる工程順序でTFTを作製する場合について図21を

用いて説明する。なお、途中の工程までは実施例4と同様であるので、同じ工程について

は同一の符号を用いることとする。また、添加する不純物元素も実施例4と同様の不純物

元素を例にとる。

【0229】

まず、実施例4の工程に従って図6(D)の状態を得る。そして、図7(A)

の工程(pチャネル型TFTのゲート配線とp++領域の形成工程)を行わずに、図7(B

)と同様にnチャネル型TFTのゲート配線およびその他の接続配線を形成する。なお、

図21(A)では図7(B)と同一の符号を用いている。但し、pチャネル型TFTとな

る領域に関しては、レジストマスク2101を形成して、後にpチャネル型TFTのゲー

ト配線となる導電膜2102を残す。

【0230】

次に、レジストマスクを残したまま、図8(A)と同様の条件でリンを添加する。この

添加工程により(n-+n--)領域2103〜2105およびn--領域2106〜210

8が形成される。(図21(B))

【0231】

次に、レジストマスク2109〜2113を形成し、実施例4の図7(C)の工程と同

様の条件でリンを添加する。こうして、高濃度にリンを含む不純物領域2114〜212

0が形成される。(図21(C))

【0232】

次に、レジストマスク2109〜2113を除去した後、新たにレジストマスク212

1〜2126を形成し、pチャネル型TFTのゲート配線2127を形成する。そして、

図7(A)と同様の条件でボロンを添加し、p++領域2128、2129を形成する。(

図21(D))

【0233】

この後は、実施例4の工程に従って図8(B)以降の工程を行えば、図8(C)で説明

した構造の画素部を得ることができる。本実施例を用いた場合、CMOS回路を形成する

pチャネル型TFTのソース領域およびドレイン領域に全くリンが添加されない構成とな

る。そのため、p++添加工程に必要なボロン濃度が低くて済み、スループットが向上する

。

【0234】

また、ソース領域またはドレイン領域を形成するn+領域またはp++領域を形成する際

、不純物元素を添加する前に、ゲート絶縁膜をエッチングして活性層の一部を露出させ、

露出させた部分に不純物元素を添加しても良い。その場合、加速電圧が低くて済むため、

活性層に与えるダメージも少ないし、スループットも向上する。

【0235】

なお、本実施例を実施した場合、工程順序の変化により、最終的に活性層に形成された

不純物領域に含まれる不純物元素の濃度が実施例4とは異なる場合もありうる。しかしな

がら、各不純物領域の実質的な機能は変わらないので、本実施例を実施した場合の最終的

な構造の説明は、図8(C)の構造の説明をそのまま参照することができる。また、本実

施例の構成を、実施例1または実施例4に適用することは可能であり、他の実施例2、3

、5〜11、13の構成と自由に組み合わせることも可能である。

【実施例18】

【0236】

本実施例では、実施例4とは異なる工程順序でTFTを作製する場合について図22を

用いて説明する。なお、途中の工程までは実施例4と同様であるので、同じ工程について

は同一の符号を用いることとする。また、添加する不純物元素も実施例4と同様の不純物

元素を例にとる。

【0237】

まず、実施例4の工程に従って図6(D)の状態を得て、実施例17の工程に従って図

21(B)に示す状態を得る。本実施例ではこの状態を図22(A)に示す。なお、図2

2(A)に用いた符号は図21(B)と同一の符号である。

【0238】

次に、レジストマスクを除去した後、新たにレジストマスク2201〜2206を形成

し、pチャネル型TFTのゲート配線2207を形成する。そして、図7(A)と同様の

条件でボロンを添加し、p++領域2208、2209を形成する。(図22(B))

【0239】

次に、レジストマスク2210〜2214を形成し、図7(C)の工程と同様の条件で

リンを添加する。こうして、高濃度にリンを含む不純物領域2215〜2221が形成さ

れる。(図22(C))

【0240】

この後は、実施例4の工程に従って図8(B)以降の工程を行えば、図8(C)で説明

した構造の画素部を得ることができる。本実施例を用いた場合、CMOS回路を形成する

pチャネル型TFTのソース領域およびドレイン領域に全くリンが添加されない構成とな

る。そのため、p++添加工程に必要なボロン濃度が低くて済み、スループットが向上する

。また、図22(C)の工程でp++領域2208、2209の端部にもリンが添加される

ようにすれば、実施例12のゲッタリング工程を行うことが可能である。

【0241】

また、ソース領域またはドレイン領域を形成するn+領域またはp++領域を形成する際

、不純物元素を添加する前に、ゲート絶縁膜をエッチングして活性層の一部を露出させ、

露出させた部分に不純物元素を添加しても良い。その場合、加速電圧が低くて済むため、

活性層に与えるダメージも少ないし、スループットも向上する。

【0242】

なお、本実施例を実施した場合、工程順序の変化により、最終的に活性層に形成された

不純物領域に含まれる不純物元素の濃度が実施例4とは異なる場合もありうる。しかしな

がら、各不純物領域の実質的な機能は変わらないので、本実施例を実施した場合の最終的

な構造の説明は、図8(C)の構造の説明をそのまま参照することができる。また、本実

施例の構成を、実施例1または実施例4に適用することは可能であり、他の実施例2、3

、5〜13の構成と自由に組み合わせることも可能である。

【実施例19】

【0243】

実施例4、14〜18に示した作製工程例では、nチャネル型TFTのゲート配線を形

成する前に、前もって後にLov領域として機能するn-領域を形成することが前提となっ

ている。そして、p++領域、n--領域はともに自己整合的に形成されることが特徴となっ

ている。

【0244】

しかしながら、本発明の効果を得るためには最終的な構造が図3(C)や図8(C)の

ような構造となっていれば良く、そこに至るプロセスに限定されるものではない。従って

、場合によってはp++領域やn--領域を、レジストマスクを用いて形成することも可能で

ある。その場合、本発明の作製工程例は実施例4、14〜18に限らず、あらゆる組み合

わせが可能である。

【0245】

本発明においてTFTの活性層となる活性層に一導電性を付与する不純物元素委を添加

する際、n-領域の形成、n+領域の形成、n--領域の形成、p++領域の形成という4つの

工程が必要である。従って、この順序を変えた作製工程だけでも24通りがあり、実施例

4、14〜18に示したのはその中の6通りである。

しかし、本発明の効果は残りの18通り全てにおいて得られるため、どの順序で不純物領

域を形成するのであっても良い。

【0246】

また、ソース領域またはドレイン領域を形成するn+領域またはp++領域を形成する際

、不純物元素を添加する前に、ゲート絶縁膜をエッチングして活性層の一部を露出させ、

露出させた部分に不純物元素を添加しても良い。その場合、加速電圧が低くて済むため、

活性層に与えるダメージも少ないし、スループットも向上する。

【0247】

なお、本実施例の構成は、実施例2〜11、13のいずれの構成とも自由に組み合わせ

ることが可能である。また、工程順によっては、実施例12と組み合わせることも可能で

ある。

【実施例20】

【0248】

本実施例では、本発明をボトムゲート型TFTに用いた場合について説明する。具体的

には、逆スタガ型TFTに用いた場合を図23に示す。本発明の逆スタガ型TFTの場合

、本発明のトップゲート型TFTとはゲート配線と活性層の位置関係が異なる以外、特に

大きく異なることはない。従って、本実施例では、図8(C)に示した構造と大きく異な

る点に注目して説明を行い、その他の部分は図8(C)と同一であるため説明を省略する

。

【0249】

図23において、11、12はそれぞれシフトレジスタ回路等を形成するCMOS回路

のpチャネル型TFT、nチャネル型TFT、13はサンプリング回路等を形成するnチ

ャネル型TFT、14は画素部を形成するnチャネル型TFTである。これらは下地膜を

設けた基板上に形成されている。

【0250】

また、15はpチャネル型TFT11のゲート配線、16はnチャネル型TFT12の

ゲート配線、17はnチャネル型TFT13のゲート配線、18はnチャネル型TFT1

4のゲート配線であり、実施例4で説明したゲート配線と同じ材料を用いて形成すること

ができる。また、19はゲート絶縁膜であり、これも実施例4と同じ材料を用いることが

できる。

【0251】

その上には各TFT11〜14の活性層(活性層)が形成される。pチャネル型TFT

11の活性層には、ソース領域20、ドレイン領域21、チャネル形成領域22が形成さ

れる。

【0252】

また、nチャネル型TFT12の活性層には、ソース領域23、ドレイン領域24、L

DD領域(この場合、Lov領域25)、チャネル形成領域26が形成される。

【0253】

また、nチャネル型TFT13の活性層には、ソース領域27、ドレイン領域28、L

DD領域(この場合、Lov領域29a、30a及びLoff領域29b、30b)、チャネル形

成領域31が形成される。

【0254】

また、nチャネル型TFT14の活性層には、ソース領域32、ドレイン領域33、L

DD領域(この場合、Loff領域34〜37)、チャネル形成領域38、39、n+領域4

0が形成される。

【0255】

なお、41〜45で示される絶縁膜は、チャネル形成領域を保護する目的とLDD領域

を形成する目的のために形成されている。

【0256】

以上のように本発明を逆スタガ型TFTに代表されるボトムゲート型TFTに適用する

ことは容易である。なお、本実施例の逆スタガ型TFTを作製するにあたっては、本明細

書中に記載された他の実施例に示される作製工程を、公知の逆スタガ型TFTの作製工程

に適用すれば良い。また、実施例5、7に示したようなアクティブマトリクス型液晶表示

装置に本実施例の構成を適用することも可能である。

【実施例21】

【0257】

本実施例では、本発明をシリコン基板上に作製した反射型液晶表示装置に適用した場合

について説明する。本実施例は、実施例1または実施例4において、結晶質シリコン膜で

なる活性層の代わりに、シリコン基板(シリコンウェハ)に直接的にn型またはp型を付

与する不純物元素を添加し、本発明のTFT構造を実現すれば良い。また、反射型である

ので、画素電極として反射率の高い金属膜を用いれば良い。

【0258】

即ち、同一基板上に画素部と駆動回路とを少なくとも含み、駆動回路を形成するnチャ

ネル型TFTのLDD領域は、少なくとも一部または全部がゲート配線と重なるように配

置され、画素部を形成する画素TFTのLDD領域はゲート配線と重ならないように配置

され、駆動回路を形成するnチャネル型TFTのLDD領域には、画素TFTのLDD領

域よりも高い濃度でn型を付与する不純物元素が含まれる、という構成を有する構造であ

れば良い。

【0259】

なお、本実施例の構成は、実施例1〜7、13〜19のいずれの構成とも自由に組み合

わせることが可能である。

【実施例22】

【0260】

実施例1〜21では、Lov領域やLoff領域をnチャネル型TFTのみに配置し、その

位置を回路仕様に応じて使い分けることを前提に説明を行ってきたが、TFTサイズが小

さくなる(チャネル長が短くなる)と、pチャネル型TFTに対しても同様のことが言え

るようになる。

【0261】

即ち、チャネル長が2μm以下となると短チャネル効果が顕在化するようになるため、

場合によってはpチャネル型TFTにもLov領域を配置する必要性が出てくる。このよう

に本発明において、pチャネル型TFTは実施例1〜21に示した構造に限定されるもの

ではなく、nチャネル型TFTと同一構造であっても構わない。

【0262】

なお、本実施例の構成は実施例1〜21のいずれの構成およびその組み合わせに対して

も当てはまることは言うまでもない。

【実施例23】

【0263】

図33は実施例4に従って作製されたnチャネル型TFT802のドレイン電流(ID

)とゲート電圧(VG)との関係を表すグラフ(以下、ID−VG曲線という)及び電界

効果移動度(μFE)のグラフである。このとき、ソース電圧(VS)は0V、ドレイン電

圧(VD)は1Vまたは14Vとした。なお、実測値はチャネル長(L)が8μm、チャ

ネル幅(W)が7.5μm、ゲート絶縁膜の膜厚(Tox)が115nmであった。

【0264】

図33において、太線はストレス試験前、点線はストレス試験後のID−VG曲線を示

しているが、ストレス試験前後で曲線に殆ど変化はなく、ホットキャリア劣化が抑制され

ていることが判った。なお、ここで行ったストレス試験は、室温にてソース電圧0V、ド

レイン電圧20V、ゲート電圧2Vをかけた状態で60秒保持する試験であり、ホットキ

ャリア劣化を促進させる試験である。

【0265】

さらに、同様のストレス試験を行い、Lov領域の長さによって電界効果移動度(μFE)

の劣化率がどのように変化するか調べた結果を図34に示す。なお、ここでμFEの劣化率

は、 1−(ストレス試験前のμFE/ストレス試験後のμFE)×100で表される。

その結果、Lov領域の長さが0.5μm以上、好ましくは1μm以上のときにホットキャリ

ア効果によるμFEの劣化が抑制されることが判った。

【0266】

また、実施例4及び実施例5に従って液晶表示装置を作製し、その長時間信頼性試験を

行った結果を図35(A)、(B)に示す。なお、本試験はソース線駆動回路のシフトレ

ジスタの電源を正電源(9.6V)、負電源1(−2.4V)

、負電源2(−9.6V)とし、ゲート線駆動回路のシフトレジスタの電源を正電源(9

.6V)、負電源1(−2.4V)、負電源2(−11.0V)として85℃大気中の環

境で動作させている。

【0267】

ここで図35(A)はソース線駆動回路のシフトレジスタにおける消費電流の経時変化

を示しており、3000時間まで殆ど変化がないことを確認することができた。また、図

35(B)はソース線駆動回路のシフトレジスタにおける最低動作電圧(シフトレジスタ

が動作する最低電圧)の経時変化を示しており、やはり3000時間まで殆ど変化がない

ことを確認することができた。また、ここでは示さないがゲート線駆動回路のシフトレジ

スタも同様の結果が得られた。

【実施例24】

【0268】

図36は実施例11に従って作製されたnチャネル型TFT(但し、nチャネル型TF

T802と同一構造)のID−VG曲線及び電界効果移動度である。このとき、ソース電

圧(VS)は0V、ドレイン電圧(VD)は1Vまたは14Vとした。なお、実測値はチ

ャネル長(L)が8.1μm、チャネル幅(W)が7.6μm、ゲート絶縁膜の膜厚(Tox

)が120nmであった。

【0269】

図36において、太線はストレス試験前、点線はストレス試験後の特性を示しており、

ストレス試験前後でホットキャリア劣化は殆ど観測されなかった。なお、ここで行ったス

トレス試験は実施例23で説明したストレス試験とほぼ同じ条件だが、ストレス時のゲー

ト電圧を4Vと高めに設定した。

【0270】

さらに、同様のストレス試験を行い、Lov領域の長さによって電界効果移動度(μFE)

の劣化率(定義は実施例23と同様)がどのように変化するか調べた結果を図37に示す

。図37から明らかなように、Lov領域の長さが1μm以上のときにホットキャリア効果

によるμFEの劣化が抑制されることが判った。

【0271】

また、実施例4、実施例5及び実施例11に従って液晶表示装置を作製し、その長時間

信頼性試験を行った結果を図38(A)、(B)に示す。なお、本試験はソース線駆動回

路のシフトレジスタの電源及びゲート線駆動回路のシフトレジスタの電源を正電源1(8

.5V)、正電源2(4.2V)、負電源(−8.0V)として80℃大気中の環境で動

作させている。

【0272】

ここで図38(A)はソース線駆動回路のシフトレジスタにおける消費電流の経時変化

を示しており、2000時間まで殆ど変化がないことを確認することができた。また、図

38(B)はソース線駆動回路のシフトレジスタにおける最低動作電圧の経時変化を示し

ており、やはり2000時間まで殆ど変化がないことを確認することができた。また、こ

こでは示さないがゲート線駆動回路のシフトレジスタも同様の結果が得られた。

【実施例25】

【0273】

本発明は従来のMOSFET上に層間絶縁膜を形成し、その上にTFTを形成する際に

用いることも可能である。即ち、三次元構造の半導体装置を実現することも可能である。

また、基板としてSIMOX、Smart−Cut(SOITEC社の登録商標)、ELTRA

N(キャノン株式会社の登録商標)などのSOI基板を用いることも可能である。

【0274】

なお、本実施例の構成は、実施例1〜7、13〜19、21〜24のいずれの構成とも

自由に組み合わせることが可能である。

【実施例26】

【0275】

本発明によって作製された液晶表示装置は様々な液晶材料を用いることが可能である。

そのような材料として、TN液晶、PDLC(ポリマー分散型液晶)、FLC(強誘電性

液晶)、AFLC(反強誘性電液晶)、またはFLCとAFLCの混合物が挙げられる。

【0276】

例えば、「H.Furue et al.;Charakteristics and Drivng Scheme of Polymer-Stabiliz

ed Monostable FLCD Exhibiting Fast Response Time and High Contrast Ratio with Gr

ay-Scale Capability,SID,1998」、「T.Yoshida et al.;A Full-Color Thresholdless An

tiferroelectric LCD Exhibiting Wide Viewing Angle with Fast Response Time,841,SI

D97DIGEST,1997」、または米国特許第5,594,569号に開示された材料を用いることができ

る。

【0277】

特に、しきい値なし(無しきい値)の反強誘電性液晶(Thresholdless Antiferroelect

ric LCD:TL−AFLCと略記する)を使うと、液晶の動作電圧を±2.5V程度に低

減しうるため電源電圧として5〜8V程度で済む場合がある。

即ち、駆動回路と画素部を同じ電源電圧で動作させることが可能となり、液晶表示装置全

体の低消費電力化を図ることができる。

【0278】

また、強誘電性液晶や反強誘電性液晶はTN液晶に比べて応答速度が速いという利点を

もつ。本発明で用いるような結晶質TFTは非常に動作速度の速いTFTを実現しうるた

め、強誘電性液晶や反強誘電性液晶の応答速度の速さを十分に生かした画像応答速度の速

い液晶表示装置を実現することが可能である。

【0279】

なお、本実施例の液晶表示装置をパーソナルコンピュータ等の電気器具の表示部として

用いることが有効であることは言うまでもない。

【0280】

また、本実施例の構成は、実施例1〜25のいずれの構成とも自由に組み合わせること

が可能である。

【実施例27】

【0281】

本願発明はアクティブマトリクス型EL(エレクトロルミネッセンス)ディスプレイ(

EL表示装置ともいう)に適用することも可能である。その例を図24に示す。

【0282】

図24は本実施例のアクティブマトリクス型ELディスプレイの回路図である。81は

表示領域を表しており、その周辺にはX方向(ソース側)駆動回路82、Y方向(ゲート

側)駆動回路83が設けられている。また、表示領域81の各画素は、スイッチング用T

FT84、コンデンサ85、電流制御用TFT86、EL素子87を有し、スイッチング

用TFT84にX方向信号線(ソース信号線)88a(または88b)、Y方向信号線(ゲ

ート信号線)89a(または89b、89c)が接続される。また、電流制御用TFT86

には、電源線90a、90bが接続される。

【0283】

なお、本実施例のアクティブマトリクス型ELディスプレイに対して、実施例1〜4、

6、8〜25のいずれの構成を組み合わせても良い。

【実施例28】

【0284】

本実施例では、本願発明を用いてEL(エレクトロルミネセンス)表示装置を作製した

例について説明する。なお、図25(A)は本願発明のEL表示装置の上面図であり、図

25(B)はその断面図である。

【0285】

図25(A)において、4002は基板4001(図13(B)参照)に形成された画

素部、4003はソース側駆動回路、4004はゲート側駆動回路であり、それぞれの駆

動回路は配線4005を経てFPC(フレキシブルプリントサーキット)4006に至り

、外部機器へと接続される。

【0286】

このとき、画素部4002、ソース側駆動回路4003及びゲート側駆動回路4004

を囲むようにして第1シール材4101、カバー材4102、充填材4103及び第2シ

ール材4104が設けられている。

【0287】

また、図25(B)は図25(A)をA−A’で切断した断面図に相当し、基板400

1の上にソース側駆動回路4003に含まれる駆動TFT(但し、ここではnチャネル型

TFTとpチャネル型TFTを図示している。)4201及び画素部4002に含まれる

電流制御用TFT(EL素子への電流を制御するTFT)4202が形成されている。

【0288】

本実施例では、駆動TFT4201には図3のpチャネル型TFT181とnチャネル

型TFT182と同じ構造のTFTが用いられ、電流制御用TFT4202には図3のp

チャネル型TFT181と同じ構造のTFTが用いられる。また、画素部4002には電

流制御用TFT4202のゲートに接続された保持容量(図示せず)が設けられる。

【0289】

駆動TFT4201及び画素TFT4202の上には樹脂材料でなる層間絶縁膜(平坦

化膜)4301が形成され、その上に画素TFT4202のドレインと電気的に接続する

画素電極(陽極)4302が形成される。画素電極4302としては仕事関数の大きい透

明導電膜が用いられる。透明導電膜としては、酸化インジウムと酸化スズとの化合物また

は酸化インジウムと酸化亜鉛との化合物を用いることができる。

【0290】

そして、画素電極4302の上には絶縁膜4303が形成され、絶縁膜4303は画素

電極4302の上に開口部が形成されている。この開口部において、画素電極4302の

上にはEL(エレクトロルミネッセンス)層4304が形成される。EL層4304は公

知の有機EL材料または無機EL材料を用いることができる。また、有機EL材料には低

分子系(モノマー系)材料と高分子系(ポリマー系)材料があるがどちらを用いても良い

。

【0291】

EL層4304の形成方法は公知の蒸着技術もしくは塗布法技術を用いれば良い。また

、EL層の構造は正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層を自由

に組み合わせて積層構造または単層構造とすれば良い。

【0292】

EL層4304の上には遮光性を有する導電膜(代表的にはアルミニウム、銅もしくは

銀を主成分とする導電膜またはそれらと他の導電膜との積層膜)からなる陰極4305が

形成される。また、陰極4305とEL層4304の界面に存在する水分や酸素は極力排

除しておくことが望ましい。従って、真空中で両者を連続成膜するか、EL層4304を

窒素または希ガス雰囲気で形成し、酸素や水分に触れさせないまま陰極4305を形成す

るといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスターツール方

式)の成膜装置を用いることで上述のような成膜を可能とする。

【0293】

そして陰極4305は4306で示される領域において配線4005に電気的に接続さ

れる。配線4005は陰極4305に所定の電圧を与えるための配線であり、異方導電性

フィルム4307を介してFPC4006に電気的に接続される。

【0294】

以上のようにして、画素電極(陽極)4302、EL層4304及び陰極4305から

なるEL素子が形成される。このEL素子は、第1シール材4101及び第1シール材4

101によって基板4001に貼り合わされたカバー材4102で囲まれ、充填材410

3により封入されている。

【0295】

カバー材4102としては、ガラス板、金属板(代表的にはステンレス板)、セラミッ

クス板、FRP(Fiberglass−Reinforced Plastics)板

、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィル

ムまたはアクリルフィルムを用いることができる。また、アルミニウムホイルをPVFフ

ィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる。

【0296】

但し、EL素子からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でな

ければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまた

はアクリルフィルムのような透明物質を用いる。

【0297】

また、充填材4103としては紫外線硬化樹脂または熱硬化樹脂を用いることができ、

PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹

脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いる

ことができる。この充填材4103の内部に吸湿性物質(好ましくは酸化バリウム)を設

けておくとEL素子の劣化を抑制できる。

【0298】

また、充填材4103の中にスペーサを含有させてもよい。このとき、スペーサを酸化

バリウムで形成すればスペーサ自体に吸湿性をもたせることが可能である。また、スペー

サを設けた場合、スペーサからの圧力を緩和するバッファ層として陰極4305上に樹脂

膜を設けることも有効である。

【0299】

また、配線4005は異方導電性フィルム4307を介してFPC4006に電気的に

接続される。配線4005は画素部4002、ソース側駆動回路4003及びゲート側駆

動回路4004に送られる信号をFPC4006に伝え、FPC4006により外部機器

と電気的に接続される。

【0300】

また、本実施例では第1シール材4101の露呈部及びFPC4006の一部を覆うよ

うに第2シール材4104を設け、EL素子を徹底的に外気から遮断する構造となってい

る。こうして図25(B)の断面構造を有するEL表示装置となる。なお、本実施例のE

L表示装置は実施例1〜4、6〜20、22のいずれの構成を組み合わせて作製しても構

わない。

【0301】

ここで画素部のさらに詳細な断面構造を図26に、上面構造を図27(A)に、回路図

を図27(B)に示す。図26、図27(A)及び図27(B)では共通の符号を用いる

ので互いに参照すれば良い。

【0302】

図26において、基板4401上に設けられたスイッチング用TFT4402は図3(

C)のnチャネル型TFT183を用いて形成される。従って、構造の説明はnチャネル

型TFT183の説明を参照すれば良い。また、4403で示される配線は、スイッチン

グ用TFT4402のゲート電極4404a、4404bを電気的に接続するゲート配線で

ある。

【0303】

なお、本実施例ではチャネル形成領域が二つ形成されるダブルゲート構造としているが

、チャネル形成領域が一つ形成されるシングルゲート構造もしくは三つ形成されるトリプ

ルゲート構造であっても良い。

【0304】

また、スイッチング用TFT4402のドレイン配線4405は電流制御用TFT44

06のゲート電極4407に電気的に接続されている。なお、電流制御用TFT4406

は図3(C)のpチャネル型TFT181を用いて形成される。従って、構造の説明はp

チャネル型TFT181の説明を参照すれば良い。なお、本実施例ではシングルゲート構

造としているが、ダブルゲート構造もしくはトリプルゲート構造であっても良い。

【0305】

スイッチング用TFT4402及び電流制御用TFT4406の上には第1パッシベー

ション膜4408が設けられ、その上に樹脂からなる平坦化膜4409が形成される。平

坦化膜4409を用いてTFTによる段差を平坦化することは非常に重要である。後に形

成されるEL層は非常に薄いため、段差が存在することによって発光不良を起こす場合が

ある。従って、EL層をできるだけ平坦面に形成しうるように画素電極を形成する前に平

坦化しておくことが望ましい。

【0306】

また、4410は透明導電膜からなる画素電極(EL素子の陽極)であり、電流制御用

TFT4406のドレイン配線4411に電気的に接続される。画素電極4410として

は酸化インジウムと酸化スズとの化合物もしくは酸化インジウムと酸化亜鉛との化合物か

らなる導電膜を用いることができる。

【0307】

画素電極4410の上にはEL層4412が形成される。なお、図26では一画素しか

図示していないが、本実施例ではR(赤)、G(緑)、B(青)の各色に対応したEL層

を作り分けている。また、本実施例では蒸着法により低分子系有機EL材料を形成してい

る。具体的には、正孔注入層として20nm厚の銅フタロシアニン(CuPc)膜を設け

、その上に発光層として70nm厚のトリス−8−キノリノラトアルミニウム錯体(Al

q3)膜を設けた積層構造としている。Alq3に蛍光色素を添加することで発光色を制御

することができる。

【0308】

但し、以上の例はEL層として用いることのできる有機EL材料の一例であって、これ

に限定する必要はまったくない。発光層、電荷輸送層または電荷注入層を自由に組み合わ

せてEL層(発光及びそのためのキャリアの移動を行わせるための層)を形成すれば良い

。例えば、本実施例では低分子系有機EL材料をEL層として用いる例を示したが、高分

子系有機EL材料を用いても良い。また、電荷輸送層や電荷注入層として炭化珪素等の無

機材料を用いることも可能である。

これらの有機EL材料や無機材料は公知の材料を用いることができる。

【0309】

次に、EL層4412の上には遮光性の導電膜からなる陰極4413が設けられる。本

実施例の場合、遮光性の導電膜としてアルミニウムとリチウムとの合金膜を用いる。勿論

、公知のMgAg膜(マグネシウムと銀との合金膜)を用いても良い。陰極材料としては

、周期表の1族もしくは2族に属する元素からなる導電膜もしくはそれらの元素を添加し

た導電膜を用いれば良い。

【0310】

この陰極4413まで形成された時点でEL素子4414が完成する。なお、ここでい

うEL素子4414は、画素電極(陽極)4410、EL層4412及び陰極4413で

形成されたコンデンサを指す。

【0311】

次に、本実施例における画素の上面構造を図27(A)を用いて説明する。スイッチン

グ用TFT4402のソースはソース配線4415に接続され、ドレインはドレイン配線

4405に接続される。また、ドレイン配線4405は電流制御用TFT4406のゲー

ト電極4407に電気的に接続される。また、電流制御用TFT4406のソースは電流

供給線4416に電気的に接続され、ドレインはドレイン配線4417に電気的に接続さ

れる。また、ドレイン配線4417は点線で示される画素電極(陽極)4418に電気的

に接続される。

【0312】

このとき、4419で示される領域には保持容量が形成される。保持容量4419は、

電流供給線4416と電気的に接続された半導体膜4420、ゲート絶縁膜と同一層の絶

縁膜(図示せず)及びゲート電極4407との間で形成される。また、ゲート電極440

7、第1層間絶縁膜と同一の層(図示せず)及び電流供給線4416で形成される容量も

保持容量として用いることが可能である。

【0313】

なお、本実施例の構成は、実施例1〜4、6、8〜25の構成と自由に組み合わせて実

施することが可能である。

【実施例29】

【0314】

本実施例では、実施例28とは異なる画素構造を有したEL表示装置について説明する

。説明には図28を用いる。なお、図26と同一の符号が付してある部分については実施

例26の説明を参照すれば良い。

【0315】

図28では電流制御用TFT4501として図3(C)のnチャネル型TFT182と

同一構造のTFTを用いる。勿論、電流制御用TFT4501のゲート電極4502はス

イッチング用TFT4402のドレイン配線4405に接続されている。また、電流制御

用TFT4501のドレイン配線4503は画素電極4504に電気的に接続されている

。

【0316】

本実施例では、画素電極4504がEL素子の陰極として機能し、遮光性の導電膜を用

いて形成する。具体的には、アルミニウムとリチウムとの合金膜を用いるが、周期表の1

族もしくは2族に属する元素からなる導電膜もしくはそれらの元素を添加した導電膜を用

いれば良い。

【0317】

画素電極4504の上にはEL層4505が形成される。なお、図28では一画素しか

図示していないが、本実施例ではG(緑)に対応したEL層を蒸着法及び塗布法(好まし

くはスピンコーティング法)により形成している。具体的には、電子注入層として20n

m厚のフッ化リチウム(LiF)膜を設け、その上に発光層として70nm厚のPPV(

ポリパラフェニレンビニレン)膜を設けた積層構造としている。

【0318】

次に、EL層4505の上には透明導電膜からなる陽極4506が設けられる。本実施

例の場合、透明導電膜として酸化インジウムと酸化スズとの化合物もしくは酸化インジウ

ムと酸化亜鉛との化合物からなる導電膜を用いる。

【0319】

この陽極4506まで形成された時点でEL素子4507が完成する。なお、ここでい

うEL素子4507は、画素電極(陰極)4504、EL層4505及び陰極4506で

形成されたコンデンサを指す。

【0320】

このとき、電流制御用TFT4501が本願発明の構造であることは非常に重要な意味

を持つ。電流制御用TFT4501はEL素子4507を流れる電流量を制御するための

素子であるため、多くの電流が流れ、熱による劣化やホットキャリアによる劣化の危険性

が高い素子でもある。そのため、電流制御用TFT4501のドレイン側に、ゲート絶縁

膜4508を介してゲート電極4502に重なるようにLDD領域4509を設ける本願

発明の構造は極めて有効である。

【0321】

また、本実施例の電流制御用TFT4501はゲート電極4502とLDD領域450

9との間にゲート容量と呼ばれる寄生容量を形成する。このゲート容量を調節することで

図27(A)、(B)に示した保持容量4419と同等の機能を持たせることも可能であ

る。特に、EL表示装置をデジタル駆動方式で動作させる場合においては、保持容量のキ

ャパシタンスがアナログ駆動方式で動作させる場合よりも小さくて済むため、ゲート容量

で保持容量を代用しうる。

【0322】

なお、本実施例の構成は、実施例1〜4、6、8〜25の構成と自由に組み合わせて実

施することが可能である。

【実施例30】

【0323】

本実施例では、実施例28もしくは実施例29に示したEL表示装置の画素部に用いる

ことができる画素構造の例を図29(A)〜(C)に示す。なお、本実施例において、4

601はスイッチング用TFT4602のソース配線、4603はスイッチング用TFT

4602のゲート配線、4604は電流制御用TFT、4605はコンデンサ、4606

、4608は電流供給線、4607はEL素子とする。

【0324】

図29(A)は、二つの画素間で電流供給線4606を共通とした場合の例である。即

ち、二つの画素が電流供給線4606を中心に線対称となるように形成されている点に特

徴がある。この場合、電源供給線の本数を減らすことができるため、画素部をさらに高精

細化することができる。

【0325】

また、図29(B)は、電流供給線4608をゲート配線4603と平行に設けた場合

の例である。なお、図29(B)では電流供給線4608とゲート配線4603とが重な

らないように設けた構造となっているが、両者が異なる層に形成される配線であれば、絶

縁膜を介して重なるように設けることもできる。この場合、電源供給線4608とゲート

配線4603とで専有面積を共有させることができるため、画素部をさらに高精細化する

ことができる。

【0326】

また、図29(C)は、図29(B)の構造と同様に電流供給線4608をゲート配線

4603と平行に設け、さらに、二つの画素を電流供給線4608を中心に線対称となる

ように形成する点に特徴がある。また、電流供給線4608をゲート配線4603のいず

れか一方と重なるように設けることも有効である。この場合、電源供給線の本数を減らす

ことができるため、画素部をさらに高精細化することができる。

【実施例31】

【0327】

本願発明の電気光学装置や半導体回路は電気器具の表示部や信号処理回路として用いる

ことができる。そのような電気器具としては、ビデオカメラ、デジタルカメラ、プロジェ

クター、プロジェクションTV、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ

)、ナビゲーションシステム、音響再生装置、ノート型パーソナルコンピュータ、ゲーム

機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍

等)、記録媒体を備えた画像再生装置などが挙げられる。それら電気器具の具体例を図3

0〜32に示す。

【0328】

図30(A)は携帯電話であり、本体2001、音声出力部2002、音声入力部20

03、表示部2004、操作スイッチ2005、アンテナ2006で構成される。本願発

明の電気光学装置は表示部2004に、本願発明の半導体回路は音声出力部2002、音

声入力部2003またはCPUやメモリ等に用いることができる。

【0329】

図30(B)はビデオカメラであり、本体2101、表示部2102、音声入力部21

03、操作スイッチ2104、バッテリー2105、受像部2106で構成される。本願

発明の電気光学装置は表示部2102に、本願発明の半導体回路は音声入力部2103ま

たはCPUやメモリ等に用いることができる。

【0330】

図30(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体2201

、カメラ部2202、受像部2203、操作スイッチ2204、表示部2205で構成さ

れる。本願発明の電気光学装置は表示部2205に、本願発明の半導体回路はCPUやメ

モリ等に用いることができる。

【0331】

図30(D)はゴーグル型ディスプレイであり、本体2301、表示部2302、アー

ム部2303で構成される。本願発明の電気光学装置は表示部2302に、本願発明の半

導体回路はCPUやメモリ等に用いることができる。

【0332】

図30(E)はリアプロジェクター(プロジェクションTV)であり、本体2401、

光源2402、液晶表示装置2403、偏光ビームスプリッタ2404、リフレクター2

405、2406、スクリーン2407で構成される。本発明は液晶表示装置2403に

用いることができ、本願発明の半導体回路はCPUやメモリ等に用いることができる。

【0333】

図30(F)はフロントプロジェクターであり、本体2501、光源2502、液晶表

示装置2503、光学系2504、スクリーン2505で構成される。

本発明は液晶表示装置2502に用いることができ、本願発明の半導体回路はCPUやメ

モリ等に用いることができる。

【0334】

図31(A)はパーソナルコンピュータであり、本体2601、映像入力部2602、

表示部2603、キーボード2604等を含む。本願発明の電気光学装置は表示部260

3に、本願発明の半導体回路はCPUやメモリ等に用いることができる。

【0335】

図31(B)は電子遊戯機器(ゲーム機器)であり、本体2701、記録媒体2702

、表示部2703及びコントローラー2704を含む。この電子遊技機器から出力された

音声や映像は筐体2705及び表示部2706を含む表示ディスプレイにて再生される。

コントローラー2704と本体2701との間の通信手段または電子遊技機器と表示ディ

スプレイとの間の通信手段は、有線通信、無線通信もしくは光通信が使える。本実施例で

は赤外線をセンサ部2707、2708で検知する構成となっている。本願発明の電気光

学装置は表示部2703、2706に、本願発明の半導体回路はCPUやメモリ等に用い

ることができる。

【0336】

図31(C)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレ

ーヤー(画像再生装置)であり、本体2801、表示部2802、スピーカ部2803、

記録媒体2804及び操作スイッチ2805を含む。なお、この画像再生装置は記録媒体

としてDVD(Digital Versatile Disc)、CD等を用い、音楽

鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本願発明の電気光学装置

は表示部2802やCPUやメモリ等に用いることができる。

【0337】

図31(D)はデジタルカメラであり、本体2901、表示部2902、接眼部290

3、操作スイッチ2904、受像部(図示せず)を含む。本願発明の電気光学装置は表示

部2902やCPUやメモリ等に用いることができる。

【0338】

なお、図30(E)のリアプロジェクターや図30(F)のフロントプロジェクターに

用いることのできる光学エンジンについての詳細な説明を図32に示す。なお、図32(

A)は光学エンジンであり、図32(B)は光学エンジンに内蔵される光源光学系である

。

【0339】

図32(A)に示す光学エンジンは、光源光学系3001、ミラー3002、3005

〜3007、ダイクロイックミラー3003、3004、光学レンズ3008a〜300

8c、プリズム3011、液晶表示装置3010、投射光学系3012を含む。投射光学

系3012は、投射レンズを備えた光学系である。本実施例は液晶表示装置3010を三

つ使用する三板式の例を示したが、単板式であってもよい。また、図32(A)中におい

て矢印で示した光路には、光学レンズ、偏光機能を有するフィルム、位相差を調節するた

めのフィルムもしくはIRフィルム等を設けてもよい。

【0340】

また、図32(B)に示すように、光源光学系3001は、光源3013、3014、

合成プリズム3015、コリメータレンズ3016、3020、レンズアレイ3017、

3018、偏光変換素子3019を含む。なお、図32(B)

に示した光源光学系は光源を2つ用いたが、一つでも良いし、三つ以上としてもよい。ま

た、光源光学系の光路のどこかに、光学レンズ、偏光機能を有するフィルム、位相差を調

節するフィルムもしくはIRフィルム等を設けてもよい。

【0341】

以上の様に、本願発明の適用範囲は極めて広く、あらゆる分野の電気器具に適用するこ

とが可能である。また、本実施例の電気器具は実施例1〜30のどのような組み合わせか

らなる構成を用いても実現することができる。

【符号の説明】

【0342】

601 基板

602a、602b 下地膜

603〜606 活性層

607 ゲート絶縁膜

612〜614 n-領域

615 第1の導電膜

616 第2の導電膜

618 第3の導電膜

626、639、640、641 ゲート配線

625、627 接続配線

631、632 p++領域

647〜653 n+領域または(n++n-)領域

654〜657 n--領域

663 保護絶縁膜

664 層間絶縁膜

665〜668 ソース配線

669〜672 ドレイン配線

673、674 接続配線

675 パッシベーション膜

676 第2の層間絶縁膜

677 遮光膜

678 酸化物

679〜681 画素電極

682 保持容量

701、704、708、713、714 チャネル形成領域

702、705、709、715 ソース領域

703、706、710、716 ドレイン領域

707、711a、712a Lov領域

711b、712b、717〜720 Loff領域

721 n+領域

【技術分野】

【0001】

本発明は絶縁表面を有する基板上に薄膜トランジスタ(以下、TFTという)

で構成された回路を有する半導体装置およびその作製方法に関する。特に本発明は、画素

部(画素マトリクス回路)とその周辺に設けられる駆動回路(ドライバー回路)を同一基

板上に設けた液晶表示装置やEL(エレクトロルミネッセンス)表示装置に代表される電

気光学装置(電子装置ともいう)、および電気光学装置を搭載した電気器具(電子機器と

もいう)に関する。

【0002】

尚、本願明細書において半導体装置とは、半導体特性を利用することで機能する装置全

般を指し、上記電気光学装置およびその電気光学装置を用いた電気器具も半導体装置に含

む。

【背景技術】

【0003】

絶縁表面を有する基板上にTFTで形成した大面積集積回路を有する半導体装置の開発

が進んでいる。アクティブマトリクス型液晶表示装置、EL表示装置、および密着型イメ

ージセンサはその代表例として知られている。特に、結晶質シリコン膜(代表的にはポリ

シリコン膜)を活性層にしたTFT(以下、ポリシリコンTFTと記す)は電界効果移動

度が高いことから、いろいろな機能回路を形成することも可能である。

【0004】

例えば、アクティブマトリクス型液晶表示装置には、機能ブロックごとに画像表示を行

う画素部や、CMOS回路を基本としたシフトレジスタ回路、レベルシフタ回路、バッフ

ァ回路、サンプリング回路などの集積回路が一枚の基板上に形成される。また、密着型イ

メージセンサでは、サンプルホールド回路、シフトレジスタ回路、マルチプレクサ回路な

どの集積回路がTFTを用いて形成されている。

【0005】

これらの駆動回路(周辺駆動回路ともいう)はそれぞれにおいて動作条件が必ずしも同

一でないので、当然TFTに要求される特性も少なからず異なっている。画素部において

は、スイッチ素子として機能する画素TFTと補助の保持容量を設けた構成であり、液晶

に電圧を印加して駆動させるものである。ここで、液晶は交流で駆動させる必要があり、

フレーム反転駆動と呼ばれる方式が多く採用されている。従って、要求されるTFTの特

性はオフ電流値(TFTがオフ動作時に流れるドレイン電流値)を十分低くさせておく必

要があった。また、バッファ回路は高い駆動電圧が印加されるため、高電圧がかかっても

壊れない程度に耐圧を高めておく必要があった。また電流駆動能力を高めるために、オン

電流値(TFTがオン動作時に流れるドレイン電流値)を十分確保する必要があった。

【0006】

しかし、ポリシリコンTFTのオフ電流値は高くなりやすいといった問題点がある。ま

た、ICなどで使われるMOSトランジスタと同様にポリシリコンTFTにはオン電流値

の低下といった劣化現象が観測される。主たる原因はホットキャリア注入であり、ドレイ

ン近傍の高電界によって発生したホットキャリアが劣化現象を引き起こすものと考えられ

ている。

【0007】

オフ電流値を低減するためのTFTの構造として、低濃度ドレイン(LDD:Lightly

Doped Drain)構造が知られている。この構造はチャネル形成領域と、高濃度に不純物

が添加されるソース領域またはドレイン領域との間に低濃度の不純物領域を設けたもので

あり、この低濃度不純物領域はLDD領域と呼ばれている。

【0008】

また、ホットキャリア注入によるオン電流値の劣化を防ぐための構造として、いわゆる

GOLD(Gate-drain Overlapped LDD)構造が知られている。この構造は、LDD領

域がゲート絶縁膜を介してゲート配線と重なるように配置されているため、ドレイン近傍

のホットキャリア注入を防ぎ、信頼性を向上させるのに有効である。例えば、「Mutsuko

Hatano,Hajime Akimoto and Takeshi Sakai,IEDM97 TECHNICAL DIGEST,p523-526,

1997」では、シリコンで形成したサイドウォールによるGOLD構造を開示しているが、

他の構造のTFTと比べ、きわめて優れた信頼性が得られることが確認されている。

【0009】

また、アクティブマトリクス型液晶表示装置の画素部には、数十から数百万個の各画素

にTFTが配置され、そのTFTのそれぞれには画素電極が設けられている。液晶を挟ん

だ対向基板側には対向電極が設けられており、液晶を誘電体とした一種のコンデンサを形

成している。そして、各画素に印加する電圧をTFTのスイッチング機能により制御して

、このコンデンサへの電荷を制御することで液晶を駆動し、透過光量を制御して画像を表

示する仕組みになっている。

【0010】

ところが、このコンデンサはオフ電流等に起因するリーク電流により次第にその蓄積容

量が減少するため、透過光量が変化して画像表示のコントラストを低下させる原因となっ

ていた。そこで、従来では容量配線を設けて、液晶を誘電体とするコンデンサとは別のコ

ンデンサ(保持容量という)を並列に設け、液晶を誘電体とするコンデンサが損失する容

量を補っていた。

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかしながら、画素部の画素TFTと、シフトレジスタ回路やバッファ回路などのロジ

ック回路(駆動回路ともいう)のTFT(以下、駆動TFTという)とでは、その要求さ

れる特性は必ずしも同じではない。例えば、画素TFTにおいては、ゲート配線に大きな

逆バイアス(nチャネル型TFTであればマイナス)

電圧が印加されるが、駆動回路のTFTは基本的に逆バイアス電圧が印加されて動作され

ることはない。また、前者の動作速度は後者の1/100以下で良い。

【0012】

また、GOLD構造は確かにオン電流値の劣化を防ぐ効果は高いが、反面、通常のLD

D構造に比べてオフ電流値が大きくなってしまう問題があった。従って、特に画素TFT

にとっては好ましい構造とは言えなかった。逆に通常のLDD構造はオフ電流値を抑える

効果は高いが、ホットキャリア注入には弱いことが知られていた。

【0013】

このように、アクティブマトリクス型液晶表示装置のような複数の集積回路を有する半

導体装置において、全てのTFTを同じ構造で形成することは必ずしも好ましくなかった

。

【0014】

さらに、従来例に示したように画素部に容量配線を用いた保持容量を形成して十分な容

量を確保しようとすると、開口率(一画素の面積に対して画像表示が可能な面積の割合)

を犠牲にしなければならなかった。特に、プロジェクター型表示装置に用いられるような

小型の高精細パネルでは、一個当たりの画素面積も小さいため、容量配線による開口率の

低下は問題となっていた。

【0015】

本発明はこのような課題を解決するための技術であり、半導体装置の各回路に配置され

るTFTの構造を、回路の機能に応じて適切なものとすることにより半導体装置の動作性

能および信頼性を向上させることを目的とする。

【0016】

また、他の目的として画素部を有する半導体装置において、画素に設けられる保持容量

の面積を縮小化し、開口率を向上させるための構造を提供することを目的とする。

【課題を解決するための手段】

【0017】

上記問題点を解決するために本発明の構成は、同一基板上に画素部と駆動回路とを含む

半導体装置において、前記駆動回路を形成するnチャネル型TFTのLDD領域は、一部

または全部が該nチャネル型TFTのゲート配線にゲート絶縁膜を挟んで重なるように形

成され、前記画素部を形成する画素TFTのLDD領域は、該画素TFTのゲート配線に

ゲート絶縁膜を挟んで重ならないように形成されることを特徴とする。

【0018】

また、上記構成に加えて、前記画素部の保持容量を樹脂膜の上に設けられた遮光膜、該

遮光膜の酸化物および画素電極で形成しても良い。こうすることで非常に小さい面積で保

持容量を形成することができるため、画素の開口率を向上させることができる。