ESD保護検証装置

【課題】 寄生バイポーラの生成を抑制しつつ、開発遅延を効果的に防止できるESD保護検証装置を提供する。

【解決手段】 回路図データを受け付ける回路図データ取得手段11aと、回路図データから外部端子を抽出する外部端子抽出手段11bと、回路図データからESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、配置配線処理において、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウトデータを出力するレイアウトデータ出力手段11fと、を備える。

【解決手段】 回路図データを受け付ける回路図データ取得手段11aと、回路図データから外部端子を抽出する外部端子抽出手段11bと、回路図データからESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、配置配線処理において、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウトデータを出力するレイアウトデータ出力手段11fと、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、適切な耐性を備えるESD保護素子の適切な配置を支援するためのレイアウトシステムに関する。

【背景技術】

【0002】

半導体装置では、人体や他の外部装置等の静電気帯電物体から放電された静電気が、外部端子を通じて内部回路を破損させることがある。このため、半導体装置では、放電された静電気から内部回路を保護するために、例えば、ESD(Electro Static Discharge)保護素子を外部端子と内部回路を結ぶ配線上に配置している。

【0003】

ESD保護素子は、例えば、外部端子である入出力端子と電源端子の間、或いは、入出力端子とGND端子間に接続されており、外部端子に放電された静電気を、電源端子やGND端子にバイパスさせ、内部回路に静電気が放電されるのを防止している。このように構成することにより、半導体装置の内部回路は、静電気の放電による破壊から保護されることになる。

【0004】

ESD保護素子の配置に関する技術としては、例えば、回路図データから、外部端子別に、当該外部端子に直接接続される素子を抽出し、抽出された素子にESD保護素子が含まれるか否かを判定する検証装置がある(例えば、特許文献1参照)。当該検証装置を用いれば、外部端子の夫々にESD保護素子が設けられているか否かを判定することができるので、ESD保護素子の配置し忘れを防止できる。

【0005】

尚、ESD保護素子を有効に働かせる為には、ESD保護素子が正しく接続されていること、及び、ESD保護素子が必要な耐性を備えていることが重要である。必要な耐性を備えるESD保護素子の配置には、例えば、実績のあるESD保護素子の再利用やESD保護素子の自動生成が有効である。更に、ESD保護素子が正しく接続され必要な耐性を備えているかを検証することが重要である。

【0006】

ESD保護素子が正しく接続され必要な耐性を備えているかを検証するための技術としては、例えば、レイアウトデータの作成後に、当該レイアウトデータに基づいて、ESD保護素子を抽出し、ESD保護素子と周辺素子及び外部端子との接続関係を検証し、ESD保護素子の寸法が適切であるか否かを検証する検証装置がある(例えば、特許文献2参照)。当該検証装置を用いれば、ESD保護素子が正しく接続されているか、及び、ESD保護素子が適切な耐性(寸法)を備えているかを判定できる。

【0007】

ところで、半導体装置では、レイアウトの配置配線処理を実行した後、ESD保護素子の配置によっては、意図しない寄生バイポーラが生成されることがある。寄生バイポーラが生成されると、静電気が、ESD保護素子ではなく、意図せずに形成された寄生バイポーラからなるESDサージ経路に流入して、ESD破壊が発生する可能性がある。尚、ESD保護素子の配置により偶発的に生成される寄生バイポーラについては、ESD保護素子の配置処理後まで生成されるか否かが分からないことから、従来は、配置配線処理後のレイアウトデータに対し、寄生バイポーラが生成されているか否かを検証している。

【0008】

寄生バイポーラの検証技術としては、例えば、レイアウトデータから寄生バイポーラを抽出し、デバイスシミュレータを用いて寄生バイポーラの回路パラメータを抽出し、当該回路パラメータを用いて回路シミュレータ(例えば、SPICE)により動作検証を行う検証装置がある(例えば、特許文献3参照)。

【0009】

この検証装置では、回路シミュレータにより動作検証を行うので、静電気放電による誤動作等を検証でき、ESD破壊が発生するのを効果的に防止できる。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2005−50209号公報

【特許文献2】特開平7−65043号公報

【特許文献3】特開2006−134955号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかしながら、上述した検証装置では、レイアウトにおける配置配線処理の実行後に、レイアウトデータに基づいて寄生バイポーラの検証を行っていることから、寄生バイポーラが生成されている場合には、寄生バイポーラに係る素子の配置修正処理を行い、再度、寄生バイポーラの検証を行う必要がある。即ち、寄生バイポーラが生成されなくなるまで、繰り返し配置修正処理と寄生バイポーラの検証を行う必要がある。

【0012】

ここで、配置配線処理後の配置修正処理は、非常に手間と時間のかかる作業であることから、繰り返し配置修正処理が実行されると、開発遅延等を引き起こす可能性があった。

【0013】

本発明は上記の問題に鑑みてなされたものであり、その目的は、レイアウトデータの生成後にESD検証を行うことによるレイアウトのやり直しを低減して、寄生バイポーラの生成を抑制しつつ、開発遅延を効果的に防止できるESD保護検証装置を提供する点にある。

【課題を解決するための手段】

【0014】

上記目的を達成するための本発明に係るESD保護検証装置は、レイアウトデータの生成に用いられる回路図データを受け付ける回路図データ取得手段と、前記回路図データから、外部端子を抽出する外部端子抽出手段と、前記回路図データから、抽出された前記外部端子に接続されたESD保護素子を抽出するESD保護素子抽出手段と、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、前記ESD保護素子抽出手段によって抽出された前記ESD保護素子の夫々について、前記第1判定条件を満たすか否かを判定する第1判定処理を実行し、前記第1判定条件を満たす前記ESD保護素子を対象素子として設定する第1判定手段と、前記回路図データに対する配置配線処理において、前記対象素子の夫々について、前記寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように前記対象素子の配置処理を実行して、前記レイアウトデータを作成するレイアウト作成手段と、前記レイアウト作成手段によって作成された前記レイアウトデータを出力するレイアウトデータ出力手段と、を備えることを第1の特徴とする。

【0015】

更に好ましくは、上記特徴のESD保護検証装置は、前記レイアウト作成手段が、前記対象素子の配置処理として、前記対象素子を所定位置に配置する第1副配置処理と、前記対象素子が前記レイアウト条件を満たすか否かを判定するレイアウト条件判定処理と、前記レイアウト条件判定処理において、前記レイアウト条件を満たさないと判定された場合に、前記対象素子を以前に実行された前記副配置処理とは異なる位置に配置する第2副配置処理と、を実行可能に構成され、前記レイアウト条件判定処理において、前記レイアウト条件を満たすと判定されるまで、前記第2副配置処理及び前記レイアウト条件判定処理を繰り返し実行する。

【0016】

更に好ましくは、上記特徴のESD保護検証装置は、前記第1判定手段が、前記第1判定処理の実行後、前記対象素子を構成するレイヤ領域の内、前記寄生バイポーラを構成する可能性のある前記レイヤ領域を特殊レイヤ領域として設定する。

【0017】

更に好ましくは、上記特徴のESD保護検証装置は、前記寄生バイポーラの発生する可能性のある2つの素子間の関係として、前記ESD保護素子の端子と他の素子の端子の端子関係を規定した判定条件テーブルを備え、前記第1判定手段が、前記第1判定処理において、前記ESD保護素子抽出手段によって抽出された前記ESD保護素子の夫々について、当該ESD保護素子と他の素子の関係が前記判定条件テーブルに規定された端子関係の何れかに合致する場合に、前記第1判定条件を満たすと判定し、前記ESD保護素子の寄生バイポーラを構成する可能性のある端子を構成する前記レイヤ領域、及び、前記他の素子の寄生バイポーラを構成する可能性のある端子を構成する前記レイヤ領域を前記特殊レイヤ領域として設定する。

【0018】

更に好ましくは、上記特徴のESD保護検証装置は、前記レイアウト条件が、前記寄生バイポーラを構成する可能性のある2つの前記特殊レイヤ領域の間の距離範囲を規定する第1距離条件を含む。

【0019】

更に好ましくは、上記第1の特徴のESD保護検証装置は、前記寄生バイポーラの発生する可能性のある2つの素子間の関係として、前記ESD保護素子の端子と他の素子の端子の端子関係を規定した判定条件テーブルを備え、前記第1判定手段が、前記第1判定処理において、前記ESD保護素子抽出手段によって抽出された前記ESD保護素子の夫々について、当該ESD保護素子と他の素子の関係が前記判定条件テーブルに規定された端子関係の何れかに合致する場合に、前記第1判定条件を満たすと判定する。

【0020】

更に好ましくは、上記特徴のESD保護検証装置は、前記レイアウト条件が、前記ESD保護素子と他の前記素子の間の距離範囲を規定する第2距離条件を含む。

【0021】

更に好ましくは、上記何れかの特徴のESD保護検証装置は、前記レイアウト条件が、配線処理において、前記外部端子と前記ESD保護素子を直接的に接続する配線とその他の配線の重なりを禁止する重なり禁止条件を含む。

【0022】

更に好ましくは、上記何れかの特徴のESD保護検証装置は、前記ESD保護素子抽出手段による前記ESD保護素子の抽出後、前記外部端子抽出手段により抽出された前記外部端子の全てに前記ESD保護素子が接続されているか否かを判定する第2判定手段と、前記ESD保護素子抽出手段によって抽出された前記ESD保護素子別に、前記ESD保護素子の耐圧情報を取得し、前記ESD保護素子の接続された前記外部端子にかかる電圧情報を取得し、前記耐圧情報と前記電圧情報に基づいて前記ESD保護素子が適切であるか否かを判定する第3判定手段と、を備え、前記第1判定手段が、前記第2判定手段により前記外部端子の全てに前記ESD保護素子が接続されていると判定され、且つ、前記第3判定手段により前記ESD保護素子の全てについて適切であると判定された場合に、前記第1判定処理を実行する。

【発明の効果】

【0023】

上記特徴のESD保護検証装置によれば、第1判定手段が、レイアウト実行前の回路図データから寄生バイポーラが発生する可能性のある対象素子を抽出し、レイアウト作成手段が、対象素子の配置処理毎に、当該対象素子の配置により寄生バイポーラが発生しないようにレイアウトを行う、即ち、配置配線処理の終了後ではなく、配置配線処理中に、配置修正を行うので、開発時間の増大を抑制できる。

【0024】

具体的には、配置配線処理後に配置修正処理を行う場合、特に、面積に余裕がない半導体装置では、配置修正処理にかかるスペースを確保することが難しく、対象素子以外の素子を含めて大規模な修正が必要になる場合がある。これに対し、上記特徴のESD保護検証装置によれば、第1判定手段により寄生バイポーラが発生する可能性のある対象素子を予め特定しておき、寄生バイポーラが生成されないように対象素子の配置処理を行うので、配置配線処理後の配置修正処理のような大幅な修正処理が必要なくなり、開発時間の増大を効果的に抑制できる。

【図面の簡単な説明】

【0025】

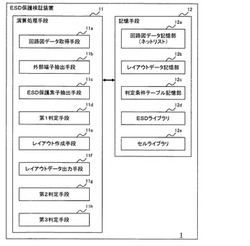

【図1】本発明に係るESD保護検証装置の概略構成例を示す概略ブロック図である。

【図2】本発明に係るESD保護検証装置の処理動作を示すフローチャートである。

【図3】本発明に係るESD保護検証装置で用いる回路図データの一例を示す図である。

【図4】本発明に係るESD保護検証装置で用いる回路図データの構造例を示す概略ブロック図である。

【図5】SPICEネットリストの読み込み処理を示すフローチャートである。

【図6】ESD保護素子の構成の一例を示す概略回路図である。

【図7】本発明に係るESD保護検証装置で用いる判定条件テーブルの一例を示す表である。

【図8】本発明に係るESD保護検証装置で用いる特殊レイヤ情報の一例を示す表である。

【図9】寄生バイポーラが発生する可能性のある特殊レイヤ領域の一例とその条件を模式的に示す概略ブロック図である。

【図10】外部端子とESD保護素子を直接的に接続する配線とその他の配線の重なりの例と、当該重なりを禁止する重なり禁止条件を示す図である。

【発明を実施するための形態】

【0026】

以下、本発明に係るESD保護検証装置(以下、適宜「本発明装置」と略称する)の実施形態を図面に基づいて説明する。

【0027】

本発明装置の実施形態について、図1〜図9を基に説明する。

【0028】

先ず、本発明装置1の構成について、図1を基に説明する。

【0029】

図1に示すように、本発明装置1は、コンピュータ処理によりレイアウトの配置配線処理等を実行する演算処理手段11と、ハードディスク等の不揮発性記憶装置及び演算処理手段11における演算結果や各種DBから取得した情報を一時的に記憶するRAM等で構成される記憶手段12を備えて構成されている。

【0030】

記憶手段12は、回路図データとして、SPICE形式のネットリストを記憶する回路図データ記憶部12a、本発明装置1によって作成されるレイアウトデータを記憶するレイアウトデータ記憶部12b、寄生バイポーラの発生する可能性のある2つの素子間の関係として、ESD保護素子の端子と他の素子の端子の端子関係を規定した判定条件テーブルを記憶する判定条件テーブル記憶部12c、過去に使用実績があるESD保護素子のレイアウトデータを記憶したESDライブラリ12d、及び、各素子のレイアウトデータを記憶したセルライブラリ12eを備えて構成されている。尚、本実施形態では、SPICE形式のネットリストを用いる場合について説明するが、これに限るものではなく、レイアウトデータの生成に用いられる回路図データであればよい。

【0031】

本実施形態では、回路図データとしてのネットリストには、トランジスタや容量素子、抵抗素子等の各素子について、各端子に接続される配線を示す接続情報や素子寸法、耐圧情報等の素子情報が記載されている。更に、外部端子について、接続される配線を示す接続情報や印加電圧の電圧値を示す電圧情報等の端子情報が記載されている。尚、本実施形態では、ネットリストに素子情報や端子情報が含まれる場合を想定しているが、これらの情報については、素子情報及び端子情報を記憶した外部ファイルを用意しておき、当該外部ファイルを利用するように構成しても良い。

【0032】

演算処理手段11は、レイアウトデータの生成に用いられる回路図データを受け付ける回路図データ取得手段11aと、回路図データから、外部端子を抽出する外部端子抽出手段11bと、回路図データから、抽出された外部端子に接続されたESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、ESD保護素子抽出手段11cによって抽出されたESD保護素子の夫々について、第1判定条件を満たすか否かを判定する第1判定処理を実行し、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、回路図データに対する配置配線処理において、対象素子の夫々について、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウト作成手段11eによって作成されたレイアウトデータを出力するレイアウトデータ出力手段11fと、を備えている。本実施形態では、回路図データ取得手段11a、外部端子抽出手段11b、ESD保護素子抽出手段11c、第1判定手段11d、レイアウト作成手段11e、及び、レイアウトデータ出力手段11fは、各手段を実現するソフトウェアで構成されている。

【0033】

本実施形態の演算処理手段11は、更に、ESD保護素子抽出手段11cによるESD保護素子の抽出後、外部端子抽出手段11bにより抽出された外部端子の全てにESD保護素子が接続されているか否かを判定する第2判定手段11gと、ESD保護素子抽出手段11cによって抽出されたESD保護素子別に、ESD保護素子の耐圧情報を取得し、ESD保護素子の接続された外部端子にかかる電圧情報を取得し、耐圧情報と電圧情報に基づいてESD保護素子が適切であるか否かを判定する第3判定手段11hと、を備えている。

【0034】

尚、本実施形態では、第1判定手段11dが、第1判定処理の実行後、対象素子を構成するレイヤ領域の内、寄生バイポーラを構成する可能性のあるレイヤ領域を特殊レイヤ領域として設定するように構成されている。

【0035】

また、本実施形態では、レイアウト作成手段11eは、市販のレイアウトツールであるネットドリブンエディタ及びリアルタイムDRC、例えば、Cadence社のVirtuosoXL及びDRDや、ジーダット社のismo及びiDRC等を利用して構成されている。尚、利用する市販ツールはこれらに限られるものではなく、本発明装置1が配置配線処理を実行する機能を備えていても良い。レイアウト作成手段11eは、回路図データの素子情報及び端子情報に基づいて、回路を構成する素子の夫々について、対応するレイアウトデータをセルライブラリ12eから取得し、レイヤ領域の追加や変形などを適宜実行しながら配置する配線処理と、配線を引く配線処理とを実行する。

【0036】

次に、本発明装置1の処理動作について、図2〜図9を基に説明する。ここで、図2は、本発明装置1の処理動作を示すフローチャートである。

【0037】

本発明装置1は、先ず、回路図データにおいて適切なESD保護素子が正しく接続されているかを検証する回路図データ検証処理(ステップ#10)を実行する。

【0038】

具体的には、先ず、回路図データ取得手段11aが、回路図データとして、SPICE形式のネットリスト等、トランジスタレベルのネットリストを受け付け、記憶手段12に記憶する(ステップ#11)。尚、本実施形態では、回路図データ取得手段11aが、回路図作成装置から回路図データを取得する場合を想定しているが、これに限るものではない。

【0039】

ここで、図3は、SPICEネットリストの記述例を、図4は、図3に示すSPICEネットリストの階層構造を示している。本実施形態では、ネットリストが階層構造を有している場合を想定しており、最上位階層TOP内に、内部回路BLOCKA、BLOCKBが構成されている。最上位階層TOPの端子T1〜Tnは外部端子であり、内部回路BLOCKAの端子TA1〜TAi、内部回路BLOCKBの端子TB1〜TBjは内部端子である。ESD保護素子抽出手段11cは、図3及び図4のネットリストでは、外部端子T1から引かれている配線に接続されているESD保護素子M1、M2、外部端子T2から引かれている配線に接続されているESD保護素子M3、M4等、最上位階層TOPだけでなく下位階層である内部回路BLOCKA、BLOCKBにある全てのESD保護素子を抽出する。本実施形態では、ESD保護素子抽出手段11cは、更に、図3に示す回路図データから、抽出されたESD保護素子の素子情報を取得する。

【0040】

図5(a)は、回路図データの一例であるSPICEネットリストの読み込み処理を示すフローチャートである。本実施形態の回路図データ取得手段11aは、ネットリストとしてSPICEネットリストを受け付けた場合、先ず、ファイルを開き(ステップ#101)、先頭行から一行ずつ読み込む(ステップ#102)。読み込んだ行が最終行の場合は処理を終了する(ステップ#102でYES分岐)。

【0041】

最終行ではない場合(ステップ#102でNO分岐)、先頭ワードが“.SUBCKT”の場合は(ステップ#103で.SUBCKT分岐)、SUBCKTをセットし(ステップ#104)、SUBCKTテーブルを作成する。SUBCKTテーブルには、図5(b)に示すように、名称情報Name及びピン情報Termが記憶される。ステップ#103において、先頭ワードがMQDRCの何れかである場合は(ステップ#103で素子分岐)、素子テーブルを作成し(ステップ#105)、SUBCKTテーブルに名称Instanceを記憶する(ステップ#106)。素子テーブルには、名称Name(SUBCKTテーブルのInstance)、ピン情報Term、素子属性Property、登録されているSUBCKT情報Subcktを記憶する。ステップ#103において、先頭ワードが“.END”である場合は(ステップ#103でEND分岐)、SUBCKTを解除する(ステップ#107)。尚、図5(a)では明記していないが、先頭ワードがV、Iで始まるSPICE用信号源、或いは、“.OPT”等のSPICE専用文や注釈行については、ステップ#103で省く処理を行っている。

【0042】

続いて、図2に示すように、外部端子抽出手段11bが、回路図データから、外部端子を抽出し、外部端子の端子情報を取得する(ステップ#12)。更に、ESD保護素子抽出手段11cが、回路図データから、抽出された外部端子に接続されたESD保護素子を抽出する(ステップ#13)。

【0043】

引き続き、本発明装置1の第2判定手段11gが、回路図データの接続情報に基づいて、外部端子の全てにESD保護素子が接続されているか否かを検証する(ステップ#14)。第2判定手段11gは、全ての外部端子にESD保護素子が接続されていない場合(ステップ#14でNO分岐)、エラーを出力し、処理を終了する(ステップ#17)。

【0044】

ステップ#14において、全ての外部端子にESD保護素子が接続されていると判定された場合は(ステップ#14でYES分岐)、本発明装置1の第3判定手段11hが、ESD保護素子別に、回路図データから、ESD保護素子の耐圧情報とESD保護素子の接続された外部端子の電圧情報を取得し、取得した耐圧情報と電圧情報に基づいてESD保護素子が適切であるか否かを検証する(ステップ#15)。尚、ここでは、ESD保護素子は、低耐圧、中耐圧、高耐圧の3種類が用意されている。本実施形態では、第3判定手段11hは、回路図データに与えられた情報から電圧情報を取得し、当該電圧情報から必要な素子寸法を求め、接続されているESD保護素子の寸法が必要な素子寸法を備えているかを判定する。第3判定手段11hは、必要な素子寸法を備えていないESD保護素子がある場合は(ステップ#15でNG分岐)、エラーを出力し、処理を終了する(ステップ#17)。

【0045】

ステップ#15において、全てのESD保護素子が適切な素子寸法を備えていると判定された場合は(ステップ#15でOK分岐)、本発明装置1は、ESD保護素子が正しく接続されているか否かを検証する(ステップ#16)。ここで、図6は、ESD保護素子の接続構成の例を示している。本発明装置1は、接続誤りのあるESD保護素子がある場合は(ステップ#16でNG分岐)、エラーを出力し、処理を終了する(ステップ#17)。

【0046】

ステップ#14において、第2判定手段11gにより外部端子の全てにESD保護素子が接続されていると判定され、且つ、ステップ#15において、第3判定手段11hによりESD保護素子の全てについて適切であると判定され、更に、ステップ#16において、ESD保護素子の接続構成が正しいと判定されると、本発明装置1は、図2に示すように、寄生バイポーラが発生する可能性のあるESD保護素子のレイヤ領域を特定する前処理を行う(ステップ#20)。

【0047】

具体的には、先ず、本発明装置1は、ESD保護素子について、後述する配置配線処理(ステップ#30)において使用するレイアウトセルをESDライブラリ12dから選択する(ステップ#21)。

【0048】

引き続き、第1判定手段11dが、第1判定処理において、ESD保護素子抽出手段11cによって抽出されたESD保護素子の夫々について、当該ESD保護素子と他の素子の関係が判定条件テーブルに規定された端子関係の何れかに合致する場合に、第1判定条件を満たすと判定して対象素子として設定し、ESD保護素子の寄生バイポーラを構成する可能性のある端子を構成するレイヤ領域、及び、他の素子の寄生バイポーラを構成する可能性のある端子を構成するレイヤ領域を特殊レイヤ領域として設定する(ステップ#22)。

【0049】

ここで、図7は、判定条件テーブルの一例を示しており、2つのMOSトランジスタの端子関係を示している。図7において、Dはドレイン端子、Gはゲート端子、Sはソース端子、Bはバックゲート端子であり、“○”は、近接配置された場合に寄生バイポーラが発生する可能性のある端子を示している。例えば、図7では、検証対象のESD保護素子と他の素子が何れも5V−NMOSである場合、ESD保護素子のドレイン端子と他の素子のドレイン端子は、近接配置されると寄生バイポーラが発生する可能性があるとしている。従って、検証対象のESD保護素子と他の素子が何れも5V−NMOSの場合、検証対象のESD保護素子のドレイン端子を構成するレイヤ領域と他の素子のドレイン端子を構成するレイヤ領域を特殊レイヤ領域として設定する。

【0050】

更に、第1判定手段11dは、設定した特殊レイヤ領域を特定するための特殊レイヤ情報を回路図データに書き込む(ステップ#23)。尚、本実施形態では、特殊レイヤ情報を回路図データに書き込む場合について説明するが、他のファイルに書き込むように構成しても良い。ここで、図8は、回路図データに書き込む特殊レイヤ情報の一例を示しており、ESD保護素子のインスタンス名、特殊レイヤID、ステップ#21で選択したレイアウトセルを特定するためのレイアウトセル情報、及び、特殊レイヤ領域を特定するための情報が記載されている。尚、図8では、特殊レイヤ領域を特定するための情報は、レイアウトセル内における特殊レイヤ領域の位置であり、レイアウトセルの原点からの座標で示されている。

【0051】

続いて、配置配線処理(ステップ#30)を行う。

【0052】

配置処理において、特殊レイヤ領域を備える対象素子の配置処理を行う場合(ステップ#31でYES分岐)、本発明装置1のレイアウト作成手段11eは、先ず、対象素子を所定位置に配置する第1副配置処理を実行する(ステップ#32)。

【0053】

第1副配置処理では、ステップ#21において回路図データに記憶したセル情報に基づいて、ESDライブラリ12dからレイアウトセルを取得し、ステップ#23で設定した特殊レイヤ領域の情報を取得する。これにより、ESD保護素子のレイアウト構造が決定される。レイアウト作成手段11eは、ESD保護素子を、決定されたレイアウト構造でチップ上に配置する。

【0054】

引き続き、レイアウト作成手段11eは、対象素子がレイアウト条件を満たすか否かを判定するレイアウト条件判定処理を実行する(ステップ#33)。尚、レイアウト条件は、寄生バイポーラを構成する可能性のある2つの特殊レイヤ領域の間の距離範囲を規定する第1距離条件を想定している。

【0055】

ここで、図9は、寄生バイポーラが発生する可能性のある特殊レイヤ領域が設定されたESD保護素子の例を示している。ここでは、同一のPウェルに形成されるN型拡散層N1及びN型拡散層N2が特殊レイヤ領域として設定されており、特殊レイヤ領域N1と特殊レイヤ領域N2の最短距離が第1距離条件で示す距離範囲内の場合は、レイアウト条件を満たさないと判定し、N型拡散層N1及びN型拡散層N2の間の最短距離が第1距離条件で示す距離範囲外の場合は、レイアウト条件を満たすと判定する。2つの特殊レイヤ領域の間の距離を、第1距離条件で示す距離範囲より大きくすることで、寄生バイポーラ素子を形成する可能性のある特殊レイヤ領域同士の近接配置が少なくなり、寄生バイポーラの生成を抑制できる。寄生バイポーラが発生し難い条件で配置処理を行うことから、寄生バイポーラの発生を効果的に防止して、寄生バイポーラの発生による配置配線終了後の配置修正処理を実行しないか実行回数を少なくすることができる。

【0056】

レイアウト作成手段11eは、レイアウト条件判定処理において、レイアウト条件を満たさないと判定された場合(ステップ#33でNG分岐)、対象素子の再配置を行う第2副配置処理(ステップ#32)を実行する。尚、レイアウト作成手段11eは、対象素子の配置処理が終了するまで、対象素子の副配置処理の実行結果を記憶しておき、各副配置処理において異なる位置に配置されるようにする。

【0057】

レイアウト作成手段11eは、レイアウト条件判定処理(ステップ#33)において、レイアウト条件を満たすと判定された場合(ステップ#33でOK分岐)、対象素子の配置処理を終了する。

【0058】

レイアウト作成手段11eは、配置処理において、対象素子以外の素子については(ステップ#31でYES分岐)、通常の配置処理を実行する(ステップ#34)。

【0059】

レイアウト作成手段11eによる配置配線処理(ステップ#30)が終了すると、レイアウトデータ出力手段11fが、レイアウト作成手段11eによって作成されたレイアウトデータを出力し(ステップ#40)、処理を終了する。

【0060】

〈別実施形態〉

〈1〉上記実施形態では、レイアウト条件として、2つの特殊レイヤ領域の間の距離範囲を規定したが、これに限るものではない。第1判定手段11dによって第1判定条件を満たすと判定されたESD保護素子と他の素子の間の距離範囲を設定するように構成しても良い。距離範囲は、寄生バイポーラが発生しない十分な距離に設定する。この場合には、第1判定手段11dは、特殊レイヤ領域を発生させる必要がなくなる。

【0061】

〈2〉上記実施形態において、レイアウト条件が、配線処理において、外部端子とESD保護素子を直接的に接続する配線とその他の配線の重なりを禁止する重なり禁止条件を含むように構成しても良い。

【0062】

具体的には、図10(a)に示すような、外部端子T1とESD保護素子を直接的に接続する配線NET1がある場合、他の配線NETXの重なりを禁止するために、ステップ#20において、重なり禁止条件情報を回路図データに記憶する。図10(b)は、重なり禁止条件情報の一例を示しており、端子名、配線名、及び、特殊レイヤIDを記載した重なり禁止条件情報を記憶している。尚、重なり禁止条件情報は、回路図データではなく外部ファイルに記憶するように構成しても良い。

【0063】

この場合、レイアウト手段による配置配線処理(ステップ#30)の配線処理において、重なり禁止条件が満たされているか否かを判定し、外部端子とESD保護素子を直接的に接続する配線に他の配線が重なっている場合には、外部端子とESD保護素子を直接的に接続する配線に他の配線が重ならないように、再度、配線処理を行う。

【0064】

〈3〉上記実施形態では、第1判定処理において、ESD保護素子と他の素子の端子関係、即ち、ESD保護素子同士の端子関係、及び、ESD保護素子と内部素子との端子関係を判定したが、内部素子同士の端子関係についても第1判定処理を行うように構成し、第1判定条件を満たす内部素子について特殊レイヤ領域を設定するように構成しても良い。また、この場合において、レイアウト条件は、2つの特殊レイヤ領域の間の距離範囲ではなく、2つの内部素子の間の距離範囲を設定しても良い。

【符号の説明】

【0065】

1 本発明に係るESD保護検証装置

11 演算処理手段

11a 回路図データ取得手段

11b 外部端子抽出手段

11c ESD保護素子抽出手段

11d 第1判定手段

11e レイアウト作成手段

11f レイアウトデータ出力手段

11g 第2判定手段

11h 第3判定手段

12 記憶手段

12a 回路図データ記憶部

12b レイアウトデータ記憶部

12c 判定条件テーブル記憶部

12d ESDライブラリ

12e セルライブラリ

【技術分野】

【0001】

本発明は、適切な耐性を備えるESD保護素子の適切な配置を支援するためのレイアウトシステムに関する。

【背景技術】

【0002】

半導体装置では、人体や他の外部装置等の静電気帯電物体から放電された静電気が、外部端子を通じて内部回路を破損させることがある。このため、半導体装置では、放電された静電気から内部回路を保護するために、例えば、ESD(Electro Static Discharge)保護素子を外部端子と内部回路を結ぶ配線上に配置している。

【0003】

ESD保護素子は、例えば、外部端子である入出力端子と電源端子の間、或いは、入出力端子とGND端子間に接続されており、外部端子に放電された静電気を、電源端子やGND端子にバイパスさせ、内部回路に静電気が放電されるのを防止している。このように構成することにより、半導体装置の内部回路は、静電気の放電による破壊から保護されることになる。

【0004】

ESD保護素子の配置に関する技術としては、例えば、回路図データから、外部端子別に、当該外部端子に直接接続される素子を抽出し、抽出された素子にESD保護素子が含まれるか否かを判定する検証装置がある(例えば、特許文献1参照)。当該検証装置を用いれば、外部端子の夫々にESD保護素子が設けられているか否かを判定することができるので、ESD保護素子の配置し忘れを防止できる。

【0005】

尚、ESD保護素子を有効に働かせる為には、ESD保護素子が正しく接続されていること、及び、ESD保護素子が必要な耐性を備えていることが重要である。必要な耐性を備えるESD保護素子の配置には、例えば、実績のあるESD保護素子の再利用やESD保護素子の自動生成が有効である。更に、ESD保護素子が正しく接続され必要な耐性を備えているかを検証することが重要である。

【0006】

ESD保護素子が正しく接続され必要な耐性を備えているかを検証するための技術としては、例えば、レイアウトデータの作成後に、当該レイアウトデータに基づいて、ESD保護素子を抽出し、ESD保護素子と周辺素子及び外部端子との接続関係を検証し、ESD保護素子の寸法が適切であるか否かを検証する検証装置がある(例えば、特許文献2参照)。当該検証装置を用いれば、ESD保護素子が正しく接続されているか、及び、ESD保護素子が適切な耐性(寸法)を備えているかを判定できる。

【0007】

ところで、半導体装置では、レイアウトの配置配線処理を実行した後、ESD保護素子の配置によっては、意図しない寄生バイポーラが生成されることがある。寄生バイポーラが生成されると、静電気が、ESD保護素子ではなく、意図せずに形成された寄生バイポーラからなるESDサージ経路に流入して、ESD破壊が発生する可能性がある。尚、ESD保護素子の配置により偶発的に生成される寄生バイポーラについては、ESD保護素子の配置処理後まで生成されるか否かが分からないことから、従来は、配置配線処理後のレイアウトデータに対し、寄生バイポーラが生成されているか否かを検証している。

【0008】

寄生バイポーラの検証技術としては、例えば、レイアウトデータから寄生バイポーラを抽出し、デバイスシミュレータを用いて寄生バイポーラの回路パラメータを抽出し、当該回路パラメータを用いて回路シミュレータ(例えば、SPICE)により動作検証を行う検証装置がある(例えば、特許文献3参照)。

【0009】

この検証装置では、回路シミュレータにより動作検証を行うので、静電気放電による誤動作等を検証でき、ESD破壊が発生するのを効果的に防止できる。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2005−50209号公報

【特許文献2】特開平7−65043号公報

【特許文献3】特開2006−134955号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかしながら、上述した検証装置では、レイアウトにおける配置配線処理の実行後に、レイアウトデータに基づいて寄生バイポーラの検証を行っていることから、寄生バイポーラが生成されている場合には、寄生バイポーラに係る素子の配置修正処理を行い、再度、寄生バイポーラの検証を行う必要がある。即ち、寄生バイポーラが生成されなくなるまで、繰り返し配置修正処理と寄生バイポーラの検証を行う必要がある。

【0012】

ここで、配置配線処理後の配置修正処理は、非常に手間と時間のかかる作業であることから、繰り返し配置修正処理が実行されると、開発遅延等を引き起こす可能性があった。

【0013】

本発明は上記の問題に鑑みてなされたものであり、その目的は、レイアウトデータの生成後にESD検証を行うことによるレイアウトのやり直しを低減して、寄生バイポーラの生成を抑制しつつ、開発遅延を効果的に防止できるESD保護検証装置を提供する点にある。

【課題を解決するための手段】

【0014】

上記目的を達成するための本発明に係るESD保護検証装置は、レイアウトデータの生成に用いられる回路図データを受け付ける回路図データ取得手段と、前記回路図データから、外部端子を抽出する外部端子抽出手段と、前記回路図データから、抽出された前記外部端子に接続されたESD保護素子を抽出するESD保護素子抽出手段と、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、前記ESD保護素子抽出手段によって抽出された前記ESD保護素子の夫々について、前記第1判定条件を満たすか否かを判定する第1判定処理を実行し、前記第1判定条件を満たす前記ESD保護素子を対象素子として設定する第1判定手段と、前記回路図データに対する配置配線処理において、前記対象素子の夫々について、前記寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように前記対象素子の配置処理を実行して、前記レイアウトデータを作成するレイアウト作成手段と、前記レイアウト作成手段によって作成された前記レイアウトデータを出力するレイアウトデータ出力手段と、を備えることを第1の特徴とする。

【0015】

更に好ましくは、上記特徴のESD保護検証装置は、前記レイアウト作成手段が、前記対象素子の配置処理として、前記対象素子を所定位置に配置する第1副配置処理と、前記対象素子が前記レイアウト条件を満たすか否かを判定するレイアウト条件判定処理と、前記レイアウト条件判定処理において、前記レイアウト条件を満たさないと判定された場合に、前記対象素子を以前に実行された前記副配置処理とは異なる位置に配置する第2副配置処理と、を実行可能に構成され、前記レイアウト条件判定処理において、前記レイアウト条件を満たすと判定されるまで、前記第2副配置処理及び前記レイアウト条件判定処理を繰り返し実行する。

【0016】

更に好ましくは、上記特徴のESD保護検証装置は、前記第1判定手段が、前記第1判定処理の実行後、前記対象素子を構成するレイヤ領域の内、前記寄生バイポーラを構成する可能性のある前記レイヤ領域を特殊レイヤ領域として設定する。

【0017】

更に好ましくは、上記特徴のESD保護検証装置は、前記寄生バイポーラの発生する可能性のある2つの素子間の関係として、前記ESD保護素子の端子と他の素子の端子の端子関係を規定した判定条件テーブルを備え、前記第1判定手段が、前記第1判定処理において、前記ESD保護素子抽出手段によって抽出された前記ESD保護素子の夫々について、当該ESD保護素子と他の素子の関係が前記判定条件テーブルに規定された端子関係の何れかに合致する場合に、前記第1判定条件を満たすと判定し、前記ESD保護素子の寄生バイポーラを構成する可能性のある端子を構成する前記レイヤ領域、及び、前記他の素子の寄生バイポーラを構成する可能性のある端子を構成する前記レイヤ領域を前記特殊レイヤ領域として設定する。

【0018】

更に好ましくは、上記特徴のESD保護検証装置は、前記レイアウト条件が、前記寄生バイポーラを構成する可能性のある2つの前記特殊レイヤ領域の間の距離範囲を規定する第1距離条件を含む。

【0019】

更に好ましくは、上記第1の特徴のESD保護検証装置は、前記寄生バイポーラの発生する可能性のある2つの素子間の関係として、前記ESD保護素子の端子と他の素子の端子の端子関係を規定した判定条件テーブルを備え、前記第1判定手段が、前記第1判定処理において、前記ESD保護素子抽出手段によって抽出された前記ESD保護素子の夫々について、当該ESD保護素子と他の素子の関係が前記判定条件テーブルに規定された端子関係の何れかに合致する場合に、前記第1判定条件を満たすと判定する。

【0020】

更に好ましくは、上記特徴のESD保護検証装置は、前記レイアウト条件が、前記ESD保護素子と他の前記素子の間の距離範囲を規定する第2距離条件を含む。

【0021】

更に好ましくは、上記何れかの特徴のESD保護検証装置は、前記レイアウト条件が、配線処理において、前記外部端子と前記ESD保護素子を直接的に接続する配線とその他の配線の重なりを禁止する重なり禁止条件を含む。

【0022】

更に好ましくは、上記何れかの特徴のESD保護検証装置は、前記ESD保護素子抽出手段による前記ESD保護素子の抽出後、前記外部端子抽出手段により抽出された前記外部端子の全てに前記ESD保護素子が接続されているか否かを判定する第2判定手段と、前記ESD保護素子抽出手段によって抽出された前記ESD保護素子別に、前記ESD保護素子の耐圧情報を取得し、前記ESD保護素子の接続された前記外部端子にかかる電圧情報を取得し、前記耐圧情報と前記電圧情報に基づいて前記ESD保護素子が適切であるか否かを判定する第3判定手段と、を備え、前記第1判定手段が、前記第2判定手段により前記外部端子の全てに前記ESD保護素子が接続されていると判定され、且つ、前記第3判定手段により前記ESD保護素子の全てについて適切であると判定された場合に、前記第1判定処理を実行する。

【発明の効果】

【0023】

上記特徴のESD保護検証装置によれば、第1判定手段が、レイアウト実行前の回路図データから寄生バイポーラが発生する可能性のある対象素子を抽出し、レイアウト作成手段が、対象素子の配置処理毎に、当該対象素子の配置により寄生バイポーラが発生しないようにレイアウトを行う、即ち、配置配線処理の終了後ではなく、配置配線処理中に、配置修正を行うので、開発時間の増大を抑制できる。

【0024】

具体的には、配置配線処理後に配置修正処理を行う場合、特に、面積に余裕がない半導体装置では、配置修正処理にかかるスペースを確保することが難しく、対象素子以外の素子を含めて大規模な修正が必要になる場合がある。これに対し、上記特徴のESD保護検証装置によれば、第1判定手段により寄生バイポーラが発生する可能性のある対象素子を予め特定しておき、寄生バイポーラが生成されないように対象素子の配置処理を行うので、配置配線処理後の配置修正処理のような大幅な修正処理が必要なくなり、開発時間の増大を効果的に抑制できる。

【図面の簡単な説明】

【0025】

【図1】本発明に係るESD保護検証装置の概略構成例を示す概略ブロック図である。

【図2】本発明に係るESD保護検証装置の処理動作を示すフローチャートである。

【図3】本発明に係るESD保護検証装置で用いる回路図データの一例を示す図である。

【図4】本発明に係るESD保護検証装置で用いる回路図データの構造例を示す概略ブロック図である。

【図5】SPICEネットリストの読み込み処理を示すフローチャートである。

【図6】ESD保護素子の構成の一例を示す概略回路図である。

【図7】本発明に係るESD保護検証装置で用いる判定条件テーブルの一例を示す表である。

【図8】本発明に係るESD保護検証装置で用いる特殊レイヤ情報の一例を示す表である。

【図9】寄生バイポーラが発生する可能性のある特殊レイヤ領域の一例とその条件を模式的に示す概略ブロック図である。

【図10】外部端子とESD保護素子を直接的に接続する配線とその他の配線の重なりの例と、当該重なりを禁止する重なり禁止条件を示す図である。

【発明を実施するための形態】

【0026】

以下、本発明に係るESD保護検証装置(以下、適宜「本発明装置」と略称する)の実施形態を図面に基づいて説明する。

【0027】

本発明装置の実施形態について、図1〜図9を基に説明する。

【0028】

先ず、本発明装置1の構成について、図1を基に説明する。

【0029】

図1に示すように、本発明装置1は、コンピュータ処理によりレイアウトの配置配線処理等を実行する演算処理手段11と、ハードディスク等の不揮発性記憶装置及び演算処理手段11における演算結果や各種DBから取得した情報を一時的に記憶するRAM等で構成される記憶手段12を備えて構成されている。

【0030】

記憶手段12は、回路図データとして、SPICE形式のネットリストを記憶する回路図データ記憶部12a、本発明装置1によって作成されるレイアウトデータを記憶するレイアウトデータ記憶部12b、寄生バイポーラの発生する可能性のある2つの素子間の関係として、ESD保護素子の端子と他の素子の端子の端子関係を規定した判定条件テーブルを記憶する判定条件テーブル記憶部12c、過去に使用実績があるESD保護素子のレイアウトデータを記憶したESDライブラリ12d、及び、各素子のレイアウトデータを記憶したセルライブラリ12eを備えて構成されている。尚、本実施形態では、SPICE形式のネットリストを用いる場合について説明するが、これに限るものではなく、レイアウトデータの生成に用いられる回路図データであればよい。

【0031】

本実施形態では、回路図データとしてのネットリストには、トランジスタや容量素子、抵抗素子等の各素子について、各端子に接続される配線を示す接続情報や素子寸法、耐圧情報等の素子情報が記載されている。更に、外部端子について、接続される配線を示す接続情報や印加電圧の電圧値を示す電圧情報等の端子情報が記載されている。尚、本実施形態では、ネットリストに素子情報や端子情報が含まれる場合を想定しているが、これらの情報については、素子情報及び端子情報を記憶した外部ファイルを用意しておき、当該外部ファイルを利用するように構成しても良い。

【0032】

演算処理手段11は、レイアウトデータの生成に用いられる回路図データを受け付ける回路図データ取得手段11aと、回路図データから、外部端子を抽出する外部端子抽出手段11bと、回路図データから、抽出された外部端子に接続されたESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、ESD保護素子抽出手段11cによって抽出されたESD保護素子の夫々について、第1判定条件を満たすか否かを判定する第1判定処理を実行し、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、回路図データに対する配置配線処理において、対象素子の夫々について、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウト作成手段11eによって作成されたレイアウトデータを出力するレイアウトデータ出力手段11fと、を備えている。本実施形態では、回路図データ取得手段11a、外部端子抽出手段11b、ESD保護素子抽出手段11c、第1判定手段11d、レイアウト作成手段11e、及び、レイアウトデータ出力手段11fは、各手段を実現するソフトウェアで構成されている。

【0033】

本実施形態の演算処理手段11は、更に、ESD保護素子抽出手段11cによるESD保護素子の抽出後、外部端子抽出手段11bにより抽出された外部端子の全てにESD保護素子が接続されているか否かを判定する第2判定手段11gと、ESD保護素子抽出手段11cによって抽出されたESD保護素子別に、ESD保護素子の耐圧情報を取得し、ESD保護素子の接続された外部端子にかかる電圧情報を取得し、耐圧情報と電圧情報に基づいてESD保護素子が適切であるか否かを判定する第3判定手段11hと、を備えている。

【0034】

尚、本実施形態では、第1判定手段11dが、第1判定処理の実行後、対象素子を構成するレイヤ領域の内、寄生バイポーラを構成する可能性のあるレイヤ領域を特殊レイヤ領域として設定するように構成されている。

【0035】

また、本実施形態では、レイアウト作成手段11eは、市販のレイアウトツールであるネットドリブンエディタ及びリアルタイムDRC、例えば、Cadence社のVirtuosoXL及びDRDや、ジーダット社のismo及びiDRC等を利用して構成されている。尚、利用する市販ツールはこれらに限られるものではなく、本発明装置1が配置配線処理を実行する機能を備えていても良い。レイアウト作成手段11eは、回路図データの素子情報及び端子情報に基づいて、回路を構成する素子の夫々について、対応するレイアウトデータをセルライブラリ12eから取得し、レイヤ領域の追加や変形などを適宜実行しながら配置する配線処理と、配線を引く配線処理とを実行する。

【0036】

次に、本発明装置1の処理動作について、図2〜図9を基に説明する。ここで、図2は、本発明装置1の処理動作を示すフローチャートである。

【0037】

本発明装置1は、先ず、回路図データにおいて適切なESD保護素子が正しく接続されているかを検証する回路図データ検証処理(ステップ#10)を実行する。

【0038】

具体的には、先ず、回路図データ取得手段11aが、回路図データとして、SPICE形式のネットリスト等、トランジスタレベルのネットリストを受け付け、記憶手段12に記憶する(ステップ#11)。尚、本実施形態では、回路図データ取得手段11aが、回路図作成装置から回路図データを取得する場合を想定しているが、これに限るものではない。

【0039】

ここで、図3は、SPICEネットリストの記述例を、図4は、図3に示すSPICEネットリストの階層構造を示している。本実施形態では、ネットリストが階層構造を有している場合を想定しており、最上位階層TOP内に、内部回路BLOCKA、BLOCKBが構成されている。最上位階層TOPの端子T1〜Tnは外部端子であり、内部回路BLOCKAの端子TA1〜TAi、内部回路BLOCKBの端子TB1〜TBjは内部端子である。ESD保護素子抽出手段11cは、図3及び図4のネットリストでは、外部端子T1から引かれている配線に接続されているESD保護素子M1、M2、外部端子T2から引かれている配線に接続されているESD保護素子M3、M4等、最上位階層TOPだけでなく下位階層である内部回路BLOCKA、BLOCKBにある全てのESD保護素子を抽出する。本実施形態では、ESD保護素子抽出手段11cは、更に、図3に示す回路図データから、抽出されたESD保護素子の素子情報を取得する。

【0040】

図5(a)は、回路図データの一例であるSPICEネットリストの読み込み処理を示すフローチャートである。本実施形態の回路図データ取得手段11aは、ネットリストとしてSPICEネットリストを受け付けた場合、先ず、ファイルを開き(ステップ#101)、先頭行から一行ずつ読み込む(ステップ#102)。読み込んだ行が最終行の場合は処理を終了する(ステップ#102でYES分岐)。

【0041】

最終行ではない場合(ステップ#102でNO分岐)、先頭ワードが“.SUBCKT”の場合は(ステップ#103で.SUBCKT分岐)、SUBCKTをセットし(ステップ#104)、SUBCKTテーブルを作成する。SUBCKTテーブルには、図5(b)に示すように、名称情報Name及びピン情報Termが記憶される。ステップ#103において、先頭ワードがMQDRCの何れかである場合は(ステップ#103で素子分岐)、素子テーブルを作成し(ステップ#105)、SUBCKTテーブルに名称Instanceを記憶する(ステップ#106)。素子テーブルには、名称Name(SUBCKTテーブルのInstance)、ピン情報Term、素子属性Property、登録されているSUBCKT情報Subcktを記憶する。ステップ#103において、先頭ワードが“.END”である場合は(ステップ#103でEND分岐)、SUBCKTを解除する(ステップ#107)。尚、図5(a)では明記していないが、先頭ワードがV、Iで始まるSPICE用信号源、或いは、“.OPT”等のSPICE専用文や注釈行については、ステップ#103で省く処理を行っている。

【0042】

続いて、図2に示すように、外部端子抽出手段11bが、回路図データから、外部端子を抽出し、外部端子の端子情報を取得する(ステップ#12)。更に、ESD保護素子抽出手段11cが、回路図データから、抽出された外部端子に接続されたESD保護素子を抽出する(ステップ#13)。

【0043】

引き続き、本発明装置1の第2判定手段11gが、回路図データの接続情報に基づいて、外部端子の全てにESD保護素子が接続されているか否かを検証する(ステップ#14)。第2判定手段11gは、全ての外部端子にESD保護素子が接続されていない場合(ステップ#14でNO分岐)、エラーを出力し、処理を終了する(ステップ#17)。

【0044】

ステップ#14において、全ての外部端子にESD保護素子が接続されていると判定された場合は(ステップ#14でYES分岐)、本発明装置1の第3判定手段11hが、ESD保護素子別に、回路図データから、ESD保護素子の耐圧情報とESD保護素子の接続された外部端子の電圧情報を取得し、取得した耐圧情報と電圧情報に基づいてESD保護素子が適切であるか否かを検証する(ステップ#15)。尚、ここでは、ESD保護素子は、低耐圧、中耐圧、高耐圧の3種類が用意されている。本実施形態では、第3判定手段11hは、回路図データに与えられた情報から電圧情報を取得し、当該電圧情報から必要な素子寸法を求め、接続されているESD保護素子の寸法が必要な素子寸法を備えているかを判定する。第3判定手段11hは、必要な素子寸法を備えていないESD保護素子がある場合は(ステップ#15でNG分岐)、エラーを出力し、処理を終了する(ステップ#17)。

【0045】

ステップ#15において、全てのESD保護素子が適切な素子寸法を備えていると判定された場合は(ステップ#15でOK分岐)、本発明装置1は、ESD保護素子が正しく接続されているか否かを検証する(ステップ#16)。ここで、図6は、ESD保護素子の接続構成の例を示している。本発明装置1は、接続誤りのあるESD保護素子がある場合は(ステップ#16でNG分岐)、エラーを出力し、処理を終了する(ステップ#17)。

【0046】

ステップ#14において、第2判定手段11gにより外部端子の全てにESD保護素子が接続されていると判定され、且つ、ステップ#15において、第3判定手段11hによりESD保護素子の全てについて適切であると判定され、更に、ステップ#16において、ESD保護素子の接続構成が正しいと判定されると、本発明装置1は、図2に示すように、寄生バイポーラが発生する可能性のあるESD保護素子のレイヤ領域を特定する前処理を行う(ステップ#20)。

【0047】

具体的には、先ず、本発明装置1は、ESD保護素子について、後述する配置配線処理(ステップ#30)において使用するレイアウトセルをESDライブラリ12dから選択する(ステップ#21)。

【0048】

引き続き、第1判定手段11dが、第1判定処理において、ESD保護素子抽出手段11cによって抽出されたESD保護素子の夫々について、当該ESD保護素子と他の素子の関係が判定条件テーブルに規定された端子関係の何れかに合致する場合に、第1判定条件を満たすと判定して対象素子として設定し、ESD保護素子の寄生バイポーラを構成する可能性のある端子を構成するレイヤ領域、及び、他の素子の寄生バイポーラを構成する可能性のある端子を構成するレイヤ領域を特殊レイヤ領域として設定する(ステップ#22)。

【0049】

ここで、図7は、判定条件テーブルの一例を示しており、2つのMOSトランジスタの端子関係を示している。図7において、Dはドレイン端子、Gはゲート端子、Sはソース端子、Bはバックゲート端子であり、“○”は、近接配置された場合に寄生バイポーラが発生する可能性のある端子を示している。例えば、図7では、検証対象のESD保護素子と他の素子が何れも5V−NMOSである場合、ESD保護素子のドレイン端子と他の素子のドレイン端子は、近接配置されると寄生バイポーラが発生する可能性があるとしている。従って、検証対象のESD保護素子と他の素子が何れも5V−NMOSの場合、検証対象のESD保護素子のドレイン端子を構成するレイヤ領域と他の素子のドレイン端子を構成するレイヤ領域を特殊レイヤ領域として設定する。

【0050】

更に、第1判定手段11dは、設定した特殊レイヤ領域を特定するための特殊レイヤ情報を回路図データに書き込む(ステップ#23)。尚、本実施形態では、特殊レイヤ情報を回路図データに書き込む場合について説明するが、他のファイルに書き込むように構成しても良い。ここで、図8は、回路図データに書き込む特殊レイヤ情報の一例を示しており、ESD保護素子のインスタンス名、特殊レイヤID、ステップ#21で選択したレイアウトセルを特定するためのレイアウトセル情報、及び、特殊レイヤ領域を特定するための情報が記載されている。尚、図8では、特殊レイヤ領域を特定するための情報は、レイアウトセル内における特殊レイヤ領域の位置であり、レイアウトセルの原点からの座標で示されている。

【0051】

続いて、配置配線処理(ステップ#30)を行う。

【0052】

配置処理において、特殊レイヤ領域を備える対象素子の配置処理を行う場合(ステップ#31でYES分岐)、本発明装置1のレイアウト作成手段11eは、先ず、対象素子を所定位置に配置する第1副配置処理を実行する(ステップ#32)。

【0053】

第1副配置処理では、ステップ#21において回路図データに記憶したセル情報に基づいて、ESDライブラリ12dからレイアウトセルを取得し、ステップ#23で設定した特殊レイヤ領域の情報を取得する。これにより、ESD保護素子のレイアウト構造が決定される。レイアウト作成手段11eは、ESD保護素子を、決定されたレイアウト構造でチップ上に配置する。

【0054】

引き続き、レイアウト作成手段11eは、対象素子がレイアウト条件を満たすか否かを判定するレイアウト条件判定処理を実行する(ステップ#33)。尚、レイアウト条件は、寄生バイポーラを構成する可能性のある2つの特殊レイヤ領域の間の距離範囲を規定する第1距離条件を想定している。

【0055】

ここで、図9は、寄生バイポーラが発生する可能性のある特殊レイヤ領域が設定されたESD保護素子の例を示している。ここでは、同一のPウェルに形成されるN型拡散層N1及びN型拡散層N2が特殊レイヤ領域として設定されており、特殊レイヤ領域N1と特殊レイヤ領域N2の最短距離が第1距離条件で示す距離範囲内の場合は、レイアウト条件を満たさないと判定し、N型拡散層N1及びN型拡散層N2の間の最短距離が第1距離条件で示す距離範囲外の場合は、レイアウト条件を満たすと判定する。2つの特殊レイヤ領域の間の距離を、第1距離条件で示す距離範囲より大きくすることで、寄生バイポーラ素子を形成する可能性のある特殊レイヤ領域同士の近接配置が少なくなり、寄生バイポーラの生成を抑制できる。寄生バイポーラが発生し難い条件で配置処理を行うことから、寄生バイポーラの発生を効果的に防止して、寄生バイポーラの発生による配置配線終了後の配置修正処理を実行しないか実行回数を少なくすることができる。

【0056】

レイアウト作成手段11eは、レイアウト条件判定処理において、レイアウト条件を満たさないと判定された場合(ステップ#33でNG分岐)、対象素子の再配置を行う第2副配置処理(ステップ#32)を実行する。尚、レイアウト作成手段11eは、対象素子の配置処理が終了するまで、対象素子の副配置処理の実行結果を記憶しておき、各副配置処理において異なる位置に配置されるようにする。

【0057】

レイアウト作成手段11eは、レイアウト条件判定処理(ステップ#33)において、レイアウト条件を満たすと判定された場合(ステップ#33でOK分岐)、対象素子の配置処理を終了する。

【0058】

レイアウト作成手段11eは、配置処理において、対象素子以外の素子については(ステップ#31でYES分岐)、通常の配置処理を実行する(ステップ#34)。

【0059】

レイアウト作成手段11eによる配置配線処理(ステップ#30)が終了すると、レイアウトデータ出力手段11fが、レイアウト作成手段11eによって作成されたレイアウトデータを出力し(ステップ#40)、処理を終了する。

【0060】

〈別実施形態〉

〈1〉上記実施形態では、レイアウト条件として、2つの特殊レイヤ領域の間の距離範囲を規定したが、これに限るものではない。第1判定手段11dによって第1判定条件を満たすと判定されたESD保護素子と他の素子の間の距離範囲を設定するように構成しても良い。距離範囲は、寄生バイポーラが発生しない十分な距離に設定する。この場合には、第1判定手段11dは、特殊レイヤ領域を発生させる必要がなくなる。

【0061】

〈2〉上記実施形態において、レイアウト条件が、配線処理において、外部端子とESD保護素子を直接的に接続する配線とその他の配線の重なりを禁止する重なり禁止条件を含むように構成しても良い。

【0062】

具体的には、図10(a)に示すような、外部端子T1とESD保護素子を直接的に接続する配線NET1がある場合、他の配線NETXの重なりを禁止するために、ステップ#20において、重なり禁止条件情報を回路図データに記憶する。図10(b)は、重なり禁止条件情報の一例を示しており、端子名、配線名、及び、特殊レイヤIDを記載した重なり禁止条件情報を記憶している。尚、重なり禁止条件情報は、回路図データではなく外部ファイルに記憶するように構成しても良い。

【0063】

この場合、レイアウト手段による配置配線処理(ステップ#30)の配線処理において、重なり禁止条件が満たされているか否かを判定し、外部端子とESD保護素子を直接的に接続する配線に他の配線が重なっている場合には、外部端子とESD保護素子を直接的に接続する配線に他の配線が重ならないように、再度、配線処理を行う。

【0064】

〈3〉上記実施形態では、第1判定処理において、ESD保護素子と他の素子の端子関係、即ち、ESD保護素子同士の端子関係、及び、ESD保護素子と内部素子との端子関係を判定したが、内部素子同士の端子関係についても第1判定処理を行うように構成し、第1判定条件を満たす内部素子について特殊レイヤ領域を設定するように構成しても良い。また、この場合において、レイアウト条件は、2つの特殊レイヤ領域の間の距離範囲ではなく、2つの内部素子の間の距離範囲を設定しても良い。

【符号の説明】

【0065】

1 本発明に係るESD保護検証装置

11 演算処理手段

11a 回路図データ取得手段

11b 外部端子抽出手段

11c ESD保護素子抽出手段

11d 第1判定手段

11e レイアウト作成手段

11f レイアウトデータ出力手段

11g 第2判定手段

11h 第3判定手段

12 記憶手段

12a 回路図データ記憶部

12b レイアウトデータ記憶部

12c 判定条件テーブル記憶部

12d ESDライブラリ

12e セルライブラリ

【特許請求の範囲】

【請求項1】

レイアウトデータの生成に用いられる回路図データを受け付ける回路図データ取得手段と、

前記回路図データから、外部端子を抽出する外部端子抽出手段と、

前記回路図データから、抽出された前記外部端子に接続されたESD保護素子を抽出するESD保護素子抽出手段と、

寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、前記ESD保護素子抽出手段によって抽出された前記ESD保護素子の夫々について、前記第1判定条件を満たすか否かを判定する第1判定処理を実行し、前記第1判定条件を満たす前記ESD保護素子を対象素子として設定する第1判定手段と、

前記回路図データに対する配置配線処理において、前記対象素子の夫々について、前記寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように前記対象素子の配置処理を実行して、前記レイアウトデータを作成するレイアウト作成手段と、

前記レイアウト作成手段によって作成された前記レイアウトデータを出力するレイアウトデータ出力手段と、を備えることを特徴とするESD保護検証装置。

【請求項2】

前記レイアウト作成手段が、前記対象素子の配置処理として、

前記対象素子を所定位置に配置する第1副配置処理と、

前記対象素子が前記レイアウト条件を満たすか否かを判定するレイアウト条件判定処理と、

前記レイアウト条件判定処理において、前記レイアウト条件を満たさないと判定された場合に、前記対象素子を以前に実行された前記副配置処理とは異なる位置に配置する第2副配置処理と、を実行可能に構成され、前記レイアウト条件判定処理において、前記レイアウト条件を満たすと判定されるまで、前記第2副配置処理及び前記レイアウト条件判定処理を繰り返し実行することを特徴とする請求項1に記載のESD保護検証装置。

【請求項3】

前記第1判定手段が、前記第1判定処理の実行後、前記対象素子を構成するレイヤ領域の内、前記寄生バイポーラを構成する可能性のある前記レイヤ領域を特殊レイヤ領域として設定することを特徴とする請求項1または2に記載のESD保護検証装置。

【請求項4】

前記寄生バイポーラの発生する可能性のある2つの素子間の関係として、前記ESD保護素子の端子と他の素子の端子の端子関係を規定した判定条件テーブルを備え、

前記第1判定手段が、前記第1判定処理において、前記ESD保護素子抽出手段によって抽出された前記ESD保護素子の夫々について、当該ESD保護素子と他の素子の関係が前記判定条件テーブルに規定された端子関係の何れかに合致する場合に、前記第1判定条件を満たすと判定し、前記ESD保護素子の寄生バイポーラを構成する可能性のある端子を構成する前記レイヤ領域、及び、前記他の素子の寄生バイポーラを構成する可能性のある端子を構成する前記レイヤ領域を前記特殊レイヤ領域として設定することを特徴とする請求項3に記載のESD保護検証装置。

【請求項5】

前記レイアウト条件が、前記寄生バイポーラを構成する可能性のある2つの前記特殊レイヤ領域の間の距離範囲を規定する第1距離条件を含むことを特徴とする請求項3または4に記載のESD保護検証装置。

【請求項6】

前記寄生バイポーラの発生する可能性のある2つの素子間の関係として、前記ESD保護素子の端子と他の素子の端子の端子関係を規定した判定条件テーブルを備え、

前記第1判定手段が、前記第1判定処理において、前記ESD保護素子抽出手段によって抽出された前記ESD保護素子の夫々について、当該ESD保護素子と他の素子の関係が前記判定条件テーブルに規定された端子関係の何れかに合致する場合に、前記第1判定条件を満たすと判定することを特徴とする請求項1に記載のESD保護検証装置。

【請求項7】

前記レイアウト条件が、前記ESD保護素子と他の前記素子の間の距離範囲を規定する第2距離条件を含むことを特徴とする請求項1または6に記載のESD保護検証装置。

【請求項8】

前記レイアウト条件が、配線処理において、前記外部端子と前記ESD保護素子を直接的に接続する配線とその他の配線の重なりを禁止する重なり禁止条件を含むことを特徴とする請求項1〜7の何れか1項に記載のESD保護検証装置。

【請求項9】

前記ESD保護素子抽出手段による前記ESD保護素子の抽出後、前記外部端子抽出手段により抽出された前記外部端子の全てに前記ESD保護素子が接続されているか否かを判定する第2判定手段と、

前記ESD保護素子抽出手段によって抽出された前記ESD保護素子別に、前記ESD保護素子の耐圧情報を取得し、前記ESD保護素子の接続された前記外部端子にかかる電圧情報を取得し、前記耐圧情報と前記電圧情報に基づいて前記ESD保護素子が適切であるか否かを判定する第3判定手段と、を備え、

前記第1判定手段が、前記第2判定手段により前記外部端子の全てに前記ESD保護素子が接続されていると判定され、且つ、前記第3判定手段により前記ESD保護素子の全てについて適切であると判定された場合に、前記第1判定処理を実行することを特徴とする請求項1〜8の何れか1項に記載のESD保護検証装置。

【請求項1】

レイアウトデータの生成に用いられる回路図データを受け付ける回路図データ取得手段と、

前記回路図データから、外部端子を抽出する外部端子抽出手段と、

前記回路図データから、抽出された前記外部端子に接続されたESD保護素子を抽出するESD保護素子抽出手段と、

寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、前記ESD保護素子抽出手段によって抽出された前記ESD保護素子の夫々について、前記第1判定条件を満たすか否かを判定する第1判定処理を実行し、前記第1判定条件を満たす前記ESD保護素子を対象素子として設定する第1判定手段と、

前記回路図データに対する配置配線処理において、前記対象素子の夫々について、前記寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように前記対象素子の配置処理を実行して、前記レイアウトデータを作成するレイアウト作成手段と、

前記レイアウト作成手段によって作成された前記レイアウトデータを出力するレイアウトデータ出力手段と、を備えることを特徴とするESD保護検証装置。

【請求項2】

前記レイアウト作成手段が、前記対象素子の配置処理として、

前記対象素子を所定位置に配置する第1副配置処理と、

前記対象素子が前記レイアウト条件を満たすか否かを判定するレイアウト条件判定処理と、

前記レイアウト条件判定処理において、前記レイアウト条件を満たさないと判定された場合に、前記対象素子を以前に実行された前記副配置処理とは異なる位置に配置する第2副配置処理と、を実行可能に構成され、前記レイアウト条件判定処理において、前記レイアウト条件を満たすと判定されるまで、前記第2副配置処理及び前記レイアウト条件判定処理を繰り返し実行することを特徴とする請求項1に記載のESD保護検証装置。

【請求項3】

前記第1判定手段が、前記第1判定処理の実行後、前記対象素子を構成するレイヤ領域の内、前記寄生バイポーラを構成する可能性のある前記レイヤ領域を特殊レイヤ領域として設定することを特徴とする請求項1または2に記載のESD保護検証装置。

【請求項4】

前記寄生バイポーラの発生する可能性のある2つの素子間の関係として、前記ESD保護素子の端子と他の素子の端子の端子関係を規定した判定条件テーブルを備え、

前記第1判定手段が、前記第1判定処理において、前記ESD保護素子抽出手段によって抽出された前記ESD保護素子の夫々について、当該ESD保護素子と他の素子の関係が前記判定条件テーブルに規定された端子関係の何れかに合致する場合に、前記第1判定条件を満たすと判定し、前記ESD保護素子の寄生バイポーラを構成する可能性のある端子を構成する前記レイヤ領域、及び、前記他の素子の寄生バイポーラを構成する可能性のある端子を構成する前記レイヤ領域を前記特殊レイヤ領域として設定することを特徴とする請求項3に記載のESD保護検証装置。

【請求項5】

前記レイアウト条件が、前記寄生バイポーラを構成する可能性のある2つの前記特殊レイヤ領域の間の距離範囲を規定する第1距離条件を含むことを特徴とする請求項3または4に記載のESD保護検証装置。

【請求項6】

前記寄生バイポーラの発生する可能性のある2つの素子間の関係として、前記ESD保護素子の端子と他の素子の端子の端子関係を規定した判定条件テーブルを備え、

前記第1判定手段が、前記第1判定処理において、前記ESD保護素子抽出手段によって抽出された前記ESD保護素子の夫々について、当該ESD保護素子と他の素子の関係が前記判定条件テーブルに規定された端子関係の何れかに合致する場合に、前記第1判定条件を満たすと判定することを特徴とする請求項1に記載のESD保護検証装置。

【請求項7】

前記レイアウト条件が、前記ESD保護素子と他の前記素子の間の距離範囲を規定する第2距離条件を含むことを特徴とする請求項1または6に記載のESD保護検証装置。

【請求項8】

前記レイアウト条件が、配線処理において、前記外部端子と前記ESD保護素子を直接的に接続する配線とその他の配線の重なりを禁止する重なり禁止条件を含むことを特徴とする請求項1〜7の何れか1項に記載のESD保護検証装置。

【請求項9】

前記ESD保護素子抽出手段による前記ESD保護素子の抽出後、前記外部端子抽出手段により抽出された前記外部端子の全てに前記ESD保護素子が接続されているか否かを判定する第2判定手段と、

前記ESD保護素子抽出手段によって抽出された前記ESD保護素子別に、前記ESD保護素子の耐圧情報を取得し、前記ESD保護素子の接続された前記外部端子にかかる電圧情報を取得し、前記耐圧情報と前記電圧情報に基づいて前記ESD保護素子が適切であるか否かを判定する第3判定手段と、を備え、

前記第1判定手段が、前記第2判定手段により前記外部端子の全てに前記ESD保護素子が接続されていると判定され、且つ、前記第3判定手段により前記ESD保護素子の全てについて適切であると判定された場合に、前記第1判定処理を実行することを特徴とする請求項1〜8の何れか1項に記載のESD保護検証装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−12096(P2013−12096A)

【公開日】平成25年1月17日(2013.1.17)

【国際特許分類】

【出願番号】特願2011−145068(P2011−145068)

【出願日】平成23年6月30日(2011.6.30)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成25年1月17日(2013.1.17)

【国際特許分類】

【出願日】平成23年6月30日(2011.6.30)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]