FFS方式液晶表示装置用アレイ基板及びその製造方法

【課題】画素の開口領域を最大化し、画素の透過率を向上させる、FFS方式液晶表示装置用アレイ基板及びその製造方法を提供する。

【解決手段】ゲート配線とデータ配線113aとの交差地点に形成された薄膜トランジスタTと、薄膜トランジスタTを含む基板101全面に形成され、薄膜トランジスタTを露出する開口部を備えた有機絶縁膜117の上部に形成された大面積の共通電極123aと、開口部から薄膜トランジスタTに接続された補助電極パターン123cと、共通電極123a及び補助電極パターン123cを含む基板101全面に形成され、薄膜トランジスタTに接続された補助電極パターン123cを露出するパッシベーション膜127の上部に形成され、露出した補助電極パターン123cを介して薄膜トランジスタTに電気的に接続され、共通電極123aとオーバーラップする複数の画素電極133aとを含む。

【解決手段】ゲート配線とデータ配線113aとの交差地点に形成された薄膜トランジスタTと、薄膜トランジスタTを含む基板101全面に形成され、薄膜トランジスタTを露出する開口部を備えた有機絶縁膜117の上部に形成された大面積の共通電極123aと、開口部から薄膜トランジスタTに接続された補助電極パターン123cと、共通電極123a及び補助電極パターン123cを含む基板101全面に形成され、薄膜トランジスタTに接続された補助電極パターン123cを露出するパッシベーション膜127の上部に形成され、露出した補助電極パターン123cを介して薄膜トランジスタTに電気的に接続され、共通電極123aとオーバーラップする複数の画素電極133aとを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶表示装置(Liquid Crystal Display Device)に関し、特に、FFS(Fringe Field Switching)方式液晶表示装置用アレイ基板及びその製造方法に関する。

【背景技術】

【0002】

一般に、液晶表示装置の駆動原理は、液晶の光学的異方性と分極特性を利用するものである。前記液晶は細長い構造であるので分子配列に方向性を有し、人為的に前記液晶に電場を印加することで分子配列の方向を制御することができる。

【0003】

つまり、前記液晶の分子配列の方向を任意に調節して前記液晶の分子配列を変化させると、光学的異方性により前記液晶の分子配列方向に光が屈折し、画像情報が表示される。

【0004】

近年、薄膜トランジスタと前記薄膜トランジスタに接続された画素電極とがマトリクス方式で配列されたアクティブマトリクス液晶表示装置(AM−LCD(Active Matrix LCD)、以下液晶表示装置という)が、解像度及び動画表示能力に優れており、最も注目されている。

【0005】

前記液晶表示装置は、共通電極が形成されたカラーフィルタ基板(すなわち、上部基板)と、画素電極が形成されたアレイ基板(すなわち、下部基板)と、上部基板と下部基板との間に充填された液晶とからなるが、このような液晶表示装置は、画素電極と共通電極が上下に印加される電場により液晶を駆動する方式であって、透過率や開口率などの特性に優れている。

【0006】

しかし、上下に印加される電場による液晶駆動方式は、視野角特性に優れていないという欠点があった。よって、上記欠点を克服するために新たに提案された技術が横電界による液晶駆動方式であるが、この横電界による液晶駆動方式は、視野角特性に優れているという利点を有する。

【0007】

このような横電界方式液晶表示装置は、カラーフィルタ基板とアレイ基板とが対向するように構成され、カラーフィルタ基板とアレイ基板との間に液晶層が介在している。

【0008】

前記アレイ基板は、透明な絶縁基板上に定義された複数の画素毎に設けられる薄膜トランジスタ、共通電極、及び画素電極から構成される。前記共通電極と前記画素電極とは、同一基板上に平行に離隔して構成される。

【0009】

また、前記カラーフィルタ基板は、透明な絶縁基板上に、ゲート配線、データ配線、及び薄膜トランジスタに対応する部分にブラックマトリクスが形成され、前記画素に対応する部分にカラーフィルタが形成される。

【0010】

さらに、前記液晶層は、前記共通電極と前記画素電極の水平電界により駆動される。

【0011】

通常、前記共通電極及び前記画素電極は、輝度を確保するために、透明電極で形成する。

【0012】

よって、このような輝度改善効果を最大化するために提案された技術がFFS技術である。前記FFS技術は、液晶を精密に制御することにより、色ずれ(color shift)がなく、高いコントラスト比が得られるという特徴がある。

【0013】

以下、このような従来のFFS方式液晶表示装置の製造方法について図5及び図6を参照して説明する。

【0014】

図5は従来のFFS方式液晶表示装置の概略平面図であり、図6は図5のII−II線断面図である。

【0015】

従来のFFS方式液晶表示装置用アレイ基板は、図5及び図6に示すように、透明な絶縁基板11上に一方向に延び、互いに平行に離隔した複数のゲート配線13と、ゲート配線13と交差し、その交差して形成される領域に画素領域を定義する複数のデータ配線21と、ゲート配線13とデータ配線21との交差地点に設けられ、ゲート配線13から垂直に延びたゲート電極13a、ゲート絶縁膜15、アクティブ層17、オーミックコンタクト層19、ソース電極21a、及びドレイン電極21bからなる薄膜トランジスタTと、薄膜トランジスタTを含む基板全面に形成された第1パッシベーション膜27と、第1パッシベーション膜27上に形成されて薄膜トランジスタTに接続された大面積の画素電極29と、画素電極29を含む第1パッシベーション膜27上に形成された第2パッシベーション膜31と、第2パッシベーション膜31上に互いに離隔して形成されて画素電極29に対応する複数の共通電極33とを含む。

【0016】

ここで、大面積の画素電極29は、ゲート配線13とデータ配線21とが交差して形成される画素領域に配置されている。

【0017】

また、共通電極33は、第2パッシベーション膜31を介して画素電極29とオーバーラップしている。ここで、画素電極29及び複数の共通電極33は、透明導電物質であるITO(Indium Tin Oxide)で形成される。

【0018】

また、画素電極29は、第1パッシベーション膜27の上部に形成されたドレインコンタクトホール27aを介してドレイン電極21bに電気的に接続される。

【0019】

さらに、画素電極29及び複数の共通電極33が形成された絶縁基板11と貼り合わせられるカラーフィルタ基板(図示せず)上には、カラーフィルタ層(図示せず)と、前記カラーフィルタ層間に配置されて光の透過を遮断するためのブラックマトリクス(図示せず)が積層されており、前記ブラックマトリクス及び前記カラーフィルタ層の上部には、これらブラックマトリクスとカラーフィルタ層間の平坦化のために、オーバーコート層(図示せず)が形成されている。

【0020】

さらに、貼り合わせられる前記カラーフィルタ基板と絶縁基板11との間には液晶層(図示せず)が形成されている。

【発明の概要】

【発明が解決しようとする課題】

【0021】

従来のFFS方式液晶表示装置においては、画素電極と薄膜トランジスタのドレイン電極を接続させるために、パッシベーション膜にドレインコンタクトホールを形成しなければならず、そのドレインコンタクトホールを形成する際に、ドレインコンタクトホール周辺部にディスクリネーション領域が発生することにより、光漏れが発生する。

【0022】

従って、ドレインコンタクトホール周辺部のディスクリネーション領域により発生する光漏れを防止するために、前記ドレインコンタクトホール周辺部の全てをブラックマトリクスにより遮蔽しなければならないので、その分、画素の開口領域、すなわち透過領域の面積が減少することにより、画素の透過率が減少する。特に、ドレインコンタクトホール周辺部のディスクリネーション領域により発生する光漏れを防止するために、貼り合わせマージンを考慮してブラックマトリクスにより遮蔽しなければならないので、その分、画素の透過領域の面積が減少することにより、画素の透過率が減少する。

【0023】

一方、ドレインコンタクトホールがなく、かつ共通電極が最上部に配置される構造においては、データ配線と画素電極間の干渉によるクロストークや横線の問題が生じる。

【0024】

つまり、共通電極が最上部に配置される構造は、データ配線と画素電極が隣接している構造であるので、データ配線と画素電極間に強い干渉が発生するという問題があった。

【0025】

本発明は、このような問題を解決するためになされたものであり、本発明の目的は、ドレイン電極と画素電極を接続させるためのドレインコンタクトホールを形成するのではなく、画素電極が最上部に配置される構造を適用することにより、画素の開口領域を最大化し、画素の透過率を向上させる、FFS方式液晶表示装置用アレイ基板及びその製造方法を提供することにある。

【課題を解決するための手段】

【0026】

上記目的を達成するための本発明によるFFS方式液晶表示装置用アレイ基板は、基板の一面に一方向に形成されたゲート配線と、前記ゲート配線と交差して画素領域を定義するデータ配線と、前記ゲート配線と前記データ配線との交差地点に形成された薄膜トランジスタと、前記薄膜トランジスタを含む基板全面に形成され、前記薄膜トランジスタを露出する開口部を備えた有機絶縁膜と、前記有機絶縁膜の上部に形成された大面積の共通電極と、前記有機絶縁膜の上部に形成され、前記開口部から前記薄膜トランジスタに接続された補助電極パターンと、前記共通電極及び前記補助電極パターンを含む基板全面に形成され、前記薄膜トランジスタに接続された補助電極パターンを露出するパッシベーション膜と、前記パッシベーション膜の上部に形成され、前記露出した補助電極パターンを介して前記薄膜トランジスタに電気的に接続され、前記共通電極とオーバーラップする複数の画素電極とを含むことを特徴とする。

【0027】

上記目的を達成するための本発明によるFFS方式液晶表示装置用アレイ基板の製造方法は、基板の一面に一方向にゲート配線を形成する段階と、前記ゲート配線と交差して画素領域を定義するデータ配線を形成する段階と、前記ゲート配線と前記データ配線との交差地点に薄膜トランジスタを形成する段階と、前記薄膜トランジスタを含む基板全面に前記薄膜トランジスタを露出する開口部を備えた有機絶縁膜を形成する段階と、前記有機絶縁膜の上部に、大面積の共通電極、及び前記開口部から前記薄膜トランジスタに接続される補助電極パターンを形成する段階と、前記共通電極及び前記補助電極パターンを含む基板全面に前記薄膜トランジスタに接続された補助電極パターンを露出するパッシベーション膜を形成する段階と、前記パッシベーション膜の上部に、前記露出した補助電極パターンを介して前記薄膜トランジスタに電気的に接続され、前記共通電極とオーバーラップする複数の画素電極を形成する段階とを含むことを特徴とする。

【発明の効果】

【0028】

本発明によるFFS方式液晶表示装置用アレイ基板及びその製造方法によれば、従来のドレイン電極と画素電極を電気的に接続させるために形成していたドレインコンタクトホールを省略し、有機絶縁膜に薄膜トランジスタの上部を露出する開口部を形成し、その露出した薄膜トランジスタと画素電極を電気的に直接接続させることにより、従来のドレインコンタクトホールを形成するために使用されていた面積が開口領域として使用されるので、透過率が従来より改善される。

【0029】

また、本発明によるFFS方式液晶表示装置用アレイ基板及びその製造方法によれば、薄膜トランジスタの上部に設けられた開口部内にドレイン電極と画素電極が電気的に接続されるコンタクトホールを形成することにより、コンタクトホールの面積が減少するので、その分開口率が上昇する。

【0030】

従って、画素電極が最上部に配置される構造であるため、データ配線と画素電極間のキャパシタンスによるクロストーク及び横線を低減することができる。

【0031】

さらに、本発明によるFFS方式液晶表示装置用アレイ基板及びその製造方法によれば、ソース電極及びドレイン電極形成領域に該当する導電層部分、並びにデータ配線の下方の不純物を含む非晶質シリコン層(n+又はp+)及び非晶質シリコン層(a−Si:H)が同時にパターニングされるため、アクティブテール(active tail)が発生する恐れがなくなる。

【図面の簡単な説明】

【0032】

【図1】本発明によるFFS方式液晶表示装置の概略平面図である。

【図2】本発明によるFFS方式液晶表示装置の薄膜トランジスタ部分の拡大平面図である。

【図3】図1のV−V線断面図である。

【図4A】本発明によるFFS方式液晶表示装置用アレイ基板の製造工程を示す断面図である。

【図4B】図4Aに続く工程を示す図である。

【図4C】図4Bに続く工程を示す図である。

【図4D】図4Cに続く工程を示す図である。

【図4E】図4Dに続く工程を示す図である。

【図4F】図4Eに続く工程を示す図である。

【図4G】図4Fに続く工程を示す図である。

【図4H】図4Gに続く工程を示す図である。

【図4I】図4Hに続く工程を示す図である。

【図4J】図4Iに続く工程を示す図である。

【図4K】図4Jに続く工程を示す図である。

【図4L】図4Kに続く工程を示す図である。

【図4M】図4Lに続く工程を示す図である。

【図4N】図4Mに続く工程を示す図である。

【図4O】図4Nに続く工程を示す図である。

【図4P】図4Oに続く工程を示す図である。

【図4Q】図4Pに続く工程を示す図である。

【図5】従来のFFS方式液晶表示装置の概略平面図である。

【図6】図5のII−II線断面図である。

【発明を実施するための形態】

【0033】

以下、本発明の好ましい実施の形態によるFFS方式液晶表示装置用アレイ基板及びその製造方法について添付図面を参照して詳細に説明する。

【0034】

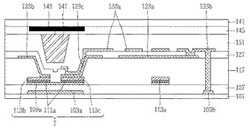

図1は本発明によるFFS方式液晶表示装置の概略平面図であり、図2は本発明によるFFS方式液晶表示装置の薄膜トランジスタ部分の拡大平面図であり、図3は図1のV−V線断面図である。

【0035】

本発明によるFFS方式液晶表示装置は、図1〜図3に示すように、透明な絶縁基板101の一面に一方向に形成されたゲート配線103と、ゲート配線103から離隔して配置された共通配線103bと、ゲート配線103と交差して画素領域を定義するデータ配線113aと、ゲート配線103とデータ配線113aとの交差地点に形成された薄膜トランジスタTと、薄膜トランジスタTを含む基板全面に形成され、薄膜トランジスタTを露出する開口部121を備えた有機絶縁膜117と、有機絶縁膜117の上部に形成された大面積の共通電極123aと、開口部121から薄膜トランジスタTに接続された補助電極パターン123cと、共通電極123a及び補助電極パターン123cを含む基板全面に形成され、薄膜トランジスタTに接続された補助電極パターン123cを露出するパッシベーション膜127と、パッシベーション膜127の上部に形成され、露出した補助電極パターン123cを介して薄膜トランジスタTに電気的に接続され、共通電極123aとオーバーラップする複数の画素電極133aとを含む。

【0036】

共通電極123aは、ゲート配線103とデータ配線113aとが交差して形成される画素領域の全面に配置されており、共通電極123aの上方には、パッシベーション膜127を介して互いに離隔するように複数の透明な棒状の画素電極133aが配置されている。ここで、共通電極123aは、画素電極133aの形成時に形成された共通接続パターン133bを介して、ゲート配線103と平行に配置された共通配線103bに電気的に接続されている。

【0037】

また、図3に示すように、画素電極133aは、別途のドレインコンタクトホールを介することなく、薄膜トランジスタTの上方に位置する開口部121から、ドレイン電極113cに直接接続された補助電極パターン123cに接続される。ここで、開口部121は、薄膜トランジスタTを構成するソース電極113b及びドレイン電極113cを露出するように形成される。

【0038】

また、ゲート配線103とデータ配線113aとが交差して形成される画素領域を除く領域に対応する上部基板(カラーフィルタ基板)141上には、光を遮断するブラックマトリクス143が形成されており、ブラックマトリクス143間には、赤色(R)カラーフィルタ層(図示せず)、緑色(G)カラーフィルタ層(図示せず)、及び青色(B)カラーフィルタ層(図示せず)を含むカラーフィルタ層145が形成されている。ここで、カラーフィルタ層145は、上部基板141上に形成するのではなく絶縁基板101上に形成するCOT(Color filter On TFT)構造を適用してもよい。すなわち、カラーフィルタ層145は、絶縁基板101においてゲート配線103とデータ配線113aとが交差して形成される画素領域に形成してもよい。

【0039】

さらに、液晶表示装置の所定のセルギャップを維持するために、カラーフィルタ層145の上部には、柱状スペーサ(column spacer)147が形成されている。ここで、柱状スペーサ147は、絶縁基板101の上部に形成されてもよい。

【0040】

従って、本発明においては、図3に示すように、従来形成していたドレインコンタクトホールが除去され、そのドレインコンタクトホールが除去された領域の面積が開口領域として使用されることにより、その分画素の透過率が改善される。

【0041】

さらに、絶縁基板101と上部基板141との間に液晶層151が形成されることにより、本発明によるFFS方式液晶表示装置が構成される。

【0042】

上記構成により、複数の共通電極123aは、液晶を駆動するための基準電圧、すなわち共通電圧を各画素に供給する。

【0043】

複数の共通電極123aは、各画素領域でパッシベーション膜127を介して大面積の画素電極133aと重なり、フリンジフィールドを形成する。

【0044】

よって、薄膜トランジスタTを介して画素電極133aにデータ信号が供給されると、共通電圧が供給された共通電極123aがフリンジフィールドを形成し、絶縁基板101と上部基板141との間に水平方向に配列された液晶分子が誘電異方性により回転し、液晶分子の回転の程度に応じて画素領域を透過する光透過率が変化することにより、階調が実現される。

【0045】

従って、本発明によるFFS方式液晶表示装置用アレイ基板によれば、従来のドレイン電極と画素電極を電気的に接続させるために形成していたドレインコンタクトホールを省略し、有機絶縁膜に薄膜トランジスタの上部を露出する開口部を形成し、その露出した薄膜トランジスタと画素電極を電気的に直接接続させることにより、従来のドレインコンタクトホールを形成するために使用されていた面積が開口領域として使用されるので、透過率が従来より改善される。

【0046】

また、本発明によるFFS方式液晶表示装置用アレイ基板は、画素電極が最上部に配置される構造であるため、データ配線と画素電極間のキャパシタンスによるクロストーク及び横線を低減することができる。

【0047】

さらに、本発明によるFFS方式液晶表示装置用アレイ基板によれば、ソース電極及びドレイン電極形成領域に該当する導電層部分、並びにデータ配線の下方の不純物を含む非晶質シリコン層(n+又はp+)及び非晶質シリコン層(a−Si:H)が同時にパターニングされるため、アクティブテールが発生する恐れがなくなる。

【0048】

一方、上記構成からなる本発明によるFFS方式液晶表示装置用アレイ基板の製造方法について図4A〜図4Qを参照して説明する。

【0049】

図4A〜図4Qは本発明によるFFS方式液晶表示装置用アレイ基板の製造工程を示す断面図である。

【0050】

まず、図4Aに示すように、透明な絶縁基板101上にスイッチングの役割を果たす複数の画素領域を定義し、絶縁基板101上に第1導電金属層102をスパッタリング法で蒸着する。ここで、第1導電金属層102を形成するターゲット物質としては、アルミニウム(Al)、タングステン(W)、銅(Cu)、モリブデン(Mo)、クロム(Cr)、チタン(Ti)、モリブデンタングステン(MoW)、モリブデンチタン(MoTi)、銅/モリブデンチタン(Cu/MoTi)を含む導電性金属群から選択される少なくとも1つを使用する。また、第1導電金属層102は、前記導電性金属群から選択される2つ以上の導電性金属からなる積層構造にしてもよい。

【0051】

次に、第1導電金属層102の上部に透過率の高いフォトレジストを塗布し、第1感光膜105を形成する。

【0052】

次に、図4Bに示すように、露光マスク(図示せず)を用いるフォトリソグラフィ法により、第1感光膜105に露光工程を行い、その後現像工程で第1感光膜105を選択的に除去し、第1感光膜パターン105aを形成する。

【0053】

次に、図4Cに示すように、第1感光膜パターン105aを遮断膜として第1導電金属層102を選択的にエッチングし、ゲート配線103(図1参照)、ゲート配線103から延びたゲート電極103a、及びゲート配線103から離隔して平行に配置される共通配線103bを同時に形成する。

【0054】

次に、第1感光膜パターン105aを除去し、その後ゲート配線103、ゲート電極103a、及び共通配線103bを含む基板全面に窒化シリコン(SiNx)又はシリコン酸化膜(SiO2)からなるゲート絶縁膜107を形成する。

【0055】

次に、図4Dに示すように、ゲート絶縁膜107上に非晶質シリコン層(a−Si:H)109及び不純物を含む非晶質シリコン層(n+又はp+)111を順次積層する。ここで、非晶質シリコン層(a−Si:H)109及び不純物を含む非晶質シリコン層(n+又はp+)111は、化学気相蒸着(Chemical Vapor Deposition; CVD)法で蒸着する。また、ゲート絶縁膜107上には、非晶質シリコン層(a−Si:H)109の代わりに、IGZOなどの酸化物系半導体材料を蒸着してもよい。

【0056】

次に、不純物を含む非晶質シリコン層(n+又はp+)111を含む基板全面に第2導電金属層113をスパッタリング法で蒸着する。ここで、第2導電金属層113を形成するターゲット物質としては、アルミニウム(Al)、タングステン(W)、銅(Cu)、モリブデン(Mo)、クロム(Cr)、チタン(Ti)、モリブデンタングステン(MoW)、モリブデンチタン(MoTi)、銅/モリブデンチタン(Cu/MoTi)を含む導電性金属群から選択される少なくとも1つを使用する。

【0057】

次に、第2導電金属層113の上部に透過率の高いフォトレジストを塗布し、第2感光膜(図示せず)を形成する。

【0058】

次に、露光マスク(図示せず)を用いるフォトリソグラフィ法により、前記第2感光膜に露光工程を行い、その後現像工程で前記第2感光膜を選択的に除去し、第2感光膜パターン115を形成する。

【0059】

次に、図4Eに示すように、第2感光膜パターン115をエッチングマスクとして第2導電金属層113を選択的にエッチングし、ゲート配線103と垂直に交差するデータ配線113aと共に、ソース電極及びドレイン電極形成領域(図示せず)を定義する。

【0060】

次いで、エッチング工程で、前記ソース電極及びドレイン電極形成領域に該当する第2導電金属層113部分、並びにデータ配線113aの下方の不純物を含む非晶質シリコン層(n+又はp+)111及び非晶質シリコン層(a−Si:H)109を順次エッチングし、オーミックコンタクト層111a及びアクティブ層109aを形成する。ここで、前記ソース電極及びドレイン電極形成領域に該当する第2導電金属層113部分、並びにデータ配線113aの下方の不純物を含む非晶質シリコン層(n+又はp+)111及び非晶質シリコン層(a−Si:H)109が同時にパターニングされるため、アクティブテールが発生する恐れがなくなる。

【0061】

次に、図4Eに示すように、アクティブ層109a、オーミックコンタクト層111a、前記ソース電極及びドレイン電極形成領域に該当する第2導電金属層113、及びデータ配線113aを含む基板全面に第1パッシベーション膜116及び有機絶縁膜117を順次蒸着する。ここで、第1パッシベーション膜116としては、窒化シリコン(SiNx)又はシリコン酸化膜(SiO2)からなる無機絶縁物質を使用する。また、有機絶縁膜117としては、感光性を有するフォトアクリル物質又はその他の感光性有機絶縁物質を使用する。なお、前記フォトアクリルは、感光性を有するため、露光工程を行う際に、フォトレジストを形成することなく露光工程を行うことができる。ここで、有機絶縁膜117の代わりに無機絶縁膜を蒸着してもよい。

【0062】

次に、図4Fに示すように、露光マスク(図示せず)を用いるフォトリソグラフィ法により、有機絶縁膜117に露光工程を行い、その後現像工程で有機絶縁膜117を選択的に除去し、前記ソース電極及びドレイン電極形成領域に該当する第2導電金属層113の上部、並びに共通配線103bの上部を露出する有機絶縁膜パターン117aを形成する。

【0063】

次に、図4Gに示すように、有機絶縁膜パターン117aをエッチングマスクとして、前記ソース電極及びドレイン電極形成領域に該当する第2導電金属層113の上部、並びに共通配線103bの上部に配置された第1パッシベーション膜116部分を選択的にエッチングし、第1開口部121a及び第2開口部121bを形成する。ここで、第1開口部121aからは、薄膜トランジスタT形成部分、すなわちソース電極及びドレイン電極形成領域が外部に露出する。また、第2開口部121bからは、共通配線103bが外部に露出する。

【0064】

次に、図4Hに示すように、第1開口部121a及び第2開口部121bを含む有機絶縁膜117の上部に透明導電物質をスパッタリング法で蒸着し、第1透明導電物質層123を形成する。ここで、前記透明導電物質としては、ITO(Indium Tin Oxide)やIZO(Indium Zinc Oxide)を含む透明な導電物質群のいずれか1つの組成物ターゲットを使用する。また、第1透明導電物質層123は、前記ソース電極及びドレイン電極形成領域に該当する第2導電金属層113の表面に直接接触する。

【0065】

次に、第1透明導電物質層123の上部に透過率の高いフォトレジストを塗布し、第3感光膜125を形成する。

【0066】

次に、図4Iに示すように、露光マスク(図示せず)を用いるフォトリソグラフィ法により、第3感光膜125に露光工程を行い、その後現像工程で第3感光膜125を選択的に除去し、第3感光膜パターン125aを形成する。このとき、薄膜トランジスタTのチャネル領域上部の第1透明導電物質層123の上面が外部に露出する。

【0067】

次に、図4Jに示すように、第3感光膜パターン125aをエッチングマスクとして、露出した第1透明導電物質層123とその下方に位置する第2導電金属層113及びオーミックコンタクト層111aを順次エッチングし、大面積の共通電極123a、ダミーパターン123b、及び補助電極パターン123cを形成すると共に、互いに離隔したソース電極113b及びドレイン電極113cを形成する。このとき、オーミックコンタクト層111aもエッチングされて離隔した状態となるので、その下方に位置するアクティブ層109aのチャネル領域(図示せず)が外部に露出する。また、補助電極パターン123cはドレイン電極113cに直接接続された状態となり、ダミーパターン123bはソース電極113bに直接接続された状態となる。ここで、ダミーパターン123bは、単にソース電極113bにのみ接続された状態であるので、別途エッチングする必要はない。

【0068】

次に、図4Kに示すように、第3感光膜パターン125aを除去し、その後基板全面に無機絶縁物質又は有機絶縁物質を蒸着し、第2パッシベーション膜127を形成し、次いで、第2パッシベーション膜127の上部に透過率の高いフォトレジストを塗布し、第4感光膜129を形成する。

【0069】

次に、図4Lに示すように、露光マスク(図示せず)を用いるフォトリソグラフィ法により露光及び現像工程を行って第4感光膜129を除去し、第4感光膜パターン129aを形成する。

【0070】

次に、図4Mに示すように、第4感光膜パターン129aをエッチングマスクとして、第2パッシベーション膜127を選択的にエッチングし、補助電極パターン123c、共通電極123a、及び共通配線103bをそれぞれ露出する画素電極コンタクトホール131a、共通電極コンタクトホール131b、及び共通配線コンタクトホール131cを同時に形成する。

【0071】

次に、図4Nに示すように、第4感光膜パターン129aを除去し、その後画素電極コンタクトホール131a、共通電極コンタクトホール131b、及び共通配線コンタクトホール131cを含む第2パッシベーション膜127の上部に透明導電物質をスパッタリング法で蒸着し、第2透明導電物質層133を形成する。ここで、前記透明導電物質としては、ITOやIZOを含む透明な導電物質群のいずれか1つの組成物ターゲットを使用する。

【0072】

次に、第2透明導電物質層133の上部に透過率の高いフォトレジストを塗布し、第5感光膜135を形成する。

【0073】

次に、図4Oに示すように、露光マスク(図示せず)を用いるフォトリソグラフィ法により、第5感光膜135に露光工程を行い、その後現像工程で第5感光膜135を選択的に除去し、第5感光膜パターン135aを形成する。

【0074】

次に、図4Pに示すように、第5感光膜パターン135aをエッチングマスクとして、第2透明導電物質層133を選択的にエッチングし、補助電極パターン123cに接続されて互いに離隔した複数の画素電極133a、並びに共通電極コンタクトホール131b及び共通配線コンタクトホール131cを介して共通電極123aと共通配線103bとを電気的に接続する共通接続パターン133bを同時に形成する。ここで、画素電極133aは、補助電極パターン123cに接続されることにより、ドレイン電極113cとも電気的に接続される。

【0075】

次に、図示していないが、残っている第5感光膜パターン135aを除去し、その後基板全面に配向膜(図示せず)を形成する工程をさらに行うことにより、本発明によるFFS方式液晶表示装置用アレイ基板の製造工程を完了する。

【0076】

そして、図4Qに示すように、ゲート配線103とデータ配線113aとが交差して形成される画素領域を除く領域に対応する上部基板141上に、光を遮断するブラックマトリクス143を形成する。

【0077】

次に、ブラックマトリクス143間に、赤色(R)カラーフィルタ層(図示せず)、緑色(G)カラーフィルタ層(図示せず)、及び青色(B)カラーフィルタ層(図示せず)を含むカラーフィルタ層145を形成する。ここで、カラーフィルタ層145は、上部基板141上に形成するのではなく絶縁基板101上に形成するCOT(Color filter On TFT)構造を適用してもよい。すなわち、カラーフィルタ層145は、第1パッシベーション膜116を形成する前の段階において、絶縁基板101においてゲート配線103とデータ配線113aとが交差して形成される画素領域に形成してもよい。

【0078】

次に、液晶表示装置の所定のセルギャップを維持するために、カラーフィルタ層145の上部に、柱状スペーサ147を形成する。ここで、柱状スペーサ147は、絶縁基板101の上部に形成してもよい。

【0079】

従って、本発明においては、従来形成していたドレインコンタクトホールが除去され、そのドレインコンタクトホールが除去された領域の面積が開口領域として使用されることにより、その分画素の透過率が改善される。

【0080】

次に、上部基板141の全面に配向膜(図示せず)を形成する工程をさらに行うことにより、カラーフィルタ基板の製造工程を完了する。

【0081】

その後、絶縁基板101と上部基板141との間に液晶層151を形成することにより、本発明によるFFS方式液晶表示装置の製造工程を完了する。

【0082】

前述したように、本発明によるFFS方式液晶表示装置用アレイ基板及びその製造方法によれば、従来のドレイン電極と画素電極を電気的に接続させるために形成していたドレインコンタクトホールを省略し、有機絶縁膜に薄膜トランジスタの上部を露出する開口部を形成し、その露出した薄膜トランジスタと画素電極を電気的に直接接続させることにより、従来のドレインコンタクトホールを形成するために使用されていた面積が開口領域として使用されるので、透過率が従来より改善される。

【0083】

また、本発明によるFFS方式液晶表示装置用アレイ基板及びその製造方法によれば、薄膜トランジスタの上部に設けられた開口部内にドレイン電極と画素電極が電気的に接続されるコンタクトホールを形成することにより、コンタクトホールの面積が減少するので、その分開口率が上昇する。

【0084】

従って、画素電極が最上部に配置される構造であるため、データ配線と画素電極間のキャパシタンスによるクロストーク及び横線を低減することができる。

【0085】

さらに、本発明によるFFS方式液晶表示装置用アレイ基板及びその製造方法によれば、ソース電極及びドレイン電極形成領域に該当する導電層部分、並びにデータ配線の下方の不純物を含む非晶質シリコン層(n+又はp+)及び非晶質シリコン層(a−Si:H)が同時にパターニングされるため、アクティブテールが発生する恐れがなくなる。

【0086】

以上、本発明の好ましい実施の形態について詳細に説明したが、当該技術分野における通常の知識を有する者であればこれから様々な変形及び均等な実施の形態が可能であることを理解するであろう。

【0087】

よって、本発明の権利範囲はこれに限定されるものではなく、特許請求の範囲で定義される本発明の基本概念を用いた当業者の様々な変形や改良形態も本発明に含まれる。

【符号の説明】

【0088】

101 絶縁基板

103 ゲート配線

103a ゲート電極

107 ゲート絶縁膜

109a アクティブ層

111a オーミックコンタクト層

113a データ配線

113b ソース電極

113c ドレイン電極

117 有機絶縁膜

121 開口部

123a 共通電極

123b ダミーパターン

123c 補助電極パターン

116 第1パッシベーション膜

127 第2パッシベーション膜

131a 画素電極コンタクトホール

131b 共通電極コンタクトホール

131c 共通配線コンタクトホール

133a 画素電極

133b 共通接続パターン

141 上部基板

143 ブラックマトリクス

145 カラーフィルタ層

147 柱状スペーサ

151 液晶層

【技術分野】

【0001】

本発明は、液晶表示装置(Liquid Crystal Display Device)に関し、特に、FFS(Fringe Field Switching)方式液晶表示装置用アレイ基板及びその製造方法に関する。

【背景技術】

【0002】

一般に、液晶表示装置の駆動原理は、液晶の光学的異方性と分極特性を利用するものである。前記液晶は細長い構造であるので分子配列に方向性を有し、人為的に前記液晶に電場を印加することで分子配列の方向を制御することができる。

【0003】

つまり、前記液晶の分子配列の方向を任意に調節して前記液晶の分子配列を変化させると、光学的異方性により前記液晶の分子配列方向に光が屈折し、画像情報が表示される。

【0004】

近年、薄膜トランジスタと前記薄膜トランジスタに接続された画素電極とがマトリクス方式で配列されたアクティブマトリクス液晶表示装置(AM−LCD(Active Matrix LCD)、以下液晶表示装置という)が、解像度及び動画表示能力に優れており、最も注目されている。

【0005】

前記液晶表示装置は、共通電極が形成されたカラーフィルタ基板(すなわち、上部基板)と、画素電極が形成されたアレイ基板(すなわち、下部基板)と、上部基板と下部基板との間に充填された液晶とからなるが、このような液晶表示装置は、画素電極と共通電極が上下に印加される電場により液晶を駆動する方式であって、透過率や開口率などの特性に優れている。

【0006】

しかし、上下に印加される電場による液晶駆動方式は、視野角特性に優れていないという欠点があった。よって、上記欠点を克服するために新たに提案された技術が横電界による液晶駆動方式であるが、この横電界による液晶駆動方式は、視野角特性に優れているという利点を有する。

【0007】

このような横電界方式液晶表示装置は、カラーフィルタ基板とアレイ基板とが対向するように構成され、カラーフィルタ基板とアレイ基板との間に液晶層が介在している。

【0008】

前記アレイ基板は、透明な絶縁基板上に定義された複数の画素毎に設けられる薄膜トランジスタ、共通電極、及び画素電極から構成される。前記共通電極と前記画素電極とは、同一基板上に平行に離隔して構成される。

【0009】

また、前記カラーフィルタ基板は、透明な絶縁基板上に、ゲート配線、データ配線、及び薄膜トランジスタに対応する部分にブラックマトリクスが形成され、前記画素に対応する部分にカラーフィルタが形成される。

【0010】

さらに、前記液晶層は、前記共通電極と前記画素電極の水平電界により駆動される。

【0011】

通常、前記共通電極及び前記画素電極は、輝度を確保するために、透明電極で形成する。

【0012】

よって、このような輝度改善効果を最大化するために提案された技術がFFS技術である。前記FFS技術は、液晶を精密に制御することにより、色ずれ(color shift)がなく、高いコントラスト比が得られるという特徴がある。

【0013】

以下、このような従来のFFS方式液晶表示装置の製造方法について図5及び図6を参照して説明する。

【0014】

図5は従来のFFS方式液晶表示装置の概略平面図であり、図6は図5のII−II線断面図である。

【0015】

従来のFFS方式液晶表示装置用アレイ基板は、図5及び図6に示すように、透明な絶縁基板11上に一方向に延び、互いに平行に離隔した複数のゲート配線13と、ゲート配線13と交差し、その交差して形成される領域に画素領域を定義する複数のデータ配線21と、ゲート配線13とデータ配線21との交差地点に設けられ、ゲート配線13から垂直に延びたゲート電極13a、ゲート絶縁膜15、アクティブ層17、オーミックコンタクト層19、ソース電極21a、及びドレイン電極21bからなる薄膜トランジスタTと、薄膜トランジスタTを含む基板全面に形成された第1パッシベーション膜27と、第1パッシベーション膜27上に形成されて薄膜トランジスタTに接続された大面積の画素電極29と、画素電極29を含む第1パッシベーション膜27上に形成された第2パッシベーション膜31と、第2パッシベーション膜31上に互いに離隔して形成されて画素電極29に対応する複数の共通電極33とを含む。

【0016】

ここで、大面積の画素電極29は、ゲート配線13とデータ配線21とが交差して形成される画素領域に配置されている。

【0017】

また、共通電極33は、第2パッシベーション膜31を介して画素電極29とオーバーラップしている。ここで、画素電極29及び複数の共通電極33は、透明導電物質であるITO(Indium Tin Oxide)で形成される。

【0018】

また、画素電極29は、第1パッシベーション膜27の上部に形成されたドレインコンタクトホール27aを介してドレイン電極21bに電気的に接続される。

【0019】

さらに、画素電極29及び複数の共通電極33が形成された絶縁基板11と貼り合わせられるカラーフィルタ基板(図示せず)上には、カラーフィルタ層(図示せず)と、前記カラーフィルタ層間に配置されて光の透過を遮断するためのブラックマトリクス(図示せず)が積層されており、前記ブラックマトリクス及び前記カラーフィルタ層の上部には、これらブラックマトリクスとカラーフィルタ層間の平坦化のために、オーバーコート層(図示せず)が形成されている。

【0020】

さらに、貼り合わせられる前記カラーフィルタ基板と絶縁基板11との間には液晶層(図示せず)が形成されている。

【発明の概要】

【発明が解決しようとする課題】

【0021】

従来のFFS方式液晶表示装置においては、画素電極と薄膜トランジスタのドレイン電極を接続させるために、パッシベーション膜にドレインコンタクトホールを形成しなければならず、そのドレインコンタクトホールを形成する際に、ドレインコンタクトホール周辺部にディスクリネーション領域が発生することにより、光漏れが発生する。

【0022】

従って、ドレインコンタクトホール周辺部のディスクリネーション領域により発生する光漏れを防止するために、前記ドレインコンタクトホール周辺部の全てをブラックマトリクスにより遮蔽しなければならないので、その分、画素の開口領域、すなわち透過領域の面積が減少することにより、画素の透過率が減少する。特に、ドレインコンタクトホール周辺部のディスクリネーション領域により発生する光漏れを防止するために、貼り合わせマージンを考慮してブラックマトリクスにより遮蔽しなければならないので、その分、画素の透過領域の面積が減少することにより、画素の透過率が減少する。

【0023】

一方、ドレインコンタクトホールがなく、かつ共通電極が最上部に配置される構造においては、データ配線と画素電極間の干渉によるクロストークや横線の問題が生じる。

【0024】

つまり、共通電極が最上部に配置される構造は、データ配線と画素電極が隣接している構造であるので、データ配線と画素電極間に強い干渉が発生するという問題があった。

【0025】

本発明は、このような問題を解決するためになされたものであり、本発明の目的は、ドレイン電極と画素電極を接続させるためのドレインコンタクトホールを形成するのではなく、画素電極が最上部に配置される構造を適用することにより、画素の開口領域を最大化し、画素の透過率を向上させる、FFS方式液晶表示装置用アレイ基板及びその製造方法を提供することにある。

【課題を解決するための手段】

【0026】

上記目的を達成するための本発明によるFFS方式液晶表示装置用アレイ基板は、基板の一面に一方向に形成されたゲート配線と、前記ゲート配線と交差して画素領域を定義するデータ配線と、前記ゲート配線と前記データ配線との交差地点に形成された薄膜トランジスタと、前記薄膜トランジスタを含む基板全面に形成され、前記薄膜トランジスタを露出する開口部を備えた有機絶縁膜と、前記有機絶縁膜の上部に形成された大面積の共通電極と、前記有機絶縁膜の上部に形成され、前記開口部から前記薄膜トランジスタに接続された補助電極パターンと、前記共通電極及び前記補助電極パターンを含む基板全面に形成され、前記薄膜トランジスタに接続された補助電極パターンを露出するパッシベーション膜と、前記パッシベーション膜の上部に形成され、前記露出した補助電極パターンを介して前記薄膜トランジスタに電気的に接続され、前記共通電極とオーバーラップする複数の画素電極とを含むことを特徴とする。

【0027】

上記目的を達成するための本発明によるFFS方式液晶表示装置用アレイ基板の製造方法は、基板の一面に一方向にゲート配線を形成する段階と、前記ゲート配線と交差して画素領域を定義するデータ配線を形成する段階と、前記ゲート配線と前記データ配線との交差地点に薄膜トランジスタを形成する段階と、前記薄膜トランジスタを含む基板全面に前記薄膜トランジスタを露出する開口部を備えた有機絶縁膜を形成する段階と、前記有機絶縁膜の上部に、大面積の共通電極、及び前記開口部から前記薄膜トランジスタに接続される補助電極パターンを形成する段階と、前記共通電極及び前記補助電極パターンを含む基板全面に前記薄膜トランジスタに接続された補助電極パターンを露出するパッシベーション膜を形成する段階と、前記パッシベーション膜の上部に、前記露出した補助電極パターンを介して前記薄膜トランジスタに電気的に接続され、前記共通電極とオーバーラップする複数の画素電極を形成する段階とを含むことを特徴とする。

【発明の効果】

【0028】

本発明によるFFS方式液晶表示装置用アレイ基板及びその製造方法によれば、従来のドレイン電極と画素電極を電気的に接続させるために形成していたドレインコンタクトホールを省略し、有機絶縁膜に薄膜トランジスタの上部を露出する開口部を形成し、その露出した薄膜トランジスタと画素電極を電気的に直接接続させることにより、従来のドレインコンタクトホールを形成するために使用されていた面積が開口領域として使用されるので、透過率が従来より改善される。

【0029】

また、本発明によるFFS方式液晶表示装置用アレイ基板及びその製造方法によれば、薄膜トランジスタの上部に設けられた開口部内にドレイン電極と画素電極が電気的に接続されるコンタクトホールを形成することにより、コンタクトホールの面積が減少するので、その分開口率が上昇する。

【0030】

従って、画素電極が最上部に配置される構造であるため、データ配線と画素電極間のキャパシタンスによるクロストーク及び横線を低減することができる。

【0031】

さらに、本発明によるFFS方式液晶表示装置用アレイ基板及びその製造方法によれば、ソース電極及びドレイン電極形成領域に該当する導電層部分、並びにデータ配線の下方の不純物を含む非晶質シリコン層(n+又はp+)及び非晶質シリコン層(a−Si:H)が同時にパターニングされるため、アクティブテール(active tail)が発生する恐れがなくなる。

【図面の簡単な説明】

【0032】

【図1】本発明によるFFS方式液晶表示装置の概略平面図である。

【図2】本発明によるFFS方式液晶表示装置の薄膜トランジスタ部分の拡大平面図である。

【図3】図1のV−V線断面図である。

【図4A】本発明によるFFS方式液晶表示装置用アレイ基板の製造工程を示す断面図である。

【図4B】図4Aに続く工程を示す図である。

【図4C】図4Bに続く工程を示す図である。

【図4D】図4Cに続く工程を示す図である。

【図4E】図4Dに続く工程を示す図である。

【図4F】図4Eに続く工程を示す図である。

【図4G】図4Fに続く工程を示す図である。

【図4H】図4Gに続く工程を示す図である。

【図4I】図4Hに続く工程を示す図である。

【図4J】図4Iに続く工程を示す図である。

【図4K】図4Jに続く工程を示す図である。

【図4L】図4Kに続く工程を示す図である。

【図4M】図4Lに続く工程を示す図である。

【図4N】図4Mに続く工程を示す図である。

【図4O】図4Nに続く工程を示す図である。

【図4P】図4Oに続く工程を示す図である。

【図4Q】図4Pに続く工程を示す図である。

【図5】従来のFFS方式液晶表示装置の概略平面図である。

【図6】図5のII−II線断面図である。

【発明を実施するための形態】

【0033】

以下、本発明の好ましい実施の形態によるFFS方式液晶表示装置用アレイ基板及びその製造方法について添付図面を参照して詳細に説明する。

【0034】

図1は本発明によるFFS方式液晶表示装置の概略平面図であり、図2は本発明によるFFS方式液晶表示装置の薄膜トランジスタ部分の拡大平面図であり、図3は図1のV−V線断面図である。

【0035】

本発明によるFFS方式液晶表示装置は、図1〜図3に示すように、透明な絶縁基板101の一面に一方向に形成されたゲート配線103と、ゲート配線103から離隔して配置された共通配線103bと、ゲート配線103と交差して画素領域を定義するデータ配線113aと、ゲート配線103とデータ配線113aとの交差地点に形成された薄膜トランジスタTと、薄膜トランジスタTを含む基板全面に形成され、薄膜トランジスタTを露出する開口部121を備えた有機絶縁膜117と、有機絶縁膜117の上部に形成された大面積の共通電極123aと、開口部121から薄膜トランジスタTに接続された補助電極パターン123cと、共通電極123a及び補助電極パターン123cを含む基板全面に形成され、薄膜トランジスタTに接続された補助電極パターン123cを露出するパッシベーション膜127と、パッシベーション膜127の上部に形成され、露出した補助電極パターン123cを介して薄膜トランジスタTに電気的に接続され、共通電極123aとオーバーラップする複数の画素電極133aとを含む。

【0036】

共通電極123aは、ゲート配線103とデータ配線113aとが交差して形成される画素領域の全面に配置されており、共通電極123aの上方には、パッシベーション膜127を介して互いに離隔するように複数の透明な棒状の画素電極133aが配置されている。ここで、共通電極123aは、画素電極133aの形成時に形成された共通接続パターン133bを介して、ゲート配線103と平行に配置された共通配線103bに電気的に接続されている。

【0037】

また、図3に示すように、画素電極133aは、別途のドレインコンタクトホールを介することなく、薄膜トランジスタTの上方に位置する開口部121から、ドレイン電極113cに直接接続された補助電極パターン123cに接続される。ここで、開口部121は、薄膜トランジスタTを構成するソース電極113b及びドレイン電極113cを露出するように形成される。

【0038】

また、ゲート配線103とデータ配線113aとが交差して形成される画素領域を除く領域に対応する上部基板(カラーフィルタ基板)141上には、光を遮断するブラックマトリクス143が形成されており、ブラックマトリクス143間には、赤色(R)カラーフィルタ層(図示せず)、緑色(G)カラーフィルタ層(図示せず)、及び青色(B)カラーフィルタ層(図示せず)を含むカラーフィルタ層145が形成されている。ここで、カラーフィルタ層145は、上部基板141上に形成するのではなく絶縁基板101上に形成するCOT(Color filter On TFT)構造を適用してもよい。すなわち、カラーフィルタ層145は、絶縁基板101においてゲート配線103とデータ配線113aとが交差して形成される画素領域に形成してもよい。

【0039】

さらに、液晶表示装置の所定のセルギャップを維持するために、カラーフィルタ層145の上部には、柱状スペーサ(column spacer)147が形成されている。ここで、柱状スペーサ147は、絶縁基板101の上部に形成されてもよい。

【0040】

従って、本発明においては、図3に示すように、従来形成していたドレインコンタクトホールが除去され、そのドレインコンタクトホールが除去された領域の面積が開口領域として使用されることにより、その分画素の透過率が改善される。

【0041】

さらに、絶縁基板101と上部基板141との間に液晶層151が形成されることにより、本発明によるFFS方式液晶表示装置が構成される。

【0042】

上記構成により、複数の共通電極123aは、液晶を駆動するための基準電圧、すなわち共通電圧を各画素に供給する。

【0043】

複数の共通電極123aは、各画素領域でパッシベーション膜127を介して大面積の画素電極133aと重なり、フリンジフィールドを形成する。

【0044】

よって、薄膜トランジスタTを介して画素電極133aにデータ信号が供給されると、共通電圧が供給された共通電極123aがフリンジフィールドを形成し、絶縁基板101と上部基板141との間に水平方向に配列された液晶分子が誘電異方性により回転し、液晶分子の回転の程度に応じて画素領域を透過する光透過率が変化することにより、階調が実現される。

【0045】

従って、本発明によるFFS方式液晶表示装置用アレイ基板によれば、従来のドレイン電極と画素電極を電気的に接続させるために形成していたドレインコンタクトホールを省略し、有機絶縁膜に薄膜トランジスタの上部を露出する開口部を形成し、その露出した薄膜トランジスタと画素電極を電気的に直接接続させることにより、従来のドレインコンタクトホールを形成するために使用されていた面積が開口領域として使用されるので、透過率が従来より改善される。

【0046】

また、本発明によるFFS方式液晶表示装置用アレイ基板は、画素電極が最上部に配置される構造であるため、データ配線と画素電極間のキャパシタンスによるクロストーク及び横線を低減することができる。

【0047】

さらに、本発明によるFFS方式液晶表示装置用アレイ基板によれば、ソース電極及びドレイン電極形成領域に該当する導電層部分、並びにデータ配線の下方の不純物を含む非晶質シリコン層(n+又はp+)及び非晶質シリコン層(a−Si:H)が同時にパターニングされるため、アクティブテールが発生する恐れがなくなる。

【0048】

一方、上記構成からなる本発明によるFFS方式液晶表示装置用アレイ基板の製造方法について図4A〜図4Qを参照して説明する。

【0049】

図4A〜図4Qは本発明によるFFS方式液晶表示装置用アレイ基板の製造工程を示す断面図である。

【0050】

まず、図4Aに示すように、透明な絶縁基板101上にスイッチングの役割を果たす複数の画素領域を定義し、絶縁基板101上に第1導電金属層102をスパッタリング法で蒸着する。ここで、第1導電金属層102を形成するターゲット物質としては、アルミニウム(Al)、タングステン(W)、銅(Cu)、モリブデン(Mo)、クロム(Cr)、チタン(Ti)、モリブデンタングステン(MoW)、モリブデンチタン(MoTi)、銅/モリブデンチタン(Cu/MoTi)を含む導電性金属群から選択される少なくとも1つを使用する。また、第1導電金属層102は、前記導電性金属群から選択される2つ以上の導電性金属からなる積層構造にしてもよい。

【0051】

次に、第1導電金属層102の上部に透過率の高いフォトレジストを塗布し、第1感光膜105を形成する。

【0052】

次に、図4Bに示すように、露光マスク(図示せず)を用いるフォトリソグラフィ法により、第1感光膜105に露光工程を行い、その後現像工程で第1感光膜105を選択的に除去し、第1感光膜パターン105aを形成する。

【0053】

次に、図4Cに示すように、第1感光膜パターン105aを遮断膜として第1導電金属層102を選択的にエッチングし、ゲート配線103(図1参照)、ゲート配線103から延びたゲート電極103a、及びゲート配線103から離隔して平行に配置される共通配線103bを同時に形成する。

【0054】

次に、第1感光膜パターン105aを除去し、その後ゲート配線103、ゲート電極103a、及び共通配線103bを含む基板全面に窒化シリコン(SiNx)又はシリコン酸化膜(SiO2)からなるゲート絶縁膜107を形成する。

【0055】

次に、図4Dに示すように、ゲート絶縁膜107上に非晶質シリコン層(a−Si:H)109及び不純物を含む非晶質シリコン層(n+又はp+)111を順次積層する。ここで、非晶質シリコン層(a−Si:H)109及び不純物を含む非晶質シリコン層(n+又はp+)111は、化学気相蒸着(Chemical Vapor Deposition; CVD)法で蒸着する。また、ゲート絶縁膜107上には、非晶質シリコン層(a−Si:H)109の代わりに、IGZOなどの酸化物系半導体材料を蒸着してもよい。

【0056】

次に、不純物を含む非晶質シリコン層(n+又はp+)111を含む基板全面に第2導電金属層113をスパッタリング法で蒸着する。ここで、第2導電金属層113を形成するターゲット物質としては、アルミニウム(Al)、タングステン(W)、銅(Cu)、モリブデン(Mo)、クロム(Cr)、チタン(Ti)、モリブデンタングステン(MoW)、モリブデンチタン(MoTi)、銅/モリブデンチタン(Cu/MoTi)を含む導電性金属群から選択される少なくとも1つを使用する。

【0057】

次に、第2導電金属層113の上部に透過率の高いフォトレジストを塗布し、第2感光膜(図示せず)を形成する。

【0058】

次に、露光マスク(図示せず)を用いるフォトリソグラフィ法により、前記第2感光膜に露光工程を行い、その後現像工程で前記第2感光膜を選択的に除去し、第2感光膜パターン115を形成する。

【0059】

次に、図4Eに示すように、第2感光膜パターン115をエッチングマスクとして第2導電金属層113を選択的にエッチングし、ゲート配線103と垂直に交差するデータ配線113aと共に、ソース電極及びドレイン電極形成領域(図示せず)を定義する。

【0060】

次いで、エッチング工程で、前記ソース電極及びドレイン電極形成領域に該当する第2導電金属層113部分、並びにデータ配線113aの下方の不純物を含む非晶質シリコン層(n+又はp+)111及び非晶質シリコン層(a−Si:H)109を順次エッチングし、オーミックコンタクト層111a及びアクティブ層109aを形成する。ここで、前記ソース電極及びドレイン電極形成領域に該当する第2導電金属層113部分、並びにデータ配線113aの下方の不純物を含む非晶質シリコン層(n+又はp+)111及び非晶質シリコン層(a−Si:H)109が同時にパターニングされるため、アクティブテールが発生する恐れがなくなる。

【0061】

次に、図4Eに示すように、アクティブ層109a、オーミックコンタクト層111a、前記ソース電極及びドレイン電極形成領域に該当する第2導電金属層113、及びデータ配線113aを含む基板全面に第1パッシベーション膜116及び有機絶縁膜117を順次蒸着する。ここで、第1パッシベーション膜116としては、窒化シリコン(SiNx)又はシリコン酸化膜(SiO2)からなる無機絶縁物質を使用する。また、有機絶縁膜117としては、感光性を有するフォトアクリル物質又はその他の感光性有機絶縁物質を使用する。なお、前記フォトアクリルは、感光性を有するため、露光工程を行う際に、フォトレジストを形成することなく露光工程を行うことができる。ここで、有機絶縁膜117の代わりに無機絶縁膜を蒸着してもよい。

【0062】

次に、図4Fに示すように、露光マスク(図示せず)を用いるフォトリソグラフィ法により、有機絶縁膜117に露光工程を行い、その後現像工程で有機絶縁膜117を選択的に除去し、前記ソース電極及びドレイン電極形成領域に該当する第2導電金属層113の上部、並びに共通配線103bの上部を露出する有機絶縁膜パターン117aを形成する。

【0063】

次に、図4Gに示すように、有機絶縁膜パターン117aをエッチングマスクとして、前記ソース電極及びドレイン電極形成領域に該当する第2導電金属層113の上部、並びに共通配線103bの上部に配置された第1パッシベーション膜116部分を選択的にエッチングし、第1開口部121a及び第2開口部121bを形成する。ここで、第1開口部121aからは、薄膜トランジスタT形成部分、すなわちソース電極及びドレイン電極形成領域が外部に露出する。また、第2開口部121bからは、共通配線103bが外部に露出する。

【0064】

次に、図4Hに示すように、第1開口部121a及び第2開口部121bを含む有機絶縁膜117の上部に透明導電物質をスパッタリング法で蒸着し、第1透明導電物質層123を形成する。ここで、前記透明導電物質としては、ITO(Indium Tin Oxide)やIZO(Indium Zinc Oxide)を含む透明な導電物質群のいずれか1つの組成物ターゲットを使用する。また、第1透明導電物質層123は、前記ソース電極及びドレイン電極形成領域に該当する第2導電金属層113の表面に直接接触する。

【0065】

次に、第1透明導電物質層123の上部に透過率の高いフォトレジストを塗布し、第3感光膜125を形成する。

【0066】

次に、図4Iに示すように、露光マスク(図示せず)を用いるフォトリソグラフィ法により、第3感光膜125に露光工程を行い、その後現像工程で第3感光膜125を選択的に除去し、第3感光膜パターン125aを形成する。このとき、薄膜トランジスタTのチャネル領域上部の第1透明導電物質層123の上面が外部に露出する。

【0067】

次に、図4Jに示すように、第3感光膜パターン125aをエッチングマスクとして、露出した第1透明導電物質層123とその下方に位置する第2導電金属層113及びオーミックコンタクト層111aを順次エッチングし、大面積の共通電極123a、ダミーパターン123b、及び補助電極パターン123cを形成すると共に、互いに離隔したソース電極113b及びドレイン電極113cを形成する。このとき、オーミックコンタクト層111aもエッチングされて離隔した状態となるので、その下方に位置するアクティブ層109aのチャネル領域(図示せず)が外部に露出する。また、補助電極パターン123cはドレイン電極113cに直接接続された状態となり、ダミーパターン123bはソース電極113bに直接接続された状態となる。ここで、ダミーパターン123bは、単にソース電極113bにのみ接続された状態であるので、別途エッチングする必要はない。

【0068】

次に、図4Kに示すように、第3感光膜パターン125aを除去し、その後基板全面に無機絶縁物質又は有機絶縁物質を蒸着し、第2パッシベーション膜127を形成し、次いで、第2パッシベーション膜127の上部に透過率の高いフォトレジストを塗布し、第4感光膜129を形成する。

【0069】

次に、図4Lに示すように、露光マスク(図示せず)を用いるフォトリソグラフィ法により露光及び現像工程を行って第4感光膜129を除去し、第4感光膜パターン129aを形成する。

【0070】

次に、図4Mに示すように、第4感光膜パターン129aをエッチングマスクとして、第2パッシベーション膜127を選択的にエッチングし、補助電極パターン123c、共通電極123a、及び共通配線103bをそれぞれ露出する画素電極コンタクトホール131a、共通電極コンタクトホール131b、及び共通配線コンタクトホール131cを同時に形成する。

【0071】

次に、図4Nに示すように、第4感光膜パターン129aを除去し、その後画素電極コンタクトホール131a、共通電極コンタクトホール131b、及び共通配線コンタクトホール131cを含む第2パッシベーション膜127の上部に透明導電物質をスパッタリング法で蒸着し、第2透明導電物質層133を形成する。ここで、前記透明導電物質としては、ITOやIZOを含む透明な導電物質群のいずれか1つの組成物ターゲットを使用する。

【0072】

次に、第2透明導電物質層133の上部に透過率の高いフォトレジストを塗布し、第5感光膜135を形成する。

【0073】

次に、図4Oに示すように、露光マスク(図示せず)を用いるフォトリソグラフィ法により、第5感光膜135に露光工程を行い、その後現像工程で第5感光膜135を選択的に除去し、第5感光膜パターン135aを形成する。

【0074】

次に、図4Pに示すように、第5感光膜パターン135aをエッチングマスクとして、第2透明導電物質層133を選択的にエッチングし、補助電極パターン123cに接続されて互いに離隔した複数の画素電極133a、並びに共通電極コンタクトホール131b及び共通配線コンタクトホール131cを介して共通電極123aと共通配線103bとを電気的に接続する共通接続パターン133bを同時に形成する。ここで、画素電極133aは、補助電極パターン123cに接続されることにより、ドレイン電極113cとも電気的に接続される。

【0075】

次に、図示していないが、残っている第5感光膜パターン135aを除去し、その後基板全面に配向膜(図示せず)を形成する工程をさらに行うことにより、本発明によるFFS方式液晶表示装置用アレイ基板の製造工程を完了する。

【0076】

そして、図4Qに示すように、ゲート配線103とデータ配線113aとが交差して形成される画素領域を除く領域に対応する上部基板141上に、光を遮断するブラックマトリクス143を形成する。

【0077】

次に、ブラックマトリクス143間に、赤色(R)カラーフィルタ層(図示せず)、緑色(G)カラーフィルタ層(図示せず)、及び青色(B)カラーフィルタ層(図示せず)を含むカラーフィルタ層145を形成する。ここで、カラーフィルタ層145は、上部基板141上に形成するのではなく絶縁基板101上に形成するCOT(Color filter On TFT)構造を適用してもよい。すなわち、カラーフィルタ層145は、第1パッシベーション膜116を形成する前の段階において、絶縁基板101においてゲート配線103とデータ配線113aとが交差して形成される画素領域に形成してもよい。

【0078】

次に、液晶表示装置の所定のセルギャップを維持するために、カラーフィルタ層145の上部に、柱状スペーサ147を形成する。ここで、柱状スペーサ147は、絶縁基板101の上部に形成してもよい。

【0079】

従って、本発明においては、従来形成していたドレインコンタクトホールが除去され、そのドレインコンタクトホールが除去された領域の面積が開口領域として使用されることにより、その分画素の透過率が改善される。

【0080】

次に、上部基板141の全面に配向膜(図示せず)を形成する工程をさらに行うことにより、カラーフィルタ基板の製造工程を完了する。

【0081】

その後、絶縁基板101と上部基板141との間に液晶層151を形成することにより、本発明によるFFS方式液晶表示装置の製造工程を完了する。

【0082】

前述したように、本発明によるFFS方式液晶表示装置用アレイ基板及びその製造方法によれば、従来のドレイン電極と画素電極を電気的に接続させるために形成していたドレインコンタクトホールを省略し、有機絶縁膜に薄膜トランジスタの上部を露出する開口部を形成し、その露出した薄膜トランジスタと画素電極を電気的に直接接続させることにより、従来のドレインコンタクトホールを形成するために使用されていた面積が開口領域として使用されるので、透過率が従来より改善される。

【0083】

また、本発明によるFFS方式液晶表示装置用アレイ基板及びその製造方法によれば、薄膜トランジスタの上部に設けられた開口部内にドレイン電極と画素電極が電気的に接続されるコンタクトホールを形成することにより、コンタクトホールの面積が減少するので、その分開口率が上昇する。

【0084】

従って、画素電極が最上部に配置される構造であるため、データ配線と画素電極間のキャパシタンスによるクロストーク及び横線を低減することができる。

【0085】

さらに、本発明によるFFS方式液晶表示装置用アレイ基板及びその製造方法によれば、ソース電極及びドレイン電極形成領域に該当する導電層部分、並びにデータ配線の下方の不純物を含む非晶質シリコン層(n+又はp+)及び非晶質シリコン層(a−Si:H)が同時にパターニングされるため、アクティブテールが発生する恐れがなくなる。

【0086】

以上、本発明の好ましい実施の形態について詳細に説明したが、当該技術分野における通常の知識を有する者であればこれから様々な変形及び均等な実施の形態が可能であることを理解するであろう。

【0087】

よって、本発明の権利範囲はこれに限定されるものではなく、特許請求の範囲で定義される本発明の基本概念を用いた当業者の様々な変形や改良形態も本発明に含まれる。

【符号の説明】

【0088】

101 絶縁基板

103 ゲート配線

103a ゲート電極

107 ゲート絶縁膜

109a アクティブ層

111a オーミックコンタクト層

113a データ配線

113b ソース電極

113c ドレイン電極

117 有機絶縁膜

121 開口部

123a 共通電極

123b ダミーパターン

123c 補助電極パターン

116 第1パッシベーション膜

127 第2パッシベーション膜

131a 画素電極コンタクトホール

131b 共通電極コンタクトホール

131c 共通配線コンタクトホール

133a 画素電極

133b 共通接続パターン

141 上部基板

143 ブラックマトリクス

145 カラーフィルタ層

147 柱状スペーサ

151 液晶層

【特許請求の範囲】

【請求項1】

基板の一面に一方向に形成されたゲート配線と、

前記ゲート配線と交差して画素領域を定義するデータ配線と、

前記ゲート配線と前記データ配線との交差地点に形成された薄膜トランジスタと、

前記薄膜トランジスタを含む基板全面に形成され、前記薄膜トランジスタを露出する開口部を備えた有機絶縁膜と、

前記有機絶縁膜の上部に形成された大面積の共通電極と、

前記有機絶縁膜の上部に形成され、前記開口部から前記薄膜トランジスタに接続された補助電極パターンと、

前記共通電極及び前記補助電極パターンを含む基板全面に形成され、前記薄膜トランジスタに接続された補助電極パターンを露出するパッシベーション膜と、

前記パッシベーション膜の上部に形成され、前記露出した補助電極パターンを介して前記薄膜トランジスタに電気的に接続され、前記共通電極とオーバーラップする複数の画素電極と

を含むことを特徴とする液晶表示装置用アレイ基板。

【請求項2】

前記開口部は、前記有機絶縁膜内に形成され、前記薄膜トランジスタの上部にオーバーラップしていることを特徴とする請求項1に記載の液晶表示装置用アレイ基板。

【請求項3】

前記画素電極は、前記補助電極パターン及び前記ドレイン電極に電気的に接続されていることを特徴とする請求項1に記載の液晶表示装置用アレイ基板。

【請求項4】

前記基板に前記ゲート配線と平行に配置された共通配線をさらに含むことを特徴とする請求項1に記載の液晶表示装置用アレイ基板。

【請求項5】

前記パッシベーション膜の上部に形成され、前記共通配線と前記共通電極とを接続する共通接続パターンをさらに含むことを特徴とする請求項4に記載の液晶表示装置用アレイ基板。

【請求項6】

前記ゲート配線と前記データ配線とが交差して形成される画素領域に形成されたカラーフィルタ層をさらに含むことを特徴とする請求項1に記載の液晶表示装置用アレイ基板。

【請求項7】

基板の一面に一方向にゲート配線を形成する段階と、

前記ゲート配線と交差して画素領域を定義するデータ配線を形成する段階と、

前記ゲート配線と前記データ配線との交差地点に薄膜トランジスタを形成する段階と、

前記薄膜トランジスタを含む基板全面に前記薄膜トランジスタを露出する開口部を備えた有機絶縁膜を形成する段階と、

前記有機絶縁膜の上部に、大面積の共通電極、及び前記開口部から前記薄膜トランジスタに接続される補助電極パターンを形成する段階と、

前記共通電極及び前記補助電極パターンを含む基板全面に前記薄膜トランジスタに接続された補助電極パターンを露出するパッシベーション膜を形成する段階と、

前記パッシベーション膜の上部に、前記露出した補助電極パターンを介して前記薄膜トランジスタに電気的に接続され、前記共通電極とオーバーラップする複数の画素電極を形成する段階と

を含むことを特徴とする液晶表示装置用アレイ基板の製造方法。

【請求項8】

前記開口部は、前記有機絶縁膜内に形成され、前記薄膜トランジスタの上部にオーバーラップしていることを特徴とする請求項7に記載の液晶表示装置用アレイ基板の製造方法。

【請求項9】

前記画素電極は、前記補助電極パターン及び前記ドレイン電極に電気的に接続されていることを特徴とする請求項7に記載の液晶表示装置用アレイ基板の製造方法。

【請求項10】

前記ゲート配線を形成する際に、前記ゲート配線と平行に共通配線を形成することを特徴とする請求項7に記載の液晶表示装置用アレイ基板の製造方法。

【請求項11】

前記画素電極を形成する際に、前記パッシベーション膜の上部に前記共通配線と前記共通電極とを接続する共通接続パターンを形成することを特徴とする請求項10に記載の液晶表示装置用アレイ基板の製造方法。

【請求項12】

前記ゲート配線と前記データ配線とが交差して形成される画素領域にカラーフィルタ層を形成する段階をさらに含むことを特徴とする請求項7に記載の液晶表示装置用アレイ基板の製造方法。

【請求項1】

基板の一面に一方向に形成されたゲート配線と、

前記ゲート配線と交差して画素領域を定義するデータ配線と、

前記ゲート配線と前記データ配線との交差地点に形成された薄膜トランジスタと、

前記薄膜トランジスタを含む基板全面に形成され、前記薄膜トランジスタを露出する開口部を備えた有機絶縁膜と、

前記有機絶縁膜の上部に形成された大面積の共通電極と、

前記有機絶縁膜の上部に形成され、前記開口部から前記薄膜トランジスタに接続された補助電極パターンと、

前記共通電極及び前記補助電極パターンを含む基板全面に形成され、前記薄膜トランジスタに接続された補助電極パターンを露出するパッシベーション膜と、

前記パッシベーション膜の上部に形成され、前記露出した補助電極パターンを介して前記薄膜トランジスタに電気的に接続され、前記共通電極とオーバーラップする複数の画素電極と

を含むことを特徴とする液晶表示装置用アレイ基板。

【請求項2】

前記開口部は、前記有機絶縁膜内に形成され、前記薄膜トランジスタの上部にオーバーラップしていることを特徴とする請求項1に記載の液晶表示装置用アレイ基板。

【請求項3】

前記画素電極は、前記補助電極パターン及び前記ドレイン電極に電気的に接続されていることを特徴とする請求項1に記載の液晶表示装置用アレイ基板。

【請求項4】

前記基板に前記ゲート配線と平行に配置された共通配線をさらに含むことを特徴とする請求項1に記載の液晶表示装置用アレイ基板。

【請求項5】

前記パッシベーション膜の上部に形成され、前記共通配線と前記共通電極とを接続する共通接続パターンをさらに含むことを特徴とする請求項4に記載の液晶表示装置用アレイ基板。

【請求項6】

前記ゲート配線と前記データ配線とが交差して形成される画素領域に形成されたカラーフィルタ層をさらに含むことを特徴とする請求項1に記載の液晶表示装置用アレイ基板。

【請求項7】

基板の一面に一方向にゲート配線を形成する段階と、

前記ゲート配線と交差して画素領域を定義するデータ配線を形成する段階と、

前記ゲート配線と前記データ配線との交差地点に薄膜トランジスタを形成する段階と、

前記薄膜トランジスタを含む基板全面に前記薄膜トランジスタを露出する開口部を備えた有機絶縁膜を形成する段階と、

前記有機絶縁膜の上部に、大面積の共通電極、及び前記開口部から前記薄膜トランジスタに接続される補助電極パターンを形成する段階と、

前記共通電極及び前記補助電極パターンを含む基板全面に前記薄膜トランジスタに接続された補助電極パターンを露出するパッシベーション膜を形成する段階と、

前記パッシベーション膜の上部に、前記露出した補助電極パターンを介して前記薄膜トランジスタに電気的に接続され、前記共通電極とオーバーラップする複数の画素電極を形成する段階と

を含むことを特徴とする液晶表示装置用アレイ基板の製造方法。

【請求項8】

前記開口部は、前記有機絶縁膜内に形成され、前記薄膜トランジスタの上部にオーバーラップしていることを特徴とする請求項7に記載の液晶表示装置用アレイ基板の製造方法。

【請求項9】

前記画素電極は、前記補助電極パターン及び前記ドレイン電極に電気的に接続されていることを特徴とする請求項7に記載の液晶表示装置用アレイ基板の製造方法。

【請求項10】

前記ゲート配線を形成する際に、前記ゲート配線と平行に共通配線を形成することを特徴とする請求項7に記載の液晶表示装置用アレイ基板の製造方法。

【請求項11】

前記画素電極を形成する際に、前記パッシベーション膜の上部に前記共通配線と前記共通電極とを接続する共通接続パターンを形成することを特徴とする請求項10に記載の液晶表示装置用アレイ基板の製造方法。

【請求項12】

前記ゲート配線と前記データ配線とが交差して形成される画素領域にカラーフィルタ層を形成する段階をさらに含むことを特徴とする請求項7に記載の液晶表示装置用アレイ基板の製造方法。

【図1】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図4F】

【図4G】

【図4H】

【図4I】

【図4J】

【図4K】

【図4L】

【図4M】

【図4N】

【図4O】

【図4P】

【図4Q】

【図5】

【図6】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図4F】

【図4G】

【図4H】

【図4I】

【図4J】

【図4K】

【図4L】

【図4M】

【図4N】

【図4O】

【図4P】

【図4Q】

【図5】

【図6】

【公開番号】特開2013−109347(P2013−109347A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2012−250783(P2012−250783)

【出願日】平成24年11月15日(2012.11.15)

【出願人】(501426046)エルジー ディスプレイ カンパニー リミテッド (732)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成24年11月15日(2012.11.15)

【出願人】(501426046)エルジー ディスプレイ カンパニー リミテッド (732)

【Fターム(参考)】

[ Back to top ]