FPGAのコンフィギュレーション制御回路、FPGA装置及び方法、並びに、コンフィギュレーションデータ更新方法

【課題】メモリ領域に格納されているコンフィギュレーションデータを直接読み出してコンフィギュレーションを実施するFPGAのコンフィギュレーションを高い信頼性をもって確実に行えるコンフィギュレーション制御回路、FPGA装置及び方法を提供する。

【解決手段】FROM12には、同じ内容のコンフィギュレーションデータが複数個格納されている。信号制御部08が、FPGA01にコンフィギュレーションのトリガを与えると、FPGA01は、FPGA01がデータの読み出し先として指定するFROM12の指定領域に格納されているデータを読み出して、コンフィギュレーションを行う。コンフィギュレーションが失敗した場合には、信号制御部08は、FROM12の指定領域を切り替え、FPGA01がFROM12の切り替え後の指定領域から別のデータを読み出してコンフィギュレーションするためのトリガをFPGA01に与える。

【解決手段】FROM12には、同じ内容のコンフィギュレーションデータが複数個格納されている。信号制御部08が、FPGA01にコンフィギュレーションのトリガを与えると、FPGA01は、FPGA01がデータの読み出し先として指定するFROM12の指定領域に格納されているデータを読み出して、コンフィギュレーションを行う。コンフィギュレーションが失敗した場合には、信号制御部08は、FROM12の指定領域を切り替え、FPGA01がFROM12の切り替え後の指定領域から別のデータを読み出してコンフィギュレーションするためのトリガをFPGA01に与える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、FPGA(Field Programmable Gate Array)のコンフィギュレーション制御回路及び方法、並びに、コンフィギュレーションデータ更新方法に関する。

【背景技術】

【0002】

FPGAは、集積回路であり、コンフィギュレーションデータを書き換えることにより、ハードウェア機能を変更することができる。GPGAは、この利便性により、汎用性の高いハードウェアとして、通信装置、情報処理装置等に広く使用されている。FPGAは、揮発性であるため、起動の度にユーザ回路をコンフィグレーションする必要がある。

【0003】

一般に、FPGAには複数のモードが用意されており、その一つにFROM(フラッシュメモリ)からコンフィギュレーションするモードがある。

【0004】

このモードでは、FPGAがFROMから読み出せるコンフィギュレーションデータは1つのみである。そのため、コンフィギュレーションデータの転送誤りによって失敗した場合には、同じコンフィギュレーションデータを再度読み込んでリコンフィギュレーションすることで復旧することは可能だが、FROMに格納されているコンフィギュレーションデータ自体が何らかの理由で破壊されている場合には、FPGAを復旧することができないという問題があった。

【0005】

この問題の解決法が、特許文献1から4に提案されている。

特許文献1では、同じ内容のコンフィギュレーションデータをそれぞれ格納する2つの領域と、制御部が読み出すコンフィギュレーションデータの格納面を示すフラグの領域とを有するメモリのフラグが示す領域から、制御部が読み出したコンフィギュレーションデータによるコンフィギュレーションが失敗した際に、フラグが示す領域とは別の領域に格納されている別のコンフィギュレーションデータを制御部が読み出して、FPGAのコンフィギュレーションを行う方法が提案されている。

【0006】

特許文献2では、通常のコンフィギュレーションデータと機能を限定したコンフィギュレーションデータを格納したメモリから制御部が読み出した通常のコンフィギュレーションデータによるコンフィギュレーションが失敗した際に、制御部は、限定されたコンフィギュレーションデータをメモリから読み出して、プログラマブル回路のコンフィギュレーションを行う方法が提案されている。

【0007】

特許文献3では、同じ内容のコンフィギュレーションデータが格納されている複数のメモリ設け、FPGAがコンフィギュレーションに失敗した際には、制御部はメモリを切り替え、切り替え後のメモリに格納されている別のコンフィギュレーションデータを読み出して、FPGAのコンフィギュレーションを行う方法が提案されている。

【0008】

特許文献4では、同じ内容のコンフィギュレーションデータを複数個格納するメモリから、制御部が選択したコンフィギュレーションデータを読み出してプログラマブル回路に転送する際に、読み出されたコンフィギュレーションデータにエラーが検出された場合は、制御部は、メモリから別のコンフィギュレーションデータを読み出して、プログラマブル回路のコンフィギュレーションを行う方法が提案されている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2005−191872公報

【特許文献2】特開2008−182327公報

【特許文献3】特開2010−066961公報

【特許文献4】特開2007−265056公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

特許文献1乃至4に提案されている方法では、メモリからのコンフィギュレーションデータの読み出しとFPGAへのデータ転送の制御を担う制御部が、コンフィギュレーションデータをFPGAに設定する。

このため、FPGAがコンフィギュレーションデータの読み出し先として指定するFROMの領域に格納されているコンフィギュレーションデータを、FPGAが直接読み出してコンフィギュレーションを実施する必要がある装置では、上記いずれの方法も採用することができない。

【0011】

また、コンフィギュレーションデータを適宜更新する場合あるが、従来のFPGAにおいては、更新データに誤りが合った場合には、復旧が困難となる場合があった。

【0012】

本発明は、上記実情に鑑みてなされたものであり、メモリ領域に格納されているコンフィギュレーションデータを直接読み出してコンフィギュレーションを実施するFPGA装置において、コンフィギュレーションを高い信頼性をもって行うことができるコンフィギュレーション制御回路及び方法を提供すること目的とする。

また、さらに、メモリ領域に格納されているコンフィギュレーションデータを直接読み出してコンフィギュレーションを実施するFPGA装置のコンフィギュレーションデータの更新を高い信頼性をもって確実に行えるコンフィギュレーションデータ更新方法を提供することを目的とする。

【課題を解決するための手段】

【0013】

上記目的を達成するため、本発明の第1の観点に係るコンフィギュレーション制御回路は、

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の領域を有する不揮発性メモリと、コンフィギュレーションデータの読み出し先として指定されている不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAとを備えるFPGA装置のコンフィギュレーション制御回路であって、

前記FPGAのコンフィギュレーションの開始からの経過時間を監視するタイマと、

前記タイマの設定時間が満了した際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAコンフィギュレーションが成功したか否かを判定する判定部と、

前記判定部により、コンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替える切替部と、

前記FPGAが前記切替部により切り替えられた前記不揮発性メモリの領域からコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える制御部と、

を具備することを特徴とする。

【0014】

また、本発明の第2の観点に係るFPGA装置は、

FPGAと、

この発明に係るコンフィギュレーション制御回路と、を備える。

【0015】

また、本発明の第3の観点に係るコンフィギュレーション方法は、

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の不揮発性メモリの領域のうち、コンフィギュレーションデータの読み出し先として指定されている不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAのコンフィギュレーション方法であって、

コンフィギュレーション開始からの経過時間を計測し、

前記経過時間が設定時間を超えた際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAのコンフィギュレーションが成功したか否かを判定し、

コンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替え、

指定を切り替えた後の不揮発性メモリの指定領域からコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とする。

【0016】

また、本発明の第4の観点に係るコンフィギュレーションデータ更新方法は、

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の領域を有する不揮発性メモリと、コンフィギュレーションデータの読み出し先として指定している前記不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAとを備えるFPGA装置のコンフィギュレーションデータ更新方法であって、

前記FPGA装置の電源がON又はリセットされた後最初の読み出し先として指定される前記不揮発性メモリの指定領域に格納されているコンフィギュレーションデータを更新データに書き換え、

前記FPGAのコンフィギュレーションを起動し、

前記FPGAのコンフィギュレーション開始からの経過時間を計測し、

前記経過時間が設定時間を超えた際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAのコンフィギュレーションが成功したか否かを判定し、

更新データによるコンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替え、

指定を切り替えた後の前記不揮発性メモリの指定領域から更新前のコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とする。

【発明の効果】

【0017】

本発明によれば、同じ内容のコンフィギュレーションデータを複数個格納し、FPGAがコンフィギュレーションに失敗したと判定された際に、FPGAが別のコンフィギュレーションデータを読み出してリコンフィギュレーションするようにした。こうすることで、FPGAの信頼性を向上させることができる。

【0018】

また、本発明によれば、コンフィギュレーションが失敗したと判定された際に、FPGAがコンフィギュレーションデータの読み出し先として指定する域を切り替え、FPGAが切り替え後の指定領域に格納されている別のコンフィギュレーションデータを読み出せる構成とした。こうすることで、上記特許文献1乃至4にて提案されている方法が適用できない、FPGAが読み出し先として指定する不揮発性メモリの領域に格納されているコンフィギュレーションデータを、FPGAが直接読み出してコンフィギュレーションする必要がある装置に適用することができる。

【0019】

また、本発明のコンフィギュレーションデータ更新方法によれば、コンフィギュレーションデータの更新時に、電源がON又はリセットされた後最初の読み出し先として指定する領域に格納されているコンフィギュレーションデータを更新データに書き換えるようにした。こうすることで、仮に更新データの不具合のために、更新データによるコンフィギュレーションに失敗したとしても、別の領域に格納されている更新前のコンフィギュレーションデータにより、FPGAはコンフィギュレーションできる。この結果、専用端末をFPGAに接続する事無く更新作業を続ける事が可能となり、コンフィギュレーションデータの更新時における、作業効率とFPGAの信頼性を向上させることができる。

【図面の簡単な説明】

【0020】

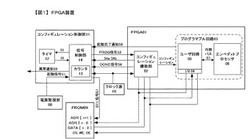

【図1】本実施形態のFPGA装置の構成を示すブロック図である。

【図2】信号制御部14とFROM09とを接続するアドレス線が1ビットの場合の 、概略のFPGA装置のブロック図である。

【図3】アドレス線が1ビットの場合の、FROM09に格納されているコンフィギ ュレーションデータ等のメモリマップのイメージ図である。

【図4】本実施形態の処理手順を示すフローチャートである。

【図5】信号制御部14とFROM09とを接続するアドレス線が2ビットの場合の 、概略のFPGA装置のブロック図である。

【図6】アドレス線が2ビットの場合の、FROM09に格納されているコンフィギ ュレーションデータ等のメモリマップのイメージ図である。

【発明を実施するための形態】

【0021】

本発明の実施形態について、図面を参照して詳細に説明する。

(実施形態)

【0022】

図1に示すように、本実施形態のFPGAを搭載する装置(以下、FPGA装置)は、FPGA01、電源監視部08、FROM09、クロック源10及びコンフィギュレーション制御部11(例えば、コンフィギュレーション制御回路)から構成されている。

FPGA(Field Programmable Gate Array)01は、コンフィギュレーション機能部02とプログラマブル回路03とから構成されている。

【0023】

コンフィギュレーション機能部02は、FPGA01に予め具備されている機能部であり、プログラマブル回路03、FROM09及び信号制御部14と接続されている。

【0024】

プログラマブル回路03は、インターフェースI/O04を備えるユーザ回路05と、エンベディトプロセッサ06と、から構成されている。ユーザ回路05とエンベディトプロセッサ06は内部バス07で接続されている。

【0025】

ユーザ回路05は、ユーザが作成したコンフィギュレーションデータに基づき任意の機能を設定できる回路である。ユーザ回路05は、コンフィギュレーション機能部02がPROG信号S2を受信したのをトリガとして、インターフェースI/O04を介してFROM09の指定された領域に格納されているコンフィギュレーションデータを読み出してコンフィギュレーションを実施する。

【0026】

エンベデットプロセッサ06は、FPGA01のプログラマブル回路03にCPUコアと周辺回路を組み込むことにより実現するプロセッサである。エンベデットプロセッサ06は、FPGA01のコンフィギュレーション完了後に、ユーザ回路05のインターフェースI/O04を介してFROM09の指定されている領域に格納されているエンベデットプロセッサ・プログラム(IPLやOSを含む)を読み出して動作する。

なお、本実施形態においては、プログラマブル回路03は、エンベデットプロセッサ06を実装する構成としたが、ユーザ回路05のみを備える構成でもよい。

【0027】

FPGA01は、コンフィギュレーションデータを書き換えることにより、ハード機能を変更することが可能な集積回路である。FPGA01は、揮発性であるため、起動の度にユーザ回路05をコンフィギュレーションする必要がある。複数のコンフィギュレーションモードが用意されているが、本実施形態のようにFPGA01にCPUコアを組み込み(エンベデットプロセッサ06)、装置の制御をFPGA01のみが担う場合は、FPGA01がコンフィギュレーションデータの読み出し先として指定するFROM09の領域(一般には、FROM09の先頭アドレス)に格納されているコンフィギュレーションデータを、FPGA01が直接読み出してコンフィギュレーションを実施するモードが使用される。

【0028】

電源監視部08は、装置の電源ON、OFF、又は、リセットの制御を行う。また、信号制御部14と接続され、FPGA01や周辺デバイスの所定のシーケンスに従って起動タイミングを計り(一般には、入力電源電圧が安定後に)、信号制御部14に対して、起動信号S1を出力する。

【0029】

FROM09は、不揮発メモリである。本実施形態では、FROM09は、同じ内容のコンフィギュレーションデータと同じ内容のエンベデットプロセッサ・プログラムが一組ずつ格納される複数の領域を有している。また、FROM09は、信号制御部14とアドレス線で接続され、FPGA01がコンフィギュレーションに失敗した際に、信号制御部14が面選択信号S7(以下、SEL信号S7)の設定値(FROM09の指定領域の最上位ビットの論理)を順次切り替えることで、FPGA01がコンフィギュレーションデータの読み出し先として指定するFROM09の領域が切り替えられる。電源ON又はリセット時におけるSEL信号S7の初期設定値は、本実施形態では、”0”とし、コンフィギュレーション及びエンベデットプロセッサの起動が失敗する度に、+1加算される。

【0030】

コンフィギュレーション制御部11は、タイマ12と、カウンタ13を備える信号制御部14と、から構成されている。

【0031】

タイマ12は、クロック源10に同期して動作するカウンタで、FPGA01のコンフィギュレーションの完了とエンベデットプロセッサ06の正常起動を監視するためのものである。タイマ12の設定値は、FPGA01のコンフィギュレーションとエンベデットプロセッサ06の起動に要する時間よりも長くそれぞれ設定する。

【0032】

カウンタ13は、信号制御部14が電源ON又はリセット後のコンフィギュレーションの回数を管理するためのカウンタである。電源ON又はリセット時における、初期設定値を”1”とし、FPGA01のコンフィギュレーション又はエンベデットプロセッサ06の起動が失敗する度に、+1加算される。つまり、カウンタ値がk−1の時にコンフィギュレーション又はエンベデットプロセッサ06の起動に失敗した際は、信号制御部14により、SEL信号S7の設定値はk−1からkに切り替えられることになる。

【0033】

信号制御部14は、FPGA01、電源監視部08、FROM09及びタイマ12と接続され、PROG信号S2、スタート信号S3、SEL信号S7等を制御する。また、信号制御部14は、コンフィギュレーションの完了とエンベデットプロセッサ06の正常起動を判定する。また、信号制御部14は、コンフィギュレーション又はエンベデットプロセッサ06の起動に失敗した際に、FPGA01がコンフィギュレーションデータの読み出し先として指定するFROM09の領域を切り替える。

【0034】

次に、図2、3を参照して、FROM09について詳細に説明する。

上述のように、FROM09には、同一のコンフィギュレーションデータとエンベデットプロセッサ・プログラムとの組がn組記憶されている。図2,3は、n=2,即ち、2組のコンフィギュレーションデータとエンベデットプロセッサ・プログラムとがFROM09に記憶されている場合の例である。

【0035】

図3は、この場合の、FROM09に格納されているコンフィギュレーションデータ及びエンベデットプロセッサ・プログラムのメモリマップのイメージである。ただし、FROM09の容量を128Kバイトとしている。

【0036】

図2に示すように、FROM09の最上位ビット(ビット17)は信号制御部14に、下位ビット(ビット16〜0)はFPGA01に接続されている。この場合、FPGA01が使用するデータの格納領域は、0x0_0000〜0x0_FFFFと0x1_0000〜0x1_FFFFとなる。そして、SEL信号S7の設定値が”0”の場合は、FPGA01はFROM09の最上位ビットが”0”の領域(0x0_0000〜0x0_FFFF)のデータを使用し、信号制御部14がSEL信号S7の設定値を”1”に切り替えた場合は、FPGA01はFROM09の最上位ビットが”1”の領域(0x1_0000〜0x1_FFFF)のデータを使用する。

【0037】

コンフィギュレーションデータは、この2つの領域の各先頭部分(アドレス0x0_0000〜0x0_AFFFと0x1_0000〜0x1_AFFF)に格納される。

【0038】

このように、信号制御部14とFROM09とを接続するアドレス線で制御できるデータのビット数がmビットの場合は、FROM09に格納できるコンフィギュレーションデータは最大で2m個となる。必ずしも、FROM09に、最大個数のコンフィギュレーションデータ等を格納する必要はなく、例えば、最大個数が8個(m=3)の場合に、コンフィギュレーションデータを5個だけ格納するようにしても構わない。

【0039】

次に、図1を参照して、電源ON又はリセットされた後の流れに沿って各信号について説明する。

【0040】

起動信号S1は、電源ON又はリセットされた後に、電源監視部08から信号制御部14に対して出力される信号である。

【0041】

PROG信号S2は、FPGA01がコンフィギュレーションをスタートするトリガとなる信号で、信号制御部14が、起動信号S1の受信をトリガとして、コンフィギュレーション機能部02に対して出力する。コンフィギュレーション機能部02のPROG信号S2の受信をトリガとして、FPGA01は内部メモリ(不図示)を初期化し、コンフィギュレーションをスタートする。また、PROG信号S2は、コンフィギュレーション又はエンベデットプロセッサ06の起動が失敗した際にも、コンフィギュレーションの回数kが所定回数n(FROM09に格納されているコンフィギュレーションデータの個数)未満の場合は、FPGA01にリコンフィギュレーションするためのトリガを与えるため、信号制御部14からコンフィギュレーション機能部02に対して出力される。

【0042】

スタート信号S3は、起動信号S1の受信をトリガとして、信号制御部14が、タイマ12をスタートさせるために、タイマ12に対して出力する信号である。また、信号制御部14は、FPGA01のコンフィギュレーションが完了した際にも、エンベデットプロセッサ06の起動を監視するために、タイマ12に対して、スタート信号S3を出力する。

【0043】

INIT信号S4aは、FPGA01の内部メモリ(不図示)の初期化が完了した際に、コンフィギュレーション機能部02から信号制御部14に対して出力される信号である。

【0044】

INIT信号S4bは、FPGA01のコンフィギュレーションが失敗した際に、CRCエラーを通知するため、コンフィギュレーション機能部02から信号制御部14に対して出力される信号である。なお、FPGAの中には、CRCエラーを別信号で通知するものも存在するが、その場合は、該別信号をINIT信号S4bの代わりに用いる。

【0045】

満了信号S5は、タイマ12の設定時間が満了した際に、タイマ12から信号制御部14に対して、出力される信号である。

【0046】

DONE信号S6は、FPGA01のコンフィギュレーションが完了した際に、コンフィギュレーション機能部02から信号制御部14に対して出力される信号である。信号制御部14は、タイマ12から満了信号S5を受信した時点で、INIT信号S4aと、DONE信号S6を受信していれば、FPGA01のコンフィギュレーションは完了したと判定し、それ以外は、コンフィギュレーションに失敗したと判定する。

【0047】

SEL信号S7は、FPGA01のコンフィギュレーション又はエンベデットプロセッサ06の起動に失敗した際に、コンフィギュレーションの回数kが所定回数n未満の場合に、信号制御部14がFROM09に対して出力する信号である。信号制御部14がSEL信号S7の設定値を切り替えることで、FPGA01がコンフィギュレーションデータの読み出し先として指定するFROM09の領域が切り替えられる。

【0048】

起動完了通知S8は、エンベデットプロセッサ06の正常起動を判定するための信号である。あらかじめFPGA01のユーザ回路05に機能として用意され、本実施形態では、初期設定は”0”とし、エンベデットプロセッサ06が正常起動した場合には、起動完了通知S6の設定を”1”にする。信号制御部14は、タイマ12から満了信号S5を受信した時点で、起動完了通知S8の設定が”1”であれば、エンベデットプロセッサ06が正常起動したと判定し、設定が”0”の場合は、起動に失敗したと判定する。

【0049】

異常通知S9は、コンフィギュレーション又はエンベデットプロセッサ06の起動に失敗した際に、コンフィギュレーションの回数kが所定回数nに達している場合に、信号制御部14が上位装置(不図示)に対して、FPGA01の異常を知らせるために出力する信号である。

【0050】

次に、図4を参照して、図1〜図3を参照して説明した本実施形態の処理手順について詳細に説明する。

この場合、FROM12に格納されているコンフィギュレーションデータの個数kは”2”となる。

【0051】

装置の電源をON又はリセットすると、カウンタ13のカウント値、SEL信号S7及び起動完了通知S8が初期化される(ステップS01)。電源監視部08は、所定のシーケンスに従って起動タイミングを計り、信号制御部14に起動信号S1を出力する(ステップS02)。そして、信号制御部14は、起動信号S1を受信すると、コンフィギュレーション機能部02に対して、PROG信号S2を出力すると共に、タイマ12をスタートさせる(ステップS03)。

【0052】

コンフィギュレーション機能部02がPROG信号S2を受信するのをトリガとして、FPGA01は、コンフィギュレーション機能部02内の内部メモリ(不図示)を初期化し、FROM09の指定領域(0x0_0000)に格納されているコンフィギュレーションデータを読み出して、この内部メモリに記憶し、記憶したコンフィグレーションデータに基づいて、コンフィギュレーションをスタートする(ステップS04)。

【0053】

タイマ12の設定時間が満了した時点で(ステップS05)、信号制御部14は、FPGA01のコンフィギュレーションが完了したか否かを判定する(ステップS06)。FPGA01のコンフィギュレーションが完了している場合には(ステップS08;YES)、エンベデットプロセッサ06は、FROM09の指定領域(0x0_1000)に格納されているエンベデットプロセッサ・プログラムを読み出して起動をスタートすると共に、信号制御部14は、タイマ12をスタートさせる(ステップS07)。

【0054】

タイマ12の設定時間が満了した時点で(ステップS08)、信号制御部14は、エンベデットプロセッサ06が正常起動したか否かを判定する(ステップS09)。起動完了通知S8の設定が”1”であれば(ステップS09;YES)、エンベデットプロセッサ06は正常起動となる。

【0055】

一方、タイマ12の設定時間が満了した時点で(ステップS05又はS08)、FPGA01のコンフィギュレーションが失敗した場合(ステップS06;NO)、又は、起動完了通知S8の設定が”1”でない場合には(ステップS09;NO)、信号制御部14は、カウンタ13により、コンフィギュレーションの回数が2回未満であるか否かを判定する(ステップS21)。

【0056】

コンフィギュレーションの回数はまだ1回目なので(ステップS21;YES)、信号制御部14は、カウンタ13のカウント数を+1加算し(ステップS22)、SEL信号S7の設定値を”1”に切り替え(ステップS23)、ステップS03に戻る。次に、信号制御部14は、コンフィギュレーション機能部02に対して、PROG信号S2を出力すると共に、タイマ12をスタートさせる(ステップS03)。

【0057】

コンフィギュレーション機能部02がPROG信号S2を受信するのをトリガとして、FPGA01は内部メモリ(不図示)を初期化して、FROM09の切り替え後の指定領域(0x1_0000)に格納されているコンフィギュレーションデータを読み出してコンフィギュレーションする(ステップS04)。

【0058】

そして、タイマ12の設定時間が満了した時点で(ステップS05)、信号制御部14は、FPGA01のコンフィギュレーションが完了したか否かを判定する(ステップS06)。FPGA01のコンフィギュレーションが完了している場合には(ステップS06;YES)、エンベデットプロセッサ06は、FROM09の切り替え後の指定領域(0x1_1000)に格納されているエンベデットプロセッサ・プログラムを読み出して起動をスタートすると共に、信号制御部14は、タイマ12をスタートさせる(ステップS07)。

【0059】

タイマ12の設定時間が満了した時点で(ステップS08)、信号制御部14は、エンベデットプロセッサ06が正常起動したか否かを判定する(ステップS09)。起動完了通知S8の設定が”1”であれば(ステップS09;YES)、エンベデットプロセッサ06は正常起動となる。

【0060】

一方、タイマ12の設定時間が満了した時点で(ステップS05又はS08)、FPGA01のコンフィギュレーションが失敗した場合(ステップS06;NO)、又は、起動完了通知S8の設定が”1”でない場合には(ステップS09;NO)、信号制御部14は、カウンタ13により、コンフィギュレーションの回数が2回未満であるか否かを判定する(ステップS21)。今回はコンフィギュレーションの回数が2回目なので(ステップS21;NO)、信号制御部14は、上位装置(不図示)に対して、異常通知S9を出力し(ステップS31)、処理を終了する。

【0061】

上記実施形態によれば、FROM09に同じ内容のコンフィギュレーションデータが複数個格納し、FPGA01は、コンフィギュレーションに失敗した場合、FROM09に格納されている別のコンフィギュレーションデータにより、リコンフィギュレーションする。こうすることで、FPGA01の信頼性を高めることができる。同様に、FROM09に同じ内容のエンベデットプロセッサ・プログラムを複数個さらに格納し、エンベデットプロセッサ06が起動に失敗した場合には、FROM09に格納されている別のエンベデットプロセッサ・プログラムにより、エンベデットプロセッサ06が再度起動する構成とした。こうすることで、エンベデットプロセッサ06を備えるFPGA01の信頼性を高めることができる。

【0062】

また、上記実施形態によれば、FPGA01のコンフィギュレーションが失敗した際に、FPGA01がコンフィギュレーションデータの読み出し先として指定するFROM09の指定領域を切り替え、FPGA01が切り替え後の指定領域に格納されている別のコンフィギュレーションデータを読み出せる構成とした。こうすることで、上記特許文献1乃至4にて提案されている方法が適用できない、FPGA01が読み出し先として指定するFROM09の領域に格納されているコンフィギュレーションデータを、FPGA01が直接読み出してコンフィギュレーションする必要がある装置に適用することができる。

【0063】

また、上記実施形態によれば、カウンタ13を設け、コンフィギュレーションの回数kが所定回数nに達した場合には(ステップS21;NO)、信号制御部14は、上位装置(不図示)に対して、異常通知S9を出力し処理を終了する構成とした。こうすることで、FROM09に格納されている全てのコンフィギュレーションデータが破壊されている場合に、FPGA01のリコンフィギュレーションがループすることを防止することができる。また、リコンフィギュレーションにより、FPGA01がコンフィギュレーションに成功した際にも、異常通知S9を出力するようにしてもよい。こうすることで、FROM09に格納されている全てのコンフィギュレーションデータが破壊される前に、破壊されたデータを修復する等の適切な対応を行うことができることから、さらに信頼性を高めることが可能となる。

【0064】

なお、上記実施形態の処理手順の説明では、図3を例にしたので、FROM09に格納されるコンフィギュレーションデータ等の個数は2個の構成とした。しかし、前述したように、信号制御部14とFROM09とを接続するアドレス線で制御できるデータのビット数を増やすことで、バックアップとしてFROM09に格納できるコンフィギュレーションデータの個数を増やすことが可能となる。こうすることで、さらに信頼性を高めることができる。例えば、図5のようにアドレス線を2ビットにした場合には、コンフィギュレーションデータ及びエンベデットプロセッサ・プログラムを4個ずつFROM09に格納できる(図6参照)。

【0065】

また、上記実施形態において、タイマ12の設定時間満了後に、コンフィギュレーションが成功したか否かを判定し、コンフィギュレーションが失敗した場合に、ステップS21に進む構成としたが、CRCエラーがINIT信号S4bにより信号制御部14に通知された時点で、ステップS21に進む構成としてもよい。こうすることで、より早い段階でリコンフィギュレーションを開始することが可能となる。

【0066】

上記実施形態において、タイマ12の設定値は、コンフィギュレーション制御部11の回路に対するハード設定等により、外部から変更できるようにしてもよい。こうすることで、ユーザが書き換えるデータに応じ、タイマ12の設定値を調整することが可能となる。

【0067】

FROM09は、不揮発性メモリであれば、他種のメモリでもよい。

【0068】

また、上記実施形態において、コンフィギュレーション制御部11にFROM09の破壊されたデータを自動で修復する機能を持たせてもよい。例えば、図6を参照して、4回目のコンフィギュレーションで、エンベデットプロセッサの起動まで成功した場合に、FROM09の0x0_0000、0x1_0000、0x2_0000にそれぞれ格納されているコンフィギュレーションデータを、エラーの無い0x3_0000に格納されているコンフィギュレーションデータで書き換える。同様に、FROM09の0x0_1000、0x1_1000、0x2_1000にそれぞれ格納されているエンベデットプロセッサ・プログラムを、エラーの無い0x3_1000に格納されているエンベデットプロセッサ・プログラムで書き換える。こうすることで、最上位ビットの数が同じ領域に格納されているコンフィギュレーションデータ及びエンベデットプロセッサ・プログラムが少なくとも1組正常であれば、自動的にエラーのある全てのコンフィギュレーションデータ及びエンベデットプロセッサ・プログラムを修復できる。この結果、FPGA01の信頼性をさらに高めることができる。なお、自動修復機能は、コンフィギュレーションデータにより実現させるようにしてもよい。

【0069】

上記自動修復機能を用いることで、コンフィギュレーションが失敗した際に、コンフィギュレーションの回数kが所定回数nに達している場合においても、エンベデットプロセッサ06の起動まで導ける可能性が生じる。例えば、図6を参照して、1回目と3回目と4回目はコンフィギュレーションに失敗し、2回目はコンフィギュレーションに成功したが、エンベデットプロセッサ06の起動に失敗した場合に、エラーのない0x1_0000に格納されているコンフィギュレーションデータで、0x0_0000、0x2_0000、0x3_0000に格納されているコンフィギュレーションデータを書き換える。そして、電源をリセットさせる。こうすることで、0x0_1000、0x2_1000、0x3_1000にそれぞれ格納されているエンベデットプロセッサ・プログラムのいずれかが正常であれば、エンベデットプロセッサ06の起動まで導くことが可能となる。

【0070】

また、本発明を用いることで、コンフィギュレーションデータ更新時における、FPGA01の信頼性を高めることが可能となる。例えば、コンフィギュレーションデータの更新を行う際に、コンフィギュレーションデータの更新データで、FROM09の初期指定領域(電源がON又はリセットされた後に、FPGA01が最初に読み出すコンフィギュレーションデータが格納されているFROM09の領域。例えば、図3では、0x0_0000領域。)に格納されているコンフィギュレーションデータを更新する。電源をON又はリセットすると、上記実施形態のフローに基づいて、FPGA01は最初に該更新データを読み出してコンフィギュレーションを行う。更新データに何らかの不具合があったために、更新データによるコンフィギュレーションに失敗した場合には、上記実施形態のフローに基づいて、更新前のコンフィギュレーションデータによりFPGA01はリコンフィギュレーションを行うことができる。一方、更新データによるコンフィギュレーションが成功した場合には、FROM09の他の領域に格納されている更新前のコンフィギュレーションデータを更新データに書き換える。

【0071】

こうすることで、更新データの不具合のために、FPGA01が更新データによるコンフィギュレーションに失敗したとしても、FROM09の別の領域に格納されている更新前のコンフィギュレーションデータにより、FPGA01はリコンフィギュレーションできる。この結果、専用端末(不図示)をFPGA01に接続する事無く更新作業を続ける事が可能となり、コンフィギュレーションデータの更新時における、作業効率とFPGA01の信頼性を一層向上させることができる。

【0072】

なお、上記実施形態及び図面の一部又は全部は、以下の付記のようにも記載されうるが、以下に限定されるわけではない。本発明の要旨を変更しない範囲で実施形態及び図面に変更を加えることができるのはもちろんである。

【0073】

(付記1)

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の領域を有する不揮発性メモリと、コンフィギュレーションデータの読み出し先として指定されている不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAとを備えるFPGA装置のコンフィギュレーション制御回路であって、

前記FPGAのコンフィギュレーションの開始からの経過時間を監視するタイマと、

前記タイマの設定時間が満了した際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAコンフィギュレーションが成功したか否かを判定する判定部と、

前記判定部により、コンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替える切替部と、

前記FPGAが前記切替部により切り替えられた前記不揮発性メモリの領域からコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える制御部と、

を具備することを特徴とするコンフィギュレーション制御回路。

【0074】

(付記2)

前記不揮発性メモリの複数の領域に、同一内容のエンベデットプロセッサ・プログラムがそれぞれさらに格納され、

前記FPGAは、FPGAのコンフィギュレーション完了後に前記不揮発性メモリの指定領域に格納されているエンベデットプロセッサ・プログラムを読み出して起動を開始するエンベデットプロセッサを備え、

前記タイマは、前記エンベデットプロセッサの起動開始からの経過時間をさらに監視し、前記タイマの設定時間が満了した際に、前記エンベデットプロセッサの起動完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記判定部は、前記エンベデットプロセッサの起動が成功したか否かをさらに判定し、前記エンベデットプロセッサの起動が失敗したと判定された際に、前記切替部は、前記不揮発性メモリの指定領域を切り替え、前記制御部は、前記FPGAが前記切替部により切り替えられた前記不揮発性メモリの指定領域から別のコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とする付記1に記載のコンフィギュレーション制御回路。

【0075】

(付記3)

前記制御部は、コンフィギュレーションに失敗したコンフィギュレーションデータを、コンフィギュレーションに成功した別のコンフィギュレーションデータに書き換えることにより、前記不揮発性メモリに格納されているデータを修復する、

ことを特徴とする付記1に記載のコンフィギュレーション制御回路。

【0076】

(付記4)

前記制御部は、エンベデットプロセッサの起動に失敗したエンベデットプロセッサ・プログラムを、起動に成功したエンベデットプロセッサ・プログラムに書き換えることにより、前記不揮発性メモリに格納されているデータを修復する、

ことを特徴とする付記2に記載のコンフィギュレーション制御回路。

【0077】

(付記5)

FPGAと、

付記1乃至4の何れか1項に記載のコンフィギュレーション制御回路と、を備えるFPGA装置。

【0078】

(付記6)

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の不揮発性メモリの領域のうち、コンフィギュレーションデータの読み出し先として指定されている不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAのコンフィギュレーション方法であって、

コンフィギュレーション開始からの経過時間を計測し、

前記経過時間が設定時間を超えた際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAのコンフィギュレーションが成功したか否かを判定し、

コンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替え、

指定を切り替えた後の不揮発性メモリの指定領域からコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とするコンフィギュレーション方法。

【0079】

(付記7)

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の領域を有する不揮発性メモリと、コンフィギュレーションデータの読み出し先として指定している前記不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAとを備えるFPGA装置のコンフィギュレーションデータ更新方法であって、

前記FPGA装置の電源がON又はリセットされた後最初の読み出し先として指定される前記不揮発性メモリの指定領域に格納されているコンフィギュレーションデータを更新データに書き換え、

前記FPGAのコンフィギュレーションを起動し、

前記FPGAのコンフィギュレーション開始からの経過時間を計測し、

前記経過時間が設定時間を超えた際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAのコンフィギュレーションが成功したか否かを判定し、

更新データによるコンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替え、

指定を切り替えた後の前記不揮発性メモリの指定領域から更新前のコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とするコンフィギュレーションデータ更新方法。

【0080】

(付記8)

前記更新データによるコンフィギュレーションが成功した際に、前記不揮発性メモリに格納されている更新前のコンフィギュレーションデータを更新データに書き換える、

ことを特徴とする付記7に記載のコンフィギュレーションデータ更新方法。

【符号の説明】

【0081】

01 FPGA

02 コンフィギュレーション機能部

03 プログラマブル回路

04 インターフェース

05 ユーザ回路

06 エンベデットプロセッサ

07 内部バス

08 電源監視部

09 FROM

10 クロック源

11 コンフィギュレーション制御部

12 タイマ

13 カウンタ

14 信号制御部

S1 起動信号

S2 PROG信号

S3 スタート信号

S4a 初期化完了信号(INIT信号)

S4b CRCエラー信号(INIT信号)

S5 満了信号

S6 DONE信号

S7 SEL信号

S8 起動完了通知

S9 異常通知

【技術分野】

【0001】

本発明は、FPGA(Field Programmable Gate Array)のコンフィギュレーション制御回路及び方法、並びに、コンフィギュレーションデータ更新方法に関する。

【背景技術】

【0002】

FPGAは、集積回路であり、コンフィギュレーションデータを書き換えることにより、ハードウェア機能を変更することができる。GPGAは、この利便性により、汎用性の高いハードウェアとして、通信装置、情報処理装置等に広く使用されている。FPGAは、揮発性であるため、起動の度にユーザ回路をコンフィグレーションする必要がある。

【0003】

一般に、FPGAには複数のモードが用意されており、その一つにFROM(フラッシュメモリ)からコンフィギュレーションするモードがある。

【0004】

このモードでは、FPGAがFROMから読み出せるコンフィギュレーションデータは1つのみである。そのため、コンフィギュレーションデータの転送誤りによって失敗した場合には、同じコンフィギュレーションデータを再度読み込んでリコンフィギュレーションすることで復旧することは可能だが、FROMに格納されているコンフィギュレーションデータ自体が何らかの理由で破壊されている場合には、FPGAを復旧することができないという問題があった。

【0005】

この問題の解決法が、特許文献1から4に提案されている。

特許文献1では、同じ内容のコンフィギュレーションデータをそれぞれ格納する2つの領域と、制御部が読み出すコンフィギュレーションデータの格納面を示すフラグの領域とを有するメモリのフラグが示す領域から、制御部が読み出したコンフィギュレーションデータによるコンフィギュレーションが失敗した際に、フラグが示す領域とは別の領域に格納されている別のコンフィギュレーションデータを制御部が読み出して、FPGAのコンフィギュレーションを行う方法が提案されている。

【0006】

特許文献2では、通常のコンフィギュレーションデータと機能を限定したコンフィギュレーションデータを格納したメモリから制御部が読み出した通常のコンフィギュレーションデータによるコンフィギュレーションが失敗した際に、制御部は、限定されたコンフィギュレーションデータをメモリから読み出して、プログラマブル回路のコンフィギュレーションを行う方法が提案されている。

【0007】

特許文献3では、同じ内容のコンフィギュレーションデータが格納されている複数のメモリ設け、FPGAがコンフィギュレーションに失敗した際には、制御部はメモリを切り替え、切り替え後のメモリに格納されている別のコンフィギュレーションデータを読み出して、FPGAのコンフィギュレーションを行う方法が提案されている。

【0008】

特許文献4では、同じ内容のコンフィギュレーションデータを複数個格納するメモリから、制御部が選択したコンフィギュレーションデータを読み出してプログラマブル回路に転送する際に、読み出されたコンフィギュレーションデータにエラーが検出された場合は、制御部は、メモリから別のコンフィギュレーションデータを読み出して、プログラマブル回路のコンフィギュレーションを行う方法が提案されている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2005−191872公報

【特許文献2】特開2008−182327公報

【特許文献3】特開2010−066961公報

【特許文献4】特開2007−265056公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

特許文献1乃至4に提案されている方法では、メモリからのコンフィギュレーションデータの読み出しとFPGAへのデータ転送の制御を担う制御部が、コンフィギュレーションデータをFPGAに設定する。

このため、FPGAがコンフィギュレーションデータの読み出し先として指定するFROMの領域に格納されているコンフィギュレーションデータを、FPGAが直接読み出してコンフィギュレーションを実施する必要がある装置では、上記いずれの方法も採用することができない。

【0011】

また、コンフィギュレーションデータを適宜更新する場合あるが、従来のFPGAにおいては、更新データに誤りが合った場合には、復旧が困難となる場合があった。

【0012】

本発明は、上記実情に鑑みてなされたものであり、メモリ領域に格納されているコンフィギュレーションデータを直接読み出してコンフィギュレーションを実施するFPGA装置において、コンフィギュレーションを高い信頼性をもって行うことができるコンフィギュレーション制御回路及び方法を提供すること目的とする。

また、さらに、メモリ領域に格納されているコンフィギュレーションデータを直接読み出してコンフィギュレーションを実施するFPGA装置のコンフィギュレーションデータの更新を高い信頼性をもって確実に行えるコンフィギュレーションデータ更新方法を提供することを目的とする。

【課題を解決するための手段】

【0013】

上記目的を達成するため、本発明の第1の観点に係るコンフィギュレーション制御回路は、

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の領域を有する不揮発性メモリと、コンフィギュレーションデータの読み出し先として指定されている不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAとを備えるFPGA装置のコンフィギュレーション制御回路であって、

前記FPGAのコンフィギュレーションの開始からの経過時間を監視するタイマと、

前記タイマの設定時間が満了した際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAコンフィギュレーションが成功したか否かを判定する判定部と、

前記判定部により、コンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替える切替部と、

前記FPGAが前記切替部により切り替えられた前記不揮発性メモリの領域からコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える制御部と、

を具備することを特徴とする。

【0014】

また、本発明の第2の観点に係るFPGA装置は、

FPGAと、

この発明に係るコンフィギュレーション制御回路と、を備える。

【0015】

また、本発明の第3の観点に係るコンフィギュレーション方法は、

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の不揮発性メモリの領域のうち、コンフィギュレーションデータの読み出し先として指定されている不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAのコンフィギュレーション方法であって、

コンフィギュレーション開始からの経過時間を計測し、

前記経過時間が設定時間を超えた際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAのコンフィギュレーションが成功したか否かを判定し、

コンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替え、

指定を切り替えた後の不揮発性メモリの指定領域からコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とする。

【0016】

また、本発明の第4の観点に係るコンフィギュレーションデータ更新方法は、

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の領域を有する不揮発性メモリと、コンフィギュレーションデータの読み出し先として指定している前記不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAとを備えるFPGA装置のコンフィギュレーションデータ更新方法であって、

前記FPGA装置の電源がON又はリセットされた後最初の読み出し先として指定される前記不揮発性メモリの指定領域に格納されているコンフィギュレーションデータを更新データに書き換え、

前記FPGAのコンフィギュレーションを起動し、

前記FPGAのコンフィギュレーション開始からの経過時間を計測し、

前記経過時間が設定時間を超えた際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAのコンフィギュレーションが成功したか否かを判定し、

更新データによるコンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替え、

指定を切り替えた後の前記不揮発性メモリの指定領域から更新前のコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とする。

【発明の効果】

【0017】

本発明によれば、同じ内容のコンフィギュレーションデータを複数個格納し、FPGAがコンフィギュレーションに失敗したと判定された際に、FPGAが別のコンフィギュレーションデータを読み出してリコンフィギュレーションするようにした。こうすることで、FPGAの信頼性を向上させることができる。

【0018】

また、本発明によれば、コンフィギュレーションが失敗したと判定された際に、FPGAがコンフィギュレーションデータの読み出し先として指定する域を切り替え、FPGAが切り替え後の指定領域に格納されている別のコンフィギュレーションデータを読み出せる構成とした。こうすることで、上記特許文献1乃至4にて提案されている方法が適用できない、FPGAが読み出し先として指定する不揮発性メモリの領域に格納されているコンフィギュレーションデータを、FPGAが直接読み出してコンフィギュレーションする必要がある装置に適用することができる。

【0019】

また、本発明のコンフィギュレーションデータ更新方法によれば、コンフィギュレーションデータの更新時に、電源がON又はリセットされた後最初の読み出し先として指定する領域に格納されているコンフィギュレーションデータを更新データに書き換えるようにした。こうすることで、仮に更新データの不具合のために、更新データによるコンフィギュレーションに失敗したとしても、別の領域に格納されている更新前のコンフィギュレーションデータにより、FPGAはコンフィギュレーションできる。この結果、専用端末をFPGAに接続する事無く更新作業を続ける事が可能となり、コンフィギュレーションデータの更新時における、作業効率とFPGAの信頼性を向上させることができる。

【図面の簡単な説明】

【0020】

【図1】本実施形態のFPGA装置の構成を示すブロック図である。

【図2】信号制御部14とFROM09とを接続するアドレス線が1ビットの場合の 、概略のFPGA装置のブロック図である。

【図3】アドレス線が1ビットの場合の、FROM09に格納されているコンフィギ ュレーションデータ等のメモリマップのイメージ図である。

【図4】本実施形態の処理手順を示すフローチャートである。

【図5】信号制御部14とFROM09とを接続するアドレス線が2ビットの場合の 、概略のFPGA装置のブロック図である。

【図6】アドレス線が2ビットの場合の、FROM09に格納されているコンフィギ ュレーションデータ等のメモリマップのイメージ図である。

【発明を実施するための形態】

【0021】

本発明の実施形態について、図面を参照して詳細に説明する。

(実施形態)

【0022】

図1に示すように、本実施形態のFPGAを搭載する装置(以下、FPGA装置)は、FPGA01、電源監視部08、FROM09、クロック源10及びコンフィギュレーション制御部11(例えば、コンフィギュレーション制御回路)から構成されている。

FPGA(Field Programmable Gate Array)01は、コンフィギュレーション機能部02とプログラマブル回路03とから構成されている。

【0023】

コンフィギュレーション機能部02は、FPGA01に予め具備されている機能部であり、プログラマブル回路03、FROM09及び信号制御部14と接続されている。

【0024】

プログラマブル回路03は、インターフェースI/O04を備えるユーザ回路05と、エンベディトプロセッサ06と、から構成されている。ユーザ回路05とエンベディトプロセッサ06は内部バス07で接続されている。

【0025】

ユーザ回路05は、ユーザが作成したコンフィギュレーションデータに基づき任意の機能を設定できる回路である。ユーザ回路05は、コンフィギュレーション機能部02がPROG信号S2を受信したのをトリガとして、インターフェースI/O04を介してFROM09の指定された領域に格納されているコンフィギュレーションデータを読み出してコンフィギュレーションを実施する。

【0026】

エンベデットプロセッサ06は、FPGA01のプログラマブル回路03にCPUコアと周辺回路を組み込むことにより実現するプロセッサである。エンベデットプロセッサ06は、FPGA01のコンフィギュレーション完了後に、ユーザ回路05のインターフェースI/O04を介してFROM09の指定されている領域に格納されているエンベデットプロセッサ・プログラム(IPLやOSを含む)を読み出して動作する。

なお、本実施形態においては、プログラマブル回路03は、エンベデットプロセッサ06を実装する構成としたが、ユーザ回路05のみを備える構成でもよい。

【0027】

FPGA01は、コンフィギュレーションデータを書き換えることにより、ハード機能を変更することが可能な集積回路である。FPGA01は、揮発性であるため、起動の度にユーザ回路05をコンフィギュレーションする必要がある。複数のコンフィギュレーションモードが用意されているが、本実施形態のようにFPGA01にCPUコアを組み込み(エンベデットプロセッサ06)、装置の制御をFPGA01のみが担う場合は、FPGA01がコンフィギュレーションデータの読み出し先として指定するFROM09の領域(一般には、FROM09の先頭アドレス)に格納されているコンフィギュレーションデータを、FPGA01が直接読み出してコンフィギュレーションを実施するモードが使用される。

【0028】

電源監視部08は、装置の電源ON、OFF、又は、リセットの制御を行う。また、信号制御部14と接続され、FPGA01や周辺デバイスの所定のシーケンスに従って起動タイミングを計り(一般には、入力電源電圧が安定後に)、信号制御部14に対して、起動信号S1を出力する。

【0029】

FROM09は、不揮発メモリである。本実施形態では、FROM09は、同じ内容のコンフィギュレーションデータと同じ内容のエンベデットプロセッサ・プログラムが一組ずつ格納される複数の領域を有している。また、FROM09は、信号制御部14とアドレス線で接続され、FPGA01がコンフィギュレーションに失敗した際に、信号制御部14が面選択信号S7(以下、SEL信号S7)の設定値(FROM09の指定領域の最上位ビットの論理)を順次切り替えることで、FPGA01がコンフィギュレーションデータの読み出し先として指定するFROM09の領域が切り替えられる。電源ON又はリセット時におけるSEL信号S7の初期設定値は、本実施形態では、”0”とし、コンフィギュレーション及びエンベデットプロセッサの起動が失敗する度に、+1加算される。

【0030】

コンフィギュレーション制御部11は、タイマ12と、カウンタ13を備える信号制御部14と、から構成されている。

【0031】

タイマ12は、クロック源10に同期して動作するカウンタで、FPGA01のコンフィギュレーションの完了とエンベデットプロセッサ06の正常起動を監視するためのものである。タイマ12の設定値は、FPGA01のコンフィギュレーションとエンベデットプロセッサ06の起動に要する時間よりも長くそれぞれ設定する。

【0032】

カウンタ13は、信号制御部14が電源ON又はリセット後のコンフィギュレーションの回数を管理するためのカウンタである。電源ON又はリセット時における、初期設定値を”1”とし、FPGA01のコンフィギュレーション又はエンベデットプロセッサ06の起動が失敗する度に、+1加算される。つまり、カウンタ値がk−1の時にコンフィギュレーション又はエンベデットプロセッサ06の起動に失敗した際は、信号制御部14により、SEL信号S7の設定値はk−1からkに切り替えられることになる。

【0033】

信号制御部14は、FPGA01、電源監視部08、FROM09及びタイマ12と接続され、PROG信号S2、スタート信号S3、SEL信号S7等を制御する。また、信号制御部14は、コンフィギュレーションの完了とエンベデットプロセッサ06の正常起動を判定する。また、信号制御部14は、コンフィギュレーション又はエンベデットプロセッサ06の起動に失敗した際に、FPGA01がコンフィギュレーションデータの読み出し先として指定するFROM09の領域を切り替える。

【0034】

次に、図2、3を参照して、FROM09について詳細に説明する。

上述のように、FROM09には、同一のコンフィギュレーションデータとエンベデットプロセッサ・プログラムとの組がn組記憶されている。図2,3は、n=2,即ち、2組のコンフィギュレーションデータとエンベデットプロセッサ・プログラムとがFROM09に記憶されている場合の例である。

【0035】

図3は、この場合の、FROM09に格納されているコンフィギュレーションデータ及びエンベデットプロセッサ・プログラムのメモリマップのイメージである。ただし、FROM09の容量を128Kバイトとしている。

【0036】

図2に示すように、FROM09の最上位ビット(ビット17)は信号制御部14に、下位ビット(ビット16〜0)はFPGA01に接続されている。この場合、FPGA01が使用するデータの格納領域は、0x0_0000〜0x0_FFFFと0x1_0000〜0x1_FFFFとなる。そして、SEL信号S7の設定値が”0”の場合は、FPGA01はFROM09の最上位ビットが”0”の領域(0x0_0000〜0x0_FFFF)のデータを使用し、信号制御部14がSEL信号S7の設定値を”1”に切り替えた場合は、FPGA01はFROM09の最上位ビットが”1”の領域(0x1_0000〜0x1_FFFF)のデータを使用する。

【0037】

コンフィギュレーションデータは、この2つの領域の各先頭部分(アドレス0x0_0000〜0x0_AFFFと0x1_0000〜0x1_AFFF)に格納される。

【0038】

このように、信号制御部14とFROM09とを接続するアドレス線で制御できるデータのビット数がmビットの場合は、FROM09に格納できるコンフィギュレーションデータは最大で2m個となる。必ずしも、FROM09に、最大個数のコンフィギュレーションデータ等を格納する必要はなく、例えば、最大個数が8個(m=3)の場合に、コンフィギュレーションデータを5個だけ格納するようにしても構わない。

【0039】

次に、図1を参照して、電源ON又はリセットされた後の流れに沿って各信号について説明する。

【0040】

起動信号S1は、電源ON又はリセットされた後に、電源監視部08から信号制御部14に対して出力される信号である。

【0041】

PROG信号S2は、FPGA01がコンフィギュレーションをスタートするトリガとなる信号で、信号制御部14が、起動信号S1の受信をトリガとして、コンフィギュレーション機能部02に対して出力する。コンフィギュレーション機能部02のPROG信号S2の受信をトリガとして、FPGA01は内部メモリ(不図示)を初期化し、コンフィギュレーションをスタートする。また、PROG信号S2は、コンフィギュレーション又はエンベデットプロセッサ06の起動が失敗した際にも、コンフィギュレーションの回数kが所定回数n(FROM09に格納されているコンフィギュレーションデータの個数)未満の場合は、FPGA01にリコンフィギュレーションするためのトリガを与えるため、信号制御部14からコンフィギュレーション機能部02に対して出力される。

【0042】

スタート信号S3は、起動信号S1の受信をトリガとして、信号制御部14が、タイマ12をスタートさせるために、タイマ12に対して出力する信号である。また、信号制御部14は、FPGA01のコンフィギュレーションが完了した際にも、エンベデットプロセッサ06の起動を監視するために、タイマ12に対して、スタート信号S3を出力する。

【0043】

INIT信号S4aは、FPGA01の内部メモリ(不図示)の初期化が完了した際に、コンフィギュレーション機能部02から信号制御部14に対して出力される信号である。

【0044】

INIT信号S4bは、FPGA01のコンフィギュレーションが失敗した際に、CRCエラーを通知するため、コンフィギュレーション機能部02から信号制御部14に対して出力される信号である。なお、FPGAの中には、CRCエラーを別信号で通知するものも存在するが、その場合は、該別信号をINIT信号S4bの代わりに用いる。

【0045】

満了信号S5は、タイマ12の設定時間が満了した際に、タイマ12から信号制御部14に対して、出力される信号である。

【0046】

DONE信号S6は、FPGA01のコンフィギュレーションが完了した際に、コンフィギュレーション機能部02から信号制御部14に対して出力される信号である。信号制御部14は、タイマ12から満了信号S5を受信した時点で、INIT信号S4aと、DONE信号S6を受信していれば、FPGA01のコンフィギュレーションは完了したと判定し、それ以外は、コンフィギュレーションに失敗したと判定する。

【0047】

SEL信号S7は、FPGA01のコンフィギュレーション又はエンベデットプロセッサ06の起動に失敗した際に、コンフィギュレーションの回数kが所定回数n未満の場合に、信号制御部14がFROM09に対して出力する信号である。信号制御部14がSEL信号S7の設定値を切り替えることで、FPGA01がコンフィギュレーションデータの読み出し先として指定するFROM09の領域が切り替えられる。

【0048】

起動完了通知S8は、エンベデットプロセッサ06の正常起動を判定するための信号である。あらかじめFPGA01のユーザ回路05に機能として用意され、本実施形態では、初期設定は”0”とし、エンベデットプロセッサ06が正常起動した場合には、起動完了通知S6の設定を”1”にする。信号制御部14は、タイマ12から満了信号S5を受信した時点で、起動完了通知S8の設定が”1”であれば、エンベデットプロセッサ06が正常起動したと判定し、設定が”0”の場合は、起動に失敗したと判定する。

【0049】

異常通知S9は、コンフィギュレーション又はエンベデットプロセッサ06の起動に失敗した際に、コンフィギュレーションの回数kが所定回数nに達している場合に、信号制御部14が上位装置(不図示)に対して、FPGA01の異常を知らせるために出力する信号である。

【0050】

次に、図4を参照して、図1〜図3を参照して説明した本実施形態の処理手順について詳細に説明する。

この場合、FROM12に格納されているコンフィギュレーションデータの個数kは”2”となる。

【0051】

装置の電源をON又はリセットすると、カウンタ13のカウント値、SEL信号S7及び起動完了通知S8が初期化される(ステップS01)。電源監視部08は、所定のシーケンスに従って起動タイミングを計り、信号制御部14に起動信号S1を出力する(ステップS02)。そして、信号制御部14は、起動信号S1を受信すると、コンフィギュレーション機能部02に対して、PROG信号S2を出力すると共に、タイマ12をスタートさせる(ステップS03)。

【0052】

コンフィギュレーション機能部02がPROG信号S2を受信するのをトリガとして、FPGA01は、コンフィギュレーション機能部02内の内部メモリ(不図示)を初期化し、FROM09の指定領域(0x0_0000)に格納されているコンフィギュレーションデータを読み出して、この内部メモリに記憶し、記憶したコンフィグレーションデータに基づいて、コンフィギュレーションをスタートする(ステップS04)。

【0053】

タイマ12の設定時間が満了した時点で(ステップS05)、信号制御部14は、FPGA01のコンフィギュレーションが完了したか否かを判定する(ステップS06)。FPGA01のコンフィギュレーションが完了している場合には(ステップS08;YES)、エンベデットプロセッサ06は、FROM09の指定領域(0x0_1000)に格納されているエンベデットプロセッサ・プログラムを読み出して起動をスタートすると共に、信号制御部14は、タイマ12をスタートさせる(ステップS07)。

【0054】

タイマ12の設定時間が満了した時点で(ステップS08)、信号制御部14は、エンベデットプロセッサ06が正常起動したか否かを判定する(ステップS09)。起動完了通知S8の設定が”1”であれば(ステップS09;YES)、エンベデットプロセッサ06は正常起動となる。

【0055】

一方、タイマ12の設定時間が満了した時点で(ステップS05又はS08)、FPGA01のコンフィギュレーションが失敗した場合(ステップS06;NO)、又は、起動完了通知S8の設定が”1”でない場合には(ステップS09;NO)、信号制御部14は、カウンタ13により、コンフィギュレーションの回数が2回未満であるか否かを判定する(ステップS21)。

【0056】

コンフィギュレーションの回数はまだ1回目なので(ステップS21;YES)、信号制御部14は、カウンタ13のカウント数を+1加算し(ステップS22)、SEL信号S7の設定値を”1”に切り替え(ステップS23)、ステップS03に戻る。次に、信号制御部14は、コンフィギュレーション機能部02に対して、PROG信号S2を出力すると共に、タイマ12をスタートさせる(ステップS03)。

【0057】

コンフィギュレーション機能部02がPROG信号S2を受信するのをトリガとして、FPGA01は内部メモリ(不図示)を初期化して、FROM09の切り替え後の指定領域(0x1_0000)に格納されているコンフィギュレーションデータを読み出してコンフィギュレーションする(ステップS04)。

【0058】

そして、タイマ12の設定時間が満了した時点で(ステップS05)、信号制御部14は、FPGA01のコンフィギュレーションが完了したか否かを判定する(ステップS06)。FPGA01のコンフィギュレーションが完了している場合には(ステップS06;YES)、エンベデットプロセッサ06は、FROM09の切り替え後の指定領域(0x1_1000)に格納されているエンベデットプロセッサ・プログラムを読み出して起動をスタートすると共に、信号制御部14は、タイマ12をスタートさせる(ステップS07)。

【0059】

タイマ12の設定時間が満了した時点で(ステップS08)、信号制御部14は、エンベデットプロセッサ06が正常起動したか否かを判定する(ステップS09)。起動完了通知S8の設定が”1”であれば(ステップS09;YES)、エンベデットプロセッサ06は正常起動となる。

【0060】

一方、タイマ12の設定時間が満了した時点で(ステップS05又はS08)、FPGA01のコンフィギュレーションが失敗した場合(ステップS06;NO)、又は、起動完了通知S8の設定が”1”でない場合には(ステップS09;NO)、信号制御部14は、カウンタ13により、コンフィギュレーションの回数が2回未満であるか否かを判定する(ステップS21)。今回はコンフィギュレーションの回数が2回目なので(ステップS21;NO)、信号制御部14は、上位装置(不図示)に対して、異常通知S9を出力し(ステップS31)、処理を終了する。

【0061】

上記実施形態によれば、FROM09に同じ内容のコンフィギュレーションデータが複数個格納し、FPGA01は、コンフィギュレーションに失敗した場合、FROM09に格納されている別のコンフィギュレーションデータにより、リコンフィギュレーションする。こうすることで、FPGA01の信頼性を高めることができる。同様に、FROM09に同じ内容のエンベデットプロセッサ・プログラムを複数個さらに格納し、エンベデットプロセッサ06が起動に失敗した場合には、FROM09に格納されている別のエンベデットプロセッサ・プログラムにより、エンベデットプロセッサ06が再度起動する構成とした。こうすることで、エンベデットプロセッサ06を備えるFPGA01の信頼性を高めることができる。

【0062】

また、上記実施形態によれば、FPGA01のコンフィギュレーションが失敗した際に、FPGA01がコンフィギュレーションデータの読み出し先として指定するFROM09の指定領域を切り替え、FPGA01が切り替え後の指定領域に格納されている別のコンフィギュレーションデータを読み出せる構成とした。こうすることで、上記特許文献1乃至4にて提案されている方法が適用できない、FPGA01が読み出し先として指定するFROM09の領域に格納されているコンフィギュレーションデータを、FPGA01が直接読み出してコンフィギュレーションする必要がある装置に適用することができる。

【0063】

また、上記実施形態によれば、カウンタ13を設け、コンフィギュレーションの回数kが所定回数nに達した場合には(ステップS21;NO)、信号制御部14は、上位装置(不図示)に対して、異常通知S9を出力し処理を終了する構成とした。こうすることで、FROM09に格納されている全てのコンフィギュレーションデータが破壊されている場合に、FPGA01のリコンフィギュレーションがループすることを防止することができる。また、リコンフィギュレーションにより、FPGA01がコンフィギュレーションに成功した際にも、異常通知S9を出力するようにしてもよい。こうすることで、FROM09に格納されている全てのコンフィギュレーションデータが破壊される前に、破壊されたデータを修復する等の適切な対応を行うことができることから、さらに信頼性を高めることが可能となる。

【0064】

なお、上記実施形態の処理手順の説明では、図3を例にしたので、FROM09に格納されるコンフィギュレーションデータ等の個数は2個の構成とした。しかし、前述したように、信号制御部14とFROM09とを接続するアドレス線で制御できるデータのビット数を増やすことで、バックアップとしてFROM09に格納できるコンフィギュレーションデータの個数を増やすことが可能となる。こうすることで、さらに信頼性を高めることができる。例えば、図5のようにアドレス線を2ビットにした場合には、コンフィギュレーションデータ及びエンベデットプロセッサ・プログラムを4個ずつFROM09に格納できる(図6参照)。

【0065】

また、上記実施形態において、タイマ12の設定時間満了後に、コンフィギュレーションが成功したか否かを判定し、コンフィギュレーションが失敗した場合に、ステップS21に進む構成としたが、CRCエラーがINIT信号S4bにより信号制御部14に通知された時点で、ステップS21に進む構成としてもよい。こうすることで、より早い段階でリコンフィギュレーションを開始することが可能となる。

【0066】

上記実施形態において、タイマ12の設定値は、コンフィギュレーション制御部11の回路に対するハード設定等により、外部から変更できるようにしてもよい。こうすることで、ユーザが書き換えるデータに応じ、タイマ12の設定値を調整することが可能となる。

【0067】

FROM09は、不揮発性メモリであれば、他種のメモリでもよい。

【0068】

また、上記実施形態において、コンフィギュレーション制御部11にFROM09の破壊されたデータを自動で修復する機能を持たせてもよい。例えば、図6を参照して、4回目のコンフィギュレーションで、エンベデットプロセッサの起動まで成功した場合に、FROM09の0x0_0000、0x1_0000、0x2_0000にそれぞれ格納されているコンフィギュレーションデータを、エラーの無い0x3_0000に格納されているコンフィギュレーションデータで書き換える。同様に、FROM09の0x0_1000、0x1_1000、0x2_1000にそれぞれ格納されているエンベデットプロセッサ・プログラムを、エラーの無い0x3_1000に格納されているエンベデットプロセッサ・プログラムで書き換える。こうすることで、最上位ビットの数が同じ領域に格納されているコンフィギュレーションデータ及びエンベデットプロセッサ・プログラムが少なくとも1組正常であれば、自動的にエラーのある全てのコンフィギュレーションデータ及びエンベデットプロセッサ・プログラムを修復できる。この結果、FPGA01の信頼性をさらに高めることができる。なお、自動修復機能は、コンフィギュレーションデータにより実現させるようにしてもよい。

【0069】

上記自動修復機能を用いることで、コンフィギュレーションが失敗した際に、コンフィギュレーションの回数kが所定回数nに達している場合においても、エンベデットプロセッサ06の起動まで導ける可能性が生じる。例えば、図6を参照して、1回目と3回目と4回目はコンフィギュレーションに失敗し、2回目はコンフィギュレーションに成功したが、エンベデットプロセッサ06の起動に失敗した場合に、エラーのない0x1_0000に格納されているコンフィギュレーションデータで、0x0_0000、0x2_0000、0x3_0000に格納されているコンフィギュレーションデータを書き換える。そして、電源をリセットさせる。こうすることで、0x0_1000、0x2_1000、0x3_1000にそれぞれ格納されているエンベデットプロセッサ・プログラムのいずれかが正常であれば、エンベデットプロセッサ06の起動まで導くことが可能となる。

【0070】

また、本発明を用いることで、コンフィギュレーションデータ更新時における、FPGA01の信頼性を高めることが可能となる。例えば、コンフィギュレーションデータの更新を行う際に、コンフィギュレーションデータの更新データで、FROM09の初期指定領域(電源がON又はリセットされた後に、FPGA01が最初に読み出すコンフィギュレーションデータが格納されているFROM09の領域。例えば、図3では、0x0_0000領域。)に格納されているコンフィギュレーションデータを更新する。電源をON又はリセットすると、上記実施形態のフローに基づいて、FPGA01は最初に該更新データを読み出してコンフィギュレーションを行う。更新データに何らかの不具合があったために、更新データによるコンフィギュレーションに失敗した場合には、上記実施形態のフローに基づいて、更新前のコンフィギュレーションデータによりFPGA01はリコンフィギュレーションを行うことができる。一方、更新データによるコンフィギュレーションが成功した場合には、FROM09の他の領域に格納されている更新前のコンフィギュレーションデータを更新データに書き換える。

【0071】

こうすることで、更新データの不具合のために、FPGA01が更新データによるコンフィギュレーションに失敗したとしても、FROM09の別の領域に格納されている更新前のコンフィギュレーションデータにより、FPGA01はリコンフィギュレーションできる。この結果、専用端末(不図示)をFPGA01に接続する事無く更新作業を続ける事が可能となり、コンフィギュレーションデータの更新時における、作業効率とFPGA01の信頼性を一層向上させることができる。

【0072】

なお、上記実施形態及び図面の一部又は全部は、以下の付記のようにも記載されうるが、以下に限定されるわけではない。本発明の要旨を変更しない範囲で実施形態及び図面に変更を加えることができるのはもちろんである。

【0073】

(付記1)

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の領域を有する不揮発性メモリと、コンフィギュレーションデータの読み出し先として指定されている不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAとを備えるFPGA装置のコンフィギュレーション制御回路であって、

前記FPGAのコンフィギュレーションの開始からの経過時間を監視するタイマと、

前記タイマの設定時間が満了した際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAコンフィギュレーションが成功したか否かを判定する判定部と、

前記判定部により、コンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替える切替部と、

前記FPGAが前記切替部により切り替えられた前記不揮発性メモリの領域からコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える制御部と、

を具備することを特徴とするコンフィギュレーション制御回路。

【0074】

(付記2)

前記不揮発性メモリの複数の領域に、同一内容のエンベデットプロセッサ・プログラムがそれぞれさらに格納され、

前記FPGAは、FPGAのコンフィギュレーション完了後に前記不揮発性メモリの指定領域に格納されているエンベデットプロセッサ・プログラムを読み出して起動を開始するエンベデットプロセッサを備え、

前記タイマは、前記エンベデットプロセッサの起動開始からの経過時間をさらに監視し、前記タイマの設定時間が満了した際に、前記エンベデットプロセッサの起動完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記判定部は、前記エンベデットプロセッサの起動が成功したか否かをさらに判定し、前記エンベデットプロセッサの起動が失敗したと判定された際に、前記切替部は、前記不揮発性メモリの指定領域を切り替え、前記制御部は、前記FPGAが前記切替部により切り替えられた前記不揮発性メモリの指定領域から別のコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とする付記1に記載のコンフィギュレーション制御回路。

【0075】

(付記3)

前記制御部は、コンフィギュレーションに失敗したコンフィギュレーションデータを、コンフィギュレーションに成功した別のコンフィギュレーションデータに書き換えることにより、前記不揮発性メモリに格納されているデータを修復する、

ことを特徴とする付記1に記載のコンフィギュレーション制御回路。

【0076】

(付記4)

前記制御部は、エンベデットプロセッサの起動に失敗したエンベデットプロセッサ・プログラムを、起動に成功したエンベデットプロセッサ・プログラムに書き換えることにより、前記不揮発性メモリに格納されているデータを修復する、

ことを特徴とする付記2に記載のコンフィギュレーション制御回路。

【0077】

(付記5)

FPGAと、

付記1乃至4の何れか1項に記載のコンフィギュレーション制御回路と、を備えるFPGA装置。

【0078】

(付記6)

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の不揮発性メモリの領域のうち、コンフィギュレーションデータの読み出し先として指定されている不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAのコンフィギュレーション方法であって、

コンフィギュレーション開始からの経過時間を計測し、

前記経過時間が設定時間を超えた際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAのコンフィギュレーションが成功したか否かを判定し、

コンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替え、

指定を切り替えた後の不揮発性メモリの指定領域からコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とするコンフィギュレーション方法。

【0079】

(付記7)

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の領域を有する不揮発性メモリと、コンフィギュレーションデータの読み出し先として指定している前記不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAとを備えるFPGA装置のコンフィギュレーションデータ更新方法であって、

前記FPGA装置の電源がON又はリセットされた後最初の読み出し先として指定される前記不揮発性メモリの指定領域に格納されているコンフィギュレーションデータを更新データに書き換え、

前記FPGAのコンフィギュレーションを起動し、

前記FPGAのコンフィギュレーション開始からの経過時間を計測し、

前記経過時間が設定時間を超えた際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAのコンフィギュレーションが成功したか否かを判定し、

更新データによるコンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替え、

指定を切り替えた後の前記不揮発性メモリの指定領域から更新前のコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とするコンフィギュレーションデータ更新方法。

【0080】

(付記8)

前記更新データによるコンフィギュレーションが成功した際に、前記不揮発性メモリに格納されている更新前のコンフィギュレーションデータを更新データに書き換える、

ことを特徴とする付記7に記載のコンフィギュレーションデータ更新方法。

【符号の説明】

【0081】

01 FPGA

02 コンフィギュレーション機能部

03 プログラマブル回路

04 インターフェース

05 ユーザ回路

06 エンベデットプロセッサ

07 内部バス

08 電源監視部

09 FROM

10 クロック源

11 コンフィギュレーション制御部

12 タイマ

13 カウンタ

14 信号制御部

S1 起動信号

S2 PROG信号

S3 スタート信号

S4a 初期化完了信号(INIT信号)

S4b CRCエラー信号(INIT信号)

S5 満了信号

S6 DONE信号

S7 SEL信号

S8 起動完了通知

S9 異常通知

【特許請求の範囲】

【請求項1】

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の領域を有する不揮発性メモリと、コンフィギュレーションデータの読み出し先として指定されている不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAとを備えるFPGA装置のコンフィギュレーション制御回路であって、

前記FPGAのコンフィギュレーションの開始からの経過時間を監視するタイマと、

前記タイマの設定時間が満了した際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAコンフィギュレーションが成功したか否かを判定する判定部と、

前記判定部により、コンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替える切替部と、

前記FPGAが前記切替部により切り替えられた前記不揮発性メモリの領域からコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える制御部と、

を具備することを特徴とするコンフィギュレーション制御回路。

【請求項2】

前記不揮発性メモリの複数の領域に、同一内容のエンベデットプロセッサ・プログラムがそれぞれさらに格納され、

前記FPGAは、FPGAのコンフィギュレーション完了後に前記不揮発性メモリの指定領域に格納されているエンベデットプロセッサ・プログラムを読み出して起動を開始するエンベデットプロセッサを備え、

前記タイマは、前記エンベデットプロセッサの起動開始からの経過時間をさらに監視し、前記タイマの設定時間が満了した際に、前記エンベデットプロセッサの起動完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記判定部は、前記エンベデットプロセッサの起動が成功したか否かをさらに判定し、前記エンベデットプロセッサの起動が失敗したと判定された際に、前記切替部は、前記不揮発性メモリの指定領域を切り替え、前記制御部は、前記FPGAが前記切替部により切り替えられた前記不揮発性メモリの指定領域から別のコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とする請求項1に記載のコンフィギュレーション制御回路。

【請求項3】

前記制御部は、コンフィギュレーションに失敗したコンフィギュレーションデータを、コンフィギュレーションに成功した別のコンフィギュレーションデータに書き換えることにより、前記不揮発性メモリに格納されているデータを修復する、

ことを特徴とする請求項1に記載のコンフィギュレーション制御回路。

【請求項4】

前記制御部は、エンベデットプロセッサの起動に失敗したエンベデットプロセッサ・プログラムを、エンベデットプロセッサの起動に成功したエンベデットプロセッサ・プログラムに書き換えることにより、前記不揮発性メモリに格納されているデータを修復する、

ことを特徴とする請求項2に記載のコンフィギュレーション制御回路。

【請求項5】

FPGAと、

請求項1乃至4の何れか1項に記載のコンフィギュレーション制御回路と、を備えるFPGA装置。

【請求項6】

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の不揮発性メモリの領域のうち、コンフィギュレーションデータの読み出し先として指定されている不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAのコンフィギュレーション方法であって、

コンフィギュレーション開始からの経過時間を計測し、

前記経過時間が設定時間を超えた際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAのコンフィギュレーションが成功したか否かを判定し、

コンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替え、

指定を切り替えた後の不揮発性メモリの指定領域からコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とするコンフィギュレーション方法。

【請求項7】

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の領域を有する不揮発性メモリと、コンフィギュレーションデータの読み出し先として指定している前記不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAとを備えるFPGA装置のコンフィギュレーションデータ更新方法であって、

前記FPGA装置の電源がON又はリセットされた後最初の読み出し先として指定される前記不揮発性メモリの指定領域に格納されているコンフィギュレーションデータを更新データに書き換え、

前記FPGAのコンフィギュレーションを起動し、

前記FPGAのコンフィギュレーション開始からの経過時間を計測し、

前記経過時間が設定時間を超えた際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAのコンフィギュレーションが成功したか否かを判定し、

更新データによるコンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替え、

指定を切り替えた後の前記不揮発性メモリの指定領域から更新前のコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とするコンフィギュレーションデータ更新方法。

【請求項8】

前記更新データによるコンフィギュレーションが成功した際に、前記不揮発性メモリに格納されている更新前のコンフィギュレーションデータを更新データに書き換える、

ことを特徴とする請求項7に記載のコンフィギュレーションデータ更新方法。

【請求項1】

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の領域を有する不揮発性メモリと、コンフィギュレーションデータの読み出し先として指定されている不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAとを備えるFPGA装置のコンフィギュレーション制御回路であって、

前記FPGAのコンフィギュレーションの開始からの経過時間を監視するタイマと、

前記タイマの設定時間が満了した際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAコンフィギュレーションが成功したか否かを判定する判定部と、

前記判定部により、コンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替える切替部と、

前記FPGAが前記切替部により切り替えられた前記不揮発性メモリの領域からコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える制御部と、

を具備することを特徴とするコンフィギュレーション制御回路。

【請求項2】

前記不揮発性メモリの複数の領域に、同一内容のエンベデットプロセッサ・プログラムがそれぞれさらに格納され、

前記FPGAは、FPGAのコンフィギュレーション完了後に前記不揮発性メモリの指定領域に格納されているエンベデットプロセッサ・プログラムを読み出して起動を開始するエンベデットプロセッサを備え、

前記タイマは、前記エンベデットプロセッサの起動開始からの経過時間をさらに監視し、前記タイマの設定時間が満了した際に、前記エンベデットプロセッサの起動完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記判定部は、前記エンベデットプロセッサの起動が成功したか否かをさらに判定し、前記エンベデットプロセッサの起動が失敗したと判定された際に、前記切替部は、前記不揮発性メモリの指定領域を切り替え、前記制御部は、前記FPGAが前記切替部により切り替えられた前記不揮発性メモリの指定領域から別のコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とする請求項1に記載のコンフィギュレーション制御回路。

【請求項3】

前記制御部は、コンフィギュレーションに失敗したコンフィギュレーションデータを、コンフィギュレーションに成功した別のコンフィギュレーションデータに書き換えることにより、前記不揮発性メモリに格納されているデータを修復する、

ことを特徴とする請求項1に記載のコンフィギュレーション制御回路。

【請求項4】

前記制御部は、エンベデットプロセッサの起動に失敗したエンベデットプロセッサ・プログラムを、エンベデットプロセッサの起動に成功したエンベデットプロセッサ・プログラムに書き換えることにより、前記不揮発性メモリに格納されているデータを修復する、

ことを特徴とする請求項2に記載のコンフィギュレーション制御回路。

【請求項5】

FPGAと、

請求項1乃至4の何れか1項に記載のコンフィギュレーション制御回路と、を備えるFPGA装置。

【請求項6】

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の不揮発性メモリの領域のうち、コンフィギュレーションデータの読み出し先として指定されている不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAのコンフィギュレーション方法であって、

コンフィギュレーション開始からの経過時間を計測し、

前記経過時間が設定時間を超えた際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAのコンフィギュレーションが成功したか否かを判定し、

コンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替え、

指定を切り替えた後の不揮発性メモリの指定領域からコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とするコンフィギュレーション方法。

【請求項7】

同一内容のコンフィギュレーションデータがそれぞれ格納されている複数の領域を有する不揮発性メモリと、コンフィギュレーションデータの読み出し先として指定している前記不揮発性メモリの指定領域から、コンフィギュレーションデータを読み出してコンフィギュレーションするFPGAとを備えるFPGA装置のコンフィギュレーションデータ更新方法であって、

前記FPGA装置の電源がON又はリセットされた後最初の読み出し先として指定される前記不揮発性メモリの指定領域に格納されているコンフィギュレーションデータを更新データに書き換え、

前記FPGAのコンフィギュレーションを起動し、

前記FPGAのコンフィギュレーション開始からの経過時間を計測し、

前記経過時間が設定時間を超えた際に、コンフィギュレーションの完了を示す信号を前記FPGAが出力しているか否かに基づいて、前記FPGAのコンフィギュレーションが成功したか否かを判定し、

更新データによるコンフィギュレーションが失敗したと判定された際に、前記不揮発性メモリの指定領域を他の領域に切り替え、

指定を切り替えた後の前記不揮発性メモリの指定領域から更新前のコンフィギュレーションデータを読み出してコンフィギュレーションするためのトリガを前記FPGAに与える、

ことを特徴とするコンフィギュレーションデータ更新方法。

【請求項8】

前記更新データによるコンフィギュレーションが成功した際に、前記不揮発性メモリに格納されている更新前のコンフィギュレーションデータを更新データに書き換える、

ことを特徴とする請求項7に記載のコンフィギュレーションデータ更新方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−74348(P2013−74348A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−210005(P2011−210005)

【出願日】平成23年9月26日(2011.9.26)

【出願人】(390010179)埼玉日本電気株式会社 (1,228)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月26日(2011.9.26)

【出願人】(390010179)埼玉日本電気株式会社 (1,228)

【Fターム(参考)】

[ Back to top ]