GaN層含有積層基板及びその製造方法並びにデバイス

【課題】大口径にすることも可能な単結晶を基板として使用する、GaN層を含む積層基板及びその製造方法並びに基板を用いたデバイスを提供する。

【解決手段】(111)シリコン基板3上に化学気相堆積法によりゲルマニウム層7をヘテロエピタキシャル成長させるゲルマニウム成長工程、得られたシリコン基板3上のゲルマニウム層7を700〜900℃の温度範囲内で熱処理を行う熱処理工程、及び、引き続いてゲルマニウム層7上にGaN層9をヘテロエピタキシャル成長させるGaN成長工程、を含むGaN層含有積層基板1の製造方法、及びこの製造方法により得られるGaN層含有積層基板1、並びに基板1を用いて製造されたデバイス。

【解決手段】(111)シリコン基板3上に化学気相堆積法によりゲルマニウム層7をヘテロエピタキシャル成長させるゲルマニウム成長工程、得られたシリコン基板3上のゲルマニウム層7を700〜900℃の温度範囲内で熱処理を行う熱処理工程、及び、引き続いてゲルマニウム層7上にGaN層9をヘテロエピタキシャル成長させるGaN成長工程、を含むGaN層含有積層基板1の製造方法、及びこの製造方法により得られるGaN層含有積層基板1、並びに基板1を用いて製造されたデバイス。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、GaN層を含む積層基板及びその製造方法並びに前記積層基板を用いたデバイスに関する。

【背景技術】

【0002】

近年、発光ダイオード(LED)用、ヘテロ接合バイポーラトランジスタ(HBT)用等のデバイス用途としてGaN結晶が注目されている。通常、GaNのバルク結晶は成長が極めて難しく、価格も極めて高く、また基板のサイズも2−3インチであり、低コスト化が難しいことも問題である。この問題を回避するために、LED用のGaNは単結晶SiCや単結晶サファイア上にヘテロエピタキシャル成長させたものを使用している。

しかしながら、単結晶SiCや単結晶サファイアもやはり高価であり、大口径基板が存在しないことから、普及の妨げとなっている。またこれらの材料は、GaNとの間に、大きな格子不整合が存在し、GaNを成長させる際には緩衝層を設ける必要性があることから生産性を大きく落とすことにもなっている。

【0003】

近年、これらの問題を回避するために、ゲルマニウムの(111)バルク結晶を用いることが提案されている(非特許文献1)。ゲルマニウム(111)とGaNは高い格子不整合(約20%)を有しているが、両者のメッシュ比が5:4となるため、実質的な格子不整合は0.4%程度になるというものである。すなわち、(111)ゲルマニウムの単位格子が5回、GaNの単位格子が4回繰り返されると、格子の位置が再び一致するということになる。しかしこの方法にも問題がある。ゲルマニウムは単結晶SiCなどと比較すると大口径の基板が得やすいと言えるが、ゲルマニウムは希少元素であるため、やはり価格は非常に高く、入手も難しい。

【0004】

【非特許文献1】"Germanium - a surprise base for high-quality nitrides" Compound Semiconductor, pp.14-16, April 2007

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明が解決しようとする課題は、大口径にすることも可能な単結晶を基板として使用する、GaN層を含む積層基板及びその製造方法並びに該積層基板を用いたデバイスを提供することである。

【課題を解決するための手段】

【0006】

上記の課題は、以下の手段(1)、(3)及び(4)により達成された。好ましい実施態様である(2)及び(5)と共に列挙する。

(1)(111)シリコン基板上に化学気相堆積法によりゲルマニウム層をヘテロエピタキシャル成長させるゲルマニウム成長工程、得られたシリコン基板上のゲルマニウム層を700〜900℃の温度範囲内で熱処理を行う熱処理工程、及び、引き続いてゲルマニウム層上にGaN層をヘテロエピタキシャル成長させるGaN成長工程、を含むことを特徴とする、GaN層含有積層基板の製造方法、

(2)ゲルマニウム成長工程の前に、シリコン基板上にSiGe層をヘテロエピタキシャル成長させる(1)に記載のGaN層含有積層基板の製造方法、

(3)少なくとも、単結晶シリコン基板と、該シリコン基板上にヘテロエピタキシャル成長させたゲルマニウム層と、該ゲルマニウム層上にヘテロエピタキシャル成長させたGaN層とを有し、ゲルマニウム層に貫通転位が存在せず、シリコン基板とゲルマニウム層の界面近傍にループ転位が局在することを特徴とするGaN層含有積層基板、

(4)(3)に記載のGaN層含有積層基板を用いて作製されたことを特徴とするデバイス、

(5)該デバイスが、LED素子又はHBT素子である(4)に記載のデバイス。

【発明の効果】

【0007】

本発明の製造方法によれば、(111)シリコンウェーハを基板とするために、低コストで8インチ以上の大口径基板のGaN層を含む積層基板を製造できた。また、ヘテロエピタキシャル成長させるゲルマニウム層に生じる貫通転位を熱処理工程により解消することができた。本発明のGaN層を含む積層基板は、発光ダイオード(LED)素子・ヘテロ接合バイポーラトランジスタ(HBT)素子等のデバイスの製造に使用することができた。

【発明を実施するための最良の形態】

【0008】

<GaN層含有積層基板及びその製造方法>

本発明のGaN層含有積層基板の製造方法は、(111)シリコン基板上に化学気相堆積法(CVD法)によりゲルマニウム層をヘテロエピタキシャル成長させるゲルマニウム成長工程、得られたシリコン基板上のゲルマニウム層を700〜900℃の範囲で熱処理を行う熱処理工程、及び、ゲルマニウム層上にGaNをヘテロエピタキシャル成長させるGaN成長工程、を含むことを特徴とする。

以下、上記の必須の3工程について、図面を参照しながら説明する。

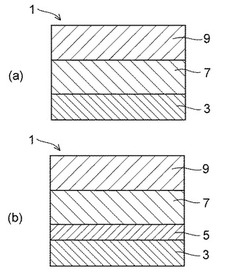

本発明のGaN層含有積層基板1は、図1(a)にその断面図を模式的に示すように、(111)シリコン基板3の上に、必須の層としてゲルマニウム層7及びGaN層9を有する。なお、図1(b)にその断面図を模式的に示すように、シリコン基板3及びゲルマニウム層7の間にSiGe層5を緩衝層として有していてもよい。

GaN層含有積層基板の製造方法は、上記のゲルマニウム成長工程、熱処理工程及びGaN成長工程の3工程を含み、好ましくはこの順に3工程を実施することが好ましい。3工程の途中に他の工程を含むことを排除するものではない。

図2は、上記の製造方法の一実施態様を示す工程図である。

【0009】

(ゲルマニウム成長工程)

本発明の製造方法では、基板としてシリコン基板を使用し、特に(111)シリコン基板を使用することが好ましく、単結晶(111)シリコンウエハを使用することがより好ましい。基板の直径は、8〜10インチの大口径まで選択が可能である。

シリコン(111)の格子定数は3.84Åであり、ゲルマニウム(111)の格子定数は4.00Åである。シリコンとゲルマニウムの格子不整合は4%になる。

【0010】

(111)シリコン基板上に、ゲルマニウムをヘテロエピタキシャル成長させるためには、化学気相堆積法(CVD)を使用する。

ゲルマニウムの成長条件は、L. Colace et al., Appl. Phys. Lett. 72(1998)3175に記載の条件に準拠することができる。使用ガスとしてGeH4を用い、超高真空下(2×10-8Pa以下)において600℃で成長を行うことにより、成長膜の厚さを約200nmとすることができる。ゲルマニウム層の厚さは50〜500nmとすることが好ましい。

【0011】

(熱処理工程)

上記のように、シリコンとゲルマニウムの格子不整合は4%になるために、ゲルマニウム層には、多数の貫通転位が発生する。しかしながら、追加の熱処理を加えることにより、転位をシリコン基板とゲルマニウム層の界面近傍に集めることが可能である。

このときの熱処理条件としては、N2雰囲気・常圧下で処理し、温度700〜900℃で0.5〜3時間、好ましくは約800℃で約1時間の温度と時間を採用し、通常の拡散炉を用いて行うことが可能である。

図3は、熱処理による変化を模式的に示す。図3(a)に示すように、ゲルマニウム層7にある貫通転位11は、上記の熱処理により図3(b)に示すように、シリコン基板3とゲルマニウム層7の界面近傍のループ転位13に変性する。さらに、GaN層9をヘテロエピタキシャル成長させる(後述)ことにより、図3(c)に示すように、ゲルマニウム層7の上にGaN層9を成長させることができる。

【0012】

(001)シリコン基板上のゲルマニウム膜については次の参考文献に報告がなされている。(M. Halbwax et al., "UHV-CVD growth and annealing of thin fully relaxed Ge films on (001)Si", Optical Materials, 27(2005), pp.822-825)

貫通転位がゲルマニウム(Ge)層の表面に現れていると、成長GaN膜にもこの欠陥は伝播することが考えられる。ヘテロエピタキシャル成長させたGe層を熱処理することにより、Ge層中の貫通転位を、シリコン基板とGe層界面近傍に局在するループ転位に変性させることができる。よって、この熱処理工程では、最終的に高品質のGaN膜が得られるだけでなく、シリコンはSiCやサファイアと異なり、導電性を有することからコンタクトがとりやすいという利点もある。

【0013】

(SiGe層の形成工程)

もちろん、シリコン基板とゲルマニウム層との間に、格子不整合を緩和するための緩衝層を形成することができる。緩衝層としては、SiGe層が好ましい。緩衝層は、化学気相堆積法(CVD)によるヘテロエピタキシャル成長により形成することができる。

【0014】

使用ガスとしてGeH4及びSiH4を用い、超高真空下(2×10-8Pa以下)において600℃で成長を行うことにより、SiGe膜を成長させることができる。SiGe層の厚さを約10〜100nmとすることが好ましい。

【0015】

(GaN層成長工程)

上記のゲルマニウム層の上に、GaN層をヘテロエピタキシャル成長させる。このGaN成長工程により、シリコン基板と同サイズのGaNへテロエピタキシャル膜を得ることができる。GaN層を成長させる方法としては分子線エピタキシー法(Molecular Beam Epitaxy:MBE法)と有機金属気相成長法(Metal Organic Chemical Vapor Deposition:MOCVD法)があるが、MBE法が好ましい。MBE法が800℃以下で成膜可能なのに対して、MOCVD法は一般に1,000〜1,100℃が必要なので、融点940℃のゲルマニウムには条件出しが難しいためである。

【0016】

(MBE法)

MBE法は、半導体の結晶成長に使用されている手法の一つである。真空蒸着法に分類され、原料供給機構から放出されたGaNがビーム状の分子線として被蒸着体に薄膜として成長する。

超高真空(10-8Pa程度)下で成長を行う。条件を選べば、面方位関係を保ったまま堆積させて、GaNをエピタキシャル成長させることができる。使用する装置は当業者に公知であり、例えば、権田俊一著、「分子線エピタキシー」(陪風館)を参照することができる。

【0017】

<GaN層含有積層基板>

本発明のGaN層含有積層基板は、少なくとも、単結晶シリコン基板と、該シリコン基板上にヘテロエピタキシャル成長させたゲルマニウム層と、該ゲルマニウム層上にヘテロエピタキシャル成長させたGaN層とを有し、ゲルマニウム層に貫通転位が存在せず、シリコン基板とゲルマニウム層の界面近傍にループ転位が局在することを特徴とする。

以下にGaN層含有積層基板について説明するが、上記のGaN層含有積層基板の製造方法の説明とほとんど重複するため、簡潔な説明に留める。

【0018】

(転位の観察)

ゲルマニウム層内の転位の観察は、透過型電子顕微鏡(TEM)を用いて行うことができる。

【0019】

<GaN層含有積層基板を用いるデバイスの製造>

本発明のGaN層含有積層基板は広くデバイスの製造に使用することができる。

このデバイスには、LED素子及び電子デバイスが含まれ、電子デバイスとしてはHBT素子が例示できる。

LED素子(発光素子)としては、青色発光素子を製造することができ、公知の方法で製造できる。

ホモエピタキシャル成長法により窒化ガリウム青色発光素子を製造する場合と比較して、本発明のGaN層含有積層基板を用いて作製されたデバイスは、安価である点で有利である。ホモエピタキシャル成長法で用いるバルクGaNは小径であり非常に高価であるが、本発明の方法では出発基板として大口径のシリコン基板を使用できるために、数桁違いの極めて低コストでGaNデバイスを製造することが可能となる。

【0020】

窒化ガリウム半導体を使用したHBT素子(ヘテロ接合バイポーラトランジスタ素子)は、公知の方法で製造できる。具体的な製造方法は多岐にわたり、当業者には適宜選択することができる。

【実施例】

【0021】

(実施例1)

(111)シリコン基板上に化学気相堆積法(CVD法)で(111)ゲルマニウムを直接シリコン上にエピタキシャル成長させ、800℃で熱処理を行った。続いて、MBE法でGaNを成長させ、約50nmのGaN膜を得た。このGaN膜をX線回折で分析したところ、380arcsec程度の鋭いピークが観察され、GaN単結晶が成長していることが確認できた。

【0022】

(実施例2)

(111)シリコン基板上に化学気相堆積法(CVD法)でSiH4ガスとGeH4ガスを用い、(111)SiGe層を30nm程度成長させ、続いて(111)ゲルマニウム層をエピタキシャル成長させ、800℃で熱処理を行った。続いて、MBE法でGaNを成長させ、約50nmのGaN膜を得た。このGaN膜をX線回折で分析したところ、実施例1同様に380arcsec程度の鋭いピークが観察され、GaN単結晶が成長していることが確認できた。

【図面の簡単な説明】

【0023】

【図1】本発明のGaN含有積層基板の一例を示す概略断面図である。

【図2】本発明のGaN含有積層基板の製造方法の一実施態様を示すフロー図である。

【図3】本発明の製造方法の熱処理工程における転位の変化を示す模式的断面図である。

【符号の説明】

【0024】

1 GaN層含有積層基板

3 (111)シリコン基板

5 SiGe層

7 ゲルマニウム層

9 GaN層

11 貫通転位

13 ループ転位

【技術分野】

【0001】

本発明は、GaN層を含む積層基板及びその製造方法並びに前記積層基板を用いたデバイスに関する。

【背景技術】

【0002】

近年、発光ダイオード(LED)用、ヘテロ接合バイポーラトランジスタ(HBT)用等のデバイス用途としてGaN結晶が注目されている。通常、GaNのバルク結晶は成長が極めて難しく、価格も極めて高く、また基板のサイズも2−3インチであり、低コスト化が難しいことも問題である。この問題を回避するために、LED用のGaNは単結晶SiCや単結晶サファイア上にヘテロエピタキシャル成長させたものを使用している。

しかしながら、単結晶SiCや単結晶サファイアもやはり高価であり、大口径基板が存在しないことから、普及の妨げとなっている。またこれらの材料は、GaNとの間に、大きな格子不整合が存在し、GaNを成長させる際には緩衝層を設ける必要性があることから生産性を大きく落とすことにもなっている。

【0003】

近年、これらの問題を回避するために、ゲルマニウムの(111)バルク結晶を用いることが提案されている(非特許文献1)。ゲルマニウム(111)とGaNは高い格子不整合(約20%)を有しているが、両者のメッシュ比が5:4となるため、実質的な格子不整合は0.4%程度になるというものである。すなわち、(111)ゲルマニウムの単位格子が5回、GaNの単位格子が4回繰り返されると、格子の位置が再び一致するということになる。しかしこの方法にも問題がある。ゲルマニウムは単結晶SiCなどと比較すると大口径の基板が得やすいと言えるが、ゲルマニウムは希少元素であるため、やはり価格は非常に高く、入手も難しい。

【0004】

【非特許文献1】"Germanium - a surprise base for high-quality nitrides" Compound Semiconductor, pp.14-16, April 2007

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明が解決しようとする課題は、大口径にすることも可能な単結晶を基板として使用する、GaN層を含む積層基板及びその製造方法並びに該積層基板を用いたデバイスを提供することである。

【課題を解決するための手段】

【0006】

上記の課題は、以下の手段(1)、(3)及び(4)により達成された。好ましい実施態様である(2)及び(5)と共に列挙する。

(1)(111)シリコン基板上に化学気相堆積法によりゲルマニウム層をヘテロエピタキシャル成長させるゲルマニウム成長工程、得られたシリコン基板上のゲルマニウム層を700〜900℃の温度範囲内で熱処理を行う熱処理工程、及び、引き続いてゲルマニウム層上にGaN層をヘテロエピタキシャル成長させるGaN成長工程、を含むことを特徴とする、GaN層含有積層基板の製造方法、

(2)ゲルマニウム成長工程の前に、シリコン基板上にSiGe層をヘテロエピタキシャル成長させる(1)に記載のGaN層含有積層基板の製造方法、

(3)少なくとも、単結晶シリコン基板と、該シリコン基板上にヘテロエピタキシャル成長させたゲルマニウム層と、該ゲルマニウム層上にヘテロエピタキシャル成長させたGaN層とを有し、ゲルマニウム層に貫通転位が存在せず、シリコン基板とゲルマニウム層の界面近傍にループ転位が局在することを特徴とするGaN層含有積層基板、

(4)(3)に記載のGaN層含有積層基板を用いて作製されたことを特徴とするデバイス、

(5)該デバイスが、LED素子又はHBT素子である(4)に記載のデバイス。

【発明の効果】

【0007】

本発明の製造方法によれば、(111)シリコンウェーハを基板とするために、低コストで8インチ以上の大口径基板のGaN層を含む積層基板を製造できた。また、ヘテロエピタキシャル成長させるゲルマニウム層に生じる貫通転位を熱処理工程により解消することができた。本発明のGaN層を含む積層基板は、発光ダイオード(LED)素子・ヘテロ接合バイポーラトランジスタ(HBT)素子等のデバイスの製造に使用することができた。

【発明を実施するための最良の形態】

【0008】

<GaN層含有積層基板及びその製造方法>

本発明のGaN層含有積層基板の製造方法は、(111)シリコン基板上に化学気相堆積法(CVD法)によりゲルマニウム層をヘテロエピタキシャル成長させるゲルマニウム成長工程、得られたシリコン基板上のゲルマニウム層を700〜900℃の範囲で熱処理を行う熱処理工程、及び、ゲルマニウム層上にGaNをヘテロエピタキシャル成長させるGaN成長工程、を含むことを特徴とする。

以下、上記の必須の3工程について、図面を参照しながら説明する。

本発明のGaN層含有積層基板1は、図1(a)にその断面図を模式的に示すように、(111)シリコン基板3の上に、必須の層としてゲルマニウム層7及びGaN層9を有する。なお、図1(b)にその断面図を模式的に示すように、シリコン基板3及びゲルマニウム層7の間にSiGe層5を緩衝層として有していてもよい。

GaN層含有積層基板の製造方法は、上記のゲルマニウム成長工程、熱処理工程及びGaN成長工程の3工程を含み、好ましくはこの順に3工程を実施することが好ましい。3工程の途中に他の工程を含むことを排除するものではない。

図2は、上記の製造方法の一実施態様を示す工程図である。

【0009】

(ゲルマニウム成長工程)

本発明の製造方法では、基板としてシリコン基板を使用し、特に(111)シリコン基板を使用することが好ましく、単結晶(111)シリコンウエハを使用することがより好ましい。基板の直径は、8〜10インチの大口径まで選択が可能である。

シリコン(111)の格子定数は3.84Åであり、ゲルマニウム(111)の格子定数は4.00Åである。シリコンとゲルマニウムの格子不整合は4%になる。

【0010】

(111)シリコン基板上に、ゲルマニウムをヘテロエピタキシャル成長させるためには、化学気相堆積法(CVD)を使用する。

ゲルマニウムの成長条件は、L. Colace et al., Appl. Phys. Lett. 72(1998)3175に記載の条件に準拠することができる。使用ガスとしてGeH4を用い、超高真空下(2×10-8Pa以下)において600℃で成長を行うことにより、成長膜の厚さを約200nmとすることができる。ゲルマニウム層の厚さは50〜500nmとすることが好ましい。

【0011】

(熱処理工程)

上記のように、シリコンとゲルマニウムの格子不整合は4%になるために、ゲルマニウム層には、多数の貫通転位が発生する。しかしながら、追加の熱処理を加えることにより、転位をシリコン基板とゲルマニウム層の界面近傍に集めることが可能である。

このときの熱処理条件としては、N2雰囲気・常圧下で処理し、温度700〜900℃で0.5〜3時間、好ましくは約800℃で約1時間の温度と時間を採用し、通常の拡散炉を用いて行うことが可能である。

図3は、熱処理による変化を模式的に示す。図3(a)に示すように、ゲルマニウム層7にある貫通転位11は、上記の熱処理により図3(b)に示すように、シリコン基板3とゲルマニウム層7の界面近傍のループ転位13に変性する。さらに、GaN層9をヘテロエピタキシャル成長させる(後述)ことにより、図3(c)に示すように、ゲルマニウム層7の上にGaN層9を成長させることができる。

【0012】

(001)シリコン基板上のゲルマニウム膜については次の参考文献に報告がなされている。(M. Halbwax et al., "UHV-CVD growth and annealing of thin fully relaxed Ge films on (001)Si", Optical Materials, 27(2005), pp.822-825)

貫通転位がゲルマニウム(Ge)層の表面に現れていると、成長GaN膜にもこの欠陥は伝播することが考えられる。ヘテロエピタキシャル成長させたGe層を熱処理することにより、Ge層中の貫通転位を、シリコン基板とGe層界面近傍に局在するループ転位に変性させることができる。よって、この熱処理工程では、最終的に高品質のGaN膜が得られるだけでなく、シリコンはSiCやサファイアと異なり、導電性を有することからコンタクトがとりやすいという利点もある。

【0013】

(SiGe層の形成工程)

もちろん、シリコン基板とゲルマニウム層との間に、格子不整合を緩和するための緩衝層を形成することができる。緩衝層としては、SiGe層が好ましい。緩衝層は、化学気相堆積法(CVD)によるヘテロエピタキシャル成長により形成することができる。

【0014】

使用ガスとしてGeH4及びSiH4を用い、超高真空下(2×10-8Pa以下)において600℃で成長を行うことにより、SiGe膜を成長させることができる。SiGe層の厚さを約10〜100nmとすることが好ましい。

【0015】

(GaN層成長工程)

上記のゲルマニウム層の上に、GaN層をヘテロエピタキシャル成長させる。このGaN成長工程により、シリコン基板と同サイズのGaNへテロエピタキシャル膜を得ることができる。GaN層を成長させる方法としては分子線エピタキシー法(Molecular Beam Epitaxy:MBE法)と有機金属気相成長法(Metal Organic Chemical Vapor Deposition:MOCVD法)があるが、MBE法が好ましい。MBE法が800℃以下で成膜可能なのに対して、MOCVD法は一般に1,000〜1,100℃が必要なので、融点940℃のゲルマニウムには条件出しが難しいためである。

【0016】

(MBE法)

MBE法は、半導体の結晶成長に使用されている手法の一つである。真空蒸着法に分類され、原料供給機構から放出されたGaNがビーム状の分子線として被蒸着体に薄膜として成長する。

超高真空(10-8Pa程度)下で成長を行う。条件を選べば、面方位関係を保ったまま堆積させて、GaNをエピタキシャル成長させることができる。使用する装置は当業者に公知であり、例えば、権田俊一著、「分子線エピタキシー」(陪風館)を参照することができる。

【0017】

<GaN層含有積層基板>

本発明のGaN層含有積層基板は、少なくとも、単結晶シリコン基板と、該シリコン基板上にヘテロエピタキシャル成長させたゲルマニウム層と、該ゲルマニウム層上にヘテロエピタキシャル成長させたGaN層とを有し、ゲルマニウム層に貫通転位が存在せず、シリコン基板とゲルマニウム層の界面近傍にループ転位が局在することを特徴とする。

以下にGaN層含有積層基板について説明するが、上記のGaN層含有積層基板の製造方法の説明とほとんど重複するため、簡潔な説明に留める。

【0018】

(転位の観察)

ゲルマニウム層内の転位の観察は、透過型電子顕微鏡(TEM)を用いて行うことができる。

【0019】

<GaN層含有積層基板を用いるデバイスの製造>

本発明のGaN層含有積層基板は広くデバイスの製造に使用することができる。

このデバイスには、LED素子及び電子デバイスが含まれ、電子デバイスとしてはHBT素子が例示できる。

LED素子(発光素子)としては、青色発光素子を製造することができ、公知の方法で製造できる。

ホモエピタキシャル成長法により窒化ガリウム青色発光素子を製造する場合と比較して、本発明のGaN層含有積層基板を用いて作製されたデバイスは、安価である点で有利である。ホモエピタキシャル成長法で用いるバルクGaNは小径であり非常に高価であるが、本発明の方法では出発基板として大口径のシリコン基板を使用できるために、数桁違いの極めて低コストでGaNデバイスを製造することが可能となる。

【0020】

窒化ガリウム半導体を使用したHBT素子(ヘテロ接合バイポーラトランジスタ素子)は、公知の方法で製造できる。具体的な製造方法は多岐にわたり、当業者には適宜選択することができる。

【実施例】

【0021】

(実施例1)

(111)シリコン基板上に化学気相堆積法(CVD法)で(111)ゲルマニウムを直接シリコン上にエピタキシャル成長させ、800℃で熱処理を行った。続いて、MBE法でGaNを成長させ、約50nmのGaN膜を得た。このGaN膜をX線回折で分析したところ、380arcsec程度の鋭いピークが観察され、GaN単結晶が成長していることが確認できた。

【0022】

(実施例2)

(111)シリコン基板上に化学気相堆積法(CVD法)でSiH4ガスとGeH4ガスを用い、(111)SiGe層を30nm程度成長させ、続いて(111)ゲルマニウム層をエピタキシャル成長させ、800℃で熱処理を行った。続いて、MBE法でGaNを成長させ、約50nmのGaN膜を得た。このGaN膜をX線回折で分析したところ、実施例1同様に380arcsec程度の鋭いピークが観察され、GaN単結晶が成長していることが確認できた。

【図面の簡単な説明】

【0023】

【図1】本発明のGaN含有積層基板の一例を示す概略断面図である。

【図2】本発明のGaN含有積層基板の製造方法の一実施態様を示すフロー図である。

【図3】本発明の製造方法の熱処理工程における転位の変化を示す模式的断面図である。

【符号の説明】

【0024】

1 GaN層含有積層基板

3 (111)シリコン基板

5 SiGe層

7 ゲルマニウム層

9 GaN層

11 貫通転位

13 ループ転位

【特許請求の範囲】

【請求項1】

(111)シリコン基板上に化学気相堆積法によりゲルマニウム層をヘテロエピタキシャル成長させるゲルマニウム成長工程、

得られたシリコン基板上のゲルマニウム層を700〜900℃の温度範囲内で熱処理を行う熱処理工程、及び、

引き続いてゲルマニウム層上にGaN層をヘテロエピタキシャル成長させるGaN成長工程、を含むことを特徴とする、

GaN層含有積層基板の製造方法。

【請求項2】

ゲルマニウム成長工程の前に、シリコン基板上にSiGe層をヘテロエピタキシャル成長させる請求項1に記載のGaN層含有積層基板の製造方法。

【請求項3】

少なくとも、単結晶シリコン基板と、該シリコン基板上にヘテロエピタキシャル成長させたゲルマニウム層と、該ゲルマニウム層上にヘテロエピタキシャル成長させたGaN層とを有し、

ゲルマニウム層に貫通転移が存在せず、

シリコン基板とゲルマニウム層の界面近傍にループ転移が局在することを特徴とする

GaN層含有積層基板。

【請求項4】

請求項3に記載のGaN層含有積層基板を用いて作製されたことを特徴とするデバイス。

【請求項5】

該デバイスがLED素子又はHBT素子である請求項4に記載のデバイス。

【請求項1】

(111)シリコン基板上に化学気相堆積法によりゲルマニウム層をヘテロエピタキシャル成長させるゲルマニウム成長工程、

得られたシリコン基板上のゲルマニウム層を700〜900℃の温度範囲内で熱処理を行う熱処理工程、及び、

引き続いてゲルマニウム層上にGaN層をヘテロエピタキシャル成長させるGaN成長工程、を含むことを特徴とする、

GaN層含有積層基板の製造方法。

【請求項2】

ゲルマニウム成長工程の前に、シリコン基板上にSiGe層をヘテロエピタキシャル成長させる請求項1に記載のGaN層含有積層基板の製造方法。

【請求項3】

少なくとも、単結晶シリコン基板と、該シリコン基板上にヘテロエピタキシャル成長させたゲルマニウム層と、該ゲルマニウム層上にヘテロエピタキシャル成長させたGaN層とを有し、

ゲルマニウム層に貫通転移が存在せず、

シリコン基板とゲルマニウム層の界面近傍にループ転移が局在することを特徴とする

GaN層含有積層基板。

【請求項4】

請求項3に記載のGaN層含有積層基板を用いて作製されたことを特徴とするデバイス。

【請求項5】

該デバイスがLED素子又はHBT素子である請求項4に記載のデバイス。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2009−143756(P2009−143756A)

【公開日】平成21年7月2日(2009.7.2)

【国際特許分類】

【出願番号】特願2007−321605(P2007−321605)

【出願日】平成19年12月13日(2007.12.13)

【出願人】(000002060)信越化学工業株式会社 (3,361)

【Fターム(参考)】

【公開日】平成21年7月2日(2009.7.2)

【国際特許分類】

【出願日】平成19年12月13日(2007.12.13)

【出願人】(000002060)信越化学工業株式会社 (3,361)

【Fターム(参考)】

[ Back to top ]