GaN系電界効果トランジスタの製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供する。

【解決手段】 GaN系電界効果トランジスタの製造方法は、基板101上にAlN層102、バッファ層103、チャネル層104、ドリフト層105および電子供給層106をエピタキシャル成長させる工程と、リセス部108を形成する工程と、アロイ工程におけるアニール時に電子供給層106を保護する保護膜113を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、オーミック接触を得るためのアニールを行なうアロイ工程と、保護膜113を除去し、ゲート絶縁膜を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、リセス部108のゲート絶縁膜上にゲート電極を形成する工程とを備える。

【解決手段】 GaN系電界効果トランジスタの製造方法は、基板101上にAlN層102、バッファ層103、チャネル層104、ドリフト層105および電子供給層106をエピタキシャル成長させる工程と、リセス部108を形成する工程と、アロイ工程におけるアニール時に電子供給層106を保護する保護膜113を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、オーミック接触を得るためのアニールを行なうアロイ工程と、保護膜113を除去し、ゲート絶縁膜を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、リセス部108のゲート絶縁膜上にゲート電極を形成する工程とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、パワーエレクトロニクス用デバイスや高周波増幅デバイスとして用いられる窒化物系化合物半導体からなるGaN系電界効果トランジスタの製造方法に関する。

【背景技術】

【0002】

III−V族窒化物系化合物半導体に代表されるワイドバンドギャップ半導体は、高い絶縁破壊耐圧、良好な電子輸送特性、良好な熱伝導度を持つので、高温、大パワー、あるいは高周波用半導体デバイスの材料として非常に魅力的である。また、たとえばAlGaN/GaNヘテロ構造を有する電界効果トランジスタ(FET)は、ピエゾ効果によって、界面に2次元電子ガスが発生している。この2次元電子ガスは、高い電子移動度とキャリア密度を有しているため、AlGaN/GaNヘテロ構造を用いたヘテロ接合FET(HFET)は、低いオン抵抗、および速いスイッチング速度を持ち、高温動作が可能である。これらの特徴は、パワースイッチング応用に非常に好適である。

【0003】

通常のAlGaN/GaN HFETは、ゲートにバイアスが印加されていないときに電流が流れ、ゲートに負電位を印加することによって電流が遮断されるノーマリオン型デバイスである。一方、パワースイッチング応用においては、デバイスが壊れたときの安全性確保のために、ゲートにバイアスが印加されていないときには電流が流れず、ゲートに正電位を印加することによって電流が流れるノーマリオフ型デバイスが好ましい。

【0004】

特許文献1には、AlGaN等からなる電子供給層をゲート部分においてエッチオフし、ドリフト層のエッチング表面上に絶縁層を形成してMOS構造とした電界効果トランジスタ(MOSFET)が開示されている。この構造では、ゲート・ドレイン間をAlGaN/GaNからなるヘテロ接合構造で形成しており、このヘテロ接合界面に形成される二次元電子ガスは電子移動度が高いため、高耐圧を維持するために必要なシートキャリア濃度においてもオン抵抗の増大を防ぐことができる。すなわち、高耐圧かつ低抵抗を実現するのに適した構造である。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】WO 03/071607号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、AlGaN/GaN 2次元電子ガス構造は、時間変化に伴って電流量が変化する「電流コラプス」と呼ばれる現象の影響を受け、ゲート・ドレイン間に高電圧をかけたあとのオン抵抗の増大、順方向通電時のオン抵抗の増大など、デバイス特性に悪影響がでる。

【0007】

電流コラプスの原因としては、HFETのAlGaN層と保護膜の間の界面準位や、HFETのチャネル層(ドリフト層)内の深いエネルギー準位が影響していると考えられている。製造工程上では、HFETのソース電極およびドレイン電極のオーミック接触用のアロイ工程の熱履歴によって生じるAlGaN層表面の損傷、AlGaN層と保護膜の反応生成物の発生が、界面準位を悪化させる原因のひとつである。

【0008】

本発明は、上記に鑑みてなされたものであって、低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記課題を解決するために、請求項1に記載の発明に係る電界効果トランジスタの製造方法は、基板上に、GaN系半導体からなるチャネル層をエピタキシャル成長させる工程と、前記チャネル層上に、前記チャネル層よりもバンドギャップエネルギーが大きいGaN系半導体からなる電子供給層をエピタキシャル成長させる工程と、電子供給層の一部をエッチング除去して前記チャネル層の表面を表出させることによって、前記表面を底面とするリセス部を形成する工程と、前記電子供給層上にソース電極およびドレイン電極を形成する工程と、前記リセス部の内表面上、前記電子供給層上、前記ソース電極および前記ドレイン電極上に第1の絶縁膜を形成する工程と、前記ソース電極および前記ドレイン電極にアニールを行なうアロイ工程と、前記アロイ工程後に、前記第1の絶縁膜を除去し、前記リセス部の内表面上、および前記電子供給層上に第2の絶縁膜を形成する工程と、前記リセス部における前記第2の絶縁膜上にゲート電極を形成する工程と、を備えることを特徴とする。

【0010】

本発明の製造方法によれば、ノーマリオフ型として動作するとともに、チャネル層の電子供給層との界面に発生した2次元電子ガスによって、低いオン抵抗と、高速のスイッチング動作とを実現する電界効果トランジスタを製造することができる。また、ソース電極およびドレイン電極の形成後で絶縁膜(第2の絶縁膜)の形成前に、絶縁膜とは別の保護膜(第1の絶縁膜)をつけた状態でオーミック接触用のアロイ工程を行うので、アロイ工程時、電子供給層の表面への損傷を低減することができる。また、保護膜を除去する際に電子供給層と保護膜の反応生成物も除去され、その後新たに絶縁膜を電子供給層上に形成するので、電子供給層と絶縁膜の界面準位を低減することができる。

【0011】

請求項2に記載の発明に係る電界効果トランジスタの製造方法は、前記チャネル層と前記電子供給層との間に、p型またはアンドープのGaN系半導体からなるドリフト層を形成する工程を有することを特徴とする。

【0012】

請求項3に記載の発明に係る電界効果トランジスタの製造方法は、前記電子供給層上に、n-GaNまたはi-GaNからなるキャップ層を形成する工程を含むことを特徴とする。

この構成によれば、電子供給層が表面に出ていないため、電子供給層と絶縁膜の間の界面準位を低減することが可能になり、電流コラプスを低減することができる。

【発明の効果】

【0013】

本発明によれば、電子供給層と絶縁膜の間の界面準位を低減することができるため、電流コラプスを低減したGaN系電界効果トランジスタを実現できるという効果を奏する。

【図面の簡単な説明】

【0014】

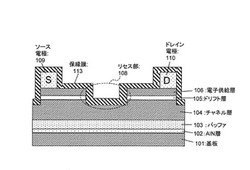

【図1】本発明の一実施形態に係る製造方法により製造されるMOSFETの模式的な断面図である。

【図2】図1に示すMOSFETを製造する一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する図である。

【図3】一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する図である。

【図4】一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する図である。

【図5】一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する図である。

【図6】一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する図である。

【図7】一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する図である。

【図8】一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する図である。

【発明を実施するための形態】

【0015】

以下に、図面を参照して本発明に係るGaN系電界効果トランジスタの製造方法の実施の形態を詳細に説明する。なお、この実施の形態によりこの発明が限定されるものではない。

【0016】

(一実施形態)

図1は、本発明の一実施形態に係る製造方法により製造されるGaN系電界効果トランジスタ(以下、「MOSFET」という。)の模式的な断面図である。このMOSFET100は、サファイア、SiC、Siなどからなる基板101上に、AlN層102と、GaN層とAlN層とを交互に積層して形成したバッファ層103と、p−GaNからなるチャネル層104が形成されている。さらに、チャネル層104上には、アンドープGaNからなるドリフト層105と、ドリフト層105よりもバンドギャップエネルギーが大きいAlGaNからなる電子供給層106が順次積層されている。

【0017】

また、ドリフト層105および電子供給層106の一部をチャネル層104に到る深さまで除去してリセス部108が形成されている。さらに、電子供給層106上には、リセス部108を挟んでソース電極109およびドレイン電極110が形成されている。ドリフト層105および電子供給層106の一部が除去されて表出したチャネル層104の表面を底面とするリセス部108の内表面上、および電子供給層106上にわたってSiO2からなるゲート絶縁膜(第2の絶縁膜)111が形成され、さらにゲート絶縁膜111上にはゲート電極112が形成されている。

なお、図面上ではリセス部108内におけるチャネル層104の表面はチャネル層104の上面近傍に位置しているが、その表面の深さについてはチャネル層104内で適宜設定することができる。

【0018】

このMOSFET100は、ノーマリオフ型として動作するとともに、ドリフト層105の電子供給層106との界面に発生した2次元電子ガスによって、低いオン抵抗と、高速のスイッチング動作とを実現できる。

【0019】

つぎに、このMOSFET100を製造する本発明の一実施形態に係るGaN系電界効果トランジスタの製造方法について説明する。図2〜図8は、図1に示すMOSFET100を製造する一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する説明図である。なお、以下では、有機金属気相成長(MOCVD)法を用いて各半導体層を形成した場合について説明するが、特に限定はされない。

【0020】

はじめに、図2に示すように、(111)面を主表面とするSiからなる基板101をMOCVD装置にセットし、濃度100%の水素ガスをキャリアガスとして用い、トリメチルガリウム(TMGa)とトリメチルアルミニウム(TMAl)とNH3とを導入し、成長温度1050℃で、基板101上に、AlN層102、バッファ層103、p−GaNからなるチャネル層104を順次エピタキシャル成長させる。なお、チャネル層104に対するp型のドーピング源としてビスシクロペンタジエニルマグネシウム(Cp2Mg)を用い、Mgの濃度が1×1017cm−3程度になるようにCp2Mgの流量を調整する。つぎに、TMGaとNH3とを導入し、成長温度1050℃で、チャネル層104上にアンドープGaNからなるドリフト層105をエピタキシャル成長させる。つぎに、TMAlとTMGaとNH3とを導入し、ドリフト層105上にAl組成が25%のAlGaNからなる電子供給層106をエピタキシャル成長させる。

【0021】

なお、上記において、バッファ層103は、厚さ200nm/20nmのGaN/AlN複合層を8層積層したものとする。また、AlN層102、チャネル層104、ドリフト層105、電子供給層106の厚さは、それぞれ100nm、500nm、100nm、20nmとする。

【0022】

つぎに、図3に示すように、プラズマ化学気相成長(PCVD)法を用いて、電子供給層106上に、アモルファスシリコン(a−Si)からなるマスク層120を厚さ500nmで形成し、フォトリソグラフィとCF4ガスを用いてパターニングを行い、素子分離部120aを形成する。さらに、マスク層120をマスクとして、エッチングガスであるCl2ガスを用いてチャネル層104、ドリフト層105および電子供給層106の一部をエッチング除去して素子分離部分130を形成する。

【0023】

つぎに、図4に示すように、マスク層120をフォトリソグラフィとCF4ガスを用いてパターニングを行い、開口部120bを形成する。さらに、マスク層120をマスクとして、エッチングガスであるCl2ガスを用いてチャネル層104、ドリフト層105および電子供給層106の一部をエッチング除去してチャネル層104の表面を底面とするリセス部108を形成する。

【0024】

なお、マスク層120は、表面からエッチングされるので、マスク層120の厚さは、チャネル層104が露出するまでドリフト層105および電子供給層106のエッチングを行なった場合に、開口部120b以外の位置の電子供給層106が露出してしまわないように、十分に厚くする。

【0025】

つぎに、図5に示すように、マスク層120を除去し、リフトオフ法を用いて電子供給層106上にソース電極109、ドレイン電極110を形成する。なお、ソース電極109、ドレイン電極110は、いずれも厚さ25nm/300nmのTi/Al構造とする。また、金属膜の成膜は、スパッタ法や真空蒸着法を用いて行うことができる。

【0026】

つぎに、図6に示すように、SiH4とN2Oを原料としたPCVD法を用いて、後述するアロイ工程におけるアニール時に電子供給層106を保護するSiO2からなる保護膜(第1の絶縁膜)113を、リセス部108の内表面上、電子供給層106上、ソース電極109、ドレイン電極110および素子分離部分130上に形成する。

つぎに、電子供給層106とソース電極109およびドレイン電極110との間でオーミック接触を得るためのアロイ工程として、600℃、10分のアニールを行なう

【0027】

つぎに、図7に示すように、バッファードフッ酸で保護膜113を除去した後、SiH4とN2Oを原料としたPCVD法を用いて、SiO2からなる厚さ60nmのゲート絶縁膜111を、リセス部108の内表面上、電子供給層106上、ソース電極109、ドレイン電極110および素子分離部分130上に成膜する。

【0028】

つぎに、図8に示すように、リフトオフ法を用いて、リセス部108のゲート絶縁膜111上にTi/Al構造のゲート電極112を形成し、図1に示すMOSFET100が完成する。ゲート電極112のドレイン側端部はゲート絶縁膜111を介してチャネル層104およびドリフト層105に重畳するように形成されており、重畳する部分の長さを適宜設定することによって、ゲート・ドレイン間の電界集中を緩和するフィールドプレート効果を持たせることができ、耐圧を向上することができる。

【0029】

以上説明した一実施形態に係るGaN系電界効果トランジスタの製造方法によれば、保護膜113をつけた状態でオーミック接触用のアロイ工程を行うので、アロイ時に電子供給層106の表面に損傷が入らず、保護膜113を除去する際にAlGaNからなる電子供給層106と保護膜113の反応生成物も除去される。その後新たにAlGaNからなる電子供給層106と保護膜113の間の界面準位の少ないゲート絶縁膜111を形成するので、電子供給層106とゲート絶縁膜111の界面準位を低減することができる。従って、電流コラプス現象の影響の小さいMOSFET100を実現することができる。

【0030】

上述した電流コラプスとしては、通電試験等によってトランジスタのオン抵抗を測定し(R1)、オフ状態にしたあとに再度オン抵抗を測定し(R2)、R1に対するR2の比を、当該トランジスタのコラプス量とした。

【0031】

なお、上述したMOSFET100の一例では、製造方法として図2〜8に示したプロセスを例にとって説明したが、製造方法としてはこれに限定されるものではなく、アニール時の保護膜を形成してからオーミック接触用のアロイ工程を行い、この保護膜を除去した後にゲート絶縁膜を形成するという工程を崩さなければよい。例えば、素子分離用のエッチングは、ゲート電極形成後に行ってもよいし、リセス部形成と同時に行ってもよい。

【0032】

また、上述したMOSFET100の製造方法の一例では、ゲート絶縁膜111として、PCVD法によって成膜したSiO2を例にとって説明したが、成膜方法としては、PCVD以外にもAPCVD法、ECRスパッタ法などの成膜方法を利用することができる。また、ゲート絶縁膜111の種類としても、SiO2以外にも、界面準位密度が低く絶縁破壊耐圧の高い絶縁膜、例えばAlN、Al2O3、Ga2O3、TaOx、またはSiONなどを用いることができる。

【0033】

また、MOSFET100の製造方法の一例では、絶縁膜113として、PCVD法によって成膜したSiNを例にとって説明したが、成膜方法としては、PCVD以外にもCat−CVD法、ECRスパッタ法などの成膜方法を利用することができる。

【0034】

また、上記一実施形態においては、ドリフト層105と電子供給層106の組み合わせとしてAlGaN/GaNを例にとって記載したが、これ以外にも、AlInGaN/GaN、GaN/InGaN、GaN/GaNAs、GaN/GaInNAsP、GaN/GaInNP、GaN/GaNP、AlGaNInNAsP/GaN、または、AlGaN/AlInGaNなどの材料系の組み合わせを適用することが可能である。また、2次元電子ガス層130の移動度を向上させるため、ドリフト層105と電子供給層106間に例えばAlNからなるスペーサ層を導入することもできる。

【0035】

また、上記一実施形態では、チャネル層104と電子供給層106との間に、p型またはアンドープのGaN系半導体からなるドリフト層105がそれぞれ形成されているが、本発明はこれに限定されない。つまり、上記各実施形態で説明したドリフト層が無く、p型GaN系半導体からなるチャネル層上に、電子供給層106が形成されている構成のMOSFETにも本発明は適用可能である。例えば、図1に示す第1実施形態に係るMOSFET100において、左右のドリフト層105が無く、p型GaN系半導体からなるチャネル層104上に、電子供給層106がそれぞれ形成されている構成のMOSFETにも本発明は適用可能である。つまり、このMOSFETでは、ドリフト層105がp型GaN系半導体からなる左右のチャネル層104となっている。

【0036】

このMOSFETでは、チャネル層104の表面には、2次元電子ガス層が形成され、チャネル層104のゲート電極112直下の領域には二次元電子ガス層が形成されていない(途切れている)。ゲート電極112に順方向に閾値以上の電圧を印加すると、ゲート電極112直下のチャネル層104に反転層が形成される。この反転層が、左右の2次元電子ガス層130と連結されてドレイン電流が流れるようになっている。このようにして、ノーマリオフ型の電界効果トランジスタの動作が得られる。

【0037】

また、上記一実施形態では、MOSFETの最上部はAlGaNからなる電子供給層であるが、本発明はこれに限定されない。電子供給層106上に、n-GaNまたはi-GaNからなるキャップ層を有するFETにも、本発明は適用可能である。この構成によれば、AlGaN層が表面に出ていないため、キャップ層と保護膜間の界面準位を低減することが可能になり、電流コラプス現象を低減することができる。

【0038】

以上説明したように、図1に示すMOSFET100は、耐圧が高く、オン抵抗が低く、電流コラプスによる特性変動の影響を受けにくいMOSFETとなる。

【符号の説明】

【0039】

100 MOSFET

101 基板

102 AlN層

103 バッファ層

104 チャネル層

105 ドリフト層

106 電子供給層

108 リセス部

109 ソース電極

110 ドレイン電極

111 ゲート絶縁膜(第2の絶縁膜)

112 ゲート電極

113 保護膜(第1の絶縁膜)

120 マスク層

120a 素子分離部

120b 開口部

130 素子分離部分

【技術分野】

【0001】

本発明は、パワーエレクトロニクス用デバイスや高周波増幅デバイスとして用いられる窒化物系化合物半導体からなるGaN系電界効果トランジスタの製造方法に関する。

【背景技術】

【0002】

III−V族窒化物系化合物半導体に代表されるワイドバンドギャップ半導体は、高い絶縁破壊耐圧、良好な電子輸送特性、良好な熱伝導度を持つので、高温、大パワー、あるいは高周波用半導体デバイスの材料として非常に魅力的である。また、たとえばAlGaN/GaNヘテロ構造を有する電界効果トランジスタ(FET)は、ピエゾ効果によって、界面に2次元電子ガスが発生している。この2次元電子ガスは、高い電子移動度とキャリア密度を有しているため、AlGaN/GaNヘテロ構造を用いたヘテロ接合FET(HFET)は、低いオン抵抗、および速いスイッチング速度を持ち、高温動作が可能である。これらの特徴は、パワースイッチング応用に非常に好適である。

【0003】

通常のAlGaN/GaN HFETは、ゲートにバイアスが印加されていないときに電流が流れ、ゲートに負電位を印加することによって電流が遮断されるノーマリオン型デバイスである。一方、パワースイッチング応用においては、デバイスが壊れたときの安全性確保のために、ゲートにバイアスが印加されていないときには電流が流れず、ゲートに正電位を印加することによって電流が流れるノーマリオフ型デバイスが好ましい。

【0004】

特許文献1には、AlGaN等からなる電子供給層をゲート部分においてエッチオフし、ドリフト層のエッチング表面上に絶縁層を形成してMOS構造とした電界効果トランジスタ(MOSFET)が開示されている。この構造では、ゲート・ドレイン間をAlGaN/GaNからなるヘテロ接合構造で形成しており、このヘテロ接合界面に形成される二次元電子ガスは電子移動度が高いため、高耐圧を維持するために必要なシートキャリア濃度においてもオン抵抗の増大を防ぐことができる。すなわち、高耐圧かつ低抵抗を実現するのに適した構造である。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】WO 03/071607号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、AlGaN/GaN 2次元電子ガス構造は、時間変化に伴って電流量が変化する「電流コラプス」と呼ばれる現象の影響を受け、ゲート・ドレイン間に高電圧をかけたあとのオン抵抗の増大、順方向通電時のオン抵抗の増大など、デバイス特性に悪影響がでる。

【0007】

電流コラプスの原因としては、HFETのAlGaN層と保護膜の間の界面準位や、HFETのチャネル層(ドリフト層)内の深いエネルギー準位が影響していると考えられている。製造工程上では、HFETのソース電極およびドレイン電極のオーミック接触用のアロイ工程の熱履歴によって生じるAlGaN層表面の損傷、AlGaN層と保護膜の反応生成物の発生が、界面準位を悪化させる原因のひとつである。

【0008】

本発明は、上記に鑑みてなされたものであって、低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記課題を解決するために、請求項1に記載の発明に係る電界効果トランジスタの製造方法は、基板上に、GaN系半導体からなるチャネル層をエピタキシャル成長させる工程と、前記チャネル層上に、前記チャネル層よりもバンドギャップエネルギーが大きいGaN系半導体からなる電子供給層をエピタキシャル成長させる工程と、電子供給層の一部をエッチング除去して前記チャネル層の表面を表出させることによって、前記表面を底面とするリセス部を形成する工程と、前記電子供給層上にソース電極およびドレイン電極を形成する工程と、前記リセス部の内表面上、前記電子供給層上、前記ソース電極および前記ドレイン電極上に第1の絶縁膜を形成する工程と、前記ソース電極および前記ドレイン電極にアニールを行なうアロイ工程と、前記アロイ工程後に、前記第1の絶縁膜を除去し、前記リセス部の内表面上、および前記電子供給層上に第2の絶縁膜を形成する工程と、前記リセス部における前記第2の絶縁膜上にゲート電極を形成する工程と、を備えることを特徴とする。

【0010】

本発明の製造方法によれば、ノーマリオフ型として動作するとともに、チャネル層の電子供給層との界面に発生した2次元電子ガスによって、低いオン抵抗と、高速のスイッチング動作とを実現する電界効果トランジスタを製造することができる。また、ソース電極およびドレイン電極の形成後で絶縁膜(第2の絶縁膜)の形成前に、絶縁膜とは別の保護膜(第1の絶縁膜)をつけた状態でオーミック接触用のアロイ工程を行うので、アロイ工程時、電子供給層の表面への損傷を低減することができる。また、保護膜を除去する際に電子供給層と保護膜の反応生成物も除去され、その後新たに絶縁膜を電子供給層上に形成するので、電子供給層と絶縁膜の界面準位を低減することができる。

【0011】

請求項2に記載の発明に係る電界効果トランジスタの製造方法は、前記チャネル層と前記電子供給層との間に、p型またはアンドープのGaN系半導体からなるドリフト層を形成する工程を有することを特徴とする。

【0012】

請求項3に記載の発明に係る電界効果トランジスタの製造方法は、前記電子供給層上に、n-GaNまたはi-GaNからなるキャップ層を形成する工程を含むことを特徴とする。

この構成によれば、電子供給層が表面に出ていないため、電子供給層と絶縁膜の間の界面準位を低減することが可能になり、電流コラプスを低減することができる。

【発明の効果】

【0013】

本発明によれば、電子供給層と絶縁膜の間の界面準位を低減することができるため、電流コラプスを低減したGaN系電界効果トランジスタを実現できるという効果を奏する。

【図面の簡単な説明】

【0014】

【図1】本発明の一実施形態に係る製造方法により製造されるMOSFETの模式的な断面図である。

【図2】図1に示すMOSFETを製造する一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する図である。

【図3】一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する図である。

【図4】一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する図である。

【図5】一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する図である。

【図6】一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する図である。

【図7】一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する図である。

【図8】一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する図である。

【発明を実施するための形態】

【0015】

以下に、図面を参照して本発明に係るGaN系電界効果トランジスタの製造方法の実施の形態を詳細に説明する。なお、この実施の形態によりこの発明が限定されるものではない。

【0016】

(一実施形態)

図1は、本発明の一実施形態に係る製造方法により製造されるGaN系電界効果トランジスタ(以下、「MOSFET」という。)の模式的な断面図である。このMOSFET100は、サファイア、SiC、Siなどからなる基板101上に、AlN層102と、GaN層とAlN層とを交互に積層して形成したバッファ層103と、p−GaNからなるチャネル層104が形成されている。さらに、チャネル層104上には、アンドープGaNからなるドリフト層105と、ドリフト層105よりもバンドギャップエネルギーが大きいAlGaNからなる電子供給層106が順次積層されている。

【0017】

また、ドリフト層105および電子供給層106の一部をチャネル層104に到る深さまで除去してリセス部108が形成されている。さらに、電子供給層106上には、リセス部108を挟んでソース電極109およびドレイン電極110が形成されている。ドリフト層105および電子供給層106の一部が除去されて表出したチャネル層104の表面を底面とするリセス部108の内表面上、および電子供給層106上にわたってSiO2からなるゲート絶縁膜(第2の絶縁膜)111が形成され、さらにゲート絶縁膜111上にはゲート電極112が形成されている。

なお、図面上ではリセス部108内におけるチャネル層104の表面はチャネル層104の上面近傍に位置しているが、その表面の深さについてはチャネル層104内で適宜設定することができる。

【0018】

このMOSFET100は、ノーマリオフ型として動作するとともに、ドリフト層105の電子供給層106との界面に発生した2次元電子ガスによって、低いオン抵抗と、高速のスイッチング動作とを実現できる。

【0019】

つぎに、このMOSFET100を製造する本発明の一実施形態に係るGaN系電界効果トランジスタの製造方法について説明する。図2〜図8は、図1に示すMOSFET100を製造する一実施形態に係るGaN系電界効果トランジスタの製造方法を説明する説明図である。なお、以下では、有機金属気相成長(MOCVD)法を用いて各半導体層を形成した場合について説明するが、特に限定はされない。

【0020】

はじめに、図2に示すように、(111)面を主表面とするSiからなる基板101をMOCVD装置にセットし、濃度100%の水素ガスをキャリアガスとして用い、トリメチルガリウム(TMGa)とトリメチルアルミニウム(TMAl)とNH3とを導入し、成長温度1050℃で、基板101上に、AlN層102、バッファ層103、p−GaNからなるチャネル層104を順次エピタキシャル成長させる。なお、チャネル層104に対するp型のドーピング源としてビスシクロペンタジエニルマグネシウム(Cp2Mg)を用い、Mgの濃度が1×1017cm−3程度になるようにCp2Mgの流量を調整する。つぎに、TMGaとNH3とを導入し、成長温度1050℃で、チャネル層104上にアンドープGaNからなるドリフト層105をエピタキシャル成長させる。つぎに、TMAlとTMGaとNH3とを導入し、ドリフト層105上にAl組成が25%のAlGaNからなる電子供給層106をエピタキシャル成長させる。

【0021】

なお、上記において、バッファ層103は、厚さ200nm/20nmのGaN/AlN複合層を8層積層したものとする。また、AlN層102、チャネル層104、ドリフト層105、電子供給層106の厚さは、それぞれ100nm、500nm、100nm、20nmとする。

【0022】

つぎに、図3に示すように、プラズマ化学気相成長(PCVD)法を用いて、電子供給層106上に、アモルファスシリコン(a−Si)からなるマスク層120を厚さ500nmで形成し、フォトリソグラフィとCF4ガスを用いてパターニングを行い、素子分離部120aを形成する。さらに、マスク層120をマスクとして、エッチングガスであるCl2ガスを用いてチャネル層104、ドリフト層105および電子供給層106の一部をエッチング除去して素子分離部分130を形成する。

【0023】

つぎに、図4に示すように、マスク層120をフォトリソグラフィとCF4ガスを用いてパターニングを行い、開口部120bを形成する。さらに、マスク層120をマスクとして、エッチングガスであるCl2ガスを用いてチャネル層104、ドリフト層105および電子供給層106の一部をエッチング除去してチャネル層104の表面を底面とするリセス部108を形成する。

【0024】

なお、マスク層120は、表面からエッチングされるので、マスク層120の厚さは、チャネル層104が露出するまでドリフト層105および電子供給層106のエッチングを行なった場合に、開口部120b以外の位置の電子供給層106が露出してしまわないように、十分に厚くする。

【0025】

つぎに、図5に示すように、マスク層120を除去し、リフトオフ法を用いて電子供給層106上にソース電極109、ドレイン電極110を形成する。なお、ソース電極109、ドレイン電極110は、いずれも厚さ25nm/300nmのTi/Al構造とする。また、金属膜の成膜は、スパッタ法や真空蒸着法を用いて行うことができる。

【0026】

つぎに、図6に示すように、SiH4とN2Oを原料としたPCVD法を用いて、後述するアロイ工程におけるアニール時に電子供給層106を保護するSiO2からなる保護膜(第1の絶縁膜)113を、リセス部108の内表面上、電子供給層106上、ソース電極109、ドレイン電極110および素子分離部分130上に形成する。

つぎに、電子供給層106とソース電極109およびドレイン電極110との間でオーミック接触を得るためのアロイ工程として、600℃、10分のアニールを行なう

【0027】

つぎに、図7に示すように、バッファードフッ酸で保護膜113を除去した後、SiH4とN2Oを原料としたPCVD法を用いて、SiO2からなる厚さ60nmのゲート絶縁膜111を、リセス部108の内表面上、電子供給層106上、ソース電極109、ドレイン電極110および素子分離部分130上に成膜する。

【0028】

つぎに、図8に示すように、リフトオフ法を用いて、リセス部108のゲート絶縁膜111上にTi/Al構造のゲート電極112を形成し、図1に示すMOSFET100が完成する。ゲート電極112のドレイン側端部はゲート絶縁膜111を介してチャネル層104およびドリフト層105に重畳するように形成されており、重畳する部分の長さを適宜設定することによって、ゲート・ドレイン間の電界集中を緩和するフィールドプレート効果を持たせることができ、耐圧を向上することができる。

【0029】

以上説明した一実施形態に係るGaN系電界効果トランジスタの製造方法によれば、保護膜113をつけた状態でオーミック接触用のアロイ工程を行うので、アロイ時に電子供給層106の表面に損傷が入らず、保護膜113を除去する際にAlGaNからなる電子供給層106と保護膜113の反応生成物も除去される。その後新たにAlGaNからなる電子供給層106と保護膜113の間の界面準位の少ないゲート絶縁膜111を形成するので、電子供給層106とゲート絶縁膜111の界面準位を低減することができる。従って、電流コラプス現象の影響の小さいMOSFET100を実現することができる。

【0030】

上述した電流コラプスとしては、通電試験等によってトランジスタのオン抵抗を測定し(R1)、オフ状態にしたあとに再度オン抵抗を測定し(R2)、R1に対するR2の比を、当該トランジスタのコラプス量とした。

【0031】

なお、上述したMOSFET100の一例では、製造方法として図2〜8に示したプロセスを例にとって説明したが、製造方法としてはこれに限定されるものではなく、アニール時の保護膜を形成してからオーミック接触用のアロイ工程を行い、この保護膜を除去した後にゲート絶縁膜を形成するという工程を崩さなければよい。例えば、素子分離用のエッチングは、ゲート電極形成後に行ってもよいし、リセス部形成と同時に行ってもよい。

【0032】

また、上述したMOSFET100の製造方法の一例では、ゲート絶縁膜111として、PCVD法によって成膜したSiO2を例にとって説明したが、成膜方法としては、PCVD以外にもAPCVD法、ECRスパッタ法などの成膜方法を利用することができる。また、ゲート絶縁膜111の種類としても、SiO2以外にも、界面準位密度が低く絶縁破壊耐圧の高い絶縁膜、例えばAlN、Al2O3、Ga2O3、TaOx、またはSiONなどを用いることができる。

【0033】

また、MOSFET100の製造方法の一例では、絶縁膜113として、PCVD法によって成膜したSiNを例にとって説明したが、成膜方法としては、PCVD以外にもCat−CVD法、ECRスパッタ法などの成膜方法を利用することができる。

【0034】

また、上記一実施形態においては、ドリフト層105と電子供給層106の組み合わせとしてAlGaN/GaNを例にとって記載したが、これ以外にも、AlInGaN/GaN、GaN/InGaN、GaN/GaNAs、GaN/GaInNAsP、GaN/GaInNP、GaN/GaNP、AlGaNInNAsP/GaN、または、AlGaN/AlInGaNなどの材料系の組み合わせを適用することが可能である。また、2次元電子ガス層130の移動度を向上させるため、ドリフト層105と電子供給層106間に例えばAlNからなるスペーサ層を導入することもできる。

【0035】

また、上記一実施形態では、チャネル層104と電子供給層106との間に、p型またはアンドープのGaN系半導体からなるドリフト層105がそれぞれ形成されているが、本発明はこれに限定されない。つまり、上記各実施形態で説明したドリフト層が無く、p型GaN系半導体からなるチャネル層上に、電子供給層106が形成されている構成のMOSFETにも本発明は適用可能である。例えば、図1に示す第1実施形態に係るMOSFET100において、左右のドリフト層105が無く、p型GaN系半導体からなるチャネル層104上に、電子供給層106がそれぞれ形成されている構成のMOSFETにも本発明は適用可能である。つまり、このMOSFETでは、ドリフト層105がp型GaN系半導体からなる左右のチャネル層104となっている。

【0036】

このMOSFETでは、チャネル層104の表面には、2次元電子ガス層が形成され、チャネル層104のゲート電極112直下の領域には二次元電子ガス層が形成されていない(途切れている)。ゲート電極112に順方向に閾値以上の電圧を印加すると、ゲート電極112直下のチャネル層104に反転層が形成される。この反転層が、左右の2次元電子ガス層130と連結されてドレイン電流が流れるようになっている。このようにして、ノーマリオフ型の電界効果トランジスタの動作が得られる。

【0037】

また、上記一実施形態では、MOSFETの最上部はAlGaNからなる電子供給層であるが、本発明はこれに限定されない。電子供給層106上に、n-GaNまたはi-GaNからなるキャップ層を有するFETにも、本発明は適用可能である。この構成によれば、AlGaN層が表面に出ていないため、キャップ層と保護膜間の界面準位を低減することが可能になり、電流コラプス現象を低減することができる。

【0038】

以上説明したように、図1に示すMOSFET100は、耐圧が高く、オン抵抗が低く、電流コラプスによる特性変動の影響を受けにくいMOSFETとなる。

【符号の説明】

【0039】

100 MOSFET

101 基板

102 AlN層

103 バッファ層

104 チャネル層

105 ドリフト層

106 電子供給層

108 リセス部

109 ソース電極

110 ドレイン電極

111 ゲート絶縁膜(第2の絶縁膜)

112 ゲート電極

113 保護膜(第1の絶縁膜)

120 マスク層

120a 素子分離部

120b 開口部

130 素子分離部分

【特許請求の範囲】

【請求項1】

基板上に、GaN系半導体からなるチャネル層をエピタキシャル成長させる工程と、

前記チャネル層上に、前記チャネル層よりもバンドギャップエネルギーが大きいGaN系半導体からなる電子供給層をエピタキシャル成長させる工程と、

電子供給層の一部をエッチング除去して前記チャネル層の表面を表出させることによって、前記表面を底面とするリセス部を形成する工程と、

前記電子供給層上にソース電極およびドレイン電極を形成する工程と、

前記リセス部の内表面上、前記電子供給層上、前記ソース電極および前記ドレイン電極上に第1の絶縁膜を形成する工程と、

前記ソース電極および前記ドレイン電極にアニールを行なうアロイ工程と、

前記アロイ工程後に、前記第1の絶縁膜を除去し、前記リセス部の内表面上、前記電子供給層上、前記ソース電極および前記ドレイン電極上に第2の絶縁膜を形成する工程と、

前記リセス部における前記第2の絶縁膜上にゲート電極を形成する工程と、を備えることを特徴とするGaN系電界効果トランジスタの製造方法。

【請求項2】

前記チャネル層と前記電子供給層との間に、p型またはアンドープのGaN系半導体からなるドリフト層を形成する工程を有することを特徴とする請求項1に記載のGaN系電界効果トランジスタの製造方法。

【請求項3】

前記電子供給層上に、n-GaNまたはi-GaNからなるキャップ層を形成する工程を有することを特徴とする請求項1または2に記載のGaN系電界効果トランジスタの製造方法。

【請求項1】

基板上に、GaN系半導体からなるチャネル層をエピタキシャル成長させる工程と、

前記チャネル層上に、前記チャネル層よりもバンドギャップエネルギーが大きいGaN系半導体からなる電子供給層をエピタキシャル成長させる工程と、

電子供給層の一部をエッチング除去して前記チャネル層の表面を表出させることによって、前記表面を底面とするリセス部を形成する工程と、

前記電子供給層上にソース電極およびドレイン電極を形成する工程と、

前記リセス部の内表面上、前記電子供給層上、前記ソース電極および前記ドレイン電極上に第1の絶縁膜を形成する工程と、

前記ソース電極および前記ドレイン電極にアニールを行なうアロイ工程と、

前記アロイ工程後に、前記第1の絶縁膜を除去し、前記リセス部の内表面上、前記電子供給層上、前記ソース電極および前記ドレイン電極上に第2の絶縁膜を形成する工程と、

前記リセス部における前記第2の絶縁膜上にゲート電極を形成する工程と、を備えることを特徴とするGaN系電界効果トランジスタの製造方法。

【請求項2】

前記チャネル層と前記電子供給層との間に、p型またはアンドープのGaN系半導体からなるドリフト層を形成する工程を有することを特徴とする請求項1に記載のGaN系電界効果トランジスタの製造方法。

【請求項3】

前記電子供給層上に、n-GaNまたはi-GaNからなるキャップ層を形成する工程を有することを特徴とする請求項1または2に記載のGaN系電界効果トランジスタの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2010−192633(P2010−192633A)

【公開日】平成22年9月2日(2010.9.2)

【国際特許分類】

【出願番号】特願2009−34725(P2009−34725)

【出願日】平成21年2月18日(2009.2.18)

【出願人】(000005290)古河電気工業株式会社 (4,457)

【Fターム(参考)】

【公開日】平成22年9月2日(2010.9.2)

【国際特許分類】

【出願日】平成21年2月18日(2009.2.18)

【出願人】(000005290)古河電気工業株式会社 (4,457)

【Fターム(参考)】

[ Back to top ]