GaN系MOS型電界効果トランジスタ

【課題】ノーマリオフ動作を可能にし、かつしきい値電圧を自由に制御出来るGaN系MOSFETを提供する。

【解決手段】p−GaNからなる電子走行層13とゲート電極18との間にゲート絶縁膜15が形成されたGaN系MOSFET10である。ゲート電極18は、AlGaInP混晶からなる。ゲート電極18は、p型AlGaInP混晶からなる第1のゲート層19と、この上に形成されたp型GaAsからなる第2のゲート層20と、この上に形成された金属層(AuGe/Au電極)21とを有する。AlGaInP混晶の混晶比を変化させることにより、しきい値電圧を制御することが出来る。

【解決手段】p−GaNからなる電子走行層13とゲート電極18との間にゲート絶縁膜15が形成されたGaN系MOSFET10である。ゲート電極18は、AlGaInP混晶からなる。ゲート電極18は、p型AlGaInP混晶からなる第1のゲート層19と、この上に形成されたp型GaAsからなる第2のゲート層20と、この上に形成された金属層(AuGe/Au電極)21とを有する。AlGaInP混晶の混晶比を変化させることにより、しきい値電圧を制御することが出来る。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、GaN系化合物半導体からなるチャネル層とゲート電極との間にゲート絶縁膜が形成されたGaN系MOS型電界効果トランジスタ(MOSFET)に関する。

【背景技術】

【0002】

III−V族窒化物系化合物半導体に代表されるワイドバンドギャップ半導体は、高い絶縁破壊耐圧、良好な電子輸送特性、良好な熱伝導度を持つので、高温環境用、大パワー用、あるいは高周波用の半導体デバイスの材料として非常に好適である。

例えば、GaN系化合物半導体材料は、GaAs系の材料に比べてそのバンドギャップエネルギーが大きく、耐熱度が高いため、GaN系化合物半導体を用いた素子は、高温環境下での動作が可能である。更に、GaN系化合物半導体を用いた素子は、絶縁破壊耐圧が高く、オン抵抗が低いため、低消費電力・省エネルギーの動作が可能となる。そのため、これらの材料、とくにGaN/AlGaN系化合物半導体を用いた電界効果トランジスタ(Field Effect Transistor:FET)やパワースイッチング用ダイオードの開発が進められている。

【0003】

このようなGaN系化合物半導体を用いた素子としては、故障時のフェイルセーフのためにノーマリオフ動作が求められている。GaN系化合物半導体を用いたノーマリオフ型の電子デバイスとして、MOS電界効果トランジスタ(GaN系MOSFET)が検討されている。 従来、GaN系MOSFETにおいては、ゲート電極としてポリシリコン(poly−Si)が使用される。これは、SiのMOSFETにおいて、ゲート電極として広くポリシリコンが使用されているためである。

しかし、p-GaNからなるチャネル層を有するGaN系MOSFETにおいては、p-GaNの仕事関数が6〜7eV程度あると考えられており、ポリシリコンの仕事関数の5eVより大きく、ゲート電圧が0Vの段階で、反転状態である。そのため、GaN系MOSFETでは、ノーマリオフ化が困難となっている。

【0004】

GaN系化合物半導体(p-GaN)からなるチャネル層とゲート電極との間にゲート絶縁膜が形成されたGaN系MOSFETにおいて、しきい値電圧を制御するパラメータとして下記の3つが挙げられる。

(1)ゲート絶縁膜の厚さ

(2)p-GaNからなるチャネル層のアクセプタ濃度

(3)ゲート電極の仕事関数

しかし、パラメータ(1)や(2)は、オン特性とトレードオフ関係になっており、これらのパラメータ(1)や(2)をしきい値制御のために変更するのは得策ではない。すなわち、しきい値を上げるために、ゲート絶縁膜を厚くしたり、チャネル層のアクセプタ濃度を高くしたりすると、オン特性が劣化してしまう。一方、パラメータ(3)は他の特性を変えずにしきい値を変更出来る利点がある。

【0005】

例えば特許文献1に開示された絶縁ゲート電界効果トランジスタ(MISHFET)では、ゲート電極としてSiCを用いている。このMISHFETでは、AlGaNバリア層の上にSiNxゲート絶縁膜、p型多結晶SiC層、オーミック電極であるPt/Auゲート電極が順次形成されている。p型多結晶SiC層は仕事関数が相対的に大きいので、ゼロバイアス状態でもMISHFETのチャネルが空乏化されて、ノーマリオフ動作が生じる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−147951号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

仕事関数は一般に物質固有の値であり、その値を自由に制御出来るわけではない。そのため、上記従来技術では、AlGaNバリア層の上に形成されたp型多結晶SiC層の仕事関数が一意に決まるため、しきい値を正に出来ても、その値を自由に制御出来なかった。

そこで、本発明は、このような従来の問題点に着目して為されたもので、その目的は、ノーマリオフ動作を可能にし、かつしきい値電圧を自由に制御出来るGaN系MOS型電界効果トランジスタを提供することにある。

【課題を解決するための手段】

【0008】

理想的なGaN系MOSFETを作製する場合、チャネル部分の物質とゲート電極の物質の仕事関数が同じで有ることが望ましい。しかし、GaNにおいてはp型ドーパントの活性化率が悪いことや、成長温度が高いことから、ゲート絶縁膜であるSiO2上にゲート電極としてp−GaNを成長させるのが困難であった。そのため、チャネル層と同程度の仕事関数を持つ他の物質を使用することとなる。本発明者らは鋭意研究の結果、そのような物質として多結晶のAlGaInPが有効であることを見出した。p型AlGaInP混晶は仕事関数が5.5〜7eVであり、p−GaNと同程度の仕事関数を持つ。例えば、p−AlPの仕事関数は7eV程度である。AlGaInPにおいてAl、Ga、Inの混晶比を変化させることにより、フラットバンド電圧を変えることが出来るので、しきい値をオン特性等の他の特性を変化させること無く制御することが出来る。本発明はこのような知見に基づきなされたものである。

【0009】

上記課題を解決するために、請求項1に記載の発明に係るGaN系MOS型電界効果トランジスタは、GaN系化合物半導体からなるチャネル層とゲート電極との間にゲート絶縁膜が形成されたGaN系MOS型電界効果トランジスタにおいて、前記ゲート電極は、AlGaInPからなることを特徴とする。

【0010】

請求項2に記載の発明に係るGaN系MOS型電界効果トランジスタは、前記AlGaInPは、仕事関数が6eV以上であることを特徴とする。

【0011】

請求項3に記載の発明に係るGaN系MOS型電界効果トランジスタは、前記AlGaInPは多結晶であることを特徴とする。

【0012】

請求項4に記載の発明に係るGaN系MOS型電界効果トランジスタは、前記AlGaInPはp型であることを特徴とする。

【0013】

請求項5に記載の発明に係るGaN系MOS型電界効果トランジスタは、前記チャネル層は、電子走行層と、前記電子走行層上に形成され、前記電子走行層よりも大きいバンドギャップエネルギーを持つGaN系化合物半導体からなる電子供給層とを有し、前記電子供給層のゲートに相当する部分に前記電子走行層に達する深さで形成されたリセス部と、該リセス部に前記ゲート絶縁膜を介して形成された前記ゲート電極と、前記ゲート電極を挟んで前記電子供給層上に形成されたソース電極とドレイン電極とを備えていることを特徴とする。

【0014】

請求項6に記載の発明に係るGaN系MOS型電界効果トランジスタは、前記ゲート電極は、前記ゲート絶縁膜上に形成された仕事関数が5.5〜7eVである第一のゲート層と、前記第一のゲート層よりも仕事関数の小さい第二のゲート層とを備えることを特徴とする。

【発明の効果】

【0015】

請求項1に記載の発明によれば、ゲート電極として、チャネル層の仕事関数と同等或いはそれ以上の仕事関数を有するAlGaInPを用いているので、ノーマリオフ動作が可能になる。また、AlGaInPの混晶比を変化させることにより、フラットバンド電圧を変えることが出来るので、しきい値電圧を、オン特性等の他の特性を変化させること無く制御することが出来る。

【図面の簡単な説明】

【0016】

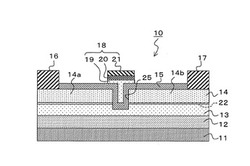

【図1】本発明の第1の実施形態に係るGaN系MOSFETの概略構成を示す断面図である。

【図2】(a)〜(d)は第1の実施形態に係るGaN系MOSFETの作製方法を説明する図である。

【図3】(a)〜(e)は第1の実施形態に係るGaN系MOSFETの作製方法を説明する図である。

【図4】本発明の第2の実施形態に係るGaN系MOSFETの概略構成を示す断面図である。

【発明を実施するための形態】

【0017】

以下に、本発明に係るGaN系MOSFETの実施の形態を図面に基づいて説明する。

図1は、本発明の一実施形態に係るGaN系MOSFET10の概略構成を示している。

GaN系MOSFET10は、GaN系化合物半導体からなるチャネル層とゲート電極との間にゲート絶縁膜が形成されたGaN系MOS型電界効果トランジスタ(GaN系MOSFET)の一例として、AlGaN/GaNからなるヘテロ接合構造を有するヘテロ接合電界効果トランジスタ(HFET: Hetero-junction Field Effect Transistor)に、MOS(Metal Oxide Semiconductor)構造を採用したGaN系MOSFETである。

【0018】

GaN系MOSFET10は、図1に示すように、シリコン(111)基板11上に、AlNとGaNの積層構造からなるバッファ層12と、チャネル層としてのp−GaNからなる電子走行層13と、電子走行層13上に形成され、電子走行層13よりも大きいバンドギャップエネルギーを持つアンドープAlGaNからなる電子供給層14とが順次積層されている。

なお、GaN系MOSFET10は、基板11とバッファ層12との間に、AlN層が形成された構造であってもよい。また、バッファ層12は、不純物として炭素(C)がドーピングされた高抵抗なAlN、GaNの積層構造であることが好ましい。

【0019】

このGaN系MOSFET10においては、電子供給層14の一部(ゲート電極形成領域)が電子走行層13に到る深さまで除去され、リセス部25が形成されている。

電子供給層14上には、リセス部25を挟んでソース電極16およびドレイン電極17が形成されている。電子供給層14上とリセス部25の内表面上とには、SiO2からなるゲート絶縁膜15が形成されている。さらに、ゲート絶縁膜15の、リセス部25を覆う部分の表面上には、ゲート電極18が形成されている。

【0020】

このGaN系MOSFET10では、電子供給層14は、ゲート電極18直下の電子走行層13、ゲート絶縁膜15およびゲート電極18で構成されるMOS構造のゲート部を挟んで互いに離隔された左右の電子供給層14a、14bを有する。なお、GaN系MOSFET10は、電子走行層13と左右の電子供給層14a、14bとの間に、電子走行層13より不純物濃度の低いp型またはアンドープのGaN系化合物半導体からなる中間層が形成された構成であってもよい。

【0021】

このようなAlGaN/GaNヘテロ接合構造を有するGaN系MOSFET10では、電子走行層13と左右の電子供給層14a、14bの界面、つまり、左右のAlGaN/GaNヘテロ接合界面にピエゾ効果によって、電子走行層13側に2次元電子ガス層22がそれぞれ発生している。2次元電子ガス層22がキャリアとなって電子走行層13は低抵抗、高移動度となるため、GaN系MOSFET10のオン抵抗を小さくし、スイッチング速度を向上させることができる。

【0022】

更に、このGaN系MOSFET10では、ノーマリオフ動作を可能にし、かつしきい値電圧を自由に制御出来るようにするために、ゲート電極18は、仕事関数が電子走行層13の仕事関数と同等或いはそれ以上であるAlGaInPを用いて形成されている。

【0023】

つまり、ゲート電極18として、電子走行層13を構成するp-GaNの仕事関数と同等或いはそれ以上の仕事関数(5.5〜7eV)を有し、かつ自由に仕事関数を制御出来る物質としてAlGaInPを用いる。AlGaInPは多結晶体であるのが好ましい。 また、AlGaInPはp型であるのが好ましい。

【0024】

図1に示すゲート電極18は、ゲート絶縁膜15上のゲート電極形成領域に形成されたAlGaInPからなるゲート部半導体層と、該ゲート部半導体層上に形成された金属層とを備えている。ゲート部半導体層は、ゲート絶縁膜15上に形成されたp型AlGaInP混晶からなる第1のゲート層19と、第1のゲート層19上に形成されたp型GaAsからなる第2のゲート層20との積層構造になっている。また、第2のゲート層20上に、AuGe/Auからなる金属層(AuGe/Au電極)21が形成されている。

【0025】

ゲート電極をAlGaInPで構成することにより、GaN系MOSFET10は、ノーマリオフ動作が可能となる。また、AlGaInPの混晶比を変化させることにより、フラットバンド電圧を変えることが出来るので、しきい値電圧を、オン特性等の他の特性を変化させること無く制御することが出来る。

【0026】

ここで、AlGaInPの混晶比とは、Al、Ga、およびInの組成を、その合計が1となるように構成した比であり、Al、Gaの組成比をそれぞれx、yとした場合、AlxGayIn1−x−yP(0≦x≦1、0≦y≦1、0≦x+y≦1)と表される。

【0027】

また、このGaN系MOSFET10では、電子走行層13のゲート電極18直下の領域には、AlGaN/GaNヘテロ接合構造が存在しないため、2次元電子ガス層が形成されていない。ゲート電極18にしきい値以上の正電圧を印加すると、ゲート電極18直下の電子走行層13に反転層が形成される。この反転層が、MOS構造のゲート部の左右に形成された2次元電子ガス層22と連結されてドレイン電流が流れるようになっている。

【0028】

つぎに、図1に示すGaN系MOSFET10の製造方法を、図2および図3に基づいて説明する。

(1)シリコン(111)基板11をMOCVD装置内にセットする。

【0029】

(2)AlN及びGaNの原料としてアンモニア(NH3)、トリメチルアルミニウム(TMAl)、トリメチルガリウム(TMGa)を使用し、シリコン基板11上に、バッファ層12、電子走行層13及び電子供給層14を順次エピタキシャル成長する(図2(a)参照)。

この工程(2)では、まず、シリコン基板11を、1100℃で10分間、水素雰囲気でサーマルクリーニングした後、シリコン基板11の(111)面上にAlN(100nm)を成長させた後、GaN(200nm)とAlN(20nm)からなる複合層を8層積層したバッファ層12を1050℃で成長させる。次に、バッファ層12の上にp−GaN(500nm)からなる電子走行層13を1050℃で成長させる。次に、電子走行層13の上にアンドープAl0.25Ga0.75N(20nm)からなる電子供給層14を1050℃で成長させる。

【0030】

なお、電子走行層13に対するp型のドーピング源としてビスシクロペンタディエニルマグネシウム(Cp2Mg)を用い、Mgの濃度が1×1018cm−3程度になるようにCp2Mgの流量を調整する。このようにして、図2(a)に示す積層構造が完成する。

【0031】

(3)次に、電子供給層14上に、SiO2からなるエッチングマスク24をプラズマ化学気相成長(PECVD)法により厚さ300nm成膜する。このとき、原料はSiH4とN2Oを用いる(図2(b)参照)。

この後、エッチングマスク24に、フォトリソグラフィーと反応性イオンエッチング(RIE)により、後述するリセス部の形成領域に開口部24aを形成する(図2(b)参照)。

【0032】

(4)次に、塩素系ガスを用いたドライエッチング装置で、エッチングマスク24を用いて、電子供給層14の一部(ゲート電極形成領域)を電子走行層13に到る深さ(40nm)までエッチングにより除去してリセス部25を形成する(図2(c)参照)。

【0033】

(5)次に、RCA洗浄後、電子供給層14上とリセス部25の内表面上とに、SiO2からなるゲート絶縁膜15を60nm成膜する(図2(d)参照)。

【0034】

(6)次に、ゲート絶縁膜15の表面全体にp型AlGaInPからなる第1の層19a、この第1の層19a上にp型GaAsからなる第2の層20aを、MOCVD法を用いてそれぞれ成長させる(図3(a)参照)。

この工程(5)では、原料としてTMAl、TMGa、トリメチルインジウム(TMIn)、ホスフィン(PH3)、アルシン(AsH3)を用い、p型ドーピングとして(TEZ)を用いる。

【0035】

(7)次に、第2の層20aの表面全体に、SiNxからなるエッチングマスク27を成膜する(図3(b)参照)。この成膜は、原料としてSiH4とN2を用いて、PECVD法により300nm成膜する。その後、エッチングマスク27に、フォトリソグラフィーと緩衝フッ酸を用いて微細加工を行い、ゲート電極形成領域以外のエッチングマスク27を除去してマスク27aを形成する(図3(c)参照)。

【0036】

(8)次に、マスク27aを用いて、第1の層19a、および第2の層20aを、エッチング液(硫酸:過酸化水素:水=1:1:4)でエッチングして、第1のゲート層19、および第2のゲート層20を形成する(図3(c)参照)。この後、マスク27aを除去する。

【0037】

(9)次に、SiO2からなるゲート絶縁膜15の、ソース電極とドレイン電極となる部分を除去し、この後、電子供給層14上のゲート絶縁膜15が除去された部分に、フォトリソグラフィー、およびリフトオフ法を用いて、ソース電極16とドレイン電極17を形成する(図3(d)参照)。

【0038】

この後、形成したソース電極16とドレイン電極17に、オーミック接触を得るための熱処理(600℃、10分)を行った。ソース電極16とドレイン電極17は、例えばTi(25nm)とAl(200nm)を積層したオーミック電極である。

【0039】

(10)次に、p型GaAsからなる第2のゲート層20上に、ゲート電極18のパット部分として、フォトリソグラフィー、スパッタや真空蒸着法、およびリフトオフ法を用いて、AuGe/Auからなる金属層(AuGe/Au電極)21を形成する(図3(e)参照)。この後、形成した金属層21に、オーミック接触を取るための熱処理(400℃、5分)を行った。

以上の工程により、図1に示すGaN系MOSFET10が形成できる。

【0040】

以上の構成を有するGaN系MOSFET10によれば、以下の作用効果を奏する。

ゲート電極18(ゲート電極18の第1のゲート層19)に、p−GaNからなる電子走行層13の仕事関数(6〜7eV)と同等或いはそれ以上の仕事関数を有するAlGaInPを用いているので、ノーマリオフ動作が可能になる。これにより、ゲート電極18にバイアス(正電圧)が印加されていないときには電流が流れず、ゲート電極に正電圧を印加することによって電流が流れるノーマリオフ型のGaN系MOSFETを実現できる。

また、AlGaInPの混晶比を変化させることにより、フラットバンド電圧を変えることが出来るので、しきい値電圧をオン特性等の他の特性を変化させること無く制御することが出来る。

【0041】

また、ゲート電極18の第1のゲート層19に、仕事関数が6eV以上のAlGaInPを用いているので、ノーマリオフ動作が可能になり、ノーマリオフ型のGaN系MOSFETを実現できる。

【0042】

また、ゲート電極18の第1のゲート層19をp型のAlGaInPとすると、その仕事関数は7eV程度であり、GaNと同程度の仕事関数とすることができる。また、AlGaInPにおいてAl、Ga、Inの混晶比を変化させることにより、フラットバンドを変えることが出来るので、しきい値をオン特性等の他の特性を変化させること無く制御することが出来る。

【0043】

更に、ゲート電極18は、ゲート絶縁膜15上に形成されたp型AlGaInPからなる第1のゲート層19と、この上に形成されたp型GaAsからなる第2のゲート層20との積層構造を有する。また、第2のゲート層20上に、AuGe/Auからなる金属層(AuGe/Au電極)21が形成されている。

【0044】

このように、ゲート電極18の第1のゲート層19におけるAlGaInP混晶の混晶比を変化させることにより、その仕事関数を変えることができる。例えば、p型InPの仕事関数は、5.75eVであり、p型GaPの仕事関数は、6.5eVである。すなわち、第1のゲート層19の組成をp型のInPからGaPに変化させることで、その仕事関数を0.75eV変えることができる。これにより、フラットバンド電圧を変えることが出来るので、しきい値電圧をオン特性等の他の特性を変化させること無く制御することが出来る。

【0045】

なお、上記一実施形態ではシリコン(111)基板11を用いているが、本発明はこれに限らず、SiC基板、サファイア基板、GaN基板、MgO基板、ZnO基板上など、GaNが結晶成長可能なあらゆる基板を用いたGaN系MOSFETについても成り立つことは言うまでも無い。また、上記一実施形態では、AlGaN/GaNからなるヘテロ接合構造を有するHFETに、MOS構造を採用したGaN系MOSFET10について説明したが、本発明はこれに限定されない。本発明は、GaN系化合物半導体からなるチャネル層とゲート電極との間にゲート絶縁膜が形成されたGaN系MOSFETに広く適用可能である。

【0046】

例えば、本発明は、図4に示すようなnチャネルのGaN系MOSFET10Aにも適用可能である。図4において31は基板であり、この基板31上にp-GaNからなるエピタキシャル層33が形成されている。35はゲート絶縁膜としてのゲート酸化膜、36はソース電極、37はドレイン電極、38はゲート電極である。また、42、44はオーミックコンタクト層(n+層)、43は電界集中の緩和を目的としたリサーフ層である。エピタキシャル層33の、オーミックコンタクト層42とリサーフ層43との間の領域がチャネル領域(チャネル層)になっている。図4に示すようなGaN系MOSFETにおいても、ゲート電極38のゲート酸化膜35に接する部分をAlGaInPで構成することにより、ノーマリオフ動作が可能になると共に、しきい値電圧を容易に制御することが出来る。

【符号の説明】

【0047】

10:GaN系MOSFET

11:シリコン(111)基板

12:バッファ層

13:電子走行層

14:電子供給層

15:ゲート絶縁膜

16:ソース電極

17:ドレイン電極

18:ゲート電極

19:第1のゲート層

20:第2のゲート層

21:金属層(AuGe/Au電極)

22:2次元電子ガス層

25:リセス部

【技術分野】

【0001】

本発明は、GaN系化合物半導体からなるチャネル層とゲート電極との間にゲート絶縁膜が形成されたGaN系MOS型電界効果トランジスタ(MOSFET)に関する。

【背景技術】

【0002】

III−V族窒化物系化合物半導体に代表されるワイドバンドギャップ半導体は、高い絶縁破壊耐圧、良好な電子輸送特性、良好な熱伝導度を持つので、高温環境用、大パワー用、あるいは高周波用の半導体デバイスの材料として非常に好適である。

例えば、GaN系化合物半導体材料は、GaAs系の材料に比べてそのバンドギャップエネルギーが大きく、耐熱度が高いため、GaN系化合物半導体を用いた素子は、高温環境下での動作が可能である。更に、GaN系化合物半導体を用いた素子は、絶縁破壊耐圧が高く、オン抵抗が低いため、低消費電力・省エネルギーの動作が可能となる。そのため、これらの材料、とくにGaN/AlGaN系化合物半導体を用いた電界効果トランジスタ(Field Effect Transistor:FET)やパワースイッチング用ダイオードの開発が進められている。

【0003】

このようなGaN系化合物半導体を用いた素子としては、故障時のフェイルセーフのためにノーマリオフ動作が求められている。GaN系化合物半導体を用いたノーマリオフ型の電子デバイスとして、MOS電界効果トランジスタ(GaN系MOSFET)が検討されている。 従来、GaN系MOSFETにおいては、ゲート電極としてポリシリコン(poly−Si)が使用される。これは、SiのMOSFETにおいて、ゲート電極として広くポリシリコンが使用されているためである。

しかし、p-GaNからなるチャネル層を有するGaN系MOSFETにおいては、p-GaNの仕事関数が6〜7eV程度あると考えられており、ポリシリコンの仕事関数の5eVより大きく、ゲート電圧が0Vの段階で、反転状態である。そのため、GaN系MOSFETでは、ノーマリオフ化が困難となっている。

【0004】

GaN系化合物半導体(p-GaN)からなるチャネル層とゲート電極との間にゲート絶縁膜が形成されたGaN系MOSFETにおいて、しきい値電圧を制御するパラメータとして下記の3つが挙げられる。

(1)ゲート絶縁膜の厚さ

(2)p-GaNからなるチャネル層のアクセプタ濃度

(3)ゲート電極の仕事関数

しかし、パラメータ(1)や(2)は、オン特性とトレードオフ関係になっており、これらのパラメータ(1)や(2)をしきい値制御のために変更するのは得策ではない。すなわち、しきい値を上げるために、ゲート絶縁膜を厚くしたり、チャネル層のアクセプタ濃度を高くしたりすると、オン特性が劣化してしまう。一方、パラメータ(3)は他の特性を変えずにしきい値を変更出来る利点がある。

【0005】

例えば特許文献1に開示された絶縁ゲート電界効果トランジスタ(MISHFET)では、ゲート電極としてSiCを用いている。このMISHFETでは、AlGaNバリア層の上にSiNxゲート絶縁膜、p型多結晶SiC層、オーミック電極であるPt/Auゲート電極が順次形成されている。p型多結晶SiC層は仕事関数が相対的に大きいので、ゼロバイアス状態でもMISHFETのチャネルが空乏化されて、ノーマリオフ動作が生じる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−147951号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

仕事関数は一般に物質固有の値であり、その値を自由に制御出来るわけではない。そのため、上記従来技術では、AlGaNバリア層の上に形成されたp型多結晶SiC層の仕事関数が一意に決まるため、しきい値を正に出来ても、その値を自由に制御出来なかった。

そこで、本発明は、このような従来の問題点に着目して為されたもので、その目的は、ノーマリオフ動作を可能にし、かつしきい値電圧を自由に制御出来るGaN系MOS型電界効果トランジスタを提供することにある。

【課題を解決するための手段】

【0008】

理想的なGaN系MOSFETを作製する場合、チャネル部分の物質とゲート電極の物質の仕事関数が同じで有ることが望ましい。しかし、GaNにおいてはp型ドーパントの活性化率が悪いことや、成長温度が高いことから、ゲート絶縁膜であるSiO2上にゲート電極としてp−GaNを成長させるのが困難であった。そのため、チャネル層と同程度の仕事関数を持つ他の物質を使用することとなる。本発明者らは鋭意研究の結果、そのような物質として多結晶のAlGaInPが有効であることを見出した。p型AlGaInP混晶は仕事関数が5.5〜7eVであり、p−GaNと同程度の仕事関数を持つ。例えば、p−AlPの仕事関数は7eV程度である。AlGaInPにおいてAl、Ga、Inの混晶比を変化させることにより、フラットバンド電圧を変えることが出来るので、しきい値をオン特性等の他の特性を変化させること無く制御することが出来る。本発明はこのような知見に基づきなされたものである。

【0009】

上記課題を解決するために、請求項1に記載の発明に係るGaN系MOS型電界効果トランジスタは、GaN系化合物半導体からなるチャネル層とゲート電極との間にゲート絶縁膜が形成されたGaN系MOS型電界効果トランジスタにおいて、前記ゲート電極は、AlGaInPからなることを特徴とする。

【0010】

請求項2に記載の発明に係るGaN系MOS型電界効果トランジスタは、前記AlGaInPは、仕事関数が6eV以上であることを特徴とする。

【0011】

請求項3に記載の発明に係るGaN系MOS型電界効果トランジスタは、前記AlGaInPは多結晶であることを特徴とする。

【0012】

請求項4に記載の発明に係るGaN系MOS型電界効果トランジスタは、前記AlGaInPはp型であることを特徴とする。

【0013】

請求項5に記載の発明に係るGaN系MOS型電界効果トランジスタは、前記チャネル層は、電子走行層と、前記電子走行層上に形成され、前記電子走行層よりも大きいバンドギャップエネルギーを持つGaN系化合物半導体からなる電子供給層とを有し、前記電子供給層のゲートに相当する部分に前記電子走行層に達する深さで形成されたリセス部と、該リセス部に前記ゲート絶縁膜を介して形成された前記ゲート電極と、前記ゲート電極を挟んで前記電子供給層上に形成されたソース電極とドレイン電極とを備えていることを特徴とする。

【0014】

請求項6に記載の発明に係るGaN系MOS型電界効果トランジスタは、前記ゲート電極は、前記ゲート絶縁膜上に形成された仕事関数が5.5〜7eVである第一のゲート層と、前記第一のゲート層よりも仕事関数の小さい第二のゲート層とを備えることを特徴とする。

【発明の効果】

【0015】

請求項1に記載の発明によれば、ゲート電極として、チャネル層の仕事関数と同等或いはそれ以上の仕事関数を有するAlGaInPを用いているので、ノーマリオフ動作が可能になる。また、AlGaInPの混晶比を変化させることにより、フラットバンド電圧を変えることが出来るので、しきい値電圧を、オン特性等の他の特性を変化させること無く制御することが出来る。

【図面の簡単な説明】

【0016】

【図1】本発明の第1の実施形態に係るGaN系MOSFETの概略構成を示す断面図である。

【図2】(a)〜(d)は第1の実施形態に係るGaN系MOSFETの作製方法を説明する図である。

【図3】(a)〜(e)は第1の実施形態に係るGaN系MOSFETの作製方法を説明する図である。

【図4】本発明の第2の実施形態に係るGaN系MOSFETの概略構成を示す断面図である。

【発明を実施するための形態】

【0017】

以下に、本発明に係るGaN系MOSFETの実施の形態を図面に基づいて説明する。

図1は、本発明の一実施形態に係るGaN系MOSFET10の概略構成を示している。

GaN系MOSFET10は、GaN系化合物半導体からなるチャネル層とゲート電極との間にゲート絶縁膜が形成されたGaN系MOS型電界効果トランジスタ(GaN系MOSFET)の一例として、AlGaN/GaNからなるヘテロ接合構造を有するヘテロ接合電界効果トランジスタ(HFET: Hetero-junction Field Effect Transistor)に、MOS(Metal Oxide Semiconductor)構造を採用したGaN系MOSFETである。

【0018】

GaN系MOSFET10は、図1に示すように、シリコン(111)基板11上に、AlNとGaNの積層構造からなるバッファ層12と、チャネル層としてのp−GaNからなる電子走行層13と、電子走行層13上に形成され、電子走行層13よりも大きいバンドギャップエネルギーを持つアンドープAlGaNからなる電子供給層14とが順次積層されている。

なお、GaN系MOSFET10は、基板11とバッファ層12との間に、AlN層が形成された構造であってもよい。また、バッファ層12は、不純物として炭素(C)がドーピングされた高抵抗なAlN、GaNの積層構造であることが好ましい。

【0019】

このGaN系MOSFET10においては、電子供給層14の一部(ゲート電極形成領域)が電子走行層13に到る深さまで除去され、リセス部25が形成されている。

電子供給層14上には、リセス部25を挟んでソース電極16およびドレイン電極17が形成されている。電子供給層14上とリセス部25の内表面上とには、SiO2からなるゲート絶縁膜15が形成されている。さらに、ゲート絶縁膜15の、リセス部25を覆う部分の表面上には、ゲート電極18が形成されている。

【0020】

このGaN系MOSFET10では、電子供給層14は、ゲート電極18直下の電子走行層13、ゲート絶縁膜15およびゲート電極18で構成されるMOS構造のゲート部を挟んで互いに離隔された左右の電子供給層14a、14bを有する。なお、GaN系MOSFET10は、電子走行層13と左右の電子供給層14a、14bとの間に、電子走行層13より不純物濃度の低いp型またはアンドープのGaN系化合物半導体からなる中間層が形成された構成であってもよい。

【0021】

このようなAlGaN/GaNヘテロ接合構造を有するGaN系MOSFET10では、電子走行層13と左右の電子供給層14a、14bの界面、つまり、左右のAlGaN/GaNヘテロ接合界面にピエゾ効果によって、電子走行層13側に2次元電子ガス層22がそれぞれ発生している。2次元電子ガス層22がキャリアとなって電子走行層13は低抵抗、高移動度となるため、GaN系MOSFET10のオン抵抗を小さくし、スイッチング速度を向上させることができる。

【0022】

更に、このGaN系MOSFET10では、ノーマリオフ動作を可能にし、かつしきい値電圧を自由に制御出来るようにするために、ゲート電極18は、仕事関数が電子走行層13の仕事関数と同等或いはそれ以上であるAlGaInPを用いて形成されている。

【0023】

つまり、ゲート電極18として、電子走行層13を構成するp-GaNの仕事関数と同等或いはそれ以上の仕事関数(5.5〜7eV)を有し、かつ自由に仕事関数を制御出来る物質としてAlGaInPを用いる。AlGaInPは多結晶体であるのが好ましい。 また、AlGaInPはp型であるのが好ましい。

【0024】

図1に示すゲート電極18は、ゲート絶縁膜15上のゲート電極形成領域に形成されたAlGaInPからなるゲート部半導体層と、該ゲート部半導体層上に形成された金属層とを備えている。ゲート部半導体層は、ゲート絶縁膜15上に形成されたp型AlGaInP混晶からなる第1のゲート層19と、第1のゲート層19上に形成されたp型GaAsからなる第2のゲート層20との積層構造になっている。また、第2のゲート層20上に、AuGe/Auからなる金属層(AuGe/Au電極)21が形成されている。

【0025】

ゲート電極をAlGaInPで構成することにより、GaN系MOSFET10は、ノーマリオフ動作が可能となる。また、AlGaInPの混晶比を変化させることにより、フラットバンド電圧を変えることが出来るので、しきい値電圧を、オン特性等の他の特性を変化させること無く制御することが出来る。

【0026】

ここで、AlGaInPの混晶比とは、Al、Ga、およびInの組成を、その合計が1となるように構成した比であり、Al、Gaの組成比をそれぞれx、yとした場合、AlxGayIn1−x−yP(0≦x≦1、0≦y≦1、0≦x+y≦1)と表される。

【0027】

また、このGaN系MOSFET10では、電子走行層13のゲート電極18直下の領域には、AlGaN/GaNヘテロ接合構造が存在しないため、2次元電子ガス層が形成されていない。ゲート電極18にしきい値以上の正電圧を印加すると、ゲート電極18直下の電子走行層13に反転層が形成される。この反転層が、MOS構造のゲート部の左右に形成された2次元電子ガス層22と連結されてドレイン電流が流れるようになっている。

【0028】

つぎに、図1に示すGaN系MOSFET10の製造方法を、図2および図3に基づいて説明する。

(1)シリコン(111)基板11をMOCVD装置内にセットする。

【0029】

(2)AlN及びGaNの原料としてアンモニア(NH3)、トリメチルアルミニウム(TMAl)、トリメチルガリウム(TMGa)を使用し、シリコン基板11上に、バッファ層12、電子走行層13及び電子供給層14を順次エピタキシャル成長する(図2(a)参照)。

この工程(2)では、まず、シリコン基板11を、1100℃で10分間、水素雰囲気でサーマルクリーニングした後、シリコン基板11の(111)面上にAlN(100nm)を成長させた後、GaN(200nm)とAlN(20nm)からなる複合層を8層積層したバッファ層12を1050℃で成長させる。次に、バッファ層12の上にp−GaN(500nm)からなる電子走行層13を1050℃で成長させる。次に、電子走行層13の上にアンドープAl0.25Ga0.75N(20nm)からなる電子供給層14を1050℃で成長させる。

【0030】

なお、電子走行層13に対するp型のドーピング源としてビスシクロペンタディエニルマグネシウム(Cp2Mg)を用い、Mgの濃度が1×1018cm−3程度になるようにCp2Mgの流量を調整する。このようにして、図2(a)に示す積層構造が完成する。

【0031】

(3)次に、電子供給層14上に、SiO2からなるエッチングマスク24をプラズマ化学気相成長(PECVD)法により厚さ300nm成膜する。このとき、原料はSiH4とN2Oを用いる(図2(b)参照)。

この後、エッチングマスク24に、フォトリソグラフィーと反応性イオンエッチング(RIE)により、後述するリセス部の形成領域に開口部24aを形成する(図2(b)参照)。

【0032】

(4)次に、塩素系ガスを用いたドライエッチング装置で、エッチングマスク24を用いて、電子供給層14の一部(ゲート電極形成領域)を電子走行層13に到る深さ(40nm)までエッチングにより除去してリセス部25を形成する(図2(c)参照)。

【0033】

(5)次に、RCA洗浄後、電子供給層14上とリセス部25の内表面上とに、SiO2からなるゲート絶縁膜15を60nm成膜する(図2(d)参照)。

【0034】

(6)次に、ゲート絶縁膜15の表面全体にp型AlGaInPからなる第1の層19a、この第1の層19a上にp型GaAsからなる第2の層20aを、MOCVD法を用いてそれぞれ成長させる(図3(a)参照)。

この工程(5)では、原料としてTMAl、TMGa、トリメチルインジウム(TMIn)、ホスフィン(PH3)、アルシン(AsH3)を用い、p型ドーピングとして(TEZ)を用いる。

【0035】

(7)次に、第2の層20aの表面全体に、SiNxからなるエッチングマスク27を成膜する(図3(b)参照)。この成膜は、原料としてSiH4とN2を用いて、PECVD法により300nm成膜する。その後、エッチングマスク27に、フォトリソグラフィーと緩衝フッ酸を用いて微細加工を行い、ゲート電極形成領域以外のエッチングマスク27を除去してマスク27aを形成する(図3(c)参照)。

【0036】

(8)次に、マスク27aを用いて、第1の層19a、および第2の層20aを、エッチング液(硫酸:過酸化水素:水=1:1:4)でエッチングして、第1のゲート層19、および第2のゲート層20を形成する(図3(c)参照)。この後、マスク27aを除去する。

【0037】

(9)次に、SiO2からなるゲート絶縁膜15の、ソース電極とドレイン電極となる部分を除去し、この後、電子供給層14上のゲート絶縁膜15が除去された部分に、フォトリソグラフィー、およびリフトオフ法を用いて、ソース電極16とドレイン電極17を形成する(図3(d)参照)。

【0038】

この後、形成したソース電極16とドレイン電極17に、オーミック接触を得るための熱処理(600℃、10分)を行った。ソース電極16とドレイン電極17は、例えばTi(25nm)とAl(200nm)を積層したオーミック電極である。

【0039】

(10)次に、p型GaAsからなる第2のゲート層20上に、ゲート電極18のパット部分として、フォトリソグラフィー、スパッタや真空蒸着法、およびリフトオフ法を用いて、AuGe/Auからなる金属層(AuGe/Au電極)21を形成する(図3(e)参照)。この後、形成した金属層21に、オーミック接触を取るための熱処理(400℃、5分)を行った。

以上の工程により、図1に示すGaN系MOSFET10が形成できる。

【0040】

以上の構成を有するGaN系MOSFET10によれば、以下の作用効果を奏する。

ゲート電極18(ゲート電極18の第1のゲート層19)に、p−GaNからなる電子走行層13の仕事関数(6〜7eV)と同等或いはそれ以上の仕事関数を有するAlGaInPを用いているので、ノーマリオフ動作が可能になる。これにより、ゲート電極18にバイアス(正電圧)が印加されていないときには電流が流れず、ゲート電極に正電圧を印加することによって電流が流れるノーマリオフ型のGaN系MOSFETを実現できる。

また、AlGaInPの混晶比を変化させることにより、フラットバンド電圧を変えることが出来るので、しきい値電圧をオン特性等の他の特性を変化させること無く制御することが出来る。

【0041】

また、ゲート電極18の第1のゲート層19に、仕事関数が6eV以上のAlGaInPを用いているので、ノーマリオフ動作が可能になり、ノーマリオフ型のGaN系MOSFETを実現できる。

【0042】

また、ゲート電極18の第1のゲート層19をp型のAlGaInPとすると、その仕事関数は7eV程度であり、GaNと同程度の仕事関数とすることができる。また、AlGaInPにおいてAl、Ga、Inの混晶比を変化させることにより、フラットバンドを変えることが出来るので、しきい値をオン特性等の他の特性を変化させること無く制御することが出来る。

【0043】

更に、ゲート電極18は、ゲート絶縁膜15上に形成されたp型AlGaInPからなる第1のゲート層19と、この上に形成されたp型GaAsからなる第2のゲート層20との積層構造を有する。また、第2のゲート層20上に、AuGe/Auからなる金属層(AuGe/Au電極)21が形成されている。

【0044】

このように、ゲート電極18の第1のゲート層19におけるAlGaInP混晶の混晶比を変化させることにより、その仕事関数を変えることができる。例えば、p型InPの仕事関数は、5.75eVであり、p型GaPの仕事関数は、6.5eVである。すなわち、第1のゲート層19の組成をp型のInPからGaPに変化させることで、その仕事関数を0.75eV変えることができる。これにより、フラットバンド電圧を変えることが出来るので、しきい値電圧をオン特性等の他の特性を変化させること無く制御することが出来る。

【0045】

なお、上記一実施形態ではシリコン(111)基板11を用いているが、本発明はこれに限らず、SiC基板、サファイア基板、GaN基板、MgO基板、ZnO基板上など、GaNが結晶成長可能なあらゆる基板を用いたGaN系MOSFETについても成り立つことは言うまでも無い。また、上記一実施形態では、AlGaN/GaNからなるヘテロ接合構造を有するHFETに、MOS構造を採用したGaN系MOSFET10について説明したが、本発明はこれに限定されない。本発明は、GaN系化合物半導体からなるチャネル層とゲート電極との間にゲート絶縁膜が形成されたGaN系MOSFETに広く適用可能である。

【0046】

例えば、本発明は、図4に示すようなnチャネルのGaN系MOSFET10Aにも適用可能である。図4において31は基板であり、この基板31上にp-GaNからなるエピタキシャル層33が形成されている。35はゲート絶縁膜としてのゲート酸化膜、36はソース電極、37はドレイン電極、38はゲート電極である。また、42、44はオーミックコンタクト層(n+層)、43は電界集中の緩和を目的としたリサーフ層である。エピタキシャル層33の、オーミックコンタクト層42とリサーフ層43との間の領域がチャネル領域(チャネル層)になっている。図4に示すようなGaN系MOSFETにおいても、ゲート電極38のゲート酸化膜35に接する部分をAlGaInPで構成することにより、ノーマリオフ動作が可能になると共に、しきい値電圧を容易に制御することが出来る。

【符号の説明】

【0047】

10:GaN系MOSFET

11:シリコン(111)基板

12:バッファ層

13:電子走行層

14:電子供給層

15:ゲート絶縁膜

16:ソース電極

17:ドレイン電極

18:ゲート電極

19:第1のゲート層

20:第2のゲート層

21:金属層(AuGe/Au電極)

22:2次元電子ガス層

25:リセス部

【特許請求の範囲】

【請求項1】

GaN系化合物半導体からなるチャネル層とゲート電極との間にゲート絶縁膜が形成されたGaN系MOS型電界効果トランジスタにおいて、

前記ゲート電極は、AlGaInPからなることを特徴とするGaN系MOS型電界効果トランジスタ。

【請求項2】

前記AlGaInPは、仕事関数が6eV以上であることを特徴とする請求項1に記載のGaN系MOS型電界効果トランジスタ。

【請求項3】

前記AlGaInPは多結晶であることを特徴とする請求項1又は2に記載のGaN系MOS型電界効果トランジスタ。

【請求項4】

前記AlGaInPはp型であることを特徴とする請求項1乃至3のいずれか一つに記載のGaN系MOS型電界効果トランジスタ。

【請求項5】

前記チャネル層は、電子走行層と、前記電子走行層上に形成され、前記電子走行層よりも大きいバンドギャップエネルギーを持つGaN系化合物半導体からなる電子供給層とを有し、

前記電子供給層のゲートに相当する部分に前記電子走行層に達する深さで形成されたリセス部と、

該リセス部に前記ゲート絶縁膜を介して形成された前記ゲート電極と、

前記ゲート電極を挟んで前記電子供給層上に形成されたソース電極とドレイン電極とを備えていることを特徴とする請求項1乃至4のいずれか一つに記載のGaN系MOS型電界効果トランジスタ。

【請求項6】

前記ゲート電極は、前記ゲート絶縁膜上に形成された仕事関数が5.5〜7eVである第一のゲート層と、前記第一のゲート層よりも仕事関数の小さい第二のゲート層とを備えることを特徴とする請求項1乃至5のいずれか一つに記載のGaN系MOS型電界効果トランジスタ。

【請求項1】

GaN系化合物半導体からなるチャネル層とゲート電極との間にゲート絶縁膜が形成されたGaN系MOS型電界効果トランジスタにおいて、

前記ゲート電極は、AlGaInPからなることを特徴とするGaN系MOS型電界効果トランジスタ。

【請求項2】

前記AlGaInPは、仕事関数が6eV以上であることを特徴とする請求項1に記載のGaN系MOS型電界効果トランジスタ。

【請求項3】

前記AlGaInPは多結晶であることを特徴とする請求項1又は2に記載のGaN系MOS型電界効果トランジスタ。

【請求項4】

前記AlGaInPはp型であることを特徴とする請求項1乃至3のいずれか一つに記載のGaN系MOS型電界効果トランジスタ。

【請求項5】

前記チャネル層は、電子走行層と、前記電子走行層上に形成され、前記電子走行層よりも大きいバンドギャップエネルギーを持つGaN系化合物半導体からなる電子供給層とを有し、

前記電子供給層のゲートに相当する部分に前記電子走行層に達する深さで形成されたリセス部と、

該リセス部に前記ゲート絶縁膜を介して形成された前記ゲート電極と、

前記ゲート電極を挟んで前記電子供給層上に形成されたソース電極とドレイン電極とを備えていることを特徴とする請求項1乃至4のいずれか一つに記載のGaN系MOS型電界効果トランジスタ。

【請求項6】

前記ゲート電極は、前記ゲート絶縁膜上に形成された仕事関数が5.5〜7eVである第一のゲート層と、前記第一のゲート層よりも仕事関数の小さい第二のゲート層とを備えることを特徴とする請求項1乃至5のいずれか一つに記載のGaN系MOS型電界効果トランジスタ。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2011−129607(P2011−129607A)

【公開日】平成23年6月30日(2011.6.30)

【国際特許分類】

【出願番号】特願2009−284785(P2009−284785)

【出願日】平成21年12月16日(2009.12.16)

【出願人】(000005290)古河電気工業株式会社 (4,457)

【Fターム(参考)】

【公開日】平成23年6月30日(2011.6.30)

【国際特許分類】

【出願日】平成21年12月16日(2009.12.16)

【出願人】(000005290)古河電気工業株式会社 (4,457)

【Fターム(参考)】

[ Back to top ]