GeSn半導体デバイスの製造方法

【課題】不整合転位や不純物をほとんど含まず良質であり、光デバイスとして利用可能なGeSn半導体デバイスを得る。

【解決手段】シリコン基板1に形成した極薄酸化膜2上に分子線エピタキシャル法を用いてGe5とSn6とを蒸着することで、GeSn半導体のナノメーターサイズの微結晶(ナノドット)3を超高密度に形成して、GeSn半導体デバイスを得る。該半導体のドット3は不整合転位や不純物をほとんど含まず良質であり、光デバイスとして利用することができる。

【解決手段】シリコン基板1に形成した極薄酸化膜2上に分子線エピタキシャル法を用いてGe5とSn6とを蒸着することで、GeSn半導体のナノメーターサイズの微結晶(ナノドット)3を超高密度に形成して、GeSn半導体デバイスを得る。該半導体のドット3は不整合転位や不純物をほとんど含まず良質であり、光デバイスとして利用することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、GeSn半導体のドットを有するGeSn半導体デバイスの製造方法に関する。

【背景技術】

【0002】

Ge及びSnからなる半導体(以下、“GeSn半導体”とする)は、Si基板上のモノリシックな多機能デバイスの実現を可能とする材料であり、その組成比によっては直接遷移型半導体となり(例えば、非特許文献1参照)、IV族半導体光デバイスとして有望視されている。このGeSn半導体は、組成比に応じてエネルギーバンドギャップが変化するため、発光波長をある程度任意に制御できる可能性も有している。

【非特許文献1】G.He,and H.A.Atwater,Interbandtransitions in SnxGe1-x alloys,Phys.Rev.Lett.79(1997)1937

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、不純物の少ないGeSn半導体を得る方法は未だ確率されていない。

【0004】

また、Ge中のSnは偏析しやすく、高い基板温度での蒸着が困難であるため、結晶性の良いGeSn半導体を得ることは難しいという問題があった。

【0005】

さらに、GeSnとSiとの格子定数の差が大きく、Si基板上にGeSn半導体薄膜を形成すると、格子不整合から生ずる歪みを緩和するための不整合転位が該薄膜内に発生してしまうという問題もあった。

【0006】

なお、そのような不整合転位の発生を抑制する方法としては、GeSnと格子定数の差が比較的少ないGeを、Si基板上に薄膜形成し、そのGe薄膜上にGeSn半導体を形成する方法が考えられる。しかし、Si基板上のGe層は、Stranski−Krasnotav成長し、平坦な緩和Ge層を得ることが難しいという問題があった。

【0007】

また、仮に良質のGeSn混晶薄膜を形成できたとしても、Snの偏析が無い状態で、かつ、直接遷移型半導体が得られるという条件の組成比(具体的には、1:1−x。但し、0.1≦x≦0.2)では、バンドギャップは0.2〜0.5eV程度にしかならず、光ファイバの透過光の波長より小さくなってしまい、光通信への利用は困難であった。

【0008】

本発明は、上述のような問題の無いGeSn半導体デバイスの製造方法を提供することを目的とするものである。

【課題を解決するための手段】

【0009】

請求項1に係る発明は、図1乃至図6に例示するものであって、単結晶Si、Ge或いはSiGeからなる基板(1)に基板側酸化膜(2)を形成する工程と、

該基板側酸化膜(2)にGe(5)とSn(6)とを蒸着することに基づきGeSn半導体のドット(3)を作製する工程と、を有するGeSn半導体デバイスの製造方法に関するものである。

【0010】

請求項2に係る発明は、請求項1に係る発明において、前記基板(1)は、単結晶Si、Ge或いはSiGe基板、又は、エピタキシャル成長したSi層、Ge層、或いはSiGe混晶層を有する基板であることを特徴とする。

【0011】

請求項3に係る発明は、図7(a) 〜(d) に例示するものであって、請求項1又は2に記載の発明において、前記GeSn半導体のドット(3)を埋めるようにSi又はGeを蒸着してスペーサー層(4)を形成する工程と、

該スペーサー層(4)を熱酸化してスペーサー層側酸化膜(12)を形成する工程と、

GeとSnとを前記スペーサー層側酸化膜(12)に蒸着することに基づきGeSn半導体のドット(13)を該スペーサー層側酸化膜表面に作製する工程と、

を少なくとも1サイクル実施することを特徴とする。

【0012】

請求項4に係る発明は、請求項1乃至3のいずれか1項に記載の発明において、前記基板側酸化膜(2)又は前記スペーサー層側酸化膜(12)は、前記基板(1)又は前記スペーサー層(4)を酸素雰囲気中で熱酸化して1nm以下の厚さに形成したことを特徴とする。

【0013】

請求項5に係る発明は、図2に例示するものであって、請求項1乃至4のいずれか1項に記載の発明において、Ge(5)の蒸着を先に行い、その後、Sn(6)の蒸着を行うことにより前記GeSn半導体のドット(3)を形成することを特徴とする。

【0014】

請求項6に係る発明は、図3に例示するものであって、請求項1乃至4のいずれか1項に記載の発明において、Sn(6)の蒸着を先に行い、その後、Ge(5)の蒸着を行うことにより前記GeSn半導体のドット(3)を形成することを特徴とする。

【0015】

請求項7に係る発明は、図4に例示するものであって、請求項1乃至4のいずれか1項に記載の発明において、Ge(5)とSn(6)を同時に蒸着することにより行うことにより前記GeSn半導体のドット(3)を形成することを特徴とする。

【0016】

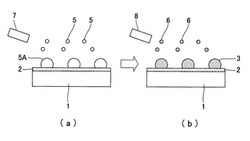

請求項8に係る発明は、図5に例示するものであって、請求項1乃至4のいずれか1項に記載の発明において、Ge(5)の蒸着を先に行ってGeの核(5A)を形成し、その後、Ge(5)とSn(6)を同時に蒸着することにより行うことにより前記GeSn半導体のドット(3)を形成することを特徴とする。

【0017】

請求項9に係る発明は、図6に例示するものであって、請求項1乃至4のいずれか1項に記載の発明において、Sn(6)の蒸着を先に行ってSnの核(6A)を形成し、その後、Ge(5)とSn(6)を同時に蒸着することにより行うことにより前記GeSn半導体のドット(3)を形成することを特徴とする。

【0018】

請求項10に係る発明は、請求項5,6,8,9のいずれか1項に記載の発明において、Ge(5)及びSn(6)を単独で蒸着するとき、基板温度は30℃から700℃の範囲であって、エピタキシャル成長をさせるか非エピタキシャル成長をさせるかに応じて調整することを特徴とする。

【0019】

請求項11に係る発明は、請求項5に係る発明において、Sn(6)の蒸着を行うときの基板温度は30℃から300℃の範囲であることを特徴とする。

【0020】

請求項12に係る発明は、請求項7乃至9に記載の発明において、Ge(5)及びSn(6)を同時に蒸着させるとき、基板温度は30℃から300℃の範囲とすることを特徴とする。

【0021】

請求項13に係る発明は、請求項10乃至12に記載の発明において、前記GeSn半導体は直接遷移型半導体であることを特徴とする。

【0022】

請求項14に係る発明は、請求項1乃至13のいずれか1項に記載の発明において、前記蒸着を、分子線エピタキシャル法、スパッタ法又は化学気相成長法により行うことを特徴とする。

【0023】

請求項15に係る発明は、請求項1乃至14のいずれか1項に記載の発明において、GeSn半導体におけるGe:Snの組成比は下式に示す通りであることを特徴とする。

【数3】

【0024】

請求項16に係る発明は、請求項12に係る発明において、Ge:Snの速度比は下式に示す通りであることを特徴とする。

【数4】

【0025】

請求項17に係る発明は、請求項1乃至16のいずれか1項に記載の発明において、前記GeSn半導体の組成比、及び該半導体のドットサイズを調整することにより、該半導体のエネルギーバンドギャップを適正範囲にして、光通信に利用可能な半導体デバイスを製造することを特徴とする。

【0026】

請求項18に係る発明は、請求項17に係る発明において、前記エネルギーバンドギャップの適正範囲は0.6eVから0.9eVの範囲であることを特徴とする。

【0027】

請求項19に係る発明は、請求項1乃至18のいずれか1項に記載の発明において、Ge及びSnの蒸着後、蒸着中或いは蒸着前に原子状の水素を前記基板に供給することを特徴とする。

【0028】

請求項20に係る発明は、請求項1乃至19のいずれか1項に記載の発明において、エレクトロルミネッセンスデバイスを製造することを特徴とする。

【0029】

なお、括弧内の番号などは、図面における対応する要素を示す便宜的なものであり、従って、本記述は図面上の記載に限定拘束されるものではない。

【発明の効果】

【0030】

請求項1乃至3、及び請求項20に係る発明によれば、GeSn半導体は微小なドットであるため歪エネルギーを低下させることができ、その結果、格子定数の不整合から生じる不整合転位を低減させることができる。また、1個当たりのドットに含まれる不純物や点欠陥の数を少なくできる(詳細は後述する)。さらに、GeSnの組成比を調整して直接遷移型半導体を得ることができ、ドットサイズを調整することにより、該半導体のエネルギーバンドギャップを適正範囲にして、光通信に利用可能な半導体デバイスを製造することができる。

【0031】

請求項4に係る発明によれば、極薄の酸化膜を用いることにより、高密度のGeSn半導体ドットを得ることができる。

【0032】

請求項5乃至16に係る発明によれば、微小で高密度な直接遷移型半導体を得るために有利でかつ結晶性の良いGeSn半導体ドットを得ることができる。

【0033】

請求項17及び18に係る発明によれば、光通信に利用できる半導体デバイスを製造することができる。

【0034】

請求項19に係る発明によれば、光デバイスとしてより良質なGeSn半導体を得ることができる。

【発明を実施するための最良の形態】

【0035】

以下、図1乃至図8に沿って、本発明を実施するための最良の形態について説明する。

【0036】

図1は、単結晶Si、Ge、或いはSiGe基板に基板側酸化膜を形成する様子を示す模式図であり、図2は、Geを蒸着した後にSnを蒸着してGeSn半導体デバイスを作製する様子を示す模式図である。また、図3は、Snを蒸着した後にGeを蒸着して半導体デバイスを作製する様子を示す模式図であり、図4は、Ge及びSnを同時に蒸着してGeSn半導体デバイスを作製する様子を示す模式図である。さらに、図5は、Geを蒸着した後にGe及びSnの同時蒸着を行って半導体デバイスを作製する様子を示す模式図であり、図6は、Snを蒸着した後にGe及びSnを蒸着してGeSn半導体デバイスを作成する様子を示す模式図である。また、図7は、多層の半導体デバイスを作製する様子を示す模式図であり、図8(a) はエピタキシャル成長時の様子を説明するための模式図であり、(b) は非エピタキシャル成長時の様子を説明するための模式図である。

【0037】

近年、シリコン系半導体においてナノメータースケールの微結晶(ナノドット)の開発が精力的に行われており、極薄Si酸化膜を利用して、SiとGeのナノドットを超高密度(>1012cm−2)に形成する技術が開発されている(A.A.Shklyaev、柴田 元司(M.Shibata)、市川 昌和(M.Ichikawa)、「High−density ultrasmall epitaxial Ge islands on Si(111)surfaces with a SiO2 coverage」、フィジカル・レビュー(Phys.Rev.)B62,(2000)1540.参照)。また、本発明者らは、超高密度シリサイドナノドットを形成する技術を提案している(特開2005−303249号公報参照)。

【0038】

本発明により製造されるGeSn半導体デバイスは、図2(b) 等に示すように、基板1と、該基板1に支持されたGeSn半導体のドット3と、を少なくとも備えている。

【0039】

ところで、本発明に用いる基板1としては、

・ 単結晶Si、Ge或いはSiGe基板や、

・ Si層、Ge層、或いはSiGe混晶層を単結晶Si基板上にエピタキシャル成長させたもの

を挙げることができる。

【0040】

なお、図2(b) 等に示すGeSn半導体デバイスの場合、符号2で示す酸化膜(後述するように、Ge5やSn6を蒸着する前に前記基板1の表面に形成されたもの。以下、"基板側酸化膜"とする)が基板1の全面にほぼ均一な膜厚で配置されていて、ドット3はこの基板側酸化膜2の表面に形成された状態となっているが、

・ 基板側酸化膜2が均一膜厚でなくても(例えば、図8(a) に符号10で示すように、基板側酸化膜2にボイドが形成されていても)、

・ 一旦形成された基板側酸化膜2が、GeやSnの蒸着等によって消失されてしまっていても(つまり、ドット3が、基板側酸化膜2の表面に形成されるのではなく、基板1の表面に形成された状態であっても)、

いずれでも良い。

【0041】

次に、本発明に係る半導体デバイスの製造方法について説明する。

【0042】

本発明に係る半導体デバイスの製造方法は、

・ 前記基板1に前記基板側酸化膜2を形成する工程と(図1(a) (b) 参照)、

・ 該基板側酸化膜2にGe5及びSn6を蒸着することに基づきGeSn半導体のドット3を形成する工程と(図2乃至図6参照)、

を備えている。

【0043】

Ge5及びSn6の蒸着順序は(1) 〜(5) のいずれかにすると良い。

(1) Ge5の蒸着を先に行ってドットを形成し(図2(a) の符号5A参照)、その後、Sn6の蒸着を行う場合(同図(b)

参照)

(2) Sn6の蒸着を先に行ってドットを形成し(図3(a) の符号6A参照)、その後、Ge5の蒸着を行う場合(同図(b)

参照)

(3) Ge5の蒸着とSn6の蒸着を同時に行う場合(図4参照)

(4) Ge5の蒸着を先に行ってGeの核を形成し(図5(a) の符号5A参照)、その後、Ge5の蒸着とSn6の蒸着を同時に行う場合(図5(b)

参照)

(5) Sn6の蒸着を先に行ってSnの核を形成し(図6(a) の符号6A参照)、その後、Ge5の蒸着とSn6の蒸着を同時に行う場合(図6(b)

参照)

【0044】

なお、GeやSnの蒸着は、分子線エピタキシャル法、スパッタ法又は化学気相成長法により行うと良い。すなわち、GeやSnの蒸着にはKnudsenセルを用い、Siの蒸着には電子線蒸着装置を用い、分子線エピタキシャル法により真空蒸着を行う方法、GeやSnをスパッタして蒸着するスパッタ法、或いは、GeやSnを含む反応ガス(GeH4、SnD4など)を供給して成長させる方法を使用すると良い。Ge、Snの蒸着量や供給量を調整してドットサイズを制御するようにすると良い(詳細は後述する)。また、Ge及びSnの蒸着後、蒸着中或いは蒸着前に原子状の水素を前記基板に供給すると良い。これにより、光デバイスとしてより良質なGeSn半導体を得ることができる。

【0045】

ところで、Ge5及びSn6を単独で蒸着するときの基板温度は30℃から700℃までの範囲にすると良い。また、その基板温度は、エピタキシャル成長させたいか、或いは非エピタキシャル成長させたいかによって調整すれば良い。なお、上記(1) (2) のようにGeの蒸着とSnの蒸着とを分けて別々に行う場合、それぞれの蒸着時の基板温度を異ならせることも可能となる。したがって、Geの蒸着時の基板温度とSnの蒸着時の基板温度とをそれぞれ最適に保持し、Ge中のSnの偏析を低減し、結晶性が良好で、光デバイスに最適な半導体ドットを形成することができる。さらに本発明によれば、安い材料にて安価に半導体デバイスを製造することが可能となり、またIV族半導体のみを使用しているため、既存のSiテクノロジーの利用とSi電子デバイスとの融合が可能となる。

【0046】

また、上記(1)

においてSnの蒸着を行うときの基板温度は30℃から300℃の範囲にすると良い。さらに、前記(3)

(4) (5) において、Geの蒸着とSnの蒸着を同時に行うときの基板温度は30℃から300℃の範囲内にすると良い。

【0047】

なお、本発明においては、

・ 前記GeSn半導体のドット3を埋めるようにSi又はGeを蒸着してスペーサー層4を形成する工程(図7(a) (b) 参照)と、

・ 該スペーサー層4を熱酸化してスペーサー層側酸化膜12を形成する工程と(図7(c) 参照)、

・ Ge5及びSn6を該スペーサー層側酸化膜12に蒸着することに基づきGeSn半導体のドット13を該スペーサー層側酸化膜表面に作製する工程と(図7(c) 参照)、

を少なくとも1サイクル実施しても良い。この場合のスペーサー層4は、Si、Ge、或いはSiGe混晶にて形成すると良く、蒸着によって形成すると良い。スペーサー層を形成する工程、スペーサー層側酸化膜を形成する工程、及びドットを形成する工程のサイクルを複数回実施し、ドット23,…、スペーサー層14,…、スペーサー層側酸化膜22,…を順番に形成していって、多層構成にすると良い。その多層構成の半導体デバイスによりエレクトロルミネッセンス(EL)デバイスを作製しても良い。

【0048】

前記基板側酸化膜2又は前記スペーサー層側酸化膜12は、前記基板1又は前記スペーサー層4を酸素雰囲気中で熱酸化して形成すると良く、その膜厚は1nm以下(好ましくは0.3nm以上)にすると良い。このような極薄の基板側酸化膜2を用いた場合、蒸着時の基板温度を調整することにより、GeSn半導体ドットをエピタキシャル成長、非エピタキシャル成長させることを選択することができる。また、このような極薄の基板側酸化膜2を用いた場合、より高密度のGeSn半導体ドット3を得ることができる。

【0049】

なお、GeSn半導体におけるGe:Snの組成比は下式に示すようにしても良い。

【数5】

【0050】

また、Ge:Snの速度比は下式に示す通りにしても良い

【数6】

【0051】

本発明によれば、GeSn半導体のドット3の組成比を適正にすることにより、基板1との格子不整合による歪みを保持させ、直接遷移型半導体を得ることができる。

【0052】

ところで、GeSn半導体が薄膜やバルク結晶の場合にはエネルギーバンドギャップを調整することができず、既述したように、例え直接遷移型半導体を形成できたとしても光通信への利用が困難な場合もあり得る。これに対し、本発明にて製造されるGeSn半導体は微小なドット形状であるので量子サイズ効果(すなわち、ナノサイズのドットにおいてその大きさを制御することによりエネルギーバンドギャップを変化させることができるという効果)を利用することができ、エネルギーバンドギャップを0.6〜0.9eV程度(好ましくは、0.7〜0.9eV程度)にして、光通信に利用可能な半導体を得ることができる。つまり、本発明によれば、前記GeSn半導体の組成比、及び該半導体のドットサイズを調整することにより、該半導体のエネルギーバンドギャップを上記適正範囲にして、光通信に利用可能な半導体デバイスを製造することができる。

【0053】

一方、GeSn半導体を薄膜状に形成した場合には上述のように不整合転位が発生してしまうおそれがあった。これに対し、本発明にて製造されるGeSn半導体は上述のように微小なドットであって半球状をしているため、歪エネルギーを低下させることができ、その結果、格子定数の不整合から生じる不整合転位を低減させることができる。該GeSn半導体ドットは、Si基板上に直接形成しても、転位を生じずに成長させることが可能である。

【0054】

また、本発明により作製されるGeSn半導体が上述のように微小なドットであるため、1個当たりのドットに含まれる不純物や点欠陥の数を少なくできる。例えば、薄膜の場合には平均1018個/cm3の割合で不純物や点欠陥を含んでしまうような場合でも、10ナノメータースケールの微結晶の場合、1個のドット中には不純物や点欠陥は0−1個程度しか存在し得ない。

【実施例1】

【0055】

本実施例では、図7(d) に示す多層構造のGeSn半導体デバイスを作製した。

【0056】

まず、図1に示すように、10−4Pa程度の酸素圧力下でSi基板1を熱酸化し、極薄Si酸化膜(基板側酸化膜)2を得た。次に、図5(a) に示すように、蒸着装置7を用いて、超高真空下で、基板温度650℃でGe5を蒸着して核5Aを酸化膜上に形成し、その後、同図(b) に示すように、蒸着装置7及び8を用いて、超高真空下で、基板温度100℃程度で、Ge5とSn6を蒸着してGeSn半導体ドット3を形成した。この条件ではGeSn半導体ドットはエピタキシャル成長している。そして、形成したGeSn半導体ドット3を埋めるようにSiのスペーサー層(図7(b)

の符号4参照)を形成し、該スペーサー層4を熱酸化して酸化膜12を形成し、該酸化膜12の表面には上述と同様の方法でGeSn半導体ドット13を形成した(同図(c)

参照)。そして、スペーサー層4,14,…の形成、酸化膜12,22,…の形成、GeSn半導体ドット13,23,…の形成を順次繰り返して半導体デバイスを作製した(同図(d)

参照)。

【0057】

なお、本実施例では上述の方法で複数の半導体デバイスを作成したが、各デバイスの半導体ドットの径は、Ge及びSnの蒸着量を調整することにより、1nmから20nmの範囲で異ならせた。また、GeとSnの蒸着速度比を1−x:1(但し、0.05≦x≦0.22)の範囲で変化させて、各デバイスの半導体ドットの組成比を異ならせた。作製したいずれのデバイスにおいても、半導体ドットの面密度は1012cm−2程度となり高密度であった。図9にGeSn半導体ドットの走査トンネル顕微鏡(STM)像と反射高速電子線解析(RHEED)図形を示す。

【実施例2】

【0058】

本実施例では、図10に示す構造のELデバイス(半導体デバイス)を作製した。まず、P型のシリコン基板1上に基板側酸化膜2を形成し、GeSn半導体ドット3,13,…、スペーサー層4,14,…、スペーサー層側酸化膜12,22,…を多層に形成し、その後、N型となるようにドーパントを入れてSiを蒸着しN型Si薄膜40にてキャップをした。さらに、蒸着法を用いて、透明電極41、AuGa電極42、Al電極43を図示の位置にそれぞれ形成した。本実施例によれば、良質のELデバイスを得ることができた。

【産業上の利用可能性】

【0059】

GeとSnを蒸着してGeSn半導体ドットを形成することによって、光デバイス材料の用途に適用できる。

【図面の簡単な説明】

【0060】

【図1】図1は、単結晶Si、Ge、或いはSiGe基板に基板側酸化膜を形成する様子を示す模式図である。

【図2】図2は、Geを蒸着した後にSnを蒸着してGeSn半導体デバイスを作製する様子を示す模式図である。

【図3】図3は、Snを蒸着した後にGeを蒸着して半導体デバイスを作製する様子を示す模式図である。

【図4】図4は、Ge及びSnを同時に蒸着してGeSn半導体デバイスを作製する様子を示す模式図である。

【図5】図5は、Geを蒸着した後にGe及びSnの同時蒸着を行って半導体デバイスを作製する様子を示す模式図である。

【図6】図6は、Snを蒸着した後にGe及びSnを蒸着してGeSn半導体デバイスを作成する様子を示す模式図である。

【図7】図7は、多層の半導体デバイスを作製する様子を示す模式図である。

【図8】図8(a) はエピタキシャル成長時の様子を説明するための模式図であり、(b) は非エピタキシャル成長時の様子を説明するための模式図である。

【図9】図9は、GeSn半導体ナノドットの走査トンネル顕微鏡(STM)像と反射高速電子回折(RHEED)図形を示す写真である。

【図10】図10は、半導体デバイスの構造の一例を示す模式図である。

【符号の説明】

【0061】

1 基板

2 基板側酸化膜

3 GeSn半導体のドット

4 スペーサー層

5 Ge

5A Geの核

6 Sn

12 スペーサー層側酸化膜

13 GeSn半導体のドット

【技術分野】

【0001】

本発明は、GeSn半導体のドットを有するGeSn半導体デバイスの製造方法に関する。

【背景技術】

【0002】

Ge及びSnからなる半導体(以下、“GeSn半導体”とする)は、Si基板上のモノリシックな多機能デバイスの実現を可能とする材料であり、その組成比によっては直接遷移型半導体となり(例えば、非特許文献1参照)、IV族半導体光デバイスとして有望視されている。このGeSn半導体は、組成比に応じてエネルギーバンドギャップが変化するため、発光波長をある程度任意に制御できる可能性も有している。

【非特許文献1】G.He,and H.A.Atwater,Interbandtransitions in SnxGe1-x alloys,Phys.Rev.Lett.79(1997)1937

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、不純物の少ないGeSn半導体を得る方法は未だ確率されていない。

【0004】

また、Ge中のSnは偏析しやすく、高い基板温度での蒸着が困難であるため、結晶性の良いGeSn半導体を得ることは難しいという問題があった。

【0005】

さらに、GeSnとSiとの格子定数の差が大きく、Si基板上にGeSn半導体薄膜を形成すると、格子不整合から生ずる歪みを緩和するための不整合転位が該薄膜内に発生してしまうという問題もあった。

【0006】

なお、そのような不整合転位の発生を抑制する方法としては、GeSnと格子定数の差が比較的少ないGeを、Si基板上に薄膜形成し、そのGe薄膜上にGeSn半導体を形成する方法が考えられる。しかし、Si基板上のGe層は、Stranski−Krasnotav成長し、平坦な緩和Ge層を得ることが難しいという問題があった。

【0007】

また、仮に良質のGeSn混晶薄膜を形成できたとしても、Snの偏析が無い状態で、かつ、直接遷移型半導体が得られるという条件の組成比(具体的には、1:1−x。但し、0.1≦x≦0.2)では、バンドギャップは0.2〜0.5eV程度にしかならず、光ファイバの透過光の波長より小さくなってしまい、光通信への利用は困難であった。

【0008】

本発明は、上述のような問題の無いGeSn半導体デバイスの製造方法を提供することを目的とするものである。

【課題を解決するための手段】

【0009】

請求項1に係る発明は、図1乃至図6に例示するものであって、単結晶Si、Ge或いはSiGeからなる基板(1)に基板側酸化膜(2)を形成する工程と、

該基板側酸化膜(2)にGe(5)とSn(6)とを蒸着することに基づきGeSn半導体のドット(3)を作製する工程と、を有するGeSn半導体デバイスの製造方法に関するものである。

【0010】

請求項2に係る発明は、請求項1に係る発明において、前記基板(1)は、単結晶Si、Ge或いはSiGe基板、又は、エピタキシャル成長したSi層、Ge層、或いはSiGe混晶層を有する基板であることを特徴とする。

【0011】

請求項3に係る発明は、図7(a) 〜(d) に例示するものであって、請求項1又は2に記載の発明において、前記GeSn半導体のドット(3)を埋めるようにSi又はGeを蒸着してスペーサー層(4)を形成する工程と、

該スペーサー層(4)を熱酸化してスペーサー層側酸化膜(12)を形成する工程と、

GeとSnとを前記スペーサー層側酸化膜(12)に蒸着することに基づきGeSn半導体のドット(13)を該スペーサー層側酸化膜表面に作製する工程と、

を少なくとも1サイクル実施することを特徴とする。

【0012】

請求項4に係る発明は、請求項1乃至3のいずれか1項に記載の発明において、前記基板側酸化膜(2)又は前記スペーサー層側酸化膜(12)は、前記基板(1)又は前記スペーサー層(4)を酸素雰囲気中で熱酸化して1nm以下の厚さに形成したことを特徴とする。

【0013】

請求項5に係る発明は、図2に例示するものであって、請求項1乃至4のいずれか1項に記載の発明において、Ge(5)の蒸着を先に行い、その後、Sn(6)の蒸着を行うことにより前記GeSn半導体のドット(3)を形成することを特徴とする。

【0014】

請求項6に係る発明は、図3に例示するものであって、請求項1乃至4のいずれか1項に記載の発明において、Sn(6)の蒸着を先に行い、その後、Ge(5)の蒸着を行うことにより前記GeSn半導体のドット(3)を形成することを特徴とする。

【0015】

請求項7に係る発明は、図4に例示するものであって、請求項1乃至4のいずれか1項に記載の発明において、Ge(5)とSn(6)を同時に蒸着することにより行うことにより前記GeSn半導体のドット(3)を形成することを特徴とする。

【0016】

請求項8に係る発明は、図5に例示するものであって、請求項1乃至4のいずれか1項に記載の発明において、Ge(5)の蒸着を先に行ってGeの核(5A)を形成し、その後、Ge(5)とSn(6)を同時に蒸着することにより行うことにより前記GeSn半導体のドット(3)を形成することを特徴とする。

【0017】

請求項9に係る発明は、図6に例示するものであって、請求項1乃至4のいずれか1項に記載の発明において、Sn(6)の蒸着を先に行ってSnの核(6A)を形成し、その後、Ge(5)とSn(6)を同時に蒸着することにより行うことにより前記GeSn半導体のドット(3)を形成することを特徴とする。

【0018】

請求項10に係る発明は、請求項5,6,8,9のいずれか1項に記載の発明において、Ge(5)及びSn(6)を単独で蒸着するとき、基板温度は30℃から700℃の範囲であって、エピタキシャル成長をさせるか非エピタキシャル成長をさせるかに応じて調整することを特徴とする。

【0019】

請求項11に係る発明は、請求項5に係る発明において、Sn(6)の蒸着を行うときの基板温度は30℃から300℃の範囲であることを特徴とする。

【0020】

請求項12に係る発明は、請求項7乃至9に記載の発明において、Ge(5)及びSn(6)を同時に蒸着させるとき、基板温度は30℃から300℃の範囲とすることを特徴とする。

【0021】

請求項13に係る発明は、請求項10乃至12に記載の発明において、前記GeSn半導体は直接遷移型半導体であることを特徴とする。

【0022】

請求項14に係る発明は、請求項1乃至13のいずれか1項に記載の発明において、前記蒸着を、分子線エピタキシャル法、スパッタ法又は化学気相成長法により行うことを特徴とする。

【0023】

請求項15に係る発明は、請求項1乃至14のいずれか1項に記載の発明において、GeSn半導体におけるGe:Snの組成比は下式に示す通りであることを特徴とする。

【数3】

【0024】

請求項16に係る発明は、請求項12に係る発明において、Ge:Snの速度比は下式に示す通りであることを特徴とする。

【数4】

【0025】

請求項17に係る発明は、請求項1乃至16のいずれか1項に記載の発明において、前記GeSn半導体の組成比、及び該半導体のドットサイズを調整することにより、該半導体のエネルギーバンドギャップを適正範囲にして、光通信に利用可能な半導体デバイスを製造することを特徴とする。

【0026】

請求項18に係る発明は、請求項17に係る発明において、前記エネルギーバンドギャップの適正範囲は0.6eVから0.9eVの範囲であることを特徴とする。

【0027】

請求項19に係る発明は、請求項1乃至18のいずれか1項に記載の発明において、Ge及びSnの蒸着後、蒸着中或いは蒸着前に原子状の水素を前記基板に供給することを特徴とする。

【0028】

請求項20に係る発明は、請求項1乃至19のいずれか1項に記載の発明において、エレクトロルミネッセンスデバイスを製造することを特徴とする。

【0029】

なお、括弧内の番号などは、図面における対応する要素を示す便宜的なものであり、従って、本記述は図面上の記載に限定拘束されるものではない。

【発明の効果】

【0030】

請求項1乃至3、及び請求項20に係る発明によれば、GeSn半導体は微小なドットであるため歪エネルギーを低下させることができ、その結果、格子定数の不整合から生じる不整合転位を低減させることができる。また、1個当たりのドットに含まれる不純物や点欠陥の数を少なくできる(詳細は後述する)。さらに、GeSnの組成比を調整して直接遷移型半導体を得ることができ、ドットサイズを調整することにより、該半導体のエネルギーバンドギャップを適正範囲にして、光通信に利用可能な半導体デバイスを製造することができる。

【0031】

請求項4に係る発明によれば、極薄の酸化膜を用いることにより、高密度のGeSn半導体ドットを得ることができる。

【0032】

請求項5乃至16に係る発明によれば、微小で高密度な直接遷移型半導体を得るために有利でかつ結晶性の良いGeSn半導体ドットを得ることができる。

【0033】

請求項17及び18に係る発明によれば、光通信に利用できる半導体デバイスを製造することができる。

【0034】

請求項19に係る発明によれば、光デバイスとしてより良質なGeSn半導体を得ることができる。

【発明を実施するための最良の形態】

【0035】

以下、図1乃至図8に沿って、本発明を実施するための最良の形態について説明する。

【0036】

図1は、単結晶Si、Ge、或いはSiGe基板に基板側酸化膜を形成する様子を示す模式図であり、図2は、Geを蒸着した後にSnを蒸着してGeSn半導体デバイスを作製する様子を示す模式図である。また、図3は、Snを蒸着した後にGeを蒸着して半導体デバイスを作製する様子を示す模式図であり、図4は、Ge及びSnを同時に蒸着してGeSn半導体デバイスを作製する様子を示す模式図である。さらに、図5は、Geを蒸着した後にGe及びSnの同時蒸着を行って半導体デバイスを作製する様子を示す模式図であり、図6は、Snを蒸着した後にGe及びSnを蒸着してGeSn半導体デバイスを作成する様子を示す模式図である。また、図7は、多層の半導体デバイスを作製する様子を示す模式図であり、図8(a) はエピタキシャル成長時の様子を説明するための模式図であり、(b) は非エピタキシャル成長時の様子を説明するための模式図である。

【0037】

近年、シリコン系半導体においてナノメータースケールの微結晶(ナノドット)の開発が精力的に行われており、極薄Si酸化膜を利用して、SiとGeのナノドットを超高密度(>1012cm−2)に形成する技術が開発されている(A.A.Shklyaev、柴田 元司(M.Shibata)、市川 昌和(M.Ichikawa)、「High−density ultrasmall epitaxial Ge islands on Si(111)surfaces with a SiO2 coverage」、フィジカル・レビュー(Phys.Rev.)B62,(2000)1540.参照)。また、本発明者らは、超高密度シリサイドナノドットを形成する技術を提案している(特開2005−303249号公報参照)。

【0038】

本発明により製造されるGeSn半導体デバイスは、図2(b) 等に示すように、基板1と、該基板1に支持されたGeSn半導体のドット3と、を少なくとも備えている。

【0039】

ところで、本発明に用いる基板1としては、

・ 単結晶Si、Ge或いはSiGe基板や、

・ Si層、Ge層、或いはSiGe混晶層を単結晶Si基板上にエピタキシャル成長させたもの

を挙げることができる。

【0040】

なお、図2(b) 等に示すGeSn半導体デバイスの場合、符号2で示す酸化膜(後述するように、Ge5やSn6を蒸着する前に前記基板1の表面に形成されたもの。以下、"基板側酸化膜"とする)が基板1の全面にほぼ均一な膜厚で配置されていて、ドット3はこの基板側酸化膜2の表面に形成された状態となっているが、

・ 基板側酸化膜2が均一膜厚でなくても(例えば、図8(a) に符号10で示すように、基板側酸化膜2にボイドが形成されていても)、

・ 一旦形成された基板側酸化膜2が、GeやSnの蒸着等によって消失されてしまっていても(つまり、ドット3が、基板側酸化膜2の表面に形成されるのではなく、基板1の表面に形成された状態であっても)、

いずれでも良い。

【0041】

次に、本発明に係る半導体デバイスの製造方法について説明する。

【0042】

本発明に係る半導体デバイスの製造方法は、

・ 前記基板1に前記基板側酸化膜2を形成する工程と(図1(a) (b) 参照)、

・ 該基板側酸化膜2にGe5及びSn6を蒸着することに基づきGeSn半導体のドット3を形成する工程と(図2乃至図6参照)、

を備えている。

【0043】

Ge5及びSn6の蒸着順序は(1) 〜(5) のいずれかにすると良い。

(1) Ge5の蒸着を先に行ってドットを形成し(図2(a) の符号5A参照)、その後、Sn6の蒸着を行う場合(同図(b)

参照)

(2) Sn6の蒸着を先に行ってドットを形成し(図3(a) の符号6A参照)、その後、Ge5の蒸着を行う場合(同図(b)

参照)

(3) Ge5の蒸着とSn6の蒸着を同時に行う場合(図4参照)

(4) Ge5の蒸着を先に行ってGeの核を形成し(図5(a) の符号5A参照)、その後、Ge5の蒸着とSn6の蒸着を同時に行う場合(図5(b)

参照)

(5) Sn6の蒸着を先に行ってSnの核を形成し(図6(a) の符号6A参照)、その後、Ge5の蒸着とSn6の蒸着を同時に行う場合(図6(b)

参照)

【0044】

なお、GeやSnの蒸着は、分子線エピタキシャル法、スパッタ法又は化学気相成長法により行うと良い。すなわち、GeやSnの蒸着にはKnudsenセルを用い、Siの蒸着には電子線蒸着装置を用い、分子線エピタキシャル法により真空蒸着を行う方法、GeやSnをスパッタして蒸着するスパッタ法、或いは、GeやSnを含む反応ガス(GeH4、SnD4など)を供給して成長させる方法を使用すると良い。Ge、Snの蒸着量や供給量を調整してドットサイズを制御するようにすると良い(詳細は後述する)。また、Ge及びSnの蒸着後、蒸着中或いは蒸着前に原子状の水素を前記基板に供給すると良い。これにより、光デバイスとしてより良質なGeSn半導体を得ることができる。

【0045】

ところで、Ge5及びSn6を単独で蒸着するときの基板温度は30℃から700℃までの範囲にすると良い。また、その基板温度は、エピタキシャル成長させたいか、或いは非エピタキシャル成長させたいかによって調整すれば良い。なお、上記(1) (2) のようにGeの蒸着とSnの蒸着とを分けて別々に行う場合、それぞれの蒸着時の基板温度を異ならせることも可能となる。したがって、Geの蒸着時の基板温度とSnの蒸着時の基板温度とをそれぞれ最適に保持し、Ge中のSnの偏析を低減し、結晶性が良好で、光デバイスに最適な半導体ドットを形成することができる。さらに本発明によれば、安い材料にて安価に半導体デバイスを製造することが可能となり、またIV族半導体のみを使用しているため、既存のSiテクノロジーの利用とSi電子デバイスとの融合が可能となる。

【0046】

また、上記(1)

においてSnの蒸着を行うときの基板温度は30℃から300℃の範囲にすると良い。さらに、前記(3)

(4) (5) において、Geの蒸着とSnの蒸着を同時に行うときの基板温度は30℃から300℃の範囲内にすると良い。

【0047】

なお、本発明においては、

・ 前記GeSn半導体のドット3を埋めるようにSi又はGeを蒸着してスペーサー層4を形成する工程(図7(a) (b) 参照)と、

・ 該スペーサー層4を熱酸化してスペーサー層側酸化膜12を形成する工程と(図7(c) 参照)、

・ Ge5及びSn6を該スペーサー層側酸化膜12に蒸着することに基づきGeSn半導体のドット13を該スペーサー層側酸化膜表面に作製する工程と(図7(c) 参照)、

を少なくとも1サイクル実施しても良い。この場合のスペーサー層4は、Si、Ge、或いはSiGe混晶にて形成すると良く、蒸着によって形成すると良い。スペーサー層を形成する工程、スペーサー層側酸化膜を形成する工程、及びドットを形成する工程のサイクルを複数回実施し、ドット23,…、スペーサー層14,…、スペーサー層側酸化膜22,…を順番に形成していって、多層構成にすると良い。その多層構成の半導体デバイスによりエレクトロルミネッセンス(EL)デバイスを作製しても良い。

【0048】

前記基板側酸化膜2又は前記スペーサー層側酸化膜12は、前記基板1又は前記スペーサー層4を酸素雰囲気中で熱酸化して形成すると良く、その膜厚は1nm以下(好ましくは0.3nm以上)にすると良い。このような極薄の基板側酸化膜2を用いた場合、蒸着時の基板温度を調整することにより、GeSn半導体ドットをエピタキシャル成長、非エピタキシャル成長させることを選択することができる。また、このような極薄の基板側酸化膜2を用いた場合、より高密度のGeSn半導体ドット3を得ることができる。

【0049】

なお、GeSn半導体におけるGe:Snの組成比は下式に示すようにしても良い。

【数5】

【0050】

また、Ge:Snの速度比は下式に示す通りにしても良い

【数6】

【0051】

本発明によれば、GeSn半導体のドット3の組成比を適正にすることにより、基板1との格子不整合による歪みを保持させ、直接遷移型半導体を得ることができる。

【0052】

ところで、GeSn半導体が薄膜やバルク結晶の場合にはエネルギーバンドギャップを調整することができず、既述したように、例え直接遷移型半導体を形成できたとしても光通信への利用が困難な場合もあり得る。これに対し、本発明にて製造されるGeSn半導体は微小なドット形状であるので量子サイズ効果(すなわち、ナノサイズのドットにおいてその大きさを制御することによりエネルギーバンドギャップを変化させることができるという効果)を利用することができ、エネルギーバンドギャップを0.6〜0.9eV程度(好ましくは、0.7〜0.9eV程度)にして、光通信に利用可能な半導体を得ることができる。つまり、本発明によれば、前記GeSn半導体の組成比、及び該半導体のドットサイズを調整することにより、該半導体のエネルギーバンドギャップを上記適正範囲にして、光通信に利用可能な半導体デバイスを製造することができる。

【0053】

一方、GeSn半導体を薄膜状に形成した場合には上述のように不整合転位が発生してしまうおそれがあった。これに対し、本発明にて製造されるGeSn半導体は上述のように微小なドットであって半球状をしているため、歪エネルギーを低下させることができ、その結果、格子定数の不整合から生じる不整合転位を低減させることができる。該GeSn半導体ドットは、Si基板上に直接形成しても、転位を生じずに成長させることが可能である。

【0054】

また、本発明により作製されるGeSn半導体が上述のように微小なドットであるため、1個当たりのドットに含まれる不純物や点欠陥の数を少なくできる。例えば、薄膜の場合には平均1018個/cm3の割合で不純物や点欠陥を含んでしまうような場合でも、10ナノメータースケールの微結晶の場合、1個のドット中には不純物や点欠陥は0−1個程度しか存在し得ない。

【実施例1】

【0055】

本実施例では、図7(d) に示す多層構造のGeSn半導体デバイスを作製した。

【0056】

まず、図1に示すように、10−4Pa程度の酸素圧力下でSi基板1を熱酸化し、極薄Si酸化膜(基板側酸化膜)2を得た。次に、図5(a) に示すように、蒸着装置7を用いて、超高真空下で、基板温度650℃でGe5を蒸着して核5Aを酸化膜上に形成し、その後、同図(b) に示すように、蒸着装置7及び8を用いて、超高真空下で、基板温度100℃程度で、Ge5とSn6を蒸着してGeSn半導体ドット3を形成した。この条件ではGeSn半導体ドットはエピタキシャル成長している。そして、形成したGeSn半導体ドット3を埋めるようにSiのスペーサー層(図7(b)

の符号4参照)を形成し、該スペーサー層4を熱酸化して酸化膜12を形成し、該酸化膜12の表面には上述と同様の方法でGeSn半導体ドット13を形成した(同図(c)

参照)。そして、スペーサー層4,14,…の形成、酸化膜12,22,…の形成、GeSn半導体ドット13,23,…の形成を順次繰り返して半導体デバイスを作製した(同図(d)

参照)。

【0057】

なお、本実施例では上述の方法で複数の半導体デバイスを作成したが、各デバイスの半導体ドットの径は、Ge及びSnの蒸着量を調整することにより、1nmから20nmの範囲で異ならせた。また、GeとSnの蒸着速度比を1−x:1(但し、0.05≦x≦0.22)の範囲で変化させて、各デバイスの半導体ドットの組成比を異ならせた。作製したいずれのデバイスにおいても、半導体ドットの面密度は1012cm−2程度となり高密度であった。図9にGeSn半導体ドットの走査トンネル顕微鏡(STM)像と反射高速電子線解析(RHEED)図形を示す。

【実施例2】

【0058】

本実施例では、図10に示す構造のELデバイス(半導体デバイス)を作製した。まず、P型のシリコン基板1上に基板側酸化膜2を形成し、GeSn半導体ドット3,13,…、スペーサー層4,14,…、スペーサー層側酸化膜12,22,…を多層に形成し、その後、N型となるようにドーパントを入れてSiを蒸着しN型Si薄膜40にてキャップをした。さらに、蒸着法を用いて、透明電極41、AuGa電極42、Al電極43を図示の位置にそれぞれ形成した。本実施例によれば、良質のELデバイスを得ることができた。

【産業上の利用可能性】

【0059】

GeとSnを蒸着してGeSn半導体ドットを形成することによって、光デバイス材料の用途に適用できる。

【図面の簡単な説明】

【0060】

【図1】図1は、単結晶Si、Ge、或いはSiGe基板に基板側酸化膜を形成する様子を示す模式図である。

【図2】図2は、Geを蒸着した後にSnを蒸着してGeSn半導体デバイスを作製する様子を示す模式図である。

【図3】図3は、Snを蒸着した後にGeを蒸着して半導体デバイスを作製する様子を示す模式図である。

【図4】図4は、Ge及びSnを同時に蒸着してGeSn半導体デバイスを作製する様子を示す模式図である。

【図5】図5は、Geを蒸着した後にGe及びSnの同時蒸着を行って半導体デバイスを作製する様子を示す模式図である。

【図6】図6は、Snを蒸着した後にGe及びSnを蒸着してGeSn半導体デバイスを作成する様子を示す模式図である。

【図7】図7は、多層の半導体デバイスを作製する様子を示す模式図である。

【図8】図8(a) はエピタキシャル成長時の様子を説明するための模式図であり、(b) は非エピタキシャル成長時の様子を説明するための模式図である。

【図9】図9は、GeSn半導体ナノドットの走査トンネル顕微鏡(STM)像と反射高速電子回折(RHEED)図形を示す写真である。

【図10】図10は、半導体デバイスの構造の一例を示す模式図である。

【符号の説明】

【0061】

1 基板

2 基板側酸化膜

3 GeSn半導体のドット

4 スペーサー層

5 Ge

5A Geの核

6 Sn

12 スペーサー層側酸化膜

13 GeSn半導体のドット

【特許請求の範囲】

【請求項1】

単結晶Si、Ge或いはSiGeからなる基板に基板側酸化膜を形成する工程と、

該基板側酸化膜にGeとSnとを蒸着することに基づきGeSn半導体のドットを作製する工程と、

を有するGeSn半導体デバイスの製造方法。

【請求項2】

前記基板は、単結晶Si、Ge或いはSiGe基板、又は、エピタキシャル成長したSi層、Ge層、或いはSiGe混晶層を有する基板である、

ことを特徴とする請求項1に記載のGeSn半導体デバイスの製造方法。

【請求項3】

前記GeSn半導体のドットを埋めるようにSi又はGeを蒸着してスペーサー層を形成する工程と、

該スペーサー層を熱酸化してスペーサー層側酸化膜を形成する工程と、

GeとSnとを前記スペーサー層側酸化膜に蒸着することに基づきGeSn半導体のドットを該スペーサー層側酸化膜表面に作製する工程と、

を少なくとも1サイクル実施する、請求項1又は2に記載のGeSn半導体デバイスの製造方法。

【請求項4】

前記基板側酸化膜又は前記スペーサー層側酸化膜は、前記基板又は前記スペーサー層を酸素雰囲気中で熱酸化して1nm以下の厚さに形成した、

ことを特徴とする請求項1乃至3のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項5】

Geの蒸着を先に行い、その後、Snの蒸着を行うことにより前記GeSn半導体のドットを形成する、

ことを特徴とする請求項1乃至4のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項6】

Snの蒸着を先に行い、その後、Geの蒸着を行うことにより前記GeSn半導体のドットを形成する、

ことを特徴とする請求項1乃至4のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項7】

GeとSnを同時に蒸着することにより行うことにより前記GeSn半導体のドットを形成する、

ことを特徴とする請求項1乃至4のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項8】

Geの蒸着を先に行ってGeの核を形成し、その後、GeとSnを同時に蒸着することにより行うことにより前記GeSn半導体のドットを形成する、

ことを特徴とする請求項1乃至4のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項9】

Snの蒸着を先に行ってSnの核を形成し、その後、GeとSnを同時に蒸着することにより行うことにより前記GeSn半導体のドットを形成する、

ことを特徴とする請求項1乃至4のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項10】

Ge及びSnを単独で蒸着するとき、基板温度は30℃から700℃の範囲であって、エピタキシャル成長をさせるか非エピタキシャル成長をさせるかに応じて調整する、

ことを特徴とする請求項5,6,8,9のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項11】

Snの蒸着を行うときの基板温度は30℃から300℃の範囲である、

ことを特徴とする請求項5に記載のGeSn半導体デバイスの製造方法。

【請求項12】

Ge及びSnを同時に蒸着させるとき、基板温度は30℃から300℃の範囲とする、

ことを特徴とする請求項7乃至9に記載のGeSn半導体デバイスの製造方法。

【請求項13】

前記GeSn半導体は直接遷移型半導体である、

ことを特徴とする請求項10乃至12に記載のGeSn半導体デバイスの製造方法。

【請求項14】

前記蒸着は、分子線エピタキシャル法、スパッタ法又は化学気相成長法により行う、

ことを特徴とする請求項1乃至13のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項15】

GeSn半導体におけるGe:Snの組成比は下式に示す通りである、

ことを特徴とする請求項1乃至14のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【数1】

【請求項16】

Ge:Snの速度比は下式に示す通りである、

ことを特徴とする請求項12に記載のGeSn半導体デバイスの製造方法。

【数2】

【請求項17】

前記GeSn半導体の組成比、及び該半導体のドットサイズを調整することにより、該半導体のエネルギーバンドギャップを適正範囲にして、光通信に利用可能な半導体デバイスを製造する、

ことを特徴とする請求項1乃至16のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項18】

前記エネルギーバンドギャップの適正範囲は0.6eVから0.9eVの範囲である、

ことを特徴とする請求項17に記載のGeSn半導体デバイスの製造方法。

【請求項19】

Ge及びSnの蒸着後、蒸着中或いは蒸着前に原子状の水素を前記基板に供給する、

ことを特徴とする請求項1乃至18のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項20】

エレクトロルミネッセンスデバイスを製造する、

ことを特徴とする請求項1乃至19のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項1】

単結晶Si、Ge或いはSiGeからなる基板に基板側酸化膜を形成する工程と、

該基板側酸化膜にGeとSnとを蒸着することに基づきGeSn半導体のドットを作製する工程と、

を有するGeSn半導体デバイスの製造方法。

【請求項2】

前記基板は、単結晶Si、Ge或いはSiGe基板、又は、エピタキシャル成長したSi層、Ge層、或いはSiGe混晶層を有する基板である、

ことを特徴とする請求項1に記載のGeSn半導体デバイスの製造方法。

【請求項3】

前記GeSn半導体のドットを埋めるようにSi又はGeを蒸着してスペーサー層を形成する工程と、

該スペーサー層を熱酸化してスペーサー層側酸化膜を形成する工程と、

GeとSnとを前記スペーサー層側酸化膜に蒸着することに基づきGeSn半導体のドットを該スペーサー層側酸化膜表面に作製する工程と、

を少なくとも1サイクル実施する、請求項1又は2に記載のGeSn半導体デバイスの製造方法。

【請求項4】

前記基板側酸化膜又は前記スペーサー層側酸化膜は、前記基板又は前記スペーサー層を酸素雰囲気中で熱酸化して1nm以下の厚さに形成した、

ことを特徴とする請求項1乃至3のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項5】

Geの蒸着を先に行い、その後、Snの蒸着を行うことにより前記GeSn半導体のドットを形成する、

ことを特徴とする請求項1乃至4のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項6】

Snの蒸着を先に行い、その後、Geの蒸着を行うことにより前記GeSn半導体のドットを形成する、

ことを特徴とする請求項1乃至4のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項7】

GeとSnを同時に蒸着することにより行うことにより前記GeSn半導体のドットを形成する、

ことを特徴とする請求項1乃至4のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項8】

Geの蒸着を先に行ってGeの核を形成し、その後、GeとSnを同時に蒸着することにより行うことにより前記GeSn半導体のドットを形成する、

ことを特徴とする請求項1乃至4のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項9】

Snの蒸着を先に行ってSnの核を形成し、その後、GeとSnを同時に蒸着することにより行うことにより前記GeSn半導体のドットを形成する、

ことを特徴とする請求項1乃至4のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項10】

Ge及びSnを単独で蒸着するとき、基板温度は30℃から700℃の範囲であって、エピタキシャル成長をさせるか非エピタキシャル成長をさせるかに応じて調整する、

ことを特徴とする請求項5,6,8,9のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項11】

Snの蒸着を行うときの基板温度は30℃から300℃の範囲である、

ことを特徴とする請求項5に記載のGeSn半導体デバイスの製造方法。

【請求項12】

Ge及びSnを同時に蒸着させるとき、基板温度は30℃から300℃の範囲とする、

ことを特徴とする請求項7乃至9に記載のGeSn半導体デバイスの製造方法。

【請求項13】

前記GeSn半導体は直接遷移型半導体である、

ことを特徴とする請求項10乃至12に記載のGeSn半導体デバイスの製造方法。

【請求項14】

前記蒸着は、分子線エピタキシャル法、スパッタ法又は化学気相成長法により行う、

ことを特徴とする請求項1乃至13のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項15】

GeSn半導体におけるGe:Snの組成比は下式に示す通りである、

ことを特徴とする請求項1乃至14のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【数1】

【請求項16】

Ge:Snの速度比は下式に示す通りである、

ことを特徴とする請求項12に記載のGeSn半導体デバイスの製造方法。

【数2】

【請求項17】

前記GeSn半導体の組成比、及び該半導体のドットサイズを調整することにより、該半導体のエネルギーバンドギャップを適正範囲にして、光通信に利用可能な半導体デバイスを製造する、

ことを特徴とする請求項1乃至16のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項18】

前記エネルギーバンドギャップの適正範囲は0.6eVから0.9eVの範囲である、

ことを特徴とする請求項17に記載のGeSn半導体デバイスの製造方法。

【請求項19】

Ge及びSnの蒸着後、蒸着中或いは蒸着前に原子状の水素を前記基板に供給する、

ことを特徴とする請求項1乃至18のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【請求項20】

エレクトロルミネッセンスデバイスを製造する、

ことを特徴とする請求項1乃至19のいずれか1項に記載のGeSn半導体デバイスの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図10】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図10】

【図9】

【公開番号】特開2007−294778(P2007−294778A)

【公開日】平成19年11月8日(2007.11.8)

【国際特許分類】

【出願番号】特願2006−122795(P2006−122795)

【出願日】平成18年4月27日(2006.4.27)

【出願人】(503360115)独立行政法人科学技術振興機構 (1,734)

【Fターム(参考)】

【公開日】平成19年11月8日(2007.11.8)

【国際特許分類】

【出願日】平成18年4月27日(2006.4.27)

【出願人】(503360115)独立行政法人科学技術振興機構 (1,734)

【Fターム(参考)】

[ Back to top ]