HDL環境のためのグローバルクロックハンドラーオブジェクト

【課題】HDL環境において模擬クロック信号を発生しコントロールすること。

【解決手段】ハードウェア記述言語(HDL)環境に使用するためのグローバルなクロックハンドラーオブジェクトが開示される。HDLモジュールは、1つ以上のクロックステートメントを含む。コンピュータシステムがクロックステートメントを実行するとき、クロックハンドラーオブジェクトがコールされる。クロックハンドラーオブジェクトは、集積回路設計の1つ以上の模擬ファンクションブロックに対する模擬クロック信号を発生する。各模擬クロックは、個別の且つ独特のスレッドに指定される。クロックハンドラーオブジェクトは、集積回路設計に対する各模擬クロック信号を管理するように構成されたシングルトンオブジェクトである。各模擬クロック信号の発生及びコントロールは、ダイナミックアレイにおけるクロックハンドラーオブジェクトにより遂行される。ダイナミックアレイは、模擬クロック信号ごとにパラメータを指定するエレメントを含む。

【解決手段】ハードウェア記述言語(HDL)環境に使用するためのグローバルなクロックハンドラーオブジェクトが開示される。HDLモジュールは、1つ以上のクロックステートメントを含む。コンピュータシステムがクロックステートメントを実行するとき、クロックハンドラーオブジェクトがコールされる。クロックハンドラーオブジェクトは、集積回路設計の1つ以上の模擬ファンクションブロックに対する模擬クロック信号を発生する。各模擬クロックは、個別の且つ独特のスレッドに指定される。クロックハンドラーオブジェクトは、集積回路設計に対する各模擬クロック信号を管理するように構成されたシングルトンオブジェクトである。各模擬クロック信号の発生及びコントロールは、ダイナミックアレイにおけるクロックハンドラーオブジェクトにより遂行される。ダイナミックアレイは、模擬クロック信号ごとにパラメータを指定するエレメントを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ハードウェア記述言語(HDL)に関し、より特定すれば、HDL環境における模擬クロック信号の発生及びコントロールに関する。

【背景技術】

【0002】

一部分は近代的な製造技術で達成できる高度な集積のために、集積回路設計は、非常に複雑になりつつある。高度な集積をもつ複雑な集積回路は、回路レベルや論理ゲートレベルで設計することが不可能である。従って、複雑な集積回路設計を管理するため、種々のハードウェア記述言語(HDL)が開発されている。HDLは、集積回路の高レベル記述を許す。この記述は、集積回路設計を模擬するためにコンピュータシステムで実行できるソフトウェアコードの形態である。更に、HDLは、ハードウェアの特定の断片を記述する他のモジュールをテストするのに使用されるテストベンチとして知られたモジュールを書くのに使用することができる。

【0003】

典型的な集積回路設計は、多数の異なるファンクションユニットを含む。例えば、システムオンチップ(SOC)設計は、複数のプロセッサコア、少なくとも1つのメモリ、グラフィック処理ユニット、スイッチングユニット、及び1つ以上のインターフェイス回路を含む。これらの異なるファンクションユニットの各々は、個別のHDLモジュールにより記述される。より詳細には、各HDLモジュールは、実際にはファンクションユニットの略記記述であるHDLコードの多数のステートメントにより記述される。これらステートメントは、内部オペレーションを記述する付加的なステートメントと共にファンクションブロックの入力及び出力を指定する。これらファンクションユニットの多くは、クロック信号を必要とする。従って、各々の対応するHDLモジュールは、クロック信号を指定する多数のステートメントを、周波数、開始時間、停止時間及び種々の統計学的監視状態のようなパラメータと共に含む。

【発明の概要】

【0004】

ハードウェア記述言語(HDL)環境に使用するためのグローバルなクロックハンドラーオブジェクトが開示される。一実施形態において、HDLモジュールは、1つ以上のクロックステートメントを含む。コンピュータシステムがクロックステートメントを実行するときに、クロックハンドラーオブジェクトがコールされる。クロックハンドラーオブジェクトは、集積回路設計の1つ以上の模擬ファンクションブロックに対する模擬クロック信号を発生する。各模擬クロックは、個別の且つ独特のスレッドに指定される。クロックハンドラーオブジェクトは、集積回路設計に対する各模擬クロック信号を管理するように構成されたシングルトンオブジェクトである。

【0005】

一実施形態において、テストベンチとして知られたHDLモジュールは、多数の異なるクロックステートメントを含む。テストベンチは、集積回路設計を実施する別のHDLモジュール(供試装置又は“DUT”)のテストを遂行するように構成される。クロックステートメントの実行に応答して、テストベンチは、クロックハンドラーオブジェクトを呼び出してそれに対応するクロック信号の模擬を発生し、そしてそれらをDUTの各ポートに指定する。各クロックハンドラーステートメントは、それに対応する模擬クロック信号のあるパラメータを指定する。そのようなパラメータは、周波数、開始時間、停止時間、別のクロック信号に対するオフセットを含む(が、それに限定されない)。クロックハンドラーオブジェクトは、種々の模擬クロック信号及びそれに対応するパラメータを追跡するためのダイナミックアレイを維持する。又、クロックハンドラーオブジェクトは、テストベンチのオペレーションに対する全ての模擬クロック信号を、テストベンチに基づくDUTの模擬中に発生しそしてコントロールすることができる。クロックハンドラーオブジェクトは、シングルトンオブジェクトであり、即ち集積回路設計の模擬中に一度インスタンス生成される。

【0006】

以下、添付図面を参照して、本発明を詳細に説明する。

【図面の簡単な説明】

【0007】

【図1】集積回路設計及びその設計に対応するハードウェア記述言語(HDL)モジュールの一実施形態の対応グループを示すブロック図である。

【図2】クロックハンドラーオブジェクトを含むHDLモジュール、及び集積回路設計をテストするためのテストベンチモジュールのグループの一実施形態の編成を示すブロック図である。

【図3】クロックハンドラーオブジェクトの一実施形態により維持されるダイナミックアレイを示す図である。

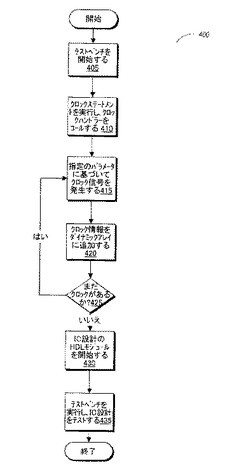

【図4】テストベンチを使用して集積回路設計のテストを開始するための方法の一実施形態を示すフローチャートである。

【図5】コンピュータ読み取り可能な媒体の一実施形態のブロック図である。

【発明を実施するための形態】

【0008】

本発明は、種々の変更を受けそして別の形態でも実施できるが、その特定の実施形態を一例として添付図面に示して以下に詳細に説明する。しかしながら、添付図面及び詳細な説明は、本発明を、ここに開示する特定の形態に限定するものではなく、本発明は、特許請求の範囲に規定される本発明の精神及び範囲内に入る全ての変更、等効物及び代替え物を網羅することを理解されたい。ここに使用する見出しは、編成上の目的に過ぎず、説明の範囲を限定するためのものではない。又、本出願全体にわたって使用される「〜してもよい(may)」という語は、許すという意味(即ち、〜の潜在性があるという意味)で使用されるもので、強制の意味(即ち、〜しなければならないという意味)ではない。同様に、「含む(include)」、「含んでいる(including)」及び「含む(includes)」という語は、含むことを意味するが、それに限定されない。

【0009】

種々のユニット、回路又は他のコンポーネントは、1つ又は複数のタスクを遂行するように「構成される」ものとして述べる。この点について、「構成される」とは、動作中に1つ又は複数のタスクを遂行する「回路を有する」ことを一般的に意味する構造を広く表現するものである。従って、ユニット/回路/コンポーネントは、そのユニット/回路/コンポーネントが現在オンでなくても、タスクを遂行するように構成することができる。一般的に、「構成される」に対応する構造を形成する回路は、ハードウェア回路、及び/又は動作を実施するよう実行できるプログラムインストラクションを記憶するメモリを含む。メモリは、スタティック又はダイナミックランダムアクセスメモリのような揮発性メモリ、及び/又は光学又は磁気ディスク記憶装置、フラッシュメモリ、プログラム可能なリードオンリメモリ、等の不揮発性メモリを含む。同様に、種々のユニット/回路/コンポーネントは、説明の便宜上、1つ又は複数のタスクを遂行するものとして説明されてもよい。そのような説明は、「構成される」という句を含むものと解釈されねばならない。1つ以上のタスクを遂行するように構成されたユニット/回路/コンポーネントを表現する場合に、そのユニット/回路/コンポーネントに関して35U.S.C.§112、第6節の解釈を引用しないことが明確に意図される。

【0010】

図1は、集積回路設計及びその設計に対応するハードウェア記述言語(HDL)モジュールの対応グループの一実施形態を示すブロック図である。図示された実施形態における集積回路(IC)10は、複数のファンクションブロックを含む予備的なIC設計のブロック図である。ここに例示するIC10は、一例に過ぎず、これに限定されるものではないことに注意されたい。

【0011】

ここに提案する設計では、IC10は、2つのコア、即ちコア12及びコア14を有するマルチコアプロセッサである。一実施形態において、コア12及び14は、互いに同一である。別の実施形態では、これらのコアが異なるものであり、例えば、一方のコアは、一般的な処理のために具現化され、他方のコアは、グラフィック処理専用とされる。IC10は、更に、両コアに結合されたメモリコントローラ15を備えている。最終的な具現化において、メモリコントローラ15は、システムメモリへのインターフェイスをなすように構成される。又、IC10は、両コア及びメモリコントローラ16に結合されたバスインターフェイス16も備えている。最終的な具現化におけるバスインターフェイス16は、IC10と1つ以上の周辺バスとの間のインターフェイスをなすように構成される。特に、バスインターフェイス16は、周辺バスに取り付けられた装置と、IC10の他のファンクションブロックとの間のトラフィック流を整合する。

【0012】

図1に示した例では、IC10の設計は、ハードウェア記述言語(HDL)モジュール20によって表され、このモジュールは、次いで、付加的なHDLモジュールより成る。この例におけるHDLモジュール22は、コア12のHDL記述である。同様に、HDLモジュール24、25及び26は、各々、コア14、メモリコントローラ15、及びバスインターフェイス16のHDL記述を与える。HDLにおいて(即ち、コンパイルの前に)、各モジュールは、多数のステートメントを含む。HDLステートメントは、各モジュールへの入力、各モジュールからの出力、各モジュールにより遂行されるオペレーション、等を指定する。更に、図1に示すHDLモジュールの各々は、それ自体、付加的なHDLモジュールを含むことに注意されたい。例えば、図1に示した所与のHDLモジュールは、加算器、除算器、マルチプレクサ、メモリ、種々の形式の状態マシン、等の付加的なモジュールを含む。HDLモジュール20内のあるHDLモジュールは、事前に設計されたライブラリから得られ、他のHDLモジュールは、IC10の設計プロセス中に書かれる。

【0013】

図2は、クロックハンドラーオブジェクトを含むHDLモジュール、及び集積回路設計をテストするためのテストベンチモジュールのグループの一実施形態の編成を示すブロック図である。この所与の例におけるテストベンチ32は、図1を参照して上述したHDLモジュール20及びその種々のモジュールに記述されたIC設計のテストを遂行するように構成されたHDLモジュールである。従って、ここに示す実施形態におけるテストベンチ32は、HDLモジュール20及びその種々のサブモジュールを包囲する。更に、テストベンチモジュール32は、実行されたときに、HDLモジュール20及びそのサブモジュールにテスト刺激を与える多数のHDLステートメントも含む。これらのステートメントは、あるケースでは、テスト刺激を与えることにより生じる結果をチェックするが、テストベンチ32には、より複雑で及び/又は完了により多くの時間を要するテストのために個別の検証ステートメントも含まれる。

【0014】

ここに示す実施形態におけるテストベンチ32は、多数の規範的なクロックステートメントを含む。これらクロックステートメントは、実行時に、クロックハンドラーオブジェクト35をコールする。各クロックステートメントの実行に応答して、クロックハンドラーオブジェクト35は、HDLモジュール20のクロックポート(例えば、Clk_1、Clk_2)の1つに与えられる対応する模擬クロック信号を発生する。又、クロックハンドラーオブジェクト35は、クロックポートを通るのではなく、HDLモジュール20の部分に内部で与えられる模擬クロック信号も発生する。いずれの場合にも、クロックハンドラーオブジェクト35は、動作中に1つ以上のクロック信号を使用するファンクションブロックに対応するHDLモジュールの各々に模擬クロック信号を与える。一般的に、クロックハンドラーオブジェクト35は、HDLモジュール20及びその各々のサブモジュールの任意の部分に対して模擬クロック信号を発生する。

【0015】

ここに示す実施形態におけるクロックハンドラーオブジェクト35は、シングルトンオブジェクトである。即ち、HDLモジュール20を経てテストベンチ32の実行中及び/又はIC設計の模擬中にアクティブであるのは、クロックハンドラーオブジェクト35の1つのインスタンスだけである。更に、ここに示す実施形態におけるクロックハンドラーオブジェクト35は、所与の模擬に対する全ての模擬クロック信号を発生及びコントロールするように構成され、従って、グローバルなクロックハンドラーとして働く。それとは対照的に、従来の実施形態は、クロックハンドラーオブジェクト35によって与えられる集中クロック信号を含まず、むしろ、HDLコードの個別区分において模擬クロック信号及び全ての各パラメータを発生する。

【0016】

図2の例に示された各クロックステートメントは、クロックハンドラーオブジェクト(‘clk_hdlr’)、クロックハンドラーにより遂行されるファンクション(例えば、‘get_clk’)、クロック名(例えば、‘CLK_1’)、模擬クロックが指定されるクロックポート(例えば、‘Clk_1’)、及び1つ以上の引数を指定する。引数は、クロック信号周波数のようなクロック信号パラメータを指定するのに使用される。更に、クロックハンドラーオブジェクト35のアプリケーションプログラミングインターフェイス(API)は、模擬クロック信号に対する付加的なパラメータをセットするのに使用される。従って、クロックハンドラーオブジェクト35をコールするHDLモジュールは、模擬クロック信号を生成するクロックステートメントであって、他の考えられるパラメータの中で、開始時間、停止時間、実行するサイクル数、デューティサイクル、及びオフセット(別のクロック信号に対する)を指定するクロックステートメントも含む。これらファンクションをコールするクロックステートメントは、テストベンチモジュール32を含めて、HDLモジュール内のどこに配置されてもよい。

【0017】

クロックハンドラーオブジェクト32のここに示す実施形態におけるクロックステートメント及びAPIのフォーマットは、単なる例示に過ぎないことに注意されたい。他のフォーマットも考えられ、意図される。

【0018】

ここに示す実施形態におけるクロックハンドラーオブジェクト32は、スレッドごとに模擬クロック信号を発生及びコントロールするように構成される。即ち、ここに示す実施形態におけるクロックハンドラーオブジェクト35は、模擬クロック信号ごとに個別の実行スレッドを発生するように構成される。ここに示す例では、スレッド1は、CLK_1専用であり、スレッド2は、CLK_2専用であり、スレッド3は、CLK_3専用である。模擬クロック信号ごとに個別のスレッドを与えることは、同時にアクティブとなる複数の模擬クロック信号の管理及びコントロールを簡単にする。例えば、所与の模擬クロック信号のパラメータが変化すると、そのクロック信号専用のスレッドに影響するが、他の模擬クロック信号の対応スレッドには影響しない。

【0019】

クロックハンドラーオブジェクト35は、複数の模擬クロック信号を管理するためにダイナミックアレイを発生し維持する。このアレイは、そのサイズを必要に応じて増加又は減少できるという点でダイナミックである。図3は、クロックハンドラーオブジェクトの一実施形態により維持されるダイナミックアレイを示す図である。ここに示す実施形態では、アレイ300は、行及び列に配列された多数のエレメントを含む。アレイ300の各エレメントは、クロックハンドラーオブジェクト35により発生される模擬クロック信号の1つに対応する。アレイ300にエレメントとして記憶される種々のパラメータは、上述したもの、例えば、クロック名、周期/周波数、開始時間、停止時間、等を含む。図3に明確に述べられず又は示されない付加的なパラメータも、ある実施形態には存在する。

【0020】

上述したように、アレイ300は、ダイナミックアレイである。従って、例えば、クロックステートメントが模擬クロック信号を要求するためにクロックハンドラーオブジェクト35をコールするときに、エレメントの新たなセットがアレイ300に追加される。エレメントの新たなセットは、新たに要求された模擬クロック信号に対応する。更に、クロックハンドラーオブジェクト35は、それらエレメントがもはや必要ない場合にアレイ300から除去する。例えば、模擬クロック信号が、模擬/テストの初期部分に対してのみ動作すべき場合には、クロックハンドラーオブジェクト35は、模擬クロック信号がインアクティブになったときにアレイ300から各エレメントを除去する。又、クロックハンドラーオブジェクト35は、模擬/テスト中にアレイ300のあるエレメントの値を変更することもある。例えば、クロックステートメントが所与の模擬クロック信号に対するオフセット値の変更を指定する場合には、クロックハンドラーオブジェクト35は、必要な変更を行いながらアレイ300における対応エレメントを更新する。

【0021】

図4は、テストベンチを使用してIC設計のテストを開始するための方法の一実施形態を示すフローチャートである。ここに示す実施形態では、方法400は、テストベンチモジュールを開始する1つ以上のインストラクションの実行で開始される(ブロック405)。一実施形態において、テストベンチモジュールを開始する1つ以上のインストラクション、及び方法400で実行される他のインストラクションは、HDLステートメントからコンパイルされたマシン言語インストラクションである。インタープリターを使用してHDLステートメントを実行する実施形態も考えられ、意図される。

【0022】

テストベンチモジュールを開始した後、1つ以上のクロックステートメントに対応するインストラクションが実行され、それに応答してクロックハンドラーオブジェクトがコールされる(ブロック410)。クロックハンドラーオブジェクトは、次いで、指定のパラメータに基づいて対応する模擬クロック信号を発生する(ブロック415)。クロックハンドラーオブジェクトは、新たに発生されたクロック信号模擬の種々のパラメータに対応するエレメントをダイナミックアレイに追加する(ブロック420)。第1のクロックステートメントの実行は、ダイナミックアレイを発生する。新たな模擬クロック信号を要求する付加的なクロックステートメントの実行(ブロック425、イエス)は、対応するエレメントをダイナミックアレイに追加させる。以前に発生された模擬クロック信号に対するあるパラメータを指定する付加的なクロックステートメントは、ダイナミックアレイを更新させる。

【0023】

IC設計の模擬及びそのテストを開始する前に付加的な模擬クロック信号が発生されない場合には(ブロック425、ノー)、IC設計に対応するHDLモジュールが開始される(ブロック430)。しかしながら、IC設計を記述するHDLモジュール及びそのファンクションブロックが模擬クロック信号の発生及び実行の前に開始される実施形態も考えられ、意図されることに注意されたい。

【0024】

テストベンチ、望ましいクロック信号の模擬、及びIC設計に対応するHDLモジュールの全部が開始されると、テストベンチの実行及びIC設計のテストを開始することができる(ブロック435)。テストベンチの実行中に、テストベクトルがIC設計の種々の入力に与えられ、そしてテスト結果が種々の出力を通して捕獲される。テスト結果の捕獲を分析して、IC設計が仕様内で正しく機能するかどうか決定することができる。

【0025】

方法400は、テストを開始する前にクロックステートメントの実行を経て1つ以上の模擬クロック信号を発生することを含むが、この方法の間にいつでも付加的なクロックステートメントを実行できることに注意されたい。例えば、テストの開始に続き、模擬クロック信号同士のオフセットを変更するクロックステートメントを実行してもよい。更に、テスト中に、模擬クロック信号を開始し及び/又は停止するステートメントも実行される。あるケースでは、テストシーケンスの残り部分に対して模擬クロック信号がインアクチベートされた場合には、クロックハンドラーオブジェクトは、それに対応するエレメントをダイナミックアレイから排除して、そのサイズ、ひいては、そのメモリフットプリントを減少する。一般的に、クロックステートメントは、テストベンチの動作及び/又はIC設計の模擬中にいつでも実行することができる。更に、本開示では、テストベンチ内から実行されるクロックステートメントの例が使用されるが、クロックハンドラーオブジェクトをコールするクロックステートメントが、IC設計のファンクションユニットを記述するものを含めて、HDLモジュールから実行されてもよいことに注意されたい。

【0026】

図5は、コンピュータ読み取り可能な媒体の一実施形態のブロック図である。ここに示す実施形態では、コンピュータ読み取り可能な媒体50は、非一時的なコンピュータ読み取り可能な媒体である。非一時的なコンピュータ読み取り可能な媒体とは、例えば、フラッシュメモリ(例えば、フラッシュドライブの)、ハードディスク記憶装置、CD−ROM、DVD−ROM、等を含む。一般的に、コンピュータ読み取り可能な媒体50は、適切に装備されたコンピュータシステムが記憶情報にアクセスするところの任意の形式の非一時的なコンピュータ読み取り可能な媒体である。

【0027】

この特定例において、コンピュータ読み取り可能な媒体50は、クロックハンドラーオブジェクト35、テストベンチモジュール32、HDLモジュール20、及びその種々のサブモジュール(HDLモジュール22、24、25及び26)の各々を作り上げる種々のデータ構造体を記憶する。ここで使用する「データ構造体」という語は、コンピュータ読み取り可能な媒体50に記憶されたクロックハンドラーオブジェクト35、テストベンチ32、及び種々のHDLモジュールのいずれかのインストラクション、データ又は他の情報を含む。

【0028】

図5には、コンピュータシステム60も示されている。このコンピュータシステム60は、ここでは、詳細に示されていないが、実質的には、コンピュータ読み取り可能な媒体50から情報をアクセスすることのできるいかなる形式のコンピュータシステムでもよい。更に、コンピュータシステム60は、種々のHDLモジュールを使用して、ここに述べるIC設計の模擬及びテストを遂行するように構成されてもよい。コンピュータシステム60は、1つ以上のプロセッサ又はプロセッサコア、種々の形式のメモリ(例えば、ダイナミックランダムアクセスメモリ又はDRAM)及び記憶装置(例えば、ハードディスクドライブ)、並びにコンピュータ読み取り可能な媒体からのデータにアクセスするところの種々のポートを含む。又、コンピュータシステム60は、その各記憶装置にソフトウェアを含んでもよい。そのようなソフトウェアは、HDLモジュールにおけるHDLステートメントをマシン読み取り可能なフォーマット(例えば、プロセッサインストラクションセットのインストラクション)へ変換するためのコンパイラーを含む。

【0029】

コンピュータ読み取り可能な媒体は、コンピュータシステム60によってアクセスすることができる。特に、コンピュータシステム60は、HDLモジュール20及びその各々のサブモジュールにより記述されたIC設計の模擬を遂行するためにコンピュータ読み取り可能な媒体50に記憶されたデータ構造体にアクセスする。又、コンピュータ読み取り可能な媒体50のデータ構造体は、テストベンチモジュール50により記述されたテストルーチン当たりのIC設計のテストを遂行するためにコンピュータシステム60によりアクセスすることもできる。テストは、コンピュータシステム60がテストベンチモジュール32並びにHDLモジュール20、22、24、25及び26の各々からのインストラクションを実行することにより達成される。模擬クロック信号を使用する模擬及びテストにおいて、クロックハンドラーオブジェクト35は、クロックステートメントに対応するインストラクションを実行することによりコールされる。クロックステートメントに対応するインストラクションの実行に応答して、クロックハンドラー35は、1つ以上の模擬クロック信号を発生し及びコントロールする。

【0030】

ここで使用するHDLは、ICにおいて具現化されるハードウェアを記述するのに使用される言語を指す。工業的に知られているHDLに加えて、この開示に関するHDLは、SystemVerilog、C/C++、等の言語も含む。

【0031】

以上の開示が完全に理解されれば、種々の修正や変更が当業者に明らかとなろう。そのような変更や修正は、全て、特許請求の範囲に包含されるものとする。

【符号の説明】

【0032】

10:集積回路

12、14:コア

15:メモリコントローラ

16:バスインターフェイス

20:HDLモジュール

22:HDLモジュール

24:HDLモジュール

25:HDLモジュール

26:HDLモジュール

32:テストベンチモジュール

35:クロックハンドラーオブジェクト

50:コンピュータ読み取り可能な媒体

60:コンピュータシステム

【技術分野】

【0001】

本発明は、ハードウェア記述言語(HDL)に関し、より特定すれば、HDL環境における模擬クロック信号の発生及びコントロールに関する。

【背景技術】

【0002】

一部分は近代的な製造技術で達成できる高度な集積のために、集積回路設計は、非常に複雑になりつつある。高度な集積をもつ複雑な集積回路は、回路レベルや論理ゲートレベルで設計することが不可能である。従って、複雑な集積回路設計を管理するため、種々のハードウェア記述言語(HDL)が開発されている。HDLは、集積回路の高レベル記述を許す。この記述は、集積回路設計を模擬するためにコンピュータシステムで実行できるソフトウェアコードの形態である。更に、HDLは、ハードウェアの特定の断片を記述する他のモジュールをテストするのに使用されるテストベンチとして知られたモジュールを書くのに使用することができる。

【0003】

典型的な集積回路設計は、多数の異なるファンクションユニットを含む。例えば、システムオンチップ(SOC)設計は、複数のプロセッサコア、少なくとも1つのメモリ、グラフィック処理ユニット、スイッチングユニット、及び1つ以上のインターフェイス回路を含む。これらの異なるファンクションユニットの各々は、個別のHDLモジュールにより記述される。より詳細には、各HDLモジュールは、実際にはファンクションユニットの略記記述であるHDLコードの多数のステートメントにより記述される。これらステートメントは、内部オペレーションを記述する付加的なステートメントと共にファンクションブロックの入力及び出力を指定する。これらファンクションユニットの多くは、クロック信号を必要とする。従って、各々の対応するHDLモジュールは、クロック信号を指定する多数のステートメントを、周波数、開始時間、停止時間及び種々の統計学的監視状態のようなパラメータと共に含む。

【発明の概要】

【0004】

ハードウェア記述言語(HDL)環境に使用するためのグローバルなクロックハンドラーオブジェクトが開示される。一実施形態において、HDLモジュールは、1つ以上のクロックステートメントを含む。コンピュータシステムがクロックステートメントを実行するときに、クロックハンドラーオブジェクトがコールされる。クロックハンドラーオブジェクトは、集積回路設計の1つ以上の模擬ファンクションブロックに対する模擬クロック信号を発生する。各模擬クロックは、個別の且つ独特のスレッドに指定される。クロックハンドラーオブジェクトは、集積回路設計に対する各模擬クロック信号を管理するように構成されたシングルトンオブジェクトである。

【0005】

一実施形態において、テストベンチとして知られたHDLモジュールは、多数の異なるクロックステートメントを含む。テストベンチは、集積回路設計を実施する別のHDLモジュール(供試装置又は“DUT”)のテストを遂行するように構成される。クロックステートメントの実行に応答して、テストベンチは、クロックハンドラーオブジェクトを呼び出してそれに対応するクロック信号の模擬を発生し、そしてそれらをDUTの各ポートに指定する。各クロックハンドラーステートメントは、それに対応する模擬クロック信号のあるパラメータを指定する。そのようなパラメータは、周波数、開始時間、停止時間、別のクロック信号に対するオフセットを含む(が、それに限定されない)。クロックハンドラーオブジェクトは、種々の模擬クロック信号及びそれに対応するパラメータを追跡するためのダイナミックアレイを維持する。又、クロックハンドラーオブジェクトは、テストベンチのオペレーションに対する全ての模擬クロック信号を、テストベンチに基づくDUTの模擬中に発生しそしてコントロールすることができる。クロックハンドラーオブジェクトは、シングルトンオブジェクトであり、即ち集積回路設計の模擬中に一度インスタンス生成される。

【0006】

以下、添付図面を参照して、本発明を詳細に説明する。

【図面の簡単な説明】

【0007】

【図1】集積回路設計及びその設計に対応するハードウェア記述言語(HDL)モジュールの一実施形態の対応グループを示すブロック図である。

【図2】クロックハンドラーオブジェクトを含むHDLモジュール、及び集積回路設計をテストするためのテストベンチモジュールのグループの一実施形態の編成を示すブロック図である。

【図3】クロックハンドラーオブジェクトの一実施形態により維持されるダイナミックアレイを示す図である。

【図4】テストベンチを使用して集積回路設計のテストを開始するための方法の一実施形態を示すフローチャートである。

【図5】コンピュータ読み取り可能な媒体の一実施形態のブロック図である。

【発明を実施するための形態】

【0008】

本発明は、種々の変更を受けそして別の形態でも実施できるが、その特定の実施形態を一例として添付図面に示して以下に詳細に説明する。しかしながら、添付図面及び詳細な説明は、本発明を、ここに開示する特定の形態に限定するものではなく、本発明は、特許請求の範囲に規定される本発明の精神及び範囲内に入る全ての変更、等効物及び代替え物を網羅することを理解されたい。ここに使用する見出しは、編成上の目的に過ぎず、説明の範囲を限定するためのものではない。又、本出願全体にわたって使用される「〜してもよい(may)」という語は、許すという意味(即ち、〜の潜在性があるという意味)で使用されるもので、強制の意味(即ち、〜しなければならないという意味)ではない。同様に、「含む(include)」、「含んでいる(including)」及び「含む(includes)」という語は、含むことを意味するが、それに限定されない。

【0009】

種々のユニット、回路又は他のコンポーネントは、1つ又は複数のタスクを遂行するように「構成される」ものとして述べる。この点について、「構成される」とは、動作中に1つ又は複数のタスクを遂行する「回路を有する」ことを一般的に意味する構造を広く表現するものである。従って、ユニット/回路/コンポーネントは、そのユニット/回路/コンポーネントが現在オンでなくても、タスクを遂行するように構成することができる。一般的に、「構成される」に対応する構造を形成する回路は、ハードウェア回路、及び/又は動作を実施するよう実行できるプログラムインストラクションを記憶するメモリを含む。メモリは、スタティック又はダイナミックランダムアクセスメモリのような揮発性メモリ、及び/又は光学又は磁気ディスク記憶装置、フラッシュメモリ、プログラム可能なリードオンリメモリ、等の不揮発性メモリを含む。同様に、種々のユニット/回路/コンポーネントは、説明の便宜上、1つ又は複数のタスクを遂行するものとして説明されてもよい。そのような説明は、「構成される」という句を含むものと解釈されねばならない。1つ以上のタスクを遂行するように構成されたユニット/回路/コンポーネントを表現する場合に、そのユニット/回路/コンポーネントに関して35U.S.C.§112、第6節の解釈を引用しないことが明確に意図される。

【0010】

図1は、集積回路設計及びその設計に対応するハードウェア記述言語(HDL)モジュールの対応グループの一実施形態を示すブロック図である。図示された実施形態における集積回路(IC)10は、複数のファンクションブロックを含む予備的なIC設計のブロック図である。ここに例示するIC10は、一例に過ぎず、これに限定されるものではないことに注意されたい。

【0011】

ここに提案する設計では、IC10は、2つのコア、即ちコア12及びコア14を有するマルチコアプロセッサである。一実施形態において、コア12及び14は、互いに同一である。別の実施形態では、これらのコアが異なるものであり、例えば、一方のコアは、一般的な処理のために具現化され、他方のコアは、グラフィック処理専用とされる。IC10は、更に、両コアに結合されたメモリコントローラ15を備えている。最終的な具現化において、メモリコントローラ15は、システムメモリへのインターフェイスをなすように構成される。又、IC10は、両コア及びメモリコントローラ16に結合されたバスインターフェイス16も備えている。最終的な具現化におけるバスインターフェイス16は、IC10と1つ以上の周辺バスとの間のインターフェイスをなすように構成される。特に、バスインターフェイス16は、周辺バスに取り付けられた装置と、IC10の他のファンクションブロックとの間のトラフィック流を整合する。

【0012】

図1に示した例では、IC10の設計は、ハードウェア記述言語(HDL)モジュール20によって表され、このモジュールは、次いで、付加的なHDLモジュールより成る。この例におけるHDLモジュール22は、コア12のHDL記述である。同様に、HDLモジュール24、25及び26は、各々、コア14、メモリコントローラ15、及びバスインターフェイス16のHDL記述を与える。HDLにおいて(即ち、コンパイルの前に)、各モジュールは、多数のステートメントを含む。HDLステートメントは、各モジュールへの入力、各モジュールからの出力、各モジュールにより遂行されるオペレーション、等を指定する。更に、図1に示すHDLモジュールの各々は、それ自体、付加的なHDLモジュールを含むことに注意されたい。例えば、図1に示した所与のHDLモジュールは、加算器、除算器、マルチプレクサ、メモリ、種々の形式の状態マシン、等の付加的なモジュールを含む。HDLモジュール20内のあるHDLモジュールは、事前に設計されたライブラリから得られ、他のHDLモジュールは、IC10の設計プロセス中に書かれる。

【0013】

図2は、クロックハンドラーオブジェクトを含むHDLモジュール、及び集積回路設計をテストするためのテストベンチモジュールのグループの一実施形態の編成を示すブロック図である。この所与の例におけるテストベンチ32は、図1を参照して上述したHDLモジュール20及びその種々のモジュールに記述されたIC設計のテストを遂行するように構成されたHDLモジュールである。従って、ここに示す実施形態におけるテストベンチ32は、HDLモジュール20及びその種々のサブモジュールを包囲する。更に、テストベンチモジュール32は、実行されたときに、HDLモジュール20及びそのサブモジュールにテスト刺激を与える多数のHDLステートメントも含む。これらのステートメントは、あるケースでは、テスト刺激を与えることにより生じる結果をチェックするが、テストベンチ32には、より複雑で及び/又は完了により多くの時間を要するテストのために個別の検証ステートメントも含まれる。

【0014】

ここに示す実施形態におけるテストベンチ32は、多数の規範的なクロックステートメントを含む。これらクロックステートメントは、実行時に、クロックハンドラーオブジェクト35をコールする。各クロックステートメントの実行に応答して、クロックハンドラーオブジェクト35は、HDLモジュール20のクロックポート(例えば、Clk_1、Clk_2)の1つに与えられる対応する模擬クロック信号を発生する。又、クロックハンドラーオブジェクト35は、クロックポートを通るのではなく、HDLモジュール20の部分に内部で与えられる模擬クロック信号も発生する。いずれの場合にも、クロックハンドラーオブジェクト35は、動作中に1つ以上のクロック信号を使用するファンクションブロックに対応するHDLモジュールの各々に模擬クロック信号を与える。一般的に、クロックハンドラーオブジェクト35は、HDLモジュール20及びその各々のサブモジュールの任意の部分に対して模擬クロック信号を発生する。

【0015】

ここに示す実施形態におけるクロックハンドラーオブジェクト35は、シングルトンオブジェクトである。即ち、HDLモジュール20を経てテストベンチ32の実行中及び/又はIC設計の模擬中にアクティブであるのは、クロックハンドラーオブジェクト35の1つのインスタンスだけである。更に、ここに示す実施形態におけるクロックハンドラーオブジェクト35は、所与の模擬に対する全ての模擬クロック信号を発生及びコントロールするように構成され、従って、グローバルなクロックハンドラーとして働く。それとは対照的に、従来の実施形態は、クロックハンドラーオブジェクト35によって与えられる集中クロック信号を含まず、むしろ、HDLコードの個別区分において模擬クロック信号及び全ての各パラメータを発生する。

【0016】

図2の例に示された各クロックステートメントは、クロックハンドラーオブジェクト(‘clk_hdlr’)、クロックハンドラーにより遂行されるファンクション(例えば、‘get_clk’)、クロック名(例えば、‘CLK_1’)、模擬クロックが指定されるクロックポート(例えば、‘Clk_1’)、及び1つ以上の引数を指定する。引数は、クロック信号周波数のようなクロック信号パラメータを指定するのに使用される。更に、クロックハンドラーオブジェクト35のアプリケーションプログラミングインターフェイス(API)は、模擬クロック信号に対する付加的なパラメータをセットするのに使用される。従って、クロックハンドラーオブジェクト35をコールするHDLモジュールは、模擬クロック信号を生成するクロックステートメントであって、他の考えられるパラメータの中で、開始時間、停止時間、実行するサイクル数、デューティサイクル、及びオフセット(別のクロック信号に対する)を指定するクロックステートメントも含む。これらファンクションをコールするクロックステートメントは、テストベンチモジュール32を含めて、HDLモジュール内のどこに配置されてもよい。

【0017】

クロックハンドラーオブジェクト32のここに示す実施形態におけるクロックステートメント及びAPIのフォーマットは、単なる例示に過ぎないことに注意されたい。他のフォーマットも考えられ、意図される。

【0018】

ここに示す実施形態におけるクロックハンドラーオブジェクト32は、スレッドごとに模擬クロック信号を発生及びコントロールするように構成される。即ち、ここに示す実施形態におけるクロックハンドラーオブジェクト35は、模擬クロック信号ごとに個別の実行スレッドを発生するように構成される。ここに示す例では、スレッド1は、CLK_1専用であり、スレッド2は、CLK_2専用であり、スレッド3は、CLK_3専用である。模擬クロック信号ごとに個別のスレッドを与えることは、同時にアクティブとなる複数の模擬クロック信号の管理及びコントロールを簡単にする。例えば、所与の模擬クロック信号のパラメータが変化すると、そのクロック信号専用のスレッドに影響するが、他の模擬クロック信号の対応スレッドには影響しない。

【0019】

クロックハンドラーオブジェクト35は、複数の模擬クロック信号を管理するためにダイナミックアレイを発生し維持する。このアレイは、そのサイズを必要に応じて増加又は減少できるという点でダイナミックである。図3は、クロックハンドラーオブジェクトの一実施形態により維持されるダイナミックアレイを示す図である。ここに示す実施形態では、アレイ300は、行及び列に配列された多数のエレメントを含む。アレイ300の各エレメントは、クロックハンドラーオブジェクト35により発生される模擬クロック信号の1つに対応する。アレイ300にエレメントとして記憶される種々のパラメータは、上述したもの、例えば、クロック名、周期/周波数、開始時間、停止時間、等を含む。図3に明確に述べられず又は示されない付加的なパラメータも、ある実施形態には存在する。

【0020】

上述したように、アレイ300は、ダイナミックアレイである。従って、例えば、クロックステートメントが模擬クロック信号を要求するためにクロックハンドラーオブジェクト35をコールするときに、エレメントの新たなセットがアレイ300に追加される。エレメントの新たなセットは、新たに要求された模擬クロック信号に対応する。更に、クロックハンドラーオブジェクト35は、それらエレメントがもはや必要ない場合にアレイ300から除去する。例えば、模擬クロック信号が、模擬/テストの初期部分に対してのみ動作すべき場合には、クロックハンドラーオブジェクト35は、模擬クロック信号がインアクティブになったときにアレイ300から各エレメントを除去する。又、クロックハンドラーオブジェクト35は、模擬/テスト中にアレイ300のあるエレメントの値を変更することもある。例えば、クロックステートメントが所与の模擬クロック信号に対するオフセット値の変更を指定する場合には、クロックハンドラーオブジェクト35は、必要な変更を行いながらアレイ300における対応エレメントを更新する。

【0021】

図4は、テストベンチを使用してIC設計のテストを開始するための方法の一実施形態を示すフローチャートである。ここに示す実施形態では、方法400は、テストベンチモジュールを開始する1つ以上のインストラクションの実行で開始される(ブロック405)。一実施形態において、テストベンチモジュールを開始する1つ以上のインストラクション、及び方法400で実行される他のインストラクションは、HDLステートメントからコンパイルされたマシン言語インストラクションである。インタープリターを使用してHDLステートメントを実行する実施形態も考えられ、意図される。

【0022】

テストベンチモジュールを開始した後、1つ以上のクロックステートメントに対応するインストラクションが実行され、それに応答してクロックハンドラーオブジェクトがコールされる(ブロック410)。クロックハンドラーオブジェクトは、次いで、指定のパラメータに基づいて対応する模擬クロック信号を発生する(ブロック415)。クロックハンドラーオブジェクトは、新たに発生されたクロック信号模擬の種々のパラメータに対応するエレメントをダイナミックアレイに追加する(ブロック420)。第1のクロックステートメントの実行は、ダイナミックアレイを発生する。新たな模擬クロック信号を要求する付加的なクロックステートメントの実行(ブロック425、イエス)は、対応するエレメントをダイナミックアレイに追加させる。以前に発生された模擬クロック信号に対するあるパラメータを指定する付加的なクロックステートメントは、ダイナミックアレイを更新させる。

【0023】

IC設計の模擬及びそのテストを開始する前に付加的な模擬クロック信号が発生されない場合には(ブロック425、ノー)、IC設計に対応するHDLモジュールが開始される(ブロック430)。しかしながら、IC設計を記述するHDLモジュール及びそのファンクションブロックが模擬クロック信号の発生及び実行の前に開始される実施形態も考えられ、意図されることに注意されたい。

【0024】

テストベンチ、望ましいクロック信号の模擬、及びIC設計に対応するHDLモジュールの全部が開始されると、テストベンチの実行及びIC設計のテストを開始することができる(ブロック435)。テストベンチの実行中に、テストベクトルがIC設計の種々の入力に与えられ、そしてテスト結果が種々の出力を通して捕獲される。テスト結果の捕獲を分析して、IC設計が仕様内で正しく機能するかどうか決定することができる。

【0025】

方法400は、テストを開始する前にクロックステートメントの実行を経て1つ以上の模擬クロック信号を発生することを含むが、この方法の間にいつでも付加的なクロックステートメントを実行できることに注意されたい。例えば、テストの開始に続き、模擬クロック信号同士のオフセットを変更するクロックステートメントを実行してもよい。更に、テスト中に、模擬クロック信号を開始し及び/又は停止するステートメントも実行される。あるケースでは、テストシーケンスの残り部分に対して模擬クロック信号がインアクチベートされた場合には、クロックハンドラーオブジェクトは、それに対応するエレメントをダイナミックアレイから排除して、そのサイズ、ひいては、そのメモリフットプリントを減少する。一般的に、クロックステートメントは、テストベンチの動作及び/又はIC設計の模擬中にいつでも実行することができる。更に、本開示では、テストベンチ内から実行されるクロックステートメントの例が使用されるが、クロックハンドラーオブジェクトをコールするクロックステートメントが、IC設計のファンクションユニットを記述するものを含めて、HDLモジュールから実行されてもよいことに注意されたい。

【0026】

図5は、コンピュータ読み取り可能な媒体の一実施形態のブロック図である。ここに示す実施形態では、コンピュータ読み取り可能な媒体50は、非一時的なコンピュータ読み取り可能な媒体である。非一時的なコンピュータ読み取り可能な媒体とは、例えば、フラッシュメモリ(例えば、フラッシュドライブの)、ハードディスク記憶装置、CD−ROM、DVD−ROM、等を含む。一般的に、コンピュータ読み取り可能な媒体50は、適切に装備されたコンピュータシステムが記憶情報にアクセスするところの任意の形式の非一時的なコンピュータ読み取り可能な媒体である。

【0027】

この特定例において、コンピュータ読み取り可能な媒体50は、クロックハンドラーオブジェクト35、テストベンチモジュール32、HDLモジュール20、及びその種々のサブモジュール(HDLモジュール22、24、25及び26)の各々を作り上げる種々のデータ構造体を記憶する。ここで使用する「データ構造体」という語は、コンピュータ読み取り可能な媒体50に記憶されたクロックハンドラーオブジェクト35、テストベンチ32、及び種々のHDLモジュールのいずれかのインストラクション、データ又は他の情報を含む。

【0028】

図5には、コンピュータシステム60も示されている。このコンピュータシステム60は、ここでは、詳細に示されていないが、実質的には、コンピュータ読み取り可能な媒体50から情報をアクセスすることのできるいかなる形式のコンピュータシステムでもよい。更に、コンピュータシステム60は、種々のHDLモジュールを使用して、ここに述べるIC設計の模擬及びテストを遂行するように構成されてもよい。コンピュータシステム60は、1つ以上のプロセッサ又はプロセッサコア、種々の形式のメモリ(例えば、ダイナミックランダムアクセスメモリ又はDRAM)及び記憶装置(例えば、ハードディスクドライブ)、並びにコンピュータ読み取り可能な媒体からのデータにアクセスするところの種々のポートを含む。又、コンピュータシステム60は、その各記憶装置にソフトウェアを含んでもよい。そのようなソフトウェアは、HDLモジュールにおけるHDLステートメントをマシン読み取り可能なフォーマット(例えば、プロセッサインストラクションセットのインストラクション)へ変換するためのコンパイラーを含む。

【0029】

コンピュータ読み取り可能な媒体は、コンピュータシステム60によってアクセスすることができる。特に、コンピュータシステム60は、HDLモジュール20及びその各々のサブモジュールにより記述されたIC設計の模擬を遂行するためにコンピュータ読み取り可能な媒体50に記憶されたデータ構造体にアクセスする。又、コンピュータ読み取り可能な媒体50のデータ構造体は、テストベンチモジュール50により記述されたテストルーチン当たりのIC設計のテストを遂行するためにコンピュータシステム60によりアクセスすることもできる。テストは、コンピュータシステム60がテストベンチモジュール32並びにHDLモジュール20、22、24、25及び26の各々からのインストラクションを実行することにより達成される。模擬クロック信号を使用する模擬及びテストにおいて、クロックハンドラーオブジェクト35は、クロックステートメントに対応するインストラクションを実行することによりコールされる。クロックステートメントに対応するインストラクションの実行に応答して、クロックハンドラー35は、1つ以上の模擬クロック信号を発生し及びコントロールする。

【0030】

ここで使用するHDLは、ICにおいて具現化されるハードウェアを記述するのに使用される言語を指す。工業的に知られているHDLに加えて、この開示に関するHDLは、SystemVerilog、C/C++、等の言語も含む。

【0031】

以上の開示が完全に理解されれば、種々の修正や変更が当業者に明らかとなろう。そのような変更や修正は、全て、特許請求の範囲に包含されるものとする。

【符号の説明】

【0032】

10:集積回路

12、14:コア

15:メモリコントローラ

16:バスインターフェイス

20:HDLモジュール

22:HDLモジュール

24:HDLモジュール

25:HDLモジュール

26:HDLモジュール

32:テストベンチモジュール

35:クロックハンドラーオブジェクト

50:コンピュータ読み取り可能な媒体

60:コンピュータシステム

【特許請求の範囲】

【請求項1】

実行された場合に、コンピュータが、

集積回路の動作を模擬する模擬クロック信号を発生するための要求を第1のハードウェア記述言語(HDL)モジュールから受け取り、

その要求に応答して、模擬クロック信号を前記第1のHDLモジュールに与える、

ようにさせるプログラムインストラクションを記憶している非一時的コンピュータ読み取り可能な記憶媒体。

【請求項2】

クロックハンドラーオブジェクトは、シングルトンオブジェクトである、請求項1に記載のコンピュータ読み取り可能な媒体。

【請求項3】

前記クロックハンドラーオブジェクトは、対応する独特のスレッド内で複数の模擬クロック信号の各々を、前記第1のHDLモジュールにおける対応する複数のクロックハンドラーステートメントの実行に応答して、発生するように構成された、請求項1に記載のコンピュータ読み取り可能な媒体。

【請求項4】

前記クロックハンドラーオブジェクトは、前記模擬クロック信号に対して、別のクロック信号に対するオフセットをセットするように構成された、請求項1に記載のコンピュータ読み取り可能な媒体。

【請求項5】

前記クロックハンドラーオブジェクトは、ダイナミックアレイを維持するように構成され、そのダイナミックアレイの各エレメントは、1つ以上の模擬クロック信号の1つに関する情報を含む、請求項1に記載のコンピュータ読み取り可能な媒体。

【請求項6】

前記クロックハンドラーオブジェクトは、複数のHDLモジュールの対応する1つにより記述される集積回路の設計の複数のファンクションブロックの1つに各々対応する複数の模擬クロック信号を発生するように構成された、請求項1に記載のコンピュータ読み取り可能な媒体。

【請求項7】

前記第1のHDLモジュールは、前記複数のHDLモジュールの少なくとも1つの他のモジュールをテストするように構成されたテストベンチモジュールであり、このテストベンチモジュールは、コンピュータにより実行されたときに、複数の模擬クロック信号を発生する複数のクロックステートメントを含む、請求項6に記載のコンピュータ読み取り可能な媒体。

【請求項8】

前記複数のクロックステートメントの各々は、複数の模擬クロック信号のうちの対応する1つの信号の1つ以上のパラメータを指示するように構成され、その1つ以上のパラメータは、クロック周期を含む、請求項7に記載のコンピュータ読み取り可能な媒体。

【請求項9】

コンピュータシステムが集積回路の模擬中にクロックハンドラーステートメントを実行する段階と、

クロックハンドラーオブジェクトがコンピュータシステム上で実行されて、前記クロックハンドラーステートメントの実行に応答して模擬クロック信号発生する段階と、

を含む方法。

【請求項10】

ハードウェア記述言語(HDL)モジュールの模擬クロックポートに模擬クロック信号を指定する段階を更に含み、前記HDLモジュールは、集積回路のブロックに対応する、請求項9に記載の方法。

【請求項11】

前記クロックハンドラーオブジェクトが、前記模擬クロック信号に対応するスレッドを発生する段階を更に含む、請求項9に記載の方法。

【請求項12】

前記クロックハンドラーオブジェクトが、前記模擬クロック信号のパラメータをセットする段階を更に含み、前記パラメータは、クロック信号オフセットを含む、請求項9に記載の方法。

【請求項13】

前記クロックハンドラーオブジェクトが、前記模擬クロック信号及び1つ以上の付加的な模擬クロック信号に対応する情報のダイナミックアレイを維持する段階を更に含み、そのダイナミックアレイの各エレメントは、前記模擬クロック信号又は1つ以上の付加的な模擬クロック信号の一方のパラメータに関する情報を含む、請求項12に記載の方法。

【請求項14】

前記ダイナミックアレイの各エレメントは、それに対応する模擬クロック信号の周期を指示する値を含む、請求項13に記載の方法。

【請求項15】

テストベンチモジュールがHDLモジュールのテストを遂行する段階を更に含み、そのテストベンチモジュールは、クロックハンドラーステートメントを含む、請求項10に記載の方法。

【請求項16】

実行された場合に、コンピュータが、

集積回路を模擬し、集積回路の設計は、ハードウェア記述言語(HDL)で記述され、集積回路の設計は、複数のHDLモジュールの対応する1つによって各々記述される1つ以上のファンクションブロックを含み、更に、その1つ以上のファンクションブロックの各々は、1つ以上のクロック信号の1つを使用し、

クロックハンドラーを使用して1つ以上の模擬クロック信号を発生し、そのクロックハンドラーは、クロックステートメントの実行に応答して、対応するファンクションブロックのための対応する模擬クロック信号を発生するように実行できる、

ことを含む動作を遂行するようにさせるプログラムインストラクションを記憶している非一時的コンピュータ読み取り可能な記憶媒体。

【請求項17】

前記クロックハンドラーは、複数のHDLモジュールの対応する1つにより記述される集積回路設計の複数のファンクションブロックの1つに各々対応する複数の模擬クロック信号を発生するよう実行できる、請求項16に記載のコンピュータ読み取り可能な媒体。

【請求項18】

前記クロックハンドラーは、複数の模擬クロック信号の各々を、複数のクロック信号の他の各々に対して独特のスレッドに指定するように実行できる、請求項17に記載のコンピュータ読み取り可能な媒体。

【請求項19】

前記クロックハンドラーは、クロックステートメントに指定された1つ以上のパラメータに基づいて模擬クロック信号を与えるように実行できる、請求項16に記載のコンピュータ読み取り可能な媒体。

【請求項20】

前記複数のHDLモジュールは、テストベンチモジュールを含み、そのテストベンチモジュールは、複数のHDLモジュールのうちの少なくとも1つの他のモジュールをテストするように構成され、更に、そのテストベンチモジュールは、クロックステートメントを含む、請求項16に記載のコンピュータ読み取り可能な媒体。

【請求項1】

実行された場合に、コンピュータが、

集積回路の動作を模擬する模擬クロック信号を発生するための要求を第1のハードウェア記述言語(HDL)モジュールから受け取り、

その要求に応答して、模擬クロック信号を前記第1のHDLモジュールに与える、

ようにさせるプログラムインストラクションを記憶している非一時的コンピュータ読み取り可能な記憶媒体。

【請求項2】

クロックハンドラーオブジェクトは、シングルトンオブジェクトである、請求項1に記載のコンピュータ読み取り可能な媒体。

【請求項3】

前記クロックハンドラーオブジェクトは、対応する独特のスレッド内で複数の模擬クロック信号の各々を、前記第1のHDLモジュールにおける対応する複数のクロックハンドラーステートメントの実行に応答して、発生するように構成された、請求項1に記載のコンピュータ読み取り可能な媒体。

【請求項4】

前記クロックハンドラーオブジェクトは、前記模擬クロック信号に対して、別のクロック信号に対するオフセットをセットするように構成された、請求項1に記載のコンピュータ読み取り可能な媒体。

【請求項5】

前記クロックハンドラーオブジェクトは、ダイナミックアレイを維持するように構成され、そのダイナミックアレイの各エレメントは、1つ以上の模擬クロック信号の1つに関する情報を含む、請求項1に記載のコンピュータ読み取り可能な媒体。

【請求項6】

前記クロックハンドラーオブジェクトは、複数のHDLモジュールの対応する1つにより記述される集積回路の設計の複数のファンクションブロックの1つに各々対応する複数の模擬クロック信号を発生するように構成された、請求項1に記載のコンピュータ読み取り可能な媒体。

【請求項7】

前記第1のHDLモジュールは、前記複数のHDLモジュールの少なくとも1つの他のモジュールをテストするように構成されたテストベンチモジュールであり、このテストベンチモジュールは、コンピュータにより実行されたときに、複数の模擬クロック信号を発生する複数のクロックステートメントを含む、請求項6に記載のコンピュータ読み取り可能な媒体。

【請求項8】

前記複数のクロックステートメントの各々は、複数の模擬クロック信号のうちの対応する1つの信号の1つ以上のパラメータを指示するように構成され、その1つ以上のパラメータは、クロック周期を含む、請求項7に記載のコンピュータ読み取り可能な媒体。

【請求項9】

コンピュータシステムが集積回路の模擬中にクロックハンドラーステートメントを実行する段階と、

クロックハンドラーオブジェクトがコンピュータシステム上で実行されて、前記クロックハンドラーステートメントの実行に応答して模擬クロック信号発生する段階と、

を含む方法。

【請求項10】

ハードウェア記述言語(HDL)モジュールの模擬クロックポートに模擬クロック信号を指定する段階を更に含み、前記HDLモジュールは、集積回路のブロックに対応する、請求項9に記載の方法。

【請求項11】

前記クロックハンドラーオブジェクトが、前記模擬クロック信号に対応するスレッドを発生する段階を更に含む、請求項9に記載の方法。

【請求項12】

前記クロックハンドラーオブジェクトが、前記模擬クロック信号のパラメータをセットする段階を更に含み、前記パラメータは、クロック信号オフセットを含む、請求項9に記載の方法。

【請求項13】

前記クロックハンドラーオブジェクトが、前記模擬クロック信号及び1つ以上の付加的な模擬クロック信号に対応する情報のダイナミックアレイを維持する段階を更に含み、そのダイナミックアレイの各エレメントは、前記模擬クロック信号又は1つ以上の付加的な模擬クロック信号の一方のパラメータに関する情報を含む、請求項12に記載の方法。

【請求項14】

前記ダイナミックアレイの各エレメントは、それに対応する模擬クロック信号の周期を指示する値を含む、請求項13に記載の方法。

【請求項15】

テストベンチモジュールがHDLモジュールのテストを遂行する段階を更に含み、そのテストベンチモジュールは、クロックハンドラーステートメントを含む、請求項10に記載の方法。

【請求項16】

実行された場合に、コンピュータが、

集積回路を模擬し、集積回路の設計は、ハードウェア記述言語(HDL)で記述され、集積回路の設計は、複数のHDLモジュールの対応する1つによって各々記述される1つ以上のファンクションブロックを含み、更に、その1つ以上のファンクションブロックの各々は、1つ以上のクロック信号の1つを使用し、

クロックハンドラーを使用して1つ以上の模擬クロック信号を発生し、そのクロックハンドラーは、クロックステートメントの実行に応答して、対応するファンクションブロックのための対応する模擬クロック信号を発生するように実行できる、

ことを含む動作を遂行するようにさせるプログラムインストラクションを記憶している非一時的コンピュータ読み取り可能な記憶媒体。

【請求項17】

前記クロックハンドラーは、複数のHDLモジュールの対応する1つにより記述される集積回路設計の複数のファンクションブロックの1つに各々対応する複数の模擬クロック信号を発生するよう実行できる、請求項16に記載のコンピュータ読み取り可能な媒体。

【請求項18】

前記クロックハンドラーは、複数の模擬クロック信号の各々を、複数のクロック信号の他の各々に対して独特のスレッドに指定するように実行できる、請求項17に記載のコンピュータ読み取り可能な媒体。

【請求項19】

前記クロックハンドラーは、クロックステートメントに指定された1つ以上のパラメータに基づいて模擬クロック信号を与えるように実行できる、請求項16に記載のコンピュータ読み取り可能な媒体。

【請求項20】

前記複数のHDLモジュールは、テストベンチモジュールを含み、そのテストベンチモジュールは、複数のHDLモジュールのうちの少なくとも1つの他のモジュールをテストするように構成され、更に、そのテストベンチモジュールは、クロックステートメントを含む、請求項16に記載のコンピュータ読み取り可能な媒体。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−101604(P2013−101604A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【外国語出願】

【出願番号】特願2012−230294(P2012−230294)

【出願日】平成24年9月28日(2012.9.28)

【出願人】(503260918)アップル インコーポレイテッド (568)

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2012−230294(P2012−230294)

【出願日】平成24年9月28日(2012.9.28)

【出願人】(503260918)アップル インコーポレイテッド (568)

【Fターム(参考)】

[ Back to top ]