I/Oモジュールおよびそれを用いた2重化システム

【課題】I/Oモジュールをコネクタに挿入したときに、バイパスコンデンサの充電電流、あるいは回路の電流が信号入力ラインに流れて電圧降下が発生し、この電圧降下によってグリッジが発生して他のI/Oモジュールを誤動作させる。本発明はこのようなことがないI/Oモジュールを提供することを目的にする。

【解決手段】コネクタから供給される電源の電圧を監視し、電源が供給されているとバイパスコンデンサあるいは回路を接続し、供給されていないと切り離すようにした。電源ラインより先に信号入力ラインが接続されても、信号入力ラインに過電流が流れないので、グリッジが発生しない。

【解決手段】コネクタから供給される電源の電圧を監視し、電源が供給されているとバイパスコンデンサあるいは回路を接続し、供給されていないと切り離すようにした。電源ラインより先に信号入力ラインが接続されても、信号入力ラインに過電流が流れないので、グリッジが発生しない。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、コネクタを勘合させてシステムに接続したときに、グリッジを発生することがないI/Oモジュールに関し、特に2重化されたシステムに用いて好適なI/Oモジュールに関するものである。

【背景技術】

【0002】

プロセス制御システムでは、I/Oモジュールを介してプロセス量を取り込み、またプロセスに制御量を出力する。図5に、オンラインメンテナンスが可能な、2重化されたI/Oモジュールの構成を示す。

【0003】

図5において、10aはI/Oモジュールであり、入力回路11a、この入力回路11aの電源端子VDとCOMに接続されるバイパスコンデンサ12a、およびコネクタ13aで構成される。入力回路11aはレベル検出部14a、およびこのレベル検出部14aの入力端子と一方の電源端子、入力端子と他方の電源端子との間に接続されたダイオード15a、16aで構成される。レベル検出部14aの電源端子および入力端子は入力回路11aの電源端子VD、COMと入力端子SIGと同じなので、ダイオード15a、15bは入力回路11aの入力端子SIGと電源端子VD間、入力端子SIGと電源端子COM間に接続される。なお、ダイオード15a、16aは、静電気保護の目的で挿入される。

【0004】

コネクタ13aの接点は、入力回路11aの電源端子VDとCOM、入力端子SIGに接続される。I/Oモジュール10aは、外部電源ライン20から供給される電源で動作し、信号入力ライン21を介して信号が入力される。

【0005】

20、21、22はそれぞれ外部電源ライン、信号入力ライン、共通電位点ラインであり、これらのライン20〜22はコネクタ23に接続されている。以降、外部電源ライン20と共通電位点ライン22を合わせて電源ラインと称する。

【0006】

入力回路11aの電源端子VD、COMと入力端子SIGは、コネクタ13aと23を介して電源ライン20、22と信号入力ライン21に接続される。なお、コネクタ13aと23は本来勘合するが、この図では切り離されている。

【0007】

10bはI/Oモジュールであり、I/Oモジュール10aとで2重化システムを構成している。I/Oモジュール10bはI/Oモジュール10aと同じ構成を有しており、入力回路11b、バイパスコンデンサ12b、コネクタ13bで構成される。また、入力回路11bは、レベル検出部14bおよびこのレベル検出部14bの入力端子と電源端子との間に接続されるダイオード15b、16bで構成される。I/Oモジュール10bは、電源ライン20、22から供給される外部電源で動作し、信号入力ライン21から信号が入力される。

【0008】

コネクタ24には電源ライン20、22および信号入力ライン21が接続され、またコネクタ13bと勘合している。電源ライン20、22と入力回路11bの電源端子VD、COM、信号入力ライン21と入力端子SIGは、コネクタ24、13bを介して接続される。

【0009】

このような構成において、コネクタ23と13aを勘合させると、I/Oモジュール10bは制御側I/Oモジュール、I/Oモジュール10aは待機側I/Oモジュールとして動作する。制御側I/Oモジュール10bに異常が発生すると、待機側I/Oモジュール10aが制御側I/Oモジュールとして動作する。

【0010】

また、待機側I/OモジュールであるI/Oモジュール10aは動作していないので、コネクタ23と13aを切り離しても、システムの動作に支障を生じない。従って、システムを動作させながらI/Oモジュール10aを抜き取り、交換することができる。すなわち、オンラインメンテナンスが可能になる。

【0011】

プロセス制御システムは、システムの継続性を担保するために24時間稼働させなければならない。このため、I/Oモジュール10a、10bを用いて2重化することにより、一方のI/Oモジュールに故障が発生すると他方のI/Oモジュールにシームレスで切り替え、またシステムを稼働させながら、故障したI/Oモジュールを交換できるようにしている。

【0012】

図7に、他の2重化されたI/Oモジュールの構成を示す。なお、図5と同じ要素には同一符号を付し、説明を省略する。

【0013】

図7において、30a、30bは2重化されたI/Oモジュールであり、それぞれコネクタ13a、13bおよび入力回路11a、11bで構成される。I/Oモジュール30aはコネクタ13a、23を介して電源ライン20および22、信号入力ライン21に接続され、I/Oモジュール30bはコネクタ13b、24を介してこれらのラインに接続される。この図では、コネクタ13aと23は切り離されている。

【0014】

図5と比較すると、I/Oモジュール30a、30bにはバイパスコンデンサ12a、12bが内蔵されていない点が異なる。動作は図5と同じなので、説明を省略する。

【0015】

特許文献1には、活線状態でモジュールを挿抜できるプロセス制御コントローラが記載されている。特許文献1では、電源コネクタと通信コネクタを分離し、電源用ショートピース、GND用ショートピースを介して複数のI/Oモジュールに電源を供給するようにする。

【先行技術文献】

【特許文献】

【0016】

【特許文献1】特開2000−330603号公報

【発明の概要】

【発明が解決しようとする課題】

【0017】

しかしながら、このようなI/Oモジュールには、次のような課題があった。

図6に、コネクタ13aと23を勘合させて、図5構成のI/Oモジュール10aを電源ライン20および22、信号入力ライン21に接続した時の状態を示す。コネクタ13a、23の各接点は同じ長さを有しているので、挿入時のコネクタの傾き等によってどの接点から接続されるかが変わる。接続される接点の順番は予測、あるいは制御することができない。

【0018】

図6において、(A)〜(C)に示すように、時刻t1〜t3で共通電位点ライン22の接点、信号入力ライン21の接点、外部電源ライン20の接点がこの順でI/Oモジュール10aに接続される。時刻t2で入力回路11aの入力端子SIGと信号入力ライン21が接続されるので、このライン上の信号レベルが高レベルであると、(D)に示すように、入力回路11aの入力信号電圧は時刻t2で高レベルに遷移する。

【0019】

時刻t2では入力回路11aに外部から電源が供給されていないので、ダイオード15aはオンになる。このため、(F)に示すように、信号入力ライン21からダイオード15aに大きな電流が流れる。バイパスコンデンサ12aはこの電流によって充電されるので、(E)に示すように入力回路11aの電源電圧は上昇する。

【0020】

時刻t3で入力回路11aに電源が供給されると、入力回路11aの電源電圧は更に上昇し、やがて安定する。なお、(D)、(E)で電圧が徐々に上昇しているのは、バイパスコンデンサ12aを充電しているためである。

【0021】

(F)に示すように、時刻t2でダイオード15aに大きな電流が流れるが、この電流は信号入力ライン21から供給される。この電流のために信号入力ライン21で電圧降下が発生し、(G)に示すように、同じ信号入力ライン21に繋がっている入力回路11bの入力信号電圧が変化するグリッジが発生する。このため、入力回路10bがこの変化を検出して誤信号を出力してしまうという課題があった。

【0022】

このような誤動作は、バイパスコンデンサを内蔵しない図7のI/Oモジュールでも発生する。

【0023】

図8に、図7構成のI/Oモジュールでコネクタ13aと23が勘合した時の状態を示す。(A)〜(C)に示すように、時刻t4〜t6で共通電位点ライン22の接点、信号入力ライン21の接点、外部電源ライン20の接点がこの順でI/Oモジュール10aに接続される。時刻t5で入力回路11aの入力端子SIGと信号入力ライン21が接続されるので、このライン上の信号レベルが高レベルであると、(D)に示すように、入力回路11aの入力信号電圧は時刻t5で高くなり、ダイオード15aがオンになる。

【0024】

入力回路11aにはダイオード15aから電流が供給されるので、(F)に示すようにダイオード15aには電流が流れ、入力回路11aの電源電圧が高くなる。

【0025】

ダイオード15aに流れる電流は信号入力ライン21から供給されるので、信号入力ライン21に電流が流れて電圧降下が発生し、(G)に示すように同じ信号入力ライン21に繋がっている入力回路11bの入力端子の電圧が変化して誤差が発生する。このため、レベル検出部14bがこの変化を検出して誤信号を出力してしまう。

【0026】

このように、コネクタの接点の接続順によっては、信号入力ライン21に電流が流れて電圧降下が発生し、同じ信号入力ライン21に接続されている入力回路11bの入力電圧にグリッジが発生して誤信号を出力してしまうことがまれに発生するという課題があった。このようなことが発生すると、最悪の場合にはシステムがシャットダウンしてしまうという課題もあった。

【0027】

特許文献1記載の発明は電源コネクタと通信コネクタを分離し、電源用ショートピース、GND用ショートピースを介して複数のI/Oモジュールに電源を供給するので、接続する順番を制御することができる。しかし、マウントベースの構造が複雑になり、かつモジュールに電源を供給するためにはショートピースを接続しなければならず、操作が煩雑になるという課題があった。

【0028】

本発明の目的は、接続時に信号入力ラインに電流が流れることを防止して、グリッジが発生することがないI/Oモジュールを実現することにある。

【課題を解決するための手段】

【0029】

このような課題を達成するために、本発明のうち請求項1記載の発明は、

コネクタを介して電源ラインおよび信号入力ラインに接続され、前記電源ラインから電源が供給されると共に、前記信号入力ライン上の信号を処理してそれに対応する信号を出力するI/Oモジュールにおいて、

前記信号入力ライン上の信号が入力され、この信号を処理すると共に、その入力端子と電源端子との間にダイオードが接続される入力回路と、

バイパスコンデンサと、

前記バイパスコンデンサを前記入力回路の電源端子に接続し、また切り離すスイッチと、

前記コネクタを介して供給される電源の電圧を監視し、前記スイッチを制御して、前記電源が供給されていると前記バイパスコンデンサを前記入力回路の電源端子に接続し、前記電源が供給されていないと前記バイパスコンデンサを前記入力回路の電源端子から切り離す電源電圧検出部と、

を具備したものである。I/Oモジュールを挿入したときに、信号入力ラインに過電流が流れないので、グリッジが発生することがない。

【0030】

請求項2記載の発明は、

コネクタを介して電源ラインおよび信号入力ラインに接続され、前記電源ラインから電源が供給されると共に、前記信号入力ライン上の信号を処理してそれに対応する信号を出力するI/Oモジュールにおいて、

前記信号入力ライン上の信号が入力され、この信号を処理すると共に、その入力端子と電源端子との間にダイオードが接続される入力回路と、

前記入力回路に電源を供給する経路を導通または遮断するスイッチと、

前記コネクタを介して供給される電源の電圧を監視し、前記スイッチを制御して、前記電源が供給されていると前記入力回路に電源を供給する経路を導通させ、前記電源が供給されていないと前記経路を遮断する電源電圧検出部と、

を具備したものである。I/Oモジュールを挿入したときに、信号入力ラインに過電流が流れないので、グリッジが発生することがない。

【0031】

請求項3記載の発明は、

請求項1若しくは請求項2記載のI/Oモジュールを2台用い、一方を制御側I/Oモジュール、他方を待機側I/Oモジュールとしたものである。待機側I/Oモジュールを挿入したときにグリッジが発生しないので、制御側I/Oモジュールが誤信号を検出することがない

【発明の効果】

【0032】

本発明によれば以下のような効果がある。

請求項1、2、および3の発明によれば、コネクタを介して供給される電源の電圧を監視し、電源が供給されるとバイパスコンデンサを入力回路の電源端子に接続し、また入力回路に電源を供給する経路を導通させ、電源が供給されていないとバイパスコンデンサを切り離し、また入力回路に電源を供給する経路を遮断するようにした。また、このI/Oモジュールを用いて2重化システムを構成した。

【0033】

I/Oモジュールをコネクタに挿入したときに、電源ラインよりも先に信号入力ラインが接続されてダイオードがオンになり、信号入力ラインに大きな電流が流れることを防止できる。このため、電圧降下に起因するグリッジが信号入力ラインに発生しないので、同じ信号入力ラインに接続されている他のI/Oモジュールが誤動作することがなくなるという効果がある。

【0034】

また、2重化システムの場合、待機側I/Oモジュールを挿入するときにグリッジが発生しないので、制御側I/Oモジュールが誤動作することがなくなる。このため、信頼性が高い2重化システムを構築できるという効果もある。

【図面の簡単な説明】

【0035】

【図1】本発明の一実施例を示した構成図である。

【図2】図1実施例の動作を説明するための特性図である。

【図3】本発明の他の実施例を示した構成図である。

【図4】図3実施例の動作を説明するための特性図である。

【図5】従来の2重化されたI/Oモジュールの構成図である。

【図6】図5従来例の動作を説明するための特性図である。

【図7】従来の2重化されたI/Oモジュールの構成図である。

【図8】図7従来例の動作を説明するための特性図である。

【発明を実施するための形態】

【0036】

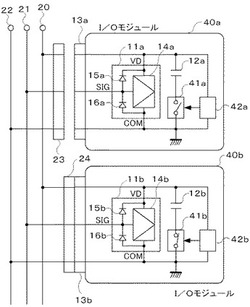

以下本発明を、図面を用いて詳細に説明する。図1は本発明に係るI/Oモジュールの一実施例を示した構成図である。この実施例は、図5従来例に対応するものである。なお、図5と同じ要素には同一符号を付し、説明を省略する。

【0037】

図1において、40aはI/Oモジュールであり、入力回路11a、バイパスコンデンサ12a、コネクタ13a、スイッチ41a、電源電圧検出部42aで構成される。また、入力回路11aは、レベル検出部14aとこのレベル検出部14aの入力端子と電源端子および共通電位点との間に接続されたダイオード15a、16aで構成される。入力回路11aとレベル検出部14aの電源端子、入力端子は共通なので、ダイオード15a、15bは、入力回路11aの入力端子SIGと電源端子VD、COM間に接続される。

【0038】

バイパスコンデンサ12aの一端は入力回路11aの電源端子VDに接続され、他端はスイッチ41aの一端に接続される。このスイッチ41aの他端は、入力回路11aの電源端子COMに接続される。スイッチ41aを操作することにより、バイパスコンデンサ12aを入力回路11aの電源端子に接続し、また切り離すことができる。

【0039】

入力回路11aは、コネクタ13aおよび23を介して電源ライン20および22、信号入力ライン21に接続される。コネクタ13aと23が勘合されると、入力回路11aには電源ライン20、22から電源が供給され、また信号入力ライン21から信号が入力される。図1では、コネクタ13aと23は切り離された状態になっている。

【0040】

コネクタ13aと23が勘合されると入力回路11aに電源が供給される。入力回路11aは信号入力ライン21上の信号レベルを検出し、この検出結果を上位システムに送信する。なお、上位システムに送信するための構成は本発明と直接関係がないので、記載を省略している。

【0041】

電源電圧検出部42aには、コネクタ13aを介して供給される電源電圧が入力される。電源電圧検出部42aは入力された電源電圧を監視し、この監視結果に基づいてスイッチ41aのオンオフを制御する。すなわち、電源電圧検出部42aは、コネクタ13aを介して電源が供給されているとスイッチ41aをオンにしてバイパスコンデンサ12aを入力回路11aの電源端子に接続し、供給されていないとスイッチ41aをオフにしてバイパスコンデンサ12aを切り離す。コネクタ13aの接点の電圧を監視することにより、電源が供給されているか否かを判定することができる。

【0042】

40bはI/Oモジュールであり、入力回路11b、バイパスコンデンサ12b、コネクタ13b、スイッチ41b、電源電圧検出部42bで構成される。また、入力回路11bには、入力回路11bの入力端子SIGと電源端子VD、COM間には、ダイオード15b、16bが接続される。

【0043】

I/Oモジュール40bは、I/Oモジュール40aと同じ構成を有している。すなわち、入力回路11bは信号入力ライン21上の信号レベルを検出し、この検出結果を上位システムに送信する。また、電源電圧検出部42bはコネクタ13bから供給される電源の電圧を監視し、この電源が供給されているとスイッチ41bをオンにしてバイパスコンデンサ12bを入力回路11bの電源端子に接続し、供給されていないとスイッチ41bをオフにしてバイパスコンデンサ12bを切り離す。図1ではコネクタ13bと24は勘合状態になっている。

【0044】

コネクタ13aと23が勘合されると、I/Oモジュール40aと40bで2重化システムが構成される。すなわち、I/Oモジュール40bは制御側I/Oモジュールとして動作し、I/Oモジュール40aは待機側I/Oモジュールとして動作する。待機側I/Oモジュールはシステムの動作には関係しないので、システムが動作状態(活線状態)でコネクタ23と13aを切り離して、修理あるいは交換を行うことができる。

【0045】

次に、図2に基づいてこの実施例の動作を説明する。図2は、コネクタ13aと23を勘合させた瞬間の、各信号の状態を表した波形図である。なお、図1に示すように、コネクタ13aと23の勘合前は、スイッチ41aはオフであるとする。

【0046】

図2において、(A)〜(C)は共通電位点ライン22、信号入力ライン21、外部電源ライン20の接点の接続状態を表した図である。コネクタ13aと23の各接点の長さは等しいので、勘合したときのコネクタの傾きなどによって接続される順番が異なる。このため、接点が接続する順番は予測あるいは制御できない。図2では、時刻t10〜t12で共通電位点ライン22、信号入力ライン21、外部電源ライン20がこの順で接続される。

【0047】

(D)は入力回路11aにおける入力端子SIGの電圧の推移を表した波形図である。時刻t11で信号入力ライン21が入力端子SIGに接続されるので、入力端子SIGの電圧は高レベルになる。

【0048】

(E)は入力回路11aの電源電圧の推移を表した波形図である。時刻t11で入力回路11aの入力端子電圧が上昇するので、ダイオード15aがオンになる。このため、時刻t11で入力回路11aの電源電圧は上昇する。

【0049】

(F)はスイッチ41aの状態である。(E)に示したように時刻t11で入力回路11aの電源電圧は上昇するが、コネクタ13aを介して電源が供給されていないので、スイッチ41aはオフ状態を維持する。

【0050】

(G)はダイオード15aに流れる電流の推移図である。時刻t11ではスイッチ41aはオフなので、バイパスコンデンサ12aは入力回路11aの電源端子から切り離されている。従って、時刻t11でダイオード15aはオンになるが、電流はほとんど流れない。

【0051】

時刻t12で外部電源ライン20の接点が接続され、コネクタ13aから電源が供給される。(E)に示すように入力回路11aの電源電圧は外部電源の電圧値まで徐々に上昇する。コネクタ13aから電源が供給されるので、電源電圧検出部52aはスイッチ41aをオンする。バイパスコンデンサ12aは入力回路11aの電源端子VD、COMに接続されるが、バイパスコンデンサ12aの充電電流は外部電源から供給されるので、(G)に示すようにダイオード15aにはほとんど電流は流れない。

【0052】

(H)は入力回路11bの入力電圧の推移図である。(G)に示したようにダイオード15aにはほとんど電流が流れないので、信号入力ライン21にも過電流は流れず、グリッジは発生しない。このため、I/Oモジュール40aが挿入されても、入力回路11bの入力電圧が変化することはない。

【0053】

図3に、本発明の他の実施例を示す。この実施例は図7従来例に対応するものである。なお、図1、図7と同じ要素には同一符号を付し、説明を省略する。また、図1と異なる点のみ説明する。

【0054】

図3において、50aはI/Oモジュールであり、入力回路11a、コネクタ13a、スイッチ51a、および電源電圧検出部52aで構成される。入力回路11aの電源端子VDはコネクタ13aに接続され、電源端子COMはスイッチ51aの一端に接続される。このスイッチ51aの他端は共通電位点に接続される。電源電圧検出部52aは外部電源ライン20から供給される電源電圧を監視し、電源が供給されるとスイッチ51aをオンにして入力回路11bへ電源を供給する経路を導通させ、電源が供給されていないと、スイッチ51aをオフにしてこの経路を遮断する。

【0055】

50bはI/Oモジュールであり、入力回路11b、コネクタ13b、スイッチ51b、および電源電圧検出部52bで構成される。I/Oモジュール50bは、I/Oモジュール50aと同じ構成を有している。

【0056】

次に、図4に基づいてこの実施例の動作を説明する。なお、(A)〜(H)は図2と同じ点の波形を表している。図4において、(A)〜(C)に示すように、共通電位点ライン22、信号入力ライン21、外部電源ライン20はそれぞれ時刻t13、t14、t15で入力回路11aに接続される。

【0057】

時刻t14で、(D)に示すように入力回路11aの入力端子SIGの電圧は高レベルに遷移する。このため、ダイオード15aがオンになり、(E)に示すように入力回路11aの電源電圧は上昇する。しかし、コネクタ13aから電源が供給されていないので、(F)に示すように、スイッチ51aは引き続きオフ状態を維持する。入力回路11aの電源供給経路は遮断されるので、入力回路11aには電源電流が流れない。このため、(G)に示すように、ダイオード15aにはほとんど電流は流れない。

【0058】

時刻t15でコネクタ13aを介して外部電源が供給されると、(E)に示すように入力回路11aの電源電圧は上昇する。コネクタ13aから電源が供給されるのでスイッチ51aがオンになり、入力回路11aには電源電流が供給される。入力回路11aの動作電流は外部電源から供給されるので、(G)に示すように、ダイオード15aに流れる電流はほぼ0になる。

【0059】

この場合も、ダイオード15aには電流が流れないので、信号入力ライン21に過電流が流れることはなくなる。このため、グリッジが発生することはなく、(H)に示すように、入力回路11bの入力端子の電圧が変動することはない。

【0060】

なお、図1、図3実施例において、I/Oモジュール40aと40b、50aと50bは同一構成としたが、必ずしも同じ構成でなくてもよい。同じ信号入力ラインに接続されるものであれば、構成が異なっていてもよい。また、必ずしも2重化システムを構成するI/Oモジュールでなくてもよい。

【0061】

また、これらの実施例ではI/Oモジュール40a、40b、50a、50bは入力された信号のレベルを検出してその結果を出力するレベル検出部を内蔵する構成としたが、必ずしもこの構成に限定されない。電圧信号が入力され、この電圧信号処理して、それに対応する信号を出力する構成であればよい。

【0062】

また、図1実施例ではバイパスコンデンサ12a(12b)と直列にスイッチを挿入し、図3実施例では入力回路11a(11b)に直列にスイッチを挿入する構成としたが、必ずしもこの構成に限定されることはない。図1実施例ではバイパスコンデンサ12a(12b)を入力回路11a(11b)の電源端子に接続しまた切り離し、図3実施例では入力回路11a(11b)に電源を供給する経路を導通、遮断する構成であればよい。

【0063】

さらに、スイッチ41a、41b、51a、51bとして、メカニカルスイッチ、半導体スイッチ、トランジスタなどを用いることができる。

【符号の説明】

【0064】

11a、11b 入力回路

12a、12b バイパスコンデンサ

13a、13b、23、24 コネクタ

15a、16a、15b、16b ダイオード

20 外部電源ライン

21 信号入力ライン

22 共通電位点ライン

40a、40b、50a、50b I/Oモジュール

41a、41b、51a、51b スイッチ

42a、42b、52a、52b 電源電圧検出部

【技術分野】

【0001】

本発明は、コネクタを勘合させてシステムに接続したときに、グリッジを発生することがないI/Oモジュールに関し、特に2重化されたシステムに用いて好適なI/Oモジュールに関するものである。

【背景技術】

【0002】

プロセス制御システムでは、I/Oモジュールを介してプロセス量を取り込み、またプロセスに制御量を出力する。図5に、オンラインメンテナンスが可能な、2重化されたI/Oモジュールの構成を示す。

【0003】

図5において、10aはI/Oモジュールであり、入力回路11a、この入力回路11aの電源端子VDとCOMに接続されるバイパスコンデンサ12a、およびコネクタ13aで構成される。入力回路11aはレベル検出部14a、およびこのレベル検出部14aの入力端子と一方の電源端子、入力端子と他方の電源端子との間に接続されたダイオード15a、16aで構成される。レベル検出部14aの電源端子および入力端子は入力回路11aの電源端子VD、COMと入力端子SIGと同じなので、ダイオード15a、15bは入力回路11aの入力端子SIGと電源端子VD間、入力端子SIGと電源端子COM間に接続される。なお、ダイオード15a、16aは、静電気保護の目的で挿入される。

【0004】

コネクタ13aの接点は、入力回路11aの電源端子VDとCOM、入力端子SIGに接続される。I/Oモジュール10aは、外部電源ライン20から供給される電源で動作し、信号入力ライン21を介して信号が入力される。

【0005】

20、21、22はそれぞれ外部電源ライン、信号入力ライン、共通電位点ラインであり、これらのライン20〜22はコネクタ23に接続されている。以降、外部電源ライン20と共通電位点ライン22を合わせて電源ラインと称する。

【0006】

入力回路11aの電源端子VD、COMと入力端子SIGは、コネクタ13aと23を介して電源ライン20、22と信号入力ライン21に接続される。なお、コネクタ13aと23は本来勘合するが、この図では切り離されている。

【0007】

10bはI/Oモジュールであり、I/Oモジュール10aとで2重化システムを構成している。I/Oモジュール10bはI/Oモジュール10aと同じ構成を有しており、入力回路11b、バイパスコンデンサ12b、コネクタ13bで構成される。また、入力回路11bは、レベル検出部14bおよびこのレベル検出部14bの入力端子と電源端子との間に接続されるダイオード15b、16bで構成される。I/Oモジュール10bは、電源ライン20、22から供給される外部電源で動作し、信号入力ライン21から信号が入力される。

【0008】

コネクタ24には電源ライン20、22および信号入力ライン21が接続され、またコネクタ13bと勘合している。電源ライン20、22と入力回路11bの電源端子VD、COM、信号入力ライン21と入力端子SIGは、コネクタ24、13bを介して接続される。

【0009】

このような構成において、コネクタ23と13aを勘合させると、I/Oモジュール10bは制御側I/Oモジュール、I/Oモジュール10aは待機側I/Oモジュールとして動作する。制御側I/Oモジュール10bに異常が発生すると、待機側I/Oモジュール10aが制御側I/Oモジュールとして動作する。

【0010】

また、待機側I/OモジュールであるI/Oモジュール10aは動作していないので、コネクタ23と13aを切り離しても、システムの動作に支障を生じない。従って、システムを動作させながらI/Oモジュール10aを抜き取り、交換することができる。すなわち、オンラインメンテナンスが可能になる。

【0011】

プロセス制御システムは、システムの継続性を担保するために24時間稼働させなければならない。このため、I/Oモジュール10a、10bを用いて2重化することにより、一方のI/Oモジュールに故障が発生すると他方のI/Oモジュールにシームレスで切り替え、またシステムを稼働させながら、故障したI/Oモジュールを交換できるようにしている。

【0012】

図7に、他の2重化されたI/Oモジュールの構成を示す。なお、図5と同じ要素には同一符号を付し、説明を省略する。

【0013】

図7において、30a、30bは2重化されたI/Oモジュールであり、それぞれコネクタ13a、13bおよび入力回路11a、11bで構成される。I/Oモジュール30aはコネクタ13a、23を介して電源ライン20および22、信号入力ライン21に接続され、I/Oモジュール30bはコネクタ13b、24を介してこれらのラインに接続される。この図では、コネクタ13aと23は切り離されている。

【0014】

図5と比較すると、I/Oモジュール30a、30bにはバイパスコンデンサ12a、12bが内蔵されていない点が異なる。動作は図5と同じなので、説明を省略する。

【0015】

特許文献1には、活線状態でモジュールを挿抜できるプロセス制御コントローラが記載されている。特許文献1では、電源コネクタと通信コネクタを分離し、電源用ショートピース、GND用ショートピースを介して複数のI/Oモジュールに電源を供給するようにする。

【先行技術文献】

【特許文献】

【0016】

【特許文献1】特開2000−330603号公報

【発明の概要】

【発明が解決しようとする課題】

【0017】

しかしながら、このようなI/Oモジュールには、次のような課題があった。

図6に、コネクタ13aと23を勘合させて、図5構成のI/Oモジュール10aを電源ライン20および22、信号入力ライン21に接続した時の状態を示す。コネクタ13a、23の各接点は同じ長さを有しているので、挿入時のコネクタの傾き等によってどの接点から接続されるかが変わる。接続される接点の順番は予測、あるいは制御することができない。

【0018】

図6において、(A)〜(C)に示すように、時刻t1〜t3で共通電位点ライン22の接点、信号入力ライン21の接点、外部電源ライン20の接点がこの順でI/Oモジュール10aに接続される。時刻t2で入力回路11aの入力端子SIGと信号入力ライン21が接続されるので、このライン上の信号レベルが高レベルであると、(D)に示すように、入力回路11aの入力信号電圧は時刻t2で高レベルに遷移する。

【0019】

時刻t2では入力回路11aに外部から電源が供給されていないので、ダイオード15aはオンになる。このため、(F)に示すように、信号入力ライン21からダイオード15aに大きな電流が流れる。バイパスコンデンサ12aはこの電流によって充電されるので、(E)に示すように入力回路11aの電源電圧は上昇する。

【0020】

時刻t3で入力回路11aに電源が供給されると、入力回路11aの電源電圧は更に上昇し、やがて安定する。なお、(D)、(E)で電圧が徐々に上昇しているのは、バイパスコンデンサ12aを充電しているためである。

【0021】

(F)に示すように、時刻t2でダイオード15aに大きな電流が流れるが、この電流は信号入力ライン21から供給される。この電流のために信号入力ライン21で電圧降下が発生し、(G)に示すように、同じ信号入力ライン21に繋がっている入力回路11bの入力信号電圧が変化するグリッジが発生する。このため、入力回路10bがこの変化を検出して誤信号を出力してしまうという課題があった。

【0022】

このような誤動作は、バイパスコンデンサを内蔵しない図7のI/Oモジュールでも発生する。

【0023】

図8に、図7構成のI/Oモジュールでコネクタ13aと23が勘合した時の状態を示す。(A)〜(C)に示すように、時刻t4〜t6で共通電位点ライン22の接点、信号入力ライン21の接点、外部電源ライン20の接点がこの順でI/Oモジュール10aに接続される。時刻t5で入力回路11aの入力端子SIGと信号入力ライン21が接続されるので、このライン上の信号レベルが高レベルであると、(D)に示すように、入力回路11aの入力信号電圧は時刻t5で高くなり、ダイオード15aがオンになる。

【0024】

入力回路11aにはダイオード15aから電流が供給されるので、(F)に示すようにダイオード15aには電流が流れ、入力回路11aの電源電圧が高くなる。

【0025】

ダイオード15aに流れる電流は信号入力ライン21から供給されるので、信号入力ライン21に電流が流れて電圧降下が発生し、(G)に示すように同じ信号入力ライン21に繋がっている入力回路11bの入力端子の電圧が変化して誤差が発生する。このため、レベル検出部14bがこの変化を検出して誤信号を出力してしまう。

【0026】

このように、コネクタの接点の接続順によっては、信号入力ライン21に電流が流れて電圧降下が発生し、同じ信号入力ライン21に接続されている入力回路11bの入力電圧にグリッジが発生して誤信号を出力してしまうことがまれに発生するという課題があった。このようなことが発生すると、最悪の場合にはシステムがシャットダウンしてしまうという課題もあった。

【0027】

特許文献1記載の発明は電源コネクタと通信コネクタを分離し、電源用ショートピース、GND用ショートピースを介して複数のI/Oモジュールに電源を供給するので、接続する順番を制御することができる。しかし、マウントベースの構造が複雑になり、かつモジュールに電源を供給するためにはショートピースを接続しなければならず、操作が煩雑になるという課題があった。

【0028】

本発明の目的は、接続時に信号入力ラインに電流が流れることを防止して、グリッジが発生することがないI/Oモジュールを実現することにある。

【課題を解決するための手段】

【0029】

このような課題を達成するために、本発明のうち請求項1記載の発明は、

コネクタを介して電源ラインおよび信号入力ラインに接続され、前記電源ラインから電源が供給されると共に、前記信号入力ライン上の信号を処理してそれに対応する信号を出力するI/Oモジュールにおいて、

前記信号入力ライン上の信号が入力され、この信号を処理すると共に、その入力端子と電源端子との間にダイオードが接続される入力回路と、

バイパスコンデンサと、

前記バイパスコンデンサを前記入力回路の電源端子に接続し、また切り離すスイッチと、

前記コネクタを介して供給される電源の電圧を監視し、前記スイッチを制御して、前記電源が供給されていると前記バイパスコンデンサを前記入力回路の電源端子に接続し、前記電源が供給されていないと前記バイパスコンデンサを前記入力回路の電源端子から切り離す電源電圧検出部と、

を具備したものである。I/Oモジュールを挿入したときに、信号入力ラインに過電流が流れないので、グリッジが発生することがない。

【0030】

請求項2記載の発明は、

コネクタを介して電源ラインおよび信号入力ラインに接続され、前記電源ラインから電源が供給されると共に、前記信号入力ライン上の信号を処理してそれに対応する信号を出力するI/Oモジュールにおいて、

前記信号入力ライン上の信号が入力され、この信号を処理すると共に、その入力端子と電源端子との間にダイオードが接続される入力回路と、

前記入力回路に電源を供給する経路を導通または遮断するスイッチと、

前記コネクタを介して供給される電源の電圧を監視し、前記スイッチを制御して、前記電源が供給されていると前記入力回路に電源を供給する経路を導通させ、前記電源が供給されていないと前記経路を遮断する電源電圧検出部と、

を具備したものである。I/Oモジュールを挿入したときに、信号入力ラインに過電流が流れないので、グリッジが発生することがない。

【0031】

請求項3記載の発明は、

請求項1若しくは請求項2記載のI/Oモジュールを2台用い、一方を制御側I/Oモジュール、他方を待機側I/Oモジュールとしたものである。待機側I/Oモジュールを挿入したときにグリッジが発生しないので、制御側I/Oモジュールが誤信号を検出することがない

【発明の効果】

【0032】

本発明によれば以下のような効果がある。

請求項1、2、および3の発明によれば、コネクタを介して供給される電源の電圧を監視し、電源が供給されるとバイパスコンデンサを入力回路の電源端子に接続し、また入力回路に電源を供給する経路を導通させ、電源が供給されていないとバイパスコンデンサを切り離し、また入力回路に電源を供給する経路を遮断するようにした。また、このI/Oモジュールを用いて2重化システムを構成した。

【0033】

I/Oモジュールをコネクタに挿入したときに、電源ラインよりも先に信号入力ラインが接続されてダイオードがオンになり、信号入力ラインに大きな電流が流れることを防止できる。このため、電圧降下に起因するグリッジが信号入力ラインに発生しないので、同じ信号入力ラインに接続されている他のI/Oモジュールが誤動作することがなくなるという効果がある。

【0034】

また、2重化システムの場合、待機側I/Oモジュールを挿入するときにグリッジが発生しないので、制御側I/Oモジュールが誤動作することがなくなる。このため、信頼性が高い2重化システムを構築できるという効果もある。

【図面の簡単な説明】

【0035】

【図1】本発明の一実施例を示した構成図である。

【図2】図1実施例の動作を説明するための特性図である。

【図3】本発明の他の実施例を示した構成図である。

【図4】図3実施例の動作を説明するための特性図である。

【図5】従来の2重化されたI/Oモジュールの構成図である。

【図6】図5従来例の動作を説明するための特性図である。

【図7】従来の2重化されたI/Oモジュールの構成図である。

【図8】図7従来例の動作を説明するための特性図である。

【発明を実施するための形態】

【0036】

以下本発明を、図面を用いて詳細に説明する。図1は本発明に係るI/Oモジュールの一実施例を示した構成図である。この実施例は、図5従来例に対応するものである。なお、図5と同じ要素には同一符号を付し、説明を省略する。

【0037】

図1において、40aはI/Oモジュールであり、入力回路11a、バイパスコンデンサ12a、コネクタ13a、スイッチ41a、電源電圧検出部42aで構成される。また、入力回路11aは、レベル検出部14aとこのレベル検出部14aの入力端子と電源端子および共通電位点との間に接続されたダイオード15a、16aで構成される。入力回路11aとレベル検出部14aの電源端子、入力端子は共通なので、ダイオード15a、15bは、入力回路11aの入力端子SIGと電源端子VD、COM間に接続される。

【0038】

バイパスコンデンサ12aの一端は入力回路11aの電源端子VDに接続され、他端はスイッチ41aの一端に接続される。このスイッチ41aの他端は、入力回路11aの電源端子COMに接続される。スイッチ41aを操作することにより、バイパスコンデンサ12aを入力回路11aの電源端子に接続し、また切り離すことができる。

【0039】

入力回路11aは、コネクタ13aおよび23を介して電源ライン20および22、信号入力ライン21に接続される。コネクタ13aと23が勘合されると、入力回路11aには電源ライン20、22から電源が供給され、また信号入力ライン21から信号が入力される。図1では、コネクタ13aと23は切り離された状態になっている。

【0040】

コネクタ13aと23が勘合されると入力回路11aに電源が供給される。入力回路11aは信号入力ライン21上の信号レベルを検出し、この検出結果を上位システムに送信する。なお、上位システムに送信するための構成は本発明と直接関係がないので、記載を省略している。

【0041】

電源電圧検出部42aには、コネクタ13aを介して供給される電源電圧が入力される。電源電圧検出部42aは入力された電源電圧を監視し、この監視結果に基づいてスイッチ41aのオンオフを制御する。すなわち、電源電圧検出部42aは、コネクタ13aを介して電源が供給されているとスイッチ41aをオンにしてバイパスコンデンサ12aを入力回路11aの電源端子に接続し、供給されていないとスイッチ41aをオフにしてバイパスコンデンサ12aを切り離す。コネクタ13aの接点の電圧を監視することにより、電源が供給されているか否かを判定することができる。

【0042】

40bはI/Oモジュールであり、入力回路11b、バイパスコンデンサ12b、コネクタ13b、スイッチ41b、電源電圧検出部42bで構成される。また、入力回路11bには、入力回路11bの入力端子SIGと電源端子VD、COM間には、ダイオード15b、16bが接続される。

【0043】

I/Oモジュール40bは、I/Oモジュール40aと同じ構成を有している。すなわち、入力回路11bは信号入力ライン21上の信号レベルを検出し、この検出結果を上位システムに送信する。また、電源電圧検出部42bはコネクタ13bから供給される電源の電圧を監視し、この電源が供給されているとスイッチ41bをオンにしてバイパスコンデンサ12bを入力回路11bの電源端子に接続し、供給されていないとスイッチ41bをオフにしてバイパスコンデンサ12bを切り離す。図1ではコネクタ13bと24は勘合状態になっている。

【0044】

コネクタ13aと23が勘合されると、I/Oモジュール40aと40bで2重化システムが構成される。すなわち、I/Oモジュール40bは制御側I/Oモジュールとして動作し、I/Oモジュール40aは待機側I/Oモジュールとして動作する。待機側I/Oモジュールはシステムの動作には関係しないので、システムが動作状態(活線状態)でコネクタ23と13aを切り離して、修理あるいは交換を行うことができる。

【0045】

次に、図2に基づいてこの実施例の動作を説明する。図2は、コネクタ13aと23を勘合させた瞬間の、各信号の状態を表した波形図である。なお、図1に示すように、コネクタ13aと23の勘合前は、スイッチ41aはオフであるとする。

【0046】

図2において、(A)〜(C)は共通電位点ライン22、信号入力ライン21、外部電源ライン20の接点の接続状態を表した図である。コネクタ13aと23の各接点の長さは等しいので、勘合したときのコネクタの傾きなどによって接続される順番が異なる。このため、接点が接続する順番は予測あるいは制御できない。図2では、時刻t10〜t12で共通電位点ライン22、信号入力ライン21、外部電源ライン20がこの順で接続される。

【0047】

(D)は入力回路11aにおける入力端子SIGの電圧の推移を表した波形図である。時刻t11で信号入力ライン21が入力端子SIGに接続されるので、入力端子SIGの電圧は高レベルになる。

【0048】

(E)は入力回路11aの電源電圧の推移を表した波形図である。時刻t11で入力回路11aの入力端子電圧が上昇するので、ダイオード15aがオンになる。このため、時刻t11で入力回路11aの電源電圧は上昇する。

【0049】

(F)はスイッチ41aの状態である。(E)に示したように時刻t11で入力回路11aの電源電圧は上昇するが、コネクタ13aを介して電源が供給されていないので、スイッチ41aはオフ状態を維持する。

【0050】

(G)はダイオード15aに流れる電流の推移図である。時刻t11ではスイッチ41aはオフなので、バイパスコンデンサ12aは入力回路11aの電源端子から切り離されている。従って、時刻t11でダイオード15aはオンになるが、電流はほとんど流れない。

【0051】

時刻t12で外部電源ライン20の接点が接続され、コネクタ13aから電源が供給される。(E)に示すように入力回路11aの電源電圧は外部電源の電圧値まで徐々に上昇する。コネクタ13aから電源が供給されるので、電源電圧検出部52aはスイッチ41aをオンする。バイパスコンデンサ12aは入力回路11aの電源端子VD、COMに接続されるが、バイパスコンデンサ12aの充電電流は外部電源から供給されるので、(G)に示すようにダイオード15aにはほとんど電流は流れない。

【0052】

(H)は入力回路11bの入力電圧の推移図である。(G)に示したようにダイオード15aにはほとんど電流が流れないので、信号入力ライン21にも過電流は流れず、グリッジは発生しない。このため、I/Oモジュール40aが挿入されても、入力回路11bの入力電圧が変化することはない。

【0053】

図3に、本発明の他の実施例を示す。この実施例は図7従来例に対応するものである。なお、図1、図7と同じ要素には同一符号を付し、説明を省略する。また、図1と異なる点のみ説明する。

【0054】

図3において、50aはI/Oモジュールであり、入力回路11a、コネクタ13a、スイッチ51a、および電源電圧検出部52aで構成される。入力回路11aの電源端子VDはコネクタ13aに接続され、電源端子COMはスイッチ51aの一端に接続される。このスイッチ51aの他端は共通電位点に接続される。電源電圧検出部52aは外部電源ライン20から供給される電源電圧を監視し、電源が供給されるとスイッチ51aをオンにして入力回路11bへ電源を供給する経路を導通させ、電源が供給されていないと、スイッチ51aをオフにしてこの経路を遮断する。

【0055】

50bはI/Oモジュールであり、入力回路11b、コネクタ13b、スイッチ51b、および電源電圧検出部52bで構成される。I/Oモジュール50bは、I/Oモジュール50aと同じ構成を有している。

【0056】

次に、図4に基づいてこの実施例の動作を説明する。なお、(A)〜(H)は図2と同じ点の波形を表している。図4において、(A)〜(C)に示すように、共通電位点ライン22、信号入力ライン21、外部電源ライン20はそれぞれ時刻t13、t14、t15で入力回路11aに接続される。

【0057】

時刻t14で、(D)に示すように入力回路11aの入力端子SIGの電圧は高レベルに遷移する。このため、ダイオード15aがオンになり、(E)に示すように入力回路11aの電源電圧は上昇する。しかし、コネクタ13aから電源が供給されていないので、(F)に示すように、スイッチ51aは引き続きオフ状態を維持する。入力回路11aの電源供給経路は遮断されるので、入力回路11aには電源電流が流れない。このため、(G)に示すように、ダイオード15aにはほとんど電流は流れない。

【0058】

時刻t15でコネクタ13aを介して外部電源が供給されると、(E)に示すように入力回路11aの電源電圧は上昇する。コネクタ13aから電源が供給されるのでスイッチ51aがオンになり、入力回路11aには電源電流が供給される。入力回路11aの動作電流は外部電源から供給されるので、(G)に示すように、ダイオード15aに流れる電流はほぼ0になる。

【0059】

この場合も、ダイオード15aには電流が流れないので、信号入力ライン21に過電流が流れることはなくなる。このため、グリッジが発生することはなく、(H)に示すように、入力回路11bの入力端子の電圧が変動することはない。

【0060】

なお、図1、図3実施例において、I/Oモジュール40aと40b、50aと50bは同一構成としたが、必ずしも同じ構成でなくてもよい。同じ信号入力ラインに接続されるものであれば、構成が異なっていてもよい。また、必ずしも2重化システムを構成するI/Oモジュールでなくてもよい。

【0061】

また、これらの実施例ではI/Oモジュール40a、40b、50a、50bは入力された信号のレベルを検出してその結果を出力するレベル検出部を内蔵する構成としたが、必ずしもこの構成に限定されない。電圧信号が入力され、この電圧信号処理して、それに対応する信号を出力する構成であればよい。

【0062】

また、図1実施例ではバイパスコンデンサ12a(12b)と直列にスイッチを挿入し、図3実施例では入力回路11a(11b)に直列にスイッチを挿入する構成としたが、必ずしもこの構成に限定されることはない。図1実施例ではバイパスコンデンサ12a(12b)を入力回路11a(11b)の電源端子に接続しまた切り離し、図3実施例では入力回路11a(11b)に電源を供給する経路を導通、遮断する構成であればよい。

【0063】

さらに、スイッチ41a、41b、51a、51bとして、メカニカルスイッチ、半導体スイッチ、トランジスタなどを用いることができる。

【符号の説明】

【0064】

11a、11b 入力回路

12a、12b バイパスコンデンサ

13a、13b、23、24 コネクタ

15a、16a、15b、16b ダイオード

20 外部電源ライン

21 信号入力ライン

22 共通電位点ライン

40a、40b、50a、50b I/Oモジュール

41a、41b、51a、51b スイッチ

42a、42b、52a、52b 電源電圧検出部

【特許請求の範囲】

【請求項1】

コネクタを介して電源ラインおよび信号入力ラインに接続され、前記電源ラインから電源が供給されると共に、前記信号入力ライン上の信号を処理してそれに対応する信号を出力するI/Oモジュールにおいて、

前記信号入力ライン上の信号が入力され、この信号を処理すると共に、その入力端子と電源端子との間にダイオードが接続される入力回路と、

バイパスコンデンサと、

前記バイパスコンデンサを前記入力回路の電源端子に接続し、また切り離すスイッチと、

前記コネクタを介して供給される電源の電圧を監視し、前記スイッチを制御して、前記電源が供給されていると前記バイパスコンデンサを前記入力回路の電源端子に接続し、前記電源が供給されていないと前記バイパスコンデンサを前記入力回路の電源端子から切り離す電源電圧検出部と、

を具備したことを特徴とするI/Oモジュール。

【請求項2】

コネクタを介して電源ラインおよび信号入力ラインに接続され、前記電源ラインから電源が供給されると共に、前記信号入力ライン上の信号を処理してそれに対応する信号を出力するI/Oモジュールにおいて、

前記信号入力ライン上の信号が入力され、この信号を処理すると共に、その入力端子と電源端子との間にダイオードが接続される入力回路と、

前記入力回路に電源を供給する経路を導通または遮断するスイッチと、

前記コネクタを介して供給される電源の電圧を監視し、前記スイッチを制御して、前記電源が供給されていると前記入力回路に電源を供給する経路を導通させ、前記電源が供給されていないと前記経路を遮断する電源電圧検出部と、

を具備したことを特徴とするI/Oモジュール。

【請求項3】

請求項1若しくは請求項2記載のI/Oモジュールを2台用い、一方を制御側I/Oモジュール、他方を待機側I/Oモジュールとしたことを特徴とする2重化システム。

【請求項1】

コネクタを介して電源ラインおよび信号入力ラインに接続され、前記電源ラインから電源が供給されると共に、前記信号入力ライン上の信号を処理してそれに対応する信号を出力するI/Oモジュールにおいて、

前記信号入力ライン上の信号が入力され、この信号を処理すると共に、その入力端子と電源端子との間にダイオードが接続される入力回路と、

バイパスコンデンサと、

前記バイパスコンデンサを前記入力回路の電源端子に接続し、また切り離すスイッチと、

前記コネクタを介して供給される電源の電圧を監視し、前記スイッチを制御して、前記電源が供給されていると前記バイパスコンデンサを前記入力回路の電源端子に接続し、前記電源が供給されていないと前記バイパスコンデンサを前記入力回路の電源端子から切り離す電源電圧検出部と、

を具備したことを特徴とするI/Oモジュール。

【請求項2】

コネクタを介して電源ラインおよび信号入力ラインに接続され、前記電源ラインから電源が供給されると共に、前記信号入力ライン上の信号を処理してそれに対応する信号を出力するI/Oモジュールにおいて、

前記信号入力ライン上の信号が入力され、この信号を処理すると共に、その入力端子と電源端子との間にダイオードが接続される入力回路と、

前記入力回路に電源を供給する経路を導通または遮断するスイッチと、

前記コネクタを介して供給される電源の電圧を監視し、前記スイッチを制御して、前記電源が供給されていると前記入力回路に電源を供給する経路を導通させ、前記電源が供給されていないと前記経路を遮断する電源電圧検出部と、

を具備したことを特徴とするI/Oモジュール。

【請求項3】

請求項1若しくは請求項2記載のI/Oモジュールを2台用い、一方を制御側I/Oモジュール、他方を待機側I/Oモジュールとしたことを特徴とする2重化システム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2012−252483(P2012−252483A)

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願番号】特願2011−124069(P2011−124069)

【出願日】平成23年6月2日(2011.6.2)

【出願人】(000006507)横河電機株式会社 (4,443)

【Fターム(参考)】

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願日】平成23年6月2日(2011.6.2)

【出願人】(000006507)横河電機株式会社 (4,443)

【Fターム(参考)】

[ Back to top ]