ICデバイス用ソケット

【課題】ICデバイスの低電圧化、高速化に伴う電源の不安定化を効果的に抑制し得る構造を備えたICデバイス用ソケットを提供する。

【解決手段】ICデバイス用ソケットは、絶縁性材料からなる基材の第1面と第2面の間の空間内にコンデンサを構成するよう配置された誘電体層と、その両面に形成された電源層2104及びGND層2201を備える。電源層2104及びGND層2201のうち少なくとも電源層2104の、その最外周によって規定される面積は、第1面の最外周によって規定される面積よりも小さく設定されており、電源層2104及びGND層2201間のキャパシタンスは、第1面から第2面を見たときに電源層2104とGND層2201の重なり合う部分ARの面積を変えることにより制御される。

【解決手段】ICデバイス用ソケットは、絶縁性材料からなる基材の第1面と第2面の間の空間内にコンデンサを構成するよう配置された誘電体層と、その両面に形成された電源層2104及びGND層2201を備える。電源層2104及びGND層2201のうち少なくとも電源層2104の、その最外周によって規定される面積は、第1面の最外周によって規定される面積よりも小さく設定されており、電源層2104及びGND層2201間のキャパシタンスは、第1面から第2面を見たときに電源層2104とGND層2201の重なり合う部分ARの面積を変えることにより制御される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、CPU、メモリ等の半導体集積回路(以下、ICという)デバイスの検査に使用されるICデバイス用ソケットに関し、特に、半導体パッケージテスト用のコンデンサ機能を具備したICデバイス用ソケットに関するものである。

【背景技術】

【0002】

BGA(ボールグリッドアレイ)デバイス等のICデバイスの信号伝送特性等の評価試験を行う際、そのICデバイスの端子それぞれに電気的に接続可能な接触子を備えたソケット(以下、ICデバイス用ソケットという)が使用される。近年、ICデバイスの扱う信号は、その処理速度の高速化に伴って高周波化している。信号の高速化に対応して、ICデバイス用ソケットも高速信号を伝送できることが求められている。また、電子機器の消費電力低減のためにICデバイスの動作電源の低電圧化もすすんでいる。このようにICデバイスの安定した高速動作には、該ICデバイスに対して安定的に電源が供給される必要である。なお、ICデバイスの高速化と低電圧化により、電源の安定供給がますます重要かつ難しくなっている。

【0003】

ICデバイスの高速動作時も安定的に電源が供給されるためには、電源とグラウンドのインピーダンスを高い周波数領域まで低く抑える必要がある。ICデバイス用ソケットにおいては、当該ICデバイス用ソケットに含まれる導電性コンタクトピンの自己インダクタンスを下げることが好ましい。このため、一般に導電性コンタクトピンは太くかつ短いものが好ましいとされている。

【0004】

高速信号伝送を志向するICデバイス用ソケットに対応する他の方法が、特許文献1に記載されている。特許文献1には、「本発明のLSIソケット101は、プリント基板102、ポゴピン103、ポゴピン支持筐体部104の3つの部品から構成されている。プリント基板102には、印加される電圧値が異なる第1の電源ピン105と第2の電源ピン106、GNDピン107、信号ピン108用となるポゴピン103がそれぞれ挿入される複数のスルーホール109が設けられており、信号ピン108が貫通するスルーホール109以外の全てのスルーホール109内面にメッキ層116が形成されている」と記載されている。

【0005】

特許文献2には、「一般的に、電源用プローブのバイパス用チップコンデンサは、検査用ソケット下面側の配線基板上において、電気的な距離ができるだけデバイスに近い配線パターン上に実装される」及び「チップコンデンサを被検査デバイスの直下であり検査ソケットの上部である位置に実装する事が必要となった」と記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】国際公開第2005/006003号パンフレット

【特許文献2】特開2009−85948号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

発明者らは、従来のICデバイス用ソケットについて検討した結果、以下のような課題を発見した。すなわち、上述のように導電性コンタクトピンは太くかつ短いものが好ましいとされている。ところが、ICデバイスの端子間のピッチの狭小化によって導電性コンタクトピンの太さは必然的に制限される。一方、導電性コンタクトピンは高価であることから、繰り返し使用により信頼性が低下した導電性コンタクトピンは随時交換されることが一般的である。したがって、導電性コンタクトピンの交換時の作業性を考慮すると該導電性コンタクトピンは一定以上の長さを有する必要がある。また、導電性コンタクトピンにスプリングプローブを用いる場合、プローブ長が短いと、プランジャーの稼動長が短くなり、基板や半導体パッケージが平坦でない場合にICデバイス側の端子と該スプリングプローブとの良好な接触状態が確保できなくなる。

【0008】

或いは、ICデバイス用ソケットの筐体や当該ICデバイス用ソケットに組み込まれる導電性コンタクトピンの電源用ピンとグラウンド用ピンに直接コンデンサを接続することにより信号ピンのインダクタンスによるインピーダンスの上昇を、コンデンサのキャパシタンスにより補償し、インピーダンスを下げていた。しかしながら、ICデバイス用ソケットの筐体や導電性コンタクトピンに直接コンデンサを接続すると、該ICデバイス用ソケットが占める体積が大きくなる。この場合、ICデバイス用ソケットの導電性コンタクトピンを高密度に配置することの妨げとなる虞がある。また、ICデバイス用ソケットの筐体や基板の周辺にコンデンサを配置・接続できたとしても、導電性コンタクトピンから数ミリメートル離れた位置にしかコンデンサを配置・接続場合がある。その場合、コンデンサまでの配線長による自己インダクタンスによってコンデンサの効果が有効に作用しない虞がある。

【0009】

本発明は、上述のような課題を解決するための構造を基本構造とし、具体的には、導電性コンタクトピンの交換作業性を低下させることなく、ICデバイスの検査時に、ソケット側の特性によりICデバイスを確実に動作させるための構造を備える。

【0010】

また、最近では、LSI等のICデバイスの低電圧化、高速化に伴い、ICデバイスを確実に動作させるためには電源の安定性がますます重要な役割を担っている(低電圧駆動のICデバイスでは、電源供給ネットワーク(以下、PDNという)をより低いインピーダンスに抑えることが重要であり、高速動作するICデバイスには、高い周波数までのPDNの低インピーダンス化が必要である)。このようにICデバイスを適切に動作させるためには、PDNの低インピーダンス化は不可欠となってきており、該PDN内の電源経路及びグラウンド経路の各インピーダンスを効果的に低減する必要がある。なお、上記PDNは、ICデバイスのパッケージ、検査装置等の回路基板(配線など)、これらICデバイスと回路基板との間に配置されるICデバイス用ソケットの各回路要素から構成されており、例えば本発明の基本構造では、後述のように、ソケット基板内に絶縁材料を介して電源層及びグラウンド層が包埋されており、これら電源層及びグラウンド層でコンデンサ機能を実現することにより、PDN全体を見たときの電源経路及びグラウンド経路の各インピーダンスがある程度低く抑えられ得る。

【0011】

一方、電源経路及びグラウンド経路の各インピーダンスの周波数依存性は、上記PDNを構成する回路要素の周波数応答と考えることができる。すなわち、導体はインダクタンスとして振る舞い、電源層、グラウンド層などの2つの導体の関係はキャパシタンスや相互インダクタンスと見なせるため、PDNは、複数のインダクタンス、キャパシタンス、抵抗からなる1つの回路として振る舞う。そのため、PDNにおける電源経路及びグラウンド経路の各インピーダンスは、周波数依存性が存在し、共振及び反共振に起因した特定の周波数におけるPDN全体のインピーダンスの増大が生じる可能性は否定できない。このようにPDNのインピーダンスが大きくなると、電源の安定性が損なわれるため、これを注意深くコントロールすることが重要になってきている。

【0012】

本発明は上述のような課題を解決するためになされたものであり、ICデバイスの低電圧化、高速化に伴う電源の不安定化を効果的に抑制し得る構造を備えたICデバイスソケットを提供することを目的としている。

【課題を解決するための手段】

【0013】

上述の課題を解決するため、本発明に係るICデバイス用ソケットは、基板と、複数の導電性コンタクトピンを備える。基板は、第1面と、該第1面に対向する第2面と、それぞれが該第1面と該第2面を連絡するとともにその内面に導電材料が設けられた複数の貫通孔とを有する。また、複数の導電性コンタクトピンは、それぞれの一部が複数の貫通孔のうちいずれかに挿入された状態で、該基板によって保持される。基板は、基材と、誘電体層と、第1及び第2導電層とを備える。

基材は、上記第1面と、上記第2面と、上記複数の貫通孔を有する。誘電体層は、複数の貫通孔と交差した状態で基材の第1面及び第2面の間に設けられており、該基材よりも高い誘電率を有する。第1及び第2導電層は、基材の第1面から第2面に向かう方向に沿って、誘電体層を挟んでいる。

【0014】

本願発明に係るICデバイス用ソケットでは、上述のように、コンデンサを構成する誘電体層及び導電層とそれらを包埋する基材とにより実質一体物の基板が形成される。そのため、各導電性コンタクトピンとコンデンサとの距離は極めて短くなり、その結果、当該ICデバイス用ソケットの性能を高めることができる。また、各導電性コンタクトピンは、基板に圧入等されることにより保持される。そのため、基板は各導電性コンタクトピンの支持体としても機能し、該各導電性コンタクトピンを支持するための他の部材が不要となる。

【0015】

特に、本発明に係るICデバイス用ソケットにおいて、第1及び第2導電体層のうち少なくともいずれかの、その最外周によって規定される面積は、第1面の最外周によって規定される面積よりも小さいことを特徴としている。

【0016】

上記複数の導電性コンタクトピンは、複数の第1導電性コンタクトピンと、該複数の第1導電性コンタクトピンとは接続状態の異なる複数の第2導電性コンタクトピンを含む。すなわち、複数の第1導電性コンタクトピンは、それぞれの一部が複数の貫通孔のうちいずれかに挿入され、該一部が対応する導電材料に接触している。複数の第2導電性コンタクトピンは、それぞれの一部が複数の貫通孔のうち別のいずれかに挿入され、第1及び第2導電体層に非接触となっている。この非接触状態は、該一部が対応する導電材料に対して非接触となっているか、又は、該対応する導電材料が第1及び第2導電層に対して非接触となっている状態を意味する。この場合、第1導電層は、対応する導電材料を介して複数の第1導電性コンタクトピンのうちいずれかに電気的に接続される。一方、第2導電層は、対応する導電材料を介して複数の第1導電性コンタクトピンのうち別のいずれかに電気的に接続される。

【0017】

以上のように本発明に係るICデバイス用ソケットにおける複数の第1導電性コンタクトピンのそれぞれは、第1導電層のみに電気的に接続される第1グループ(例えば電源ピンのグループ)と、第2導電層のみに電気的に接続される第2グループ(例えばグラウンドピンのグループ)とに区分される。また、第1及び第2導電層の何れにも電気的に接続されない複数の第2導電性コンタクトピンのそれぞれは信号ピンとして機能することになる。

【0018】

なお、本発明に係るICデバイス用ソケットにおいて、第1及び第2導電体層のうち少なくともいずれかの最外周は、基板(又は基材)の第1面の最外周よりも25μm以上内側に位置するのが好ましい。

【発明の効果】

【0019】

本発明に係るICデバイス用ソケットは、PDNの一回路要素として、交換可能な構造を有し、かつ、複数の導電性コンタクトピンを保持した基板内に任意に調節されたキャパシタンスを持つ。このように当該ICデバイス用ソケットをPDNの一回路要素に組み入れることにより、ICデバイスの低電圧化、高速化に伴う電源の不安定化が効果的に抑制され得る。

【図面の簡単な説明】

【0020】

【図1】本発明に係るICデバイス用ソケットの一実施形態の構成を示す斜視図である。

【図2】図1に示されたICデバイス用ソケットの、II−II線に沿った断面構造を示す図である。

【図3】図1に示されたICデバイス用ソケットにおける基板の構成を示す平面図である。

【図4】図2に示された断面構造のうちIII部を拡大した図である。

【図5】電源層の面積を説明するための図である。

【図6】基板表面に対する電源層の第1配置例を示す図である。

【図7】基板表面に対する電源層の第2配置例を示す図である。

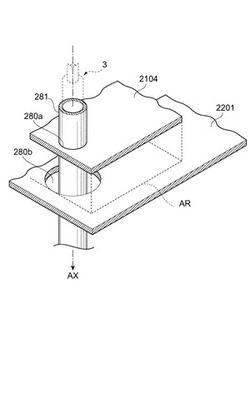

【図8】図3中のV部で示された貫通孔近傍の局部における導電層配置を立体的に示す図である。

【図9】本実施形態に係るICデバイス用ソケットにおける基板の平面図であり、ピン配置と分割された導電層の位置関係の他の例を説明するための図である(その1)。

【図10】本実施形態に係るICデバイス用ソケットにおける基板の平面図であり、ピン配置と分割された導電層の位置関係の他の例を説明するための図である(その2)。

【図11】本実施形態に係るICデバイス用ソケットにおける基板の平面図であり、ピン配置と分割された導電層の位置関係の他の例を説明するための図である(その3)。

【図12】本実施形態に係るICデバイス用ソケットにおける基板の平面図であり、ピン配置と分割された導電層の位置関係の他の例を説明するための図である(その4)。

【発明を実施するための形態】

【0021】

以下、本発明に係るICデバイス用ソケットの各実施形態を、図1〜図12を用いて詳細に説明する。なお、図面の説明において同一の要素には同一符号を付して重複する説明を省略する。

【0022】

まず、本実施形態に係るICデバイス用ソケットの基本構造について、図1〜図4を用いて詳細に説明する。

【0023】

図1は、本発明に係るICデバイス用ソケット1の一実施形態の構成を示す斜視図である。図2は、図1に示されたICデバイス用ソケットの、II−II線に沿った断面構造を示す図である。また、図3は、図1に示されたICデバイス用ソケット1における基板2の構成を示す平面図である。なお、図3中の矢印Lは、図2のII−II線に実質的に一致している。ICデバイス用ソケット1は、基板2と、基板2に圧入等により保持された複数の導電性のコンタクトピン3と、基板2を支持するガイドボディ4とを備える。ガイドボディ4は、検査すべきICデバイス(図示せず)を基板2上の所定位置に配置するためのガイド部又はガイド壁41を有し、さらにICデバイスを検査する検査装置(図示せず)の所定位置に、当該ICデバイス用ソケット1を配置するための位置決め部(本実施形態では図2に示す位置決めピン42)を有する。なお、ガイドボディ4は、必要に応じてICデバイス用ソケット1に組み込まれる。また、基板2は、位置決め手段と協働して位置決めを行う孔や切欠きを有していてもよい。

【0024】

図4は、図2に示された断面構造のうちIII部を拡大した図である。図4に示されたように、基板2は、ガラス繊維入りエポキシ樹脂等の誘電体からなる基材21と、この基材21に包埋された少なくとも1つ(図示例では4つ)の誘電体層22〜25(第1〜第4誘電体層)を有し、誘電体層の上面側及び下面側には銅等の導電層が形成されている。したがって、誘電体層とその両面上に形成された導電層は、協働してコンデンサを構成する。つまり、基板2は、基材21を構成する材料(基材の一部)と、導電層と、誘電体層とを積層することにより構成されている。また、コンデンサの容量を高めるためには各誘電体層の誘電率は高い程好ましく、例えば誘電体層22〜25それぞれは、基材21の誘電率よりも高い誘電率を有する高誘電体からなるのが好ましい。例えば、高誘電体としてスリーエム社製のEmbedded Capacitor Material(ECM)が使用可能である。ECMは、高誘電材料を柔軟性のあるシート状に形成したものである。このような基板は、印刷回路板を作製する方法によって、作製することができる。

【0025】

基板2を構成する材料、すなわち、基材21の材料は、ガラス繊維の代わりに紙を含んでいてもよいし、エポキシ樹脂の代わりにフェノール樹脂やポリアミド樹脂を含んでもよい。また導電層を構成する材料として、銅以外に銀や金が使用されてもよい。誘電体層22〜25のそれぞれは、ポリマーを含んでもよい。好ましくは、誘電体22〜25のそれぞれは、ポリマーと複数の粒子とを含み、具体的には樹脂と粒子とを混合することによって作製される。好適な樹脂としては、エポキシ、ポリイミド、ポリフッ化ビニリデン、シアノエチルプルラン、ベンゾシクロブテン、ポリノルボルネン、ポリテトラフルオロエチレン、アクリレート、及びそれらの混合物が挙げられる。粒子は、誘電性(又は絶縁性)粒子を含み、その代表例としては、チタン酸バリウム、チタン酸バリウムストロンチウム、酸化チタン、チタン酸鉛ジルコニウム、及びそれらの混合物が挙げられる。

【0026】

誘電体層22〜25それぞれの厚みは、例えば0.5μm以上とすることができ、100μm以下とすることができる。各誘電体層の厚みはより薄い方が、キャパシタの静電容量を高くできるので好ましく、例えば15μm以下、或いは10μm以下とすることができる。ただし、各誘電体層の厚みはより厚い方が、接着強度の点からは好ましく、例えば1μm以上とすることができる。

【0027】

また、誘電体の比誘電率は高い程好ましく、例えば10以上、或いは12以上とすることができる。比誘電率の上限には特に制限はないが、例えば100以下、40以下、或いは20以下とすることができる。

【0028】

また、誘電体層22〜25のそれぞれに対して高誘電率を有する材料を使用すると、隣接する2つのコンデンサ間の距離を小さくできるというメリットがある。2つのコンデンサが隣接すると、1つのコンデンサを構成する電源層と隣接する他のコンデンサを構成するグラウンド層(以下、GND層という)との間でも静電容量が構成される。静電容量を構成したい導電層間に高誘電体を使用すると、1つのコンデンサを構成する導電層間の距離と、2つのコンデンサの隣接距離とを同じにしても、1つのコンデンサが生じる静電容量が大きくなる。そのため、隣接するコンデンサ間の距離を相対的に短くすることができ、基板2の薄型化に貢献する。

【0029】

誘電体層22〜25のそれぞれの両面に形成された導電層のうち、一方の導電層は当該ICデバイス用ソケット1の電源ピンと電気的に接続された電源層を構成し、他方の導電層は当該ICデバイス用ソケット1のグラウンドピン(以下、GNDピンという)と電気的に接続されたGND層を構成する。詳細には、基板2のICデバイス側の面(図2では上面)26に最も近い第1誘電体層22の上面221に第1電源層222が形成され、下面223に第1GND層224が形成される。同様に、第1誘電体層22の直下に位置する第2誘電体層23の上面231に第2電源層232が形成され、下面233に第2GND層234が形成される。さらに、基板2の検査装置側の面(図2では下面)27に最も近い第4誘電体層25の上面251に第4電源層252が形成され、下面253に第4GND層254が形成される。同様に、第4誘電体層25の直上に位置する第3誘電体層24の上面241に第3電源層242が形成され、下面243に第3GND層244が形成される。なお、図4の基本構造では、基板2の上面26は、基材21の上面と一致しており、基板2の下面27は、基材21の下面に一致している。

【0030】

ここで、第1電源層222及び第3電源層242は実質同電位であり、第2電源層232及び第4電源層252は実質同電位である。同様に、第1GND層224及び第3GND層244は実質同電位であり、第2GND層234及び第4GND層254は実質同電位である。

【0031】

なお、各誘電体層及びそれぞれの両面に形成された導電層は、基板2に全面的に配置される。したがって、基板2の面積と略等しい面積のコンデンサが形成可能である。

【0032】

導電性コンタクトピン3のそれぞれは、基板2の上面26又は下面27に略垂直に基板2を貫通する。詳細には、基板2を構成する基材21、各誘電体層及びそれぞれの両面に形成された導電層には、各導電性コンタクトピン3を圧入可能な貫通孔28が形成されており、さらに、各貫通孔28の内面には銅、金又は銀等の導電性材料281がメッキ等により形成されている。導電性材料281が導電層のいずれか1つに導通接続されることにより、貫通孔28内に圧入された導電性コンタクトピン3のピンボディ31は、該導電性コンタクトピン3が信号ピンである場合を除き、導電性材料281を介していずれかの導電層に電気的に接続されることになる。なお、信号ピン用の孔の内面にも導電性材料281を形成してもよいが、しなくてもよい。

【0033】

各貫通孔28の寸法は、該貫通孔内に保持された導電性コンタクトピン3が、検査装置の基板にICデバイス用ソケット1を配置したときに生ずる当該導電性コンタクトピン3の内蔵バネの反力によって脱落しないように決定される。例えば、導電性コンタクトピン3の圧入保持力は0.1N以上であることが好ましい。また、各貫通孔28の寸法は、導電性コンタクトピン3の保守・交換時等には貫通孔28から導電性コンタクトピン3が比較的容易に抜き出すことができるように決定され、また、導電性コンタクトピン3を基板2から引き抜いたときに貫通孔28内面の導電性材料281が剥離しないように決定される。例えば、導電性コンタクトピン3の圧入保持力は2.0N以下であることが好ましい。

【0034】

導電性コンタクトピン3のそれぞれは、基板2に圧入保持される略円筒状のピンボディ31と、該ピンボディ31の一端(図示例では下端)から突出することで検査装置(図示せず)に電気的に当接すなわち導通接続可能な第1接触部32と、ピンボディ31の他端(図示例では上端)から突出することでICデバイス(図示せず)に電気的に当接すなわち導通接続可能な第2接触部33とを有する。導電性コンタクトピン3としては、種々の形態が適用可能であるが、例えば、スプリングプローブと呼ばれるタイプのように、両接触部32、33がピンボディ31に対してスプリング等(図示せず)によってピンボディ31の軸方向に変位可能なものが好適である。

【0035】

導電性コンタクトピン3のピンボディ31は、円筒状であることが好ましい。このような形状を有する導電性コンタクトピン3の場合、ピンボディ31の外周表面と貫通孔28とが広い面積で接するので、当該導電性コンタクトピン3を貫通孔28に対して略同軸上に配置することが容易になる。さらに、導電性材料281と導電性コンタクトピン3との接触面積が増えるため、電気的に安定した接続を実現できる。

【0036】

導電性コンタクトピン3は、上述の電源層に電気的に接続される電源ピンのグループと、GND層に接続されるGNDピンのグループと、いずれの層にも接続されない信号ピンのグループとに分類される。例えば、図3に示されたように、導電性コンタクトピン3b、3iのそれぞれは、第1電源層222及び第3電源層242の双方に接続されており、第1電源ピンとして機能する。導電性コンタクトピン3c、3fのそれぞれは、第2電源層232及び第4電源層252の双方に接続されており、第2電源ピンとして機能する。同様に、導電性コンタクトピン3a、3hのそれぞれは、第1GND層224及び第3電源層244の双方に接続されており、第1GNDピンとして機能する。導電性コンタクトピン3d、3gのそれぞれは、第2GND層234及び第4電源層254の双方に接続されており、第2GNDピンとして機能する。また、導電性コンタクトピン3eはいずれの導電層にも接続されておらず、信号ピンとして機能する。

【0037】

本基本構造では、コンデンサを構成する各誘電体層及びそれぞれの両面に形成された導電層とそれらを包埋する基材とにより実質一体物の基板2が形成されている。したがって、導電性コンタクトピン3とコンデンサとの距離を極めて短くすることができ、当該ICデバイス用ソケット1の性能を高めることができる。また、導電性コンタクトピン3のそれぞれは、基板2に摩擦力によって保持(好ましくは圧入)されている。そのため、基板2は導電性コンタクトピン3の支持体としても作用し、導電性コンタクトピン3を支持するための他の部材が不要になる。つまり、導電性コンタクトピン3は、実質的に基板2のみによって保持及び位置決めされる。また、高誘電体からなる誘電体層を使用することにより、基板2のさらなる薄型化が図られる。

【0038】

図4に示されたように、基板2は高誘電体(誘電体層)を挟む電源層とGND層とで構成されるコンデンサを、基板2の上面26及び下面27(基材21の上面及び下面にぞれぞれ一致)に成るべく近い位置(すなわち表層側)に具備することが好ましい。この理由は、基板2の表面と導電層との距離が小さい方が、ICデバイス検査時において良好な電源の安定性が得られるからである。より具体的に言えば、基板2の上面26と第1及び第2誘電体層22、23との距離が短い程、検査対象であるICデバイスの入力感度が上昇する。したがって、第1及び第2誘電体層22、23は、基板2の上面26と下面27の中間点を基準にして、該上面26側に配置されるのが好ましい。また、第3及び第4誘電体層24、25は、基板2の上面26と下面27の中間点を基準にして、該下面27側に配置されるのが好ましい。本基本構造では、基板2が電源層とGND層とに挟まれた高誘電体からなる誘電体層を内包した実質一体物として構成されている。そのため、コンデンサを基板2の表面近傍に配置した構成が容易に実現可能になり、より正確なICデバイスの検査が実現できる。

【0039】

上述のように、導電性コンタクトピン3は実質的に基板2のみによって保持される。そのため、コンデンサを基板2内における任意の位置に配置することが可能になる。また、基板2は、その厚さ方向の中心付近に、誘電体層とその両面に形成された導電層とからなるコンデンサをさらに備えてもよい。

【0040】

導電性コンタクトピン3の長さは、電気特性等の観点からは短い方が好ましい。しかしながら、導電性コンタクトピン3の長さが短い程、ピン交換の作業性や組立性は落ちることになる。これに対し、本基本構造によれば、上記基板2の構成とキャパシタンス値のコントロールにより、所望の周波数以下での電気特性に関しては実際より短いポゴピンが使用された場合と同様の効果が得られるので、比較的長い導電性コンタクトピン3を使用しても当該ICデバイス用ソケット1の性能低下を考慮する必要はない。

【0041】

ピンボディ31の長さが基板2の厚さよりも長ければ、結果的に導電性コンタクトピン3も長くなって電気特性が低下する。一方、ピンボディ31の長さが基板2の厚さよりも短すぎてピンボディ31の軸方向端部がある導電層よりも基板厚さ方向について基板内部側に位置する場合、導電性コンタクトピン3からその導電層に至る経路が複雑になってICデバイス用ソケットの性能低下につながる。したがって、各導電性コンタクトピン3のピンボディ31の軸方向長さは、基板2の厚さと概ね同等であることが好ましい。

【0042】

加えて、本発明の基本構造を有する、上述のICデバイス用ソケット1は、一例として、4つの誘電体層22〜25(それぞれの両面には電源層及びGND層が形成されている)が基材21の一部を介して積層された構造を備える。この構成によれば、例えば第1電源層222と第2電源層224とで、異なる電位設定が可能なことから、当該ICデバイス用ソケット1によっても、1つのパッケージ内において異なる電源設定及び又はグラウンド設定が可能である。

【0043】

上述のように本発明の基本構造においても、誘電体層を電源層及びGND層で挟むことにより基板2内にコンデンサ機能を実現しており、より高い周波数での信号伝送効率を向上させるため、当該ICデバイス用ソケット1を含むPDNにおける電源系と及びグラウンド経路のインピーダンスをある程度低く抑えることは可能である。しかしながら、ICデバイスの低電圧化、高速化に伴う電源の安定化をより効果的に向上させるため、本発明に係るICデバイス用ソケットは、基板2内のコンデンサ機能を実現する構造を利用して、任意に調節されたキャパシタンス値を実現する。すなわち、当該ICデバイス用ソケットは、ICデバイスへの電源供給を担うPDNに組み込み可能な構造を有するため、PDN全体のインピーダンスをコントロールする主要素として当該ICデバイス用ソケットは機能し得る。

【0044】

例えば、インダクタンスLと抵抗Rからなるインピーダンスは式(R+jωL)で与えられるが、キャパシタンスCが直列に接続されるとインピーダンスは式(R+jωL+1/(jωC))で与えられる(ω=2πf、fは周波数)。このキャパシタンスCの追加により、低い周波数ではインピーダンスに対するキャパシタンスの影響が支配的となる一方で、高い周波数ではインピーダンスに対するインダクタンスの影響が支配的となる。上記式から分かるように、複数のキャパシタンスCと複数のインダクタンスLからなる回路では、周波数に対して複雑な振舞を示すことになる。したがって、複数の異なった値のキャパシタンスを追加することにより、広い周波数範囲においてインピーダンスの制御が可能になる。

【0045】

従来、低い周波数領域でのPDNのインピーダンスのみにキャパシタンスが影響するときは、一つのキャパシタンスを追加するだけですんだが、広い周波数領域において、所望のインピーダンス値以下に抑えるためにはより精密な制御が必要となる。

【0046】

なお、平行平板コンデンサのキャパシタンスはε*(S/d)で与えられるため(Sは面積、dは平板導体間距離、εは誘電率)、できるだけ広い面積をとることにより大きいキャパシタンス値を得ることができる。ただし、精密な制御をするためには、この面積を変更することによりキャパシタンス値を変えることができる。

【0047】

以上の技術的考察に鑑み、本発明に係るICデバイス用ソケットでは、誘電体層を挟む電源層及びGND層のうち少なくともいずれかの、その最外周で規定される面積が、所望のキャパシタンス値が得られるよう、基板2(又は基材21)の上面26(又は下面27)の、その最外周で規定される面積よりも小さく設定される。

【0048】

なお、単純化のため、以下に説明される一例では、基板2の上面26又は下面27に対して電源層が基板2の上面26又は下面27に対して小さな面積を有する一方、該電源層と誘電体層を介してコンデンサを構成するGND層が基板2の上面26又は下面27と一致した面積を有するものとする。

【0049】

図5は、電源層の面積を説明するための図である。図3に示された平面図におけるIV部に相当する電源層2101の一部の構成を示す平面図である。図5に示されたように、電源層2101は、基板2に設けられた貫通孔28に相当する位置に、それぞれ直径の異なる2種類の開口280a、280bが設けられている。なお、電源層2101に設けられた、これら2種類の開口280a、280bは、図5中の矢印L1に沿った方向に配置されており、この矢印L1は、図3中の線Lに一致している。開口280aは、貫通孔28の直径と略一致した直径を有しており、より詳細には、該貫通孔28の内面に形成された導電材料281と当該電源層2101との間で十分に電気的接触状態が維持できる程度の開口径を有する。一方、開口280bは、貫通孔28の直径よりも大きな直径を有しており、より詳細には、該貫通孔28の内面に形成された導電材料281と当該電源層2101との間で十分に電気的分離状態が維持できる程度、例えば貫通孔28の直径よりも50μm程度大きな開口径を有する。

【0050】

なお、GND層も、上述の電源層2101と同様に、直径の異なる2種類の開口を有する平面形状を有する。

【0051】

図5に示された例では、電源層2101は上述の基本構造のように基板2面の全面に配置されない。すなわち、GND層が基板2の全面に配置されている図5の例では、基板2の上面26から下面27に向かう方向に沿って見たときに、GND層と電源層2101とが重なり合う領域(コンデンサを構成する領域)の面積は、当該電源層2101の面積を変更することにより調節される。具体的に電源層2101の面積は、該電源層2101の最外周を示す実線S222で囲まれた領域の面積で規定される。なお、実線S222で囲まれた領域内には開口280a、280bが存在するが、これらが占める面積は、当該電源層2101の面積を規定する上で考慮しないものとする。

【0052】

次に、基板2に対する電源層の配置例について図6及び図7を用いて説明する。まず、図6に示された第1配置例では、電源層2102の平面形状は基板2の相似形であるが、電源2102の、その最外周で規定される面積は、基板2の上面26又は下面27の、その最外周(図6中の実線)で規定される面積よりも小さくなっている。すなわち、電源層2102の最外周は、基板2の最外周(図6中の実線)よりも25μm以上基板2の内側に位置する。

【0053】

高誘電率の誘電体層を2枚の導電層で挟み込む構造により平行平板コンデンサを構成する場合、2枚の導電層間距離は小さいほどキャパシタンス値を大きく取ることができる。そこで、幅広い範囲でキャパシタンス値を変化させるためには、導電層間距離が小さい平行平板コンデンサを利用することになる。ところが、基板製造工程において、基板の外形をルータや金型により機械的に形成する場合や、ドリルにより基板に穴あけを行う場合に不具合が生じる可能性がある。すなわち、2枚の導電層両方のエッジが基板の外周面に接すると、基板外形を形成する工程でこれら2枚の導電層がショートする恐れがある。対策としては、導電層の最外周を基板の最外周の内側にオフセットすることで基板製造の歩留まりが向上する。さらに、基板製造工程において、導電層を平面成形した後に、各導電層を誘電体層に熱圧着することによりコンデンサを形成する場合や、ドリルで基板に穴あけを行う場合についても別の不具合が生じる可能性がある。すなわち、誘電体層を挟み込む2枚の導電層間の位置ずれを完全になくすことはできない。そのため、導電層の最外周は、25μm以上、好ましくは50μm以上、基板の最外周から内側に設定されるのが有効である。

【0054】

また、図7に示された例では、電源層2103の平面形状は基板2とは異なる形状を有する。また、電源層2103は、導電性コンタクトピン3は配置される全領域を含まなくともよい。この図7に示された例でも、電源2103の、その最外周で規定される面積は、基板2の上面26又は下面27の、その最外周(図7中の実線)で規定される面積よりも小さくなっている。

【0055】

上述のような平面形状を有する電源層とGND層の配置関係の一例を図8に示す。なお、図8は、図3中のV部で示された貫通孔近傍の局部における導電層配置を立体的に示す図であって、信号ピンとして機能する導電性コンタクトピン3が挿入された貫通孔近傍の構造を示している。また、図8には、誘電体層の他、基材の一部を構成する絶縁材料は省略されている。

【0056】

図8に示されたように、信号ピンとして機能する導電性コンタクトピン3が挿入された貫通孔28の内面には導電材料281が設けられており、この導電材慮281の位置には、誘電体層を挟んで配置された電源層2104の開口280aとGND層2201の開口280bが位置している。この構成により、電源層2104は導電材料281と電気的に接触することとなり、GND層2201は、開口280bを介して導電材料281と電気的に分離された構造が実現されている。このように配置された電源層2104とGND層2201により構成されるコンデンサのキャパシタンス値は、基板2の上面26から下面27に向かって見たとき(貫通孔28の中心軸AXに沿った方向)、これらの電源層2014とGND層2201の重なり合う領域ARの面積によって調節される。

【0057】

なお、以上の実施形態では、GND層を基板2の全面に配置する一方、電源層の面積のみ調節することにより、当該ICデバイス用ソケット1の有するキャパシタンス値が調節されている。しかしながら、このような実施形態に限定されることなく、本願発明に係るICデバイス用ソケットは、電源層を基板2の全面に配置する一方、GND層の面積を調節する構成によっても実現可能である。例えば、電源層及びGND層の双方が、基板2の上面26又は下面27よりも小さい面積を有していてもよいのは言うまでもない。さらに、電源層とGND層の面積は、必ずしも異なっている必要はない。基板2の上面26又は下面27よりも小さい面積を有していれば、コンデンサを構成する電源層とGND層の面積は一致していてもよい。

【0058】

以上のように、本願発明に係るICデバイス用ソケットは、ICデバイスへの電源供給用PDNの一回路要素として、交換可能な構造を有し、かつ、複数の導電性コンタクトピンを保持した基板内に任意に調節されたキャパシタンスを持つことがかのうである。このように当該ICデバイス用ソケットをPDNの一回路要素に組み入れることにより、ICデバイスの低電圧化、高速化に伴う電源の不安定化が効果的に抑制され得る。

【0059】

さらに、本発明に係るICデバイス用ソケット1において、基板2に保持される導電性コンタクトピン3の配置は、図3、図6及び図7に示されたような矩形形状には限定されず、種々の配置パターンが採用可能である。また、採用される導電性コンタクトピン3の配列パターンによって分割される導電層(電源層及び/又はGND層)の面積及び形状の任意に設定される。例えば、その一例を図9〜図12に示す。なお、図9〜図12は、それぞれ、本実施形態に係るICデバイス用ソケットにおける基板の平面図であり、ピン配置と分割された導電層の位置関係の他の例を説明するための図である。また、これら図9〜図12は、図6及び図7の例に倣って、基板2と導電層に相当する要素(一つの誘電体層の一方の面に設けられた導電層)の位置関係が示されている。

【0060】

図9に示された例において、基板2aには、矩形外周と矩形内周とで挟まれた矩形リング領域に導電性コンタクトピン3が配置されており、基板2a内に配置される導電層は、絶縁領域2900aを介して水平方向に、2つの分割領域2105a、2105bに分割され、それぞれが異なる電位に設定可能になっている。また、これら分割領域2105a、2105bは、いずれも基板2の上面26又は下面27よりも小さい面積を有し、その形状は任意に設定され得る。

【0061】

また、図10に示された例において、基板2bには、内側矩形領域に導電性コンタクトピン3が配置されるとともに、該内側矩形領域を取り囲む矩形リング領域にも導電性コンタクトピン3が配置されている。この場合、基板2b内に配置される導電層は、例えば絶縁領域2900bを介して分割領域2106bを分割領域2106aが取り囲むように分割されてもよく、それぞれが異なる電位に設定可能になっている。また、これら分割領域2106a、2106bは、いずれも基板2の上面26又は下面27よりも小さい面積を有し、その形状は任意に設定され得る。

【0062】

図11に示された例において、基板2cには、矩形領域の最外周に沿って導電性コンタクトピン3が配置されている。この場合、基板2c内に配置される導電層は、例えば絶縁領域2900cを介して、導電性コンタクトピン3の配列に沿った形状の分割領域2107a、2107bに分割され、それぞれが異なる電位に設定可能になっている。また、これら分割領域2107a、2107bは、いずれも基板2の上面26又は下面27よりも小さい面積を有し、その形状は任意に設定され得る。

【0063】

さらに、図12に示された例において、基板2dには、所定距離だけ離間した状態で2列に導電性コンタクトピン3が配置されている。この場合、基板2d内に配置される導電層は、例えば絶縁領域2900dを介して各列に対応した分割領域2108a、2108bに分割領域されてもよく、それぞれが異なる電位に設定可能になっている。また、これら分割領域2108a、2108bは、いずれも基板2の上面26又は下面27よりも小さい面積を有し、その形状は任意に設定され得る。

【符号の説明】

【0064】

1…ICデバイス用ソケット、2、2a、2b、2c、2d…基板、21…基材、22〜25…誘電体層、222、232、242、252、2101〜2104、2105a、2105b、2106a、2106b、2107a、2107b、2108a、2108b…電源層、224、234、244、254、2201…GND層、28…貫通孔、3、3a〜3i…導電性コンタクトピン、31…ピンボディ、32…第1接触部、33…第2接触部、4…ガイドボディ、2900a、2900b、2900c、2900d…絶縁領域。

【技術分野】

【0001】

本発明は、CPU、メモリ等の半導体集積回路(以下、ICという)デバイスの検査に使用されるICデバイス用ソケットに関し、特に、半導体パッケージテスト用のコンデンサ機能を具備したICデバイス用ソケットに関するものである。

【背景技術】

【0002】

BGA(ボールグリッドアレイ)デバイス等のICデバイスの信号伝送特性等の評価試験を行う際、そのICデバイスの端子それぞれに電気的に接続可能な接触子を備えたソケット(以下、ICデバイス用ソケットという)が使用される。近年、ICデバイスの扱う信号は、その処理速度の高速化に伴って高周波化している。信号の高速化に対応して、ICデバイス用ソケットも高速信号を伝送できることが求められている。また、電子機器の消費電力低減のためにICデバイスの動作電源の低電圧化もすすんでいる。このようにICデバイスの安定した高速動作には、該ICデバイスに対して安定的に電源が供給される必要である。なお、ICデバイスの高速化と低電圧化により、電源の安定供給がますます重要かつ難しくなっている。

【0003】

ICデバイスの高速動作時も安定的に電源が供給されるためには、電源とグラウンドのインピーダンスを高い周波数領域まで低く抑える必要がある。ICデバイス用ソケットにおいては、当該ICデバイス用ソケットに含まれる導電性コンタクトピンの自己インダクタンスを下げることが好ましい。このため、一般に導電性コンタクトピンは太くかつ短いものが好ましいとされている。

【0004】

高速信号伝送を志向するICデバイス用ソケットに対応する他の方法が、特許文献1に記載されている。特許文献1には、「本発明のLSIソケット101は、プリント基板102、ポゴピン103、ポゴピン支持筐体部104の3つの部品から構成されている。プリント基板102には、印加される電圧値が異なる第1の電源ピン105と第2の電源ピン106、GNDピン107、信号ピン108用となるポゴピン103がそれぞれ挿入される複数のスルーホール109が設けられており、信号ピン108が貫通するスルーホール109以外の全てのスルーホール109内面にメッキ層116が形成されている」と記載されている。

【0005】

特許文献2には、「一般的に、電源用プローブのバイパス用チップコンデンサは、検査用ソケット下面側の配線基板上において、電気的な距離ができるだけデバイスに近い配線パターン上に実装される」及び「チップコンデンサを被検査デバイスの直下であり検査ソケットの上部である位置に実装する事が必要となった」と記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】国際公開第2005/006003号パンフレット

【特許文献2】特開2009−85948号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

発明者らは、従来のICデバイス用ソケットについて検討した結果、以下のような課題を発見した。すなわち、上述のように導電性コンタクトピンは太くかつ短いものが好ましいとされている。ところが、ICデバイスの端子間のピッチの狭小化によって導電性コンタクトピンの太さは必然的に制限される。一方、導電性コンタクトピンは高価であることから、繰り返し使用により信頼性が低下した導電性コンタクトピンは随時交換されることが一般的である。したがって、導電性コンタクトピンの交換時の作業性を考慮すると該導電性コンタクトピンは一定以上の長さを有する必要がある。また、導電性コンタクトピンにスプリングプローブを用いる場合、プローブ長が短いと、プランジャーの稼動長が短くなり、基板や半導体パッケージが平坦でない場合にICデバイス側の端子と該スプリングプローブとの良好な接触状態が確保できなくなる。

【0008】

或いは、ICデバイス用ソケットの筐体や当該ICデバイス用ソケットに組み込まれる導電性コンタクトピンの電源用ピンとグラウンド用ピンに直接コンデンサを接続することにより信号ピンのインダクタンスによるインピーダンスの上昇を、コンデンサのキャパシタンスにより補償し、インピーダンスを下げていた。しかしながら、ICデバイス用ソケットの筐体や導電性コンタクトピンに直接コンデンサを接続すると、該ICデバイス用ソケットが占める体積が大きくなる。この場合、ICデバイス用ソケットの導電性コンタクトピンを高密度に配置することの妨げとなる虞がある。また、ICデバイス用ソケットの筐体や基板の周辺にコンデンサを配置・接続できたとしても、導電性コンタクトピンから数ミリメートル離れた位置にしかコンデンサを配置・接続場合がある。その場合、コンデンサまでの配線長による自己インダクタンスによってコンデンサの効果が有効に作用しない虞がある。

【0009】

本発明は、上述のような課題を解決するための構造を基本構造とし、具体的には、導電性コンタクトピンの交換作業性を低下させることなく、ICデバイスの検査時に、ソケット側の特性によりICデバイスを確実に動作させるための構造を備える。

【0010】

また、最近では、LSI等のICデバイスの低電圧化、高速化に伴い、ICデバイスを確実に動作させるためには電源の安定性がますます重要な役割を担っている(低電圧駆動のICデバイスでは、電源供給ネットワーク(以下、PDNという)をより低いインピーダンスに抑えることが重要であり、高速動作するICデバイスには、高い周波数までのPDNの低インピーダンス化が必要である)。このようにICデバイスを適切に動作させるためには、PDNの低インピーダンス化は不可欠となってきており、該PDN内の電源経路及びグラウンド経路の各インピーダンスを効果的に低減する必要がある。なお、上記PDNは、ICデバイスのパッケージ、検査装置等の回路基板(配線など)、これらICデバイスと回路基板との間に配置されるICデバイス用ソケットの各回路要素から構成されており、例えば本発明の基本構造では、後述のように、ソケット基板内に絶縁材料を介して電源層及びグラウンド層が包埋されており、これら電源層及びグラウンド層でコンデンサ機能を実現することにより、PDN全体を見たときの電源経路及びグラウンド経路の各インピーダンスがある程度低く抑えられ得る。

【0011】

一方、電源経路及びグラウンド経路の各インピーダンスの周波数依存性は、上記PDNを構成する回路要素の周波数応答と考えることができる。すなわち、導体はインダクタンスとして振る舞い、電源層、グラウンド層などの2つの導体の関係はキャパシタンスや相互インダクタンスと見なせるため、PDNは、複数のインダクタンス、キャパシタンス、抵抗からなる1つの回路として振る舞う。そのため、PDNにおける電源経路及びグラウンド経路の各インピーダンスは、周波数依存性が存在し、共振及び反共振に起因した特定の周波数におけるPDN全体のインピーダンスの増大が生じる可能性は否定できない。このようにPDNのインピーダンスが大きくなると、電源の安定性が損なわれるため、これを注意深くコントロールすることが重要になってきている。

【0012】

本発明は上述のような課題を解決するためになされたものであり、ICデバイスの低電圧化、高速化に伴う電源の不安定化を効果的に抑制し得る構造を備えたICデバイスソケットを提供することを目的としている。

【課題を解決するための手段】

【0013】

上述の課題を解決するため、本発明に係るICデバイス用ソケットは、基板と、複数の導電性コンタクトピンを備える。基板は、第1面と、該第1面に対向する第2面と、それぞれが該第1面と該第2面を連絡するとともにその内面に導電材料が設けられた複数の貫通孔とを有する。また、複数の導電性コンタクトピンは、それぞれの一部が複数の貫通孔のうちいずれかに挿入された状態で、該基板によって保持される。基板は、基材と、誘電体層と、第1及び第2導電層とを備える。

基材は、上記第1面と、上記第2面と、上記複数の貫通孔を有する。誘電体層は、複数の貫通孔と交差した状態で基材の第1面及び第2面の間に設けられており、該基材よりも高い誘電率を有する。第1及び第2導電層は、基材の第1面から第2面に向かう方向に沿って、誘電体層を挟んでいる。

【0014】

本願発明に係るICデバイス用ソケットでは、上述のように、コンデンサを構成する誘電体層及び導電層とそれらを包埋する基材とにより実質一体物の基板が形成される。そのため、各導電性コンタクトピンとコンデンサとの距離は極めて短くなり、その結果、当該ICデバイス用ソケットの性能を高めることができる。また、各導電性コンタクトピンは、基板に圧入等されることにより保持される。そのため、基板は各導電性コンタクトピンの支持体としても機能し、該各導電性コンタクトピンを支持するための他の部材が不要となる。

【0015】

特に、本発明に係るICデバイス用ソケットにおいて、第1及び第2導電体層のうち少なくともいずれかの、その最外周によって規定される面積は、第1面の最外周によって規定される面積よりも小さいことを特徴としている。

【0016】

上記複数の導電性コンタクトピンは、複数の第1導電性コンタクトピンと、該複数の第1導電性コンタクトピンとは接続状態の異なる複数の第2導電性コンタクトピンを含む。すなわち、複数の第1導電性コンタクトピンは、それぞれの一部が複数の貫通孔のうちいずれかに挿入され、該一部が対応する導電材料に接触している。複数の第2導電性コンタクトピンは、それぞれの一部が複数の貫通孔のうち別のいずれかに挿入され、第1及び第2導電体層に非接触となっている。この非接触状態は、該一部が対応する導電材料に対して非接触となっているか、又は、該対応する導電材料が第1及び第2導電層に対して非接触となっている状態を意味する。この場合、第1導電層は、対応する導電材料を介して複数の第1導電性コンタクトピンのうちいずれかに電気的に接続される。一方、第2導電層は、対応する導電材料を介して複数の第1導電性コンタクトピンのうち別のいずれかに電気的に接続される。

【0017】

以上のように本発明に係るICデバイス用ソケットにおける複数の第1導電性コンタクトピンのそれぞれは、第1導電層のみに電気的に接続される第1グループ(例えば電源ピンのグループ)と、第2導電層のみに電気的に接続される第2グループ(例えばグラウンドピンのグループ)とに区分される。また、第1及び第2導電層の何れにも電気的に接続されない複数の第2導電性コンタクトピンのそれぞれは信号ピンとして機能することになる。

【0018】

なお、本発明に係るICデバイス用ソケットにおいて、第1及び第2導電体層のうち少なくともいずれかの最外周は、基板(又は基材)の第1面の最外周よりも25μm以上内側に位置するのが好ましい。

【発明の効果】

【0019】

本発明に係るICデバイス用ソケットは、PDNの一回路要素として、交換可能な構造を有し、かつ、複数の導電性コンタクトピンを保持した基板内に任意に調節されたキャパシタンスを持つ。このように当該ICデバイス用ソケットをPDNの一回路要素に組み入れることにより、ICデバイスの低電圧化、高速化に伴う電源の不安定化が効果的に抑制され得る。

【図面の簡単な説明】

【0020】

【図1】本発明に係るICデバイス用ソケットの一実施形態の構成を示す斜視図である。

【図2】図1に示されたICデバイス用ソケットの、II−II線に沿った断面構造を示す図である。

【図3】図1に示されたICデバイス用ソケットにおける基板の構成を示す平面図である。

【図4】図2に示された断面構造のうちIII部を拡大した図である。

【図5】電源層の面積を説明するための図である。

【図6】基板表面に対する電源層の第1配置例を示す図である。

【図7】基板表面に対する電源層の第2配置例を示す図である。

【図8】図3中のV部で示された貫通孔近傍の局部における導電層配置を立体的に示す図である。

【図9】本実施形態に係るICデバイス用ソケットにおける基板の平面図であり、ピン配置と分割された導電層の位置関係の他の例を説明するための図である(その1)。

【図10】本実施形態に係るICデバイス用ソケットにおける基板の平面図であり、ピン配置と分割された導電層の位置関係の他の例を説明するための図である(その2)。

【図11】本実施形態に係るICデバイス用ソケットにおける基板の平面図であり、ピン配置と分割された導電層の位置関係の他の例を説明するための図である(その3)。

【図12】本実施形態に係るICデバイス用ソケットにおける基板の平面図であり、ピン配置と分割された導電層の位置関係の他の例を説明するための図である(その4)。

【発明を実施するための形態】

【0021】

以下、本発明に係るICデバイス用ソケットの各実施形態を、図1〜図12を用いて詳細に説明する。なお、図面の説明において同一の要素には同一符号を付して重複する説明を省略する。

【0022】

まず、本実施形態に係るICデバイス用ソケットの基本構造について、図1〜図4を用いて詳細に説明する。

【0023】

図1は、本発明に係るICデバイス用ソケット1の一実施形態の構成を示す斜視図である。図2は、図1に示されたICデバイス用ソケットの、II−II線に沿った断面構造を示す図である。また、図3は、図1に示されたICデバイス用ソケット1における基板2の構成を示す平面図である。なお、図3中の矢印Lは、図2のII−II線に実質的に一致している。ICデバイス用ソケット1は、基板2と、基板2に圧入等により保持された複数の導電性のコンタクトピン3と、基板2を支持するガイドボディ4とを備える。ガイドボディ4は、検査すべきICデバイス(図示せず)を基板2上の所定位置に配置するためのガイド部又はガイド壁41を有し、さらにICデバイスを検査する検査装置(図示せず)の所定位置に、当該ICデバイス用ソケット1を配置するための位置決め部(本実施形態では図2に示す位置決めピン42)を有する。なお、ガイドボディ4は、必要に応じてICデバイス用ソケット1に組み込まれる。また、基板2は、位置決め手段と協働して位置決めを行う孔や切欠きを有していてもよい。

【0024】

図4は、図2に示された断面構造のうちIII部を拡大した図である。図4に示されたように、基板2は、ガラス繊維入りエポキシ樹脂等の誘電体からなる基材21と、この基材21に包埋された少なくとも1つ(図示例では4つ)の誘電体層22〜25(第1〜第4誘電体層)を有し、誘電体層の上面側及び下面側には銅等の導電層が形成されている。したがって、誘電体層とその両面上に形成された導電層は、協働してコンデンサを構成する。つまり、基板2は、基材21を構成する材料(基材の一部)と、導電層と、誘電体層とを積層することにより構成されている。また、コンデンサの容量を高めるためには各誘電体層の誘電率は高い程好ましく、例えば誘電体層22〜25それぞれは、基材21の誘電率よりも高い誘電率を有する高誘電体からなるのが好ましい。例えば、高誘電体としてスリーエム社製のEmbedded Capacitor Material(ECM)が使用可能である。ECMは、高誘電材料を柔軟性のあるシート状に形成したものである。このような基板は、印刷回路板を作製する方法によって、作製することができる。

【0025】

基板2を構成する材料、すなわち、基材21の材料は、ガラス繊維の代わりに紙を含んでいてもよいし、エポキシ樹脂の代わりにフェノール樹脂やポリアミド樹脂を含んでもよい。また導電層を構成する材料として、銅以外に銀や金が使用されてもよい。誘電体層22〜25のそれぞれは、ポリマーを含んでもよい。好ましくは、誘電体22〜25のそれぞれは、ポリマーと複数の粒子とを含み、具体的には樹脂と粒子とを混合することによって作製される。好適な樹脂としては、エポキシ、ポリイミド、ポリフッ化ビニリデン、シアノエチルプルラン、ベンゾシクロブテン、ポリノルボルネン、ポリテトラフルオロエチレン、アクリレート、及びそれらの混合物が挙げられる。粒子は、誘電性(又は絶縁性)粒子を含み、その代表例としては、チタン酸バリウム、チタン酸バリウムストロンチウム、酸化チタン、チタン酸鉛ジルコニウム、及びそれらの混合物が挙げられる。

【0026】

誘電体層22〜25それぞれの厚みは、例えば0.5μm以上とすることができ、100μm以下とすることができる。各誘電体層の厚みはより薄い方が、キャパシタの静電容量を高くできるので好ましく、例えば15μm以下、或いは10μm以下とすることができる。ただし、各誘電体層の厚みはより厚い方が、接着強度の点からは好ましく、例えば1μm以上とすることができる。

【0027】

また、誘電体の比誘電率は高い程好ましく、例えば10以上、或いは12以上とすることができる。比誘電率の上限には特に制限はないが、例えば100以下、40以下、或いは20以下とすることができる。

【0028】

また、誘電体層22〜25のそれぞれに対して高誘電率を有する材料を使用すると、隣接する2つのコンデンサ間の距離を小さくできるというメリットがある。2つのコンデンサが隣接すると、1つのコンデンサを構成する電源層と隣接する他のコンデンサを構成するグラウンド層(以下、GND層という)との間でも静電容量が構成される。静電容量を構成したい導電層間に高誘電体を使用すると、1つのコンデンサを構成する導電層間の距離と、2つのコンデンサの隣接距離とを同じにしても、1つのコンデンサが生じる静電容量が大きくなる。そのため、隣接するコンデンサ間の距離を相対的に短くすることができ、基板2の薄型化に貢献する。

【0029】

誘電体層22〜25のそれぞれの両面に形成された導電層のうち、一方の導電層は当該ICデバイス用ソケット1の電源ピンと電気的に接続された電源層を構成し、他方の導電層は当該ICデバイス用ソケット1のグラウンドピン(以下、GNDピンという)と電気的に接続されたGND層を構成する。詳細には、基板2のICデバイス側の面(図2では上面)26に最も近い第1誘電体層22の上面221に第1電源層222が形成され、下面223に第1GND層224が形成される。同様に、第1誘電体層22の直下に位置する第2誘電体層23の上面231に第2電源層232が形成され、下面233に第2GND層234が形成される。さらに、基板2の検査装置側の面(図2では下面)27に最も近い第4誘電体層25の上面251に第4電源層252が形成され、下面253に第4GND層254が形成される。同様に、第4誘電体層25の直上に位置する第3誘電体層24の上面241に第3電源層242が形成され、下面243に第3GND層244が形成される。なお、図4の基本構造では、基板2の上面26は、基材21の上面と一致しており、基板2の下面27は、基材21の下面に一致している。

【0030】

ここで、第1電源層222及び第3電源層242は実質同電位であり、第2電源層232及び第4電源層252は実質同電位である。同様に、第1GND層224及び第3GND層244は実質同電位であり、第2GND層234及び第4GND層254は実質同電位である。

【0031】

なお、各誘電体層及びそれぞれの両面に形成された導電層は、基板2に全面的に配置される。したがって、基板2の面積と略等しい面積のコンデンサが形成可能である。

【0032】

導電性コンタクトピン3のそれぞれは、基板2の上面26又は下面27に略垂直に基板2を貫通する。詳細には、基板2を構成する基材21、各誘電体層及びそれぞれの両面に形成された導電層には、各導電性コンタクトピン3を圧入可能な貫通孔28が形成されており、さらに、各貫通孔28の内面には銅、金又は銀等の導電性材料281がメッキ等により形成されている。導電性材料281が導電層のいずれか1つに導通接続されることにより、貫通孔28内に圧入された導電性コンタクトピン3のピンボディ31は、該導電性コンタクトピン3が信号ピンである場合を除き、導電性材料281を介していずれかの導電層に電気的に接続されることになる。なお、信号ピン用の孔の内面にも導電性材料281を形成してもよいが、しなくてもよい。

【0033】

各貫通孔28の寸法は、該貫通孔内に保持された導電性コンタクトピン3が、検査装置の基板にICデバイス用ソケット1を配置したときに生ずる当該導電性コンタクトピン3の内蔵バネの反力によって脱落しないように決定される。例えば、導電性コンタクトピン3の圧入保持力は0.1N以上であることが好ましい。また、各貫通孔28の寸法は、導電性コンタクトピン3の保守・交換時等には貫通孔28から導電性コンタクトピン3が比較的容易に抜き出すことができるように決定され、また、導電性コンタクトピン3を基板2から引き抜いたときに貫通孔28内面の導電性材料281が剥離しないように決定される。例えば、導電性コンタクトピン3の圧入保持力は2.0N以下であることが好ましい。

【0034】

導電性コンタクトピン3のそれぞれは、基板2に圧入保持される略円筒状のピンボディ31と、該ピンボディ31の一端(図示例では下端)から突出することで検査装置(図示せず)に電気的に当接すなわち導通接続可能な第1接触部32と、ピンボディ31の他端(図示例では上端)から突出することでICデバイス(図示せず)に電気的に当接すなわち導通接続可能な第2接触部33とを有する。導電性コンタクトピン3としては、種々の形態が適用可能であるが、例えば、スプリングプローブと呼ばれるタイプのように、両接触部32、33がピンボディ31に対してスプリング等(図示せず)によってピンボディ31の軸方向に変位可能なものが好適である。

【0035】

導電性コンタクトピン3のピンボディ31は、円筒状であることが好ましい。このような形状を有する導電性コンタクトピン3の場合、ピンボディ31の外周表面と貫通孔28とが広い面積で接するので、当該導電性コンタクトピン3を貫通孔28に対して略同軸上に配置することが容易になる。さらに、導電性材料281と導電性コンタクトピン3との接触面積が増えるため、電気的に安定した接続を実現できる。

【0036】

導電性コンタクトピン3は、上述の電源層に電気的に接続される電源ピンのグループと、GND層に接続されるGNDピンのグループと、いずれの層にも接続されない信号ピンのグループとに分類される。例えば、図3に示されたように、導電性コンタクトピン3b、3iのそれぞれは、第1電源層222及び第3電源層242の双方に接続されており、第1電源ピンとして機能する。導電性コンタクトピン3c、3fのそれぞれは、第2電源層232及び第4電源層252の双方に接続されており、第2電源ピンとして機能する。同様に、導電性コンタクトピン3a、3hのそれぞれは、第1GND層224及び第3電源層244の双方に接続されており、第1GNDピンとして機能する。導電性コンタクトピン3d、3gのそれぞれは、第2GND層234及び第4電源層254の双方に接続されており、第2GNDピンとして機能する。また、導電性コンタクトピン3eはいずれの導電層にも接続されておらず、信号ピンとして機能する。

【0037】

本基本構造では、コンデンサを構成する各誘電体層及びそれぞれの両面に形成された導電層とそれらを包埋する基材とにより実質一体物の基板2が形成されている。したがって、導電性コンタクトピン3とコンデンサとの距離を極めて短くすることができ、当該ICデバイス用ソケット1の性能を高めることができる。また、導電性コンタクトピン3のそれぞれは、基板2に摩擦力によって保持(好ましくは圧入)されている。そのため、基板2は導電性コンタクトピン3の支持体としても作用し、導電性コンタクトピン3を支持するための他の部材が不要になる。つまり、導電性コンタクトピン3は、実質的に基板2のみによって保持及び位置決めされる。また、高誘電体からなる誘電体層を使用することにより、基板2のさらなる薄型化が図られる。

【0038】

図4に示されたように、基板2は高誘電体(誘電体層)を挟む電源層とGND層とで構成されるコンデンサを、基板2の上面26及び下面27(基材21の上面及び下面にぞれぞれ一致)に成るべく近い位置(すなわち表層側)に具備することが好ましい。この理由は、基板2の表面と導電層との距離が小さい方が、ICデバイス検査時において良好な電源の安定性が得られるからである。より具体的に言えば、基板2の上面26と第1及び第2誘電体層22、23との距離が短い程、検査対象であるICデバイスの入力感度が上昇する。したがって、第1及び第2誘電体層22、23は、基板2の上面26と下面27の中間点を基準にして、該上面26側に配置されるのが好ましい。また、第3及び第4誘電体層24、25は、基板2の上面26と下面27の中間点を基準にして、該下面27側に配置されるのが好ましい。本基本構造では、基板2が電源層とGND層とに挟まれた高誘電体からなる誘電体層を内包した実質一体物として構成されている。そのため、コンデンサを基板2の表面近傍に配置した構成が容易に実現可能になり、より正確なICデバイスの検査が実現できる。

【0039】

上述のように、導電性コンタクトピン3は実質的に基板2のみによって保持される。そのため、コンデンサを基板2内における任意の位置に配置することが可能になる。また、基板2は、その厚さ方向の中心付近に、誘電体層とその両面に形成された導電層とからなるコンデンサをさらに備えてもよい。

【0040】

導電性コンタクトピン3の長さは、電気特性等の観点からは短い方が好ましい。しかしながら、導電性コンタクトピン3の長さが短い程、ピン交換の作業性や組立性は落ちることになる。これに対し、本基本構造によれば、上記基板2の構成とキャパシタンス値のコントロールにより、所望の周波数以下での電気特性に関しては実際より短いポゴピンが使用された場合と同様の効果が得られるので、比較的長い導電性コンタクトピン3を使用しても当該ICデバイス用ソケット1の性能低下を考慮する必要はない。

【0041】

ピンボディ31の長さが基板2の厚さよりも長ければ、結果的に導電性コンタクトピン3も長くなって電気特性が低下する。一方、ピンボディ31の長さが基板2の厚さよりも短すぎてピンボディ31の軸方向端部がある導電層よりも基板厚さ方向について基板内部側に位置する場合、導電性コンタクトピン3からその導電層に至る経路が複雑になってICデバイス用ソケットの性能低下につながる。したがって、各導電性コンタクトピン3のピンボディ31の軸方向長さは、基板2の厚さと概ね同等であることが好ましい。

【0042】

加えて、本発明の基本構造を有する、上述のICデバイス用ソケット1は、一例として、4つの誘電体層22〜25(それぞれの両面には電源層及びGND層が形成されている)が基材21の一部を介して積層された構造を備える。この構成によれば、例えば第1電源層222と第2電源層224とで、異なる電位設定が可能なことから、当該ICデバイス用ソケット1によっても、1つのパッケージ内において異なる電源設定及び又はグラウンド設定が可能である。

【0043】

上述のように本発明の基本構造においても、誘電体層を電源層及びGND層で挟むことにより基板2内にコンデンサ機能を実現しており、より高い周波数での信号伝送効率を向上させるため、当該ICデバイス用ソケット1を含むPDNにおける電源系と及びグラウンド経路のインピーダンスをある程度低く抑えることは可能である。しかしながら、ICデバイスの低電圧化、高速化に伴う電源の安定化をより効果的に向上させるため、本発明に係るICデバイス用ソケットは、基板2内のコンデンサ機能を実現する構造を利用して、任意に調節されたキャパシタンス値を実現する。すなわち、当該ICデバイス用ソケットは、ICデバイスへの電源供給を担うPDNに組み込み可能な構造を有するため、PDN全体のインピーダンスをコントロールする主要素として当該ICデバイス用ソケットは機能し得る。

【0044】

例えば、インダクタンスLと抵抗Rからなるインピーダンスは式(R+jωL)で与えられるが、キャパシタンスCが直列に接続されるとインピーダンスは式(R+jωL+1/(jωC))で与えられる(ω=2πf、fは周波数)。このキャパシタンスCの追加により、低い周波数ではインピーダンスに対するキャパシタンスの影響が支配的となる一方で、高い周波数ではインピーダンスに対するインダクタンスの影響が支配的となる。上記式から分かるように、複数のキャパシタンスCと複数のインダクタンスLからなる回路では、周波数に対して複雑な振舞を示すことになる。したがって、複数の異なった値のキャパシタンスを追加することにより、広い周波数範囲においてインピーダンスの制御が可能になる。

【0045】

従来、低い周波数領域でのPDNのインピーダンスのみにキャパシタンスが影響するときは、一つのキャパシタンスを追加するだけですんだが、広い周波数領域において、所望のインピーダンス値以下に抑えるためにはより精密な制御が必要となる。

【0046】

なお、平行平板コンデンサのキャパシタンスはε*(S/d)で与えられるため(Sは面積、dは平板導体間距離、εは誘電率)、できるだけ広い面積をとることにより大きいキャパシタンス値を得ることができる。ただし、精密な制御をするためには、この面積を変更することによりキャパシタンス値を変えることができる。

【0047】

以上の技術的考察に鑑み、本発明に係るICデバイス用ソケットでは、誘電体層を挟む電源層及びGND層のうち少なくともいずれかの、その最外周で規定される面積が、所望のキャパシタンス値が得られるよう、基板2(又は基材21)の上面26(又は下面27)の、その最外周で規定される面積よりも小さく設定される。

【0048】

なお、単純化のため、以下に説明される一例では、基板2の上面26又は下面27に対して電源層が基板2の上面26又は下面27に対して小さな面積を有する一方、該電源層と誘電体層を介してコンデンサを構成するGND層が基板2の上面26又は下面27と一致した面積を有するものとする。

【0049】

図5は、電源層の面積を説明するための図である。図3に示された平面図におけるIV部に相当する電源層2101の一部の構成を示す平面図である。図5に示されたように、電源層2101は、基板2に設けられた貫通孔28に相当する位置に、それぞれ直径の異なる2種類の開口280a、280bが設けられている。なお、電源層2101に設けられた、これら2種類の開口280a、280bは、図5中の矢印L1に沿った方向に配置されており、この矢印L1は、図3中の線Lに一致している。開口280aは、貫通孔28の直径と略一致した直径を有しており、より詳細には、該貫通孔28の内面に形成された導電材料281と当該電源層2101との間で十分に電気的接触状態が維持できる程度の開口径を有する。一方、開口280bは、貫通孔28の直径よりも大きな直径を有しており、より詳細には、該貫通孔28の内面に形成された導電材料281と当該電源層2101との間で十分に電気的分離状態が維持できる程度、例えば貫通孔28の直径よりも50μm程度大きな開口径を有する。

【0050】

なお、GND層も、上述の電源層2101と同様に、直径の異なる2種類の開口を有する平面形状を有する。

【0051】

図5に示された例では、電源層2101は上述の基本構造のように基板2面の全面に配置されない。すなわち、GND層が基板2の全面に配置されている図5の例では、基板2の上面26から下面27に向かう方向に沿って見たときに、GND層と電源層2101とが重なり合う領域(コンデンサを構成する領域)の面積は、当該電源層2101の面積を変更することにより調節される。具体的に電源層2101の面積は、該電源層2101の最外周を示す実線S222で囲まれた領域の面積で規定される。なお、実線S222で囲まれた領域内には開口280a、280bが存在するが、これらが占める面積は、当該電源層2101の面積を規定する上で考慮しないものとする。

【0052】

次に、基板2に対する電源層の配置例について図6及び図7を用いて説明する。まず、図6に示された第1配置例では、電源層2102の平面形状は基板2の相似形であるが、電源2102の、その最外周で規定される面積は、基板2の上面26又は下面27の、その最外周(図6中の実線)で規定される面積よりも小さくなっている。すなわち、電源層2102の最外周は、基板2の最外周(図6中の実線)よりも25μm以上基板2の内側に位置する。

【0053】

高誘電率の誘電体層を2枚の導電層で挟み込む構造により平行平板コンデンサを構成する場合、2枚の導電層間距離は小さいほどキャパシタンス値を大きく取ることができる。そこで、幅広い範囲でキャパシタンス値を変化させるためには、導電層間距離が小さい平行平板コンデンサを利用することになる。ところが、基板製造工程において、基板の外形をルータや金型により機械的に形成する場合や、ドリルにより基板に穴あけを行う場合に不具合が生じる可能性がある。すなわち、2枚の導電層両方のエッジが基板の外周面に接すると、基板外形を形成する工程でこれら2枚の導電層がショートする恐れがある。対策としては、導電層の最外周を基板の最外周の内側にオフセットすることで基板製造の歩留まりが向上する。さらに、基板製造工程において、導電層を平面成形した後に、各導電層を誘電体層に熱圧着することによりコンデンサを形成する場合や、ドリルで基板に穴あけを行う場合についても別の不具合が生じる可能性がある。すなわち、誘電体層を挟み込む2枚の導電層間の位置ずれを完全になくすことはできない。そのため、導電層の最外周は、25μm以上、好ましくは50μm以上、基板の最外周から内側に設定されるのが有効である。

【0054】

また、図7に示された例では、電源層2103の平面形状は基板2とは異なる形状を有する。また、電源層2103は、導電性コンタクトピン3は配置される全領域を含まなくともよい。この図7に示された例でも、電源2103の、その最外周で規定される面積は、基板2の上面26又は下面27の、その最外周(図7中の実線)で規定される面積よりも小さくなっている。

【0055】

上述のような平面形状を有する電源層とGND層の配置関係の一例を図8に示す。なお、図8は、図3中のV部で示された貫通孔近傍の局部における導電層配置を立体的に示す図であって、信号ピンとして機能する導電性コンタクトピン3が挿入された貫通孔近傍の構造を示している。また、図8には、誘電体層の他、基材の一部を構成する絶縁材料は省略されている。

【0056】

図8に示されたように、信号ピンとして機能する導電性コンタクトピン3が挿入された貫通孔28の内面には導電材料281が設けられており、この導電材慮281の位置には、誘電体層を挟んで配置された電源層2104の開口280aとGND層2201の開口280bが位置している。この構成により、電源層2104は導電材料281と電気的に接触することとなり、GND層2201は、開口280bを介して導電材料281と電気的に分離された構造が実現されている。このように配置された電源層2104とGND層2201により構成されるコンデンサのキャパシタンス値は、基板2の上面26から下面27に向かって見たとき(貫通孔28の中心軸AXに沿った方向)、これらの電源層2014とGND層2201の重なり合う領域ARの面積によって調節される。

【0057】

なお、以上の実施形態では、GND層を基板2の全面に配置する一方、電源層の面積のみ調節することにより、当該ICデバイス用ソケット1の有するキャパシタンス値が調節されている。しかしながら、このような実施形態に限定されることなく、本願発明に係るICデバイス用ソケットは、電源層を基板2の全面に配置する一方、GND層の面積を調節する構成によっても実現可能である。例えば、電源層及びGND層の双方が、基板2の上面26又は下面27よりも小さい面積を有していてもよいのは言うまでもない。さらに、電源層とGND層の面積は、必ずしも異なっている必要はない。基板2の上面26又は下面27よりも小さい面積を有していれば、コンデンサを構成する電源層とGND層の面積は一致していてもよい。

【0058】

以上のように、本願発明に係るICデバイス用ソケットは、ICデバイスへの電源供給用PDNの一回路要素として、交換可能な構造を有し、かつ、複数の導電性コンタクトピンを保持した基板内に任意に調節されたキャパシタンスを持つことがかのうである。このように当該ICデバイス用ソケットをPDNの一回路要素に組み入れることにより、ICデバイスの低電圧化、高速化に伴う電源の不安定化が効果的に抑制され得る。

【0059】

さらに、本発明に係るICデバイス用ソケット1において、基板2に保持される導電性コンタクトピン3の配置は、図3、図6及び図7に示されたような矩形形状には限定されず、種々の配置パターンが採用可能である。また、採用される導電性コンタクトピン3の配列パターンによって分割される導電層(電源層及び/又はGND層)の面積及び形状の任意に設定される。例えば、その一例を図9〜図12に示す。なお、図9〜図12は、それぞれ、本実施形態に係るICデバイス用ソケットにおける基板の平面図であり、ピン配置と分割された導電層の位置関係の他の例を説明するための図である。また、これら図9〜図12は、図6及び図7の例に倣って、基板2と導電層に相当する要素(一つの誘電体層の一方の面に設けられた導電層)の位置関係が示されている。

【0060】

図9に示された例において、基板2aには、矩形外周と矩形内周とで挟まれた矩形リング領域に導電性コンタクトピン3が配置されており、基板2a内に配置される導電層は、絶縁領域2900aを介して水平方向に、2つの分割領域2105a、2105bに分割され、それぞれが異なる電位に設定可能になっている。また、これら分割領域2105a、2105bは、いずれも基板2の上面26又は下面27よりも小さい面積を有し、その形状は任意に設定され得る。

【0061】

また、図10に示された例において、基板2bには、内側矩形領域に導電性コンタクトピン3が配置されるとともに、該内側矩形領域を取り囲む矩形リング領域にも導電性コンタクトピン3が配置されている。この場合、基板2b内に配置される導電層は、例えば絶縁領域2900bを介して分割領域2106bを分割領域2106aが取り囲むように分割されてもよく、それぞれが異なる電位に設定可能になっている。また、これら分割領域2106a、2106bは、いずれも基板2の上面26又は下面27よりも小さい面積を有し、その形状は任意に設定され得る。

【0062】

図11に示された例において、基板2cには、矩形領域の最外周に沿って導電性コンタクトピン3が配置されている。この場合、基板2c内に配置される導電層は、例えば絶縁領域2900cを介して、導電性コンタクトピン3の配列に沿った形状の分割領域2107a、2107bに分割され、それぞれが異なる電位に設定可能になっている。また、これら分割領域2107a、2107bは、いずれも基板2の上面26又は下面27よりも小さい面積を有し、その形状は任意に設定され得る。

【0063】

さらに、図12に示された例において、基板2dには、所定距離だけ離間した状態で2列に導電性コンタクトピン3が配置されている。この場合、基板2d内に配置される導電層は、例えば絶縁領域2900dを介して各列に対応した分割領域2108a、2108bに分割領域されてもよく、それぞれが異なる電位に設定可能になっている。また、これら分割領域2108a、2108bは、いずれも基板2の上面26又は下面27よりも小さい面積を有し、その形状は任意に設定され得る。

【符号の説明】

【0064】

1…ICデバイス用ソケット、2、2a、2b、2c、2d…基板、21…基材、22〜25…誘電体層、222、232、242、252、2101〜2104、2105a、2105b、2106a、2106b、2107a、2107b、2108a、2108b…電源層、224、234、244、254、2201…GND層、28…貫通孔、3、3a〜3i…導電性コンタクトピン、31…ピンボディ、32…第1接触部、33…第2接触部、4…ガイドボディ、2900a、2900b、2900c、2900d…絶縁領域。

【特許請求の範囲】

【請求項1】

第1面と、該第1面に対向する第2面と、それぞれが該第1面と該第2面を連絡するとともにその内面に導電材料が設けられた複数の貫通孔と、を有する基板と、

それぞれの一部が前記複数の貫通孔のうちいずれかに挿入された複数の導電性コンタクトピンと、を備えたIC用ソケットであって、

前記基板は、

前記第1面と、前記第2面と、前記複数の貫通孔と、を有する基材と、

前記複数の貫通孔と交差した状態で前記基材の第1面及び第2面の間に設けられた誘電体層であって、該基材よりも高い誘電率を有する誘電体層と、

前記基材の第1面から第2面に向かう方向に沿って、前記誘電体層を挟む第1及び第2導電体層と、を備え、

前記複数の導電性コンタクトピンは、

それぞれの一部が前記複数の貫通孔のうちいずれかに挿入され、該一部が対応する導電材料に接触された複数の第1導電性コンタクトピンと、

それぞれの一部が前記複数の貫通孔のうち別のいずれかに挿入され、該一部が対応する導電材料に非接触となっているか、又は、該対応する導電材料が前記第1及び第2導電層に非接触となっている複数の第2導電性コンタクトピンと、を含み、

前記第1導電層は、対応する導電材料を介して前記複数の第1導電性コンタクトピンのうち少なくともいずれかに電気的に接続される一方、前記第2導電層は、対応する導電材料を介して前記複数の第1導電性コンタクトピンのうち少なくとも別のいずれかに電気的に接続されており、

前記第1及び第2導電体層のうち少なくともいずれかの、その最外周によって規定される面積は、前記第1面の最外周によって規定される面積よりも小さい、ICデバイス用ソケット。

【請求項2】

前記第1及び第2導電体層のうち少なくともいずれかの最外周は、前記第1面の最外周よりも25μm以上内側に位置することを特徴とする請求項1記載のICデバイス用ソケット。

【請求項3】

前記第1及び第2導電層間のキャパシタンスは、該第1面から該第2面を見たときに該第1導電層と該第2導電層の重なり合う部分の面積を変えることにより制御されることを特徴とする請求項1記載のICデバイス用ソケット。

【請求項4】

前記基板を支持するガイドボディであって、検査すべきICデバイスを前記基板上の所定位置に配置するためのガイド部と、前記ICデバイスを検査する検査装置の所定位置に当該ICデバイス用ソケットを配置するための位置決め部とを有するガイドボディを更に備えたことを特徴とする請求項1記載のICデバイス用ソケット。

【請求項1】

第1面と、該第1面に対向する第2面と、それぞれが該第1面と該第2面を連絡するとともにその内面に導電材料が設けられた複数の貫通孔と、を有する基板と、

それぞれの一部が前記複数の貫通孔のうちいずれかに挿入された複数の導電性コンタクトピンと、を備えたIC用ソケットであって、

前記基板は、

前記第1面と、前記第2面と、前記複数の貫通孔と、を有する基材と、

前記複数の貫通孔と交差した状態で前記基材の第1面及び第2面の間に設けられた誘電体層であって、該基材よりも高い誘電率を有する誘電体層と、

前記基材の第1面から第2面に向かう方向に沿って、前記誘電体層を挟む第1及び第2導電体層と、を備え、

前記複数の導電性コンタクトピンは、

それぞれの一部が前記複数の貫通孔のうちいずれかに挿入され、該一部が対応する導電材料に接触された複数の第1導電性コンタクトピンと、

それぞれの一部が前記複数の貫通孔のうち別のいずれかに挿入され、該一部が対応する導電材料に非接触となっているか、又は、該対応する導電材料が前記第1及び第2導電層に非接触となっている複数の第2導電性コンタクトピンと、を含み、

前記第1導電層は、対応する導電材料を介して前記複数の第1導電性コンタクトピンのうち少なくともいずれかに電気的に接続される一方、前記第2導電層は、対応する導電材料を介して前記複数の第1導電性コンタクトピンのうち少なくとも別のいずれかに電気的に接続されており、

前記第1及び第2導電体層のうち少なくともいずれかの、その最外周によって規定される面積は、前記第1面の最外周によって規定される面積よりも小さい、ICデバイス用ソケット。

【請求項2】

前記第1及び第2導電体層のうち少なくともいずれかの最外周は、前記第1面の最外周よりも25μm以上内側に位置することを特徴とする請求項1記載のICデバイス用ソケット。

【請求項3】

前記第1及び第2導電層間のキャパシタンスは、該第1面から該第2面を見たときに該第1導電層と該第2導電層の重なり合う部分の面積を変えることにより制御されることを特徴とする請求項1記載のICデバイス用ソケット。

【請求項4】

前記基板を支持するガイドボディであって、検査すべきICデバイスを前記基板上の所定位置に配置するためのガイド部と、前記ICデバイスを検査する検査装置の所定位置に当該ICデバイス用ソケットを配置するための位置決め部とを有するガイドボディを更に備えたことを特徴とする請求項1記載のICデバイス用ソケット。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2012−159425(P2012−159425A)

【公開日】平成24年8月23日(2012.8.23)

【国際特許分類】

【出願番号】特願2011−19951(P2011−19951)

【出願日】平成23年2月1日(2011.2.1)

【出願人】(505005049)スリーエム イノベイティブ プロパティズ カンパニー (2,080)

【Fターム(参考)】

【公開日】平成24年8月23日(2012.8.23)

【国際特許分類】

【出願日】平成23年2月1日(2011.2.1)

【出願人】(505005049)スリーエム イノベイティブ プロパティズ カンパニー (2,080)

【Fターム(参考)】

[ Back to top ]