III−V族化合物半導体層を含む半導体素子及びその製造方法

【課題】III−V族化合物半導体層を含む半導体素子及びその製造方法を提供する。

【解決手段】III−V族物質を含む半導体素子及びその製造方法に係り、該半導体素子は、溝を含むシリコン基板30と、溝周囲の基板上に形成されたハードマスク32と、溝を充填する、ハードマスク上に形成された第1物質層34と、第1物質層上に形成された上部物質層36、及び上部物質層上に形成された素子層と、を含み、該第1物質層は、III−V族物質層であり、該上部物質層は、第1物質層の一部でもあり、該上部物質層は、第1物質層と同一物質または異なる物質であってもよい。

【解決手段】III−V族物質を含む半導体素子及びその製造方法に係り、該半導体素子は、溝を含むシリコン基板30と、溝周囲の基板上に形成されたハードマスク32と、溝を充填する、ハードマスク上に形成された第1物質層34と、第1物質層上に形成された上部物質層36、及び上部物質層上に形成された素子層と、を含み、該第1物質層は、III−V族物質層であり、該上部物質層は、第1物質層の一部でもあり、該上部物質層は、第1物質層と同一物質または異なる物質であってもよい。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子及びその製造方法に係り、さらに詳細には、III−V族化合物半導体層を含む半導体素子及びその製造方法に関する。

【背景技術】

【0002】

半導体素子の集積度が高まると同時に、半導体素子を構成する要素のサイズが小さくなり、要素間の間隔も狭くなっている。例えば、シリコン(Si)基板トランジスタの場合、ソース、ドレイン及びゲートのサイズが小さくなるだけではなく、ソース、ドレイン及びゲートの間の間隔が狭まっている。ゲートサイズが小さくなると、チャネル長が短くなるが、短いチャネル効果(short channel effect)によって、+トランジスタの特性が低下する。

【0003】

このようなゲートサイズ限界を克服するための代案として、チャネル物質をIII−V族物質で代替する研究が進められている。また、シリコン(Si)素子とIII−V族物質とを含む光素子を1つのデバイスに集積するための試み、及び高効率のIII−V族物質を含む太陽電池を、シリコン基板の上に製造するための研究も進められている。

【0004】

しかし、III−V族物質とシリコンとの大きい結晶定数差と熱伝導度差とによって、2つの物質の界面で多くの欠陥が生じる。このような欠陥によって、III−V族物質がシリコン基板素子に適用されるのに制限が生じる。

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の一実施形態は、成長欠陥を低減させたIII−V族物質を含む半導体素子を提供するものである。

【0006】

本発明の一実施形態は、このような半導体素子の製造方法を提供するものである。

【課題を解決するための手段】

【0007】

本発明の一実施形態による半導体素子は、溝を含むシリコン基板と、前記溝周囲の前記基板上に形成されたハードマスクと、前記溝を充填する、前記ハードマスク上に形成された第1物質層と、前記第1物質層上に形成された上部物質層及び前記上部物質層上に形成された素子層と、を含み、前記第1物質層は、III−V族物質層である。

【0008】

このような半導体素子で、前記III−V族物質層は、III−V族化合物半導体層であってもよい。

【0009】

前記上部物質層は、前記第1物質層の一部であってもよい。

【0010】

前記上部物質層は、前記第1物質層と同一物質または異なる物質であってもよい。

【0011】

前記第1物質層と前記上部物質層との間に、バッファ層がさらに具備されてもよい。

【0012】

前記第1物質層と前記上部物質層との間に具備された第1バリア層と、前記上部物質層上に具備された第2バリア層と、をさらに含んでもよい。

【0013】

前記素子層は、フィン電界効果トランジスタ(fin FET)、太陽電池、LEDまたはLDを含んでもよい。

【0014】

前記バッファ層は、前記第1物質層と同一物質または異なる物質であってもよい。

【0015】

前記第1バリア層及び第2バリア層は、前記上部物質層よりバンドギャップ(band gap)が大きくてもよい。

【0016】

前記第1バリア層及び第2バリア層は、前記第1物質層と同一物質または異なる物質であってもよい。

【0017】

前記第1物質層は、前記溝を充填した部分に空きスペースを含んでもよい。

【0018】

本発明の一実施形態による半導体素子の製造方法は、シリコン基板の上部面上に、前記上部面の一部を露出させるハードマスクを形成し、前記基板の露出した部分に溝を形成し、前記ハードマスク上に、前記溝を充填する第1物質層を成長させ、前記第1物質層上に、上部物質層を成長させ、前記上部物質層上に、素子層を形成する過程を含み、前記第1物質層は、III−V族物質層であってもよい。

【0019】

このような製造方法で、前記III−V族物質層は、III−V族化合物半導体層であってもよい。

【0020】

前記上部物質層と前記第1物質層との関係は、上述の通りである。

【0021】

前記上部物質層は、前記第1物質層の一部として形成し、前記第1物質層と前記上部物質層は、連続して成長させることができる。

【0022】

前記素子層は、上述の通りである。

【0023】

前記製造方法は、前記第1物質層の上部面を平坦化する段階と、前記第1物質層の平坦化された上部面上に、バッファ層を成長させる段階と、前記バッファ層上に、前記上部物質層を成長させる段階と、をさらに含んでもよい。

【0024】

前記バッファ層と前記第1物質層との関係は、上述の通りである。

【0025】

前記第1物質層と前記上部物質層との間に、前記上部物質層よりバンドギャップが大きい第1バリア層をさらに成長させることができる。このとき、前記上部物質層上に、前記上部物質層よりバンドギャップが大きい第2バリア層をさらに成長させることができる。

【0026】

前記第1バリア層は、前記第1物質層と同一物質または異なる物質で成長させることができる。そして、前記第2バリア層は、前記第1物質層と同一物質または異なる物質で成長させることができる。

【0027】

前記第1物質層と前記上部物質層は、二元系、三元系または四元系のIII−V族化合物半導体として成長させることができる。

【発明の効果】

【0028】

本発明の一実施形態はシリコン基板の限定された領域に所定深さの溝を形成し、前記溝でIII−V族物質の側面成長を始め、前記シリコン基板上にIII−V族物質を成長させる。このような成長方法で、シリコンとIII−V族物質との界面に形成される欠陥の存在する領域は、前記溝内に限定される。これにより、シリコン基板上に形成されたIII−V物質の欠陥密度は、既存のものより遥かに低くなる。前記III−V族物質の成長過程で、前記溝内側に成長されるIII−V族物質に、ボイド(void)のような空いた空間が形成されるように成長条件を調節することにより、シリコン基板上に形成されたIII−V物質の欠陥密度は、さらに低くなる。

【0029】

このように欠陥密度が低くなったIII−V族物質(化合物半導体)が半導体素子に使われることにより、当該半導体素子の特性は、既存のものよりさらに向上する。

【図面の簡単な説明】

【0030】

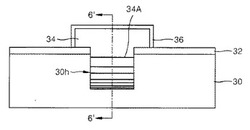

【図1】本発明の一実施形態による半導体素子の製造方法を段階別に示した断面図である。

【図2】本発明の一実施形態による半導体素子の製造方法を段階別に示した断面図である。

【図3A】本発明の一実施形態による半導体素子の製造方法を段階別に示した断面図である。

【図3B】本発明の一実施形態による半導体素子の製造方法を段階別に示した断面図である。

【図4】本発明の一実施形態による半導体素子の製造方法を段階別に示した断面図である。

【図5】本発明の一実施形態による半導体素子の製造方法を段階別に示した断面図である。

【図6】図5を6−6’方向に切開した断面図である。

【図7】図6の左側側面図である。

【図8】本発明の他の実施形態による半導体素子の断面図である。

【図9】本発明の一実施形態による半導体素子の製造方法で、基板の溝に充填された第1物質層に空きスペースが形成される場合を示した断面図である。

【図10】本発明の一実施形態による半導体素子の製造方法で、第1物質層とチャネル層(または、アクティブ層)との間に、バッファ層がさらに成長される場合を示した断面図である。

【図11】本発明の一実施形態による半導体素子の製造方法で、チャネル層(または、アクティブ層)の上部及び下部に、バリア層がさらに成長される場合を示した断面図である。

【発明を実施するための形態】

【0031】

以下、本発明の一実施形態によるIII−V族物質を含む半導体素子及びその製造方法について、添付された図面を参照しつつ詳細に説明する。この過程で、図面に図示された層や領域の厚さは、明細書の明確性のために誇張されて図示されている。

【0032】

まず、図1ないし図5を参照しつつ、本発明の一実施形態による半導体素子の製造方法について説明する。

【0033】

図1を参照すれば、基板30上に、ハードマスク32を形成する。基板30は、シリコン基板であってもよい。ハードマスク32は、例えば、シリコン酸化物マスクであってもよい。前記シリコン酸化物は、SiO2であってもよい。

【0034】

図2を参照すれば、ハードマスク32の一部を除去し、基板30の上部面の一部を露出させる。次に、図3Aに図示されているように、基板30の上部面の露出した部分を選択的にエッチングし、基板30に所定深さの溝(hole)30hを形成する。前記エッチングは、異方性エッチングであってもよい。

【0035】

一方、溝30hを形成した後、図3Bに図示されているように、溝30hの底を、絶縁層35で覆った後、後続工程を進めることもできる。このとき、絶縁層35は、シリコン酸化物層であってもよい。

【0036】

次に、図4を参照すれば、ハードマスク32上に、溝30hを充填する第1物質層34を形成する。第1物質層34は、エピタキシ(epitaxy)方法で形成する。第1物質層34は、次のような成長条件で形成されてもよい。

【0037】

例えば、第1物質層34は、MOCVD(metal organic chemical vapor deposition)法を利用して成長させる。このとき、反応器の温度は400〜500℃に維持し、100mbarの圧力下で第1物質層34を成長させるが、例えば、ガリウムソース(TMGa)と、AsH3またはTBA(tertiary-butyl-arsine)とを使ってGaAs層を成長させる。この場合、第1物質層34は、30nm厚に成長させ、成長速度は、0.05〜0.1μm/hrに維持する。この後、成長温度を550〜700℃に上げ、0.3μm/hrほどの成長速度で、さらに早く成長させる。

【0038】

このような成長条件で、第1物質層34は、垂直方向よりサイド方向に成長が早くなる。従って、第1物質層34は、溝30hの側面に垂直な方向に成長されて溝30hを充填した後、ハードマスク32上に拡張される。第1物質層34の成長と共に生じる欠陥34Aは、溝30hの側面に垂直な方向に形成される。このような欠陥34Aの密度は、溝30hの底に近いほど高く、溝30hの底から遠くなるほど低くなる。これにより、欠陥34Aのほとんどは、溝30h内に存在し、溝30h外に形成された第1物質層34には、欠陥34Aがほとんど存在しない。フィン電界効果トランジスタ(fin FET)を形成するために、第1物質層34は、溝30h周囲のハードマスク32の一部領域上にだけ形成される。このように、ハードマスク32の一部領域上にのみ第1物質層34を形成するために、ハードマスク32上に、第1物質層34を形成した後、第1物質層34を所定形態にパターニングする。他の半導体素子または光学素子を形成するために、第1物質層34は、ハードマスク32の上部面全体を覆うように形成されもする。第1物質層34は、バッファ層の役目を行うことができる。第1物質層34は、例えばIII−V族物質層であってもよい。前記III−V族物質層は、例えば、化合物半導体層を含んでもよい。前記III−V族物質層は、少なくとも1つのIII族元素と、少なくとも1つのV族元素とを含む化合物であってもよい。前記少なくとも1つのIII族元素は、例えば、In、Ga及びAlからなる群のうち少なくとも一つであってもよい。前記少なくとも1つのV族元素は、例えば、As、P及びSbからなる群のうち少なくとも一つである。これにより、第1物質層34は、III−V族の二元系、三元系または四元系の化合物層であってもよい。第1物質層34が二元系化合物層であるとき、第1物質層34は、例えば、GaAs、GaP、InP、InAs、GaSb、InSb、AlP、AlAsまたはAlSbで形成する。

【0039】

次に、図5を参照すれば、ハードマスク32の一部領域上に形成された第1物質層34上に、上部物質層として、チャネル層36を形成する。チャネル層36は、エピタキシ法で形成する。チャネル層36は、第1物質層34の上部面及び側面を覆うように形成する。チャネル層36は、第1物質層34と同一の物質で形成する。このとき、チャネル層36は、第1物質層34の表面層であってもよいし、チャネル層36を形成する工程は、第1物質層34を形成する工程に含まれる。すなわち、チャネル層36が、第1物質層34と同一の物質であるとき、第1物質層34の表面層が、チャネル層として使われるが、チャネル層36を形成するための別途の工程は、必要ではない。

【0040】

一方、チャネル層36は、第1物質層34と異なる物質で形成することもできる。このとき、チャネル層36は、上述の第1物質層34を形成する物質のうち、第1物質層34を形成するのに使われた物質を除外したいずれか1つの物質で形成する。

【0041】

次には、図5を、6−6’方向に切開した断面を示す図6を参照しつつ説明を続ける。

【0042】

図6を参照すれば、チャネル層36上に、ゲート電極40、ソース電極42及びドレイン電極44を互いに離隔させて形成する。ソース電極42及びドレイン電極44は、同時に形成する。ゲート電極40は、ソース電極42及びドレイン電極44の形成前後に形成する。ゲート電極40とチャネル層36との間にゲート絶縁膜38をさらに形成する。このようにして、シリコン基板30上に、III−V族物質で形成されたチャネル層36を有するフィン電界効果トランジスタが形成される。図6の結果物は、本発明の一実施形態による半導体素子になる。

【0043】

図7は、図6の左側側面を示している。

【0044】

図7を参照すれば、第1物質層34の上部面及び側面は、チャネル層36で覆われており、チャネル層36は、ソース電極42で覆われている。ドレイン電極44及びゲート電極40も、ソース電極42と同様に、チャネル層34の上部面及び側面を覆う形態で具備される。

【0045】

図8は、本発明の他の実施形態による半導体素子を示している。

【0046】

図8を参照すれば、第1物質層34上に、上部物質層として、アクティブ層(active layer)56が形成されている。アクティブ層56は、図5のチャネル層36と同一の方式で形成し、同一の物質で形成する。

【0047】

アクティブ層56上に、素子層(device layer)100が形成されている。素子層100は、太陽電池、発光ダイオード(LED)またはレーザダイオード(LD)を含んでもよく、LEDとLDとが集積されたOEICs(optoelectronic integrated circuits)を含んでもよい。前記太陽電池、LED、LD、OEICは、その構成が現在周知の一般的なものであってもよく、従って、これらの構成に係わる詳細な説明は省略する。

【0048】

一方、図9に図示されているように、上述の本発明の実施形態による半導体素子で、第1物質層34を形成するとき、第1物質層34の溝30hを充填する部分に、空きスペース60あるいはボイドが形成されるように第1物質層34を成長させる。空いた空間60を含む第1物質層34の成長条件は、次の通りである。

【0049】

MOCVD法を利用する。このとき、MOCVD反応器の温度は、400〜500℃に維持し、100mbar圧力で、ガリウムソース(TMGa)と、AsH3またはTBAとを使い、第1物質層34の一例として、GaAs層を60nm厚に成長する。このとき、成長速度は、0.05〜0.2μm/hrで維持するが、第1物質層34の厚さが厚くなるにつれ、成長速度を高める。その後、成長温度を550〜700℃に高め、成長速度は、0.3μm/hrで維持する。

【0050】

空いた空間60は、第1物質層34の側面成長の間、基板30と第1物質層34との格子定数差または熱膨脹係数差によるストレスを緩和させる役目が可能であり、第1物質層34の側面成長過程で生じる欠陥34Aの成長を止める役目を行うこともできる。

【0051】

他方で、図10を参照すれば、上述の本発明の実施形態による半導体素子の製造方法で、第1物質層34の上部面を平坦化し、第1物質層34の厚さを薄くした後、平坦化された第1物質層34上に、第2物質層80及びチャネル層36を順次に形成する。第2物質層80は、第1物質層34と同一の工程及び同一の物質で形成する。チャネル層36は、第2物質層80と同一の工程で形成し、同一の物質または異なる物質で形成する。チャネル層36が、第2物質層80と異なる物質で形成される場合、チャネル層36は、第2物質層80として使われる物質のうち、第2物質層80として使われる物質と異なる物質を使って形成する。

【0052】

また、図11を参照すれば、上述の本発明の実施形態による半導体素子の製造方法で、チャネル層36の下部及び上部に、それぞれ第1バリア層90及び第2バリア層92が形成されてもよい。第1バリア層90及び第2バリア層92は、チャネル層36よりバンドギャップが大きい物質で形成する。このようにして、キャリアのチャネル層36への移動の時に、界面での散乱を防止する。第1バリア層90及び第2バリア層92は、エピタキシ法で形成するが、第1物質層34を形成するときと同一の工程で形成する。第1バリア層90及び第2バリア層92は、III−V族物質、例えば、III−V族化合物半導体で形成する。このとき、第1バリア層90及び第2バリア層92として使われる物質は、第1物質層34として使われる物質のうちから選択されたものであってもよい。

【0053】

前述の説明で多くの事項が具体的に記載しているが、それらは発明の範囲を限定するものとするより、望ましい実施形態の例示として解釈されなければならない。従って、本発明の範囲は、前述の実施形態によって決められるものではなく、特許請求の範囲に記載した技術的思想によって決められなければならない。

【産業上の利用可能性】

【0054】

本発明は、高品質の基板が要求される半導体素子に適用されるが、例えば、電界効果トランジスタ、太陽電池、LED(light emitting diode)、LD(laser diode)またはパワー素子などに適用されてもよい。

【符号の説明】

【0055】

30 基板

30h 溝

32 ハードマスク

34,80 第1及び第2物質層

32A 欠陥

36 チャネル層

38 ゲート絶縁膜

40 ゲート電極

42 ソース電極

44 ドレイン電極

56 アクティブ層

60 空いた空間(ボイド)

90,92 第1バリア層及び第2バリア層

100 素子層面

【技術分野】

【0001】

本発明は、半導体素子及びその製造方法に係り、さらに詳細には、III−V族化合物半導体層を含む半導体素子及びその製造方法に関する。

【背景技術】

【0002】

半導体素子の集積度が高まると同時に、半導体素子を構成する要素のサイズが小さくなり、要素間の間隔も狭くなっている。例えば、シリコン(Si)基板トランジスタの場合、ソース、ドレイン及びゲートのサイズが小さくなるだけではなく、ソース、ドレイン及びゲートの間の間隔が狭まっている。ゲートサイズが小さくなると、チャネル長が短くなるが、短いチャネル効果(short channel effect)によって、+トランジスタの特性が低下する。

【0003】

このようなゲートサイズ限界を克服するための代案として、チャネル物質をIII−V族物質で代替する研究が進められている。また、シリコン(Si)素子とIII−V族物質とを含む光素子を1つのデバイスに集積するための試み、及び高効率のIII−V族物質を含む太陽電池を、シリコン基板の上に製造するための研究も進められている。

【0004】

しかし、III−V族物質とシリコンとの大きい結晶定数差と熱伝導度差とによって、2つの物質の界面で多くの欠陥が生じる。このような欠陥によって、III−V族物質がシリコン基板素子に適用されるのに制限が生じる。

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の一実施形態は、成長欠陥を低減させたIII−V族物質を含む半導体素子を提供するものである。

【0006】

本発明の一実施形態は、このような半導体素子の製造方法を提供するものである。

【課題を解決するための手段】

【0007】

本発明の一実施形態による半導体素子は、溝を含むシリコン基板と、前記溝周囲の前記基板上に形成されたハードマスクと、前記溝を充填する、前記ハードマスク上に形成された第1物質層と、前記第1物質層上に形成された上部物質層及び前記上部物質層上に形成された素子層と、を含み、前記第1物質層は、III−V族物質層である。

【0008】

このような半導体素子で、前記III−V族物質層は、III−V族化合物半導体層であってもよい。

【0009】

前記上部物質層は、前記第1物質層の一部であってもよい。

【0010】

前記上部物質層は、前記第1物質層と同一物質または異なる物質であってもよい。

【0011】

前記第1物質層と前記上部物質層との間に、バッファ層がさらに具備されてもよい。

【0012】

前記第1物質層と前記上部物質層との間に具備された第1バリア層と、前記上部物質層上に具備された第2バリア層と、をさらに含んでもよい。

【0013】

前記素子層は、フィン電界効果トランジスタ(fin FET)、太陽電池、LEDまたはLDを含んでもよい。

【0014】

前記バッファ層は、前記第1物質層と同一物質または異なる物質であってもよい。

【0015】

前記第1バリア層及び第2バリア層は、前記上部物質層よりバンドギャップ(band gap)が大きくてもよい。

【0016】

前記第1バリア層及び第2バリア層は、前記第1物質層と同一物質または異なる物質であってもよい。

【0017】

前記第1物質層は、前記溝を充填した部分に空きスペースを含んでもよい。

【0018】

本発明の一実施形態による半導体素子の製造方法は、シリコン基板の上部面上に、前記上部面の一部を露出させるハードマスクを形成し、前記基板の露出した部分に溝を形成し、前記ハードマスク上に、前記溝を充填する第1物質層を成長させ、前記第1物質層上に、上部物質層を成長させ、前記上部物質層上に、素子層を形成する過程を含み、前記第1物質層は、III−V族物質層であってもよい。

【0019】

このような製造方法で、前記III−V族物質層は、III−V族化合物半導体層であってもよい。

【0020】

前記上部物質層と前記第1物質層との関係は、上述の通りである。

【0021】

前記上部物質層は、前記第1物質層の一部として形成し、前記第1物質層と前記上部物質層は、連続して成長させることができる。

【0022】

前記素子層は、上述の通りである。

【0023】

前記製造方法は、前記第1物質層の上部面を平坦化する段階と、前記第1物質層の平坦化された上部面上に、バッファ層を成長させる段階と、前記バッファ層上に、前記上部物質層を成長させる段階と、をさらに含んでもよい。

【0024】

前記バッファ層と前記第1物質層との関係は、上述の通りである。

【0025】

前記第1物質層と前記上部物質層との間に、前記上部物質層よりバンドギャップが大きい第1バリア層をさらに成長させることができる。このとき、前記上部物質層上に、前記上部物質層よりバンドギャップが大きい第2バリア層をさらに成長させることができる。

【0026】

前記第1バリア層は、前記第1物質層と同一物質または異なる物質で成長させることができる。そして、前記第2バリア層は、前記第1物質層と同一物質または異なる物質で成長させることができる。

【0027】

前記第1物質層と前記上部物質層は、二元系、三元系または四元系のIII−V族化合物半導体として成長させることができる。

【発明の効果】

【0028】

本発明の一実施形態はシリコン基板の限定された領域に所定深さの溝を形成し、前記溝でIII−V族物質の側面成長を始め、前記シリコン基板上にIII−V族物質を成長させる。このような成長方法で、シリコンとIII−V族物質との界面に形成される欠陥の存在する領域は、前記溝内に限定される。これにより、シリコン基板上に形成されたIII−V物質の欠陥密度は、既存のものより遥かに低くなる。前記III−V族物質の成長過程で、前記溝内側に成長されるIII−V族物質に、ボイド(void)のような空いた空間が形成されるように成長条件を調節することにより、シリコン基板上に形成されたIII−V物質の欠陥密度は、さらに低くなる。

【0029】

このように欠陥密度が低くなったIII−V族物質(化合物半導体)が半導体素子に使われることにより、当該半導体素子の特性は、既存のものよりさらに向上する。

【図面の簡単な説明】

【0030】

【図1】本発明の一実施形態による半導体素子の製造方法を段階別に示した断面図である。

【図2】本発明の一実施形態による半導体素子の製造方法を段階別に示した断面図である。

【図3A】本発明の一実施形態による半導体素子の製造方法を段階別に示した断面図である。

【図3B】本発明の一実施形態による半導体素子の製造方法を段階別に示した断面図である。

【図4】本発明の一実施形態による半導体素子の製造方法を段階別に示した断面図である。

【図5】本発明の一実施形態による半導体素子の製造方法を段階別に示した断面図である。

【図6】図5を6−6’方向に切開した断面図である。

【図7】図6の左側側面図である。

【図8】本発明の他の実施形態による半導体素子の断面図である。

【図9】本発明の一実施形態による半導体素子の製造方法で、基板の溝に充填された第1物質層に空きスペースが形成される場合を示した断面図である。

【図10】本発明の一実施形態による半導体素子の製造方法で、第1物質層とチャネル層(または、アクティブ層)との間に、バッファ層がさらに成長される場合を示した断面図である。

【図11】本発明の一実施形態による半導体素子の製造方法で、チャネル層(または、アクティブ層)の上部及び下部に、バリア層がさらに成長される場合を示した断面図である。

【発明を実施するための形態】

【0031】

以下、本発明の一実施形態によるIII−V族物質を含む半導体素子及びその製造方法について、添付された図面を参照しつつ詳細に説明する。この過程で、図面に図示された層や領域の厚さは、明細書の明確性のために誇張されて図示されている。

【0032】

まず、図1ないし図5を参照しつつ、本発明の一実施形態による半導体素子の製造方法について説明する。

【0033】

図1を参照すれば、基板30上に、ハードマスク32を形成する。基板30は、シリコン基板であってもよい。ハードマスク32は、例えば、シリコン酸化物マスクであってもよい。前記シリコン酸化物は、SiO2であってもよい。

【0034】

図2を参照すれば、ハードマスク32の一部を除去し、基板30の上部面の一部を露出させる。次に、図3Aに図示されているように、基板30の上部面の露出した部分を選択的にエッチングし、基板30に所定深さの溝(hole)30hを形成する。前記エッチングは、異方性エッチングであってもよい。

【0035】

一方、溝30hを形成した後、図3Bに図示されているように、溝30hの底を、絶縁層35で覆った後、後続工程を進めることもできる。このとき、絶縁層35は、シリコン酸化物層であってもよい。

【0036】

次に、図4を参照すれば、ハードマスク32上に、溝30hを充填する第1物質層34を形成する。第1物質層34は、エピタキシ(epitaxy)方法で形成する。第1物質層34は、次のような成長条件で形成されてもよい。

【0037】

例えば、第1物質層34は、MOCVD(metal organic chemical vapor deposition)法を利用して成長させる。このとき、反応器の温度は400〜500℃に維持し、100mbarの圧力下で第1物質層34を成長させるが、例えば、ガリウムソース(TMGa)と、AsH3またはTBA(tertiary-butyl-arsine)とを使ってGaAs層を成長させる。この場合、第1物質層34は、30nm厚に成長させ、成長速度は、0.05〜0.1μm/hrに維持する。この後、成長温度を550〜700℃に上げ、0.3μm/hrほどの成長速度で、さらに早く成長させる。

【0038】

このような成長条件で、第1物質層34は、垂直方向よりサイド方向に成長が早くなる。従って、第1物質層34は、溝30hの側面に垂直な方向に成長されて溝30hを充填した後、ハードマスク32上に拡張される。第1物質層34の成長と共に生じる欠陥34Aは、溝30hの側面に垂直な方向に形成される。このような欠陥34Aの密度は、溝30hの底に近いほど高く、溝30hの底から遠くなるほど低くなる。これにより、欠陥34Aのほとんどは、溝30h内に存在し、溝30h外に形成された第1物質層34には、欠陥34Aがほとんど存在しない。フィン電界効果トランジスタ(fin FET)を形成するために、第1物質層34は、溝30h周囲のハードマスク32の一部領域上にだけ形成される。このように、ハードマスク32の一部領域上にのみ第1物質層34を形成するために、ハードマスク32上に、第1物質層34を形成した後、第1物質層34を所定形態にパターニングする。他の半導体素子または光学素子を形成するために、第1物質層34は、ハードマスク32の上部面全体を覆うように形成されもする。第1物質層34は、バッファ層の役目を行うことができる。第1物質層34は、例えばIII−V族物質層であってもよい。前記III−V族物質層は、例えば、化合物半導体層を含んでもよい。前記III−V族物質層は、少なくとも1つのIII族元素と、少なくとも1つのV族元素とを含む化合物であってもよい。前記少なくとも1つのIII族元素は、例えば、In、Ga及びAlからなる群のうち少なくとも一つであってもよい。前記少なくとも1つのV族元素は、例えば、As、P及びSbからなる群のうち少なくとも一つである。これにより、第1物質層34は、III−V族の二元系、三元系または四元系の化合物層であってもよい。第1物質層34が二元系化合物層であるとき、第1物質層34は、例えば、GaAs、GaP、InP、InAs、GaSb、InSb、AlP、AlAsまたはAlSbで形成する。

【0039】

次に、図5を参照すれば、ハードマスク32の一部領域上に形成された第1物質層34上に、上部物質層として、チャネル層36を形成する。チャネル層36は、エピタキシ法で形成する。チャネル層36は、第1物質層34の上部面及び側面を覆うように形成する。チャネル層36は、第1物質層34と同一の物質で形成する。このとき、チャネル層36は、第1物質層34の表面層であってもよいし、チャネル層36を形成する工程は、第1物質層34を形成する工程に含まれる。すなわち、チャネル層36が、第1物質層34と同一の物質であるとき、第1物質層34の表面層が、チャネル層として使われるが、チャネル層36を形成するための別途の工程は、必要ではない。

【0040】

一方、チャネル層36は、第1物質層34と異なる物質で形成することもできる。このとき、チャネル層36は、上述の第1物質層34を形成する物質のうち、第1物質層34を形成するのに使われた物質を除外したいずれか1つの物質で形成する。

【0041】

次には、図5を、6−6’方向に切開した断面を示す図6を参照しつつ説明を続ける。

【0042】

図6を参照すれば、チャネル層36上に、ゲート電極40、ソース電極42及びドレイン電極44を互いに離隔させて形成する。ソース電極42及びドレイン電極44は、同時に形成する。ゲート電極40は、ソース電極42及びドレイン電極44の形成前後に形成する。ゲート電極40とチャネル層36との間にゲート絶縁膜38をさらに形成する。このようにして、シリコン基板30上に、III−V族物質で形成されたチャネル層36を有するフィン電界効果トランジスタが形成される。図6の結果物は、本発明の一実施形態による半導体素子になる。

【0043】

図7は、図6の左側側面を示している。

【0044】

図7を参照すれば、第1物質層34の上部面及び側面は、チャネル層36で覆われており、チャネル層36は、ソース電極42で覆われている。ドレイン電極44及びゲート電極40も、ソース電極42と同様に、チャネル層34の上部面及び側面を覆う形態で具備される。

【0045】

図8は、本発明の他の実施形態による半導体素子を示している。

【0046】

図8を参照すれば、第1物質層34上に、上部物質層として、アクティブ層(active layer)56が形成されている。アクティブ層56は、図5のチャネル層36と同一の方式で形成し、同一の物質で形成する。

【0047】

アクティブ層56上に、素子層(device layer)100が形成されている。素子層100は、太陽電池、発光ダイオード(LED)またはレーザダイオード(LD)を含んでもよく、LEDとLDとが集積されたOEICs(optoelectronic integrated circuits)を含んでもよい。前記太陽電池、LED、LD、OEICは、その構成が現在周知の一般的なものであってもよく、従って、これらの構成に係わる詳細な説明は省略する。

【0048】

一方、図9に図示されているように、上述の本発明の実施形態による半導体素子で、第1物質層34を形成するとき、第1物質層34の溝30hを充填する部分に、空きスペース60あるいはボイドが形成されるように第1物質層34を成長させる。空いた空間60を含む第1物質層34の成長条件は、次の通りである。

【0049】

MOCVD法を利用する。このとき、MOCVD反応器の温度は、400〜500℃に維持し、100mbar圧力で、ガリウムソース(TMGa)と、AsH3またはTBAとを使い、第1物質層34の一例として、GaAs層を60nm厚に成長する。このとき、成長速度は、0.05〜0.2μm/hrで維持するが、第1物質層34の厚さが厚くなるにつれ、成長速度を高める。その後、成長温度を550〜700℃に高め、成長速度は、0.3μm/hrで維持する。

【0050】

空いた空間60は、第1物質層34の側面成長の間、基板30と第1物質層34との格子定数差または熱膨脹係数差によるストレスを緩和させる役目が可能であり、第1物質層34の側面成長過程で生じる欠陥34Aの成長を止める役目を行うこともできる。

【0051】

他方で、図10を参照すれば、上述の本発明の実施形態による半導体素子の製造方法で、第1物質層34の上部面を平坦化し、第1物質層34の厚さを薄くした後、平坦化された第1物質層34上に、第2物質層80及びチャネル層36を順次に形成する。第2物質層80は、第1物質層34と同一の工程及び同一の物質で形成する。チャネル層36は、第2物質層80と同一の工程で形成し、同一の物質または異なる物質で形成する。チャネル層36が、第2物質層80と異なる物質で形成される場合、チャネル層36は、第2物質層80として使われる物質のうち、第2物質層80として使われる物質と異なる物質を使って形成する。

【0052】

また、図11を参照すれば、上述の本発明の実施形態による半導体素子の製造方法で、チャネル層36の下部及び上部に、それぞれ第1バリア層90及び第2バリア層92が形成されてもよい。第1バリア層90及び第2バリア層92は、チャネル層36よりバンドギャップが大きい物質で形成する。このようにして、キャリアのチャネル層36への移動の時に、界面での散乱を防止する。第1バリア層90及び第2バリア層92は、エピタキシ法で形成するが、第1物質層34を形成するときと同一の工程で形成する。第1バリア層90及び第2バリア層92は、III−V族物質、例えば、III−V族化合物半導体で形成する。このとき、第1バリア層90及び第2バリア層92として使われる物質は、第1物質層34として使われる物質のうちから選択されたものであってもよい。

【0053】

前述の説明で多くの事項が具体的に記載しているが、それらは発明の範囲を限定するものとするより、望ましい実施形態の例示として解釈されなければならない。従って、本発明の範囲は、前述の実施形態によって決められるものではなく、特許請求の範囲に記載した技術的思想によって決められなければならない。

【産業上の利用可能性】

【0054】

本発明は、高品質の基板が要求される半導体素子に適用されるが、例えば、電界効果トランジスタ、太陽電池、LED(light emitting diode)、LD(laser diode)またはパワー素子などに適用されてもよい。

【符号の説明】

【0055】

30 基板

30h 溝

32 ハードマスク

34,80 第1及び第2物質層

32A 欠陥

36 チャネル層

38 ゲート絶縁膜

40 ゲート電極

42 ソース電極

44 ドレイン電極

56 アクティブ層

60 空いた空間(ボイド)

90,92 第1バリア層及び第2バリア層

100 素子層面

【特許請求の範囲】

【請求項1】

溝を含むシリコン基板と、

前記溝周囲の前記基板上に形成された成長防止層と、

前記溝を充填する、前記成長防止層上に形成された第1物質層と、

前記第1物質層上に形成された上部物質層と、

前記上部物質層上に形成された素子層と、を含み、

前記第1物質層は、III−V族物質層である半導体素子。

【請求項2】

前記III−V族物質層は、III−V族化合物半導体層であることを特徴とする請求項1に記載の半導体素子。

【請求項3】

前記上部物質層は、前記第1物質層の一部であることを特徴とする請求項1に記載の半導体素子。

【請求項4】

前記上部物質層は、前記第1物質層と同一物質または異なる物質であることを特徴とする請求項1に記載の半導体素子。

【請求項5】

前記第1物質層と前記上部物質層との間に、バッファ層がさらに具備されたことを特徴とする請求項1に記載の半導体素子。

【請求項6】

前記第1物質層と前記上部物質層との間に具備された第1バリア層と、

前記上部物質層上に具備された第2バリア層と、をさらに含むことを特徴とする請求項1に記載の半導体素子。

【請求項7】

前記素子層は、フィン電界効果トランジスタ、太陽電池、LEDまたはLDを含むことを特徴とする請求項1に記載の半導体素子。

【請求項8】

前記バッファ層は、前記第1物質層と同一物質または異なる物質であることを特徴とする請求項5に記載の半導体素子。

【請求項9】

前記第1バリア層及び第2バリア層は、前記上部物質層よりバンドギャップが大きいことを特徴とする請求項6に記載の半導体素子。

【請求項10】

前記第1バリア層及び第2バリア層は、前記第1物質層と同一物質または異なる物質であることを特徴とする請求項6に記載の半導体素子。

【請求項11】

前記第1物質層は、前記溝を充填した部分に空きスペースを含むことを特徴とする請求項1に記載の半導体素子。

【請求項12】

前記素子層は、フィン電界効果トランジスタ、太陽電池、LEDまたはLDを含むことを特徴とする請求項5に記載の半導体素子。

【請求項13】

前記素子層は、フィン電界効果トランジスタ、太陽電池、LEDまたはLDを含むことを特徴とする請求項6に記載の半導体素子。

【請求項14】

シリコン基板の上部面上に、前記上部面の一部を露出させるハードマスクを形成する段階と、

前記基板の露出した部分に溝を形成する段階と、

前記ハードマスク上に、前記溝を充填する第1物質層を成長させる段階と、

前記第1物質層上に、上部物質層を成長させる段階と、

前記上部物質層上に、素子層を形成する段階と、を含み、

前記第1物質層は、III−V族物質層である半導体素子の製造方法。

【請求項15】

前記III−V族物質層は、III−V族化合物半導体層であることを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項16】

前記上部物質層は、前記第1物質層と同一の物質または異なる物質で成長させることを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項17】

前記上部物質層は、前記第1物質層の一部として形成し、前記第1物質層と前記上部物質層は、連続して成長させることを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項18】

前記素子層は、フィン電界効果トランジスタ(fin FET)、太陽電池、LEDまたはLDを含むことを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項19】

前記第1物質層の上部面を平坦化する段階と、

前記第1物質層の平坦化された上部面上に、バッファ層を成長させる段階と、

前記バッファ層上に、前記上部物質層を成長させる段階と、を含むことを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項20】

前記バッファ層は、前記第1物質層と同一物質または異なる物質で成長させることを特徴とする請求項19に記載の半導体素子の製造方法。

【請求項21】

前記第1物質層と前記上部物質層との間に、前記上部物質層よりバンドギャップが大きい第1バリア層をさらに成長させることを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項22】

前記上部物質層上に、前記上部物質層よりバンド値が大きい第2バリア層をさらに成長させることを特徴とする請求項21に記載の半導体素子の製造方法。

【請求項23】

前記第1バリア層は、前記第1物質層と同一物質または異なる物質で成長させることを特徴とする請求項21に記載の半導体素子の製造方法。

【請求項24】

前記第2バリア層は、前記第1物質層と同一物質または異なる物質で成長させることを特徴とする請求項21に記載の半導体素子の製造方法。

【請求項25】

前記第1物質層と前記上部物質層は、二元系、三元系または四元系のIII−V族化合物半導体として成長させることを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項1】

溝を含むシリコン基板と、

前記溝周囲の前記基板上に形成された成長防止層と、

前記溝を充填する、前記成長防止層上に形成された第1物質層と、

前記第1物質層上に形成された上部物質層と、

前記上部物質層上に形成された素子層と、を含み、

前記第1物質層は、III−V族物質層である半導体素子。

【請求項2】

前記III−V族物質層は、III−V族化合物半導体層であることを特徴とする請求項1に記載の半導体素子。

【請求項3】

前記上部物質層は、前記第1物質層の一部であることを特徴とする請求項1に記載の半導体素子。

【請求項4】

前記上部物質層は、前記第1物質層と同一物質または異なる物質であることを特徴とする請求項1に記載の半導体素子。

【請求項5】

前記第1物質層と前記上部物質層との間に、バッファ層がさらに具備されたことを特徴とする請求項1に記載の半導体素子。

【請求項6】

前記第1物質層と前記上部物質層との間に具備された第1バリア層と、

前記上部物質層上に具備された第2バリア層と、をさらに含むことを特徴とする請求項1に記載の半導体素子。

【請求項7】

前記素子層は、フィン電界効果トランジスタ、太陽電池、LEDまたはLDを含むことを特徴とする請求項1に記載の半導体素子。

【請求項8】

前記バッファ層は、前記第1物質層と同一物質または異なる物質であることを特徴とする請求項5に記載の半導体素子。

【請求項9】

前記第1バリア層及び第2バリア層は、前記上部物質層よりバンドギャップが大きいことを特徴とする請求項6に記載の半導体素子。

【請求項10】

前記第1バリア層及び第2バリア層は、前記第1物質層と同一物質または異なる物質であることを特徴とする請求項6に記載の半導体素子。

【請求項11】

前記第1物質層は、前記溝を充填した部分に空きスペースを含むことを特徴とする請求項1に記載の半導体素子。

【請求項12】

前記素子層は、フィン電界効果トランジスタ、太陽電池、LEDまたはLDを含むことを特徴とする請求項5に記載の半導体素子。

【請求項13】

前記素子層は、フィン電界効果トランジスタ、太陽電池、LEDまたはLDを含むことを特徴とする請求項6に記載の半導体素子。

【請求項14】

シリコン基板の上部面上に、前記上部面の一部を露出させるハードマスクを形成する段階と、

前記基板の露出した部分に溝を形成する段階と、

前記ハードマスク上に、前記溝を充填する第1物質層を成長させる段階と、

前記第1物質層上に、上部物質層を成長させる段階と、

前記上部物質層上に、素子層を形成する段階と、を含み、

前記第1物質層は、III−V族物質層である半導体素子の製造方法。

【請求項15】

前記III−V族物質層は、III−V族化合物半導体層であることを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項16】

前記上部物質層は、前記第1物質層と同一の物質または異なる物質で成長させることを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項17】

前記上部物質層は、前記第1物質層の一部として形成し、前記第1物質層と前記上部物質層は、連続して成長させることを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項18】

前記素子層は、フィン電界効果トランジスタ(fin FET)、太陽電池、LEDまたはLDを含むことを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項19】

前記第1物質層の上部面を平坦化する段階と、

前記第1物質層の平坦化された上部面上に、バッファ層を成長させる段階と、

前記バッファ層上に、前記上部物質層を成長させる段階と、を含むことを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項20】

前記バッファ層は、前記第1物質層と同一物質または異なる物質で成長させることを特徴とする請求項19に記載の半導体素子の製造方法。

【請求項21】

前記第1物質層と前記上部物質層との間に、前記上部物質層よりバンドギャップが大きい第1バリア層をさらに成長させることを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項22】

前記上部物質層上に、前記上部物質層よりバンド値が大きい第2バリア層をさらに成長させることを特徴とする請求項21に記載の半導体素子の製造方法。

【請求項23】

前記第1バリア層は、前記第1物質層と同一物質または異なる物質で成長させることを特徴とする請求項21に記載の半導体素子の製造方法。

【請求項24】

前記第2バリア層は、前記第1物質層と同一物質または異なる物質で成長させることを特徴とする請求項21に記載の半導体素子の製造方法。

【請求項25】

前記第1物質層と前記上部物質層は、二元系、三元系または四元系のIII−V族化合物半導体として成長させることを特徴とする請求項14に記載の半導体素子の製造方法。

【図1】

【図2】

【図3A】

【図3B】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3A】

【図3B】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−98559(P2013−98559A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2012−236618(P2012−236618)

【出願日】平成24年10月26日(2012.10.26)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成24年10月26日(2012.10.26)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

[ Back to top ]