III族窒化物化合物半導体発光素子の製造方法、及びIII族窒化物化合物半導体発光素子、並びにランプ

【課題】生産性に優れるとともに、優れた発光特性を備えたIII族窒化物化合物半導体発光素子の製造方法、及びIII族窒化物化合物半導体発光素子、並びにランプを提供する。

【解決手段】基板11上に、III族元素としてGaを含むIII族窒化物化合物半導体からなる半導体層をスパッタ法によって成膜する工程を含む製造方法であり、半導体層をスパッタ法で成膜する際に、基板11に印加するバイアス値を0.1W/cm2以上とする。

【解決手段】基板11上に、III族元素としてGaを含むIII族窒化物化合物半導体からなる半導体層をスパッタ法によって成膜する工程を含む製造方法であり、半導体層をスパッタ法で成膜する際に、基板11に印加するバイアス値を0.1W/cm2以上とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、発光ダイオード(LED)、レーザダイオード(LD)、電子デバイス等に好適に用いられるIII族窒化物化合物半導体発光素子の製造方法に関し、特に、結晶性の良好なIII族窒化物化合物半導体結晶を基板上にエピタキシャル成長させることが可能なIII族窒化物化合物半導体発光素子の製造方法、及びIII族窒化物化合物半導体発光素子、並びにランプに関する。

【背景技術】

【0002】

III族窒化物半導体発光素子は、可視光から紫外光領域の範囲に相当するエネルギーの直接遷移型のバンドギャップを有し、発光効率に優れていることから、LEDやLD等の発光素子として用いられている。

また、電子デバイスに用いた場合でも、III族窒化物半導体発光素子は、従来のIII−V族化合物半導体を用いた場合に比べ、優れた特性を有する電子デバイスが得られる。

【0003】

このようなIII族窒化物化合物半導体は、一般的に、トリメチルガリウム、トリメチルアルミニウムおよびアンモニアを原料として、MOCVD法によって製造されている。MOCVD法は、キャリアガスに原料の蒸気を含ませて基板表面に運搬し、加熱された基板との反応で分解することにより、結晶を成長させる方法である。

【0004】

従来、III−V族化合物半導体の単結晶ウェーハとしては、異なる材料の単結晶ウェーハ上に結晶を成長させて得る方法が一般的である。このような、異種基板と、その上にエピタキシャル成長させるIII族窒化物半導体結晶との間には、大きな格子不整合が存在する。例えば、サファイア(Al2O3)基板上に窒化ガリウム(GaN)を成長させた場合、両者の間には16%の格子不整合が存在し、SiC基板上に窒化ガリウムを成長させた場合には、両者の間に6%の格子不整合が存在する。

一般に、上述のような大きな格子不整合が存在する場合、基板上に結晶を直接エピタキシャル成長させることが困難となり、また、成長させた場合であっても結晶性の良好な結晶が得られないという問題がある。

【0005】

そこで、有機金属化学気相成長(MOCVD)法により、サファイア単結晶基板もしくはSiC単結晶基板の上に、III族窒化物半導体結晶をエピタキシャル成長させる際、基板上に、まず、窒化アルミニウム(AlN)やAlGaNからなる低温バッファ層と呼ばれる層を積層し、その上に高温でIII族窒化物半導体結晶をエピタキシャル成長させる方法が提案されており、一般に行われている(例えば、特許文献1、2)。

【0006】

一方、III族窒化物化合物半導体結晶をスパッタによって製造する研究も行われており、例えば、N2ガスを用いた高周波マグネトロンスパッタリングにより、Si(100)及びAl2O3(0001)上にGaN膜を成膜する方法が提案されている(例えば、非特許文献1)。非特許文献1に記載の方法では、成膜の条件として、全ガス圧力を2mTorr、投入電力を100Wとし、基板温度をRT〜900℃まで変化させており、また、スパッタ装置として、ターゲットと基板とを対向させたものが用いられている。

【0007】

また、カソードとターゲットとを向かい合わせ、基板とターゲットとの間にメッシュを入れた装置を用いてGaNを成膜する方法が提案されている(例えば、非特許文献2)。非特許文献2に記載の方法では、成膜条件として、N2ガス中で圧力を0.67Paとし、基板温度を84〜600℃とし、投入電力を150W、基板とターゲットとの間の距離を80mmとしている。

【0008】

また、ターゲット同士を向かい合わせた対面カソードと呼ばれる方式で、基板上にAlNを成膜する方法が提案されている(例えば、非特許文献3)。

また、DCマグネトロンスパッタリング法を用いて、基板上にAlNを成膜する方法が提案されている(例えば、非特許文献4)。非特許文献4に記載の方法では、基板とターゲットとを対向させ、ArとN2の混合ガス雰囲気中でスパッタを行なっており、成膜条件として、圧力を0.2〜0.8Paの範囲、基板とターゲットとの距離を60〜180mmの間で変化させている。

【0009】

また、バッファ層としてAlN等の層をMOCVD以外の方法で成膜し、その上に成膜される層をMOCVD法で成膜する方法に関し、例えば、高周波スパッタで成膜したバッファ層上に、MOCVD法で同じ組成の結晶を成長させる方法が提案されている(例えば、特許文献3)。しかしながら、特許文献3に記載の方法では、安定して良好な結晶を得ることができないという問題がある(特許文献4、5を参照)。

【0010】

そこで、安定して良好な結晶を得るため、例えば、バッファ層成長後にアンモニアと水素からなる混合ガス中でアニールする方法(例えば、特許文献4)や、バッファ層を400℃以上の温度でDCスパッタにより成膜する方法(例えば、特許文献5)が提案されている。

また、特許文献4及び5に記載の方法では、基板材料として、サファイア、シリコン、炭化シリコン、酸化亜鉛、リン化ガリウム、ヒ化ガリウム、酸化マグネシウム、酸化マンガン、III族窒化物系化合物半導体単結晶等が用いられ、中でもサファイアのa面基板が好適とされている。

【特許文献1】特許第3026087号公報

【特許文献2】特開平4−297023号公報

【特許文献3】特公平5−86646号公報

【特許文献4】特許第3440873号公報

【特許文献5】特許第3700492号公報

【非特許文献1】牛玖 由紀子(Y.USHIKU)他、「21世紀連合シンポジウム論文集」、Vol.2nd、p295(2003)、

【非特許文献2】ティー・キクマ(T.Kikuma)他、「バキューム(Vacuum)」、Vol.66、P233(2002)

【非特許文献3】キクオ・トミナガ(Kikuo Tominaga)他、「ジャパニーズ・ジャーナル・オブ・アプライド・オブ・フィジックス(Japanese Journal of Applied Physics)」、Vol.28、p7(1989)

【非特許文献4】エム・イシハラ(M.Ishihara)他、「スィン・ソリッド・フィルム(Thin Solid Films)」、vol.316、p152(1998)

【発明の開示】

【発明が解決しようとする課題】

【0011】

しかしながら、本出願人等が鋭意実験、検討を行なった結果、特許文献4及び5に記載の条件で成膜を行なった場合でも、III族元素としてGaを含むIII族窒化物化合物半導体を、安定して良好な結晶で得ることができないことが明らかとなった。即ち、特許文献4、5に記載の方法では、スパッタ法で成膜されたバッファ層上にMOCVD法によってGaN層を成膜している。スパッタ法によってバッファ層を成膜した場合、成膜速度が速い反面、成膜条件によっては、結晶性に劣るバッファ層となる場合がある。このような結晶性の低いバッファ層上に、MOCVD法によってGaN層を成長させると、GaN層の結晶性が大幅に低下する虞があった。

また、非特許文献1、2に記載の条件を用いて、スパッタ法でGaN層を成膜した場合であっても、バッファ層上に結晶性の良好なGaN層を形成するのが困難であるという問題があった。

【0012】

本発明は上記課題に鑑みてなされたものであり、均一性の良好なIII族窒化物化合物半導体からなる結晶膜を、安定して短時間で形成することができ、生産性に優れるとともに、優れた発光特性を備えたIII族窒化物化合物半導体発光素子の製造方法、及びIII族窒化物化合物半導体発光素子、並びにランプを提供することを目的とする。

【課題を解決するための手段】

【0013】

本発明者は、上記問題を解決するために鋭意検討した結果、本発明を完成した。

即ち、本発明は以下に関する。

【0014】

[1] 基板上に、III族元素としてGaを含むIII族窒化物化合物半導体からなる半導体層をスパッタ法によって成膜する工程を含むIII族窒化物化合物半導体発光素子の製造方法であって、前記半導体層をスパッタ法で成膜する際に、前記基板に印加するバイアス値を0.1W/cm2以上とすることを特徴とするIII族窒化物化合物半導体発光素子の製造方法。

[2] 基板上に、III族元素としてGaを含むIII族窒化物化合物半導体からなる半導体層をスパッタ法によって成膜する工程を含むIII族窒化物化合物半導体発光素子の製造方法であって、前記半導体層をスパッタ法で成膜する際に、スパッタターゲットに印加するパワーを0.1W/cm2〜100W/cm2の範囲とすることを特徴とするIII族窒化物化合物半導体発光素子の製造方法。

【0015】

[3] 窒化物原料をリアクタ内に流通させるリアクティブスパッタ法によって前記半導体層を成膜することを特徴とする[1]又は[2]に記載のIII族窒化物化合物半導体発光素子の製造方法。

[4] 前記窒化物原料として窒素を用いたことを特徴とする[3]に記載のIII族窒化物化合物半導体発光素子の製造方法。

【0016】

[5] 前記基板と前記半導体層との間に、柱状結晶からなるバッファ層を形成することを特徴とする[1]〜[4]の何れかに記載のIII族窒化物化合物半導体発光素子の製造方法。

[6] 前記バッファ層を、スパッタ法で形成することを特徴とする[5]に記載のIII族窒化物化合物半導体発光素子の製造方法。

[7] 前記バッファ層を、Alを含有するIII族窒化物化合物で形成することを特徴とする[6]に記載のIII族窒化物化合物半導体発光素子の製造方法。

[8] 前記バッファ層を、AlNで形成することを特徴とする[7]に記載のIII族窒化物化合物半導体発光素子の製造方法。

[9] 前記バッファ層を、前記基板の表面の少なくとも90%以上を覆うように形成することを特徴とする[5]〜[8]の何れかに記載のIII族窒化物化合物半導体発光素子の製造方法。

[10] 前記バッファ層を構成する柱状結晶の幅が0.1〜100nmの範囲であることを特徴とする[5]〜[9]の何れかに記載のIII族窒化物化合物半導体発光素子の製造方法。

[11] 前記バッファ層の膜厚が10〜500nmの範囲であることを特徴とする[5]〜[10]の何れかに記載のIII族窒化物化合物半導体発光素子の製造方法。

[12] 前記バッファ層をAlNで形成するとともに、III族窒化物化合物からなる前記半導体層をGaNで形成することを特徴とする[5]〜[11]の何れかに記載のIII族窒化物化合物半導体発光素子の製造方法。

[13] 前記基板にサファイアを用いることを特徴とする[1]〜[12]の何れかに記載のIII族窒化物化合物半導体発光素子の製造方法。

【0017】

[14] 上記[1]〜[13]の何れかに記載の製造方法で得られるIII族窒化物化合物半導体発光素子。

[15] 上記[14]に記載のIII族窒化物化合物半導体発光素子が用いられてなるランプ。

【発明の効果】

【0018】

本発明のIII族窒化物化合物半導体発光素子の製造方法によれば、上記構成により、均一性の良好な結晶膜を、スパッタ法によって短時間で形成することができる。これにより、結晶性の良好なIII族窒化物化合物半導体層を、安定して形成することが可能となる。従って、生産性に優れるとともに、優れた発光特性を備えたIII族窒化物化合物半導体発光素子が得られる。

【発明を実施するための最良の形態】

【0019】

以下に、本発明に係るIII族窒化物化合物半導体発光素子の製造方法、及びIII族窒化物化合物半導体発光素子、並びにランプの一実施形態について、図1〜7を適宜参照しながら説明する。

【0020】

本実施形態のIII族窒化物化合物半導体発光素子(以下、発光素子と略称することがある)の製造方法は、基板上に、少なくともスパッタ法を用いてIII族窒化物化合物半導体からなる半導体層を成膜する方法であって、III族窒化物化合物半導体としてGaを含有する化合物を用いる方法である。

【0021】

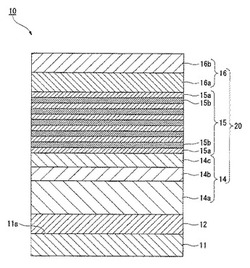

本実施形態の製造方法によって得られる発光素子の積層構造を、図1に例示する積層半導体10を用いて説明する。この積層半導体10は、基板11上にIII族窒化物化合物からなるバッファ層12が積層され、該バッファ層12上に、n型半導体層14、発光層15、及びp型半導体層16が順次積層されてなる半導体層20が形成されている。

そして、本実施形態の積層半導体10は、図2及び図3に示す例のように、p型半導体層16上に透光性正極17が積層され、その上に正極ボンディングパッド18形成されるとともに、n型半導体層14のn型コンタクト層14bに形成された露出領域14dに負極19が積層されてなる発光素子1を構成することができる。

【0022】

[スパッタ法を用いた半導体層の成膜]

本発明に係る発光素子の製造方法は、上述したように、少なくともスパッタ法を用いて基板11上に半導体層20を構成する層を成膜する方法であり、本実施形態では、半導体層20の内、n型半導体層14を構成する下地層14a及びn型コンタクト層14bを、スパッタ法によって成膜する方法としている。

結晶性に優れたIII族窒化物化合物半導体を、スパッタ法を用いて基板上に成膜するためには、よりエネルギーの高い反応種を生成して基板上におけるマイグレーションを活発にする必要があることから、本実施形態では以下に詳述するような方法としている。

【0023】

本実施形態の製造方法で用いるスパッタ法としては、RF(高周波)スパッタ法、又はDCスパッタ法を用いることにより、スパッタターゲットに対してパワーを印加することが好ましい。

また、一般に、後述するリアクティブスパッタ法を用いた場合には、成膜レートを容易にコントロールできる点から、RFスパッタ法を用いることがより好ましい。

また、DCスパッタ法では、リアクティブスパッタ法を用いる場合、DCで電場を連続してかけた状態にするとスパッタターゲットがチャージアップしてしまい、成膜レートを高くすることが困難になるため、パルス的にバイアスを与えるパルス式DCスパッタ法とすることが好ましい。

【0024】

また、半導体層をスパッタ法によって成膜する場合、窒化物原料をリアクタ内に流通させるリアクティブスパッタ法によって成膜する方法とすることが、反応を制御することで結晶性を良好に保つことができ、その良好な結晶性を安定に再現することができる点でより好ましい。

【0025】

また、本実施形態では、スパッタ法で半導体層を成膜する際、ターゲット47に対し、磁場を回転させるか、又は磁場を揺動させることが好ましい。

特に、RFスパッタを用いた場合、チャージアップを回避する方法として、マグネットの位置をターゲット(スパッタターゲット)内で移動させつつ成膜することが好ましい。具体的なマグネットの運動方法は、スパッタ装置の種類によって適宜選択することができ、例えば、マグネットを揺動させたり、又は回転運動させたりすることができる。

【0026】

図7に例示するRFスパッタ装置40では、金属ターゲット(スパッタターゲット)47の下方(図7の下方)にマグネット42が配され、該マグネット42が図示略の駆動装置によって金属ターゲット47の下方で揺動する。チャンバ41には窒素ガス、及びアルゴンガスが供給され、ヒータ44に取り付けられた基板11上に半導体層が成膜される。

【0027】

本実施形態では、スパッタ法を用いた成膜における重要なパラメータとして、バイアス、ターゲットに印加するパワー、基板温度、炉内の圧力、窒素分圧や成膜レート等が挙げられる。

【0028】

本実施形態の製造方法では、スパッタ法で半導体層を成膜する際、基板11に印加するバイアス値を0.1W/cm2以上とすることが好ましく、0.2W/cm2以上とすることがより好ましく、0.5W/cm2以上とすることが最も好ましい。

基板11に印加するバイアス値を上記とすることにより、高バイアスの反応種を生成し、また、この反応種を高い運動エネルギーで基板11へ供給できるので、基板11上におけるマイグレーションが活発になり、転位をループ化させるのが容易になる。

【0029】

また、本実施形態の製造方法では、スパッタ法で半導体層を成膜する際、金属ターゲット(スパッタターゲット)47に印加するパワーを0.1W/cm2〜100W/cm2の範囲とすることが好ましく、1W/cm2〜50W/cm2の範囲とすることがより好ましく、1.5W/cm2〜50W/cm2の範囲とすることが最も好ましい。

金属ターゲット47に印加するパワーを上記範囲とすることにより、大きなパワーの反応種を生成し、また、この反応種を高い運動エネルギーで基板11へ供給できるので、基板11上におけるマイグレーションが活発になり、転位をループ化させるのが容易になる。

【0030】

また、スパッタ法で成膜する際のチャンバ41内の実際の圧力は、0.3Pa以上であることが好ましい。チャンバ41内の圧力が0.3Pa未満とすると、窒素の存在量が小さくなり過ぎ、スパッタされた金属が窒化物とならない状態で基板11上に付着する虞がある。また、チャンバ41内の圧力の上限は特に限定されないが、プラズマを発生させることができる程度の圧力に抑制することが必要である。

【0031】

また、窒素(N2)とArの流量に対する窒素流量の比は、N2が20%以上98%以下の範囲であることが好ましい。この範囲を下回る流量比だと、スパッタ金属が金属のまま基板に付着してしまう。また、上記範囲を上回る流量比だと、Arの量が少な過ぎるためにスパッタレートが低下してしまう。

窒素(N2)とArの流量に対する窒素流量の比は、特に好ましくは、25%以上90%以下の範囲である。

【0032】

本実施形態の製造方法では、上述のように、スパッタ装置のチャンバ内におけるガス中の窒素濃度を高くし、さらに、重量の大きな気体であるArを上記流量比で混合している。チャンバ内のガスが窒素のみの場合だと、金属ターゲット47を叩く力が弱いために、成膜レートが制限されてしまうところ、本実施形態では、重量の大きなArと上記流量比で混合することにより、成膜レートを向上させるとともに、基板11上におけるマイグレーションを活発にすることができる。

【0033】

本実施形態で用いる窒素原料としては、一般に知られている窒素化合物を何ら制限されることなく用いることができるが、アンモニアや窒素(N2)は取り扱いが簡単であるとともに、比較的安価で入手可能であることから好ましい。

アンモニアは分解効率が良好であり、高い成長速度で成膜することが可能であるが、反応性や毒性が高いため、除害設備やガス検知器が必要となり、また、反応装置に使用する部材の材料を安定性の高いものにする必要がある。

また、窒素(N2)を原料として用いた場合には、装置としては簡便なものを用いることができるが、高い反応速度は得られない。しかしながら、窒素を電界や熱等により分解してから装置に導入する方法とすれば、アンモニアよりは低いものの工業生産的に利用可能な程度の成膜速度を得ることができるため、装置コストとの兼ね合いを考えると、最も好適な窒素源である。

【0034】

スパッタ法を用いた成膜の際の成膜レートは、0.01nm/s〜10nm/sの範囲とすることが好ましい。成膜レートが0.01nm/s未満だと、成膜プロセスが長時間となってしまい、工業生産的に無駄が大きくなる。成膜レートが10nm/sを超えると、良好な結晶を得ることが困難となる。

【0035】

本実施形態の製造方法では、少なくともスパッタ法を用いて半導体層20の内、n型半導体層14を構成する下地層14a及びn型コンタクト層14bを成膜するので、成膜レートを高くすることができ、成膜(製造)時間を短縮することが可能となる。製造時間が短縮されることにより、スパッタ装置内のチャンバ内に不純物が入り込むのを最小限に抑制することができる。

【0036】

基板11は、湿式の前処理を行うことが望ましい。例えば、シリコンからなる基板11に対しては、よく知られたRCA洗浄方法などを行い、表面を水素終端させておくことにより、成膜プロセスが安定する。

また、基板11は、反応器の中に導入した後、バッファ層12を形成する前に、スパッタ法等の方法を用いて前処理を行うことができる。具体的には、基板11をArやN2のプラズマ中に曝す事によって表面を整えることができる。例えば、ArガスやN2ガスなどのプラズマを基板11表面に作用させることで、基板11表面に付着した有機物や酸化物を除去することができる。この場合、基板11とチャンバとの間に電圧を印加すれば、プラズマ粒子が効率的に基板11に作用する。

【0037】

本発明者等が鋭意実験、検討を行なったところ、成膜時の基板11の温度は、室温〜1200℃の範囲とすることが好ましく、300〜1000℃の範囲とすることがより好ましく、500〜800℃の範囲とすることが最も好ましい。

基板11の温度が上記下限未満だと、基板11上でのマイグレーションが抑制され、結晶性の良いIII族窒化物化合物半導体結晶を成膜することができない。基板11の温度が上記上限を超えると、III族窒化物化合物半導体結晶が分解する虞がある。

なお、本発明で説明する室温とは、工程の環境等にも影響される温度であるが、具体的な温度としては、0〜30℃の範囲である。

【0038】

本実施形態の製造方法では、スパッタ法による成膜時の基板11の温度を上記範囲とし、基板温度を高くすることにより、基板11に到達した反応種(金属ターゲット47から取り出された金属)の、結晶表面での運動を活性化することができる。

【0039】

スパッタ法を用いて混晶を成膜する際には、ターゲットとなる金属を予め金属材料の混合物(必ずしも、合金を形成していなくても構わない)として行う方法もあるし、また、異なる材料からなる2つのターゲットを用意して同時にスパッタする方法としても良い。

例えば、一定の組成の膜を成膜する場合には混合材料のターゲットを用い、組成の異なる何種類かの膜を成膜する場合には複数のターゲットをチャンバ内に設置すれば良い。

【0040】

本実施形態の製造方法では、上記条件下において、少なくともスパッタ法を用いて半導体層20の内、n型半導体層14を構成する下地層14a及びn型コンタクト層14bを成膜することにより、高バイアス、又はパワーが大きい反応種を生成し、また、この反応種を高い運動エネルギーで基板11へ供給できるので、基板11上でマイグレーションを生じさせ、転位をループ化させるのが容易になる。これにより、半導体層20を構成するn型半導体層14の下地層14aは、基板11上に成膜された柱状結晶の集合体であるバッファ層12の結晶性をそのまま引き継ぐことが無い。従って、成膜効率が高く生産性に優れ、また、結晶性に優れたIII族窒化物化合物半導体を成膜することができる。

【0041】

[発光素子の積層構造]

以下、上述のように、基板11上に、少なくともスパッタ法を用いて半導体層20を成膜する本実施形態の製造方法で得られる発光素子1の構成について詳述する。

【0042】

<基板>

本実施形態において、基板11に用いることができる材料としては、III族窒化物化合物半導体結晶が表面にエピタキシャル成長される基板材料であれば、特に限定されず、各種材料を選択して用いることができる。例えば、サファイア、SiC、シリコン、酸化亜鉛、酸化マグネシウム、酸化マンガン、酸化ジルコニウム、酸化マンガン亜鉛鉄、酸化マグネシウムアルミニウム、ホウ化ジルコニウム、酸化ガリウム、酸化インジウム、酸化リチウムガリウム、酸化リチウムアルミニウム、酸化ネオジウムガリウム、酸化ランタンストロンチウムアルミニウムタンタル、酸化ストロンチウムチタン、酸化チタン、ハフニウム、タングステン、モリブデン等が挙げられる。

【0043】

なお、アンモニアを使用せずにバッファ層を成膜するとともに、アンモニアを使用する方法で後述のn型半導体層を構成する下地層を成膜し、さらに、上記基板材料の内、高温でアンモニアに接触することで化学的な変性を引き起こすことが知られている酸化物基板や金属基板等を用いた場合には、本実施形態のバッファ層がコート層としても作用するので、基板の化学的な変質を防ぐ点で効果的である。

また、一般的に、スパッタ法は基板の温度を低く抑えることが可能なので、高温で分解してしまう性質を持つ材料からなる基板を用いた場合でも、基板11にダメージを与えることなく基板上への各層の成膜が可能である。

【0044】

<バッファ層>

本実施形態の積層半導体10は、基板11上に、スパッタ法によってIII族窒化物化合物からなるバッファ層12が成膜されている。バッファ層12は、スパッタ法により、例えば、金属原料とV族元素を含んだガスとがプラズマで活性化されて反応することで成膜される。

【0045】

本実施形態のIII族窒化物化合物半導体発光素子1の積層半導体10では、基板11上にIII族窒化物化合物半導体結晶をエピタキシャル成長させるに際し、柱状結晶の集合体からなるバッファ層12を、III族金属原料と窒素元素を含むガスとをプラズマによって活性化するスパッタ法によって成膜し、その上に、n型半導体層14を構成する下地層14a、及びn型コンタクト層14bをスパッタ法で形成することができる。

【0046】

III族窒化物化合物半導体の結晶は、六方晶系の結晶構造を持ち、六角柱を基本とした集合組織を形成しやすい。特に、プラズマ化した金属材料を用いた成膜方法によって形成した膜は柱状結晶となりやすい。ここで、本発明で説明する柱状結晶とは、隣接する結晶粒との間に結晶粒界を形成して隔てられており、自身は縦断面形状として柱状になっている結晶のことをいう。

【0047】

図5は、後述する実施例1におけるIII族窒化物化合物半導体積層構造体の断面の透過型電子顕微鏡(TEM)写真であり、図6は、図5を模式化した図である。バッファ層12は、図6中に実線で示したような境界によって区切られており、境界と境界の間にある個々の結晶塊は六角形の柱の形状をしている。本発明では、このような結晶形態を柱状結晶の集合体と呼ぶ。なお、図5及び図6から判るように、このような結晶形態は、境界で区切られた層ということもできるが、本発明では、このような層も含めて柱状結晶の集合体として説明する。

上述のような柱状結晶からなるバッファ層12が基板11上に成膜された場合には、その上に成膜されるIII族窒化物化合物半導体からなる半導体層は、良好な結晶性を持つ結晶膜となる。

【0048】

バッファ層12は、基板11の表面11aの少なくとも60%以上、好ましくは80%以上を覆っている必要があり、90%以上を覆うように形成されていることが好ましい。また、バッファ層12は、表面11aの100%、即ち、基板11の表面11a上を隙間無く覆うように形成されていることが最も好ましい。

バッファ層12が基板11の表面11aを覆う領域が小さくなると、基板11が大きく露出した状態となり、バッファ層12上に成膜される下地層14aと基板11上に直接成膜される下地層14aとでは格子定数が異なるため、均一な結晶とならず、ヒロックやピットを生じてしまう。

【0049】

また、バッファ層12が基板11の表面11aを覆う割合は、図5に示すような断面TEM写真から測定することができる。特に、バッファ層12と下地層14aの材料が異なる場合には、EDSなどを用いて基板11と該基板11上の層との界面を、基板11の表面と平行にスキャンすることにより、バッファ層12が形成されていない領域の比を見積もることができる。

また、本実施形態では、上述のように、断面TEM写真から基板11の露出した面積を測定しているが、バッファ層12のみを成膜した試料を用意し、AFM等の方法によって基板11の露出した面積を測定することも可能である。

【0050】

また、基板11上にバッファ層12を形成する際、基板11の表面11aのみを覆うように形成しても良いが、基板11の表面11a及び側面を覆うように形成しても良い。また、基板11の表面11a、側面及び裏面を覆うようにして形成しても良い。

【0051】

バッファ層12は、柱状結晶の集合体からなることが、バッファ機能の面から好ましい。

III族窒化物化合物半導体の結晶は、六方晶系の結晶構造を有し、六角柱を基本とした集合組織を形成しやすい。特に、プラズマ化した金属材料を用いる成膜方法によって形成された膜は、柱状結晶となりやすい。

このような、柱状結晶からなるバッファ層12を基板11上に成膜した場合、バッファ層12のバッファ機能が有効に作用するため、その上に成膜されたIII族窒化物化合物半導体は良好な結晶性を持つ結晶膜となる。

【0052】

また、バッファ層12は、前記柱状結晶の各々のグレインの幅の平均値が、0.1〜100nmの範囲とされていることが、バッファ機能の面から好ましく、1〜70nmの範囲とされていることがより好ましい。

III族窒化物化合物半導体の結晶層の結晶性を良好にするためには、柱状結晶の各々の結晶のグレインの幅を適正に制御する必要があり、具体的には、上記範囲とすることが好ましい。

各柱状結晶のグレインの幅は、断面TEM観察などにより容易に測定することが可能である。即ち、図6に示す模式図における各柱状結晶の境界の間隔が、各柱状結晶のグレインの幅である。また、図5に示すTEM写真でも判るように、各柱状結晶の幅は精密に規定できるものではなく、ある程度の幅の分布を有する。従って、各柱状結晶のグレインの幅が、上記範囲から外れる結晶が例えば数%程度あったとしても、本発明の効果に影響を及ぼすものではない。また、各柱状結晶のグレインの幅は、90%以上が上記範囲に入っていることが好ましい。

【0053】

結晶のグレインは、上述したように、略柱状の形状をしていることが好ましく、バッファ層12は、柱状のグレインが集合して層を成していることが望ましい。

ここで、上述したグレインの幅とは、バッファ層12が柱状グレインの集合体である場合は、結晶の界面と界面の距離のことをいう。一方、グレインが島状に点在する場合には、グレインの幅とは、結晶グレインが基板面に接する面の最も大きい部分の大きさを言う。

【0054】

バッファ層12の膜厚は、10〜500nmの範囲とされていることが好ましく、20〜100nmの範囲とされていることがより好ましい。

バッファ層12の膜厚が10nm未満だと、上述したようなバッファ機能が充分でなくなる。また、500nmを超える膜厚でバッファ層12を形成し場合、コート層としての機能には変化が無いのにも関わらず、成膜処理時間が長くなり、生産性が低下する虞がある。

なお、バッファ層12の層厚についても、上述した断面TEM写真により、容易に測定することが可能である。

【0055】

バッファ層12は、Alを含有する組成とされていることが好ましく、AlNからなる構成とすることが特に好ましい。

また、バッファ層12を構成する材料としては、一般式AlGaInNで表されるIII族窒化物化合物半導体であれば、どのような材料でも用いることができる。さらに、V族として、AsやPが含有される構成としても良い。

バッファ層12を、Alを含んだ組成とした場合、中でも、GaAlNとすることが好ましく、この際、Alの組成が50%以上とされていることが好ましい。

また、バッファ層12は、AlNからなる構成とすることにより、効率的に柱状結晶集合体とすることができるので、より好ましい。

【0056】

また、上述したように、バッファ層12は、基板11の表面11aに加え、側面11bを覆うようにして形成しても良く、さらに、基板11の裏面11cを覆うようにして形成しても良い。しかしながら、従来の成膜方法でバッファ層を成膜した場合、最大で6回から8回程度の成膜処理を行う必要があり、長時間の工程となってしまう。これ以外の成膜方法としては、基板を保持せずにチャンバ内に設置することにより、基板全面に成膜する方法も考えられるが、基板を加熱する必要がある場合には装置が複雑になる虞がある。

【0057】

そこで、例えば、基板を揺動させたり又は回転運動させたりすることにより、基板の位置を、成膜材料のスパッタ方向に対して変更させつつ、成膜する方法が考えられる。このような方法とすることにより、基板の表面及び側面を一度の工程で成膜することが可能となり、次いで基板裏面への成膜工程を行うことにより、計2回の工程で基板全面を覆うことが可能となる。

【0058】

また、成膜材料源が、大きな面積の発生源から生じる構成とし、且つ、材料の発生位置を移動させることにより、基板を移動させずに基板全面に成膜する方法としても良い。このような方法としては、上述したように、マグネットを揺動させたり又は回転運動させたりすることにより、カソードのマグネットの位置をターゲット内で移動させつつ成膜する、RFスパッタ法が挙げられる。また、このようなRFスパッタ法で成膜を行なう場合、基板側とカソード側の両方を移動させる方法としても良い。さらに、材料の発生源であるカソードを基板近傍に配することにより、発生するプラズマを基板に対してビーム状に供給するのではなく、基板を包み込むように供給するような構成とすれば、基板表面及び側面の同時成膜が可能となる。

【0059】

<半導体層>

図1に示すように、本実施形態の積層半導体10は、基板11上に、上述のようなバッファ層12を介して、窒化物系化合物半導体からなり、n型半導体層14、発光層15及びp型半導体層16を備える半導体層20が積層されている。

そして、n型半導体層14には、少なくともスパッタ法によって成膜され、III族窒化物化合物半導体からなる下地層14a及びn型コンタクト層14bが備えられており、バッファ層12上に下地層14aが積層されている。

【0060】

III族窒化物化合物半導体からなる下地層14aの上には、上述したように、図1に示す積層半導体10のような機能性を持つ結晶積層構造が積層された構成とすることができる。例えば、発光素子のための半導体積層構造を形成する場合、Si、Ge、Sn等のn型ドーパントをドープしたn型導電性の層や、マグネシウムなどのp型ドーパントをドープしたp型導電性の層等を積層して形成することができる。また、材料としては、発光層等にはInGaNを用いることができ、クラッド層等にはAlGaNを用いることができる。このように、下地層14a上に、さらに機能を持たせたIII族窒化物半導体結晶層を形成することにより、発光ダイオードやレーザダイオード、あるいは電子デバイス等の作製に用いられる、半導体積層構造を有するウェーハを作製することが出来る。

以下に、積層半導体10について詳述する。

【0061】

窒化物系化合物半導体としては、例えば一般式AlXGaYInZN1−AMA(0≦X≦1、0≦Y≦1、0≦Z≦1で且つ、X+Y+Z=1。記号Mは窒素(N)とは別の第V族元素を表し、0≦A<1である。)で表わされる窒化ガリウム系化合物半導体が多数知られており、本発明においても、それら周知の窒化ガリウム系化合物半導体を含めて一般式AlXGaYInZN1−AMA(0≦X≦1、0≦Y≦1、0≦Z≦1で且つ、X+Y+Z=1。記号Mは窒素(N)とは別の第V族元素を表し、0≦A<1である。)で表わされる窒化ガリウム系化合物半導体を何ら制限なく用いることができる。

【0062】

窒化ガリウム系化合物半導体は、Al、GaおよびIn以外に他のIII族元素を含有することができ、必要に応じてGe、Si、Mg、Ca、Zn、Be、P、As及びB等の元素を含有することもできる。さらに、意図的に添加した元素に限らず、成膜条件等に依存して必然的に含まれる不純物、並びに原料、反応管材質に含まれる微量不純物を含む場合もある。

【0063】

これらの窒化ガリウム系化合物半導体の成長方法は特に限定されず、上述したスパッタ法の他、MOCVD(有機金属化学気相成長法)、HVPE(ハライド気相成長法)、MBE(分子線エピタキシー法)等、窒化物半導体を成長させることが知られている全ての方法を適用できる。好ましい成長方法としては、膜厚制御性、量産性の観点からMOCVD法である。MOCVD法では、キャリアガスとして水素(H2)または窒素(N2)、III族原料であるGa源としてトリメチルガリウム(TMG)またはトリエチルガリウム(TEG)、Al源としてトリメチルアルミニウム(TMA)またはトリエチルアルミニウム(TEA)、In源としてトリメチルインジウム(TMI)またはトリエチルインジウム(TEI)、V族原料であるN源としてアンモニア(NH3)、ヒドラジン(N2H4)などが用いられる。また、ドーパントとしては、n型にはSi原料としてモノシラン(SiH4)またはジシラン(Si2H6)を、Ge原料としてゲルマンガス(GeH4)や、テトラメチルゲルマニウム((CH3)4Ge)やテトラエチルゲルマニウム((C2H5)4Ge)等の有機ゲルマニウム化合物を利用できる。MBE法では、元素状のゲルマニウムもドーピング源として利用できる。p型にはMg原料としては例えばビスシクロペンタジエニルマグネシウム(Cp2Mg)またはビスエチルシクロペンタジエニルマグネシウム(EtCp2Mg)を用いる。

【0064】

「n型半導体層」

n型半導体層14は、通常、前記バッファ層12上に積層され、下地層14a、n型コンタクト層14b及びn型クラッド層14cから構成される。なお、n型コンタクト層は、下地層、及び/又は、n型クラッド層を兼ねることが可能であるが、下地層が、n型コンタクト層、及び/又は、n型クラッド層を兼ねることも可能である。

【0065】

(下地層)

本実施形態の下地層14aはIII族窒化物化合物半導体からなり、スパッタ法によってバッファ層13上に積層して成膜される。

下地層14aの材料としては、必ずしも基板11上に成膜されたバッファ層12と同じである必要はなく、異なる材料を用いても構わないが、AlXGa1―XN層(0≦x≦1、好ましくは0≦x≦0.5、さらに好ましくは0≦x≦0.1)から構成されることが好ましい。

【0066】

本発明者等が実験したところ、下地層14aに用いる材料として、Gaを含むIII族窒化物化合物、即ちGaN系化合物半導体が好ましいことが明らかとなった。

前記バッファ層12をAlNからなる構成とした場合、下地層14aは、柱状結晶の集合体であるバッファ層12の結晶性をそのまま引き継がないように、マイグレーションによって転位をループ化させる必要がある。転位のループ化を生じやすい材料としては、Gaを含むGaN系化合物半導体が挙げられ、特に、AlGaN、又はGaNが好適である。

【0067】

下地層14aの膜厚は0.1μm以上が好ましく、より好ましくは0.5μm以上であり、1μm以上が最も好ましい。この膜厚以上にした方が結晶性の良好なAlXGa1―XN層が得られやすい。

【0068】

下地層14aには、必要に応じて、n型不純物を1×1017〜1×1019/cm3の範囲内であればドープしても良いが、アンドープ(<1×1017/cm3)とすることもでき、アンドープの方が良好な結晶性の維持という点で好ましい。

基板11が導電性である場合には、下地層14aにドーパントをドープして導電性とすることにより、発光素子の上下に電極を形成することができる。一方、基板11に絶縁性の材料を用いる場合には、発光素子の同じ面に正極及び負極の各電極が設けられたチップ構造をとることになるので、基板11直上の層はドープしない結晶とした方が、結晶性が良好となる。

n型不純物としては、特に限定されないが、例えば、Si、GeおよびSn等が挙げられ、好ましくはSiおよびGeが挙げられる。

【0069】

基板11に導電性の基板を用いる場合には、上述したように、下地層14aをドーピングして、下地層14aの層構造を縦方向に電流が流れるようにすることにより、発光素子のチップ両面に電極を設ける構造とすることができる。

また、基板11に絶縁性の基板を用いる場合には、発光素子のチップの同じ面に電極が形成されるチップ構造を採用することになるので、基板11上にバッファ層12を介して積層される下地層14aはドープしない結晶とした方が、結晶性が良好となる。

【0070】

下地層14aをスパッタ法によって成膜する場合、窒化物原料をリアクタ内に流通させるリアクティブスパッタ法によって成膜する方法とすることが、反応を制御することで結晶性を良好に保つことができ、その良好な結晶性を安定に再現することができる点でより好ましい。

また、下地層14aをスパッタ法によって成膜する場合には、MOCVD法やMBE法等と比較して、装置を簡便な構成とすることが可能となる。

【0071】

下地層14aを成膜する際の基板11の温度、つまり、下地層14aの成長温度は、800℃以上の温度とすることが好ましい。これは、下地層14aを成膜する際の基板11の温度を高くすることによって原子のマイグレーションが生じやすくなり、転位のループ化が容易に進行するからである。また、下地層14aを成膜する際の基板11の温度は、結晶の分解する温度よりも低温である必要があるため、1200℃未満とすることが好ましい。下地層14aを成膜する際の基板11の温度が上記温度範囲内であれば、結晶性の良い下地層14aが得られる。

【0072】

(n型コンタクト層)

本実施形態のn型コンタクト層14bはIII族窒化物化合物半導体からなり、スパッタ法によって下地層14a上に積層して成膜される。

n型コンタクト層14bとしては、下地層14aと同様にAlXGa1―XN層(0≦x≦1、好ましくは0≦x≦0.5、さらに好ましくは0≦x≦0.1)から構成されることが好ましい。また、n型不純物がドープされていることが好ましく、n型不純物を1×1017〜1×1019/cm3、好ましくは1×1018〜1×1019/cm3の濃度で含有すると、負極との良好なオーミック接触の維持、クラック発生の抑制、良好な結晶性の維持の点で好ましい。n型不純物としては、特に限定されないが、例えば、Si、GeおよびSn等が挙げられ、好ましくはSiおよびGeである。成長温度は下地層と同様である。また、上述したように、n型コンタクト層14bは、下地層を兼ねた構成とすることもできる。

【0073】

下地層14a及びn型コンタクト層14bを構成する窒化ガリウム系化合物半導体は同一組成であることが好ましく、これらの合計の膜厚を0.1〜20μm、好ましくは0.5〜15μm、さらに好ましくは1〜12μmの範囲に設定することが好ましい。膜厚がこの範囲であると、半導体の結晶性が良好に維持される。

【0074】

(n型クラッド層)

上述のn型コンタクト層14bと後述の発光層15との間には、n型クラッド層14cを設けることが好ましい。n型クラッド層14cを設けることにより、n型コンタクト層14bの最表面に生じた平坦性の悪化を埋めることできる。n型クラッド層14cは、従来公知のMOCVD法等を用いて、AlGaN、GaN、GaInN等により成膜することが可能である。また、これらの構造のヘテロ接合や複数回積層した超格子構造としてもよい。GaInNとする場合には、発光層15のGaInNのバンドギャップよりも大きくすることが望ましいことは言うまでもない。

【0075】

n型クラッド層14cの膜厚は、特に限定されないが、好ましくは5〜500nmの範囲であり、より好ましくは5〜100nmの範囲である。

また、n型クラッド層14cのn型ドープ濃度は1×1017〜1×1020/cm3の範囲が好ましく、より好ましくは1×1018〜1×1019/cm3の範囲である。ドープ濃度がこの範囲であると、良好な結晶性の維持および発光素子の動作電圧低減の点で好ましい。

【0076】

「p型半導体層」

p型半導体層16は、通常、p型クラッド層16a及びp型コンタクト層16bから構成され、従来公知のMOCVD法等を用いて成膜することができる。また、p型コンタクト層がp型クラッド層を兼ねる構成としてもよい。

【0077】

(p型クラッド層)

p型クラッド層16aとしては、詳細を後述する発光層15のバンドギャップエネルギーより大きくなる組成であり、発光層15へのキャリアの閉じ込めができるものであれば特に限定されないが、好ましくは、AldGa1−dN(0<d≦0.4、好ましくは0.1≦d≦0.3)のものが挙げられる。p型クラッド層16aが、このようなAlGaNからなると、発光層15へのキャリアの閉じ込めの点で好ましい。p型クラッド層16aの膜厚は、特に限定されないが、好ましくは1〜400nmであり、より好ましくは5〜100nmである。p型クラッド層16aのp型ドープ濃度は、1×1018〜1×1021/cm3が好ましく、より好ましくは1×1019〜1×1020/cm3である。p型ドープ濃度が上記範囲であると、結晶性を低下させることなく良好なp型結晶が得られる。

【0078】

(p型コンタクト層)

p型コンタクト層16bとしては、少なくともAleGa1−eN(0≦e<0.5、好ましくは0≦e≦0.2、より好ましくは0≦e≦0.1)を含んでなる窒化ガリウム系化合物半導体層である。Al組成が上記範囲であると、良好な結晶性の維持およびpオーミック電極(後述の透光性電極17を参照)との良好なオーミック接触の点で好ましい。

また、p型ドーパントを1×1018〜1×1021/cm3の範囲の濃度で含有していると、良好なオーミック接触の維持、クラック発生の防止、良好な結晶性の維持の点で好ましく、より好ましくは5×1019〜5×1020/cm3の範囲である。

p型不純物としては、特に限定されないが、例えば、好ましくはMgが挙げられる。

p型コンタクト層16bの膜厚は、特に限定されないが、10〜500nmが好ましく、より好ましくは50〜200nmである。膜厚がこの範囲であると、発光出力の点で好ましい。

【0079】

<発光層>

発光層15は、n型半導体層14上に積層されるとともにp型半導体層16がその上に積層される層であり、従来公知のMOCVD法等を用いて成膜することができる。また、発光層15は、図1に示すように、窒化ガリウム系化合物半導体からなる障壁層15aと、インジウムを含有する窒化ガリウム系化合物半導体からなる井戸層15bとが交互に繰り返して積層され、且つ、n型半導体層14側及びp型半導体層16側に障壁層15aが配される順で積層して形成される。

また、図1に示す例では、発光層15は、6層の障壁層15aと5層の井戸層15bとが交互に繰り返して積層され、発光層15の最上層及び最下層に障壁層15aが配され、各障壁層15a間に井戸層15bが配される構成とされている。

【0080】

障壁層15aとしては、例えば、インジウムを含有した窒化ガリウム系化合物半導体からなる井戸層15bよりもバンドギャップエネルギーが大きいAlcGa1−cN(0≦c<0.3)等の窒化ガリウム系化合物半導体を、好適に用いることができる。

また、井戸層15bには、インジウムを含有する窒化ガリウム系化合物半導体として、例えば、Ga1−sInsN(0<s<0.4)等の窒化ガリウムインジウムを用いることができる。

【0081】

また、発光層15全体の膜厚としては、特に限定されないが、量子効果の得られる程度の膜厚、即ち臨界膜厚が好ましい。例えば、発光層15の膜厚は、1〜500nmの範囲であることが好ましく、100nm前後の膜厚であればより好ましい。膜厚が上記範囲であると、発光出力の向上に寄与する。

【0082】

<透光性正極>

透光性正極17は、上述のようにして作製される積層半導体10のp型半導体層16上に形成される透光性の電極である。

透光性正極17の材質としては、特に限定されず、ITO(In2O3−SnO2)、AZnO(ZnO−Al2O3)、IZnO(In2O3−ZnO)、GZO(ZnO−GeO2)等の材料を、この技術分野でよく知られた慣用の手段で設けることができる。また、その構造も、従来公知の構造を含めて如何なる構造のものも何ら制限なく用いることができる。

【0083】

透光性正極17は、Mgドープp型半導体層16上のほぼ全面を覆うように形成しても構わないし、隙間を開けて格子状や樹形状に形成しても良い。透光性正極17を形成した後に、合金化や透明化を目的とした熱アニールを施す場合もあるが、施さなくても構わない。

【0084】

<正極ボンディングパッド及び負極>

正極ボンディングパッド18は、上述の透光性正極17上に形成される電極である。

正極ボンディングパッド18の材料としては、Au、Al、NiおよびCu等を用いた各種構造が周知であり、これら周知の材料、構造のものを何ら制限無く用いることができる。

正極ボンディングパッド18の厚さは、100〜1000nmの範囲内であることが好ましい。また、ボンディングパッドの特性上、厚さが大きい方が、ボンダビリティーが高くなるため、正極ボンディングパッド18の厚さは300nm以上とすることがより好ましい。さらに、製造コストの観点から500nm以下とすることが好ましい。

【0085】

負極19は、基板11上に、n型半導体層14、発光層15及びp型半導体層16が順次積層された半導体層において、n型半導体層14のn型コンタクト層14bに接するように形成される。

このため、負極ボンディングパッド17を形成する際は、発光層15、p型半導体層16、及びn型半導体層14の一部を除去してn型コンタクト層14bの露出領域14dを形成し、この上に負極19を形成する。

負極19の材料としては、各種組成および構造の負極が周知であり、これら周知の負極を何ら制限無く用いることができ、この技術分野でよく知られた慣用の手段で設けることができる。

【0086】

以上説明したような、本実施形態のIII族窒化物化合物半導体発光素子の製造方法によれば、上記構成により、均一性の良好な結晶膜を、スパッタ法によって短時間で形成することができる。これにより、結晶性の良好なIII族窒化物化合物半導体層を、安定して形成することが可能となる。

【0087】

本実施形態の製造方法では、上記条件下において、少なくともスパッタ法を用いて半導体層20を構成する層の内、n型半導体層14を構成する下地層14a及びn型コンタクト層14bを成膜することにより、高バイアス、又はパワーが大きい反応種を生成し、また、この反応種を高い運動エネルギーで基板11へ供給できるので、基板11上でマイグレーションを生じさせ、転位をループ化させるのが容易になる。これにより、n型半導体層14の下地層14aは、基板11上に成膜された柱状結晶の集合体であるバッファ層12の結晶性をそのまま引き継ぐことが無い。これにより、結晶性の良好なIII族窒化物化合物からなる半導体層を成膜することができる。

また、本実施形態では、少なくともスパッタ法を用いて半導体層を成膜するので、成膜レートを高くすることができ、成膜(製造)時間を短縮することが可能となる。さらに、製造時間が短縮されることにより、スパッタ装置内のチャンバ内に不純物が入り込むのを最小限に抑制することができる。

従って、生産性に優れるとともに、優れた発光特性を備えたIII族窒化物化合物半導体発光素子が得られる。

【0088】

[ランプ]

以上説明したような、本発明に係るIII族窒化物化合物半導体発光素子と蛍光体とを組み合わせることにより、当業者周知の手段によってランプを構成することができる。従来より、発光素子と蛍光体と組み合わせることによって発光色を変える技術が知られており、このような技術を何ら制限されることなく採用することが可能である。

例えば、蛍光体を適正に選定することにより、発光素子より長波長の発光を得ることも可能となり、また、発光素子自体の発光波長と蛍光体によって変換された波長とを混ぜることにより、白色発光を呈するランプとすることもできる。

また、ランプとしては、一般用途の砲弾型、携帯のバックライト用途のサイドビュー型、表示器に用いられるトップビュー型等、何れの用途にも用いることができる。

【0089】

例えば、図4に示す例のように、同一面電極型のIII族窒化物化合物半導体発光素子1を砲弾型に実装する場合には、2本のフレームの内の一方(図4ではフレーム31)に発光素子1を接着し、また、発光素子1の負極(図3に示す符号19参照)をワイヤー34でフレーム32に接合し、発光素子1の正極ボンディングパッド(図3に示す符号18参照)をワイヤー33でフレーム31に接合する。そして、透明な樹脂からなるモールド35で発光素子1の周辺をモールドすることにより、図4に示すような砲弾型のランプ3を作成することができる。

【0090】

また、本発明に係るIII族窒化物化合物半導体発光素子は、上述の発光素子の他、レーザ素子や受光素子等の光電気変換素子、又は、HBTやHEMT等の電子デバイスなどに用いることができる。これらの半導体素子は、各種構造のものが多数知られており、本発明に係るIII族窒化物化合物半導体発光素子の積層構造体の素子構造は、これら周知の素子構造を含めて何ら制限されない。

【実施例】

【0091】

次に、本発明のIII族窒化物化合物半導体発光素子の製造方法を、実施例によりさらに詳細に説明するが、本発明はこれらの実施例にのみ限定されるものではない。

【0092】

[実施例1]

図1に、本実験例で作製したIII族窒化物化合物半導体発光素子の積層半導体の断面模式図を示す。

本例では、サファイアからなる基板11のc面上に、バッファ層12としてRFスパッタ法を用いてAlNからなる柱状結晶の集合体を形成し、その上に、下地層14aとして、RFスパッタ法を用いてGaNからなる層を形成した。

【0093】

まず、片面のみをエピタキシャル成長に使用できる程度に鏡面研磨したサファイアからなる基板11を、特に湿式等の前処理を行わずにスパッタ装置の中へ導入した。ここで、スパッタ装置としては、高周波式の電源を有し、また、ターゲット内でマグネットの位置を動かすことができる機構を有する装置を使用した。

そして、スパッタ装置内で基板11を750℃まで加熱し、窒素ガスのみを15sccmの流量で導入した後、チャンバ内の圧力を0.08Paに保持し、基板11側に50Wの高周波バイアスを印加し、窒素プラズマに晒すことによって基板11表面を洗浄した。

【0094】

次いで、スパッタ装置内にアルゴン及び窒素ガスを導入した後、基板11の温度を500℃まで低下させた。そして、基板11側に0.5W/cm2の高周波バイアスを印加するとともに、1W/cm2のパワーを金属Alターゲット側に印加し、炉内の圧力を0.5Paに保ち、Arガスを5sccm、窒素ガスを15sccm流通させた条件下(ガス全体における窒素の比は75%)で、サファイアからなる基板11上にAlNからなるバッファ層12を成膜した。成長レートは0.12nm/sであった。

ターゲット内のマグネットは、基板11の洗浄時、及び成膜時の何れにおいても回転させた。

そして、予め測定した成膜速度に従い、規定した時間の処理を行い、50nmのAlN(バッファ層12)を成膜後、プラズマ動作を停止し、基板11の温度を低下させた。

【0095】

次いで、バッファ層12が成膜された基板11をスパッタ装置から取り出して別のスパッタ装置に搬送し、GaN層(III族窒化物半導体)が成膜された試料を、スパッタ法を用いて以下の手順で作製した。ここで、GaN層を成膜するスパッタ装置としては、高周波式の電源を備え、四角形のGaターゲット内をマグネットがスイープすることにより、磁場のかかる位置を動かすことができる機構を有する装置を使用した。また、Gaターゲット内には冷媒を流通させるための配管を設置し、配管内を20℃に冷却した冷媒を流通させ、熱によるGaの融解を防止した。

【0096】

まず、チャンバ内にアルゴン及び窒素ガスを導入した後、基板11の温度を1000℃まで昇温させた。そして、基板11側に0.5W/cm2の高周波バイアスを印加するとともに、1W/cm2のパワーを金属Gaターゲット側に印加し、チャンバ内の圧力を0.5Paに保ちながら、Arガスを5sccm、窒素ガスを15sccm流通させた条件(ガス全体に対する窒素の比は75%)で、サファイアからなる基板11上にGaNからなる層を成膜した。この際の成長速度は、おおよそ1nm/sであった。そして、6μmのGaN層を成膜後、プラズマを立てるのを停止した。

【0097】

次いで、同様の条件にて、1×1019cm−3の電子濃度を持つ2μmのSiドープGaN層を成膜した。成膜の各条件はアンドープGaN層と同様とし、チャンバ内に設置したSiターゲットに向けて、イオン銃から放出したイオンを照射してSiを取り出し、Siをドープした。

【0098】

以上の工程により、サファイアからなる基板11上に、柱状構造を有し、AlNからなるバッファ層12を形成し、その上に、アンドープで6μmの膜厚のGaN層(下地層14a)を形成し、さらにその上に、1×1019cm−3の電子濃度を持つ2μmのSiドープGaN層(n型コンタクト層14b)を形成し、実施例1の試料を作製した。この試料は、表面が無色透明のミラー状を呈した。

【0099】

そして、上記方法で得られたアンドープGaN層(下地層14a)のX線ロッキングカーブ(XRC)を、X線測定器(パナリティカル社製;四結晶X線測定装置、型番:X‘pert)を用いて測定した。この測定は、Cuβ線X線発生源を光源として用い、対称面である(0002)面と非対称面である(11−20)面で行った。一般的に、III族窒化物化合物半導体の場合、(0002)面のXRCスペクトル半値幅は結晶の平坦性(モザイシティ)の指標となり、(11−20)面のXRCスペクトル半値幅は転位密度(ツイスト)の指標となる。この測定の結果、本発明の製造方法で作製したアンドープGaN層は、(0002)面の測定では半値幅180arcsec、(11−20)面では半値幅300arcsecを示した。

【0100】

[実施例2]

本例では、実施例1と同じ条件で成膜した6μmのアンドープGaN結晶(下地層14a)上に、同じスパッタ装置を用いて、Siをドーパントとしたn型コンタクト層14bを成膜した。

そして、試料をMOCVD炉に導入して、この上の各層を成膜し、最終的に、図1に示すようなIII族窒化物化合物半導体発光素子用のエピタキシャル層構造を有するエピタキシャルウェーハ(積層半導体10)を作製した。

このエピタキシャルウェーハは、c面を有するサファイアからなる基板11上に、実施例1と同様の成長方法により、柱状構造を有するAlNからなるバッファ層12を成膜した後、基板11側から順に、6μmのアンドープGaNからなる下地層14a、1×1019cm−3の電子濃度を持つ2μmのSiドープGaNからなるn型コンタクト層14b、1×1018cm−3の電子濃度を持つ20nmのIn0.1Ga0.9N型クラッド層(n型クラッド層14c)、GaN障壁層に始まりGaN障壁層に終わる積層構造であって、層厚を16nmとしたGaNからなる6層の障壁層15aと、層厚を3nmとしたノンドープのIn0.2Ga0.8Nからなる5層の井戸層15bとが交互に積層されてなる発光層(多重量子井戸構造)15、5nmのMgをドープしたAl0.1Ga0.9Nからなるp型クラッド層16a、及び膜厚200nmのMgドープAl0.02Ga0.98Nからなるp型コンタクト層16bとを具備したp型半導体層16を積層した構造を有する。

【0101】

以上のような手順により、半導体発光素子用のエピタキシャル層構造を有するエピタキシャルウェーハを作製した。ここで、MgドープAl0.02Ga0.98Nからなるp型コンタクト層16bは、p型キャリアを活性化するためのアニール処理を行わなくてもp型特性を示した。

【0102】

次いで、上述のようなサファイアからなる基板11上にエピタキシャル層構造が積層されたエピタキシャルウェーハ(図1の積層半導体10参照)を用いて、半導体発光素子の一種である発光ダイオードを作製した(図2及び3の発光素子1を参照)。

まず、作製したウェーハについて、公知のフォトリソグラフィーによってMgドープAl0.02Ga0.98Nからなるp型コンタクト層16bの表面上に、ITOからなる透光性正極17と、その上に正極表面側から順にTi、Al、Auを積層した構造を有する正極ボンディングパッド18を形成した。また、ウェーハの一部にドライエッチングを施し、n型コンタクト層14b上の露出領域14dを露出させ、この部分にNi、Al、Ti、及びAuの4層よりなる負極19を作製した。これらの工程により、ウェーハ上に、図2及び3に示すような形状を持つ各電極を作製した。

【0103】

上述のようにしてp型半導体層及びn型半導体層の両方に電極を形成したウェーハについて、基板11の裏側を研削及び研磨してミラー状の面として350μm角の正方形のチップに切断し、各電極が上になるようにリードフレーム上に載置し、金線でリードフレームに結線することにより、半導体発光素子とした。この半導体発光素子(発光ダイオード)の正極ボンディングパッド18及び負極19の電極間に順方向電流を流したところ、電流20mAにおける順方向電圧は3.0Vであった。また、p側の透光性正極17を通して発光状態を観察したところ、発光波長は470nmであり、発光出力は15mWを示した。このような発光ダイオードの発光特性は、作製したウェーハのほぼ全面から作製された発光ダイオードについて、ばらつきなく得られた。

【0104】

[実施例3]

本例では、サファイアからなる基板のc面上に、バッファ層として、回転カソード式のRFスパッタ装置を用いてAlNの柱状結晶の集合体を形成し、その上に、下地層として、AlNからなるバッファ層を成膜したのと同じスパッタ装置でGaN層(n型コンタクト層14b)を形成した。そして、その上にMOCVD法により、実施例2と同様に発光素子半導体積層構造を形成した。

バッファ層をスパッタする際の基板の温度は700℃とし、下地層を成膜する際の基板の温度は900℃とした。その他の成膜条件は、全て実施例2と同一とした。

そして、反応装置からウェーハを取り出したところ、ウェーハの表面が鏡面であることが確認できた。

【0105】

そして、断面TEM法を用いて上記ウェーハを観察した。RFスパッタにて成膜したAlN層(バッファ層)は、グレインの幅が50nm程度の柱状結晶となっていることが確認できた。また、バッファ層は基板全面を覆って形成されていた。

【0106】

次いで、上述のようにして作製したウェーハを、実施例2と同様にして発光ダイオードチップとした。電極間に順方向電流を流したところ、電流20mAにおける順方向電圧は3.1Vであった。また、p側の透光性電極を通して発光を観察したところ、発光波長は460nmであり、発光出力は13mWを示した。このような発光ダイオードの発光特性は、作製したウェーハのほぼ全面から作製された発光ダイオードについて、ばらつきなく得られた。

【0107】

[実施例4]

本例では、Si(111)基板上に、バッファ層として、回転カソード式のRFスパッタ装置を用いてAlGaNの柱状結晶の集合体を形成し、その上に、下地層として、実施例1同じ装置を用いてSiをドープしたAlGaNの層を形成し、さらにその上に、実施例2と同様の方法で発光素子半導体積層構造を形成した。ここで、バッファ層のAl組成は70%とし、下地層のAl組成は15%とした。また、スパッタ時の基板の温度は500℃とし、下地層の成膜温度は700℃とした。その他の成膜条件は、実施例1と同一である。

実施例4では、発光素子半導体積層構造を成長させた後、反応装置からウェーハを取り出したところ、ウェーハ表面が鏡面であることが確認できた。

【0108】

そして、断面TEM法を用いて上記ウェーハを観察した。RFスパッタにて成膜したGaAlN層(バッファ層)は、グレインの幅が30nm程度の柱状結晶となっていることが確認できた。また、バッファ層は基板全面を覆って形成されていた。

【0109】

次いで、上記のようにして作製したウェーハを、実施例2と同様にして発光ダイオードチップとした。本例では、各電極を、半導体積層構造側と基板側の上下に設置した。電極間に順方向電流を流したところ、電流20mAにおける順方向電圧は2.9Vであった。また、p側の透光性電極を通して発光を観察したところ、発光波長は460nmであり、発光出力は10mWを示した。このような発光ダイオードの発光特性は、作製したウェーハのほぼ全面から作製された発光ダイオードについて、ばらつきなく得られた。

【0110】

[実施例5]

本例では、ZnO(0001)基板上に、バッファ層として、RFマグネトロンスパッタ法を用いてGaNの柱状結晶の集合体を形成し、その上に、下地層として、実施例1と同じ装置を用いて、GeをドープしたAlGaNの層を形成し、さらにその上に、実施例2と同様の方法で発光素子半導体積層構造を形成した。ここで、下地層のAl組成は10%とした。また、バッファ層のスパッタ時の基板の温度は室温とし、下地層の成膜時の基板の温度は750℃とした。また、本例では、525nm付近の緑色LEDの作製を試みたため、発光層に含有されるInの原料流量を増量した。

実施例5では、発光素子半導体積層構造を成長させた後、反応装置からウェーハを取り出したところ、ウェーハ表面が鏡面であることが確認できた。

【0111】

そして、断面TEM法を用いて上記ウェーハを観察した。GaN層は、グレインの幅が5nm程度の柱状結晶となっていることが確認できた。また、バッファ層は基板全面を覆って形成されていた。

【0112】

上述のようにして作製したウェーハを、実施例2と同様の方法で発光ダイオードチップとし、また、実施例4と同様に、各電極を積層構造側と基板側の上下に設置した。そして、電極間に順方向電流を流したところ、電流20mAにおける順方向電圧は3.3Vであった。また、p側の透光性電極を通して発光を観察したところ、発光波長は525nmであり、発光出力は10mWを示した。このような発光ダイオードの発光特性は、作製したウェーハのほぼ全面から作製された発光ダイオードについて、ばらつきなく得られた。

【0113】

以上の結果により、本発明に係るIII族窒化物化合物半導体発光素子が、生産性に優れ、また、優れた発光特性を備えていることが明らかである。

【産業上の利用可能性】

【0114】

本発明で得られるIII族窒化物化合物半導体発光素子は、良好な結晶性を持つIII族窒化物化合物半導体結晶からなる表面層を有している。

従って、優れた発光特性を有する発光ダイオード、レーザダイオード、或いは電子デバイス等の半導体素子を作製することが可能となる。

【図面の簡単な説明】

【0115】

【図1】本発明に係るIII族窒化物化合物半導体発光素子の一例を模式的に説明する図であり、積層半導体の断面構造を示す概略図である。

【図2】本発明に係るIII族窒化物化合物半導体発光素子の一例を模式的に説明する図であり、平面構造を示す概略図である。

【図3】本発明に係るIII族窒化物化合物半導体発光素子の一例を模式的に説明する図であり、断面構造を示す概略図である。

【図4】本発明に係るIII族窒化物化合物半導体発光素子を用いて構成したランプを模式的に説明する概略図である。

【図5】本発明に係るIII族窒化物化合物半導体発光素子の一例を模式的に説明する図であり、断面構造を示す透過型電子顕微鏡(TEM)写真である。

【図6】本発明に係るIII族窒化物化合物半導体発光素子の一例を模式的に説明する図であり、図5に示すTEM写真を模式化して示す図である。

【図7】本発明に係るIII族窒化物化合物半導体発光素子の製造方法の一例を模式的に説明する図であり、スパッタ装置の構造を示す概略図である。

【符号の説明】

【0116】

1…III族窒化物化合物半導体発光素子、10…積層半導体、11…基板、11a…表面、12…バッファ層、13…下地層、14…n型半導体層、15…発光層、16…p型半導体層、17…透光性正極、3…ランプ

【技術分野】

【0001】

本発明は、発光ダイオード(LED)、レーザダイオード(LD)、電子デバイス等に好適に用いられるIII族窒化物化合物半導体発光素子の製造方法に関し、特に、結晶性の良好なIII族窒化物化合物半導体結晶を基板上にエピタキシャル成長させることが可能なIII族窒化物化合物半導体発光素子の製造方法、及びIII族窒化物化合物半導体発光素子、並びにランプに関する。

【背景技術】

【0002】

III族窒化物半導体発光素子は、可視光から紫外光領域の範囲に相当するエネルギーの直接遷移型のバンドギャップを有し、発光効率に優れていることから、LEDやLD等の発光素子として用いられている。

また、電子デバイスに用いた場合でも、III族窒化物半導体発光素子は、従来のIII−V族化合物半導体を用いた場合に比べ、優れた特性を有する電子デバイスが得られる。

【0003】

このようなIII族窒化物化合物半導体は、一般的に、トリメチルガリウム、トリメチルアルミニウムおよびアンモニアを原料として、MOCVD法によって製造されている。MOCVD法は、キャリアガスに原料の蒸気を含ませて基板表面に運搬し、加熱された基板との反応で分解することにより、結晶を成長させる方法である。

【0004】

従来、III−V族化合物半導体の単結晶ウェーハとしては、異なる材料の単結晶ウェーハ上に結晶を成長させて得る方法が一般的である。このような、異種基板と、その上にエピタキシャル成長させるIII族窒化物半導体結晶との間には、大きな格子不整合が存在する。例えば、サファイア(Al2O3)基板上に窒化ガリウム(GaN)を成長させた場合、両者の間には16%の格子不整合が存在し、SiC基板上に窒化ガリウムを成長させた場合には、両者の間に6%の格子不整合が存在する。

一般に、上述のような大きな格子不整合が存在する場合、基板上に結晶を直接エピタキシャル成長させることが困難となり、また、成長させた場合であっても結晶性の良好な結晶が得られないという問題がある。

【0005】

そこで、有機金属化学気相成長(MOCVD)法により、サファイア単結晶基板もしくはSiC単結晶基板の上に、III族窒化物半導体結晶をエピタキシャル成長させる際、基板上に、まず、窒化アルミニウム(AlN)やAlGaNからなる低温バッファ層と呼ばれる層を積層し、その上に高温でIII族窒化物半導体結晶をエピタキシャル成長させる方法が提案されており、一般に行われている(例えば、特許文献1、2)。

【0006】

一方、III族窒化物化合物半導体結晶をスパッタによって製造する研究も行われており、例えば、N2ガスを用いた高周波マグネトロンスパッタリングにより、Si(100)及びAl2O3(0001)上にGaN膜を成膜する方法が提案されている(例えば、非特許文献1)。非特許文献1に記載の方法では、成膜の条件として、全ガス圧力を2mTorr、投入電力を100Wとし、基板温度をRT〜900℃まで変化させており、また、スパッタ装置として、ターゲットと基板とを対向させたものが用いられている。

【0007】

また、カソードとターゲットとを向かい合わせ、基板とターゲットとの間にメッシュを入れた装置を用いてGaNを成膜する方法が提案されている(例えば、非特許文献2)。非特許文献2に記載の方法では、成膜条件として、N2ガス中で圧力を0.67Paとし、基板温度を84〜600℃とし、投入電力を150W、基板とターゲットとの間の距離を80mmとしている。

【0008】

また、ターゲット同士を向かい合わせた対面カソードと呼ばれる方式で、基板上にAlNを成膜する方法が提案されている(例えば、非特許文献3)。

また、DCマグネトロンスパッタリング法を用いて、基板上にAlNを成膜する方法が提案されている(例えば、非特許文献4)。非特許文献4に記載の方法では、基板とターゲットとを対向させ、ArとN2の混合ガス雰囲気中でスパッタを行なっており、成膜条件として、圧力を0.2〜0.8Paの範囲、基板とターゲットとの距離を60〜180mmの間で変化させている。

【0009】

また、バッファ層としてAlN等の層をMOCVD以外の方法で成膜し、その上に成膜される層をMOCVD法で成膜する方法に関し、例えば、高周波スパッタで成膜したバッファ層上に、MOCVD法で同じ組成の結晶を成長させる方法が提案されている(例えば、特許文献3)。しかしながら、特許文献3に記載の方法では、安定して良好な結晶を得ることができないという問題がある(特許文献4、5を参照)。

【0010】

そこで、安定して良好な結晶を得るため、例えば、バッファ層成長後にアンモニアと水素からなる混合ガス中でアニールする方法(例えば、特許文献4)や、バッファ層を400℃以上の温度でDCスパッタにより成膜する方法(例えば、特許文献5)が提案されている。

また、特許文献4及び5に記載の方法では、基板材料として、サファイア、シリコン、炭化シリコン、酸化亜鉛、リン化ガリウム、ヒ化ガリウム、酸化マグネシウム、酸化マンガン、III族窒化物系化合物半導体単結晶等が用いられ、中でもサファイアのa面基板が好適とされている。

【特許文献1】特許第3026087号公報

【特許文献2】特開平4−297023号公報

【特許文献3】特公平5−86646号公報

【特許文献4】特許第3440873号公報

【特許文献5】特許第3700492号公報

【非特許文献1】牛玖 由紀子(Y.USHIKU)他、「21世紀連合シンポジウム論文集」、Vol.2nd、p295(2003)、

【非特許文献2】ティー・キクマ(T.Kikuma)他、「バキューム(Vacuum)」、Vol.66、P233(2002)

【非特許文献3】キクオ・トミナガ(Kikuo Tominaga)他、「ジャパニーズ・ジャーナル・オブ・アプライド・オブ・フィジックス(Japanese Journal of Applied Physics)」、Vol.28、p7(1989)

【非特許文献4】エム・イシハラ(M.Ishihara)他、「スィン・ソリッド・フィルム(Thin Solid Films)」、vol.316、p152(1998)

【発明の開示】

【発明が解決しようとする課題】

【0011】

しかしながら、本出願人等が鋭意実験、検討を行なった結果、特許文献4及び5に記載の条件で成膜を行なった場合でも、III族元素としてGaを含むIII族窒化物化合物半導体を、安定して良好な結晶で得ることができないことが明らかとなった。即ち、特許文献4、5に記載の方法では、スパッタ法で成膜されたバッファ層上にMOCVD法によってGaN層を成膜している。スパッタ法によってバッファ層を成膜した場合、成膜速度が速い反面、成膜条件によっては、結晶性に劣るバッファ層となる場合がある。このような結晶性の低いバッファ層上に、MOCVD法によってGaN層を成長させると、GaN層の結晶性が大幅に低下する虞があった。

また、非特許文献1、2に記載の条件を用いて、スパッタ法でGaN層を成膜した場合であっても、バッファ層上に結晶性の良好なGaN層を形成するのが困難であるという問題があった。

【0012】

本発明は上記課題に鑑みてなされたものであり、均一性の良好なIII族窒化物化合物半導体からなる結晶膜を、安定して短時間で形成することができ、生産性に優れるとともに、優れた発光特性を備えたIII族窒化物化合物半導体発光素子の製造方法、及びIII族窒化物化合物半導体発光素子、並びにランプを提供することを目的とする。

【課題を解決するための手段】

【0013】

本発明者は、上記問題を解決するために鋭意検討した結果、本発明を完成した。

即ち、本発明は以下に関する。

【0014】

[1] 基板上に、III族元素としてGaを含むIII族窒化物化合物半導体からなる半導体層をスパッタ法によって成膜する工程を含むIII族窒化物化合物半導体発光素子の製造方法であって、前記半導体層をスパッタ法で成膜する際に、前記基板に印加するバイアス値を0.1W/cm2以上とすることを特徴とするIII族窒化物化合物半導体発光素子の製造方法。

[2] 基板上に、III族元素としてGaを含むIII族窒化物化合物半導体からなる半導体層をスパッタ法によって成膜する工程を含むIII族窒化物化合物半導体発光素子の製造方法であって、前記半導体層をスパッタ法で成膜する際に、スパッタターゲットに印加するパワーを0.1W/cm2〜100W/cm2の範囲とすることを特徴とするIII族窒化物化合物半導体発光素子の製造方法。

【0015】

[3] 窒化物原料をリアクタ内に流通させるリアクティブスパッタ法によって前記半導体層を成膜することを特徴とする[1]又は[2]に記載のIII族窒化物化合物半導体発光素子の製造方法。

[4] 前記窒化物原料として窒素を用いたことを特徴とする[3]に記載のIII族窒化物化合物半導体発光素子の製造方法。

【0016】

[5] 前記基板と前記半導体層との間に、柱状結晶からなるバッファ層を形成することを特徴とする[1]〜[4]の何れかに記載のIII族窒化物化合物半導体発光素子の製造方法。

[6] 前記バッファ層を、スパッタ法で形成することを特徴とする[5]に記載のIII族窒化物化合物半導体発光素子の製造方法。

[7] 前記バッファ層を、Alを含有するIII族窒化物化合物で形成することを特徴とする[6]に記載のIII族窒化物化合物半導体発光素子の製造方法。

[8] 前記バッファ層を、AlNで形成することを特徴とする[7]に記載のIII族窒化物化合物半導体発光素子の製造方法。

[9] 前記バッファ層を、前記基板の表面の少なくとも90%以上を覆うように形成することを特徴とする[5]〜[8]の何れかに記載のIII族窒化物化合物半導体発光素子の製造方法。

[10] 前記バッファ層を構成する柱状結晶の幅が0.1〜100nmの範囲であることを特徴とする[5]〜[9]の何れかに記載のIII族窒化物化合物半導体発光素子の製造方法。

[11] 前記バッファ層の膜厚が10〜500nmの範囲であることを特徴とする[5]〜[10]の何れかに記載のIII族窒化物化合物半導体発光素子の製造方法。

[12] 前記バッファ層をAlNで形成するとともに、III族窒化物化合物からなる前記半導体層をGaNで形成することを特徴とする[5]〜[11]の何れかに記載のIII族窒化物化合物半導体発光素子の製造方法。

[13] 前記基板にサファイアを用いることを特徴とする[1]〜[12]の何れかに記載のIII族窒化物化合物半導体発光素子の製造方法。

【0017】

[14] 上記[1]〜[13]の何れかに記載の製造方法で得られるIII族窒化物化合物半導体発光素子。

[15] 上記[14]に記載のIII族窒化物化合物半導体発光素子が用いられてなるランプ。

【発明の効果】

【0018】

本発明のIII族窒化物化合物半導体発光素子の製造方法によれば、上記構成により、均一性の良好な結晶膜を、スパッタ法によって短時間で形成することができる。これにより、結晶性の良好なIII族窒化物化合物半導体層を、安定して形成することが可能となる。従って、生産性に優れるとともに、優れた発光特性を備えたIII族窒化物化合物半導体発光素子が得られる。

【発明を実施するための最良の形態】

【0019】

以下に、本発明に係るIII族窒化物化合物半導体発光素子の製造方法、及びIII族窒化物化合物半導体発光素子、並びにランプの一実施形態について、図1〜7を適宜参照しながら説明する。

【0020】

本実施形態のIII族窒化物化合物半導体発光素子(以下、発光素子と略称することがある)の製造方法は、基板上に、少なくともスパッタ法を用いてIII族窒化物化合物半導体からなる半導体層を成膜する方法であって、III族窒化物化合物半導体としてGaを含有する化合物を用いる方法である。

【0021】

本実施形態の製造方法によって得られる発光素子の積層構造を、図1に例示する積層半導体10を用いて説明する。この積層半導体10は、基板11上にIII族窒化物化合物からなるバッファ層12が積層され、該バッファ層12上に、n型半導体層14、発光層15、及びp型半導体層16が順次積層されてなる半導体層20が形成されている。

そして、本実施形態の積層半導体10は、図2及び図3に示す例のように、p型半導体層16上に透光性正極17が積層され、その上に正極ボンディングパッド18形成されるとともに、n型半導体層14のn型コンタクト層14bに形成された露出領域14dに負極19が積層されてなる発光素子1を構成することができる。

【0022】

[スパッタ法を用いた半導体層の成膜]

本発明に係る発光素子の製造方法は、上述したように、少なくともスパッタ法を用いて基板11上に半導体層20を構成する層を成膜する方法であり、本実施形態では、半導体層20の内、n型半導体層14を構成する下地層14a及びn型コンタクト層14bを、スパッタ法によって成膜する方法としている。

結晶性に優れたIII族窒化物化合物半導体を、スパッタ法を用いて基板上に成膜するためには、よりエネルギーの高い反応種を生成して基板上におけるマイグレーションを活発にする必要があることから、本実施形態では以下に詳述するような方法としている。

【0023】

本実施形態の製造方法で用いるスパッタ法としては、RF(高周波)スパッタ法、又はDCスパッタ法を用いることにより、スパッタターゲットに対してパワーを印加することが好ましい。

また、一般に、後述するリアクティブスパッタ法を用いた場合には、成膜レートを容易にコントロールできる点から、RFスパッタ法を用いることがより好ましい。

また、DCスパッタ法では、リアクティブスパッタ法を用いる場合、DCで電場を連続してかけた状態にするとスパッタターゲットがチャージアップしてしまい、成膜レートを高くすることが困難になるため、パルス的にバイアスを与えるパルス式DCスパッタ法とすることが好ましい。

【0024】

また、半導体層をスパッタ法によって成膜する場合、窒化物原料をリアクタ内に流通させるリアクティブスパッタ法によって成膜する方法とすることが、反応を制御することで結晶性を良好に保つことができ、その良好な結晶性を安定に再現することができる点でより好ましい。

【0025】

また、本実施形態では、スパッタ法で半導体層を成膜する際、ターゲット47に対し、磁場を回転させるか、又は磁場を揺動させることが好ましい。

特に、RFスパッタを用いた場合、チャージアップを回避する方法として、マグネットの位置をターゲット(スパッタターゲット)内で移動させつつ成膜することが好ましい。具体的なマグネットの運動方法は、スパッタ装置の種類によって適宜選択することができ、例えば、マグネットを揺動させたり、又は回転運動させたりすることができる。

【0026】

図7に例示するRFスパッタ装置40では、金属ターゲット(スパッタターゲット)47の下方(図7の下方)にマグネット42が配され、該マグネット42が図示略の駆動装置によって金属ターゲット47の下方で揺動する。チャンバ41には窒素ガス、及びアルゴンガスが供給され、ヒータ44に取り付けられた基板11上に半導体層が成膜される。

【0027】

本実施形態では、スパッタ法を用いた成膜における重要なパラメータとして、バイアス、ターゲットに印加するパワー、基板温度、炉内の圧力、窒素分圧や成膜レート等が挙げられる。

【0028】

本実施形態の製造方法では、スパッタ法で半導体層を成膜する際、基板11に印加するバイアス値を0.1W/cm2以上とすることが好ましく、0.2W/cm2以上とすることがより好ましく、0.5W/cm2以上とすることが最も好ましい。

基板11に印加するバイアス値を上記とすることにより、高バイアスの反応種を生成し、また、この反応種を高い運動エネルギーで基板11へ供給できるので、基板11上におけるマイグレーションが活発になり、転位をループ化させるのが容易になる。

【0029】

また、本実施形態の製造方法では、スパッタ法で半導体層を成膜する際、金属ターゲット(スパッタターゲット)47に印加するパワーを0.1W/cm2〜100W/cm2の範囲とすることが好ましく、1W/cm2〜50W/cm2の範囲とすることがより好ましく、1.5W/cm2〜50W/cm2の範囲とすることが最も好ましい。

金属ターゲット47に印加するパワーを上記範囲とすることにより、大きなパワーの反応種を生成し、また、この反応種を高い運動エネルギーで基板11へ供給できるので、基板11上におけるマイグレーションが活発になり、転位をループ化させるのが容易になる。

【0030】

また、スパッタ法で成膜する際のチャンバ41内の実際の圧力は、0.3Pa以上であることが好ましい。チャンバ41内の圧力が0.3Pa未満とすると、窒素の存在量が小さくなり過ぎ、スパッタされた金属が窒化物とならない状態で基板11上に付着する虞がある。また、チャンバ41内の圧力の上限は特に限定されないが、プラズマを発生させることができる程度の圧力に抑制することが必要である。

【0031】

また、窒素(N2)とArの流量に対する窒素流量の比は、N2が20%以上98%以下の範囲であることが好ましい。この範囲を下回る流量比だと、スパッタ金属が金属のまま基板に付着してしまう。また、上記範囲を上回る流量比だと、Arの量が少な過ぎるためにスパッタレートが低下してしまう。

窒素(N2)とArの流量に対する窒素流量の比は、特に好ましくは、25%以上90%以下の範囲である。

【0032】

本実施形態の製造方法では、上述のように、スパッタ装置のチャンバ内におけるガス中の窒素濃度を高くし、さらに、重量の大きな気体であるArを上記流量比で混合している。チャンバ内のガスが窒素のみの場合だと、金属ターゲット47を叩く力が弱いために、成膜レートが制限されてしまうところ、本実施形態では、重量の大きなArと上記流量比で混合することにより、成膜レートを向上させるとともに、基板11上におけるマイグレーションを活発にすることができる。

【0033】

本実施形態で用いる窒素原料としては、一般に知られている窒素化合物を何ら制限されることなく用いることができるが、アンモニアや窒素(N2)は取り扱いが簡単であるとともに、比較的安価で入手可能であることから好ましい。

アンモニアは分解効率が良好であり、高い成長速度で成膜することが可能であるが、反応性や毒性が高いため、除害設備やガス検知器が必要となり、また、反応装置に使用する部材の材料を安定性の高いものにする必要がある。

また、窒素(N2)を原料として用いた場合には、装置としては簡便なものを用いることができるが、高い反応速度は得られない。しかしながら、窒素を電界や熱等により分解してから装置に導入する方法とすれば、アンモニアよりは低いものの工業生産的に利用可能な程度の成膜速度を得ることができるため、装置コストとの兼ね合いを考えると、最も好適な窒素源である。

【0034】

スパッタ法を用いた成膜の際の成膜レートは、0.01nm/s〜10nm/sの範囲とすることが好ましい。成膜レートが0.01nm/s未満だと、成膜プロセスが長時間となってしまい、工業生産的に無駄が大きくなる。成膜レートが10nm/sを超えると、良好な結晶を得ることが困難となる。

【0035】

本実施形態の製造方法では、少なくともスパッタ法を用いて半導体層20の内、n型半導体層14を構成する下地層14a及びn型コンタクト層14bを成膜するので、成膜レートを高くすることができ、成膜(製造)時間を短縮することが可能となる。製造時間が短縮されることにより、スパッタ装置内のチャンバ内に不純物が入り込むのを最小限に抑制することができる。

【0036】

基板11は、湿式の前処理を行うことが望ましい。例えば、シリコンからなる基板11に対しては、よく知られたRCA洗浄方法などを行い、表面を水素終端させておくことにより、成膜プロセスが安定する。

また、基板11は、反応器の中に導入した後、バッファ層12を形成する前に、スパッタ法等の方法を用いて前処理を行うことができる。具体的には、基板11をArやN2のプラズマ中に曝す事によって表面を整えることができる。例えば、ArガスやN2ガスなどのプラズマを基板11表面に作用させることで、基板11表面に付着した有機物や酸化物を除去することができる。この場合、基板11とチャンバとの間に電圧を印加すれば、プラズマ粒子が効率的に基板11に作用する。

【0037】

本発明者等が鋭意実験、検討を行なったところ、成膜時の基板11の温度は、室温〜1200℃の範囲とすることが好ましく、300〜1000℃の範囲とすることがより好ましく、500〜800℃の範囲とすることが最も好ましい。

基板11の温度が上記下限未満だと、基板11上でのマイグレーションが抑制され、結晶性の良いIII族窒化物化合物半導体結晶を成膜することができない。基板11の温度が上記上限を超えると、III族窒化物化合物半導体結晶が分解する虞がある。

なお、本発明で説明する室温とは、工程の環境等にも影響される温度であるが、具体的な温度としては、0〜30℃の範囲である。

【0038】

本実施形態の製造方法では、スパッタ法による成膜時の基板11の温度を上記範囲とし、基板温度を高くすることにより、基板11に到達した反応種(金属ターゲット47から取り出された金属)の、結晶表面での運動を活性化することができる。

【0039】

スパッタ法を用いて混晶を成膜する際には、ターゲットとなる金属を予め金属材料の混合物(必ずしも、合金を形成していなくても構わない)として行う方法もあるし、また、異なる材料からなる2つのターゲットを用意して同時にスパッタする方法としても良い。

例えば、一定の組成の膜を成膜する場合には混合材料のターゲットを用い、組成の異なる何種類かの膜を成膜する場合には複数のターゲットをチャンバ内に設置すれば良い。

【0040】

本実施形態の製造方法では、上記条件下において、少なくともスパッタ法を用いて半導体層20の内、n型半導体層14を構成する下地層14a及びn型コンタクト層14bを成膜することにより、高バイアス、又はパワーが大きい反応種を生成し、また、この反応種を高い運動エネルギーで基板11へ供給できるので、基板11上でマイグレーションを生じさせ、転位をループ化させるのが容易になる。これにより、半導体層20を構成するn型半導体層14の下地層14aは、基板11上に成膜された柱状結晶の集合体であるバッファ層12の結晶性をそのまま引き継ぐことが無い。従って、成膜効率が高く生産性に優れ、また、結晶性に優れたIII族窒化物化合物半導体を成膜することができる。

【0041】

[発光素子の積層構造]

以下、上述のように、基板11上に、少なくともスパッタ法を用いて半導体層20を成膜する本実施形態の製造方法で得られる発光素子1の構成について詳述する。

【0042】

<基板>

本実施形態において、基板11に用いることができる材料としては、III族窒化物化合物半導体結晶が表面にエピタキシャル成長される基板材料であれば、特に限定されず、各種材料を選択して用いることができる。例えば、サファイア、SiC、シリコン、酸化亜鉛、酸化マグネシウム、酸化マンガン、酸化ジルコニウム、酸化マンガン亜鉛鉄、酸化マグネシウムアルミニウム、ホウ化ジルコニウム、酸化ガリウム、酸化インジウム、酸化リチウムガリウム、酸化リチウムアルミニウム、酸化ネオジウムガリウム、酸化ランタンストロンチウムアルミニウムタンタル、酸化ストロンチウムチタン、酸化チタン、ハフニウム、タングステン、モリブデン等が挙げられる。

【0043】

なお、アンモニアを使用せずにバッファ層を成膜するとともに、アンモニアを使用する方法で後述のn型半導体層を構成する下地層を成膜し、さらに、上記基板材料の内、高温でアンモニアに接触することで化学的な変性を引き起こすことが知られている酸化物基板や金属基板等を用いた場合には、本実施形態のバッファ層がコート層としても作用するので、基板の化学的な変質を防ぐ点で効果的である。

また、一般的に、スパッタ法は基板の温度を低く抑えることが可能なので、高温で分解してしまう性質を持つ材料からなる基板を用いた場合でも、基板11にダメージを与えることなく基板上への各層の成膜が可能である。

【0044】

<バッファ層>

本実施形態の積層半導体10は、基板11上に、スパッタ法によってIII族窒化物化合物からなるバッファ層12が成膜されている。バッファ層12は、スパッタ法により、例えば、金属原料とV族元素を含んだガスとがプラズマで活性化されて反応することで成膜される。

【0045】

本実施形態のIII族窒化物化合物半導体発光素子1の積層半導体10では、基板11上にIII族窒化物化合物半導体結晶をエピタキシャル成長させるに際し、柱状結晶の集合体からなるバッファ層12を、III族金属原料と窒素元素を含むガスとをプラズマによって活性化するスパッタ法によって成膜し、その上に、n型半導体層14を構成する下地層14a、及びn型コンタクト層14bをスパッタ法で形成することができる。

【0046】

III族窒化物化合物半導体の結晶は、六方晶系の結晶構造を持ち、六角柱を基本とした集合組織を形成しやすい。特に、プラズマ化した金属材料を用いた成膜方法によって形成した膜は柱状結晶となりやすい。ここで、本発明で説明する柱状結晶とは、隣接する結晶粒との間に結晶粒界を形成して隔てられており、自身は縦断面形状として柱状になっている結晶のことをいう。

【0047】

図5は、後述する実施例1におけるIII族窒化物化合物半導体積層構造体の断面の透過型電子顕微鏡(TEM)写真であり、図6は、図5を模式化した図である。バッファ層12は、図6中に実線で示したような境界によって区切られており、境界と境界の間にある個々の結晶塊は六角形の柱の形状をしている。本発明では、このような結晶形態を柱状結晶の集合体と呼ぶ。なお、図5及び図6から判るように、このような結晶形態は、境界で区切られた層ということもできるが、本発明では、このような層も含めて柱状結晶の集合体として説明する。

上述のような柱状結晶からなるバッファ層12が基板11上に成膜された場合には、その上に成膜されるIII族窒化物化合物半導体からなる半導体層は、良好な結晶性を持つ結晶膜となる。

【0048】

バッファ層12は、基板11の表面11aの少なくとも60%以上、好ましくは80%以上を覆っている必要があり、90%以上を覆うように形成されていることが好ましい。また、バッファ層12は、表面11aの100%、即ち、基板11の表面11a上を隙間無く覆うように形成されていることが最も好ましい。

バッファ層12が基板11の表面11aを覆う領域が小さくなると、基板11が大きく露出した状態となり、バッファ層12上に成膜される下地層14aと基板11上に直接成膜される下地層14aとでは格子定数が異なるため、均一な結晶とならず、ヒロックやピットを生じてしまう。

【0049】

また、バッファ層12が基板11の表面11aを覆う割合は、図5に示すような断面TEM写真から測定することができる。特に、バッファ層12と下地層14aの材料が異なる場合には、EDSなどを用いて基板11と該基板11上の層との界面を、基板11の表面と平行にスキャンすることにより、バッファ層12が形成されていない領域の比を見積もることができる。

また、本実施形態では、上述のように、断面TEM写真から基板11の露出した面積を測定しているが、バッファ層12のみを成膜した試料を用意し、AFM等の方法によって基板11の露出した面積を測定することも可能である。

【0050】

また、基板11上にバッファ層12を形成する際、基板11の表面11aのみを覆うように形成しても良いが、基板11の表面11a及び側面を覆うように形成しても良い。また、基板11の表面11a、側面及び裏面を覆うようにして形成しても良い。

【0051】

バッファ層12は、柱状結晶の集合体からなることが、バッファ機能の面から好ましい。

III族窒化物化合物半導体の結晶は、六方晶系の結晶構造を有し、六角柱を基本とした集合組織を形成しやすい。特に、プラズマ化した金属材料を用いる成膜方法によって形成された膜は、柱状結晶となりやすい。

このような、柱状結晶からなるバッファ層12を基板11上に成膜した場合、バッファ層12のバッファ機能が有効に作用するため、その上に成膜されたIII族窒化物化合物半導体は良好な結晶性を持つ結晶膜となる。

【0052】

また、バッファ層12は、前記柱状結晶の各々のグレインの幅の平均値が、0.1〜100nmの範囲とされていることが、バッファ機能の面から好ましく、1〜70nmの範囲とされていることがより好ましい。

III族窒化物化合物半導体の結晶層の結晶性を良好にするためには、柱状結晶の各々の結晶のグレインの幅を適正に制御する必要があり、具体的には、上記範囲とすることが好ましい。

各柱状結晶のグレインの幅は、断面TEM観察などにより容易に測定することが可能である。即ち、図6に示す模式図における各柱状結晶の境界の間隔が、各柱状結晶のグレインの幅である。また、図5に示すTEM写真でも判るように、各柱状結晶の幅は精密に規定できるものではなく、ある程度の幅の分布を有する。従って、各柱状結晶のグレインの幅が、上記範囲から外れる結晶が例えば数%程度あったとしても、本発明の効果に影響を及ぼすものではない。また、各柱状結晶のグレインの幅は、90%以上が上記範囲に入っていることが好ましい。

【0053】

結晶のグレインは、上述したように、略柱状の形状をしていることが好ましく、バッファ層12は、柱状のグレインが集合して層を成していることが望ましい。

ここで、上述したグレインの幅とは、バッファ層12が柱状グレインの集合体である場合は、結晶の界面と界面の距離のことをいう。一方、グレインが島状に点在する場合には、グレインの幅とは、結晶グレインが基板面に接する面の最も大きい部分の大きさを言う。

【0054】

バッファ層12の膜厚は、10〜500nmの範囲とされていることが好ましく、20〜100nmの範囲とされていることがより好ましい。

バッファ層12の膜厚が10nm未満だと、上述したようなバッファ機能が充分でなくなる。また、500nmを超える膜厚でバッファ層12を形成し場合、コート層としての機能には変化が無いのにも関わらず、成膜処理時間が長くなり、生産性が低下する虞がある。

なお、バッファ層12の層厚についても、上述した断面TEM写真により、容易に測定することが可能である。

【0055】

バッファ層12は、Alを含有する組成とされていることが好ましく、AlNからなる構成とすることが特に好ましい。

また、バッファ層12を構成する材料としては、一般式AlGaInNで表されるIII族窒化物化合物半導体であれば、どのような材料でも用いることができる。さらに、V族として、AsやPが含有される構成としても良い。

バッファ層12を、Alを含んだ組成とした場合、中でも、GaAlNとすることが好ましく、この際、Alの組成が50%以上とされていることが好ましい。

また、バッファ層12は、AlNからなる構成とすることにより、効率的に柱状結晶集合体とすることができるので、より好ましい。

【0056】

また、上述したように、バッファ層12は、基板11の表面11aに加え、側面11bを覆うようにして形成しても良く、さらに、基板11の裏面11cを覆うようにして形成しても良い。しかしながら、従来の成膜方法でバッファ層を成膜した場合、最大で6回から8回程度の成膜処理を行う必要があり、長時間の工程となってしまう。これ以外の成膜方法としては、基板を保持せずにチャンバ内に設置することにより、基板全面に成膜する方法も考えられるが、基板を加熱する必要がある場合には装置が複雑になる虞がある。

【0057】

そこで、例えば、基板を揺動させたり又は回転運動させたりすることにより、基板の位置を、成膜材料のスパッタ方向に対して変更させつつ、成膜する方法が考えられる。このような方法とすることにより、基板の表面及び側面を一度の工程で成膜することが可能となり、次いで基板裏面への成膜工程を行うことにより、計2回の工程で基板全面を覆うことが可能となる。

【0058】

また、成膜材料源が、大きな面積の発生源から生じる構成とし、且つ、材料の発生位置を移動させることにより、基板を移動させずに基板全面に成膜する方法としても良い。このような方法としては、上述したように、マグネットを揺動させたり又は回転運動させたりすることにより、カソードのマグネットの位置をターゲット内で移動させつつ成膜する、RFスパッタ法が挙げられる。また、このようなRFスパッタ法で成膜を行なう場合、基板側とカソード側の両方を移動させる方法としても良い。さらに、材料の発生源であるカソードを基板近傍に配することにより、発生するプラズマを基板に対してビーム状に供給するのではなく、基板を包み込むように供給するような構成とすれば、基板表面及び側面の同時成膜が可能となる。

【0059】

<半導体層>

図1に示すように、本実施形態の積層半導体10は、基板11上に、上述のようなバッファ層12を介して、窒化物系化合物半導体からなり、n型半導体層14、発光層15及びp型半導体層16を備える半導体層20が積層されている。

そして、n型半導体層14には、少なくともスパッタ法によって成膜され、III族窒化物化合物半導体からなる下地層14a及びn型コンタクト層14bが備えられており、バッファ層12上に下地層14aが積層されている。

【0060】

III族窒化物化合物半導体からなる下地層14aの上には、上述したように、図1に示す積層半導体10のような機能性を持つ結晶積層構造が積層された構成とすることができる。例えば、発光素子のための半導体積層構造を形成する場合、Si、Ge、Sn等のn型ドーパントをドープしたn型導電性の層や、マグネシウムなどのp型ドーパントをドープしたp型導電性の層等を積層して形成することができる。また、材料としては、発光層等にはInGaNを用いることができ、クラッド層等にはAlGaNを用いることができる。このように、下地層14a上に、さらに機能を持たせたIII族窒化物半導体結晶層を形成することにより、発光ダイオードやレーザダイオード、あるいは電子デバイス等の作製に用いられる、半導体積層構造を有するウェーハを作製することが出来る。

以下に、積層半導体10について詳述する。

【0061】

窒化物系化合物半導体としては、例えば一般式AlXGaYInZN1−AMA(0≦X≦1、0≦Y≦1、0≦Z≦1で且つ、X+Y+Z=1。記号Mは窒素(N)とは別の第V族元素を表し、0≦A<1である。)で表わされる窒化ガリウム系化合物半導体が多数知られており、本発明においても、それら周知の窒化ガリウム系化合物半導体を含めて一般式AlXGaYInZN1−AMA(0≦X≦1、0≦Y≦1、0≦Z≦1で且つ、X+Y+Z=1。記号Mは窒素(N)とは別の第V族元素を表し、0≦A<1である。)で表わされる窒化ガリウム系化合物半導体を何ら制限なく用いることができる。

【0062】

窒化ガリウム系化合物半導体は、Al、GaおよびIn以外に他のIII族元素を含有することができ、必要に応じてGe、Si、Mg、Ca、Zn、Be、P、As及びB等の元素を含有することもできる。さらに、意図的に添加した元素に限らず、成膜条件等に依存して必然的に含まれる不純物、並びに原料、反応管材質に含まれる微量不純物を含む場合もある。

【0063】

これらの窒化ガリウム系化合物半導体の成長方法は特に限定されず、上述したスパッタ法の他、MOCVD(有機金属化学気相成長法)、HVPE(ハライド気相成長法)、MBE(分子線エピタキシー法)等、窒化物半導体を成長させることが知られている全ての方法を適用できる。好ましい成長方法としては、膜厚制御性、量産性の観点からMOCVD法である。MOCVD法では、キャリアガスとして水素(H2)または窒素(N2)、III族原料であるGa源としてトリメチルガリウム(TMG)またはトリエチルガリウム(TEG)、Al源としてトリメチルアルミニウム(TMA)またはトリエチルアルミニウム(TEA)、In源としてトリメチルインジウム(TMI)またはトリエチルインジウム(TEI)、V族原料であるN源としてアンモニア(NH3)、ヒドラジン(N2H4)などが用いられる。また、ドーパントとしては、n型にはSi原料としてモノシラン(SiH4)またはジシラン(Si2H6)を、Ge原料としてゲルマンガス(GeH4)や、テトラメチルゲルマニウム((CH3)4Ge)やテトラエチルゲルマニウム((C2H5)4Ge)等の有機ゲルマニウム化合物を利用できる。MBE法では、元素状のゲルマニウムもドーピング源として利用できる。p型にはMg原料としては例えばビスシクロペンタジエニルマグネシウム(Cp2Mg)またはビスエチルシクロペンタジエニルマグネシウム(EtCp2Mg)を用いる。

【0064】

「n型半導体層」

n型半導体層14は、通常、前記バッファ層12上に積層され、下地層14a、n型コンタクト層14b及びn型クラッド層14cから構成される。なお、n型コンタクト層は、下地層、及び/又は、n型クラッド層を兼ねることが可能であるが、下地層が、n型コンタクト層、及び/又は、n型クラッド層を兼ねることも可能である。

【0065】

(下地層)

本実施形態の下地層14aはIII族窒化物化合物半導体からなり、スパッタ法によってバッファ層13上に積層して成膜される。

下地層14aの材料としては、必ずしも基板11上に成膜されたバッファ層12と同じである必要はなく、異なる材料を用いても構わないが、AlXGa1―XN層(0≦x≦1、好ましくは0≦x≦0.5、さらに好ましくは0≦x≦0.1)から構成されることが好ましい。

【0066】

本発明者等が実験したところ、下地層14aに用いる材料として、Gaを含むIII族窒化物化合物、即ちGaN系化合物半導体が好ましいことが明らかとなった。

前記バッファ層12をAlNからなる構成とした場合、下地層14aは、柱状結晶の集合体であるバッファ層12の結晶性をそのまま引き継がないように、マイグレーションによって転位をループ化させる必要がある。転位のループ化を生じやすい材料としては、Gaを含むGaN系化合物半導体が挙げられ、特に、AlGaN、又はGaNが好適である。

【0067】

下地層14aの膜厚は0.1μm以上が好ましく、より好ましくは0.5μm以上であり、1μm以上が最も好ましい。この膜厚以上にした方が結晶性の良好なAlXGa1―XN層が得られやすい。

【0068】

下地層14aには、必要に応じて、n型不純物を1×1017〜1×1019/cm3の範囲内であればドープしても良いが、アンドープ(<1×1017/cm3)とすることもでき、アンドープの方が良好な結晶性の維持という点で好ましい。

基板11が導電性である場合には、下地層14aにドーパントをドープして導電性とすることにより、発光素子の上下に電極を形成することができる。一方、基板11に絶縁性の材料を用いる場合には、発光素子の同じ面に正極及び負極の各電極が設けられたチップ構造をとることになるので、基板11直上の層はドープしない結晶とした方が、結晶性が良好となる。

n型不純物としては、特に限定されないが、例えば、Si、GeおよびSn等が挙げられ、好ましくはSiおよびGeが挙げられる。

【0069】

基板11に導電性の基板を用いる場合には、上述したように、下地層14aをドーピングして、下地層14aの層構造を縦方向に電流が流れるようにすることにより、発光素子のチップ両面に電極を設ける構造とすることができる。

また、基板11に絶縁性の基板を用いる場合には、発光素子のチップの同じ面に電極が形成されるチップ構造を採用することになるので、基板11上にバッファ層12を介して積層される下地層14aはドープしない結晶とした方が、結晶性が良好となる。

【0070】

下地層14aをスパッタ法によって成膜する場合、窒化物原料をリアクタ内に流通させるリアクティブスパッタ法によって成膜する方法とすることが、反応を制御することで結晶性を良好に保つことができ、その良好な結晶性を安定に再現することができる点でより好ましい。

また、下地層14aをスパッタ法によって成膜する場合には、MOCVD法やMBE法等と比較して、装置を簡便な構成とすることが可能となる。

【0071】

下地層14aを成膜する際の基板11の温度、つまり、下地層14aの成長温度は、800℃以上の温度とすることが好ましい。これは、下地層14aを成膜する際の基板11の温度を高くすることによって原子のマイグレーションが生じやすくなり、転位のループ化が容易に進行するからである。また、下地層14aを成膜する際の基板11の温度は、結晶の分解する温度よりも低温である必要があるため、1200℃未満とすることが好ましい。下地層14aを成膜する際の基板11の温度が上記温度範囲内であれば、結晶性の良い下地層14aが得られる。

【0072】

(n型コンタクト層)

本実施形態のn型コンタクト層14bはIII族窒化物化合物半導体からなり、スパッタ法によって下地層14a上に積層して成膜される。

n型コンタクト層14bとしては、下地層14aと同様にAlXGa1―XN層(0≦x≦1、好ましくは0≦x≦0.5、さらに好ましくは0≦x≦0.1)から構成されることが好ましい。また、n型不純物がドープされていることが好ましく、n型不純物を1×1017〜1×1019/cm3、好ましくは1×1018〜1×1019/cm3の濃度で含有すると、負極との良好なオーミック接触の維持、クラック発生の抑制、良好な結晶性の維持の点で好ましい。n型不純物としては、特に限定されないが、例えば、Si、GeおよびSn等が挙げられ、好ましくはSiおよびGeである。成長温度は下地層と同様である。また、上述したように、n型コンタクト層14bは、下地層を兼ねた構成とすることもできる。

【0073】

下地層14a及びn型コンタクト層14bを構成する窒化ガリウム系化合物半導体は同一組成であることが好ましく、これらの合計の膜厚を0.1〜20μm、好ましくは0.5〜15μm、さらに好ましくは1〜12μmの範囲に設定することが好ましい。膜厚がこの範囲であると、半導体の結晶性が良好に維持される。

【0074】

(n型クラッド層)

上述のn型コンタクト層14bと後述の発光層15との間には、n型クラッド層14cを設けることが好ましい。n型クラッド層14cを設けることにより、n型コンタクト層14bの最表面に生じた平坦性の悪化を埋めることできる。n型クラッド層14cは、従来公知のMOCVD法等を用いて、AlGaN、GaN、GaInN等により成膜することが可能である。また、これらの構造のヘテロ接合や複数回積層した超格子構造としてもよい。GaInNとする場合には、発光層15のGaInNのバンドギャップよりも大きくすることが望ましいことは言うまでもない。

【0075】

n型クラッド層14cの膜厚は、特に限定されないが、好ましくは5〜500nmの範囲であり、より好ましくは5〜100nmの範囲である。

また、n型クラッド層14cのn型ドープ濃度は1×1017〜1×1020/cm3の範囲が好ましく、より好ましくは1×1018〜1×1019/cm3の範囲である。ドープ濃度がこの範囲であると、良好な結晶性の維持および発光素子の動作電圧低減の点で好ましい。

【0076】

「p型半導体層」

p型半導体層16は、通常、p型クラッド層16a及びp型コンタクト層16bから構成され、従来公知のMOCVD法等を用いて成膜することができる。また、p型コンタクト層がp型クラッド層を兼ねる構成としてもよい。

【0077】

(p型クラッド層)

p型クラッド層16aとしては、詳細を後述する発光層15のバンドギャップエネルギーより大きくなる組成であり、発光層15へのキャリアの閉じ込めができるものであれば特に限定されないが、好ましくは、AldGa1−dN(0<d≦0.4、好ましくは0.1≦d≦0.3)のものが挙げられる。p型クラッド層16aが、このようなAlGaNからなると、発光層15へのキャリアの閉じ込めの点で好ましい。p型クラッド層16aの膜厚は、特に限定されないが、好ましくは1〜400nmであり、より好ましくは5〜100nmである。p型クラッド層16aのp型ドープ濃度は、1×1018〜1×1021/cm3が好ましく、より好ましくは1×1019〜1×1020/cm3である。p型ドープ濃度が上記範囲であると、結晶性を低下させることなく良好なp型結晶が得られる。

【0078】

(p型コンタクト層)

p型コンタクト層16bとしては、少なくともAleGa1−eN(0≦e<0.5、好ましくは0≦e≦0.2、より好ましくは0≦e≦0.1)を含んでなる窒化ガリウム系化合物半導体層である。Al組成が上記範囲であると、良好な結晶性の維持およびpオーミック電極(後述の透光性電極17を参照)との良好なオーミック接触の点で好ましい。

また、p型ドーパントを1×1018〜1×1021/cm3の範囲の濃度で含有していると、良好なオーミック接触の維持、クラック発生の防止、良好な結晶性の維持の点で好ましく、より好ましくは5×1019〜5×1020/cm3の範囲である。

p型不純物としては、特に限定されないが、例えば、好ましくはMgが挙げられる。

p型コンタクト層16bの膜厚は、特に限定されないが、10〜500nmが好ましく、より好ましくは50〜200nmである。膜厚がこの範囲であると、発光出力の点で好ましい。

【0079】

<発光層>

発光層15は、n型半導体層14上に積層されるとともにp型半導体層16がその上に積層される層であり、従来公知のMOCVD法等を用いて成膜することができる。また、発光層15は、図1に示すように、窒化ガリウム系化合物半導体からなる障壁層15aと、インジウムを含有する窒化ガリウム系化合物半導体からなる井戸層15bとが交互に繰り返して積層され、且つ、n型半導体層14側及びp型半導体層16側に障壁層15aが配される順で積層して形成される。

また、図1に示す例では、発光層15は、6層の障壁層15aと5層の井戸層15bとが交互に繰り返して積層され、発光層15の最上層及び最下層に障壁層15aが配され、各障壁層15a間に井戸層15bが配される構成とされている。

【0080】

障壁層15aとしては、例えば、インジウムを含有した窒化ガリウム系化合物半導体からなる井戸層15bよりもバンドギャップエネルギーが大きいAlcGa1−cN(0≦c<0.3)等の窒化ガリウム系化合物半導体を、好適に用いることができる。

また、井戸層15bには、インジウムを含有する窒化ガリウム系化合物半導体として、例えば、Ga1−sInsN(0<s<0.4)等の窒化ガリウムインジウムを用いることができる。

【0081】

また、発光層15全体の膜厚としては、特に限定されないが、量子効果の得られる程度の膜厚、即ち臨界膜厚が好ましい。例えば、発光層15の膜厚は、1〜500nmの範囲であることが好ましく、100nm前後の膜厚であればより好ましい。膜厚が上記範囲であると、発光出力の向上に寄与する。

【0082】

<透光性正極>

透光性正極17は、上述のようにして作製される積層半導体10のp型半導体層16上に形成される透光性の電極である。

透光性正極17の材質としては、特に限定されず、ITO(In2O3−SnO2)、AZnO(ZnO−Al2O3)、IZnO(In2O3−ZnO)、GZO(ZnO−GeO2)等の材料を、この技術分野でよく知られた慣用の手段で設けることができる。また、その構造も、従来公知の構造を含めて如何なる構造のものも何ら制限なく用いることができる。

【0083】

透光性正極17は、Mgドープp型半導体層16上のほぼ全面を覆うように形成しても構わないし、隙間を開けて格子状や樹形状に形成しても良い。透光性正極17を形成した後に、合金化や透明化を目的とした熱アニールを施す場合もあるが、施さなくても構わない。

【0084】

<正極ボンディングパッド及び負極>

正極ボンディングパッド18は、上述の透光性正極17上に形成される電極である。

正極ボンディングパッド18の材料としては、Au、Al、NiおよびCu等を用いた各種構造が周知であり、これら周知の材料、構造のものを何ら制限無く用いることができる。

正極ボンディングパッド18の厚さは、100〜1000nmの範囲内であることが好ましい。また、ボンディングパッドの特性上、厚さが大きい方が、ボンダビリティーが高くなるため、正極ボンディングパッド18の厚さは300nm以上とすることがより好ましい。さらに、製造コストの観点から500nm以下とすることが好ましい。

【0085】

負極19は、基板11上に、n型半導体層14、発光層15及びp型半導体層16が順次積層された半導体層において、n型半導体層14のn型コンタクト層14bに接するように形成される。

このため、負極ボンディングパッド17を形成する際は、発光層15、p型半導体層16、及びn型半導体層14の一部を除去してn型コンタクト層14bの露出領域14dを形成し、この上に負極19を形成する。

負極19の材料としては、各種組成および構造の負極が周知であり、これら周知の負極を何ら制限無く用いることができ、この技術分野でよく知られた慣用の手段で設けることができる。

【0086】

以上説明したような、本実施形態のIII族窒化物化合物半導体発光素子の製造方法によれば、上記構成により、均一性の良好な結晶膜を、スパッタ法によって短時間で形成することができる。これにより、結晶性の良好なIII族窒化物化合物半導体層を、安定して形成することが可能となる。

【0087】

本実施形態の製造方法では、上記条件下において、少なくともスパッタ法を用いて半導体層20を構成する層の内、n型半導体層14を構成する下地層14a及びn型コンタクト層14bを成膜することにより、高バイアス、又はパワーが大きい反応種を生成し、また、この反応種を高い運動エネルギーで基板11へ供給できるので、基板11上でマイグレーションを生じさせ、転位をループ化させるのが容易になる。これにより、n型半導体層14の下地層14aは、基板11上に成膜された柱状結晶の集合体であるバッファ層12の結晶性をそのまま引き継ぐことが無い。これにより、結晶性の良好なIII族窒化物化合物からなる半導体層を成膜することができる。

また、本実施形態では、少なくともスパッタ法を用いて半導体層を成膜するので、成膜レートを高くすることができ、成膜(製造)時間を短縮することが可能となる。さらに、製造時間が短縮されることにより、スパッタ装置内のチャンバ内に不純物が入り込むのを最小限に抑制することができる。

従って、生産性に優れるとともに、優れた発光特性を備えたIII族窒化物化合物半導体発光素子が得られる。

【0088】

[ランプ]

以上説明したような、本発明に係るIII族窒化物化合物半導体発光素子と蛍光体とを組み合わせることにより、当業者周知の手段によってランプを構成することができる。従来より、発光素子と蛍光体と組み合わせることによって発光色を変える技術が知られており、このような技術を何ら制限されることなく採用することが可能である。

例えば、蛍光体を適正に選定することにより、発光素子より長波長の発光を得ることも可能となり、また、発光素子自体の発光波長と蛍光体によって変換された波長とを混ぜることにより、白色発光を呈するランプとすることもできる。

また、ランプとしては、一般用途の砲弾型、携帯のバックライト用途のサイドビュー型、表示器に用いられるトップビュー型等、何れの用途にも用いることができる。

【0089】

例えば、図4に示す例のように、同一面電極型のIII族窒化物化合物半導体発光素子1を砲弾型に実装する場合には、2本のフレームの内の一方(図4ではフレーム31)に発光素子1を接着し、また、発光素子1の負極(図3に示す符号19参照)をワイヤー34でフレーム32に接合し、発光素子1の正極ボンディングパッド(図3に示す符号18参照)をワイヤー33でフレーム31に接合する。そして、透明な樹脂からなるモールド35で発光素子1の周辺をモールドすることにより、図4に示すような砲弾型のランプ3を作成することができる。

【0090】

また、本発明に係るIII族窒化物化合物半導体発光素子は、上述の発光素子の他、レーザ素子や受光素子等の光電気変換素子、又は、HBTやHEMT等の電子デバイスなどに用いることができる。これらの半導体素子は、各種構造のものが多数知られており、本発明に係るIII族窒化物化合物半導体発光素子の積層構造体の素子構造は、これら周知の素子構造を含めて何ら制限されない。

【実施例】

【0091】

次に、本発明のIII族窒化物化合物半導体発光素子の製造方法を、実施例によりさらに詳細に説明するが、本発明はこれらの実施例にのみ限定されるものではない。

【0092】

[実施例1]

図1に、本実験例で作製したIII族窒化物化合物半導体発光素子の積層半導体の断面模式図を示す。

本例では、サファイアからなる基板11のc面上に、バッファ層12としてRFスパッタ法を用いてAlNからなる柱状結晶の集合体を形成し、その上に、下地層14aとして、RFスパッタ法を用いてGaNからなる層を形成した。

【0093】

まず、片面のみをエピタキシャル成長に使用できる程度に鏡面研磨したサファイアからなる基板11を、特に湿式等の前処理を行わずにスパッタ装置の中へ導入した。ここで、スパッタ装置としては、高周波式の電源を有し、また、ターゲット内でマグネットの位置を動かすことができる機構を有する装置を使用した。

そして、スパッタ装置内で基板11を750℃まで加熱し、窒素ガスのみを15sccmの流量で導入した後、チャンバ内の圧力を0.08Paに保持し、基板11側に50Wの高周波バイアスを印加し、窒素プラズマに晒すことによって基板11表面を洗浄した。

【0094】

次いで、スパッタ装置内にアルゴン及び窒素ガスを導入した後、基板11の温度を500℃まで低下させた。そして、基板11側に0.5W/cm2の高周波バイアスを印加するとともに、1W/cm2のパワーを金属Alターゲット側に印加し、炉内の圧力を0.5Paに保ち、Arガスを5sccm、窒素ガスを15sccm流通させた条件下(ガス全体における窒素の比は75%)で、サファイアからなる基板11上にAlNからなるバッファ層12を成膜した。成長レートは0.12nm/sであった。

ターゲット内のマグネットは、基板11の洗浄時、及び成膜時の何れにおいても回転させた。

そして、予め測定した成膜速度に従い、規定した時間の処理を行い、50nmのAlN(バッファ層12)を成膜後、プラズマ動作を停止し、基板11の温度を低下させた。

【0095】

次いで、バッファ層12が成膜された基板11をスパッタ装置から取り出して別のスパッタ装置に搬送し、GaN層(III族窒化物半導体)が成膜された試料を、スパッタ法を用いて以下の手順で作製した。ここで、GaN層を成膜するスパッタ装置としては、高周波式の電源を備え、四角形のGaターゲット内をマグネットがスイープすることにより、磁場のかかる位置を動かすことができる機構を有する装置を使用した。また、Gaターゲット内には冷媒を流通させるための配管を設置し、配管内を20℃に冷却した冷媒を流通させ、熱によるGaの融解を防止した。

【0096】

まず、チャンバ内にアルゴン及び窒素ガスを導入した後、基板11の温度を1000℃まで昇温させた。そして、基板11側に0.5W/cm2の高周波バイアスを印加するとともに、1W/cm2のパワーを金属Gaターゲット側に印加し、チャンバ内の圧力を0.5Paに保ちながら、Arガスを5sccm、窒素ガスを15sccm流通させた条件(ガス全体に対する窒素の比は75%)で、サファイアからなる基板11上にGaNからなる層を成膜した。この際の成長速度は、おおよそ1nm/sであった。そして、6μmのGaN層を成膜後、プラズマを立てるのを停止した。

【0097】

次いで、同様の条件にて、1×1019cm−3の電子濃度を持つ2μmのSiドープGaN層を成膜した。成膜の各条件はアンドープGaN層と同様とし、チャンバ内に設置したSiターゲットに向けて、イオン銃から放出したイオンを照射してSiを取り出し、Siをドープした。

【0098】

以上の工程により、サファイアからなる基板11上に、柱状構造を有し、AlNからなるバッファ層12を形成し、その上に、アンドープで6μmの膜厚のGaN層(下地層14a)を形成し、さらにその上に、1×1019cm−3の電子濃度を持つ2μmのSiドープGaN層(n型コンタクト層14b)を形成し、実施例1の試料を作製した。この試料は、表面が無色透明のミラー状を呈した。

【0099】

そして、上記方法で得られたアンドープGaN層(下地層14a)のX線ロッキングカーブ(XRC)を、X線測定器(パナリティカル社製;四結晶X線測定装置、型番:X‘pert)を用いて測定した。この測定は、Cuβ線X線発生源を光源として用い、対称面である(0002)面と非対称面である(11−20)面で行った。一般的に、III族窒化物化合物半導体の場合、(0002)面のXRCスペクトル半値幅は結晶の平坦性(モザイシティ)の指標となり、(11−20)面のXRCスペクトル半値幅は転位密度(ツイスト)の指標となる。この測定の結果、本発明の製造方法で作製したアンドープGaN層は、(0002)面の測定では半値幅180arcsec、(11−20)面では半値幅300arcsecを示した。

【0100】

[実施例2]

本例では、実施例1と同じ条件で成膜した6μmのアンドープGaN結晶(下地層14a)上に、同じスパッタ装置を用いて、Siをドーパントとしたn型コンタクト層14bを成膜した。

そして、試料をMOCVD炉に導入して、この上の各層を成膜し、最終的に、図1に示すようなIII族窒化物化合物半導体発光素子用のエピタキシャル層構造を有するエピタキシャルウェーハ(積層半導体10)を作製した。

このエピタキシャルウェーハは、c面を有するサファイアからなる基板11上に、実施例1と同様の成長方法により、柱状構造を有するAlNからなるバッファ層12を成膜した後、基板11側から順に、6μmのアンドープGaNからなる下地層14a、1×1019cm−3の電子濃度を持つ2μmのSiドープGaNからなるn型コンタクト層14b、1×1018cm−3の電子濃度を持つ20nmのIn0.1Ga0.9N型クラッド層(n型クラッド層14c)、GaN障壁層に始まりGaN障壁層に終わる積層構造であって、層厚を16nmとしたGaNからなる6層の障壁層15aと、層厚を3nmとしたノンドープのIn0.2Ga0.8Nからなる5層の井戸層15bとが交互に積層されてなる発光層(多重量子井戸構造)15、5nmのMgをドープしたAl0.1Ga0.9Nからなるp型クラッド層16a、及び膜厚200nmのMgドープAl0.02Ga0.98Nからなるp型コンタクト層16bとを具備したp型半導体層16を積層した構造を有する。

【0101】

以上のような手順により、半導体発光素子用のエピタキシャル層構造を有するエピタキシャルウェーハを作製した。ここで、MgドープAl0.02Ga0.98Nからなるp型コンタクト層16bは、p型キャリアを活性化するためのアニール処理を行わなくてもp型特性を示した。

【0102】

次いで、上述のようなサファイアからなる基板11上にエピタキシャル層構造が積層されたエピタキシャルウェーハ(図1の積層半導体10参照)を用いて、半導体発光素子の一種である発光ダイオードを作製した(図2及び3の発光素子1を参照)。

まず、作製したウェーハについて、公知のフォトリソグラフィーによってMgドープAl0.02Ga0.98Nからなるp型コンタクト層16bの表面上に、ITOからなる透光性正極17と、その上に正極表面側から順にTi、Al、Auを積層した構造を有する正極ボンディングパッド18を形成した。また、ウェーハの一部にドライエッチングを施し、n型コンタクト層14b上の露出領域14dを露出させ、この部分にNi、Al、Ti、及びAuの4層よりなる負極19を作製した。これらの工程により、ウェーハ上に、図2及び3に示すような形状を持つ各電極を作製した。

【0103】

上述のようにしてp型半導体層及びn型半導体層の両方に電極を形成したウェーハについて、基板11の裏側を研削及び研磨してミラー状の面として350μm角の正方形のチップに切断し、各電極が上になるようにリードフレーム上に載置し、金線でリードフレームに結線することにより、半導体発光素子とした。この半導体発光素子(発光ダイオード)の正極ボンディングパッド18及び負極19の電極間に順方向電流を流したところ、電流20mAにおける順方向電圧は3.0Vであった。また、p側の透光性正極17を通して発光状態を観察したところ、発光波長は470nmであり、発光出力は15mWを示した。このような発光ダイオードの発光特性は、作製したウェーハのほぼ全面から作製された発光ダイオードについて、ばらつきなく得られた。

【0104】

[実施例3]

本例では、サファイアからなる基板のc面上に、バッファ層として、回転カソード式のRFスパッタ装置を用いてAlNの柱状結晶の集合体を形成し、その上に、下地層として、AlNからなるバッファ層を成膜したのと同じスパッタ装置でGaN層(n型コンタクト層14b)を形成した。そして、その上にMOCVD法により、実施例2と同様に発光素子半導体積層構造を形成した。

バッファ層をスパッタする際の基板の温度は700℃とし、下地層を成膜する際の基板の温度は900℃とした。その他の成膜条件は、全て実施例2と同一とした。

そして、反応装置からウェーハを取り出したところ、ウェーハの表面が鏡面であることが確認できた。

【0105】

そして、断面TEM法を用いて上記ウェーハを観察した。RFスパッタにて成膜したAlN層(バッファ層)は、グレインの幅が50nm程度の柱状結晶となっていることが確認できた。また、バッファ層は基板全面を覆って形成されていた。

【0106】

次いで、上述のようにして作製したウェーハを、実施例2と同様にして発光ダイオードチップとした。電極間に順方向電流を流したところ、電流20mAにおける順方向電圧は3.1Vであった。また、p側の透光性電極を通して発光を観察したところ、発光波長は460nmであり、発光出力は13mWを示した。このような発光ダイオードの発光特性は、作製したウェーハのほぼ全面から作製された発光ダイオードについて、ばらつきなく得られた。

【0107】

[実施例4]

本例では、Si(111)基板上に、バッファ層として、回転カソード式のRFスパッタ装置を用いてAlGaNの柱状結晶の集合体を形成し、その上に、下地層として、実施例1同じ装置を用いてSiをドープしたAlGaNの層を形成し、さらにその上に、実施例2と同様の方法で発光素子半導体積層構造を形成した。ここで、バッファ層のAl組成は70%とし、下地層のAl組成は15%とした。また、スパッタ時の基板の温度は500℃とし、下地層の成膜温度は700℃とした。その他の成膜条件は、実施例1と同一である。

実施例4では、発光素子半導体積層構造を成長させた後、反応装置からウェーハを取り出したところ、ウェーハ表面が鏡面であることが確認できた。

【0108】

そして、断面TEM法を用いて上記ウェーハを観察した。RFスパッタにて成膜したGaAlN層(バッファ層)は、グレインの幅が30nm程度の柱状結晶となっていることが確認できた。また、バッファ層は基板全面を覆って形成されていた。

【0109】

次いで、上記のようにして作製したウェーハを、実施例2と同様にして発光ダイオードチップとした。本例では、各電極を、半導体積層構造側と基板側の上下に設置した。電極間に順方向電流を流したところ、電流20mAにおける順方向電圧は2.9Vであった。また、p側の透光性電極を通して発光を観察したところ、発光波長は460nmであり、発光出力は10mWを示した。このような発光ダイオードの発光特性は、作製したウェーハのほぼ全面から作製された発光ダイオードについて、ばらつきなく得られた。

【0110】

[実施例5]

本例では、ZnO(0001)基板上に、バッファ層として、RFマグネトロンスパッタ法を用いてGaNの柱状結晶の集合体を形成し、その上に、下地層として、実施例1と同じ装置を用いて、GeをドープしたAlGaNの層を形成し、さらにその上に、実施例2と同様の方法で発光素子半導体積層構造を形成した。ここで、下地層のAl組成は10%とした。また、バッファ層のスパッタ時の基板の温度は室温とし、下地層の成膜時の基板の温度は750℃とした。また、本例では、525nm付近の緑色LEDの作製を試みたため、発光層に含有されるInの原料流量を増量した。

実施例5では、発光素子半導体積層構造を成長させた後、反応装置からウェーハを取り出したところ、ウェーハ表面が鏡面であることが確認できた。

【0111】

そして、断面TEM法を用いて上記ウェーハを観察した。GaN層は、グレインの幅が5nm程度の柱状結晶となっていることが確認できた。また、バッファ層は基板全面を覆って形成されていた。

【0112】

上述のようにして作製したウェーハを、実施例2と同様の方法で発光ダイオードチップとし、また、実施例4と同様に、各電極を積層構造側と基板側の上下に設置した。そして、電極間に順方向電流を流したところ、電流20mAにおける順方向電圧は3.3Vであった。また、p側の透光性電極を通して発光を観察したところ、発光波長は525nmであり、発光出力は10mWを示した。このような発光ダイオードの発光特性は、作製したウェーハのほぼ全面から作製された発光ダイオードについて、ばらつきなく得られた。

【0113】

以上の結果により、本発明に係るIII族窒化物化合物半導体発光素子が、生産性に優れ、また、優れた発光特性を備えていることが明らかである。

【産業上の利用可能性】

【0114】

本発明で得られるIII族窒化物化合物半導体発光素子は、良好な結晶性を持つIII族窒化物化合物半導体結晶からなる表面層を有している。

従って、優れた発光特性を有する発光ダイオード、レーザダイオード、或いは電子デバイス等の半導体素子を作製することが可能となる。

【図面の簡単な説明】

【0115】

【図1】本発明に係るIII族窒化物化合物半導体発光素子の一例を模式的に説明する図であり、積層半導体の断面構造を示す概略図である。

【図2】本発明に係るIII族窒化物化合物半導体発光素子の一例を模式的に説明する図であり、平面構造を示す概略図である。

【図3】本発明に係るIII族窒化物化合物半導体発光素子の一例を模式的に説明する図であり、断面構造を示す概略図である。

【図4】本発明に係るIII族窒化物化合物半導体発光素子を用いて構成したランプを模式的に説明する概略図である。

【図5】本発明に係るIII族窒化物化合物半導体発光素子の一例を模式的に説明する図であり、断面構造を示す透過型電子顕微鏡(TEM)写真である。

【図6】本発明に係るIII族窒化物化合物半導体発光素子の一例を模式的に説明する図であり、図5に示すTEM写真を模式化して示す図である。

【図7】本発明に係るIII族窒化物化合物半導体発光素子の製造方法の一例を模式的に説明する図であり、スパッタ装置の構造を示す概略図である。

【符号の説明】

【0116】

1…III族窒化物化合物半導体発光素子、10…積層半導体、11…基板、11a…表面、12…バッファ層、13…下地層、14…n型半導体層、15…発光層、16…p型半導体層、17…透光性正極、3…ランプ

【特許請求の範囲】

【請求項1】

基板上に、III族元素としてGaを含むIII族窒化物化合物半導体からなる半導体層をスパッタ法によって成膜する工程を含むIII族窒化物化合物半導体発光素子の製造方法であって、

前記半導体層をスパッタ法で成膜する際に、前記基板に印加するバイアス値を0.1W/cm2以上とすることを特徴とするIII族窒化物化合物半導体発光素子の製造方法。

【請求項2】

基板上に、III族元素としてGaを含むIII族窒化物化合物半導体からなる半導体層をスパッタ法によって成膜する工程を含むIII族窒化物化合物半導体発光素子の製造方法であって、

前記半導体層をスパッタ法で成膜する際に、スパッタターゲットに印加するパワーを0.1W/cm2〜100W/cm2の範囲とすることを特徴とするIII族窒化物化合物半導体発光素子の製造方法。

【請求項3】

窒化物原料をリアクタ内に流通させるリアクティブスパッタ法によって前記半導体層を成膜することを特徴とする請求項1又は2に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項4】

前記窒化物原料として窒素を用いたことを特徴とする請求項3に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項5】

前記基板と前記半導体層との間に、柱状結晶からなるバッファ層を形成することを特徴とする請求項1〜4の何れか1項に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項6】

前記バッファ層を、スパッタ法で形成することを特徴とする請求項5に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項7】

前記バッファ層を、Alを含有するIII族窒化物化合物で形成することを特徴とする請求項5又は6に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項8】

前記バッファ層を、AlNで形成することを特徴とする請求項7に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項9】

前記バッファ層を、前記基板の表面の少なくとも90%以上を覆うように形成することを特徴とする請求項5〜8の何れか1項に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項10】

前記バッファ層を構成する柱状結晶の幅が0.1〜100nmの範囲であることを特徴とする請求項5〜9の何れか1項に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項11】

前記バッファ層の膜厚が10〜500nmの範囲であることを特徴とする請求項5〜10の何れか1項に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項12】

前記バッファ層をAlNで形成するとともに、III族窒化物化合物からなる前記半導体層をGaNで形成することを特徴とする請求項5〜11の何れか1項に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項13】

前記基板にサファイアを用いることを特徴とする請求項1〜12の何れか1項に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項14】

請求項1〜13の何れか1項に記載の製造方法で得られるIII族窒化物化合物半導体発光素子。

【請求項15】

請求項14に記載のIII族窒化物化合物半導体発光素子が用いられてなるランプ。

【請求項1】

基板上に、III族元素としてGaを含むIII族窒化物化合物半導体からなる半導体層をスパッタ法によって成膜する工程を含むIII族窒化物化合物半導体発光素子の製造方法であって、

前記半導体層をスパッタ法で成膜する際に、前記基板に印加するバイアス値を0.1W/cm2以上とすることを特徴とするIII族窒化物化合物半導体発光素子の製造方法。

【請求項2】

基板上に、III族元素としてGaを含むIII族窒化物化合物半導体からなる半導体層をスパッタ法によって成膜する工程を含むIII族窒化物化合物半導体発光素子の製造方法であって、

前記半導体層をスパッタ法で成膜する際に、スパッタターゲットに印加するパワーを0.1W/cm2〜100W/cm2の範囲とすることを特徴とするIII族窒化物化合物半導体発光素子の製造方法。

【請求項3】

窒化物原料をリアクタ内に流通させるリアクティブスパッタ法によって前記半導体層を成膜することを特徴とする請求項1又は2に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項4】

前記窒化物原料として窒素を用いたことを特徴とする請求項3に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項5】

前記基板と前記半導体層との間に、柱状結晶からなるバッファ層を形成することを特徴とする請求項1〜4の何れか1項に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項6】

前記バッファ層を、スパッタ法で形成することを特徴とする請求項5に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項7】

前記バッファ層を、Alを含有するIII族窒化物化合物で形成することを特徴とする請求項5又は6に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項8】

前記バッファ層を、AlNで形成することを特徴とする請求項7に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項9】

前記バッファ層を、前記基板の表面の少なくとも90%以上を覆うように形成することを特徴とする請求項5〜8の何れか1項に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項10】

前記バッファ層を構成する柱状結晶の幅が0.1〜100nmの範囲であることを特徴とする請求項5〜9の何れか1項に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項11】

前記バッファ層の膜厚が10〜500nmの範囲であることを特徴とする請求項5〜10の何れか1項に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項12】

前記バッファ層をAlNで形成するとともに、III族窒化物化合物からなる前記半導体層をGaNで形成することを特徴とする請求項5〜11の何れか1項に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項13】

前記基板にサファイアを用いることを特徴とする請求項1〜12の何れか1項に記載のIII族窒化物化合物半導体発光素子の製造方法。

【請求項14】

請求項1〜13の何れか1項に記載の製造方法で得られるIII族窒化物化合物半導体発光素子。

【請求項15】

請求項14に記載のIII族窒化物化合物半導体発光素子が用いられてなるランプ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2008−47763(P2008−47763A)

【公開日】平成20年2月28日(2008.2.28)

【国際特許分類】

【出願番号】特願2006−223261(P2006−223261)

【出願日】平成18年8月18日(2006.8.18)

【出願人】(000002004)昭和電工株式会社 (3,251)

【Fターム(参考)】

【公開日】平成20年2月28日(2008.2.28)

【国際特許分類】

【出願日】平成18年8月18日(2006.8.18)

【出願人】(000002004)昭和電工株式会社 (3,251)

【Fターム(参考)】

[ Back to top ]