III族窒化物化合物半導体積層構造体の成膜方法

【課題】均一性の良い結晶膜を短時間で得ることができる技術である、スパッタ法をIII族窒化物化合物半導体層を作製するに際して使用し、安定して良好な結晶性のIII族窒化物化合物半導体層を得る。

【解決手段】基板上に、III族窒化物化合物半導体からなる多層膜構造を成膜させる方法において、該多層膜構造は少なくとも基板側からバッファ層と下地層を含み、バッファ層と下地層をスパッタ法で積層し、かつ、バッファ層の膜厚が5nm〜500nmであることを特徴とするIII族窒化物化合物半導体積層構造体の成膜方法。

【解決手段】基板上に、III族窒化物化合物半導体からなる多層膜構造を成膜させる方法において、該多層膜構造は少なくとも基板側からバッファ層と下地層を含み、バッファ層と下地層をスパッタ法で積層し、かつ、バッファ層の膜厚が5nm〜500nmであることを特徴とするIII族窒化物化合物半導体積層構造体の成膜方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、発光ダイオード(LED)、レーザダイオード(LD)および電子デバイス等の作製に用いられる結晶性の良いIII族窒化物化合物半導体(以下、III族窒化物化合物半導体はInGaAlNで表されるものとする)積層構造体の成膜方法に関する。特に、本発明は結晶性の良いIII族窒化物化合物半導体結晶をサファイア基板上にエピタキシャル成長させるために好適に用いることができるIII族窒化物化合物半導体積層構造体の成膜方法に関する。

【背景技術】

【0002】

III族窒化物化合物半導体は、可視光から紫外光領域に相当するエネルギーの直接遷移型のバンドギャップを持ち高効率な発光が可能であるため、LEDやLDとして製品化されている。また、電子デバイスとしても従来のIII−V族化合物半導体では得られない特性が得られるポテンシャルを持っている。

【0003】

一般的には、トリメチルガリウム(TMG)、トリメチルアルミニウム(TMA)およびアンモニア(NH3)を原料として、III族窒化物化合物半導体は有機金属化学気相成長(MOCVD)法によって製造されている。MOCVD法は、キャリアガスに原料の蒸気を含ませて基板表面に運搬し、加熱された基板との反応により原料が分解して結晶を成長させる方法である。

【0004】

III族窒化物化合物半導体の単結晶ウエーハはいまだ市販されておらず、III族窒化物化合物半導体は異なる材料の単結晶ウエーハ上に結晶を成長させる方法が一般的である。このような異種基板と、その上にエピタキシャル成長させるIII族窒化物化合物半導体結晶の間には大きな格子不整合が存在する。例えばサファイア(Al2O3)と窒化ガリウム(GaN)の間には16%、SiCと窒化ガリウムの間には6%の格子不整合が存在する。一般にこのような大きな格子不整合が存在する場合には、基板上に結晶を直接エピタキシャル成長させることが困難であり、成長させても結晶性の良好な結晶は得られない。そこで、有機金属化学気相成長(MOCVD)法によりサファイア単結晶基板やSiC単結晶基板の上にIII族窒化物化合物半導体結晶をエピタキシャル成長する場合、特許第3026087号公報(特許文献1)や特開平4−297023号公報(特許文献2)に示されているように、窒化アルミニウム(AlN)や窒化アルミニウムガリウム(AlGaN)で構成される低温バッファ層と呼ばれる層を基板の上にまず堆積し、その上に高温でIII族窒化物化合物半導体結晶をエピタキシャル成長させる方法が一般に行われてきた。

【0005】

バッファ層としてAlNなどの層を、MOCVD以外の方法で成膜し、それ以降の層をMOCVD法で成膜する技術に関しても、いくつか報告がある。例えば、特公平5−86646号公報(特許文献3)には高周波スパッタで成膜したバッファ層上に、MOCVD法で同じ組成の結晶を成長させる技術が記載されている。しかし、特許第3440873号公報(特許文献4)および特許第3700492号公報(特許文献5)のなかで、この特公平5−86646号公報(特許文献3)に記載されている技術だけでは安定して良好な結晶を得ることができない旨が記載されている。安定して良好な結晶を得るために、特許第3440873号公報(特許文献4)ではバッファ層成長後にアンモニアと水素からなる混合ガス中でアニールすることが、そして特許第3700492号公報(特許文献5)ではバッファ層を400℃以上の温度でDCスパッタにより成膜することが重要であるとされている。

【0006】

一方、III族窒化物化合物半導体結晶をスパッタによって製造する研究も行われている。例えば、特開昭60−39819号公報(特許文献6)では、高抵抗のGaNを積層することを目的として、サファイア基板上に直接スパッタによるGaNの成膜を実施している。用いている条件は、到達真空度5×10-7〜10-8Torr、チャンバ内流通ガスはArとN2、スパッタ時ガス圧3〜5×10-2Torr、RF電圧0.7〜0.9kV(パワーにして20〜40W)、基板とターゲットの距離20〜50mm、基板温度150〜450℃などである。しかし目的とする用途には、発光素子の下地層には言及されておらず、この膜の上に層を形成する記述はない。

【0007】

また、21世紀連合シンポジウム論文集、Vol 2nd、p295(2003)(非特許文献1)には、N2ガスを用いた高周波マグネトロンスパッタリングによってSi(100)およびAl2O3(0001)上にGaN膜を成膜したと記載されている。成膜の条件としては、全ガス圧力は2mTorr、投入電力は100Wとし、基板温度を室温から900℃まで変化させている。論文に掲げられた図によれば、用いた装置はターゲットと基板を対向させたものである。

【0008】

また、Vacuum、Vol66、P233(2002)(非特許文献2)では、カソードとターゲットを向かい合わせ、基板とターゲットの間にメッシュを入れた装置でGaNを成膜している。これによると、成膜条件はN2ガス中で圧力を0.67Paとし、基板温度は84〜600℃であり、投入電力は150W、基板とターゲット間の距離は80mmとされている。

【0009】

【特許文献1】特許第3026087号公報

【特許文献2】特開平4−297023号公報

【特許文献3】特公平5−86646号公報

【特許文献4】特許第3440873号公報

【特許文献5】特許第3700492号公報

【特許文献6】特開昭60−39819号公報

【非特許文献1】21世紀連合シンポジウム論文集、Vol 2nd、p295(2003)

【非特許文献2】Vacuum、Vol66、P233(2002)

【発明の開示】

【発明が解決しようとする課題】

【0010】

本発明の目的は、均一性の良い結晶膜を短時間で得ることができる技術である、スパッタ法をIII族窒化物化合物半導体層を作製する際に使用し、安定して良好な結晶性のIII族窒化物化合物半導体層を得ることである。

【課題を解決するための手段】

【0011】

本発明は、上記の課題を解決するために下記の発明を提供する。

(1)基板上に、III族窒化物化合物半導体からなる多層膜構造を成膜させる方法において、該多層膜構造は少なくとも基板側からバッファ層と下地層を含み、バッファ層と下地層をスパッタ法で積層し、かつ、バッファ層の膜厚が5nm〜500nmであることを特徴とするIII族窒化物化合物半導体積層構造体の成膜方法;

(2)バッファ層がAlを含んでいる上記(1)記載のIII族窒化物化合物半導体積層構造体の成膜方法;

(3)バッファ層がAlNである上記(2)記載のIII族窒化物化合物半導体積層構造体の成膜方法;

(4)バッファ層が柱状結晶の集合体である上記(2)もしくは(3)記載のIII族窒化物化合物半導体積層構造体の成膜方法;

(5)バッファ層が基板表面の少なくとも60%を覆っている上記(2)〜(4)のいずれか記載のIII族窒化物化合物半導体積層構造体の成膜方法;

(6)下地層がGaを含んでいる上記(1)記載のIII族窒化物化合物半導体積層構造体の成膜方法;

(7)下地層がGaNである上記(6)記載のIII族窒化物化合物半導体積層構造体の成膜方法;

(8)バッファ層がAlNであり、かつ、下地層がGaNである上記(1)〜(3)、(6)および(7)のいずれか記載のIII族窒化物化合物半導体積層構造体の成膜方法、

である。

【発明の効果】

【0012】

本発明のIII族窒化物化合物半導体積層構造体の成膜方法によれば、最も膜厚が厚く良好な均一性が必要な下地層を、量産性、均一性の良好なスパッタ法で形成することで、生産性の改善と特性の良好な素子の形成を実現できる。すなわち、本発明は、スパッタ法で特定の膜厚を有するバッファ層を成膜し、その上に同じくスパッタ法でGaを含む層を成膜する、III族窒化物化合物半導体積層構造体を成膜する技術を提供しうる。

【発明を実施するための最良の形態】

【0013】

本発明は、III族窒化物半導体積層構造を成膜するに当たり、バッファ層と下地層をスパッタ法で作製する際の、バッファ層の適正な膜厚を規定する。

【0014】

一般的にスパッタ法は単組成の結晶を成膜するのに適しており、均一性、生産性、安定性に優れている。また、ダストなどのチャンバ内のコンタミネーションも少ない。このため、スパッタによって良好な結晶性のGaN膜の成膜を行う技術が求められていた。本発明者は、鋭意研究を重ねた結果、スパッタ法によって結晶性の良好なIII族窒化物化合物半導体結晶を得るために、バッファ層の膜厚がIII族窒化物化合物半導体からなる下地層の結晶性を制御するために重要であることを見出した。

【0015】

本発明において、バッファ層の膜厚は5nm〜500nmであることが必要である。これより薄いと基板との格子定数の差から生じる歪を解消しきれない。一方、これより厚いとバッファ層の表面に凹凸を生じて、良好なバッファ層として機能しなくなる。更に望ましくは膜厚が、10nm〜300nmであり、特に望ましくは膜厚が、150Å〜1000Åである。

【0016】

バッファ層成膜時の基板温度は、室温〜1200℃であることが望ましい。それより低い温度では、基板面でのマイグレーションが抑えられて、結晶性の良いIII族窒化物化合物半導体結晶ができにくい。一方、これより高い温度ではIII族窒化物化合物半導体結晶が分解を引き起こす。

【0017】

さらに望ましくは室温〜800℃の温度であり、更に望ましくは300〜800℃である。

【0018】

一方、下地層の成膜温度としては、300℃〜1500℃が望ましく、更に望ましくは500℃〜1000℃である。

【0019】

バッファ層と下地層の成膜温度の差としては、100℃〜800℃が望ましく、更に望ましくは400℃〜700℃である。

<スパッタ成膜装置>

スパッタ法には、RFスパッタとDCスパッタがある。一般的に、本発明におけるように金属と窒素を反応させて成膜するリアクティブスパッタを用いた場合には、連続的に放電させるDCスパッタでは帯電が激しく、成膜レートがコントロールできない。このため、RFスパッタや、DCスパッタでもパルス的にバイアスを与えるパルスDCスパッタを用いることが望ましい。

【0020】

また、RFスパッタを用いた場合には、膜厚の均一性を向上させる方法として、マグネットの位置をターゲット内で移動させることが望ましい。具体的な運動の方法は装置により選択することができ、揺動させたり、回転運動させたりすることができる。

【0021】

スパッタによってIII族窒化物系化合物半導体結晶を成膜する場合には、結晶成長時に、より高エネルギーの反応種を基板に供給することが望ましい。このため、装置としては、基板がプラズマ中に位置するようにする。そこで、ターゲットと基板の位置が、対面していることが望ましい。また、基板とターゲットの距離が10mm〜100mmであることが望ましい。

【0022】

また、チャンバ内にはできるだけ不純物を残したくないので、成膜に使用する装置は、到達真空度が、1.0×10-3Pa以下であることが望ましい。

<バッファ層の材料>

バッファ層を構成する材料としては、一般式AlGaInNで表される、III族窒化物化合物半導体であればどのような材料をも用いることができる。更に、V族としてAsやPを含んでも構わない。しかし、中でも、Alを含んだ組成とすることが望ましい。また、特に、GaAlNとすることが望ましく、Alの組成は50%以上であることが好適である。更に、AlNは良好な結晶性を得ることができるので、更に好適である。

【0023】

バッファ層は、以下に記述されるような柱状結晶の集合体を成すことが望ましい。そのためには、スパッタ法を用いて低温で成膜することで、良好な柱状結晶とすることができて、その密度や結晶性や被覆率を制御することも容易である。

【0024】

本発明でいう柱状結晶とは隣接する結晶粒との間に結晶粒界を形成して隔てられており、自身は縦断面形状として、柱状になっている結晶をいう。柱状結晶からなるバッファ層を基板上に形成して成膜した場合に、その上に成膜したIII族窒化物化合物半導体は良好な結晶性を持つ結晶膜となる。

【0025】

バッファ層は、隙間なく基板上を覆っていることが望ましい。バッファ層が基板を覆っておらず、基板の表面が一部分でも露出していると、バッファ層上に成膜したIII族窒化物結晶層と基板上に直接成膜されたIII族窒化物結晶層で結晶の格子定数が異なるため、均一な結晶とならないおそれがある。結果として、ヒロックやピットを生じてしまう。

【0026】

このため、バッファ層は、基板表面の少なくとも60%を覆っている必要がある。更に望ましくは80%以上であり、90%以上を覆っていることが最も望ましい。

【0027】

バッファ層が基板を覆っている割合は、上記断面TEM写真から測定することができる。特に、バッファ層とIII族窒化物結晶層の材料が異なる場合には、電子線エネルギー分散スペクトル(EDS)などを用いて基板と層の界面を基板面と平行にスキャンすることで、バッファ層が形成されていない領域の比を見積もることもできる。また、バッファ層だけを成膜した試料を用意することで、原子間力顕微鏡(AFM)などの手法により基板の露出した面積を測定することも可能である。本発明では上記断面透過電子顕微鏡(TEM)写真から測定した。

【0028】

バッファ層は、柱状結晶の個々の結晶のグレインの幅を適正に制御することが好適である。具体的には、各柱状結晶の幅が、0.1nm〜100nmの間の値であることが望ましい。更に望ましくは、1nm〜70nmの間の値である。

【0029】

各柱状結晶の幅は、上記断面TEM写真により容易に測定することが可能である。即ち、各柱状結晶の境界の間隔が各柱状結晶の幅である。各柱状結晶の幅は精密に規定できるものではなく、ある程度の分布を持つ。従って、各柱状結晶の幅が上記範囲から外れる結晶が数%程度あったとしても、本発明の効果に影響を及ぼすものではない。90%以上が上記範囲に入っていることが好ましい。

<バッファ層の成膜条件>

スパッタを用いて成膜する場合、重要なパラメーターは、基板温度、窒素分圧、成膜レート、バイアス、パワーである。

【0030】

チャンバ内の雰囲気には、窒素を含むことが必然であることは言うまでもない。窒素は、プラズマ化されて分解し、結晶成長の原料となる。また、ターゲットを効率よくスパッタするために、重くて反応性の低い気体を混入させることも良く行われる。例えば、アルゴンなどである。窒素とアルゴンの流量に対する窒素流量の比は、窒素が20%〜98%であることが望ましい。これより小さい流量比ではスパッタ金属が金属のまま付着するし、これより大きい流量比ではアルゴンの量が少なく、スパッタ速度が低下する。特に望ましくは25%〜90%である。

【0031】

成膜速度は、0.001nm/秒〜0.5nm/秒とすることが望ましい。これより大きい速度では膜が結晶体とならずに非晶質となる。これより小さい成膜速度では、プロセスが無駄に長時間となり、工業的に利用することが難しい。

【0032】

結晶成長時のマイグレーションを活発にしたいので、基板側にかかるバイアス、およびターゲット側にかかるパワーは大きいほうが良い。例えば、成膜時の基板にかけるバイアスを1.5W以上とする、成膜時にターゲットに印加するパワーを0.01W/cm2〜5kW/cm2の間とする、などである。

<下地層の材料>

本発明者等の実験の結果では、下地層の材料としてはGaを含むIII族窒化物が望ましい。良好な結晶性となすために、マイグレーションによって転位をループ化させる必要があるが、転位のループ化を生じやすい材料とは、Gaを含む窒化物である。特に、AlGaNが望ましく、GaNも好適である。

【0033】

下地層は、必要に応じてドーパントをドープした構造とすることもできるし、ドープしない構造とすることもできる。導電性の基板を用いる場合には、下地層をドーピングして層構造を縦方向に電流が流れるようにすることで、チップの両面に電極をつけた構造とすることが望ましい。絶縁性の基板を用いる場合には、チップの同じ面に電極が形成されたチップ構造を採ることになるので、基板直上の層は結晶性の良好なドープしない結晶とすることが、望ましい。

【0034】

下地層は、上記バッファ層上に生じた結晶核を種として成長し、転位をループ化させながら平坦化してゆくことが望ましい。転位をループ化させながら成長させるためには、マイグレーションを活発にしてファセット成長に近づける必要がある。

【0035】

このため、下地層の成膜時の基板温度は、バッファ層より高いことが望ましい。バッファ層の成膜温度より高い温度とすることで、バッファ層に生じさせた転位(柱状結晶の界面)をループ化させることができる。バッファ層よりも低い温度で下地層を成膜すると、バッファ層と同等の結晶性の膜を成膜することになり、転位密度の低減が達成できない。

<下地層の成膜条件>

次に、下地層を成膜する際のパラメーターについて述べる。

【0036】

チャンバ内の雰囲気には、窒素を含むことが必然であることは言うまでもない。窒素は、プラズマ化されて分解し、結晶成長の原料となる。また、ターゲットを効率よくスパッタするために、重くて反応性の低い気体を混入させることも良く行われる。例えば、アルゴンなどである。窒素とアルゴンの流量に対する窒素流量の比は、窒素が20%〜100%であることが望ましい。これより小さい流量比ではスパッタ金属が金属のまま付着するおそれがあり、特に望ましくは50%〜100%である。

【0037】

成膜速度は、0.05nm/秒〜5nm/秒とすることが望ましい。これより大きい速度では膜が結晶体とならずに非晶質となる。これより小さい成膜速度では、プロセスが無駄に長時間となり、工業的に利用することが難しい。

【0038】

結晶成長時のマイグレーションを活発にしたいので、基板側にかかるバイアス、およびターゲット側にかかるパワーは大きいほうが良い。例えば、成膜時の基板にかけるバイアスを1.5W以上とする、成膜時にターゲットに印加するパワーを0.01W/cm2〜5kW/cm2の間とする、などである。

<その他の層>

上記下地層には、更に素子機能を持つ層を積層することが可能である。例えば、発光層であればコンタクト層、クラッド層、発光層、レーザ素子であればこれらのほかに光閉じ込め層などを形成できる。また、電子デバイスであれば、電子走行層や閉じ込め層などを形成できる。

【0039】

これらの層は、スパッタ法に限らず、一般に知られたどのような方法を用いても作製することが可能である。例えば、MOCVD法やMBE法を用いることが可能である。

<基板>

本発明に用いることができる基板としては、一般にIII族窒化物化合物半導体結晶を成膜できる基板であれば、どのような材料も用いることが可能である。例えば、サファイア、SiC、シリコン、酸化亜鉛、酸化マグネシウム、酸化マンガン、酸化ジルコニウム、酸化マンガン亜鉛鉄、酸化マグネシウムアルミニウム、ホウ化ジルコニウム、酸化ガリウム、酸化インジウム、酸化リチウムガリウム、酸化リチウムアルミニウム、酸化ネオジウムガリウム、酸化ランタンストロンチウムアルミニウムタンタル、酸化ストロンチウムチタン、酸化チタン、ハフニウム、タングステンおよびモリブデンなどである。中でも、高温でアンモニアに接触することで化学的な変性を引き起こすことが知られている酸化物基板や金属基板などに対して、アンモニアを使用しないスパッタ法は有効な成膜方法として利用できる。

【0040】

また、一般的にスパッタ法は基板の温度を低く抑えることが可能なので、高温で分解してしまう性質を持つ基板上にも、基板にダメージを与えることなく成膜が可能である。

【0041】

基板は、湿式の前処理を行うことが望ましい。例えばシリコン基板に対しては、よく知られたRCA洗浄方法などを行い、表面を水素終端させておくことで安定したプロセスとなる。

【0042】

一方、反応器の中に導入後に、逆スパッタなどの方法を用いて前処理を行うこともできる。具体的には、ArやN2のプラズマ中にさらす事によって表面を整えることができる。例えば、ArガスやN2ガスなどのプラズマを基板表面に作用させることで、表面に付着した有機物や酸化物を除去することが可能である。この場合は基板とチャンバ間に電圧をかけることにより、プラズマ粒子が効率的に基板に作用する。

<用途に関して>

本発明方法で製造した素子をパッケージしてランプとして使用することが可能である。また蛍光体と組み合わせることにより、発光色を変える技術が知られており、これをなんら問題なく利用することが可能である。例えば、蛍光体を適正に選定することにより発光素子より長波長の発光を得ることができるし、発光素子自身の発光波長と蛍光体によって変換された波長とを混ぜることによって、白色のパッケージとすることもできる。

【実施例】

【0043】

以下、本発明を実施例に基づいて具体的に説明する。しかし、本発明はこれらの実施例にのみ限定されるものではない。

【0044】

(実施例1)

本実施例では、c面サファイア基板上に、バッファ層としてRFスパッタ法を用いてAlNの柱状結晶の集合体を形成し、その上に第二の層として異なるチャンバ内で、RFスパッタ中でGaNの層を形成した。

【0045】

まず、片面のみをエピタキシャル成長に使用できる程度に鏡面研磨したc面サファイア基板を、特に湿式の前処理を行わずにスパッタ機の中へ導入した。使用するスパッタ機は、高周波式の電源を持ち、ターゲット内でマグネットを回転させることにより、磁場の掛かる位置を動かすことができる機構を持っている。

【0046】

はじめに、スパッタ装置内で基板を750℃まで加熱し、窒素ガスを15sccmの流量で導入した後、チャンバ内の圧力を0.08Paに保持して、基板側に50Wの高周波バイアスを印加し、窒素プラズマに晒すことで、基板表面を洗浄した。

【0047】

続いて、アルゴンおよび窒素ガスを導入した後、基板温度を500℃まで低下させた。0.95W/cm2のパワーを金属Alターゲット側に印加し、炉内の圧力を0.5Paに保ち、Arガスを15sccm、窒素ガスを5sccm流通させた条件(ガス全体に対する窒素の比は25%)で、サファイア基板上にAlNを成膜した。成長速度は0.12nm/sであった。

【0048】

ターゲット内のマグネットは、基板洗浄の際も成膜の際も、回転させておいた。

【0049】

500ÅのAlNを成膜後、プラズマを立てるのを止め、基板を取り出した。

【0050】

続いて、異なるスパッタチャンバ内に基板を搬送した。GaNの成膜に使用するスパッタ機は、高周波式の電源を持ち、四角形のGaターゲット内をマグネットがスイープすることで磁場の掛かる位置を動かすことができる機構を持っている。Gaターゲット内には冷媒を流通させるための配管を設置し、配管内を20℃に冷却した冷媒を流通させて、熱によるGaの融解を防いだ。

【0051】

続いて、アルゴンおよび窒素ガスを導入した後、基板温度を1000℃まで上昇させた。1.3W/cm2のパワーを金属Gaターゲット側に印加し、炉内の圧力を0.5Paに保ち、Arガスを5sccm、窒素ガスを15sccm流通させた条件(ガス全体に対する窒素の比は75%)で、サファイア基板上にGaNを成膜した。成長速度は、おおよそ1nm/sであった。6μmのGaNを成膜後、プラズマを立てるのを止めた。

【0052】

続いて同じ条件にて、1×1019cm-3の電子濃度を持つ2μmのSiドープGaN層を成膜した。

【0053】

各条件はアンドープ層と同じとし、そこへチャンバ内に設置したSiターゲットへイオン銃から放出したイオンを照射してSiを取り出し、Siをドープした。

【0054】

以上の工程により、サファイア基板上に柱状構造を持つAlNの第一の層を形成し、その上にアンドープで6μmの膜厚のGaN層と1×1019cm-3の電子濃度を持つ2μmのSiドープGaN層を形成した本発明のIII族窒化物化合物半導体積層構造体を作製した。取り出した基板は無色透明のミラー状を呈した。

【0055】

次に、上記の方法で成長を行ったアンドープGaN層のX線ロッキングカーブ(XRC)測定を行った。測定には、Cuβ線X線発生源を光源として用いて、対称面である(0002)面と非対称面である(10−10)面で行った。一般的に、III族窒化物化合物半導体の場合、(0002)面のXRCスペクトル半値幅は結晶の平坦性(モザイシティ)の指標となり、(10−10)面のXRCスペクトル半値幅は転位密度(ツイスト)の指標となる。この測定の結果、本発明の方法で作製したアンドープGaN層は、(0002)面の測定では半値幅80arcsec、(10−10)面では半値幅250arcsecを示した。

【0056】

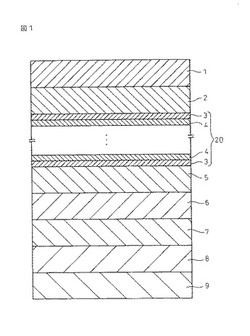

以上の手順にて作製したSiドープGaN層上に、MOCVD法にて素子構造を形成し、最終的に図1に示す半導体発光素子用の層構造を有するエピタキシャルウェーハを作製した。つまりエピタキシャルウェーハは、c面を有するサファイア基板9上に、柱状の構造を持つAlN層8(バッファ層)を形成したのち、基板側から順に、6μmのアンドープGaN層7(下地層)、1×1019cm-3の電子濃度を持つ2μmのSiドープGaN層6、1×1018cm-3の電子濃度を持つ20nmのIn0.1Ga0.9Nクラッド層5、GaN障壁層に始まりGaN障壁層に終わる、層厚を16nmとする6層のGaN障壁層3と、層厚を3nmとする5層のノンドープのIn0.2Ga0.8N井戸層4とからなる多重量子井戸構造20、5nmのMgをドープしたAl0.1Ga0.9Nクラッド層2、膜厚200nmのMgドープAl0.02Ga0.98N層1、を積層した構造を有する。

【0057】

また、本実施例で作製した半導体発光素子の電極構造の平面図を図2に示す。図中、10はn側電極、11はn電極を形成するためのSiドープGaN層6の露出面、12はp電極ボンディングパッド、および13は透光性p電極である。

【0058】

スパッタにて作製したSiドープGaNウエーハは、MOCVDチャンバ内に入れる前に純水で洗浄し、乾燥させておいた。表面に残ったパーティクルの類を除去することが目的である。

【0059】

まず、SiドープGaN層が成長された基板を、MOCVD炉内へ導入した。

【0060】

その後、炉内を窒素で置換した状態で基板の温度を1000℃まで上昇させて、Si−GaN層の最表面に付着した汚れを昇華させて除去した。基板温度が830℃以上からは、アンモニアを炉内に流通させた。

【0061】

続いて、基板温度を740℃まで低下させたあと、アンモニアはそのまま流通させながら、シラン(SiH4)ガス、およびバブリングによって発生したトリメチルインジウム(TMI)およびトリメチルガリウム(TEG)の蒸気を炉内へ流通し、18nmの膜厚を成すSiドープIn0.1Ga0.9Nクラッド層5を形成した。その後、TMI、TEGおよびSiH4のバルブを切り替え、これらの原料の供給を停止した。

【0062】

次に、GaNよりなる障壁層3とIn0.2Ga0.8Nよりなる井戸層4で構成される多重量子井戸構造20を作製した。多重量子井戸構造の作製にあたっては、SiドープIn0.1Ga0.9Nクラッド層5上に、始めにGaN障壁層3を形成し、そのGaN障壁層上にIn0.2Ga0.8N井戸層4を形成した。この構造を5回繰り返し積層したのち、5番目のIn0.2Ga0.8N井戸層上に、6番目のGaN障壁層を形成し、多重量子井戸構造20の両側をGaN障壁層3から構成した構造とした。

【0063】

すなわち、SiドープIn0.1Ga0.9Nクラッド層5の成長終了後、基板温度や炉内の圧力、キャリアガスの流量や種類はそのままで、TEGのバルブを切り替えてTEGの炉内への供給を行い、GaN障壁層を成長した。これにより、16nmの膜厚を成すGaN障壁層3を形成した。

【0064】

GaN障壁層の成長終了後、基板温度や炉内の圧力、キャリアガスの流量や種類はそのままで、TEGとTMIのバルブを切り替えてTEGとTMIの炉内への供給を行い、In0.2Ga0.8N井戸層を成長した。これにより3nmの膜厚を成すIn0.2Ga0.8N井戸層4を形成した。

【0065】

In0.2Ga0.8N井戸層の成長終了後、再びGaN障壁層の成長を行った。このような手順を5回繰り返し、5層のGaN障壁層と5層のIn0.2Ga0.8N井戸層を作製した。更に、最後のIn0.2Ga0.8N井戸層上にGaN障壁層を形成した。

【0066】

このGaN障壁層で終了する多重量子井戸構造20上に、引き続きMOCVD法を用いて、MgをドープしたAl0.1Ga0.9Nクラッド層2を作製した。

【0067】

まず、炉内の圧力を200mbar、基板温度を1020℃、キャリアガスを窒素から水素に変更し、炉内の圧力と温度が安定するのを待って、TEGとTMAとビスシクロペンタジエニルマグネシウム(Cp2Mg)のバルブを切り替え、これらの原料の炉内への供給を開始し、MgドープのAl0.1Ga0.9Nクラッド層の成長を行った。これにより、5nmの膜厚を成すMgドープのAl0.1Ga0.9Nクラッド層2を形成した。

【0068】

このMgドープのAl0.1Ga0.9Nクラッド層上に、MgドープのAl0.02Ga0.98N層1を作製した。

【0069】

温度、圧力、キャリアガスをクラッド層の成長時と同じに保ったまま、TMAとTMGとCp2Mgの炉内への供給を開始し、成長を行った。Cp2Mgを流通させる量は事前に検討してあり、MgドープAl0.02Ga0.98Nコンタクト層の正孔濃度が8×1017cm-3となるように調整した。これにより、0.15μmの膜厚を成すMgドープAl0.02Ga0.98N層1が形成された。

【0070】

MgドープAl0.02Ga0.98N層の成長を終了した後、ヒータを停止して、基板の温度を室温まで20分をかけて降温した。成長終了直後、NH3の流量を1/50に減量してキャリアを水素から窒素に切り替えた。その後950℃にてNH3を完全に停止した。

【0071】

基板温度が室温まで降温したのを確認して、ウェーハを大気中に取り出した。

【0072】

以上のような手順により、半導体発光素子用のエピタキシャル層構造を有するエピタキシャルウェーハを作製した。ここでMgドープAl0.02Ga0.98N層1はp型キャリアを活性化するためのアニール処理を行わなくてもp型を示した。

【0073】

次いで、上記のサファイア基板上にエピタキシャル層構造が積層されたエピタキシャルウェーハを用いて半導体発光素子の一種である発光ダイオードを作製した。作製したウェーハについて、公知のフォトリソグラフィー技術によってMgドープAl0.02Ga0.98N層の表面上に、ITOからなる透明p電極13と、その上に順にチタン、アルミニウムおよび金を積層した構造を持つp電極ボンディングパッド12を形成し、p側電極とした。更にその後ウェーハにドライエッチングを行い、SiドープGaN層のn側電極を形成する部分11を露出させ、露出した部分にNi、Al、TiおよびAuの4層よりなるn側電極10を作製した。これらの作業により、ウエーハ上に図2に示すような形状を持つ電極を作製した。

【0074】

このようにしてp側およびn側の電極を形成したウェーハについて、サファイア基板の裏面を研削および研磨してミラー状の面とした。その後、該ウェーハを350μm角の正方形のチップに切断し、電極が上になるように、リードフレーム上に載置し、金線でリードフレームへ結線して発光素子とした。上記のようにして作製した発光ダイオードのp側およびn側の電極間に順方向電流を流したところ、電流20mAにおける順方向電圧は3.0Vであった。また、p側の透光性電極を通して発光を観察したところ、発光波長は470nmであり、発光出力は15mWを示した。このような発光ダイオードの特性は、作製したウェーハのほぼ全面から作製された発光ダイオードについて、ばらつきなく得られた。

【産業上の利用可能性】

【0075】

本発明方法により得られるIII族窒化物化合物半導体積層構造体は、良好な結晶性を持つIII族窒化物化合物半導体結晶からなる。従って、この積層構造体の上に、さらに機能を持たせたIII族窒化物化合物半導体結晶層を形成することにより、優れた特性を有する発光ダイオード、レーザダイオード、或いは電子デバイス等の半導体素子を作製することができる。

【図面の簡単な説明】

【0076】

【図1】本発明の実施例1に係わる半導体発光素子用のエピタキシャル層構造を有するエピタキシャルウェーハの断面を示す模式図である。

【図2】本発明の実施例1に係わる半導体発光素子の電極構造を示す平面図である。

【符号の説明】

【0077】

1 MgドープAl0.02Ga0.98N層

2 MgドープのAl0.1Ga0.9Nクラッド層

3 GaN障壁層

4 In0.2Ga0.8N井戸層

5 In0.1Ga0.9Nクラッド層

6 Siドープn型GaN層

7 アンドープGaN層(第二の層)

8 柱状結晶の集合体からなるAlN層(第一の層)

9 基板

10 n側電極

11 SiドープGaN層のn側電極を形成する部分

12 p電極ボンディングパッド

13 透光性p電極

20 多重量子井戸構造

【技術分野】

【0001】

本発明は、発光ダイオード(LED)、レーザダイオード(LD)および電子デバイス等の作製に用いられる結晶性の良いIII族窒化物化合物半導体(以下、III族窒化物化合物半導体はInGaAlNで表されるものとする)積層構造体の成膜方法に関する。特に、本発明は結晶性の良いIII族窒化物化合物半導体結晶をサファイア基板上にエピタキシャル成長させるために好適に用いることができるIII族窒化物化合物半導体積層構造体の成膜方法に関する。

【背景技術】

【0002】

III族窒化物化合物半導体は、可視光から紫外光領域に相当するエネルギーの直接遷移型のバンドギャップを持ち高効率な発光が可能であるため、LEDやLDとして製品化されている。また、電子デバイスとしても従来のIII−V族化合物半導体では得られない特性が得られるポテンシャルを持っている。

【0003】

一般的には、トリメチルガリウム(TMG)、トリメチルアルミニウム(TMA)およびアンモニア(NH3)を原料として、III族窒化物化合物半導体は有機金属化学気相成長(MOCVD)法によって製造されている。MOCVD法は、キャリアガスに原料の蒸気を含ませて基板表面に運搬し、加熱された基板との反応により原料が分解して結晶を成長させる方法である。

【0004】

III族窒化物化合物半導体の単結晶ウエーハはいまだ市販されておらず、III族窒化物化合物半導体は異なる材料の単結晶ウエーハ上に結晶を成長させる方法が一般的である。このような異種基板と、その上にエピタキシャル成長させるIII族窒化物化合物半導体結晶の間には大きな格子不整合が存在する。例えばサファイア(Al2O3)と窒化ガリウム(GaN)の間には16%、SiCと窒化ガリウムの間には6%の格子不整合が存在する。一般にこのような大きな格子不整合が存在する場合には、基板上に結晶を直接エピタキシャル成長させることが困難であり、成長させても結晶性の良好な結晶は得られない。そこで、有機金属化学気相成長(MOCVD)法によりサファイア単結晶基板やSiC単結晶基板の上にIII族窒化物化合物半導体結晶をエピタキシャル成長する場合、特許第3026087号公報(特許文献1)や特開平4−297023号公報(特許文献2)に示されているように、窒化アルミニウム(AlN)や窒化アルミニウムガリウム(AlGaN)で構成される低温バッファ層と呼ばれる層を基板の上にまず堆積し、その上に高温でIII族窒化物化合物半導体結晶をエピタキシャル成長させる方法が一般に行われてきた。

【0005】

バッファ層としてAlNなどの層を、MOCVD以外の方法で成膜し、それ以降の層をMOCVD法で成膜する技術に関しても、いくつか報告がある。例えば、特公平5−86646号公報(特許文献3)には高周波スパッタで成膜したバッファ層上に、MOCVD法で同じ組成の結晶を成長させる技術が記載されている。しかし、特許第3440873号公報(特許文献4)および特許第3700492号公報(特許文献5)のなかで、この特公平5−86646号公報(特許文献3)に記載されている技術だけでは安定して良好な結晶を得ることができない旨が記載されている。安定して良好な結晶を得るために、特許第3440873号公報(特許文献4)ではバッファ層成長後にアンモニアと水素からなる混合ガス中でアニールすることが、そして特許第3700492号公報(特許文献5)ではバッファ層を400℃以上の温度でDCスパッタにより成膜することが重要であるとされている。

【0006】

一方、III族窒化物化合物半導体結晶をスパッタによって製造する研究も行われている。例えば、特開昭60−39819号公報(特許文献6)では、高抵抗のGaNを積層することを目的として、サファイア基板上に直接スパッタによるGaNの成膜を実施している。用いている条件は、到達真空度5×10-7〜10-8Torr、チャンバ内流通ガスはArとN2、スパッタ時ガス圧3〜5×10-2Torr、RF電圧0.7〜0.9kV(パワーにして20〜40W)、基板とターゲットの距離20〜50mm、基板温度150〜450℃などである。しかし目的とする用途には、発光素子の下地層には言及されておらず、この膜の上に層を形成する記述はない。

【0007】

また、21世紀連合シンポジウム論文集、Vol 2nd、p295(2003)(非特許文献1)には、N2ガスを用いた高周波マグネトロンスパッタリングによってSi(100)およびAl2O3(0001)上にGaN膜を成膜したと記載されている。成膜の条件としては、全ガス圧力は2mTorr、投入電力は100Wとし、基板温度を室温から900℃まで変化させている。論文に掲げられた図によれば、用いた装置はターゲットと基板を対向させたものである。

【0008】

また、Vacuum、Vol66、P233(2002)(非特許文献2)では、カソードとターゲットを向かい合わせ、基板とターゲットの間にメッシュを入れた装置でGaNを成膜している。これによると、成膜条件はN2ガス中で圧力を0.67Paとし、基板温度は84〜600℃であり、投入電力は150W、基板とターゲット間の距離は80mmとされている。

【0009】

【特許文献1】特許第3026087号公報

【特許文献2】特開平4−297023号公報

【特許文献3】特公平5−86646号公報

【特許文献4】特許第3440873号公報

【特許文献5】特許第3700492号公報

【特許文献6】特開昭60−39819号公報

【非特許文献1】21世紀連合シンポジウム論文集、Vol 2nd、p295(2003)

【非特許文献2】Vacuum、Vol66、P233(2002)

【発明の開示】

【発明が解決しようとする課題】

【0010】

本発明の目的は、均一性の良い結晶膜を短時間で得ることができる技術である、スパッタ法をIII族窒化物化合物半導体層を作製する際に使用し、安定して良好な結晶性のIII族窒化物化合物半導体層を得ることである。

【課題を解決するための手段】

【0011】

本発明は、上記の課題を解決するために下記の発明を提供する。

(1)基板上に、III族窒化物化合物半導体からなる多層膜構造を成膜させる方法において、該多層膜構造は少なくとも基板側からバッファ層と下地層を含み、バッファ層と下地層をスパッタ法で積層し、かつ、バッファ層の膜厚が5nm〜500nmであることを特徴とするIII族窒化物化合物半導体積層構造体の成膜方法;

(2)バッファ層がAlを含んでいる上記(1)記載のIII族窒化物化合物半導体積層構造体の成膜方法;

(3)バッファ層がAlNである上記(2)記載のIII族窒化物化合物半導体積層構造体の成膜方法;

(4)バッファ層が柱状結晶の集合体である上記(2)もしくは(3)記載のIII族窒化物化合物半導体積層構造体の成膜方法;

(5)バッファ層が基板表面の少なくとも60%を覆っている上記(2)〜(4)のいずれか記載のIII族窒化物化合物半導体積層構造体の成膜方法;

(6)下地層がGaを含んでいる上記(1)記載のIII族窒化物化合物半導体積層構造体の成膜方法;

(7)下地層がGaNである上記(6)記載のIII族窒化物化合物半導体積層構造体の成膜方法;

(8)バッファ層がAlNであり、かつ、下地層がGaNである上記(1)〜(3)、(6)および(7)のいずれか記載のIII族窒化物化合物半導体積層構造体の成膜方法、

である。

【発明の効果】

【0012】

本発明のIII族窒化物化合物半導体積層構造体の成膜方法によれば、最も膜厚が厚く良好な均一性が必要な下地層を、量産性、均一性の良好なスパッタ法で形成することで、生産性の改善と特性の良好な素子の形成を実現できる。すなわち、本発明は、スパッタ法で特定の膜厚を有するバッファ層を成膜し、その上に同じくスパッタ法でGaを含む層を成膜する、III族窒化物化合物半導体積層構造体を成膜する技術を提供しうる。

【発明を実施するための最良の形態】

【0013】

本発明は、III族窒化物半導体積層構造を成膜するに当たり、バッファ層と下地層をスパッタ法で作製する際の、バッファ層の適正な膜厚を規定する。

【0014】

一般的にスパッタ法は単組成の結晶を成膜するのに適しており、均一性、生産性、安定性に優れている。また、ダストなどのチャンバ内のコンタミネーションも少ない。このため、スパッタによって良好な結晶性のGaN膜の成膜を行う技術が求められていた。本発明者は、鋭意研究を重ねた結果、スパッタ法によって結晶性の良好なIII族窒化物化合物半導体結晶を得るために、バッファ層の膜厚がIII族窒化物化合物半導体からなる下地層の結晶性を制御するために重要であることを見出した。

【0015】

本発明において、バッファ層の膜厚は5nm〜500nmであることが必要である。これより薄いと基板との格子定数の差から生じる歪を解消しきれない。一方、これより厚いとバッファ層の表面に凹凸を生じて、良好なバッファ層として機能しなくなる。更に望ましくは膜厚が、10nm〜300nmであり、特に望ましくは膜厚が、150Å〜1000Åである。

【0016】

バッファ層成膜時の基板温度は、室温〜1200℃であることが望ましい。それより低い温度では、基板面でのマイグレーションが抑えられて、結晶性の良いIII族窒化物化合物半導体結晶ができにくい。一方、これより高い温度ではIII族窒化物化合物半導体結晶が分解を引き起こす。

【0017】

さらに望ましくは室温〜800℃の温度であり、更に望ましくは300〜800℃である。

【0018】

一方、下地層の成膜温度としては、300℃〜1500℃が望ましく、更に望ましくは500℃〜1000℃である。

【0019】

バッファ層と下地層の成膜温度の差としては、100℃〜800℃が望ましく、更に望ましくは400℃〜700℃である。

<スパッタ成膜装置>

スパッタ法には、RFスパッタとDCスパッタがある。一般的に、本発明におけるように金属と窒素を反応させて成膜するリアクティブスパッタを用いた場合には、連続的に放電させるDCスパッタでは帯電が激しく、成膜レートがコントロールできない。このため、RFスパッタや、DCスパッタでもパルス的にバイアスを与えるパルスDCスパッタを用いることが望ましい。

【0020】

また、RFスパッタを用いた場合には、膜厚の均一性を向上させる方法として、マグネットの位置をターゲット内で移動させることが望ましい。具体的な運動の方法は装置により選択することができ、揺動させたり、回転運動させたりすることができる。

【0021】

スパッタによってIII族窒化物系化合物半導体結晶を成膜する場合には、結晶成長時に、より高エネルギーの反応種を基板に供給することが望ましい。このため、装置としては、基板がプラズマ中に位置するようにする。そこで、ターゲットと基板の位置が、対面していることが望ましい。また、基板とターゲットの距離が10mm〜100mmであることが望ましい。

【0022】

また、チャンバ内にはできるだけ不純物を残したくないので、成膜に使用する装置は、到達真空度が、1.0×10-3Pa以下であることが望ましい。

<バッファ層の材料>

バッファ層を構成する材料としては、一般式AlGaInNで表される、III族窒化物化合物半導体であればどのような材料をも用いることができる。更に、V族としてAsやPを含んでも構わない。しかし、中でも、Alを含んだ組成とすることが望ましい。また、特に、GaAlNとすることが望ましく、Alの組成は50%以上であることが好適である。更に、AlNは良好な結晶性を得ることができるので、更に好適である。

【0023】

バッファ層は、以下に記述されるような柱状結晶の集合体を成すことが望ましい。そのためには、スパッタ法を用いて低温で成膜することで、良好な柱状結晶とすることができて、その密度や結晶性や被覆率を制御することも容易である。

【0024】

本発明でいう柱状結晶とは隣接する結晶粒との間に結晶粒界を形成して隔てられており、自身は縦断面形状として、柱状になっている結晶をいう。柱状結晶からなるバッファ層を基板上に形成して成膜した場合に、その上に成膜したIII族窒化物化合物半導体は良好な結晶性を持つ結晶膜となる。

【0025】

バッファ層は、隙間なく基板上を覆っていることが望ましい。バッファ層が基板を覆っておらず、基板の表面が一部分でも露出していると、バッファ層上に成膜したIII族窒化物結晶層と基板上に直接成膜されたIII族窒化物結晶層で結晶の格子定数が異なるため、均一な結晶とならないおそれがある。結果として、ヒロックやピットを生じてしまう。

【0026】

このため、バッファ層は、基板表面の少なくとも60%を覆っている必要がある。更に望ましくは80%以上であり、90%以上を覆っていることが最も望ましい。

【0027】

バッファ層が基板を覆っている割合は、上記断面TEM写真から測定することができる。特に、バッファ層とIII族窒化物結晶層の材料が異なる場合には、電子線エネルギー分散スペクトル(EDS)などを用いて基板と層の界面を基板面と平行にスキャンすることで、バッファ層が形成されていない領域の比を見積もることもできる。また、バッファ層だけを成膜した試料を用意することで、原子間力顕微鏡(AFM)などの手法により基板の露出した面積を測定することも可能である。本発明では上記断面透過電子顕微鏡(TEM)写真から測定した。

【0028】

バッファ層は、柱状結晶の個々の結晶のグレインの幅を適正に制御することが好適である。具体的には、各柱状結晶の幅が、0.1nm〜100nmの間の値であることが望ましい。更に望ましくは、1nm〜70nmの間の値である。

【0029】

各柱状結晶の幅は、上記断面TEM写真により容易に測定することが可能である。即ち、各柱状結晶の境界の間隔が各柱状結晶の幅である。各柱状結晶の幅は精密に規定できるものではなく、ある程度の分布を持つ。従って、各柱状結晶の幅が上記範囲から外れる結晶が数%程度あったとしても、本発明の効果に影響を及ぼすものではない。90%以上が上記範囲に入っていることが好ましい。

<バッファ層の成膜条件>

スパッタを用いて成膜する場合、重要なパラメーターは、基板温度、窒素分圧、成膜レート、バイアス、パワーである。

【0030】

チャンバ内の雰囲気には、窒素を含むことが必然であることは言うまでもない。窒素は、プラズマ化されて分解し、結晶成長の原料となる。また、ターゲットを効率よくスパッタするために、重くて反応性の低い気体を混入させることも良く行われる。例えば、アルゴンなどである。窒素とアルゴンの流量に対する窒素流量の比は、窒素が20%〜98%であることが望ましい。これより小さい流量比ではスパッタ金属が金属のまま付着するし、これより大きい流量比ではアルゴンの量が少なく、スパッタ速度が低下する。特に望ましくは25%〜90%である。

【0031】

成膜速度は、0.001nm/秒〜0.5nm/秒とすることが望ましい。これより大きい速度では膜が結晶体とならずに非晶質となる。これより小さい成膜速度では、プロセスが無駄に長時間となり、工業的に利用することが難しい。

【0032】

結晶成長時のマイグレーションを活発にしたいので、基板側にかかるバイアス、およびターゲット側にかかるパワーは大きいほうが良い。例えば、成膜時の基板にかけるバイアスを1.5W以上とする、成膜時にターゲットに印加するパワーを0.01W/cm2〜5kW/cm2の間とする、などである。

<下地層の材料>

本発明者等の実験の結果では、下地層の材料としてはGaを含むIII族窒化物が望ましい。良好な結晶性となすために、マイグレーションによって転位をループ化させる必要があるが、転位のループ化を生じやすい材料とは、Gaを含む窒化物である。特に、AlGaNが望ましく、GaNも好適である。

【0033】

下地層は、必要に応じてドーパントをドープした構造とすることもできるし、ドープしない構造とすることもできる。導電性の基板を用いる場合には、下地層をドーピングして層構造を縦方向に電流が流れるようにすることで、チップの両面に電極をつけた構造とすることが望ましい。絶縁性の基板を用いる場合には、チップの同じ面に電極が形成されたチップ構造を採ることになるので、基板直上の層は結晶性の良好なドープしない結晶とすることが、望ましい。

【0034】

下地層は、上記バッファ層上に生じた結晶核を種として成長し、転位をループ化させながら平坦化してゆくことが望ましい。転位をループ化させながら成長させるためには、マイグレーションを活発にしてファセット成長に近づける必要がある。

【0035】

このため、下地層の成膜時の基板温度は、バッファ層より高いことが望ましい。バッファ層の成膜温度より高い温度とすることで、バッファ層に生じさせた転位(柱状結晶の界面)をループ化させることができる。バッファ層よりも低い温度で下地層を成膜すると、バッファ層と同等の結晶性の膜を成膜することになり、転位密度の低減が達成できない。

<下地層の成膜条件>

次に、下地層を成膜する際のパラメーターについて述べる。

【0036】

チャンバ内の雰囲気には、窒素を含むことが必然であることは言うまでもない。窒素は、プラズマ化されて分解し、結晶成長の原料となる。また、ターゲットを効率よくスパッタするために、重くて反応性の低い気体を混入させることも良く行われる。例えば、アルゴンなどである。窒素とアルゴンの流量に対する窒素流量の比は、窒素が20%〜100%であることが望ましい。これより小さい流量比ではスパッタ金属が金属のまま付着するおそれがあり、特に望ましくは50%〜100%である。

【0037】

成膜速度は、0.05nm/秒〜5nm/秒とすることが望ましい。これより大きい速度では膜が結晶体とならずに非晶質となる。これより小さい成膜速度では、プロセスが無駄に長時間となり、工業的に利用することが難しい。

【0038】

結晶成長時のマイグレーションを活発にしたいので、基板側にかかるバイアス、およびターゲット側にかかるパワーは大きいほうが良い。例えば、成膜時の基板にかけるバイアスを1.5W以上とする、成膜時にターゲットに印加するパワーを0.01W/cm2〜5kW/cm2の間とする、などである。

<その他の層>

上記下地層には、更に素子機能を持つ層を積層することが可能である。例えば、発光層であればコンタクト層、クラッド層、発光層、レーザ素子であればこれらのほかに光閉じ込め層などを形成できる。また、電子デバイスであれば、電子走行層や閉じ込め層などを形成できる。

【0039】

これらの層は、スパッタ法に限らず、一般に知られたどのような方法を用いても作製することが可能である。例えば、MOCVD法やMBE法を用いることが可能である。

<基板>

本発明に用いることができる基板としては、一般にIII族窒化物化合物半導体結晶を成膜できる基板であれば、どのような材料も用いることが可能である。例えば、サファイア、SiC、シリコン、酸化亜鉛、酸化マグネシウム、酸化マンガン、酸化ジルコニウム、酸化マンガン亜鉛鉄、酸化マグネシウムアルミニウム、ホウ化ジルコニウム、酸化ガリウム、酸化インジウム、酸化リチウムガリウム、酸化リチウムアルミニウム、酸化ネオジウムガリウム、酸化ランタンストロンチウムアルミニウムタンタル、酸化ストロンチウムチタン、酸化チタン、ハフニウム、タングステンおよびモリブデンなどである。中でも、高温でアンモニアに接触することで化学的な変性を引き起こすことが知られている酸化物基板や金属基板などに対して、アンモニアを使用しないスパッタ法は有効な成膜方法として利用できる。

【0040】

また、一般的にスパッタ法は基板の温度を低く抑えることが可能なので、高温で分解してしまう性質を持つ基板上にも、基板にダメージを与えることなく成膜が可能である。

【0041】

基板は、湿式の前処理を行うことが望ましい。例えばシリコン基板に対しては、よく知られたRCA洗浄方法などを行い、表面を水素終端させておくことで安定したプロセスとなる。

【0042】

一方、反応器の中に導入後に、逆スパッタなどの方法を用いて前処理を行うこともできる。具体的には、ArやN2のプラズマ中にさらす事によって表面を整えることができる。例えば、ArガスやN2ガスなどのプラズマを基板表面に作用させることで、表面に付着した有機物や酸化物を除去することが可能である。この場合は基板とチャンバ間に電圧をかけることにより、プラズマ粒子が効率的に基板に作用する。

<用途に関して>

本発明方法で製造した素子をパッケージしてランプとして使用することが可能である。また蛍光体と組み合わせることにより、発光色を変える技術が知られており、これをなんら問題なく利用することが可能である。例えば、蛍光体を適正に選定することにより発光素子より長波長の発光を得ることができるし、発光素子自身の発光波長と蛍光体によって変換された波長とを混ぜることによって、白色のパッケージとすることもできる。

【実施例】

【0043】

以下、本発明を実施例に基づいて具体的に説明する。しかし、本発明はこれらの実施例にのみ限定されるものではない。

【0044】

(実施例1)

本実施例では、c面サファイア基板上に、バッファ層としてRFスパッタ法を用いてAlNの柱状結晶の集合体を形成し、その上に第二の層として異なるチャンバ内で、RFスパッタ中でGaNの層を形成した。

【0045】

まず、片面のみをエピタキシャル成長に使用できる程度に鏡面研磨したc面サファイア基板を、特に湿式の前処理を行わずにスパッタ機の中へ導入した。使用するスパッタ機は、高周波式の電源を持ち、ターゲット内でマグネットを回転させることにより、磁場の掛かる位置を動かすことができる機構を持っている。

【0046】

はじめに、スパッタ装置内で基板を750℃まで加熱し、窒素ガスを15sccmの流量で導入した後、チャンバ内の圧力を0.08Paに保持して、基板側に50Wの高周波バイアスを印加し、窒素プラズマに晒すことで、基板表面を洗浄した。

【0047】

続いて、アルゴンおよび窒素ガスを導入した後、基板温度を500℃まで低下させた。0.95W/cm2のパワーを金属Alターゲット側に印加し、炉内の圧力を0.5Paに保ち、Arガスを15sccm、窒素ガスを5sccm流通させた条件(ガス全体に対する窒素の比は25%)で、サファイア基板上にAlNを成膜した。成長速度は0.12nm/sであった。

【0048】

ターゲット内のマグネットは、基板洗浄の際も成膜の際も、回転させておいた。

【0049】

500ÅのAlNを成膜後、プラズマを立てるのを止め、基板を取り出した。

【0050】

続いて、異なるスパッタチャンバ内に基板を搬送した。GaNの成膜に使用するスパッタ機は、高周波式の電源を持ち、四角形のGaターゲット内をマグネットがスイープすることで磁場の掛かる位置を動かすことができる機構を持っている。Gaターゲット内には冷媒を流通させるための配管を設置し、配管内を20℃に冷却した冷媒を流通させて、熱によるGaの融解を防いだ。

【0051】

続いて、アルゴンおよび窒素ガスを導入した後、基板温度を1000℃まで上昇させた。1.3W/cm2のパワーを金属Gaターゲット側に印加し、炉内の圧力を0.5Paに保ち、Arガスを5sccm、窒素ガスを15sccm流通させた条件(ガス全体に対する窒素の比は75%)で、サファイア基板上にGaNを成膜した。成長速度は、おおよそ1nm/sであった。6μmのGaNを成膜後、プラズマを立てるのを止めた。

【0052】

続いて同じ条件にて、1×1019cm-3の電子濃度を持つ2μmのSiドープGaN層を成膜した。

【0053】

各条件はアンドープ層と同じとし、そこへチャンバ内に設置したSiターゲットへイオン銃から放出したイオンを照射してSiを取り出し、Siをドープした。

【0054】

以上の工程により、サファイア基板上に柱状構造を持つAlNの第一の層を形成し、その上にアンドープで6μmの膜厚のGaN層と1×1019cm-3の電子濃度を持つ2μmのSiドープGaN層を形成した本発明のIII族窒化物化合物半導体積層構造体を作製した。取り出した基板は無色透明のミラー状を呈した。

【0055】

次に、上記の方法で成長を行ったアンドープGaN層のX線ロッキングカーブ(XRC)測定を行った。測定には、Cuβ線X線発生源を光源として用いて、対称面である(0002)面と非対称面である(10−10)面で行った。一般的に、III族窒化物化合物半導体の場合、(0002)面のXRCスペクトル半値幅は結晶の平坦性(モザイシティ)の指標となり、(10−10)面のXRCスペクトル半値幅は転位密度(ツイスト)の指標となる。この測定の結果、本発明の方法で作製したアンドープGaN層は、(0002)面の測定では半値幅80arcsec、(10−10)面では半値幅250arcsecを示した。

【0056】

以上の手順にて作製したSiドープGaN層上に、MOCVD法にて素子構造を形成し、最終的に図1に示す半導体発光素子用の層構造を有するエピタキシャルウェーハを作製した。つまりエピタキシャルウェーハは、c面を有するサファイア基板9上に、柱状の構造を持つAlN層8(バッファ層)を形成したのち、基板側から順に、6μmのアンドープGaN層7(下地層)、1×1019cm-3の電子濃度を持つ2μmのSiドープGaN層6、1×1018cm-3の電子濃度を持つ20nmのIn0.1Ga0.9Nクラッド層5、GaN障壁層に始まりGaN障壁層に終わる、層厚を16nmとする6層のGaN障壁層3と、層厚を3nmとする5層のノンドープのIn0.2Ga0.8N井戸層4とからなる多重量子井戸構造20、5nmのMgをドープしたAl0.1Ga0.9Nクラッド層2、膜厚200nmのMgドープAl0.02Ga0.98N層1、を積層した構造を有する。

【0057】

また、本実施例で作製した半導体発光素子の電極構造の平面図を図2に示す。図中、10はn側電極、11はn電極を形成するためのSiドープGaN層6の露出面、12はp電極ボンディングパッド、および13は透光性p電極である。

【0058】

スパッタにて作製したSiドープGaNウエーハは、MOCVDチャンバ内に入れる前に純水で洗浄し、乾燥させておいた。表面に残ったパーティクルの類を除去することが目的である。

【0059】

まず、SiドープGaN層が成長された基板を、MOCVD炉内へ導入した。

【0060】

その後、炉内を窒素で置換した状態で基板の温度を1000℃まで上昇させて、Si−GaN層の最表面に付着した汚れを昇華させて除去した。基板温度が830℃以上からは、アンモニアを炉内に流通させた。

【0061】

続いて、基板温度を740℃まで低下させたあと、アンモニアはそのまま流通させながら、シラン(SiH4)ガス、およびバブリングによって発生したトリメチルインジウム(TMI)およびトリメチルガリウム(TEG)の蒸気を炉内へ流通し、18nmの膜厚を成すSiドープIn0.1Ga0.9Nクラッド層5を形成した。その後、TMI、TEGおよびSiH4のバルブを切り替え、これらの原料の供給を停止した。

【0062】

次に、GaNよりなる障壁層3とIn0.2Ga0.8Nよりなる井戸層4で構成される多重量子井戸構造20を作製した。多重量子井戸構造の作製にあたっては、SiドープIn0.1Ga0.9Nクラッド層5上に、始めにGaN障壁層3を形成し、そのGaN障壁層上にIn0.2Ga0.8N井戸層4を形成した。この構造を5回繰り返し積層したのち、5番目のIn0.2Ga0.8N井戸層上に、6番目のGaN障壁層を形成し、多重量子井戸構造20の両側をGaN障壁層3から構成した構造とした。

【0063】

すなわち、SiドープIn0.1Ga0.9Nクラッド層5の成長終了後、基板温度や炉内の圧力、キャリアガスの流量や種類はそのままで、TEGのバルブを切り替えてTEGの炉内への供給を行い、GaN障壁層を成長した。これにより、16nmの膜厚を成すGaN障壁層3を形成した。

【0064】

GaN障壁層の成長終了後、基板温度や炉内の圧力、キャリアガスの流量や種類はそのままで、TEGとTMIのバルブを切り替えてTEGとTMIの炉内への供給を行い、In0.2Ga0.8N井戸層を成長した。これにより3nmの膜厚を成すIn0.2Ga0.8N井戸層4を形成した。

【0065】

In0.2Ga0.8N井戸層の成長終了後、再びGaN障壁層の成長を行った。このような手順を5回繰り返し、5層のGaN障壁層と5層のIn0.2Ga0.8N井戸層を作製した。更に、最後のIn0.2Ga0.8N井戸層上にGaN障壁層を形成した。

【0066】

このGaN障壁層で終了する多重量子井戸構造20上に、引き続きMOCVD法を用いて、MgをドープしたAl0.1Ga0.9Nクラッド層2を作製した。

【0067】

まず、炉内の圧力を200mbar、基板温度を1020℃、キャリアガスを窒素から水素に変更し、炉内の圧力と温度が安定するのを待って、TEGとTMAとビスシクロペンタジエニルマグネシウム(Cp2Mg)のバルブを切り替え、これらの原料の炉内への供給を開始し、MgドープのAl0.1Ga0.9Nクラッド層の成長を行った。これにより、5nmの膜厚を成すMgドープのAl0.1Ga0.9Nクラッド層2を形成した。

【0068】

このMgドープのAl0.1Ga0.9Nクラッド層上に、MgドープのAl0.02Ga0.98N層1を作製した。

【0069】

温度、圧力、キャリアガスをクラッド層の成長時と同じに保ったまま、TMAとTMGとCp2Mgの炉内への供給を開始し、成長を行った。Cp2Mgを流通させる量は事前に検討してあり、MgドープAl0.02Ga0.98Nコンタクト層の正孔濃度が8×1017cm-3となるように調整した。これにより、0.15μmの膜厚を成すMgドープAl0.02Ga0.98N層1が形成された。

【0070】

MgドープAl0.02Ga0.98N層の成長を終了した後、ヒータを停止して、基板の温度を室温まで20分をかけて降温した。成長終了直後、NH3の流量を1/50に減量してキャリアを水素から窒素に切り替えた。その後950℃にてNH3を完全に停止した。

【0071】

基板温度が室温まで降温したのを確認して、ウェーハを大気中に取り出した。

【0072】

以上のような手順により、半導体発光素子用のエピタキシャル層構造を有するエピタキシャルウェーハを作製した。ここでMgドープAl0.02Ga0.98N層1はp型キャリアを活性化するためのアニール処理を行わなくてもp型を示した。

【0073】

次いで、上記のサファイア基板上にエピタキシャル層構造が積層されたエピタキシャルウェーハを用いて半導体発光素子の一種である発光ダイオードを作製した。作製したウェーハについて、公知のフォトリソグラフィー技術によってMgドープAl0.02Ga0.98N層の表面上に、ITOからなる透明p電極13と、その上に順にチタン、アルミニウムおよび金を積層した構造を持つp電極ボンディングパッド12を形成し、p側電極とした。更にその後ウェーハにドライエッチングを行い、SiドープGaN層のn側電極を形成する部分11を露出させ、露出した部分にNi、Al、TiおよびAuの4層よりなるn側電極10を作製した。これらの作業により、ウエーハ上に図2に示すような形状を持つ電極を作製した。

【0074】

このようにしてp側およびn側の電極を形成したウェーハについて、サファイア基板の裏面を研削および研磨してミラー状の面とした。その後、該ウェーハを350μm角の正方形のチップに切断し、電極が上になるように、リードフレーム上に載置し、金線でリードフレームへ結線して発光素子とした。上記のようにして作製した発光ダイオードのp側およびn側の電極間に順方向電流を流したところ、電流20mAにおける順方向電圧は3.0Vであった。また、p側の透光性電極を通して発光を観察したところ、発光波長は470nmであり、発光出力は15mWを示した。このような発光ダイオードの特性は、作製したウェーハのほぼ全面から作製された発光ダイオードについて、ばらつきなく得られた。

【産業上の利用可能性】

【0075】

本発明方法により得られるIII族窒化物化合物半導体積層構造体は、良好な結晶性を持つIII族窒化物化合物半導体結晶からなる。従って、この積層構造体の上に、さらに機能を持たせたIII族窒化物化合物半導体結晶層を形成することにより、優れた特性を有する発光ダイオード、レーザダイオード、或いは電子デバイス等の半導体素子を作製することができる。

【図面の簡単な説明】

【0076】

【図1】本発明の実施例1に係わる半導体発光素子用のエピタキシャル層構造を有するエピタキシャルウェーハの断面を示す模式図である。

【図2】本発明の実施例1に係わる半導体発光素子の電極構造を示す平面図である。

【符号の説明】

【0077】

1 MgドープAl0.02Ga0.98N層

2 MgドープのAl0.1Ga0.9Nクラッド層

3 GaN障壁層

4 In0.2Ga0.8N井戸層

5 In0.1Ga0.9Nクラッド層

6 Siドープn型GaN層

7 アンドープGaN層(第二の層)

8 柱状結晶の集合体からなるAlN層(第一の層)

9 基板

10 n側電極

11 SiドープGaN層のn側電極を形成する部分

12 p電極ボンディングパッド

13 透光性p電極

20 多重量子井戸構造

【特許請求の範囲】

【請求項1】

基板上に、III族窒化物化合物半導体からなる多層膜構造を成膜させる方法において、該多層膜構造は少なくとも基板側からバッファ層と下地層を含み、

バッファ層と下地層をスパッタ法で積層し、かつ、

バッファ層の膜厚が5nm〜500nmであることを特徴とするIII族窒化物化合物半導体積層構造体の成膜方法。

【請求項2】

バッファ層がAlを含んでいる請求項1記載のIII族窒化物化合物半導体積層構造体の成膜方法。

【請求項3】

バッファ層がAlNである請求項2記載のIII族窒化物化合物半導体積層構造体の成膜方法。

【請求項4】

バッファ層が柱状結晶の集合体である請求項2もしくは3記載のIII族窒化物化合物半導体積層構造体の成膜方法。

【請求項5】

バッファ層が基板表面の少なくとも60%を覆っている請求項2〜4のいずれか記載のIII族窒化物化合物半導体積層構造体の成膜方法。

【請求項6】

下地層がGaを含んでいる請求項1記載のIII族窒化物化合物半導体積層構造体の成膜方法。

【請求項7】

下地層がGaNである請求項6記載のIII族窒化物化合物半導体積層構造体の成膜方法。

【請求項8】

バッファ層がAlNであり、かつ、下地層がGaNである請求項1〜3、6および7のいずれか記載のIII族窒化物化合物半導体積層構造体の成膜方法。

【請求項1】

基板上に、III族窒化物化合物半導体からなる多層膜構造を成膜させる方法において、該多層膜構造は少なくとも基板側からバッファ層と下地層を含み、

バッファ層と下地層をスパッタ法で積層し、かつ、

バッファ層の膜厚が5nm〜500nmであることを特徴とするIII族窒化物化合物半導体積層構造体の成膜方法。

【請求項2】

バッファ層がAlを含んでいる請求項1記載のIII族窒化物化合物半導体積層構造体の成膜方法。

【請求項3】

バッファ層がAlNである請求項2記載のIII族窒化物化合物半導体積層構造体の成膜方法。

【請求項4】

バッファ層が柱状結晶の集合体である請求項2もしくは3記載のIII族窒化物化合物半導体積層構造体の成膜方法。

【請求項5】

バッファ層が基板表面の少なくとも60%を覆っている請求項2〜4のいずれか記載のIII族窒化物化合物半導体積層構造体の成膜方法。

【請求項6】

下地層がGaを含んでいる請求項1記載のIII族窒化物化合物半導体積層構造体の成膜方法。

【請求項7】

下地層がGaNである請求項6記載のIII族窒化物化合物半導体積層構造体の成膜方法。

【請求項8】

バッファ層がAlNであり、かつ、下地層がGaNである請求項1〜3、6および7のいずれか記載のIII族窒化物化合物半導体積層構造体の成膜方法。

【図1】

【図2】

【図2】

【公開番号】特開2008−98245(P2008−98245A)

【公開日】平成20年4月24日(2008.4.24)

【国際特許分類】

【出願番号】特願2006−275485(P2006−275485)

【出願日】平成18年10月6日(2006.10.6)

【出願人】(000002004)昭和電工株式会社 (3,251)

【Fターム(参考)】

【公開日】平成20年4月24日(2008.4.24)

【国際特許分類】

【出願日】平成18年10月6日(2006.10.6)

【出願人】(000002004)昭和電工株式会社 (3,251)

【Fターム(参考)】

[ Back to top ]