III族窒化物半導体の製造方法、III族窒化物半導体発光素子の製造方法、及びIII族窒化物半導体発光素子、並びにランプ

【課題】スパッタ法によって基板上に積層するIII族窒化物半導体の結晶性を、成膜後にアニール等の熱処理を行なうことなく改善できるIII族窒化物半導体の製造方法、III族窒化物半導体発光素子の製造方法、及び、発光特性に優れたIII族窒化物半導体発光素子並びにランプを提供する。

【解決手段】チャンバ内に基板11及びターゲットを配置し、基板11上にMgがドープされたIII族窒化物半導体を反応性スパッタ法によって形成するスパッタ工程が備えられた製造方法であり、スパッタ工程は、Mgをドープして半導体薄膜を成膜する成膜工程と、該成膜工程で成膜された半導体薄膜に対して不活性ガスプラズマによる処理を行うプラズマ処理工程の各小工程を含み、成膜工程とプラズマ処理工程とを交互に繰り返して半導体薄膜を積層することにより、MgドープIII族窒化物半導体からなるp型半導体層16を形成する方法としている。

【解決手段】チャンバ内に基板11及びターゲットを配置し、基板11上にMgがドープされたIII族窒化物半導体を反応性スパッタ法によって形成するスパッタ工程が備えられた製造方法であり、スパッタ工程は、Mgをドープして半導体薄膜を成膜する成膜工程と、該成膜工程で成膜された半導体薄膜に対して不活性ガスプラズマによる処理を行うプラズマ処理工程の各小工程を含み、成膜工程とプラズマ処理工程とを交互に繰り返して半導体薄膜を積層することにより、MgドープIII族窒化物半導体からなるp型半導体層16を形成する方法としている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、発光ダイオード(LED)、レーザダイオード(LD)、電子デバイス等に、好適に用いられ、一般式AlaGabIncN(0≦a≦1、0≦b≦1、0≦c≦1、a+b+c=1)で表されるIII族窒化物半導体の製造方法に関し、特に、マグネシウム(Mg)が添加されてなるp型のIII族窒化物半導体層を形成するためのIII族窒化物半導体の製造方法、III族窒化物半導体発光素子の製造方法、及びIII族窒化物半導体発光素子、並びにランプに関する。

【背景技術】

【0002】

III族窒化物半導体は、可視光から紫外光領域の範囲に相当するエネルギーの直接遷移型のバンドギャップを有し、発光効率に優れていることから、発光ダイオード(LED)やレーザダイオード(LD)等の半導体発光素子として製品化され、各種用途で使用されている。また、電子デバイスに用いた場合でも、III族窒化物半導体は、従来のIII−V族化合物半導体を用いた場合に比べて優れた特性が得られるポテンシャルを有している。

【0003】

このようなIII族窒化物半導体は、一般的に、トリメチルガリウム、トリメチルアルミニウムおよびアンモニアを原料として、有機金属化学気相成長(MOCVD)法によって製造されている。MOCVD法は、キャリアガスに原料の蒸気を含ませて基板表面に運搬し、加熱された基板の表面で原料を分解させることにより、結晶を成長させる方法である。

【0004】

従来、III族窒化物半導体の単結晶ウェーハは市販されておらず、III族窒化物半導体としては、異なる材料の単結晶ウェーハ上に結晶を成長させて得る方法が一般的である。このような、異種基板と、その上にエピタキシャル成長させるIII族窒化物半導体結晶との間には、大きな格子不整合が存在する。例えば、サファイア(Al2O3)基板上に窒化ガリウム(GaN)を成長させた場合、両者の間には16%の格子不整合が存在し、SiC基板上に窒化ガリウムを成長させた場合には、両者の間に6%の格子不整合が存在する。一般に、上述のような大きな格子不整合が存在する場合、基板上に結晶を直接エピタキシャル成長させることが困難となり、また、成長させた場合であっても結晶性の良好な結晶が得られないという問題がある。

【0005】

そこで、有機金属化学気相成長(MOCVD)法により、サファイア単結晶基板もしくはSiC単結晶基板の上に、III族窒化物半導体結晶をエピタキシャル成長させる際、まず、基板上に窒化アルミニウム(AlN)や窒化アルミニウムガリウム(AlGaN)からなる低温バッファ層と呼ばれる層を積層し、その上に高温でIII族窒化物半導体結晶をエピタキシャル成長させる方法が提案されており、一般に行われている。

【0006】

また、バッファ層としてAlN等の層をMOCVD以外の方法で基板上に成膜し、その上に成膜される層をMOCVD法で成膜する方法に関し、例えば、高周波スパッタで成膜したバッファ層上に、MOCVD法で同じ組成の結晶を成長させる方法が提案されている(例えば、特許文献1)。

しかしながら、特許文献1に記載の方法では、安定して良好な結晶を得ることができないという問題がある。

【0007】

そこで、安定して良好な結晶を得るため、例えば、バッファ層成長後にアンモニアと水素からなる混合ガス中でアニールする方法(例えば、特許文献2)や、バッファ層を400℃以上の温度でDCスパッタにより成膜する方法(例えば、特許文献3)が提案されている。

【0008】

一方、III族窒化物半導体結晶をスパッタによって製造する研究も行われており、例えば、高抵抗のGaNを積層することを目的とし、サファイアからなる基板上に、スパッタ法によってGaNを直接成膜する方法が提案されている(例えば、特許文献4)。

【0009】

また、半導体層上に電極を形成する際に、半導体層に対する前処理としてArガスを用いて逆スパッタを行なう方法がある(例えば、特許文献5)。特許文献5に記載の方法によれば、III族窒化物化合物半導体層の表面に逆スパッタを施すことにより、半導体層と電極との間の電気的接触特性を改善できるというものである。

【0010】

上述のようなスパッタ法を用いて、アクセプター不純物としてMgをドーピングしたGaNを基板上に成膜する際、チャンバ内の雰囲気ガスに水素(H2)を流通させたほうが、結晶性の良好なGaNを成膜することができる。しかしながら、水素ガスを構成する水素原子(H)はMgと結合し易いため、ドーパント(Mg)のキャリア濃度の低下を招くという問題がある。

【0011】

また、GaN結晶膜をMOCVD法で成膜する場合には、一般にN(窒素)源としてアンモニアガス(NH3)を用いるため、この場合にも結晶膜中に水素が混入する。そこで、不活性化ガス中において、600℃以上等の温度でアニール処理を行う活性化アニール法と呼ばれる方法により、水素をGaN結晶中から排出させる方法が採用されている。しかしながら、LED等のIII族窒化物半導体発光素子の構造においては、アニールを行なった場合、アニール熱によってInGaN結晶からなる発光層に損傷が発生するという問題がある。また、通常、GaN結晶膜にアニールを施した場合でも、ドープされたMgの内の1/10〜1/5程度は活性化されず、アニール効果が得られにくいという問題があった。

【特許文献1】特公平5−86646号公報

【特許文献2】特許第3440873号公報

【特許文献3】特許第3700492号公報

【特許文献4】特開昭60−039819号公報

【特許文献5】特開平8−264478号公報

【発明の開示】

【発明が解決しようとする課題】

【0012】

本発明は上記問題に鑑みてなされたものであり、スパッタ法によって基板上に積層するIII族窒化物半導体の結晶性を、成膜後にアニール等の熱処理を行なうことなく改善することができ、ドーパントとしてMgを添加して充分に高いキャリア濃度を有するp型のIII族窒化物半導体を積層することが可能なIII族窒化物半導体の製造方法、III族窒化物半導体発光素子の製造方法、及び、発光特性に優れたIII族窒化物半導体発光素子並びにランプを提供することを目的とする。

【課題を解決するための手段】

【0013】

本発明者等が鋭意検討したところ、上述のようなGaN結晶膜への水素の混入に関し、スパッタ法によってMgドープGaN結晶膜を成膜した後、ArガスプラズマによってGaN結晶膜を逆スパッタ(プラズマ処理)することにより、結晶膜中の水素が外部へ離脱することが明らかとなった。但し、このような逆スパッタによる水素の離脱効果は、膜の表面から100Å(0.01μm)程度の範囲までしか得られず、最大で1.0μm近い膜厚を有するMgドープGaN結晶膜の場合、結晶膜表面付近は水素が離脱するものの、表面から離れた結晶膜中の水素は排出することが困難であった。このため、成膜後のMgドープGaN結晶膜に対して逆スパッタを施したとしても、GaN結晶膜中のMgドープ濃度低下が避けられず、GaN結晶の不活性化を招く虞があった。

【0014】

このような問題に対し、本発明者等は、MgドープGaN結晶膜(p型半導体層)を積層する際、所定範囲の膜厚でGaNからなる半導体薄膜を成膜する工程と、この半導体薄膜に不活性ガスプラズマによる処理を行う工程とを交互に繰り返して半導体薄膜を積層することにより、アニール処理等を行うことなく効果的に水素を排出しながら、充分に高いキャリア濃度を有するp型のIII族窒化物半導体の成膜が可能となることを見出し、本発明を完成した。

即ち、本発明は以下に関する。

【0015】

[1] チャンバ内に基板及びターゲットを配置し、前記基板上にMgがドープされたIII族窒化物半導体を反応性スパッタ法によって形成するスパッタ工程が備えられたIII族窒化物半導体の製造方法であって、前記スパッタ工程は、Mgをドープして半導体薄膜を成膜する成膜工程と、該成膜工程で成膜された半導体薄膜に対して不活性ガスプラズマによる処理を行うプラズマ処理工程の各小工程を含み、前記成膜工程と前記プラズマ処理工程とを交互に繰り返して前記半導体薄膜を積層することにより、III族窒化物半導体を形成することを特徴とするIII族窒化物半導体の製造方法。

[2] 前記スパッタ工程は、前記成膜工程において、Mgがドープされた前記半導体薄膜を1〜100nmの範囲の膜厚で成膜し、この膜厚で行なう成膜工程と前記プラズマ処理工程とを交互に繰り返して前記半導体薄膜を積層することにより、III族窒化物半導体を形成することを特徴とする[1]に記載のIII族窒化物半導体の製造方法。

[3] 前記成膜工程は、前記チャンバ内に、水素含有ガス及び/又は窒素含有ガスを流通させて行なうことを特徴とする[1]又は[2]に記載のIII族窒化物半導体の製造方法。

[4] 前記窒素含有ガスがアンモニアガスであることを特徴とする[3]に記載のIII族窒化物半導体の製造方法。

[5] 前記成膜工程は、前記基板の温度を300℃〜1200℃の範囲とすることを特徴とする[1]〜[4]の何れかに記載のIII族窒化物半導体の製造方法。

【0016】

[6] 前記プラズマ処理工程は、前記チャンバ内において不活性ガスプラズマを発生させる際のパワーが10〜5000Wの範囲であることを特徴とする[1]〜[5]の何れかに記載のIII族窒化物半導体の製造方法。

[7] 前記プラズマ処理工程は、前記不活性ガスプラズマによる処理時間が1〜600秒の範囲であることを特徴とする[1]〜[6]の何れかに記載のIII族窒化物半導体の製造方法。

[8] 前記プラズマ処理工程は、前記チャンバ内に流通させる不活性ガスとして、He、Ne、Ar、Kr及びXeの内の何れか1種以上を用いることを特徴とする[1]〜[7]の何れかに記載のIII族窒化物半導体の製造方法。

[9] 前記プラズマ処理工程は、前記基板の温度を室温〜800℃の範囲とすることを特徴とする[1]〜[8]の何れかに記載のIII族窒化物半導体の製造方法。

[10] 前記プラズマ処理工程は、前記チャンバ内の圧力を1×10−5〜10Paの範囲として行なうことを特徴とする[1]〜[9]の何れかに記載のIII族窒化物半導体の製造方法。

【0017】

[11] 前記スパッタ工程は、前記成膜工程と前記プラズマ処理工程との交互の繰り返し回数を1〜1000回の範囲として前記半導体薄膜を積層することを特徴とする[1]〜[10]の何れかに記載のIII族窒化物半導体の製造方法。

[12] 前記スパッタ工程は、交互に繰り返して行う前記成膜工程と前記プラズマ処理工程との工程間に、1〜300秒の範囲の間隔を設けることを特徴とする[1]〜[11]の何れかに記載のIII族窒化物半導体の製造方法。

[13] 前記スパッタ工程は、交互に繰り返して行う前記成膜工程と前記プラズマ処理工程との工程間に、前記成膜工程又は前記プラズマ処理工程の少なくとも何れかの処理条件を変更する調整工程が備えられていることを特徴とする[1]〜[12]の何れかに記載のIII族窒化物半導体の製造方法。

[14] 前記調整工程は、前記成膜工程における処理時間又は基板の温度、或いは前記プラズマ処理工程におけるパワー、処理時間、基板の温度又はチャンバ内の圧力の内、何れか1以上の処理条件を変更することを特徴とする[13]に記載のIII族窒化物半導体の製造方法。

[15] 少なくとも前記スパッタ工程の前に、前記基板上にIII族窒化物半導体からなる下地層を形成する工程が備えられていることを特徴とする[1]〜[14]の何れかに記載のIII族窒化物半導体の製造方法。

【0018】

[16] III族窒化物半導体から各々なるn型半導体層、発光層及びp型半導体層が順に積層された半導体層を備え、前記p型半導体層の少なくとも一部がMgの添加されたIII族窒化物半導体からなるIII族窒化物半導体発光素子の製造方法であって、前記p型半導体層の少なくとも一部を、[1]〜[15]の何れかに記載のIII族窒化物半導体の製造方法によって形成することを特徴とするIII族窒化物半導体発光素子の製造方法。

【0019】

[17]III族窒化物半導体から各々なるn型半導体層、発光層及びp型半導体層が順に積層された半導体層を備え、前記p型半導体層の少なくとも一部がMgの添加されたIII族窒化物半導体からなるIII族窒化物半導体発光素子であって、前記p型半導体層の少なくとも一部が、[1]〜[15]の何れかに記載のIII族窒化物半導体の製造方法によって形成されてなることを特徴とするIII族窒化物半導体発光素子。

[18] 前記p型半導体層の膜厚が0.05〜1μmの範囲とされていることを特徴とする[17]に記載のIII族窒化物半導体発光素子。

[19] 前記p型半導体層のMgドープ濃度が1×1019〜5×1020個/cm3の範囲とされていることを特徴とする[17]又は[18]に記載のIII族窒化物半導体発光素子。

[20] 前記p型半導体層の水素濃度が1×1016個/cm3以下とされていることを特徴とする[17]〜[19]の何れかに記載のIII族窒化物半導体発光素子。

[21] 上記[17]〜[20]の何れかに記載のIII族窒化物半導体発光素子が用いられてなるランプ。

【発明の効果】

【0020】

本発明のIII族窒化物半導体の製造方法によれば、MgがドープされたIII族窒化物半導体をスパッタ法によって成膜する際、Mgをドープして半導体薄膜を成膜する成膜工程と、該成膜工程で成膜された半導体薄膜に対して不活性ガスプラズマによる処理を行うプラズマ処理工程とを交互に繰り返して半導体薄膜を積層する方法としたので、Mgがドープされた半導体層から効果的に水素を排出させることができ、ドーパントのMgが活性化されたIII族窒化物半導体を成長させることが出来る。また、半導体層中のMgが活性化されるので、Mgのドープ量を減らすことが可能となり、この場合には、より結晶性の良好なIII族窒化物半導体が得られる。これにより、水素を排出させるためのアニール工程等の設備を必要とせず、量産性並びに再現性に優れるスパッタ法を用いて、発光特性に優れたIII族窒化物半導体発光素子を製造することが可能となる。

【0021】

また、成膜工程において、チャンバ内に水素含有ガス及び窒素含有ガスを流通させて結晶性の高いMgドープ半導体薄膜を成膜し、その後のプラズマ処理工程において、Mgドープ半導体薄膜に対して不活性ガスによるプラズマ処理を行った場合には、成膜工程を水素含有ガス雰囲気で行なうことによる優れた結晶性と、プラズマ処理工程の水素脱離効果によるMgの活性化効果の両方を得ることが可能となる。

【0022】

また、本発明のIII族窒化物半導体発光素子の製造方法によれば、p型半導体層の少なくとも一部が、上記製造方法により、MgがドープされたIII族窒化物半導体から形成する方法とされているので、結晶性の良好なIII族窒化物半導体からなるp型半導体層を備え、優れた発光特性を有するIII族窒化物半導体発光素子が得られる。

【発明を実施するための最良の形態】

【0023】

以下に、本発明に係るIII族窒化物半導体の製造方法、III族窒化物半導体発光素子の製造方法、及びIII族窒化物半導体発光素子、並びにランプの一実施形態について、図1〜6を適宜参照しながら説明する。

【0024】

[III族窒化物半導体の製造方法]

本実施形態のIII族窒化物半導体の製造方法は、チャンバ41(図5を参照)内に基板11(図1〜3を参照)及びターゲット47(図5を参照)を配置し、基板11上にMgがドープされたIII族窒化物半導体(図1に示すp型半導体層16)を反応性スパッタ法によって形成するスパッタ工程が備えられ、該スパッタ工程は、Mgをドープして半導体薄膜(図6に示す符号Aを参照)を成膜する成膜工程と、該成膜工程で成膜された半導体薄膜に対して不活性ガスプラズマによる処理を行うプラズマ処理工程の各小工程を含み、前記成膜工程と前記プラズマ処理工程とを交互に繰り返して半導体薄膜を積層することにより、III族窒化物半導体を形成する方法である。

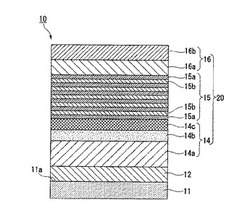

【0025】

<半導体の積層構造>

図1は、本発明に係るIII族窒化物半導体の製造方法の一例を説明するための図であり、基板上にIII族窒化物半導体が形成された積層半導体の一例を示す概略断面図である。図1に示す積層半導体10は、基板11上にIII族窒化物化合物からなるバッファ層12が積層され、該バッファ層12上に、n型半導体層14、発光層15、及びp型半導体層16が順次積層されてなる半導体層20が形成されている。

本実施形態のp型半導体層16は、MgがドープされたIII族窒化物半導体からなり、詳細を後述する本発明のIII族窒化物半導体の製造方法によって形成されるものである。

以下、本実施形態のIII族窒化物半導体の積層構造について詳述する。

【0026】

『基板』

本実施形態において、基板11に用いることができる材料としては、III族窒化物半導体結晶が表面にエピタキシャル成長される基板材料であれば、特に限定されず、各種材料を選択して用いることができる。例えば、サファイア、SiC、シリコン、酸化亜鉛、酸化マグネシウム、酸化マンガン、酸化ジルコニウム、酸化マンガン亜鉛鉄、酸化マグネシウムアルミニウム、ホウ化ジルコニウム、酸化ガリウム、酸化インジウム、酸化リチウムガリウム、酸化リチウムアルミニウム、酸化ネオジウムガリウム、酸化ランタンストロンチウムアルミニウムタンタル、酸化ストロンチウムチタン、酸化チタン、ハフニウム、タングステン、モリブデン等が挙げられる。この中でも、サファイア、SiC等の六方晶構造を有する材料を基板に用いることが、結晶性の良好なIII族窒化物半導体を積層できる点で好ましい。

また、基板の大きさとしては、通常は直径2インチ程度のものが用いられるが、本発明のIII族窒化物半導体では、直径4〜6インチの基板を使用することも可能である。

【0027】

なお、アンモニアを使用せずにバッファ層を成膜するとともに、アンモニアを使用する方法で後述のn型半導体層を構成する下地層を成膜することにより、上記基板材料の内、高温でアンモニアに接触することで化学的な変性を引き起こすことが知られている酸化物基板や金属基板等を用いた場合には、本実施形態のバッファ層がコート層として作用するので、基板の化学的な変質を防ぐ点で効果的である。また、一般的に、スパッタ法は基板の温度を低く抑えることが可能なので、高温で分解してしまう性質を持つ材料からなる基板を用いた場合でも、基板11にダメージを与えることなく基板上への各層の成膜が可能である。

【0028】

『バッファ層』

本実施形態の積層半導体10は、基板11上に、金属原料とV族元素を含んだガスとがプラズマで活性化されて反応することにより、III族窒化物化合物からなるバッファ層12が成膜されている。本実施形態のような、プラズマ化した金属原料を用いた方法で成膜された膜は、配向が得られ易いという作用がある。

【0029】

このようなバッファ層をなすIII族窒化物化合物の結晶は、六方晶系の結晶構造を持ち、成膜条件をコントロールすることにより、単結晶膜とすることができる。また、III族窒化物化合物の結晶は、上記成膜条件をコントロールすることにより、六角柱を基本とした集合組織からなる柱状結晶とすることも可能である。なお、ここで説明する柱状結晶とは、隣接する結晶粒との間に結晶粒界を形成して隔てられており、それ自体は縦断面形状として柱状になっている結晶のことをいう。

【0030】

バッファ層12は、単結晶構造であることが、バッファ機能の面から好ましい。上述したように、III族窒化物化合物の結晶は六方晶系の結晶を有し、六角柱を基本とした組織を形成する。III族窒化物化合物の結晶は、成膜等の条件を制御することにより、面内方向にも成長した結晶を成膜することが可能となる。このような単結晶構造を有するバッファ層12を基板11上に成膜した場合、バッファ層12のバッファ機能が有効に作用するため、その上に成膜されるIII族窒化物半導体の層は、良好な配向性及び結晶性を持つ結晶膜となる。

【0031】

バッファ層12の膜厚は、20〜80nmの範囲とされていることが好ましい。バッファ層12の膜厚をこの範囲とすることにより、良好な配向性を有し、また、バッファ層12上にIII族窒化物半導体からなる各層を成膜する際に、コート層として有効に機能するバッファ層12が得られる。

バッファ層12の膜厚が20nm未満だと、上述したコート層としての機能が充分でなくなる虞がある。また、80nmを超える膜厚でバッファ層12を形成した場合、コート層としての機能には変化が無いのにも関わらず成膜処理時間が長くなり、生産性が低下する虞がある。

【0032】

バッファ層12は、Alを含有する組成とされていることが好ましく、一般式AlGaInNで表されるIII族窒化物半導体であれば、どのような材料でも用いることができる。さらに、V族として、AsやPが含有される構成としても良い。

また、バッファ層12を、Alを含んだ組成とした場合、中でも、GaAlNとすることが好ましく、この際、Alの組成が50%以上とされていることが好ましい。また、バッファ層12は、AlNからなる構成とすることがより好ましい。

【0033】

また、バッファ層12を構成する材料としては、III族窒化物半導体と同じ結晶構造を有するものであれば、どのような材料でも用いることができるが、格子の長さが後述の下地層を構成するIII族窒化物半導体に近いものが好ましく、特に周期表のIIIa族元素の窒化物が好適である。

【0034】

『半導体層』

図1に示すように、本実施形態の積層半導体10は、基板11上に、上述のようなバッファ層12を介して、III族窒化物系半導体からなり、n型半導体層14、発光層15及びp型半導体層16から構成される半導体層20が積層されてなる。また、図示例の積層半導体10は、n型半導体層14に備えられた下地層14aがバッファ層12上に積層されている。

【0035】

III族窒化物半導体としては、例えば、一般式AlXGaYInZN1−AMA(0≦X≦1、0≦Y≦1、0≦Z≦1で且つ、X+Y+Z=1。記号Mは窒素(N)とは別の第V族元素を表し、0≦A<1である。)で表わされる窒化ガリウム系化合物半導体が多数知られており、本発明においても、それら周知の窒化ガリウム系化合物半導体を含めて一般式AlXGaYInZN1−AMA(0≦X≦1、0≦Y≦1、0≦Z≦1で且つ、X+Y+Z=1。記号Mは窒素(N)とは別の第V族元素を表し、0≦A<1である。)で表わされる窒化ガリウム系化合物半導体を何ら制限なく用いることができる。

【0036】

窒化ガリウム系化合物半導体は、Al、GaおよびIn以外に他のIII族元素を含有することができ、必要に応じてGe、Si、Mg、Ca、Zn、Be、P及びAs等の元素を含有することもできる。さらに、意図的に添加した元素に限らず、成膜条件等に依存して必然的に含まれる不純物、並びに原料、反応管材質に含まれる微量不純物を含む場合もある。

【0037】

「n型半導体層」

n型半導体層14は、通常、前記バッファ層12上に積層され、下地層14a、n型コンタクト層14b及びn型クラッド層14cから構成される。なお、n型コンタクト層は、下地層、及び/又は、n型クラッド層を兼ねることが可能であるが、下地層が、n型コンタクト層、及び/又は、n型クラッド層を兼ねることも可能である。

【0038】

{下地層}

本実施形態の下地層14aはIII族窒化物半導体からなり、従来公知のMOCVD法によってバッファ層12上に積層して成膜される。

下地層14aの材料としては、必ずしも基板11上に成膜されたバッファ層12と同じである必要はなく、異なる材料を用いても構わないが、AlyGa1―yN層(0≦y≦1、好ましくは0≦y≦0.5、さらに好ましくは0≦y≦0.1)から構成されることが好ましい。

【0039】

基板上にIII族窒化物半導体からなる各層を成膜する場合、例えば、サファイアからなる基板の(0001)C面上に、スパッタ法でIII族窒化物半導体の単結晶を直接形成することは、基板とIII族窒化物半導体の格子定数の違いから困難である。そこで、本発明では、バッファ層12を形成した基板11上に、単結晶のIII族窒化物半導体からなる下地層14aを予め形成する。単結晶の下地層14aの上には、結晶性の良好なIII族窒化物半導体の単結晶層を容易にスパッタ法により形成することができるため、Mgをドープして導電性をp型に制御したIII族窒化物半導体(後述のp型半導体16)が得られやすくなる。

【0040】

下地層14aに用いる材料としては、Gaを含むIII族窒化物化合物、即ちGaN系化合物半導体が用いられ、特に、AlGaN、又はGaNを好適に用いることができる。

また、バッファ層12をAlNからなる柱状結晶の集合体として形成した場合には、下地層14aがバッファ層12の結晶性をそのまま引き継がないように、マイグレーションによって転位をループ化させる必要があるが、このような材料としても上記Gaを含むGaN系化合物半導体が挙げられ、特に、AlGaN、又はGaNが好適である。

【0041】

下地層14aの膜厚は、0.1〜8μmの範囲とすることが、結晶性の良好な下地層が得られる点で好ましく、0.1〜2μmの範囲とすることが、成膜に要する工程時間を短縮でき、生産性が向上する点でより好ましい。

【0042】

下地層14aは、必要に応じて、n型不純物が1×1017〜1×1019個/cm3の範囲内でドープされた構成としても良いが、アンドープ(<1×1017個/cm3)の構成とすることもでき、アンドープの方が良好な結晶性を維持できる点で好ましい。

基板11が導電性である場合には、下地層14aにドーパントをドープして導電性とすることにより、発光素子の上下に電極を形成することができる。一方、基板11に絶縁性の材料を用いる場合には、発光素子の同じ面に正極及び負極の各電極が設けられたチップ構造をとることになるので、下地層14aはドープしない結晶とした方が、結晶性が良好となるので好ましい。n型不純物としては、特に限定されないが、例えば、Si、GeおよびSn等が挙げられ、好ましくはSiおよびGeが挙げられる。

【0043】

{n型コンタクト層}

本実施形態のn型コンタクト層14bはIII族窒化物半導体からなり、スパッタ法によって下地層14a上に積層して成膜される。

n型コンタクト層14bとしては、下地層14aと同様にAlXGa1―XN層(0≦x≦1、好ましくは0≦x≦0.5、さらに好ましくは0≦x≦0.1)から構成されることが好ましい。また、n型不純物がドープされていることが好ましく、n型不純物を1×1017〜1×1019個/cm3、好ましくは1×1018〜1×1019個/cm3の濃度で含有すると、負極との良好なオーミック接触の維持、クラック発生の抑制、良好な結晶性の維持の点で好ましい。n型不純物としては、特に限定されないが、例えば、Si、GeおよびSn等が挙げられ、好ましくはSiおよびGeである。成長温度は下地層と同様である。また、上述したように、n型コンタクト層14bは、下地層を兼ねた構成とすることもできる。

【0044】

下地層14a及びn型コンタクト層14bを構成する窒化ガリウム系化合物半導体は同一組成であることが好ましく、これらの合計の膜厚を0.1〜20μm、好ましくは0.5〜15μm、さらに好ましくは1〜12μmの範囲に設定することが好ましい。膜厚がこの範囲であると、半導体の結晶性が良好に維持される。

【0045】

{n型クラッド層}

上述のn型コンタクト層14bと詳細を後述する発光層15との間には、n型クラッド層14cを設けることが好ましい。n型クラッド層14cを設けることにより、n型コンタクト層14bの最表面に生じた平坦性の悪化を改善することができる。n型クラッド層14cは、スパッタ法等を用いて、AlGaN、GaN、GaInN等により成膜することが可能である。また、これらの構造のヘテロ接合や複数回積層した超格子構造としてもよい。GaInNとする場合には、発光層15のGaInNのバンドギャップよりも大きくすることが望ましいことは言うまでもない。

【0046】

n型クラッド層14cの膜厚は、特に限定されないが、好ましくは5〜500nmの範囲であり、より好ましくは5〜100nmの範囲である。

また、n型クラッド層14cのn型ドープ濃度は1×1017〜1×1020個/cm3の範囲とされていることが好ましく、より好ましくは1×1018〜1×1019個/cm3の範囲である。ドープ濃度がこの範囲であると、良好な結晶性の維持および発光素子の動作電圧低減の点で好ましい。

【0047】

「p型半導体層」

p型半導体層16は、通常、p型クラッド層16a及びp型コンタクト層16bから構成され、反応性スパッタ法を用いて成膜されてなる。また、p型コンタクト層がp型クラッド層を兼ねる構成とすることもできる。

【0048】

本実施形態のp型半導体層16は、導電性をp型に制御するためのp型不純物が添加されてなる。p型不純物としては、特に限定されないが、Mgを用いることが好ましく、また、同様にZnを用いることも可能である。

また、p型半導体層16全体の膜厚としては、特に限定されないが、好ましくは0.05〜1μmの範囲である。

【0049】

{p型クラッド層}

p型クラッド層16aとしては、詳細を後述する発光層15のバンドギャップエネルギーより大きくなる組成であり、発光層15へのキャリアの閉じ込めができるものであれば特に限定されないが、好ましくは、AldGa1−dN(0<d≦0.4、好ましくは0.1≦d≦0.3)のものが挙げられる。p型クラッド層16aが、このようなAlGaNからなると、発光層15へのキャリアの閉じ込めの点で好ましい。

p型クラッド層16aの膜厚は、特に限定されないが、好ましくは1〜400nmであり、より好ましくは5〜100nmである。

【0050】

p型クラッド層16aにp型不純物を添加することによって得られるp型ドープ濃度は、1×1018〜5×1021個/cm3の範囲とされていることが好ましく、より好ましくは1×1019〜5×1020個/cm3である。p型ドープ濃度が上記範囲であると、結晶性を低下させることなく良好なp型結晶が得られる。

【0051】

{p型コンタクト層}

p型コンタクト層16bとしては、少なくともAleGa1−eN(0≦e<0.5、好ましくは0≦e≦0.2、より好ましくは0≦e≦0.1)を含んでなる窒化ガリウム系化合物半導体層である。Al組成が上記範囲であると、良好な結晶性の維持およびpオーミック電極(後述の透光性電極17を参照)との良好なオーミック接触の点で好ましい。

p型コンタクト層16bの膜厚は、特に限定されないが、10〜500nmが好ましく、より好ましくは50〜200nmである。膜厚がこの範囲であると、発光出力の点で好ましい。

【0052】

また、p型コンタクト層16bにp型不純物を添加することによって得られるp型ドープ濃度は、1×1018〜1×1021個/cm3の範囲とされていると、良好なオーミック接触の維持、クラック発生の防止、良好な結晶性の維持の点で好ましく、より好ましくは5×1019〜5×1020個/cm3の範囲である。

【0053】

「発光層」

発光層15は、n型半導体層14上に積層されるとともにp型半導体層16がその上に積層される層であり、従来公知のMOCVD法等を用いて成膜することができる。また、発光層15は、図1に示すように、窒化ガリウム系化合物半導体からなる障壁層15aと、インジウムを含有する窒化ガリウム系化合物半導体からなる井戸層15bとが交互に繰り返して積層されてなり、図示例では、n型半導体層14側及びp型半導体層16側に障壁層15aが配される順で積層して形成されている。

【0054】

障壁層15aとしては、例えば、インジウムを含有した窒化ガリウム系化合物半導体からなる井戸層15bよりもバンドギャップエネルギーが大きいAlcGa1−cN(0≦c<0.3)等の窒化ガリウム系化合物半導体を、好適に用いることができる。

また、井戸層15bには、インジウムを含有する窒化ガリウム系化合物半導体として、例えば、Ga1−sInsN(0<s<0.4)等の窒化ガリウムインジウムを用いることができる。

【0055】

また、発光層15全体の膜厚としては、特に限定されない。例えば、発光層15の膜厚は、1〜500nmの範囲であることが好ましく、100nm前後の膜厚であればより好ましい。膜厚が上記範囲であると、発光出力の向上に寄与する。

【0056】

<製造方法>

本実施形態のIII族窒化物半導体の製造方法は、上述したように、チャンバ41内に基板11及びターゲット47を配置し、基板11上にMgがドープされたIII族窒化物半導体(p型半導体層16)を反応性スパッタ法によって形成するスパッタ工程が備えられ、該スパッタ工程は、Mgをドープして半導体薄膜(図6に示す符号Aを参照)を成膜する成膜工程と、該成膜工程で成膜された半導体薄膜に対して不活性ガスプラズマによる処理を行うプラズマ処理工程の各小工程を含み、前記成膜工程と前記プラズマ処理工程とを交互に繰り返して半導体薄膜を積層することにより、III族窒化物半導体からなるp型半導体層16を形成する方法である。

【0057】

本実施形態の製造方法では、基板11上にIII族窒化物半導体結晶をエピタキシャル成長させ、図1に示すような積層半導体10を形成する際、基板11上にバッファ層12を成膜し、その上に半導体層20を形成する。本実施形態では、バッファ層12を、スパッタ法を用いて形成し、その上に、n型半導体層14の下地層14aをMOCVD法によって形成した後、n型コンタクト層14bをスパッタ法で形成し、その上のn型クラッド層14c及び発光層15の各層をMOCVD法で形成し、そして、p型半導体層16をスパッタ法で形成する方法としている。

【0058】

『バッファ層の形成』

基板11を反応器の中に導入した後、バッファ層12を形成する前に、スパッタ法等の方法を用いて前処理を行うことが望ましい。具体的には、基板11をArやN2のプラズマ中に曝す事によって表面を整えることができる。例えば、ArガスやN2ガスなどのプラズマを基板11表面に作用させることで、基板11表面に付着した有機物や酸化物を除去することができる。この場合、基板11とチャンバとの間に電圧を印加すれば、プラズマ粒子が効率的に基板11に作用する。このような前処理を基板11に施すことにより、基板11の表面11a全面にバッファ層12を成膜することができ、その上に成膜される膜の結晶性を高めることが可能となる。

また、バッファ層12を基板11上に成膜する際、基板11には湿式の前処理を行っても良い。例えば、シリコンからなる基板11に対しては、よく知られたRCA洗浄方法などを行い、表面を水素終端させておくことにより、成膜プロセスが安定する。

【0059】

基板11表面の前処理を行なった後、スパッタ装置内にアルゴン及び窒素ガスを導入し、基板11の温度を500℃程度にする。そして、基板11側に高周波バイアスを印加するとともに、金属AlからなるAlターゲット側にパワーを印加し、炉内の圧力を一定に保ちながら、基板11上にAlNからなるバッファ層12を成膜する。

【0060】

バッファ層12を基板11上に成膜する方法としては、スパッタ法の他、例えば、MOCVD法、パルスレーザーデポジション(PLD)法、パルス電子線堆積(PED)法等が挙げられ、適宜選択して用いることができるが、スパッタ法が最も簡便で量産にも適しているため、好適な方法である。なお、DCスパッタを用いる場合、ターゲット表面のチャージアップを招き、成膜速度が安定しない可能性があるので、パルスDCスパッタ法とするか、RFスパッタ法とすることが望ましい。

【0061】

『半導体層の形成』

バッファ層12上には、n型半導体層14、発光層15、p型半導体層16をこの順で積層することにより、半導体層20を形成する。本実施形態の製造方法では、上述したように、n型半導体層14の下地層14aをMOCVD法によって形成した後、n型コンタクト層14bをスパッタ法で形成し、その上のn型クラッド層14c及び発光層15の各層をMOCVD法で形成し、そして、p型半導体層16をスパッタ法で形成する。

【0062】

本実施形態において、半導体層20を形成する際の窒化ガリウム系化合物半導体の成長方法は特に限定されず、上述したスパッタ法の他、MOCVD(有機金属化学気相成長法)、HVPE(ハイドライド気相成長法)、MBE(分子線エピタキシー法)等、窒化物半導体を成長させることが知られている全ての方法を適用できる。これらの方法の内、MOCVD法では、キャリアガスとして水素(H2)または窒素(N2)、III族原料であるGa源としてトリメチルガリウム(TMG)またはトリエチルガリウム(TEG)、Al源としてトリメチルアルミニウム(TMA)またはトリエチルアルミニウム(TEA)、In源としてトリメチルインジウム(TMI)またはトリエチルインジウム(TEI)、V族原料であるN源としてアンモニア(NH3)、ヒドラジン(N2H4)などが用いられる。また、ドーパントとしては、n型にはSi原料としてモノシラン(SiH4)またはジシラン(Si2H6)を、Ge原料としてゲルマンガス(GeH4)や、テトラメチルゲルマニウム((CH3)4Ge)やテトラエチルゲルマニウム((C2H5)4Ge)等の有機ゲルマニウム化合物を利用できる。MBE法では、元素状のゲルマニウムもドーピング源として利用できる。p型にはMg原料としては、例えばビスシクロペンタジエニルマグネシウム(Cp2Mg)またはビスエチルシクロペンタジエニルマグネシウム(EtCp2Mg)を用いる。

【0063】

上述したような窒化ガリウム系化合物半導体は、Al、GaおよびIn以外に他のIII族元素を含有することができ、必要に応じてGe、Si、Mg、Ca、Zn、Be、P、及びAs等のドーパント元素を含有することができる。さらに、意図的に添加した元素に限らず、成膜条件等に依存して必然的に含まれる不純物、並びに原料、反応管材質に含まれる微量不純物を含む場合もある。

【0064】

「n型半導体層の形成」

本実施形態の半導体層20を形成する際、まず、n型半導体層14の下地層14aを、従来公知のMOCVD法により、バッファ層12上に積層して成膜する。次いで、下地層14a上に、n型コンタクト層14bをスパッタ法で成膜した後、n型クラッド層14cをMOCVD法によって成膜する。この際、下地層14a及びn型クラッド層14cの各層は、同じMOCVD炉を用いて成膜することができる。

【0065】

単結晶のIII族窒化物半導体からなる下地層14aを形成する方法としては、例えばMOCVD法により、上述のAlyGa1−yN(0≦y≦1)からなる低温バッファ層を基板11上に形成し、その上に、低温バッファ層を形成する温度より高温でMOCVD法により単結晶のGaN層を形成する方法がある。また、MOCVD法による低温バッファ層の代わりに、スパッタ法でAlyGa1−yN(0≦y≦1)からなる多結晶のバッファ層を形成し、その上に、MOCVD法によって単結晶のGaN層を形成しても良い。また、単結晶のGaN層を、スパッタ法を用いて成長させても良い。

【0066】

「発光層の形成」

n型クラッド層14c上には、発光層15を、従来公知のMOCVD法によって形成する。

本実施形態で形成する、図1に例示するような発光層15は、GaN障壁層に始まりGaN障壁層に終わる積層構造を有しており、GaNからなる6層の障壁層15aと、ノンドープのIn0.2Ga0.8Nからなる5層の井戸層15bとを交互に積層して形成する。

また、本実施形態の製造方法では、n型クラッド層14cの成膜に用いるMOCVD炉と同じものを使用することにより、従来公知のMOCVD法で発光層15を成膜することができる。

【0067】

「p型半導体層の形成」

発光層15上、つまり、発光層15の最上層となる障壁層15a上には、p型クラッド層16a及びp型コンタクト層16bからなるp型半導体層16を、スパッタ法を用いて形成する。

本実施形態では、まず、MgをドープしたAl0.1Ga0.9Nからなるp型クラッド層16aを発光層15(最上層の障壁層15a)上に形成し、さらにその上に、MgをドープしたAl0.02Ga0.98Nからなるp型コンタクト層16bを形成する。この際、p型クラッド層16a及びp型コンタクト層16bの積層には、同じスパッタ装置を用いることができる。

【0068】

{スパッタ工程}

以下、本実施形態の製造方法に備えられたスパッタ工程について、図5に例示したようなスパッタ装置40、及び図6に示すプラズマ処理模式図を適宜参照しながら詳述する。

本実施形態のスパッタ工程は、上記各条件により、図1(図3も参照)に示すようなIII族窒化物半導体からなる半導体層20の内、p型半導体層16の少なくとも一部を、反応性スパッタ法を用いて、MgがドープされたIII族窒化物半導体から形成する工程であり、Mgをドープして半導体薄膜を成膜する成膜工程と、該成膜工程で成膜された半導体薄膜に対して不活性ガスプラズマによる処理を行うプラズマ処理工程の各小工程を含み、前記成膜工程と前記プラズマ処理工程とを交互に繰り返して半導体薄膜を積層することにより、III族窒化物半導体からなるp型半導体層16を形成する方法である。

【0069】

(成膜工程)

本実施形態のスパッタ工程において小工程として備えられる成膜工程は、発光層15上に、スパッタ法により、MgがドープされたIII族窒化物半導体を成膜する工程である。本実施形態では、発光層15上、つまり、発光層15の最上層となる障壁層15a上に、p型クラッド層16a及びp型コンタクト層16bからなるp型半導体層16を従来公知のスパッタ法によって形成する。

本実施形態では、まず、MgをドープしたAl0.1Ga0.9Nからなるp型クラッド層16aを発光層15(最上層の障壁層15a)上に形成し、さらにその上に、MgをドープしたAl0.02Ga0.98Nからなるp型コンタクト層16bを形成する。

このような、スパッタ法を用いてIII族窒化物半導体からなる半導体層を形成する工程において、重要となる他のパラメータとしては、窒素原子含有ガスの分圧、成膜速度、基板温度、バイアス及びパワー等が挙げられる。

【0070】

本発明で用いられる窒素原料としては、一般に知られている窒素化合物を何ら問題なく用いることができるが、特にアンモニアと窒素は取り扱いも容易で、比較的安価で入手可能であることから好ましい。アンモニアは分解の効率も良く、高い成長速度での成膜が可能となるが、反応性や毒性が高く、除害設備やガス検知器が必要であり、また、反応装置に使用する部材の材質を化学的に安定性の高いものにする必要がある等、工夫を要する。

一方、窒素を原料として用いた場合、装置が簡便で済むものの、高い反応速度は得られない。しかしながら、窒素を電界や熱等によって分解してから装置に導入する方法では、アンモニアには劣るものの、利用可能な程度の成膜速度が得られることから、装置コストとの兼ね合いを考慮した場合、最も好適な窒素源である。

また、チャンバ41内のガス雰囲気中に水素含有ガスを流通させた場合には、半導体積層過程でのIII族窒化物半導体の表面における反応種のマイグレーションが生じやすくなり、結晶性の優れたAlGaNからなる膜を成膜することが可能となる。

【0071】

チャンバ41内のガス雰囲気中の水素ガスの割合は0.2〜50%の範囲とすることが好ましい。水素ガスの割合が0.2%未満だと、基板上において反応種のマイグレーションを活性化する作用が充分に得られず、結晶性の良好なIII族窒化物半導体を積層するのが困難になる。また、水素ガスの割合が50%を越えると、形成されたIII族窒化物半導体に取り込まれる水素が多くなり過ぎ、アクセプター不純物の活性化を阻害する要因となる虞がある。

【0072】

また、ターゲット47を効率よくスパッタするためには、さらに、アルゴン(Ar)等の重量が大きく反応性の低い不活性ガスを混入させた雰囲気とすることがより好ましい。このような場合、窒素ガス(N2)とアルゴン(Ar)の流量の比(N2/Ar)は、例えば0.25〜50の範囲とすることができる。(N2/Ar)が0.25未満だと、スパッタ原料が金属のまま付着する虞があり、(N2/Ar)が50超だと、アルゴンの量が少なすぎ、スパッタ速度が低下する。

【0073】

また、特に結晶性の良好なIII族窒化物半導体を積層するためには、チャンバ41内の雰囲気中の(N2/Ar)を0.25〜4の範囲とし、残部が不活性ガスを含有するガスとされていることが好ましい。これにより、III族原料が豊富な雰囲気中においてIII族窒化物半導体の成長を行うことができるので、より結晶性の良好なIII族窒化物半導体を成長させることが可能となる。

【0074】

上述したように、チャンバ41内のガス雰囲気中において、窒素原子含有ガス及び水素ガスを除く残部は、不活性ガスとすることが好ましい。このような不活性ガスは、ターゲットを効率よくスパッタすることを目的に用いるので、重量が大きく反応性の低いAr等を用いることが好ましい。また、ガス雰囲気中には、窒素原子含有ガス、水素ガス及び不活性ガスの働きを阻害しない範囲で、その他のガス成分を加えることも可能である。

【0075】

本実施形態の成膜工程における基板11の温度は、300℃〜1200℃の範囲とすることが好ましい。

本発明者等が鋭意実験したところ、一般に、結晶性の良好なIII族窒化物半導体からなる半導体層をスパッタ法で形成するためには、基板温度を300〜1200℃の範囲とすること好ましいことが明らかとなった。基板温度が300℃より低いと、基板面での反応種のマイグレーションが抑えられ、結晶性の良好なIII族窒化物半導体を形成するのが困難とある。また、基板温度が1200℃を超えると、形成されたIII族窒化物半導体が再分解を起こす虞がある。

【0076】

また、Mgをドープして導電性をp型に制御するためには、基板温度を600℃〜1050℃の範囲とすることがより好ましい。基板温度を600℃〜1050℃の範囲とすることで、点欠陥等の欠陥密度が少なく結晶性の良好なIII族窒化物半導体を成長させることができる。これにより、III族窒化物半導体にMgをドープして導電性をp型に制御することが可能になる。

【0077】

本実施形態のスパッタ法による成膜工程における、III族窒化物半導体からなる半導体薄膜の成膜速度は、0.01〜10nm/秒とすることが好ましい。成膜速度が10nm/秒を超えると、プラズマ処理によっても水素を排出できない虞があり、また、0.01nm/秒未満だとプロセスが無駄に長時間となり、工業生産に利用することが困難となる。

【0078】

また、成膜工程において成膜するMgがドープされた半導体薄膜の膜厚は、成膜工程による成膜処理1回あたりで1〜100nmの範囲の膜厚とすることが好ましい。そして、この膜厚で半導体薄膜を成膜する成膜工程と、詳細を後述するプラズマ処理工程とを交互に繰り返して半導体薄膜を積層することにより、最終的に所定の膜厚、例えば、最大で1000nm(1μm)程度の膜厚を有するIII族窒化物半導体(p型半導体層16)を成膜する。

本実施形態のスパッタ工程に備えられる、後述のプラズマ処理工程は、MgドープIII族窒化物半導体の結晶膜から水素を脱離させる作用を有するが、このような水素脱離効果が得られるのは結晶膜表面から10nm(0.01μm)程度の膜厚までであり、この膜厚よりもMgドープIII族窒化物半導体の膜厚が大幅に上回る場合には、本発明のドーパントMgの活性化及び結晶性向上の効果が得られ難くなる虞が有る。このため、本実施形態の成膜工程では、成膜処理1回あたりの膜厚を上記範囲として半導体薄膜を成膜し、プラズマ処理による水素離脱効果が最大限得られるような膜厚とすることにより、成膜後の結晶膜から水素を効率良く離脱させる方法としている。

【0079】

本実施形態の成膜工程において、結晶成長中の基板11表面における反応種のマイグレーションを活発にするためには、基板11側に印加されるバイアス、及びターゲット47側に印加されるパワーは大きいほうが好ましい。例えば、成膜時に基板11に印加するバイアスは1.5W/cm2以上が好ましく、また、成膜時にターゲット47に印加するパワーを1.5W/cm2〜5kW/cm2の範囲とすることが好ましい。

【0080】

本実施形態の成膜工程で成膜されるIII族窒化物半導体からなる半導体層の組成は、ターゲットに用いるIII族金属の組成を所望の値に調整することによりコントロールすることができる。例えば、GaNからなる層を形成する場合には、ターゲットにGa金属を用い、AlGaN層を形成する場合には、ターゲットにAlGa合金を用いれば良い。また、InGaNを形成する場合には、InGa合金を用いれば良い。III族窒化物半導体の組成は、ターゲット47のIII族金属の組成に応じて変化するので、ターゲット47の組成を実験的に求めることで、所望の組成のIII族窒化物半導体からなる半導体層を形成することが可能となる。

【0081】

あるいは、例えば、AlGaN層を積層する場合、ターゲットとしてGaメタルとAlメタルの両方を併置してもよい。この場合には、GaメタルターゲットとAlメタルターゲットの表面積の比を変化させることにより、積層されるAlGaN層の組成を制御することが可能となる。同様に、InGaN層を積層する場合には、GaメタルターゲットとInメタルターゲットの両方を併置しても良い。

【0082】

また、III族窒化物半導体へのMg(p型不純物)のドーピングは、III族金属とアクセプター不純物とが混合されてなる混合ターゲットを用いて行なっても良い。例えば、スパッタ法を用いてMgをドーピングしたGaNを形成する場合には、Ga金属とMgとを含有した混合ターゲットを使用する。この場合、固体のGa金属にMgが固溶した状態とし、Mgが固溶したGaメタルをターゲットに使用することにより、MgをドープしたGaNを形成することができる。また、GaメタルとMgの小片を別々に併置してターゲットに用いることも可能である。この際、ターゲットとなるGaとMgの割合を実験的に求めることにより、所望の不純物濃度のGaNを形成することができる。例えば、固体のGaにMgを固溶させてターゲットとした場合、Gaの重量に対するMgの重量の割合を1(Ga):0.05〜0.0005(Mg)の範囲とすることで、1×1018cm−3〜1×1016cm−3のキャリア濃度を有する、p型のGaN単結晶層(p型半導体層16)を成膜させることが出来る。

【0083】

なお、III族窒化物半導体へのMgのドーピング方法は、上記方法には限定されず、その他の方法を用いることも可能である。

また、上述したように、p型不純物としては、Mgのみならず、例えば亜鉛(Zn)等も同様に用いることができる。

【0084】

(プラズマ処理工程)

本実施形態のスパッタ工程に備えられるプラズマ処理工程は、上述したような成膜工程で発光層15上に成膜されたMgドープ半導体薄膜に対し、不活性ガスプラズマによる処理を行う小工程である。本実施形態のプラズマ処理工程を行なうことにより、成膜されたMgドープ半導体薄膜から効果的に水素を脱離させることができ、1×1016cm−3以下の水素濃度とすることが好ましい。

【0085】

Mgドープ半導体薄膜にプラズマ処理を施すための不活性ガスとしては、一種類のみの成分からなるガスで構成しても良いし、また、数種類の成分のガスを混合した構成のものを用いても良い。このようなプラズマ処理に用いる不活性ガスとして、例えば、He、Ne、Ar、Kr及びXeの内の何れか1種以上を用いることができる。

また、このような不活性ガスで行なうプラズマ処理は、逆スパッタ法で行うことが好適である。本実施形態のプラズマ処理工程では、基板11とチャンバとの間に電圧を印加することにより、プラズマ粒子が効率的にMgドープ半導体薄膜に作用する。

【0086】

また、本実施形態のプラズマ処理工程は、上記不活性ガスの他、さらに窒素のような、活性なプラズマ種を発生するガスを含むプラズマ中で行なうことができる。この場合には、ガス中の窒素含有量を50%以下に抑えることが、膜の変質等を防止する点で好ましい。

【0087】

本実施形態のプラズマ処理工程は、チャンバ41内で不活性ガスプラズマを発生させる際のパワーを10〜5000Wの範囲とすることが好ましい。パワー値がこの範囲であれば、Mgドープ半導体薄膜から効率的に水素を脱離させることができる。

また、本実施形態では、プラズマ処理に用いるプラズマをRF放電によって発生させることが好ましい。プラズマをRF放電によって発生させることにより、Mgドープ半導体薄膜に対して効率良くプラズマ処理を施すことができる。

【0088】

本実施形態のプラズマ処理工程は、チャンバ41内の圧力が1×10−5〜10Paの範囲であることが好ましく、0.01〜1Paの範囲であることが更に好ましい。チャンバ41内の圧力が高すぎると、プラズマ粒子の持つエネルギーが低下し、上述したような、Mgドープ半導体薄膜に対するプラズマ処理効果が低下する。また、チャンバ41内の圧力が低すぎると、プラズマ粒子の持つエネルギーが高すぎ、Mgドープ半導体薄膜に対してダメージを与えてしまうことがある。

【0089】

プラズマ処理工程の処理時間としては、1秒〜600秒(10分)の範囲であることが好ましい。処理時間が上記範囲よりも短いと、プラズマ処理による効果が得られないことは言うまでもないが、上記範囲より長い場合も特段に特性が良くなるということはなく、かえって稼働率を低下させる虞がある。

【0090】

プラズマ処理工程を行う際の温度、つまり、基板11の温度としては、室温〜800℃の範囲であることが好ましい。プラズマ処理工程における処理温度が低すぎると、プラズマ処理による水素の離脱効果が充分に得られず、また、処理温度が高すぎると、Mgドープ半導体薄膜の表面や基板にダメージを残すことがある。また、プラズマ処理工程における処理温度は、さらに好ましくは、300℃〜800℃の範囲である。

【0091】

本実施形態のプラズマ処理工程において用いるチャンバとしては、上述の成膜工程で使用するスパッタ装置40を用い、チャンバ41内の雰囲気ガスを入れ替えて使用しても良いし、あるいは、別のチャンバを用いても良い。成膜工程及びプラズマ処理工程で用いる装置を共通のスパッタ装置とすれば、製造設備をコストダウンすることができる点で好適であり、また、成膜工程とプラズマ処理工程とを交互に繰り返して行なった場合でも工程時間のロスを低減することができ、稼働率が向上する。

【0092】

本実施形態の製造方法では、上述のプラズマ処理工程を備えることにより、Mgドープ半導体薄膜(III族窒化物半導体)から、不活性ガスプラズマ処理によって効果的に水素を脱離させることが可能となる。

【0093】

図6の模式図に示すように、成膜工程によって成膜されたMgドープの半導体薄膜Aは、チャンバ内における雰囲気ガス中の水素が含まれた状態で成膜されている(図6の(a)成膜工程を参照)。そして、この半導体薄膜Aに対して不活性ガスプラズマ処理を施すことにより、半導体薄膜Aから水素が脱離し、Mgドープの半導体薄膜Bとされる(図6の(b)プラズマ処理工程を参照)。このように、Mgドープの半導体薄膜から水素が脱離することにより、ドーパントとして用いられるMgが活性化されるので、p型半導体層16を、膜中のMgが活性化された状態で成膜することが可能となる。

【0094】

また、本実施形態のプラズマ処理工程を備えた方法とすることにより、III族窒化物半導体にドープされたMgが活性化されるので、成膜されるp型半導体層16中のMgドープ量を減らした場合でも、良好なp型特性が得られる。このように、p型半導体層16中のMgドープ量を低減した場合には、より結晶性の良好なp型半導体層16を成膜することが可能となる。

【0095】

また、本実施形態のプラズマ処理工程を備えることにより、成膜工程において水素が豊富に含有されるガスを雰囲気ガスとして用いた場合でも、その後のプラズマ処理工程においてIII族窒化物半導体から効果的に水素を脱離させることができる。これにより、成膜工程において、水素含有ガス雰囲気中で結晶性の高いMgドープ半導体薄膜を成膜した後、プラズマ処理工程において水素を脱離させ、ドーパントのMgが活性化されたMgドープ半導体薄膜を成膜することができる。従って、良好なp型特性を有するとともに、結晶性に優れたp型半導体層16を成膜することが可能となる。

【0096】

従来のように、成膜後のMgドープIII族窒化物半導体(p型半導体層)をアニール処理することにより、水素を脱離させてMgを活性化させる方法では、水素を効率的に脱離させることが難しく、結晶中に含まれるMgの内の1/10〜1/5は活性化されないという問題があった。これに対し、本実施形態では、上述のようなプラズマ処理工程が備えられた方法とすることにより、III族窒化物半導体中にドープされたMgを高効率で活性化することが可能となる。

【0097】

(成膜工程とプラズマ処理工程の繰り返し)

本実施形態のスパッタ工程は、上述したような成膜工程とプラズマ処理工程とを、交互に繰り返して半導体薄膜を積層することにより、MgドープIII族窒化物半導体からなるp型半導体層16を形成する方法としている。

上述のようなプラズマ処理工程におけるプラズマ処理により、基板上に成膜されたIII族窒化物半導体中の水素を離脱させることが可能であるが、このような水素離脱効果は、III族窒化物半導体表面から10nm(0.01μm)程度の膜厚までしか得られない。例えば、10nmよりも膜厚の大きなIII族窒化物半導体層だと、その表層部付近では水素離脱効果が得られるものの、表層部から離れた膜中ではその効果が得られない。

【0098】

そこで、本実施形態のスパッタ工程では、成膜工程とプラズマ処理工程とを交互に繰り返して行なう方法とし、例えば、まず、成膜工程において、10nmの膜厚のMgドープの半導体薄膜を成膜し、これにプラズマ処理工程においてプラズマ処理を施し、水素を離脱させる。そして、さらに、上述のような成膜工程とプラズマ処理工程とを交互に繰り返して半導体薄膜を積層することにより、MgドープIII族窒化物半導体を目的の膜厚とし、p型半導体層16が得られる(図6の模式図も参照)。このように、薄い膜厚のMgドープ半導体薄膜にプラズマ処理を施して水素を効率良く離脱させ、半導体薄膜を繰り返して成膜する工程とすることにより、最終的に厚い膜厚のMgドープIII族窒化物半導体を成膜する場合であっても、半導体層全体から水素を高効率で離脱させることが可能となる。

【0099】

本実施形態のスパッタ工程では、上述したような成膜工程とプラズマ処理工程との交互の繰り返し回数を1〜1000回の範囲として行なうことが好ましい。この繰り返し回数は、目的とするMgドープIII族窒化物半導体(p型半導体層)の膜厚と、成膜工程における成膜処理1回あたりの膜厚とから、適宜、設定することが可能である。

【0100】

なお、本実施形態のスパッタ工程は、交互に繰り返して行う成膜工程とプラズマ処理工程との工程間に、1〜300秒(5分)の範囲の間隔を設ける方法とすることが好ましい。成膜工程とプラズマ処理工程との工程間に所定時間の間隔を設けることにより、例えば、成膜工程においてチャンバ41内を水素含有ガス雰囲気とした場合、チャンバ41内の水素をスパッタ工程開始前に、外部に排出させることができるので、スパッタ工程における水素離脱処理をより効果的に行うことができる。

【0101】

また、本実施形態のスパッタ工程は、交互に繰り返して行う成膜工程とプラズマ処理工程との工程間に、成膜工程又はプラズマ処理工程の少なくとも何れかの処理条件を変更する調整工程が備えられた構成とすることができる。

スパッタ工程において、上述のような調整工程を設けた場合、この調整工程を、例えば、成膜工程における処理時間又は基板の温度、或いはプラズマ処理工程におけるパワー、処理時間、基板の温度又はチャンバ内の圧力等の内、何れか1以上の処理条件を変更する工程とすることができる。このような構成とした場合には、成膜工程やプラズマ処理工程の状況に応じ、迅速且つ細やかに処理条件を変更することができ、歩留まりや生産性を向上させることが可能となる。

【0102】

本実施形態のスパッタ工程では、上記成膜工程とプラズマ処理工程の繰り返しにより、MgドープIII族窒化物半導体からなるp型半導体層16を形成する。このようなスパッタ工程で形成されるp型半導体層16は、上述したように、好ましい膜厚としては0.05〜1μmの範囲であり、また、Mg(アクセプター不純物)の好ましいドープ濃度は1×1018〜5×1021個/cm3の範囲、より好ましくは1×1019〜5×1020個/cm3の範囲ある。また、上記スパッタ工程で形成されるp型半導体層16の好ましい水素濃度は1×1016cm−3以下である。

【0103】

(スパッタ装置)

本実施形態の製造方法のように、III族窒化物半導体からなる半導体層をスパッタ法で成膜する場合、一般に、III族金属をターゲットにし、スパッタ装置のチャンバ内に窒素含有ガス(窒素ガス:N2、アンモニア:NH3等)を導入し、気相中でIII族金属と窒素を反応させる反応性スパッタ法(反応性リアクティブスパッタ法)を用いる。スパッタ法としては、RFスパッタ及びDCスパッタがあるが、本発明に係る製造方法のように反応性スパッタ法を用いた場合には、連続的に放電させるDCスパッタでは帯電が激しく、成膜速度のコントロールが困難となる。このため、本発明に係る製造方法では、RFスパッタ法、又は、DCスパッタ法の中でもパルス的にバイアスを与えることができるパルスDCスパッタを用いることが好ましく、このようなスパッタ方法で処理可能なスパッタ装置を使用することが好ましい。

【0104】

また、RFスパッタを用いた場合には、帯電を回避する方法として、マグネットの位置をターゲット内で移動させることが好ましい。具体的な運動の方法は、使用するスパッタ装置によって選択することができ、揺動させたり、回転運動させたりすることができる。

図5に例示するスパッタ装置40では、ターゲット47の下方にマグネット42が備えられ、このマグネット42がターゲット47の下方で回転運動できる構成とされている。

【0105】

スパッタによってIII族窒化物半導体からなる半導体層を形成する場合には、より高エネルギーの反応種を基板に供給することが好ましい。このため、スパッタ装置内において基板11がプラズマ中に位置するように構成し、また、ターゲット47と基板11とが対面する位置関係として構成することが好ましい。また、基板11とターゲット47との間の距離を、10〜100mmの範囲とすることが好ましい。

【0106】

また、チャンバ41内には、できるだけ不純物を残さないことが好ましいので、スパッタ装置40の到達真空度は、1.0×10−3Pa以下であることが好ましい。

【0107】

また、本実施形態の製造方法では、スパッタ工程に備えられる成膜工程及びプラズマ処理工程を、同じスパッタ装置を用いて行なう方法とすることができる。この場合には、成膜工程とプラズマ処理工程との間に所定時間の間隔を設け、この間にチャンバ47内の雰囲気ガスを入れ替えるようにしても良い。

【0108】

以上説明したような、本実施形態のIII族窒化物半導体の製造方法によれば、MgがドープされたIII族窒化物半導体からなるp型半導体層16をスパッタ法によって成膜する際、Mgをドープして半導体薄膜を成膜する成膜工程と、該成膜工程で成膜された半導体薄膜に対して不活性ガスプラズマによる処理を行うプラズマ処理工程とを交互に繰り返すことにより、III族窒化物半導体を形成する方法としたので、MgがドープされたIII族窒化物半導体から効果的に水素を排出させることができ、ドーパントのMgが活性化されたIII族窒化物半導体を成長させることが出来る。また、半導体層中のMgが活性化されるので、Mgのドープ量を減らすことが可能となり、この場合には、より結晶性の良好なIII族窒化物半導体が得られる。これにより、水素を排出させるためのアニール工程等の設備を必要とせず、量産性並びに再現性に優れるスパッタ法を用いて、発光特性に優れたIII族窒化物半導体発光素子を製造することが可能となる。

【0109】

また、成膜工程において、チャンバ41内に水素含有ガス及び窒素含有ガスを流通させて結晶性の高いMgドープ半導体薄膜を成膜し、その後のプラズマ処理工程において、Mgドープ半導体薄膜に対して不活性ガスによるプラズマ処理を行った場合には、成膜工程を水素含有ガス雰囲気で行なうことによる優れた結晶性と、プラズマ処理工程の水素脱離効果によるMgの活性化効果の両方を得ることが可能となる。

【0110】

本発明に係る、p型不純物を添加して導電性をp型に制御したIII族窒化物半導体は、詳細を後述する発光ダイオード(LED)やレーザディスク(LD)等の発光素子に備えられるp型半導体層や、トランジスタのような電子デバイス等の各種半導体素子に用いることができる。

【0111】

[III族窒化物半導体発光素子の製造方法]

本発明に係るIII族窒化物半導体発光素子の製造方法は、図3(図1も参照)に例示するようなIII族窒化物半導体から各々なるn型半導体層14、発光層15及びp型半導体層16が順に積層された半導体層20を備え、p型半導体層16の少なくとも一部がMgがドープされたIII族窒化物半導体からなる方法であり、p型半導体層16の少なくとも一部を、上述したようなIII族窒化物半導体の製造方法によって形成する方法である。

【0112】

<発光素子の積層構造>

図2及び図3は、本実施形態の発光素子の製造方法の一例を説明するための図であり、基板上にIII族窒化物半導体からなる各層が形成された積層半導体10(図1参照)を用いて発光素子1を構成した例を示す概略図で、図2は平面図、図3は断面図である。

本実施形態の発光素子1は、上記製造方法で製造された積層半導体10のp型半導体層16上に透光性正極17が積層され、その上に正極ボンディングパッド18が形成されるとともに、n型半導体層14のn型コンタクト層14bに形成された露出領域14dに負極19が積層されて概略構成される。

そして、本実施形態のp型半導体層16は、MgがドープされたIII族窒化物半導体からなり、上記製造方法によって形成されたものである。

【0113】

『透光性正極』

透光性正極17は、上述した積層半導体10のp型半導体層16(p型コンタクト層16b)上に形成される透光性の電極である。

透光性正極17の材質としては、特に限定されず、ITO(In2O3−SnO2)、AZO(ZnO−Al2O3)、IZO(In2O3−ZnO)、GZO(ZnO−Ga2O3)等の材料を、この技術分野でよく知られた慣用の手段で設けることができる。また、その構造も、従来公知の構造を含めて如何なる構造のものも何ら制限なく用いることができる。

また、透光性正極17は、Mgがドープされたp型半導体層16上のほぼ全面を覆うように形成しても構わないし、隙間を開けて格子状や樹形状に形成しても良い。

【0114】

『正極ボンディングパッド及び負極』

正極ボンディングパッド18は、上述の透光性正極17上に形成される電極である。

正極ボンディングパッド18の材料としては、Au、Al、Ni及びCu等を用いた各種構造が周知であり、これら周知の材料、構造のものを何ら制限無く用いることができる。

正極ボンディングパッド18の厚さは、100〜1000nmの範囲内であることが好ましい。また、ボンディングパッドの特性上、厚い方が、ボンダビリティーが高くなるため、正極ボンディングパッド18の厚さは300nm以上とすることがより好ましい。さらに、製造コストの観点から500nm以下とすることが好ましい。

【0115】

負極19は、基板11上に、n型半導体層14、発光層15及びp型半導体層16が順次積層された半導体層において、n型半導体層14のn型コンタクト層14bに接するように形成される。

このため、負極19を設ける際は、p型半導体層16、発光層15及びn型半導体層14の一部を除去することにより、n型コンタクト層14bの露出領域14dを形成し、この上に負極19を形成する。

負極19の材料としては、各種組成および構造の負極が周知であり、これら周知の負極を何ら制限無く用いることができ、この技術分野でよく知られた慣用の手段で設けることができる。

【0116】

<発光素子の製造方法>

以下に、図2及び図3に示すような発光素子1の製造方法の一例について説明する。

本実施形態の発光素子1の製造方法は、上記製造方法で得られた積層半導体10を用い、該積層半導体10のp型半導体層16上に透光性正極17を積層し、その上に正極ボンディングパッド18を形成するとともに、n型半導体層14のn型コンタクト層14bに形成された露出領域14dに負極19を積層する方法である。

【0117】

『透光性正極の形成』

上述のような方法により、基板11上に、バッファ層12及び半導体層が積層された積層半導体10のp型コンタクト層16b上に、ITOからなる透光性正極17を形成する。

透光性正極17の形成方法としては、特に限定されず、この技術分野でよく知られた慣用の手段で設けることができる。また、その構造も、従来公知の構造を含めて如何なる構造のものも何ら制限なく用いることができる。

【0118】

また、上述したように、透光性正極17の材料は、ITOには限定されず、AZO、IZO、GZO等の材料を用いて形成することが可能である。

また、透光性正極17を形成した後、合金化や透明化を目的とした熱アニールを施す場合もあるが、施さなくても構わない。

【0119】

『正極ボンディングパッド及び負極の形成』

積層半導体10上に形成された透光性正極17上に、さらに、正極ボンディングパッド18を形成する。

この正極ボンディングパッド18は、例えば、透光性正極17の表面側から順に、Ti、Al、Auの各材料を、従来公知の方法で積層することによって形成することができる。

【0120】

また、負極19を形成する際は、まず、基板11上に形成されたp型半導体層16、発光層15及びn型半導体層14の一部をドライエッチング等の方法によって除去することにより、n型コンタクト層14bの露出領域14dを形成する(図2及び図3参照)。そして、この露出領域14d上に、例えば、露出領域14d表面側から順に、Ni、Al、Ti、及びAuの各材料を、従来公知の方法で積層することにより、4層構造の負極19を形成することができる。

【0121】

そして、上述のようにして、積層半導体10上に、透光性正極17、正極ボンディングパッド18及び負極19を設けたウェーハを、基板11の裏面を研削及び研磨してミラー状の面とした後、例えば、350μm角の正方形に切断することにより、発光素子チップ(発光素子1)とすることができる。

【0122】

以上説明したような、本実施形態のIII族窒化物半導体発光素子の製造方法によれば、p型半導体層16の少なくとも一部が、上記製造方法により、MgドープされたIII族窒化物半導体から形成する方法とされているので、結晶性の良好なIII族窒化物半導体からなるp型半導体層16を備え、優れた発光特性を有するIII族窒化物半導体発光素子が得られる。

【0123】

[ランプ]

以上説明したような、本発明に係るIII族窒化物半導体発光素子と蛍光体とを組み合わせることにより、当業者周知の手段によってランプを構成することができる。従来より、発光素子と蛍光体と組み合わせることによって発光色を変える技術が知られており、このような技術を何ら制限されることなく採用することが可能である。

例えば、蛍光体を適正に選定することにより、発光素子より長波長の発光を得ることも可能となり、また、発光素子自体の発光波長と蛍光体によって変換された波長とを混ぜることにより、白色発光を呈するランプとすることもできる。

また、ランプとしては、一般用途の砲弾型、携帯のバックライト用途のサイドビュー型、表示器に用いられるトップビュー型等、何れの用途にも用いることができる。

【0124】

例えば、図4に示す例のように、同一面電極型のIII族窒化物半導体発光素子1を砲弾型に実装する場合には、2本のフレームの内の一方(図4ではフレーム31)に発光素子1を接着し、また、発光素子1の負極(図3に示す符号19参照)をワイヤー34でフレーム32に接合し、発光素子1の正極ボンディングパッド(図3に示す符号18参照)をワイヤー33でフレーム31に接合する。そして、透明な樹脂からなるモールド35で発光素子1の周辺をモールドすることにより、図4に示すような砲弾型のランプ3を作成することができる。

【0125】

また、本発明に係る、Mgをドープして導電性をp型に制御したIII族窒化物半導体は、上述のような発光素子の他、レーザ素子や受光素子等の光電気変換素子、又は、HBT(Heterojunction Bipolar Transistor)やHEMT(High Electron Mobility Transistor)等の電子デバイスにも用いることができる。これらの半導体素子は、各種構造のものが多数知られており、本発明に係るIII族窒化物半導体の積層構造体の素子構造は、これら周知の素子構造を含めて何ら制限されない。

【実施例】

【0126】

次に、本発明のIII族窒化物半導体の製造方法、及びIII族窒化物半導体発光素子の製造方法を、実施例によりさらに詳細に説明するが、本発明はこれらの実施例にのみ限定されるものではない。

【0127】

[実施例1]

本実施例では、サファイアからなる基板上に、スパッタ法を用いてAlNからなる単結晶のバッファ層を積層し、その上に、MOCVD法を用いて単結晶のGaNからなる下地層を積層し、さらにその上に、アクセプター不純物をドープしたp型のGaN層をスパッタ法により積層し、積層半導体サンプルを作製した。

【0128】

『バッファ層の形成』

まず、表面を鏡面研磨した直径2インチの(0001)c面サファイア基板を、フッ酸及び有機溶媒によって洗浄した後、スパッタ装置のチャンバ(図5の符号41を参照)中へ導入した。この際、スパッタ装置としては、高周波式の電源部を備え、ターゲット内でマグネットを回転させることにより、磁場の掛かる位置を動かすことができる機構を備えたものを使用した。

【0129】

そして、スパッタ装置のチャンバ内で基板を500℃まで加熱し、窒素ガスを15sccmの流量で導入した後、チャンバ内の圧力を1.0Paに保持し、基板に50Wの高周波バイアスを印加しながら窒素プラズマに晒すことにより、基板の表面を洗浄した。

【0130】

次いで、チャンバ内にアルゴン及び窒素ガスを導入した後、基板の温度を500℃まで低下させた。そして、2000Wの高周波パワーを金属Alターゲット側に印加し、炉内の圧力を0.5Paに保ち、Arガスを5sccm、窒素ガスを15sccmの流量で流通させた条件(ガス全体に対する窒素の比は75%)で、サファイア基板上に単結晶のAlNからなるバッファ層を成膜した。この際の成長速度は0.12nm/sであった。

【0131】

なお、ターゲット内のマグネットは、基板洗浄及びバッファ層の成膜の何れの際も回転させた。上述のようにして50nmのAlNからなるバッファ層を成膜した後、プラズマを立てるのを停止した。以上の手順により、基板上に、50nmの厚さの単結晶のAlNからなるバッファ層を形成した。

【0132】

『下地層の形成』

次に、バッファ層が形成された基板を、MOCVD法によってGaNからなる下地層を成長させるため、MOCVD装置のチャンバ内へ搬送した。そして、チャンバ内に水素ガスを流通した状態で基板の温度を1050℃まで上昇させ、バッファ層の表面に付着した汚れを昇華させて除去した。また、この際、基板の温度が830℃以上となった時点から、アンモニアを炉内に流通させた。

【0133】

次いで、基板の温度を1020℃まで低下させた後、アンモニアをそのままチャンバ内に流通させながら、バブリングによって発生させたトリメチルガリウム(TMG)の蒸気を炉内へ流通し、単結晶のGaNからなる下地層を2μmの膜厚で形成した。その後、TMGの供給を停止し、GaNの成長を停止させて降温した。

【0134】

『p型GaN層の形成(スパッタ工程)』

次に、上記方法で下地層を形成した基板を、スパッタ工程においてp型GaN層(p型半導体層)を基板上に成長させるため、スパッタ装置のチャンバ内に移送した。この際、スパッタ工程には、図5に示すスパッタ装置40のような、高周波式の電源部を有し、四角形のGaターゲット内をマグネットがスイープすることで磁場の掛かる位置を動かすことができる機構を備えたものを使用した。また、Gaターゲット内には、冷媒を流通させるための配管を設置し、20℃に冷却した冷媒を配管内に流通させ、熱によるGaの融解を防止した。

また、上記Gaターゲットとしては、GaメタルにMgを固溶したものを使用した。また、Gaメタルの重量に対するMgの重量の割合は、およそ1%とした。

【0135】

本実施例のスパッタ工程では、小工程である成膜工程として、まず、スパッタ装置のチャンバ内にアルゴン、窒素及び水素からなる混合ガスを導入した後、基板の温度を800℃まで上昇させた。そして、2000Wの高周波バイアスをターゲット側に印加し、炉内の圧力を0.5Paに保ちながら、Arガスを10sccm、窒素ガスを10sccm、水素ガスを10sccmの流量で流通させた条件で、下地層上に単結晶のGaNからなる半導体薄膜を成膜した。この際、GaNの成長速度を概ね100nm/hrとし、Mgドープの単結晶GaNからなる薄膜を5nmの膜厚で成膜した後、プラズマを立てるのを停止した。

【0136】

次いで、チャンバ41内に流通させるガスを、上記組成のガスから、Arガス10sccmのみに切り替え、プラズマ処理工程を行なった。この際、チャンバ41内の圧力を0.5Paとした状態で、基板側に50Wの高周波バイアスを印加することにより、基板を不活性ガスプラズマに曝し、プラズマ処理を行った(逆スパッタ)。また、この際の基板の温度は800℃とし、処理時間は4秒とした。

【0137】

そして、上記規定時間のプラズマ処理が終了した後、さらに、上記条件の成膜工程を行い、また、さらに、上記条件のプラズマ処理工程を行なった。このような、成膜工程とプラズマ処理工程とを交互に繰り返し、この繰り返し回数を42回としてスパッタ工程を行ない、半導体薄膜を積層した。このようにして、膜厚が210nmのp型GaN層(p型半導体層)を成膜した。

【0138】

上述のようなスパッタ工程が終了した後、スパッタ装置から取り出した基板上のp型GaN層中の水素濃度及びMgドープ量を二次イオン質量分析(SIMS)法によって分析したところ、水素の含有量は1×1019cm−3程度であり、一方、Mgのドープ量は5×1020cm−3程度であった。

【0139】

また、上記スパッタ工程で成膜されたp型GaN層を目視確認したところ、表面が鏡面であり、また、透明であった。また、このGaN層のホール測定を行ったところ、p型キャリアを活性化するためのアニール処理を行わなくてもp型の導電性を示し、キャリア濃度が5×1017cm−3程度であり、移動度は10cm2/Vs程度と充分な数値を示した。これは、p型GaN層の結晶性が向上し、結晶中のMgが活性化したためと考えられる。

【0140】

[比較例1]

比較例1では、MgドープGaN層をスパッタ法で積層する際、上述のようなプラズマ処理工程を設けず、膜厚が210nmのp型GaN層(p型半導体層)を、成膜工程において連続処理で成膜し、その他の成膜条件は実施例1と同様の条件として、下地層上にMgドープの単結晶のp型GaN層が積層されたサンプルを作製した。

【0141】

上述のようなスパッタ工程が終了した後、スパッタ装置から取り出した基板上のp型GaN層中の水素濃度及びMgドープ量を、実施例1と同様の方法を用いて分析したところ、Mgのドープ量は5×1020cm−3程度であり、実施例1と同等であったが、水素の含有量は5×1020cm−3程度と、Mgドープ量とほぼ同程度の含有量であった。

【0142】

得られたサンプルを目視確認したところ、積層されたMgドープのGaN層の表面は鏡面であり、また、透明であった。しかしながら、このMgドープのGaN層のホール測定を行ったところ、電気的測定が出来なかった。これは、GaN層の結晶性が低いために、Mgドープによって導電性を制御することが困難なためと考えられる。

【0143】

[実施例2]

実施例2では、基板11に成膜するバッファ層を、成膜条件を下記のようにコントロールすることにより、AlNからなる柱状結晶の集合体として多結晶構造で形成した点を除き、実施例1と同様の方法により、基板11上にGaNからなる下地層を積層し、さらにその上に、アクセプター不純物をドープしたp型のGaN層をスパッタ法により積層し、積層半導体サンプルを作製した。

この際、基板11の表面を窒素プラズマに晒して洗浄する際の条件として、基板温度を750℃、チャンバ内の圧力を0.08Paとし、また、AlNからなるバッファ層の成膜条件として、Arガスを15sccm、窒素ガスを5sccm(ガス全体に対する窒素の比は25%)の流量とした点が、実施例1に示した条件とは異なる。

【0144】

このような工程により、基板11上に、柱状結晶の集合体でAlNからなるバッファ層を形成した後、その上に、単結晶のGaNからなる下地層を2μmの膜厚で形成し、さらに、膜厚が210nmのp型GaN層(p型半導体層)を成膜した。

そして、スパッタ装置から取り出した基板上のp型GaN層中の水素濃度及びMgドープ量を二次イオン質量分析(SIMS)法によって分析したところ、水素の含有量は1×1019cm−3程度であり、一方、Mgのドープ量は5×1020cm−3程度であった。

【0145】

また、実施例2のサンプルにおいて、p型GaN層の表面を目視確認したところ、表面が鏡面であり、透明であった。また、このGaN層のホール測定を行ったところ、p型キャリアを活性化するためのアニール処理を行わなくてもp型の導電性を示し、キャリア濃度が5×1017cm−3程度であり、移動度は10cm2/Vs程度と充分な数値を示した。これは、p型GaN層の結晶性が向上し、結晶中のMgが活性化したためと考えられる。

【0146】

[実施例3]

実施例3では、プラズマ処理工程の処理時間で基板側に印加する高周波バイアスを5Wとした点を除き、実施例1と同様の条件で、膜厚が210nmのp型GaN層(p型半導体層)を成膜した。

【0147】

上述のようなスパッタ工程が終了した後、スパッタ装置から取り出した基板上のp型GaN層中の水素濃度及びMgドープ量を、実施例1と同様の方法を用いて分析したところ、水素の含有量は1×1020cm−3程度であり、また、Mgのドープ量は5×1020cm−3程度であり、実施例1と同等であった。

【0148】

また、上記スパッタ工程で成膜されたp型GaN層を目視確認したところ、表面が鏡面であり、また、透明であった。また、このGaN層のホール測定を行ったところ、p型キャリアを活性化するためのアニール処理を行わなくてもp型の導電性を示し、キャリア濃度が3×1017cm−3と高い数値を示している。これは、実施例1と同様、p型GaN層の結晶性が向上し、結晶中のMgが活性化したためと考えられる。

一方、実施例3のサンプルは、実施例1のサンプルと比較した場合、キャリア濃度が若干低い値となっている。これは、実施例3では、プラズマ処理工程において基板側に印加する高周波バイアス(パワー)が5Wと低いため、プラズマ処理による水素脱離効果が、実施例1に比べて小さくなっているためと考えられる。

【0149】

[実施例4]

本実施例では、スパッタ法により積層したMgドープのp型AlGaNを用いて、図2及び図3に示すような発光ダイオード(LED)のサンプルを作製した。本例では、まず、図1に示すような積層半導体10を、バッファ層12をスパッタ法、下地層14aをMOCVD法、n型コンタクト層14bをスパッタ法、nクラッド層14c及び発光層15をMOCVD法の各方法で形成し、その上のp型半導体層16を、本発明のスパッタ工程によって形成した。

【0150】

『バッファ層及び下地層の形成』

まず、第一のスパッタ装置を用いて、c面サファイア基板(基板11)上にプラズマによる前処理を施した後、RFスパッタ法を用いてAlNの単結晶からなるバッファ層12を形成し、その上に、GaNからなる下地層14aをMOCVD装置内で形成した。この際、AlNからなるバッファ層12とGaNからなる下地層14aは、実施例1と同様の方法で基板11上に成膜した。

【0151】

『n型コンタクト層の形成』

次いで、下地層14aを形成した基板11を第二のスパッタ装置内に搬送し、GaNからなるn型コンタクト層14bを、RFスパッタ法を用いて形成した。この際、n型コンタクト層14bには、Siをドープした。

【0152】

ここで、GaNの成膜に使用する第二のスパッタ装置としては、高周波式の電源部を有し、四角形のGaターゲット内をマグネットがスイープすることで磁場の掛かる位置を動かすことができる機構を備えたものを使用した。この際、Gaターゲット内には冷媒を流通させるための配管を設置し、20℃に冷却した冷媒を配管内に流通させ、熱によるGaの融解を防止した。

【0153】

次いで、チャンバ内にアルゴン及び窒素ガスを導入した後、基板の温度を1000℃まで上昇させた。そして、2000Wの高周波バイアスを金属Gaターゲット側に印加し、炉内の圧力を0.5Paに保ちながら、Arガスを5sccm、窒素ガスを15sccmの流量で流通させた条件(ガス全体に対する窒素の比は75%)で、下地層14a上に、GaNからなるn型コンタクト層14bを成膜した。この際、チャンバ内にSiターゲットを併置し、同時にスパッタさせることによってSiを気相中に取り出し、n型コンタクト層14bをなすGaN結晶中にSiをドープした。この際の成長速度は、おおよそ1nm/sであった。そして、GaNからなるn型コンタクト層14bを成膜した後、プラズマを立てるのを停止した。

上記手順により、1×1019cm−3の電子濃度を有し、2μmの膜厚のSiドープGaNからなるn型コンタクト層14bを成膜した。

【0154】

以上説明したような工程により、サファイア基板(基板11)上に、単結晶構造を有するAlNからなるバッファ層12を形成し、その上にアンドープで2μmの膜厚のGaN層(n型下地層14a)と、1×1019cm−3のキャリア濃度を持つ2μmのSiドープのGaN層(n型コンタクト層14b)を形成した。成膜後にチャンバから取り出した基板は無色透明であり、GaN層(ここではn型コンタクト層14b)の表面は鏡面であった。

【0155】

『n型クラッド層及び発光層の形成』

上記手順で作製したサンプルのn型コンタクト層14b上に、MOCVD法を用いてn型クラッド層14c及び発光層15を積層した。

【0156】

「n型クラッド層の形成」

まず、SiドープGaNからなるn型コンタクト層14bが成長された基板を、MOCVD装置のチャンバ内へ搬送した。そして、チャンバ内を窒素で置換した状態として基板の温度を1000℃まで上昇させ、n型コンタクト層14bの最表面に付着した汚れを昇華させて除去した。また、この際、基板の温度が830℃以上となった時点から、アンモニアを炉内に流通させた。

【0157】

次いで、基板の温度を740℃まで低下させた後、アンモニアをチャンバ内にそのまま流通させながら、SiH4ガスと、バブリングによって発生させたTMI及びTEGの蒸気を炉内へ流通させ、180Åの膜厚を有し、SiドープIn0.1Ga0.9Nからなるn型クラッド層14cを形成した。そして、TMI、TEG及びSiH4のバルブを切り替え、これらの原料の供給を停止した。

【0158】

「発光層の形成」

次いで、GaNからなる障壁層15aと、In0.2Ga0.8Nからなる井戸層15bとから構成され、多重量子井戸構造を有する発光層15を形成した。この、発光層15の形成にあたっては、SiドープIn0.1Ga0.9Nからなるn型クラッド層14c上に、まず、障壁層15aを形成し、この障壁層15a上に、In0.2Ga0.8Nからなる井戸層15bを形成した。このような積層手順を5回繰り返した後、5番目に積層した井戸層15b上に、6番目の障壁層15aを形成し、多重量子井戸構造を有する発光層15の両側に障壁層15aを配した構造とした。

【0159】

すなわち、SiドープIn0.1Ga0.9Nからなるn型クラッド層14cの成長終了後、基板温度や炉内の圧力、キャリアガスの流量や種類はそのままとし、TEGのバルブを切り替え、炉内へTEGを供給することにより、GaNからなる障壁層15aを成長させた。これにより、150Åの膜厚を有する障壁層15aを形成した。

【0160】

次いで、障壁層15aの成長を終了させた後、基板11の温度や炉内の圧力、キャリアガスの流量や種類はそのままとして、TEG及びTMIのバルブを切り替えてTEG及びTMIを炉内へ供給し、In0.2Ga0.8Nからなる井戸層15bを成長させた。これにより、20Åの膜厚を有する井戸層15bを形成した。

【0161】

井戸層15bの成長を終了させた後、再び障壁層15aを成長させた。そして、このような手順を5回繰り返すことにより、5層の障壁層15aと5層の井戸層15bを形成した。さらに、最後に積層した井戸層15b上に、障壁層15aを形成し、発光層15とした。

【0162】

『p型半導体層の形成』

上述の各工程処理によって得られたウェーハを第三のスパッタ装置に搬送し、p型半導体層16を成膜するためのスパッタ工程を行なった。

ここで、スパッタ工程に使用するスパッタ装置としては、高周波式の電源部を有し、回転式のGaターゲット及びAlターゲットをチャンバ内に備えたものを使用した。また、Gaターゲット内には冷媒を流通させるための配管を設置し、20℃に冷却した冷媒を配管内に流通させ、熱によるGaの融解を防止した。また、Alターゲットは、Gaターゲットと比較して表面積がおよそ1/10の割合とされたものを用いた。これにより、成長させるAlGaN層の組成がAl0.08Ga0.92Nとなるように調整した。

また、GaターゲットはMgを固溶したものを用い、Gaメタルの重量に対するMgの重量の割合は、およそ1%とした。

【0163】

そして、成膜工程として、まず、スパッタ装置のチャンバ内にアルゴン、窒素及び水素からなる混合ガスを導入した後、基板の温度を800℃まで上昇させた。そして、2000Wの高周波バイアスをGaターゲットに印加し、炉内の圧力を0.5Paに保ちながら、Arガスを10sccm、窒素ガスを10sccm、水素ガスを10sccmの流量で流通させた条件で、MgドープAlGaNからなる半導体薄膜を成膜した。この際、MgドープAlGaNの成長速度を概ね100nm/hrとし、MgドープAlGaNを5nmの膜厚で成膜した後、プラズマを立てるのを停止した。

【0164】

次いで、チャンバ内に流通させるガスを、上記組成のガスから、Arガス10sccmのみに切り替え、プラズマ処理工程を行なった。この際、チャンバ内の圧力を0.5Paとした状態で、基板側に50Wの高周波バイアス(パワー)を印加することにより、基板を不活性ガスプラズマに曝し、プラズマ処理を行った(逆スパッタ)。また、この際の基板の温度は800℃とし、処理時間は4秒とした。

【0165】

そして、上記規定時間のプラズマ処理が終了した後、さらに、上記条件の成膜工程を行い、また、さらに、上記条件のプラズマ処理工程を行なった。このような、成膜工程とプラズマ処理工程とを交互に繰り返し、この繰り返し回数を42回としてスパッタ工程を行なうことにより、MgドープAlGaNからなる半導体薄膜を積層した。このようにして、膜厚が210nmのMgドープAl0.08Ga0.92Nからなるp型半導体層16を成膜した。

【0166】

上述のようなスパッタ工程が終了した後、スパッタ装置から取り出した基板上のp型GaN層中の水素濃度及びMgドープ量を二次イオン質量分析(SIMS)法によって分析したところ、水素の含有量は1×1019cm−3程度であり、一方、Mgのドープ量は5×1020cm−3程度であった。

【0167】

上述の工程で得られたMgドープAlGaNからなるp型半導体層16は、p型キャリアを活性化するためのアニール処理を行わなくてもp型を示しており、キャリア濃度は5×1017cm−3程度であり、移動度は10cm2/Vs程度と充分な数値を示した。

【0168】

上述のようにして作製したLED用のエピタキシャルウェーハは、図1に示す積層半導体10のように、c面を有するサファイアからなる基板11上に、AlN層(バッファ層12)を形成した後、基板11側から順に、2μmのアンドープGaN層(下地層14a)、1×1019cm−3の電子濃度を持つ2μmのSiドープGaN層(n型コンタクト層14b)、1×1018cm−3の電子濃度を持つ180ÅのIn0.1Ga0.9Nクラッド層(n型クラッド層14c)、GaN障壁層に始まってGaN障壁層に終わり、層厚が150Åとされた6層のGaN障壁層(障壁層15a)と、層厚が20Åとされた5層のノンドープのIn0.2Ga0.8N井戸層(井戸層15b)とからなる多重量子井戸構造(発光層15)、膜厚が10nmのMgドープAl0.1Ga0.9Nからなるp型クラッド層16aと、膜厚が200nmのMgドープAl0.02Ga0.98Nからなるp型コンタクト層16bとから構成されるMgドープAlGaN層(p型半導体層16)を積層した構造を有する。

【0169】

『LEDの作製』

次いで、上記エピタキシャルウェーハ(積層半導体10)を用いてLEDを作製した。

すなわち、上記エピタキシャルウェーハのMgドープAlGaN層(p型半導体層16b)の表面に、公知のフォトリソグラフィー技術によってITOからなる透光性電極17を形成し、その上に、チタン、アルミニウム及び金を順に積層した構造を有する正極ボンディングパッド18(p電極ボンディングパッド)を形成し、p側電極とした。さらに、ウェーハに対してドライエッチングを施し、n型コンタクト層14bのn側電極(負極)を形成する領域を露出させ、この露出領域14dにNi、Al、Ti及びAuの4層が順に積層されてなる負極19(n側電極)を形成した。このような手順により、ウェーハ(図1の積層半導体10を参照)上に、図2に示すような形状を有する各電極を形成した。

【0170】

そして、上述の手順でp側及びn側の各電極が形成されたウェーハについて、サファイアからなる基板11の裏面を研削及び研磨してミラー状の面とした。そして、このウェーハを350μm角の正方形のチップに切断し、各電極が上になるようにリードフレーム上に配置し、金線でリードフレームへ結線して発光素子とした(図4のランプ3を参照)。

上述のようにして作製した発光ダイオードのp側およびn側の電極間に順方向電流を流したところ、電流20mAにおける順方向電圧は3.1Vであった。また、p側の透光性電極17を通して発光状態を観察したところ、発光波長は460nmであり、発光出力は15mWを示した。このような発光ダイオードの特性は、作製したウェーハのほぼ全面から作製された発光ダイオードについて、ばらつきなく得られた。

【0171】

以上の結果により、本発明に係るIII族窒化物半導体が素子特性に優れており、また、本発明に係るIII族窒化物半導体発光素子が優れた発光特性を備えていることが明らかである。

【産業上の利用可能性】

【0172】

本発明のIII族窒化物半導体の製造方法は、スパッタ法によりMgをドープして導電性をp型に制御したIII族窒化物半導体を作製することができるため、発光ダイオード(LED)やレーザダイオード(LD)のp型コンタクト層、また、FETのような電子デバイス等のさまざまな半導体素子の製造に用いることができる。

【図面の簡単な説明】

【0173】

【図1】本発明に係るIII族窒化物半導体の一例を模式的に説明する図であり、積層半導体の断面構造を示す概略図である。

【図2】本発明に係るIII族窒化物半導体の一例を模式的に説明する図であり、III族窒化物半導体によって構成される発光素子の平面構造を示す概略図である。

【図3】本発明に係るIII族窒化物半導体の一例を模式的に説明する図であり、III族窒化物半導体によって構成される発光素子の断面構造を示す概略図である。

【図4】本発明に係るIII族窒化物半導体発光素子を用いて構成したランプを模式的に説明する概略図である。

【図5】本発明に係るIII族窒化物半導体発光素子の製造方法の一例を模式的に説明する図であり、チャンバ内にターゲットが備えられたスパッタ装置の構造を示す概略図である。

【図6】本発明に係るIII族窒化物半導体の製造方法の一例を説明する図であり、(a)成膜工程において基板上にMgドープIII族窒化物半導体を成膜し、(b)プラズマ処理工程においてMgドープIII族窒化物半導体に不活性ガスプラズマ処理を施した状態を示す模式図である。

【符号の説明】

【0174】

1…III族窒化物半導体発光素子、10…積層半導体(III族窒化物半導体)、11…基板、11a…表面、12…バッファ層、14…n型半導体層、15…発光層、16…p型半導体層(III族窒化物半導体)、16a…p型クラッド層、16b…p型コンタクト層、3…ランプ、40…スパッタ装置、41…チャンバ、47…ターゲット、A、B…半導体薄膜

【技術分野】

【0001】

本発明は、発光ダイオード(LED)、レーザダイオード(LD)、電子デバイス等に、好適に用いられ、一般式AlaGabIncN(0≦a≦1、0≦b≦1、0≦c≦1、a+b+c=1)で表されるIII族窒化物半導体の製造方法に関し、特に、マグネシウム(Mg)が添加されてなるp型のIII族窒化物半導体層を形成するためのIII族窒化物半導体の製造方法、III族窒化物半導体発光素子の製造方法、及びIII族窒化物半導体発光素子、並びにランプに関する。

【背景技術】

【0002】

III族窒化物半導体は、可視光から紫外光領域の範囲に相当するエネルギーの直接遷移型のバンドギャップを有し、発光効率に優れていることから、発光ダイオード(LED)やレーザダイオード(LD)等の半導体発光素子として製品化され、各種用途で使用されている。また、電子デバイスに用いた場合でも、III族窒化物半導体は、従来のIII−V族化合物半導体を用いた場合に比べて優れた特性が得られるポテンシャルを有している。

【0003】

このようなIII族窒化物半導体は、一般的に、トリメチルガリウム、トリメチルアルミニウムおよびアンモニアを原料として、有機金属化学気相成長(MOCVD)法によって製造されている。MOCVD法は、キャリアガスに原料の蒸気を含ませて基板表面に運搬し、加熱された基板の表面で原料を分解させることにより、結晶を成長させる方法である。

【0004】

従来、III族窒化物半導体の単結晶ウェーハは市販されておらず、III族窒化物半導体としては、異なる材料の単結晶ウェーハ上に結晶を成長させて得る方法が一般的である。このような、異種基板と、その上にエピタキシャル成長させるIII族窒化物半導体結晶との間には、大きな格子不整合が存在する。例えば、サファイア(Al2O3)基板上に窒化ガリウム(GaN)を成長させた場合、両者の間には16%の格子不整合が存在し、SiC基板上に窒化ガリウムを成長させた場合には、両者の間に6%の格子不整合が存在する。一般に、上述のような大きな格子不整合が存在する場合、基板上に結晶を直接エピタキシャル成長させることが困難となり、また、成長させた場合であっても結晶性の良好な結晶が得られないという問題がある。

【0005】

そこで、有機金属化学気相成長(MOCVD)法により、サファイア単結晶基板もしくはSiC単結晶基板の上に、III族窒化物半導体結晶をエピタキシャル成長させる際、まず、基板上に窒化アルミニウム(AlN)や窒化アルミニウムガリウム(AlGaN)からなる低温バッファ層と呼ばれる層を積層し、その上に高温でIII族窒化物半導体結晶をエピタキシャル成長させる方法が提案されており、一般に行われている。

【0006】

また、バッファ層としてAlN等の層をMOCVD以外の方法で基板上に成膜し、その上に成膜される層をMOCVD法で成膜する方法に関し、例えば、高周波スパッタで成膜したバッファ層上に、MOCVD法で同じ組成の結晶を成長させる方法が提案されている(例えば、特許文献1)。

しかしながら、特許文献1に記載の方法では、安定して良好な結晶を得ることができないという問題がある。

【0007】

そこで、安定して良好な結晶を得るため、例えば、バッファ層成長後にアンモニアと水素からなる混合ガス中でアニールする方法(例えば、特許文献2)や、バッファ層を400℃以上の温度でDCスパッタにより成膜する方法(例えば、特許文献3)が提案されている。

【0008】

一方、III族窒化物半導体結晶をスパッタによって製造する研究も行われており、例えば、高抵抗のGaNを積層することを目的とし、サファイアからなる基板上に、スパッタ法によってGaNを直接成膜する方法が提案されている(例えば、特許文献4)。

【0009】

また、半導体層上に電極を形成する際に、半導体層に対する前処理としてArガスを用いて逆スパッタを行なう方法がある(例えば、特許文献5)。特許文献5に記載の方法によれば、III族窒化物化合物半導体層の表面に逆スパッタを施すことにより、半導体層と電極との間の電気的接触特性を改善できるというものである。

【0010】

上述のようなスパッタ法を用いて、アクセプター不純物としてMgをドーピングしたGaNを基板上に成膜する際、チャンバ内の雰囲気ガスに水素(H2)を流通させたほうが、結晶性の良好なGaNを成膜することができる。しかしながら、水素ガスを構成する水素原子(H)はMgと結合し易いため、ドーパント(Mg)のキャリア濃度の低下を招くという問題がある。

【0011】

また、GaN結晶膜をMOCVD法で成膜する場合には、一般にN(窒素)源としてアンモニアガス(NH3)を用いるため、この場合にも結晶膜中に水素が混入する。そこで、不活性化ガス中において、600℃以上等の温度でアニール処理を行う活性化アニール法と呼ばれる方法により、水素をGaN結晶中から排出させる方法が採用されている。しかしながら、LED等のIII族窒化物半導体発光素子の構造においては、アニールを行なった場合、アニール熱によってInGaN結晶からなる発光層に損傷が発生するという問題がある。また、通常、GaN結晶膜にアニールを施した場合でも、ドープされたMgの内の1/10〜1/5程度は活性化されず、アニール効果が得られにくいという問題があった。

【特許文献1】特公平5−86646号公報

【特許文献2】特許第3440873号公報

【特許文献3】特許第3700492号公報

【特許文献4】特開昭60−039819号公報

【特許文献5】特開平8−264478号公報

【発明の開示】

【発明が解決しようとする課題】

【0012】

本発明は上記問題に鑑みてなされたものであり、スパッタ法によって基板上に積層するIII族窒化物半導体の結晶性を、成膜後にアニール等の熱処理を行なうことなく改善することができ、ドーパントとしてMgを添加して充分に高いキャリア濃度を有するp型のIII族窒化物半導体を積層することが可能なIII族窒化物半導体の製造方法、III族窒化物半導体発光素子の製造方法、及び、発光特性に優れたIII族窒化物半導体発光素子並びにランプを提供することを目的とする。

【課題を解決するための手段】

【0013】

本発明者等が鋭意検討したところ、上述のようなGaN結晶膜への水素の混入に関し、スパッタ法によってMgドープGaN結晶膜を成膜した後、ArガスプラズマによってGaN結晶膜を逆スパッタ(プラズマ処理)することにより、結晶膜中の水素が外部へ離脱することが明らかとなった。但し、このような逆スパッタによる水素の離脱効果は、膜の表面から100Å(0.01μm)程度の範囲までしか得られず、最大で1.0μm近い膜厚を有するMgドープGaN結晶膜の場合、結晶膜表面付近は水素が離脱するものの、表面から離れた結晶膜中の水素は排出することが困難であった。このため、成膜後のMgドープGaN結晶膜に対して逆スパッタを施したとしても、GaN結晶膜中のMgドープ濃度低下が避けられず、GaN結晶の不活性化を招く虞があった。

【0014】

このような問題に対し、本発明者等は、MgドープGaN結晶膜(p型半導体層)を積層する際、所定範囲の膜厚でGaNからなる半導体薄膜を成膜する工程と、この半導体薄膜に不活性ガスプラズマによる処理を行う工程とを交互に繰り返して半導体薄膜を積層することにより、アニール処理等を行うことなく効果的に水素を排出しながら、充分に高いキャリア濃度を有するp型のIII族窒化物半導体の成膜が可能となることを見出し、本発明を完成した。

即ち、本発明は以下に関する。

【0015】

[1] チャンバ内に基板及びターゲットを配置し、前記基板上にMgがドープされたIII族窒化物半導体を反応性スパッタ法によって形成するスパッタ工程が備えられたIII族窒化物半導体の製造方法であって、前記スパッタ工程は、Mgをドープして半導体薄膜を成膜する成膜工程と、該成膜工程で成膜された半導体薄膜に対して不活性ガスプラズマによる処理を行うプラズマ処理工程の各小工程を含み、前記成膜工程と前記プラズマ処理工程とを交互に繰り返して前記半導体薄膜を積層することにより、III族窒化物半導体を形成することを特徴とするIII族窒化物半導体の製造方法。

[2] 前記スパッタ工程は、前記成膜工程において、Mgがドープされた前記半導体薄膜を1〜100nmの範囲の膜厚で成膜し、この膜厚で行なう成膜工程と前記プラズマ処理工程とを交互に繰り返して前記半導体薄膜を積層することにより、III族窒化物半導体を形成することを特徴とする[1]に記載のIII族窒化物半導体の製造方法。

[3] 前記成膜工程は、前記チャンバ内に、水素含有ガス及び/又は窒素含有ガスを流通させて行なうことを特徴とする[1]又は[2]に記載のIII族窒化物半導体の製造方法。

[4] 前記窒素含有ガスがアンモニアガスであることを特徴とする[3]に記載のIII族窒化物半導体の製造方法。

[5] 前記成膜工程は、前記基板の温度を300℃〜1200℃の範囲とすることを特徴とする[1]〜[4]の何れかに記載のIII族窒化物半導体の製造方法。

【0016】

[6] 前記プラズマ処理工程は、前記チャンバ内において不活性ガスプラズマを発生させる際のパワーが10〜5000Wの範囲であることを特徴とする[1]〜[5]の何れかに記載のIII族窒化物半導体の製造方法。

[7] 前記プラズマ処理工程は、前記不活性ガスプラズマによる処理時間が1〜600秒の範囲であることを特徴とする[1]〜[6]の何れかに記載のIII族窒化物半導体の製造方法。

[8] 前記プラズマ処理工程は、前記チャンバ内に流通させる不活性ガスとして、He、Ne、Ar、Kr及びXeの内の何れか1種以上を用いることを特徴とする[1]〜[7]の何れかに記載のIII族窒化物半導体の製造方法。

[9] 前記プラズマ処理工程は、前記基板の温度を室温〜800℃の範囲とすることを特徴とする[1]〜[8]の何れかに記載のIII族窒化物半導体の製造方法。

[10] 前記プラズマ処理工程は、前記チャンバ内の圧力を1×10−5〜10Paの範囲として行なうことを特徴とする[1]〜[9]の何れかに記載のIII族窒化物半導体の製造方法。

【0017】

[11] 前記スパッタ工程は、前記成膜工程と前記プラズマ処理工程との交互の繰り返し回数を1〜1000回の範囲として前記半導体薄膜を積層することを特徴とする[1]〜[10]の何れかに記載のIII族窒化物半導体の製造方法。

[12] 前記スパッタ工程は、交互に繰り返して行う前記成膜工程と前記プラズマ処理工程との工程間に、1〜300秒の範囲の間隔を設けることを特徴とする[1]〜[11]の何れかに記載のIII族窒化物半導体の製造方法。

[13] 前記スパッタ工程は、交互に繰り返して行う前記成膜工程と前記プラズマ処理工程との工程間に、前記成膜工程又は前記プラズマ処理工程の少なくとも何れかの処理条件を変更する調整工程が備えられていることを特徴とする[1]〜[12]の何れかに記載のIII族窒化物半導体の製造方法。

[14] 前記調整工程は、前記成膜工程における処理時間又は基板の温度、或いは前記プラズマ処理工程におけるパワー、処理時間、基板の温度又はチャンバ内の圧力の内、何れか1以上の処理条件を変更することを特徴とする[13]に記載のIII族窒化物半導体の製造方法。

[15] 少なくとも前記スパッタ工程の前に、前記基板上にIII族窒化物半導体からなる下地層を形成する工程が備えられていることを特徴とする[1]〜[14]の何れかに記載のIII族窒化物半導体の製造方法。

【0018】

[16] III族窒化物半導体から各々なるn型半導体層、発光層及びp型半導体層が順に積層された半導体層を備え、前記p型半導体層の少なくとも一部がMgの添加されたIII族窒化物半導体からなるIII族窒化物半導体発光素子の製造方法であって、前記p型半導体層の少なくとも一部を、[1]〜[15]の何れかに記載のIII族窒化物半導体の製造方法によって形成することを特徴とするIII族窒化物半導体発光素子の製造方法。

【0019】

[17]III族窒化物半導体から各々なるn型半導体層、発光層及びp型半導体層が順に積層された半導体層を備え、前記p型半導体層の少なくとも一部がMgの添加されたIII族窒化物半導体からなるIII族窒化物半導体発光素子であって、前記p型半導体層の少なくとも一部が、[1]〜[15]の何れかに記載のIII族窒化物半導体の製造方法によって形成されてなることを特徴とするIII族窒化物半導体発光素子。

[18] 前記p型半導体層の膜厚が0.05〜1μmの範囲とされていることを特徴とする[17]に記載のIII族窒化物半導体発光素子。

[19] 前記p型半導体層のMgドープ濃度が1×1019〜5×1020個/cm3の範囲とされていることを特徴とする[17]又は[18]に記載のIII族窒化物半導体発光素子。

[20] 前記p型半導体層の水素濃度が1×1016個/cm3以下とされていることを特徴とする[17]〜[19]の何れかに記載のIII族窒化物半導体発光素子。

[21] 上記[17]〜[20]の何れかに記載のIII族窒化物半導体発光素子が用いられてなるランプ。

【発明の効果】

【0020】

本発明のIII族窒化物半導体の製造方法によれば、MgがドープされたIII族窒化物半導体をスパッタ法によって成膜する際、Mgをドープして半導体薄膜を成膜する成膜工程と、該成膜工程で成膜された半導体薄膜に対して不活性ガスプラズマによる処理を行うプラズマ処理工程とを交互に繰り返して半導体薄膜を積層する方法としたので、Mgがドープされた半導体層から効果的に水素を排出させることができ、ドーパントのMgが活性化されたIII族窒化物半導体を成長させることが出来る。また、半導体層中のMgが活性化されるので、Mgのドープ量を減らすことが可能となり、この場合には、より結晶性の良好なIII族窒化物半導体が得られる。これにより、水素を排出させるためのアニール工程等の設備を必要とせず、量産性並びに再現性に優れるスパッタ法を用いて、発光特性に優れたIII族窒化物半導体発光素子を製造することが可能となる。

【0021】

また、成膜工程において、チャンバ内に水素含有ガス及び窒素含有ガスを流通させて結晶性の高いMgドープ半導体薄膜を成膜し、その後のプラズマ処理工程において、Mgドープ半導体薄膜に対して不活性ガスによるプラズマ処理を行った場合には、成膜工程を水素含有ガス雰囲気で行なうことによる優れた結晶性と、プラズマ処理工程の水素脱離効果によるMgの活性化効果の両方を得ることが可能となる。

【0022】

また、本発明のIII族窒化物半導体発光素子の製造方法によれば、p型半導体層の少なくとも一部が、上記製造方法により、MgがドープされたIII族窒化物半導体から形成する方法とされているので、結晶性の良好なIII族窒化物半導体からなるp型半導体層を備え、優れた発光特性を有するIII族窒化物半導体発光素子が得られる。

【発明を実施するための最良の形態】

【0023】

以下に、本発明に係るIII族窒化物半導体の製造方法、III族窒化物半導体発光素子の製造方法、及びIII族窒化物半導体発光素子、並びにランプの一実施形態について、図1〜6を適宜参照しながら説明する。

【0024】

[III族窒化物半導体の製造方法]

本実施形態のIII族窒化物半導体の製造方法は、チャンバ41(図5を参照)内に基板11(図1〜3を参照)及びターゲット47(図5を参照)を配置し、基板11上にMgがドープされたIII族窒化物半導体(図1に示すp型半導体層16)を反応性スパッタ法によって形成するスパッタ工程が備えられ、該スパッタ工程は、Mgをドープして半導体薄膜(図6に示す符号Aを参照)を成膜する成膜工程と、該成膜工程で成膜された半導体薄膜に対して不活性ガスプラズマによる処理を行うプラズマ処理工程の各小工程を含み、前記成膜工程と前記プラズマ処理工程とを交互に繰り返して半導体薄膜を積層することにより、III族窒化物半導体を形成する方法である。

【0025】

<半導体の積層構造>

図1は、本発明に係るIII族窒化物半導体の製造方法の一例を説明するための図であり、基板上にIII族窒化物半導体が形成された積層半導体の一例を示す概略断面図である。図1に示す積層半導体10は、基板11上にIII族窒化物化合物からなるバッファ層12が積層され、該バッファ層12上に、n型半導体層14、発光層15、及びp型半導体層16が順次積層されてなる半導体層20が形成されている。

本実施形態のp型半導体層16は、MgがドープされたIII族窒化物半導体からなり、詳細を後述する本発明のIII族窒化物半導体の製造方法によって形成されるものである。

以下、本実施形態のIII族窒化物半導体の積層構造について詳述する。

【0026】

『基板』

本実施形態において、基板11に用いることができる材料としては、III族窒化物半導体結晶が表面にエピタキシャル成長される基板材料であれば、特に限定されず、各種材料を選択して用いることができる。例えば、サファイア、SiC、シリコン、酸化亜鉛、酸化マグネシウム、酸化マンガン、酸化ジルコニウム、酸化マンガン亜鉛鉄、酸化マグネシウムアルミニウム、ホウ化ジルコニウム、酸化ガリウム、酸化インジウム、酸化リチウムガリウム、酸化リチウムアルミニウム、酸化ネオジウムガリウム、酸化ランタンストロンチウムアルミニウムタンタル、酸化ストロンチウムチタン、酸化チタン、ハフニウム、タングステン、モリブデン等が挙げられる。この中でも、サファイア、SiC等の六方晶構造を有する材料を基板に用いることが、結晶性の良好なIII族窒化物半導体を積層できる点で好ましい。

また、基板の大きさとしては、通常は直径2インチ程度のものが用いられるが、本発明のIII族窒化物半導体では、直径4〜6インチの基板を使用することも可能である。

【0027】

なお、アンモニアを使用せずにバッファ層を成膜するとともに、アンモニアを使用する方法で後述のn型半導体層を構成する下地層を成膜することにより、上記基板材料の内、高温でアンモニアに接触することで化学的な変性を引き起こすことが知られている酸化物基板や金属基板等を用いた場合には、本実施形態のバッファ層がコート層として作用するので、基板の化学的な変質を防ぐ点で効果的である。また、一般的に、スパッタ法は基板の温度を低く抑えることが可能なので、高温で分解してしまう性質を持つ材料からなる基板を用いた場合でも、基板11にダメージを与えることなく基板上への各層の成膜が可能である。

【0028】

『バッファ層』

本実施形態の積層半導体10は、基板11上に、金属原料とV族元素を含んだガスとがプラズマで活性化されて反応することにより、III族窒化物化合物からなるバッファ層12が成膜されている。本実施形態のような、プラズマ化した金属原料を用いた方法で成膜された膜は、配向が得られ易いという作用がある。

【0029】

このようなバッファ層をなすIII族窒化物化合物の結晶は、六方晶系の結晶構造を持ち、成膜条件をコントロールすることにより、単結晶膜とすることができる。また、III族窒化物化合物の結晶は、上記成膜条件をコントロールすることにより、六角柱を基本とした集合組織からなる柱状結晶とすることも可能である。なお、ここで説明する柱状結晶とは、隣接する結晶粒との間に結晶粒界を形成して隔てられており、それ自体は縦断面形状として柱状になっている結晶のことをいう。

【0030】

バッファ層12は、単結晶構造であることが、バッファ機能の面から好ましい。上述したように、III族窒化物化合物の結晶は六方晶系の結晶を有し、六角柱を基本とした組織を形成する。III族窒化物化合物の結晶は、成膜等の条件を制御することにより、面内方向にも成長した結晶を成膜することが可能となる。このような単結晶構造を有するバッファ層12を基板11上に成膜した場合、バッファ層12のバッファ機能が有効に作用するため、その上に成膜されるIII族窒化物半導体の層は、良好な配向性及び結晶性を持つ結晶膜となる。

【0031】

バッファ層12の膜厚は、20〜80nmの範囲とされていることが好ましい。バッファ層12の膜厚をこの範囲とすることにより、良好な配向性を有し、また、バッファ層12上にIII族窒化物半導体からなる各層を成膜する際に、コート層として有効に機能するバッファ層12が得られる。

バッファ層12の膜厚が20nm未満だと、上述したコート層としての機能が充分でなくなる虞がある。また、80nmを超える膜厚でバッファ層12を形成した場合、コート層としての機能には変化が無いのにも関わらず成膜処理時間が長くなり、生産性が低下する虞がある。

【0032】

バッファ層12は、Alを含有する組成とされていることが好ましく、一般式AlGaInNで表されるIII族窒化物半導体であれば、どのような材料でも用いることができる。さらに、V族として、AsやPが含有される構成としても良い。

また、バッファ層12を、Alを含んだ組成とした場合、中でも、GaAlNとすることが好ましく、この際、Alの組成が50%以上とされていることが好ましい。また、バッファ層12は、AlNからなる構成とすることがより好ましい。

【0033】

また、バッファ層12を構成する材料としては、III族窒化物半導体と同じ結晶構造を有するものであれば、どのような材料でも用いることができるが、格子の長さが後述の下地層を構成するIII族窒化物半導体に近いものが好ましく、特に周期表のIIIa族元素の窒化物が好適である。

【0034】

『半導体層』

図1に示すように、本実施形態の積層半導体10は、基板11上に、上述のようなバッファ層12を介して、III族窒化物系半導体からなり、n型半導体層14、発光層15及びp型半導体層16から構成される半導体層20が積層されてなる。また、図示例の積層半導体10は、n型半導体層14に備えられた下地層14aがバッファ層12上に積層されている。

【0035】

III族窒化物半導体としては、例えば、一般式AlXGaYInZN1−AMA(0≦X≦1、0≦Y≦1、0≦Z≦1で且つ、X+Y+Z=1。記号Mは窒素(N)とは別の第V族元素を表し、0≦A<1である。)で表わされる窒化ガリウム系化合物半導体が多数知られており、本発明においても、それら周知の窒化ガリウム系化合物半導体を含めて一般式AlXGaYInZN1−AMA(0≦X≦1、0≦Y≦1、0≦Z≦1で且つ、X+Y+Z=1。記号Mは窒素(N)とは別の第V族元素を表し、0≦A<1である。)で表わされる窒化ガリウム系化合物半導体を何ら制限なく用いることができる。

【0036】

窒化ガリウム系化合物半導体は、Al、GaおよびIn以外に他のIII族元素を含有することができ、必要に応じてGe、Si、Mg、Ca、Zn、Be、P及びAs等の元素を含有することもできる。さらに、意図的に添加した元素に限らず、成膜条件等に依存して必然的に含まれる不純物、並びに原料、反応管材質に含まれる微量不純物を含む場合もある。

【0037】

「n型半導体層」

n型半導体層14は、通常、前記バッファ層12上に積層され、下地層14a、n型コンタクト層14b及びn型クラッド層14cから構成される。なお、n型コンタクト層は、下地層、及び/又は、n型クラッド層を兼ねることが可能であるが、下地層が、n型コンタクト層、及び/又は、n型クラッド層を兼ねることも可能である。

【0038】

{下地層}

本実施形態の下地層14aはIII族窒化物半導体からなり、従来公知のMOCVD法によってバッファ層12上に積層して成膜される。

下地層14aの材料としては、必ずしも基板11上に成膜されたバッファ層12と同じである必要はなく、異なる材料を用いても構わないが、AlyGa1―yN層(0≦y≦1、好ましくは0≦y≦0.5、さらに好ましくは0≦y≦0.1)から構成されることが好ましい。

【0039】

基板上にIII族窒化物半導体からなる各層を成膜する場合、例えば、サファイアからなる基板の(0001)C面上に、スパッタ法でIII族窒化物半導体の単結晶を直接形成することは、基板とIII族窒化物半導体の格子定数の違いから困難である。そこで、本発明では、バッファ層12を形成した基板11上に、単結晶のIII族窒化物半導体からなる下地層14aを予め形成する。単結晶の下地層14aの上には、結晶性の良好なIII族窒化物半導体の単結晶層を容易にスパッタ法により形成することができるため、Mgをドープして導電性をp型に制御したIII族窒化物半導体(後述のp型半導体16)が得られやすくなる。

【0040】

下地層14aに用いる材料としては、Gaを含むIII族窒化物化合物、即ちGaN系化合物半導体が用いられ、特に、AlGaN、又はGaNを好適に用いることができる。

また、バッファ層12をAlNからなる柱状結晶の集合体として形成した場合には、下地層14aがバッファ層12の結晶性をそのまま引き継がないように、マイグレーションによって転位をループ化させる必要があるが、このような材料としても上記Gaを含むGaN系化合物半導体が挙げられ、特に、AlGaN、又はGaNが好適である。

【0041】

下地層14aの膜厚は、0.1〜8μmの範囲とすることが、結晶性の良好な下地層が得られる点で好ましく、0.1〜2μmの範囲とすることが、成膜に要する工程時間を短縮でき、生産性が向上する点でより好ましい。

【0042】

下地層14aは、必要に応じて、n型不純物が1×1017〜1×1019個/cm3の範囲内でドープされた構成としても良いが、アンドープ(<1×1017個/cm3)の構成とすることもでき、アンドープの方が良好な結晶性を維持できる点で好ましい。

基板11が導電性である場合には、下地層14aにドーパントをドープして導電性とすることにより、発光素子の上下に電極を形成することができる。一方、基板11に絶縁性の材料を用いる場合には、発光素子の同じ面に正極及び負極の各電極が設けられたチップ構造をとることになるので、下地層14aはドープしない結晶とした方が、結晶性が良好となるので好ましい。n型不純物としては、特に限定されないが、例えば、Si、GeおよびSn等が挙げられ、好ましくはSiおよびGeが挙げられる。

【0043】

{n型コンタクト層}

本実施形態のn型コンタクト層14bはIII族窒化物半導体からなり、スパッタ法によって下地層14a上に積層して成膜される。

n型コンタクト層14bとしては、下地層14aと同様にAlXGa1―XN層(0≦x≦1、好ましくは0≦x≦0.5、さらに好ましくは0≦x≦0.1)から構成されることが好ましい。また、n型不純物がドープされていることが好ましく、n型不純物を1×1017〜1×1019個/cm3、好ましくは1×1018〜1×1019個/cm3の濃度で含有すると、負極との良好なオーミック接触の維持、クラック発生の抑制、良好な結晶性の維持の点で好ましい。n型不純物としては、特に限定されないが、例えば、Si、GeおよびSn等が挙げられ、好ましくはSiおよびGeである。成長温度は下地層と同様である。また、上述したように、n型コンタクト層14bは、下地層を兼ねた構成とすることもできる。

【0044】

下地層14a及びn型コンタクト層14bを構成する窒化ガリウム系化合物半導体は同一組成であることが好ましく、これらの合計の膜厚を0.1〜20μm、好ましくは0.5〜15μm、さらに好ましくは1〜12μmの範囲に設定することが好ましい。膜厚がこの範囲であると、半導体の結晶性が良好に維持される。

【0045】

{n型クラッド層}

上述のn型コンタクト層14bと詳細を後述する発光層15との間には、n型クラッド層14cを設けることが好ましい。n型クラッド層14cを設けることにより、n型コンタクト層14bの最表面に生じた平坦性の悪化を改善することができる。n型クラッド層14cは、スパッタ法等を用いて、AlGaN、GaN、GaInN等により成膜することが可能である。また、これらの構造のヘテロ接合や複数回積層した超格子構造としてもよい。GaInNとする場合には、発光層15のGaInNのバンドギャップよりも大きくすることが望ましいことは言うまでもない。

【0046】

n型クラッド層14cの膜厚は、特に限定されないが、好ましくは5〜500nmの範囲であり、より好ましくは5〜100nmの範囲である。

また、n型クラッド層14cのn型ドープ濃度は1×1017〜1×1020個/cm3の範囲とされていることが好ましく、より好ましくは1×1018〜1×1019個/cm3の範囲である。ドープ濃度がこの範囲であると、良好な結晶性の維持および発光素子の動作電圧低減の点で好ましい。

【0047】

「p型半導体層」

p型半導体層16は、通常、p型クラッド層16a及びp型コンタクト層16bから構成され、反応性スパッタ法を用いて成膜されてなる。また、p型コンタクト層がp型クラッド層を兼ねる構成とすることもできる。

【0048】

本実施形態のp型半導体層16は、導電性をp型に制御するためのp型不純物が添加されてなる。p型不純物としては、特に限定されないが、Mgを用いることが好ましく、また、同様にZnを用いることも可能である。

また、p型半導体層16全体の膜厚としては、特に限定されないが、好ましくは0.05〜1μmの範囲である。

【0049】

{p型クラッド層}

p型クラッド層16aとしては、詳細を後述する発光層15のバンドギャップエネルギーより大きくなる組成であり、発光層15へのキャリアの閉じ込めができるものであれば特に限定されないが、好ましくは、AldGa1−dN(0<d≦0.4、好ましくは0.1≦d≦0.3)のものが挙げられる。p型クラッド層16aが、このようなAlGaNからなると、発光層15へのキャリアの閉じ込めの点で好ましい。

p型クラッド層16aの膜厚は、特に限定されないが、好ましくは1〜400nmであり、より好ましくは5〜100nmである。

【0050】

p型クラッド層16aにp型不純物を添加することによって得られるp型ドープ濃度は、1×1018〜5×1021個/cm3の範囲とされていることが好ましく、より好ましくは1×1019〜5×1020個/cm3である。p型ドープ濃度が上記範囲であると、結晶性を低下させることなく良好なp型結晶が得られる。

【0051】

{p型コンタクト層}

p型コンタクト層16bとしては、少なくともAleGa1−eN(0≦e<0.5、好ましくは0≦e≦0.2、より好ましくは0≦e≦0.1)を含んでなる窒化ガリウム系化合物半導体層である。Al組成が上記範囲であると、良好な結晶性の維持およびpオーミック電極(後述の透光性電極17を参照)との良好なオーミック接触の点で好ましい。

p型コンタクト層16bの膜厚は、特に限定されないが、10〜500nmが好ましく、より好ましくは50〜200nmである。膜厚がこの範囲であると、発光出力の点で好ましい。

【0052】

また、p型コンタクト層16bにp型不純物を添加することによって得られるp型ドープ濃度は、1×1018〜1×1021個/cm3の範囲とされていると、良好なオーミック接触の維持、クラック発生の防止、良好な結晶性の維持の点で好ましく、より好ましくは5×1019〜5×1020個/cm3の範囲である。

【0053】

「発光層」

発光層15は、n型半導体層14上に積層されるとともにp型半導体層16がその上に積層される層であり、従来公知のMOCVD法等を用いて成膜することができる。また、発光層15は、図1に示すように、窒化ガリウム系化合物半導体からなる障壁層15aと、インジウムを含有する窒化ガリウム系化合物半導体からなる井戸層15bとが交互に繰り返して積層されてなり、図示例では、n型半導体層14側及びp型半導体層16側に障壁層15aが配される順で積層して形成されている。

【0054】

障壁層15aとしては、例えば、インジウムを含有した窒化ガリウム系化合物半導体からなる井戸層15bよりもバンドギャップエネルギーが大きいAlcGa1−cN(0≦c<0.3)等の窒化ガリウム系化合物半導体を、好適に用いることができる。

また、井戸層15bには、インジウムを含有する窒化ガリウム系化合物半導体として、例えば、Ga1−sInsN(0<s<0.4)等の窒化ガリウムインジウムを用いることができる。

【0055】

また、発光層15全体の膜厚としては、特に限定されない。例えば、発光層15の膜厚は、1〜500nmの範囲であることが好ましく、100nm前後の膜厚であればより好ましい。膜厚が上記範囲であると、発光出力の向上に寄与する。

【0056】

<製造方法>

本実施形態のIII族窒化物半導体の製造方法は、上述したように、チャンバ41内に基板11及びターゲット47を配置し、基板11上にMgがドープされたIII族窒化物半導体(p型半導体層16)を反応性スパッタ法によって形成するスパッタ工程が備えられ、該スパッタ工程は、Mgをドープして半導体薄膜(図6に示す符号Aを参照)を成膜する成膜工程と、該成膜工程で成膜された半導体薄膜に対して不活性ガスプラズマによる処理を行うプラズマ処理工程の各小工程を含み、前記成膜工程と前記プラズマ処理工程とを交互に繰り返して半導体薄膜を積層することにより、III族窒化物半導体からなるp型半導体層16を形成する方法である。

【0057】

本実施形態の製造方法では、基板11上にIII族窒化物半導体結晶をエピタキシャル成長させ、図1に示すような積層半導体10を形成する際、基板11上にバッファ層12を成膜し、その上に半導体層20を形成する。本実施形態では、バッファ層12を、スパッタ法を用いて形成し、その上に、n型半導体層14の下地層14aをMOCVD法によって形成した後、n型コンタクト層14bをスパッタ法で形成し、その上のn型クラッド層14c及び発光層15の各層をMOCVD法で形成し、そして、p型半導体層16をスパッタ法で形成する方法としている。

【0058】

『バッファ層の形成』

基板11を反応器の中に導入した後、バッファ層12を形成する前に、スパッタ法等の方法を用いて前処理を行うことが望ましい。具体的には、基板11をArやN2のプラズマ中に曝す事によって表面を整えることができる。例えば、ArガスやN2ガスなどのプラズマを基板11表面に作用させることで、基板11表面に付着した有機物や酸化物を除去することができる。この場合、基板11とチャンバとの間に電圧を印加すれば、プラズマ粒子が効率的に基板11に作用する。このような前処理を基板11に施すことにより、基板11の表面11a全面にバッファ層12を成膜することができ、その上に成膜される膜の結晶性を高めることが可能となる。

また、バッファ層12を基板11上に成膜する際、基板11には湿式の前処理を行っても良い。例えば、シリコンからなる基板11に対しては、よく知られたRCA洗浄方法などを行い、表面を水素終端させておくことにより、成膜プロセスが安定する。

【0059】

基板11表面の前処理を行なった後、スパッタ装置内にアルゴン及び窒素ガスを導入し、基板11の温度を500℃程度にする。そして、基板11側に高周波バイアスを印加するとともに、金属AlからなるAlターゲット側にパワーを印加し、炉内の圧力を一定に保ちながら、基板11上にAlNからなるバッファ層12を成膜する。

【0060】

バッファ層12を基板11上に成膜する方法としては、スパッタ法の他、例えば、MOCVD法、パルスレーザーデポジション(PLD)法、パルス電子線堆積(PED)法等が挙げられ、適宜選択して用いることができるが、スパッタ法が最も簡便で量産にも適しているため、好適な方法である。なお、DCスパッタを用いる場合、ターゲット表面のチャージアップを招き、成膜速度が安定しない可能性があるので、パルスDCスパッタ法とするか、RFスパッタ法とすることが望ましい。

【0061】

『半導体層の形成』

バッファ層12上には、n型半導体層14、発光層15、p型半導体層16をこの順で積層することにより、半導体層20を形成する。本実施形態の製造方法では、上述したように、n型半導体層14の下地層14aをMOCVD法によって形成した後、n型コンタクト層14bをスパッタ法で形成し、その上のn型クラッド層14c及び発光層15の各層をMOCVD法で形成し、そして、p型半導体層16をスパッタ法で形成する。

【0062】

本実施形態において、半導体層20を形成する際の窒化ガリウム系化合物半導体の成長方法は特に限定されず、上述したスパッタ法の他、MOCVD(有機金属化学気相成長法)、HVPE(ハイドライド気相成長法)、MBE(分子線エピタキシー法)等、窒化物半導体を成長させることが知られている全ての方法を適用できる。これらの方法の内、MOCVD法では、キャリアガスとして水素(H2)または窒素(N2)、III族原料であるGa源としてトリメチルガリウム(TMG)またはトリエチルガリウム(TEG)、Al源としてトリメチルアルミニウム(TMA)またはトリエチルアルミニウム(TEA)、In源としてトリメチルインジウム(TMI)またはトリエチルインジウム(TEI)、V族原料であるN源としてアンモニア(NH3)、ヒドラジン(N2H4)などが用いられる。また、ドーパントとしては、n型にはSi原料としてモノシラン(SiH4)またはジシラン(Si2H6)を、Ge原料としてゲルマンガス(GeH4)や、テトラメチルゲルマニウム((CH3)4Ge)やテトラエチルゲルマニウム((C2H5)4Ge)等の有機ゲルマニウム化合物を利用できる。MBE法では、元素状のゲルマニウムもドーピング源として利用できる。p型にはMg原料としては、例えばビスシクロペンタジエニルマグネシウム(Cp2Mg)またはビスエチルシクロペンタジエニルマグネシウム(EtCp2Mg)を用いる。

【0063】

上述したような窒化ガリウム系化合物半導体は、Al、GaおよびIn以外に他のIII族元素を含有することができ、必要に応じてGe、Si、Mg、Ca、Zn、Be、P、及びAs等のドーパント元素を含有することができる。さらに、意図的に添加した元素に限らず、成膜条件等に依存して必然的に含まれる不純物、並びに原料、反応管材質に含まれる微量不純物を含む場合もある。

【0064】

「n型半導体層の形成」

本実施形態の半導体層20を形成する際、まず、n型半導体層14の下地層14aを、従来公知のMOCVD法により、バッファ層12上に積層して成膜する。次いで、下地層14a上に、n型コンタクト層14bをスパッタ法で成膜した後、n型クラッド層14cをMOCVD法によって成膜する。この際、下地層14a及びn型クラッド層14cの各層は、同じMOCVD炉を用いて成膜することができる。

【0065】

単結晶のIII族窒化物半導体からなる下地層14aを形成する方法としては、例えばMOCVD法により、上述のAlyGa1−yN(0≦y≦1)からなる低温バッファ層を基板11上に形成し、その上に、低温バッファ層を形成する温度より高温でMOCVD法により単結晶のGaN層を形成する方法がある。また、MOCVD法による低温バッファ層の代わりに、スパッタ法でAlyGa1−yN(0≦y≦1)からなる多結晶のバッファ層を形成し、その上に、MOCVD法によって単結晶のGaN層を形成しても良い。また、単結晶のGaN層を、スパッタ法を用いて成長させても良い。

【0066】

「発光層の形成」

n型クラッド層14c上には、発光層15を、従来公知のMOCVD法によって形成する。

本実施形態で形成する、図1に例示するような発光層15は、GaN障壁層に始まりGaN障壁層に終わる積層構造を有しており、GaNからなる6層の障壁層15aと、ノンドープのIn0.2Ga0.8Nからなる5層の井戸層15bとを交互に積層して形成する。

また、本実施形態の製造方法では、n型クラッド層14cの成膜に用いるMOCVD炉と同じものを使用することにより、従来公知のMOCVD法で発光層15を成膜することができる。

【0067】

「p型半導体層の形成」

発光層15上、つまり、発光層15の最上層となる障壁層15a上には、p型クラッド層16a及びp型コンタクト層16bからなるp型半導体層16を、スパッタ法を用いて形成する。

本実施形態では、まず、MgをドープしたAl0.1Ga0.9Nからなるp型クラッド層16aを発光層15(最上層の障壁層15a)上に形成し、さらにその上に、MgをドープしたAl0.02Ga0.98Nからなるp型コンタクト層16bを形成する。この際、p型クラッド層16a及びp型コンタクト層16bの積層には、同じスパッタ装置を用いることができる。

【0068】

{スパッタ工程}

以下、本実施形態の製造方法に備えられたスパッタ工程について、図5に例示したようなスパッタ装置40、及び図6に示すプラズマ処理模式図を適宜参照しながら詳述する。

本実施形態のスパッタ工程は、上記各条件により、図1(図3も参照)に示すようなIII族窒化物半導体からなる半導体層20の内、p型半導体層16の少なくとも一部を、反応性スパッタ法を用いて、MgがドープされたIII族窒化物半導体から形成する工程であり、Mgをドープして半導体薄膜を成膜する成膜工程と、該成膜工程で成膜された半導体薄膜に対して不活性ガスプラズマによる処理を行うプラズマ処理工程の各小工程を含み、前記成膜工程と前記プラズマ処理工程とを交互に繰り返して半導体薄膜を積層することにより、III族窒化物半導体からなるp型半導体層16を形成する方法である。

【0069】

(成膜工程)

本実施形態のスパッタ工程において小工程として備えられる成膜工程は、発光層15上に、スパッタ法により、MgがドープされたIII族窒化物半導体を成膜する工程である。本実施形態では、発光層15上、つまり、発光層15の最上層となる障壁層15a上に、p型クラッド層16a及びp型コンタクト層16bからなるp型半導体層16を従来公知のスパッタ法によって形成する。

本実施形態では、まず、MgをドープしたAl0.1Ga0.9Nからなるp型クラッド層16aを発光層15(最上層の障壁層15a)上に形成し、さらにその上に、MgをドープしたAl0.02Ga0.98Nからなるp型コンタクト層16bを形成する。

このような、スパッタ法を用いてIII族窒化物半導体からなる半導体層を形成する工程において、重要となる他のパラメータとしては、窒素原子含有ガスの分圧、成膜速度、基板温度、バイアス及びパワー等が挙げられる。

【0070】

本発明で用いられる窒素原料としては、一般に知られている窒素化合物を何ら問題なく用いることができるが、特にアンモニアと窒素は取り扱いも容易で、比較的安価で入手可能であることから好ましい。アンモニアは分解の効率も良く、高い成長速度での成膜が可能となるが、反応性や毒性が高く、除害設備やガス検知器が必要であり、また、反応装置に使用する部材の材質を化学的に安定性の高いものにする必要がある等、工夫を要する。

一方、窒素を原料として用いた場合、装置が簡便で済むものの、高い反応速度は得られない。しかしながら、窒素を電界や熱等によって分解してから装置に導入する方法では、アンモニアには劣るものの、利用可能な程度の成膜速度が得られることから、装置コストとの兼ね合いを考慮した場合、最も好適な窒素源である。

また、チャンバ41内のガス雰囲気中に水素含有ガスを流通させた場合には、半導体積層過程でのIII族窒化物半導体の表面における反応種のマイグレーションが生じやすくなり、結晶性の優れたAlGaNからなる膜を成膜することが可能となる。

【0071】

チャンバ41内のガス雰囲気中の水素ガスの割合は0.2〜50%の範囲とすることが好ましい。水素ガスの割合が0.2%未満だと、基板上において反応種のマイグレーションを活性化する作用が充分に得られず、結晶性の良好なIII族窒化物半導体を積層するのが困難になる。また、水素ガスの割合が50%を越えると、形成されたIII族窒化物半導体に取り込まれる水素が多くなり過ぎ、アクセプター不純物の活性化を阻害する要因となる虞がある。

【0072】

また、ターゲット47を効率よくスパッタするためには、さらに、アルゴン(Ar)等の重量が大きく反応性の低い不活性ガスを混入させた雰囲気とすることがより好ましい。このような場合、窒素ガス(N2)とアルゴン(Ar)の流量の比(N2/Ar)は、例えば0.25〜50の範囲とすることができる。(N2/Ar)が0.25未満だと、スパッタ原料が金属のまま付着する虞があり、(N2/Ar)が50超だと、アルゴンの量が少なすぎ、スパッタ速度が低下する。

【0073】

また、特に結晶性の良好なIII族窒化物半導体を積層するためには、チャンバ41内の雰囲気中の(N2/Ar)を0.25〜4の範囲とし、残部が不活性ガスを含有するガスとされていることが好ましい。これにより、III族原料が豊富な雰囲気中においてIII族窒化物半導体の成長を行うことができるので、より結晶性の良好なIII族窒化物半導体を成長させることが可能となる。

【0074】

上述したように、チャンバ41内のガス雰囲気中において、窒素原子含有ガス及び水素ガスを除く残部は、不活性ガスとすることが好ましい。このような不活性ガスは、ターゲットを効率よくスパッタすることを目的に用いるので、重量が大きく反応性の低いAr等を用いることが好ましい。また、ガス雰囲気中には、窒素原子含有ガス、水素ガス及び不活性ガスの働きを阻害しない範囲で、その他のガス成分を加えることも可能である。

【0075】

本実施形態の成膜工程における基板11の温度は、300℃〜1200℃の範囲とすることが好ましい。

本発明者等が鋭意実験したところ、一般に、結晶性の良好なIII族窒化物半導体からなる半導体層をスパッタ法で形成するためには、基板温度を300〜1200℃の範囲とすること好ましいことが明らかとなった。基板温度が300℃より低いと、基板面での反応種のマイグレーションが抑えられ、結晶性の良好なIII族窒化物半導体を形成するのが困難とある。また、基板温度が1200℃を超えると、形成されたIII族窒化物半導体が再分解を起こす虞がある。

【0076】

また、Mgをドープして導電性をp型に制御するためには、基板温度を600℃〜1050℃の範囲とすることがより好ましい。基板温度を600℃〜1050℃の範囲とすることで、点欠陥等の欠陥密度が少なく結晶性の良好なIII族窒化物半導体を成長させることができる。これにより、III族窒化物半導体にMgをドープして導電性をp型に制御することが可能になる。

【0077】

本実施形態のスパッタ法による成膜工程における、III族窒化物半導体からなる半導体薄膜の成膜速度は、0.01〜10nm/秒とすることが好ましい。成膜速度が10nm/秒を超えると、プラズマ処理によっても水素を排出できない虞があり、また、0.01nm/秒未満だとプロセスが無駄に長時間となり、工業生産に利用することが困難となる。

【0078】

また、成膜工程において成膜するMgがドープされた半導体薄膜の膜厚は、成膜工程による成膜処理1回あたりで1〜100nmの範囲の膜厚とすることが好ましい。そして、この膜厚で半導体薄膜を成膜する成膜工程と、詳細を後述するプラズマ処理工程とを交互に繰り返して半導体薄膜を積層することにより、最終的に所定の膜厚、例えば、最大で1000nm(1μm)程度の膜厚を有するIII族窒化物半導体(p型半導体層16)を成膜する。

本実施形態のスパッタ工程に備えられる、後述のプラズマ処理工程は、MgドープIII族窒化物半導体の結晶膜から水素を脱離させる作用を有するが、このような水素脱離効果が得られるのは結晶膜表面から10nm(0.01μm)程度の膜厚までであり、この膜厚よりもMgドープIII族窒化物半導体の膜厚が大幅に上回る場合には、本発明のドーパントMgの活性化及び結晶性向上の効果が得られ難くなる虞が有る。このため、本実施形態の成膜工程では、成膜処理1回あたりの膜厚を上記範囲として半導体薄膜を成膜し、プラズマ処理による水素離脱効果が最大限得られるような膜厚とすることにより、成膜後の結晶膜から水素を効率良く離脱させる方法としている。

【0079】

本実施形態の成膜工程において、結晶成長中の基板11表面における反応種のマイグレーションを活発にするためには、基板11側に印加されるバイアス、及びターゲット47側に印加されるパワーは大きいほうが好ましい。例えば、成膜時に基板11に印加するバイアスは1.5W/cm2以上が好ましく、また、成膜時にターゲット47に印加するパワーを1.5W/cm2〜5kW/cm2の範囲とすることが好ましい。

【0080】

本実施形態の成膜工程で成膜されるIII族窒化物半導体からなる半導体層の組成は、ターゲットに用いるIII族金属の組成を所望の値に調整することによりコントロールすることができる。例えば、GaNからなる層を形成する場合には、ターゲットにGa金属を用い、AlGaN層を形成する場合には、ターゲットにAlGa合金を用いれば良い。また、InGaNを形成する場合には、InGa合金を用いれば良い。III族窒化物半導体の組成は、ターゲット47のIII族金属の組成に応じて変化するので、ターゲット47の組成を実験的に求めることで、所望の組成のIII族窒化物半導体からなる半導体層を形成することが可能となる。

【0081】

あるいは、例えば、AlGaN層を積層する場合、ターゲットとしてGaメタルとAlメタルの両方を併置してもよい。この場合には、GaメタルターゲットとAlメタルターゲットの表面積の比を変化させることにより、積層されるAlGaN層の組成を制御することが可能となる。同様に、InGaN層を積層する場合には、GaメタルターゲットとInメタルターゲットの両方を併置しても良い。

【0082】

また、III族窒化物半導体へのMg(p型不純物)のドーピングは、III族金属とアクセプター不純物とが混合されてなる混合ターゲットを用いて行なっても良い。例えば、スパッタ法を用いてMgをドーピングしたGaNを形成する場合には、Ga金属とMgとを含有した混合ターゲットを使用する。この場合、固体のGa金属にMgが固溶した状態とし、Mgが固溶したGaメタルをターゲットに使用することにより、MgをドープしたGaNを形成することができる。また、GaメタルとMgの小片を別々に併置してターゲットに用いることも可能である。この際、ターゲットとなるGaとMgの割合を実験的に求めることにより、所望の不純物濃度のGaNを形成することができる。例えば、固体のGaにMgを固溶させてターゲットとした場合、Gaの重量に対するMgの重量の割合を1(Ga):0.05〜0.0005(Mg)の範囲とすることで、1×1018cm−3〜1×1016cm−3のキャリア濃度を有する、p型のGaN単結晶層(p型半導体層16)を成膜させることが出来る。

【0083】

なお、III族窒化物半導体へのMgのドーピング方法は、上記方法には限定されず、その他の方法を用いることも可能である。

また、上述したように、p型不純物としては、Mgのみならず、例えば亜鉛(Zn)等も同様に用いることができる。

【0084】

(プラズマ処理工程)

本実施形態のスパッタ工程に備えられるプラズマ処理工程は、上述したような成膜工程で発光層15上に成膜されたMgドープ半導体薄膜に対し、不活性ガスプラズマによる処理を行う小工程である。本実施形態のプラズマ処理工程を行なうことにより、成膜されたMgドープ半導体薄膜から効果的に水素を脱離させることができ、1×1016cm−3以下の水素濃度とすることが好ましい。

【0085】

Mgドープ半導体薄膜にプラズマ処理を施すための不活性ガスとしては、一種類のみの成分からなるガスで構成しても良いし、また、数種類の成分のガスを混合した構成のものを用いても良い。このようなプラズマ処理に用いる不活性ガスとして、例えば、He、Ne、Ar、Kr及びXeの内の何れか1種以上を用いることができる。

また、このような不活性ガスで行なうプラズマ処理は、逆スパッタ法で行うことが好適である。本実施形態のプラズマ処理工程では、基板11とチャンバとの間に電圧を印加することにより、プラズマ粒子が効率的にMgドープ半導体薄膜に作用する。

【0086】

また、本実施形態のプラズマ処理工程は、上記不活性ガスの他、さらに窒素のような、活性なプラズマ種を発生するガスを含むプラズマ中で行なうことができる。この場合には、ガス中の窒素含有量を50%以下に抑えることが、膜の変質等を防止する点で好ましい。

【0087】

本実施形態のプラズマ処理工程は、チャンバ41内で不活性ガスプラズマを発生させる際のパワーを10〜5000Wの範囲とすることが好ましい。パワー値がこの範囲であれば、Mgドープ半導体薄膜から効率的に水素を脱離させることができる。

また、本実施形態では、プラズマ処理に用いるプラズマをRF放電によって発生させることが好ましい。プラズマをRF放電によって発生させることにより、Mgドープ半導体薄膜に対して効率良くプラズマ処理を施すことができる。

【0088】

本実施形態のプラズマ処理工程は、チャンバ41内の圧力が1×10−5〜10Paの範囲であることが好ましく、0.01〜1Paの範囲であることが更に好ましい。チャンバ41内の圧力が高すぎると、プラズマ粒子の持つエネルギーが低下し、上述したような、Mgドープ半導体薄膜に対するプラズマ処理効果が低下する。また、チャンバ41内の圧力が低すぎると、プラズマ粒子の持つエネルギーが高すぎ、Mgドープ半導体薄膜に対してダメージを与えてしまうことがある。

【0089】

プラズマ処理工程の処理時間としては、1秒〜600秒(10分)の範囲であることが好ましい。処理時間が上記範囲よりも短いと、プラズマ処理による効果が得られないことは言うまでもないが、上記範囲より長い場合も特段に特性が良くなるということはなく、かえって稼働率を低下させる虞がある。

【0090】

プラズマ処理工程を行う際の温度、つまり、基板11の温度としては、室温〜800℃の範囲であることが好ましい。プラズマ処理工程における処理温度が低すぎると、プラズマ処理による水素の離脱効果が充分に得られず、また、処理温度が高すぎると、Mgドープ半導体薄膜の表面や基板にダメージを残すことがある。また、プラズマ処理工程における処理温度は、さらに好ましくは、300℃〜800℃の範囲である。

【0091】

本実施形態のプラズマ処理工程において用いるチャンバとしては、上述の成膜工程で使用するスパッタ装置40を用い、チャンバ41内の雰囲気ガスを入れ替えて使用しても良いし、あるいは、別のチャンバを用いても良い。成膜工程及びプラズマ処理工程で用いる装置を共通のスパッタ装置とすれば、製造設備をコストダウンすることができる点で好適であり、また、成膜工程とプラズマ処理工程とを交互に繰り返して行なった場合でも工程時間のロスを低減することができ、稼働率が向上する。

【0092】

本実施形態の製造方法では、上述のプラズマ処理工程を備えることにより、Mgドープ半導体薄膜(III族窒化物半導体)から、不活性ガスプラズマ処理によって効果的に水素を脱離させることが可能となる。

【0093】

図6の模式図に示すように、成膜工程によって成膜されたMgドープの半導体薄膜Aは、チャンバ内における雰囲気ガス中の水素が含まれた状態で成膜されている(図6の(a)成膜工程を参照)。そして、この半導体薄膜Aに対して不活性ガスプラズマ処理を施すことにより、半導体薄膜Aから水素が脱離し、Mgドープの半導体薄膜Bとされる(図6の(b)プラズマ処理工程を参照)。このように、Mgドープの半導体薄膜から水素が脱離することにより、ドーパントとして用いられるMgが活性化されるので、p型半導体層16を、膜中のMgが活性化された状態で成膜することが可能となる。

【0094】

また、本実施形態のプラズマ処理工程を備えた方法とすることにより、III族窒化物半導体にドープされたMgが活性化されるので、成膜されるp型半導体層16中のMgドープ量を減らした場合でも、良好なp型特性が得られる。このように、p型半導体層16中のMgドープ量を低減した場合には、より結晶性の良好なp型半導体層16を成膜することが可能となる。

【0095】

また、本実施形態のプラズマ処理工程を備えることにより、成膜工程において水素が豊富に含有されるガスを雰囲気ガスとして用いた場合でも、その後のプラズマ処理工程においてIII族窒化物半導体から効果的に水素を脱離させることができる。これにより、成膜工程において、水素含有ガス雰囲気中で結晶性の高いMgドープ半導体薄膜を成膜した後、プラズマ処理工程において水素を脱離させ、ドーパントのMgが活性化されたMgドープ半導体薄膜を成膜することができる。従って、良好なp型特性を有するとともに、結晶性に優れたp型半導体層16を成膜することが可能となる。

【0096】

従来のように、成膜後のMgドープIII族窒化物半導体(p型半導体層)をアニール処理することにより、水素を脱離させてMgを活性化させる方法では、水素を効率的に脱離させることが難しく、結晶中に含まれるMgの内の1/10〜1/5は活性化されないという問題があった。これに対し、本実施形態では、上述のようなプラズマ処理工程が備えられた方法とすることにより、III族窒化物半導体中にドープされたMgを高効率で活性化することが可能となる。

【0097】

(成膜工程とプラズマ処理工程の繰り返し)

本実施形態のスパッタ工程は、上述したような成膜工程とプラズマ処理工程とを、交互に繰り返して半導体薄膜を積層することにより、MgドープIII族窒化物半導体からなるp型半導体層16を形成する方法としている。

上述のようなプラズマ処理工程におけるプラズマ処理により、基板上に成膜されたIII族窒化物半導体中の水素を離脱させることが可能であるが、このような水素離脱効果は、III族窒化物半導体表面から10nm(0.01μm)程度の膜厚までしか得られない。例えば、10nmよりも膜厚の大きなIII族窒化物半導体層だと、その表層部付近では水素離脱効果が得られるものの、表層部から離れた膜中ではその効果が得られない。

【0098】

そこで、本実施形態のスパッタ工程では、成膜工程とプラズマ処理工程とを交互に繰り返して行なう方法とし、例えば、まず、成膜工程において、10nmの膜厚のMgドープの半導体薄膜を成膜し、これにプラズマ処理工程においてプラズマ処理を施し、水素を離脱させる。そして、さらに、上述のような成膜工程とプラズマ処理工程とを交互に繰り返して半導体薄膜を積層することにより、MgドープIII族窒化物半導体を目的の膜厚とし、p型半導体層16が得られる(図6の模式図も参照)。このように、薄い膜厚のMgドープ半導体薄膜にプラズマ処理を施して水素を効率良く離脱させ、半導体薄膜を繰り返して成膜する工程とすることにより、最終的に厚い膜厚のMgドープIII族窒化物半導体を成膜する場合であっても、半導体層全体から水素を高効率で離脱させることが可能となる。

【0099】

本実施形態のスパッタ工程では、上述したような成膜工程とプラズマ処理工程との交互の繰り返し回数を1〜1000回の範囲として行なうことが好ましい。この繰り返し回数は、目的とするMgドープIII族窒化物半導体(p型半導体層)の膜厚と、成膜工程における成膜処理1回あたりの膜厚とから、適宜、設定することが可能である。

【0100】

なお、本実施形態のスパッタ工程は、交互に繰り返して行う成膜工程とプラズマ処理工程との工程間に、1〜300秒(5分)の範囲の間隔を設ける方法とすることが好ましい。成膜工程とプラズマ処理工程との工程間に所定時間の間隔を設けることにより、例えば、成膜工程においてチャンバ41内を水素含有ガス雰囲気とした場合、チャンバ41内の水素をスパッタ工程開始前に、外部に排出させることができるので、スパッタ工程における水素離脱処理をより効果的に行うことができる。

【0101】

また、本実施形態のスパッタ工程は、交互に繰り返して行う成膜工程とプラズマ処理工程との工程間に、成膜工程又はプラズマ処理工程の少なくとも何れかの処理条件を変更する調整工程が備えられた構成とすることができる。

スパッタ工程において、上述のような調整工程を設けた場合、この調整工程を、例えば、成膜工程における処理時間又は基板の温度、或いはプラズマ処理工程におけるパワー、処理時間、基板の温度又はチャンバ内の圧力等の内、何れか1以上の処理条件を変更する工程とすることができる。このような構成とした場合には、成膜工程やプラズマ処理工程の状況に応じ、迅速且つ細やかに処理条件を変更することができ、歩留まりや生産性を向上させることが可能となる。

【0102】

本実施形態のスパッタ工程では、上記成膜工程とプラズマ処理工程の繰り返しにより、MgドープIII族窒化物半導体からなるp型半導体層16を形成する。このようなスパッタ工程で形成されるp型半導体層16は、上述したように、好ましい膜厚としては0.05〜1μmの範囲であり、また、Mg(アクセプター不純物)の好ましいドープ濃度は1×1018〜5×1021個/cm3の範囲、より好ましくは1×1019〜5×1020個/cm3の範囲ある。また、上記スパッタ工程で形成されるp型半導体層16の好ましい水素濃度は1×1016cm−3以下である。

【0103】

(スパッタ装置)

本実施形態の製造方法のように、III族窒化物半導体からなる半導体層をスパッタ法で成膜する場合、一般に、III族金属をターゲットにし、スパッタ装置のチャンバ内に窒素含有ガス(窒素ガス:N2、アンモニア:NH3等)を導入し、気相中でIII族金属と窒素を反応させる反応性スパッタ法(反応性リアクティブスパッタ法)を用いる。スパッタ法としては、RFスパッタ及びDCスパッタがあるが、本発明に係る製造方法のように反応性スパッタ法を用いた場合には、連続的に放電させるDCスパッタでは帯電が激しく、成膜速度のコントロールが困難となる。このため、本発明に係る製造方法では、RFスパッタ法、又は、DCスパッタ法の中でもパルス的にバイアスを与えることができるパルスDCスパッタを用いることが好ましく、このようなスパッタ方法で処理可能なスパッタ装置を使用することが好ましい。

【0104】

また、RFスパッタを用いた場合には、帯電を回避する方法として、マグネットの位置をターゲット内で移動させることが好ましい。具体的な運動の方法は、使用するスパッタ装置によって選択することができ、揺動させたり、回転運動させたりすることができる。

図5に例示するスパッタ装置40では、ターゲット47の下方にマグネット42が備えられ、このマグネット42がターゲット47の下方で回転運動できる構成とされている。

【0105】

スパッタによってIII族窒化物半導体からなる半導体層を形成する場合には、より高エネルギーの反応種を基板に供給することが好ましい。このため、スパッタ装置内において基板11がプラズマ中に位置するように構成し、また、ターゲット47と基板11とが対面する位置関係として構成することが好ましい。また、基板11とターゲット47との間の距離を、10〜100mmの範囲とすることが好ましい。

【0106】

また、チャンバ41内には、できるだけ不純物を残さないことが好ましいので、スパッタ装置40の到達真空度は、1.0×10−3Pa以下であることが好ましい。

【0107】

また、本実施形態の製造方法では、スパッタ工程に備えられる成膜工程及びプラズマ処理工程を、同じスパッタ装置を用いて行なう方法とすることができる。この場合には、成膜工程とプラズマ処理工程との間に所定時間の間隔を設け、この間にチャンバ47内の雰囲気ガスを入れ替えるようにしても良い。

【0108】

以上説明したような、本実施形態のIII族窒化物半導体の製造方法によれば、MgがドープされたIII族窒化物半導体からなるp型半導体層16をスパッタ法によって成膜する際、Mgをドープして半導体薄膜を成膜する成膜工程と、該成膜工程で成膜された半導体薄膜に対して不活性ガスプラズマによる処理を行うプラズマ処理工程とを交互に繰り返すことにより、III族窒化物半導体を形成する方法としたので、MgがドープされたIII族窒化物半導体から効果的に水素を排出させることができ、ドーパントのMgが活性化されたIII族窒化物半導体を成長させることが出来る。また、半導体層中のMgが活性化されるので、Mgのドープ量を減らすことが可能となり、この場合には、より結晶性の良好なIII族窒化物半導体が得られる。これにより、水素を排出させるためのアニール工程等の設備を必要とせず、量産性並びに再現性に優れるスパッタ法を用いて、発光特性に優れたIII族窒化物半導体発光素子を製造することが可能となる。

【0109】

また、成膜工程において、チャンバ41内に水素含有ガス及び窒素含有ガスを流通させて結晶性の高いMgドープ半導体薄膜を成膜し、その後のプラズマ処理工程において、Mgドープ半導体薄膜に対して不活性ガスによるプラズマ処理を行った場合には、成膜工程を水素含有ガス雰囲気で行なうことによる優れた結晶性と、プラズマ処理工程の水素脱離効果によるMgの活性化効果の両方を得ることが可能となる。

【0110】

本発明に係る、p型不純物を添加して導電性をp型に制御したIII族窒化物半導体は、詳細を後述する発光ダイオード(LED)やレーザディスク(LD)等の発光素子に備えられるp型半導体層や、トランジスタのような電子デバイス等の各種半導体素子に用いることができる。

【0111】

[III族窒化物半導体発光素子の製造方法]

本発明に係るIII族窒化物半導体発光素子の製造方法は、図3(図1も参照)に例示するようなIII族窒化物半導体から各々なるn型半導体層14、発光層15及びp型半導体層16が順に積層された半導体層20を備え、p型半導体層16の少なくとも一部がMgがドープされたIII族窒化物半導体からなる方法であり、p型半導体層16の少なくとも一部を、上述したようなIII族窒化物半導体の製造方法によって形成する方法である。

【0112】

<発光素子の積層構造>

図2及び図3は、本実施形態の発光素子の製造方法の一例を説明するための図であり、基板上にIII族窒化物半導体からなる各層が形成された積層半導体10(図1参照)を用いて発光素子1を構成した例を示す概略図で、図2は平面図、図3は断面図である。

本実施形態の発光素子1は、上記製造方法で製造された積層半導体10のp型半導体層16上に透光性正極17が積層され、その上に正極ボンディングパッド18が形成されるとともに、n型半導体層14のn型コンタクト層14bに形成された露出領域14dに負極19が積層されて概略構成される。

そして、本実施形態のp型半導体層16は、MgがドープされたIII族窒化物半導体からなり、上記製造方法によって形成されたものである。

【0113】

『透光性正極』

透光性正極17は、上述した積層半導体10のp型半導体層16(p型コンタクト層16b)上に形成される透光性の電極である。

透光性正極17の材質としては、特に限定されず、ITO(In2O3−SnO2)、AZO(ZnO−Al2O3)、IZO(In2O3−ZnO)、GZO(ZnO−Ga2O3)等の材料を、この技術分野でよく知られた慣用の手段で設けることができる。また、その構造も、従来公知の構造を含めて如何なる構造のものも何ら制限なく用いることができる。

また、透光性正極17は、Mgがドープされたp型半導体層16上のほぼ全面を覆うように形成しても構わないし、隙間を開けて格子状や樹形状に形成しても良い。

【0114】

『正極ボンディングパッド及び負極』

正極ボンディングパッド18は、上述の透光性正極17上に形成される電極である。

正極ボンディングパッド18の材料としては、Au、Al、Ni及びCu等を用いた各種構造が周知であり、これら周知の材料、構造のものを何ら制限無く用いることができる。

正極ボンディングパッド18の厚さは、100〜1000nmの範囲内であることが好ましい。また、ボンディングパッドの特性上、厚い方が、ボンダビリティーが高くなるため、正極ボンディングパッド18の厚さは300nm以上とすることがより好ましい。さらに、製造コストの観点から500nm以下とすることが好ましい。

【0115】

負極19は、基板11上に、n型半導体層14、発光層15及びp型半導体層16が順次積層された半導体層において、n型半導体層14のn型コンタクト層14bに接するように形成される。

このため、負極19を設ける際は、p型半導体層16、発光層15及びn型半導体層14の一部を除去することにより、n型コンタクト層14bの露出領域14dを形成し、この上に負極19を形成する。

負極19の材料としては、各種組成および構造の負極が周知であり、これら周知の負極を何ら制限無く用いることができ、この技術分野でよく知られた慣用の手段で設けることができる。

【0116】

<発光素子の製造方法>

以下に、図2及び図3に示すような発光素子1の製造方法の一例について説明する。

本実施形態の発光素子1の製造方法は、上記製造方法で得られた積層半導体10を用い、該積層半導体10のp型半導体層16上に透光性正極17を積層し、その上に正極ボンディングパッド18を形成するとともに、n型半導体層14のn型コンタクト層14bに形成された露出領域14dに負極19を積層する方法である。

【0117】

『透光性正極の形成』

上述のような方法により、基板11上に、バッファ層12及び半導体層が積層された積層半導体10のp型コンタクト層16b上に、ITOからなる透光性正極17を形成する。

透光性正極17の形成方法としては、特に限定されず、この技術分野でよく知られた慣用の手段で設けることができる。また、その構造も、従来公知の構造を含めて如何なる構造のものも何ら制限なく用いることができる。

【0118】

また、上述したように、透光性正極17の材料は、ITOには限定されず、AZO、IZO、GZO等の材料を用いて形成することが可能である。

また、透光性正極17を形成した後、合金化や透明化を目的とした熱アニールを施す場合もあるが、施さなくても構わない。

【0119】

『正極ボンディングパッド及び負極の形成』

積層半導体10上に形成された透光性正極17上に、さらに、正極ボンディングパッド18を形成する。

この正極ボンディングパッド18は、例えば、透光性正極17の表面側から順に、Ti、Al、Auの各材料を、従来公知の方法で積層することによって形成することができる。

【0120】

また、負極19を形成する際は、まず、基板11上に形成されたp型半導体層16、発光層15及びn型半導体層14の一部をドライエッチング等の方法によって除去することにより、n型コンタクト層14bの露出領域14dを形成する(図2及び図3参照)。そして、この露出領域14d上に、例えば、露出領域14d表面側から順に、Ni、Al、Ti、及びAuの各材料を、従来公知の方法で積層することにより、4層構造の負極19を形成することができる。

【0121】

そして、上述のようにして、積層半導体10上に、透光性正極17、正極ボンディングパッド18及び負極19を設けたウェーハを、基板11の裏面を研削及び研磨してミラー状の面とした後、例えば、350μm角の正方形に切断することにより、発光素子チップ(発光素子1)とすることができる。

【0122】

以上説明したような、本実施形態のIII族窒化物半導体発光素子の製造方法によれば、p型半導体層16の少なくとも一部が、上記製造方法により、MgドープされたIII族窒化物半導体から形成する方法とされているので、結晶性の良好なIII族窒化物半導体からなるp型半導体層16を備え、優れた発光特性を有するIII族窒化物半導体発光素子が得られる。

【0123】

[ランプ]

以上説明したような、本発明に係るIII族窒化物半導体発光素子と蛍光体とを組み合わせることにより、当業者周知の手段によってランプを構成することができる。従来より、発光素子と蛍光体と組み合わせることによって発光色を変える技術が知られており、このような技術を何ら制限されることなく採用することが可能である。

例えば、蛍光体を適正に選定することにより、発光素子より長波長の発光を得ることも可能となり、また、発光素子自体の発光波長と蛍光体によって変換された波長とを混ぜることにより、白色発光を呈するランプとすることもできる。

また、ランプとしては、一般用途の砲弾型、携帯のバックライト用途のサイドビュー型、表示器に用いられるトップビュー型等、何れの用途にも用いることができる。

【0124】

例えば、図4に示す例のように、同一面電極型のIII族窒化物半導体発光素子1を砲弾型に実装する場合には、2本のフレームの内の一方(図4ではフレーム31)に発光素子1を接着し、また、発光素子1の負極(図3に示す符号19参照)をワイヤー34でフレーム32に接合し、発光素子1の正極ボンディングパッド(図3に示す符号18参照)をワイヤー33でフレーム31に接合する。そして、透明な樹脂からなるモールド35で発光素子1の周辺をモールドすることにより、図4に示すような砲弾型のランプ3を作成することができる。

【0125】

また、本発明に係る、Mgをドープして導電性をp型に制御したIII族窒化物半導体は、上述のような発光素子の他、レーザ素子や受光素子等の光電気変換素子、又は、HBT(Heterojunction Bipolar Transistor)やHEMT(High Electron Mobility Transistor)等の電子デバイスにも用いることができる。これらの半導体素子は、各種構造のものが多数知られており、本発明に係るIII族窒化物半導体の積層構造体の素子構造は、これら周知の素子構造を含めて何ら制限されない。

【実施例】

【0126】

次に、本発明のIII族窒化物半導体の製造方法、及びIII族窒化物半導体発光素子の製造方法を、実施例によりさらに詳細に説明するが、本発明はこれらの実施例にのみ限定されるものではない。

【0127】

[実施例1]

本実施例では、サファイアからなる基板上に、スパッタ法を用いてAlNからなる単結晶のバッファ層を積層し、その上に、MOCVD法を用いて単結晶のGaNからなる下地層を積層し、さらにその上に、アクセプター不純物をドープしたp型のGaN層をスパッタ法により積層し、積層半導体サンプルを作製した。

【0128】

『バッファ層の形成』

まず、表面を鏡面研磨した直径2インチの(0001)c面サファイア基板を、フッ酸及び有機溶媒によって洗浄した後、スパッタ装置のチャンバ(図5の符号41を参照)中へ導入した。この際、スパッタ装置としては、高周波式の電源部を備え、ターゲット内でマグネットを回転させることにより、磁場の掛かる位置を動かすことができる機構を備えたものを使用した。

【0129】