III族窒化物積層基板

【課題】割れの発生を抑制することに加え、結晶性も向上させたIII族窒化物半導体を提供する。

【解決手段】シリコン基板と、該シリコン基板上に形成した歪超格子積層体と、該歪超格子積層体上に成長したIII族窒化物積層体とを具えるIII族窒化物積層基板であって、前記歪超格子積層体は、少なくとも前記シリコン基板側から順に第1超格子積層体と第2超格子積層体とを有し、前記第1超格子積層体は、AlN層とGaN層とを交互に積層してなり、前記第2超格子積層体は、AlN層とAlxGa1-xN(0<x<1)層とを交互に積層してなり、かつ前記第1超格子積層体の総厚が1μmを超えることを特徴とする。

【解決手段】シリコン基板と、該シリコン基板上に形成した歪超格子積層体と、該歪超格子積層体上に成長したIII族窒化物積層体とを具えるIII族窒化物積層基板であって、前記歪超格子積層体は、少なくとも前記シリコン基板側から順に第1超格子積層体と第2超格子積層体とを有し、前記第1超格子積層体は、AlN層とGaN層とを交互に積層してなり、前記第2超格子積層体は、AlN層とAlxGa1-xN(0<x<1)層とを交互に積層してなり、かつ前記第1超格子積層体の総厚が1μmを超えることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、III族窒化物積層基板に関し、特に、電子デバイス等に用いられるIII族窒化物積層基板に関する。

【背景技術】

【0002】

一般に、Al、Ga、InなどのIII族元素と窒素との化合物であるIII族窒化物半導体は、発光素子やHEMT等の電子デバイスに広く用いられている。このようなデバイスの特性は、III族窒化物半導体の結晶性に大きく影響されるため、結晶性の高いIII族窒化物半導体が求められている。

【0003】

III族窒化物半導体の成長用基板としては、サファイアを用いるのが一般的であったが、近年、安価で比較的放熱性が良い等の理由から、シリコン基板を用いる技術が開発されている。このようなシリコン基板は、上記サファイア基板と比較してIII族窒化物半導体との格子定数差が大きいため、結晶性の高いIII族窒化物半導体を得ることは困難であった。

【0004】

特許文献1には、シリコン基板とIII族窒化物半導体との間にAl組成の低いAlGaN層とAl組成の高いAlGaN層とを交互に積層した超格子積層体を設けることにより、表面が平坦で割れのないIII族窒化物半導体を得る技術が開示されているが、このIII族窒化物半導体の結晶性については、何ら考慮されていなかった。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2007−67077号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の目的は、III族窒化物半導体の割れの発生を抑制し、かつ結晶性の高いIII族窒化物積層基板を提供することにある。

【課題を解決するための手段】

【0007】

上記目的を達成するため、本発明の要旨構成は以下のとおりである。

(1)シリコン基板と、該シリコン基板上に形成した歪超格子積層体と、該歪超格子積層体上に成長したIII族窒化物積層体とを具えるIII族窒化物積層基板であって、

前記歪超格子積層体は、少なくとも前記シリコン基板側から順に第1超格子積層体と第2超格子積層体とを有し、前記第1超格子積層体は、AlN層とGaN層とを交互に積層してなり、前記第2超格子積層体は、AlN層とAlxGa1-xN(0<x<1)層とを交互に積層してなり、かつ前記第1超格子積層体の総厚が1μmを超えることを特徴とするIII族窒化物積層基板。

【0008】

(2)前記歪超格子積層体は、前記シリコン基板上にバッファ層を介して形成される上記(1)に記載のIII族窒化物積層基板。

【0009】

(3)前記歪超格子積層体は、前記シリコン基板上に直接形成される上記(1)に記載のIII族窒化物積層基板。

【0010】

(4)前記第1超格子積層体の前記AlN層および前記GaN層の組数は、50〜120の範囲である上記(1)、(2)または(3)に記載のIII族窒化物積層基板。

【0011】

(5)前記第2超格子積層体のAl組成比xは、0<x<0.4の範囲である上記(1)〜(4)のいずれか一に記載のIII族窒化物積層基板。

【0012】

(6)前記第2超格子積層体の前記AlN層および前記AlxGa1-xN(0<x<1)層の組数は、50〜120の範囲である上記(1)〜(5)のいずれか一に記載のIII族窒化物積層基板。

【発明の効果】

【0013】

本発明によれば、シリコン基板上に適切な歪超格子積層体を設けることにより、その上に積層するIII族窒化物半導体の割れの発生を抑制し、かつ結晶性を向上させることができる。

【図面の簡単な説明】

【0014】

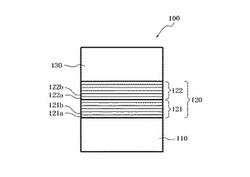

【図1】図1は、本発明に従うIII族窒化物積層基板の実施形態の模式的断面図を示す。

【図2】図2は、本発明に従うIII族窒化物積層基板の他の実施形態の模式的断面図を示す。

【図3】図3は、本発明に従うIII族窒化物積層基板の他の実施形態の模式的断面図を示す。

【図4】図4は、本発明に従うIII族窒化物積層基板の他の実施形態の模式的断面図を示す。

【発明を実施するための形態】

【0015】

次に、本発明のIII族窒化物積層基板の実施形態について図面を参照しながら説明する。図1は、本発明に従うIII族窒化物積層基板の断面構造を模式的に示したものであって、説明の便宜上、厚さ方向が誇張して描かれている。

【0016】

本発明に従うIII族窒化物積層基板100は、一例として図1に示すように、シリコン基板110と、このシリコン基板110上に形成した歪超格子積層体120と、この歪超格子積層体120上に成長したIII族窒化物積層体130とを具え、歪超格子積層体120は、少なくともシリコン基板110側から順に第1超格子積層体121と第2超格子積層体122とを有し、第1超格子積層体121は、AlN層121aとGaN層121bとを交互に積層してなり、第2超格子積層体122は、AlN層122aとAlxGa1-xN(0<x<1)層122bとを交互に積層してなり、かつ第1超格子積層体121の総厚が1μmを超えることを特徴とし、かかる構成を有することにより、III族窒化物半導体130の割れの発生を抑制し、かつ結晶性を向上させることができるものである。

【0017】

ここで、III族窒化物半導体130の結晶性とは、III族窒化物半導体130の特定の結晶面のX線ロッキングカーブの半値幅で評価されるものとする。特に、III族窒化物半導体130がGaN層の場合には、C軸方向のずれとらせん転位密度を(0004)面のロッキングカーブで評価し、A軸方向のずれと刃状転位密度を(20-24)面のロッキングカーブで評価する。

【0018】

HEMT等の縦方向に電流を流さないデバイスに対して、歪超格子積層体120は、一例として図2に示すように、シリコン基板110上にバッファ層140を介して形成することができる。シリコン基板上でIII族窒化物半導体層の結晶核生成とその後の平滑なエピタキシャル成長をしやすくするためである。このバッファ層140は、例えばAlN層、またはこのAlN層上にAlyGa1-yN(0<y<1)層を形成したものとすることができる。これはAlN層がGaとSiの反応を抑制し、いわゆるメルトバックエッチングを抑えやすくし、かつAlN層成長時の凹凸を、その上に形成したAlyGa1-yN(0<y<1)層により平滑にするためである。また、上記AlN層の厚さは、5〜200nmの範囲であるのが好ましく、上記AlyGa1-yN層の厚さは100nm以下とするのが好ましい。上記AlN層の厚さが5nm未満だと、上記メルトバックエッチングを引き起こし多結晶化するなど、デバイスの作製に供するには不適切な状態となるおそれがあり、上記AlN層の厚さが200nm超えおよび/または上記AlyGa1-yN層の厚さが100nmを超えると、反りが大きくなったり割れが発生しやすくなったりするおそれがあるためである。

【0019】

これに対し、縦方向に電流を流すデバイスに対しては、歪超格子積層体120は、シリコン基板110上に直接形成することもできる。この場合、成長面に対して垂直方向に余計な抵抗が入らないため、電流降下を抑制することができる。ただし、この場合の第1超格子積層体121の最初の層はAlN層121aとする。

【0020】

III族窒化物積層体130に割れが発生するのを抑制するため、第1超格子積層体121の総厚は1μmより大きく、第1超格子積層体121のAlN層121aおよびGaN層121bの組数は、50〜120の範囲であるのが好ましい。組数が50未満だと、割れが発生したりIII族窒化物積層体130の結晶性が悪化するおそれがあり、組数が120を超えると、積層体中の応力が大きくなることで反りが大きくなったり割れが発生するおそれがあるためである。また、上記AlN層121aの各々の厚さは4〜6nmの範囲であるのがより好ましく、GaN層121bの各々の厚さは17〜25nmの範囲であるのがより好ましい。上記AlN層121aの厚さが4nm未満および/または上記GaN層121bの厚さが17nm未満だと、積層体中の応力を十分緩和出来ないことにより転位密度の増大、すなわち結晶性の悪化となるおそれがあり、上記AlN層121aの厚さが6nm超えおよび/または上記GaN層121bの厚さが25nmを超えると、やはり積層体中の応力を十分緩和出来ずに反りが大きくなったり、積層体中に割れが入ったりするおそれがあるためである。

【0021】

また、III族窒化物積層体130に割れが発生するのを抑制するため、第2超格子積層体122のAl組成比xは、0<x<0.4の範囲であるのが好ましく、0.05<x<0.4の範囲であるのがより好ましい。Al組成比xが0だと第1超格子積層を適性組数以上積んだ場合と同じく、積層体中の応力が大きくなることで反りが大きくなったり割れが発生したりするおそれがあり、Al組成比xが0.4を超えるとやはり結晶性の悪化、反り増大につながるおそれがあるためである。

【0022】

さらに、III族窒化物積層体130に割れが発生するのを抑制するため、第2超格子積層体122のAlN層122aおよびAlxGa1-xN(0<x<1)層122bの組数は、50〜120の範囲であるのが好ましい。組数が50未満だと、積層体中の応力を十分緩和出来ないことにより転位密度の増大、すなわち結晶性の悪化となるおそれがあり、組数が120を超えると、やはり積層体中の応力を十分緩和出来ずに反りが大きくなったり、積層体中に割れが入ったりするおそれがあるためである。また、AlN層122aの各々の厚さは5〜15nmの範囲であるのがより好ましく、AlxGa1-xN(0<x<1)層122bの厚さは20〜40nmの範囲であるのがより好ましい。上記AlN層122aの厚さが5nm未満および/または上記AlxGa1-xN(0<x<1)層122bの厚さが20nm未満だと、積層体中の応力を十分緩和出来ないことにより転位密度の増大、すなわち結晶性の悪化となるおそれがあり、上記AlN層122aの厚さが15nm超えおよび/または上記AlxGa1-xN(0<x<1)層122bの厚さが40nmを超えると、やはり積層体中の応力を十分緩和出来ずに反りが大きくなったり、積層体中に割れが入ったりするおそれがあるためである。

上記の第1超格子積層体121および第2超格子積層体122の構成により、シリコン基板110とIII族窒化物積層体130との間の格子定数差、熱膨張係数差により積層内に発生する応力を、歪超格子積層体120で緩和し、転位の発生・増殖を抑えることにより、結晶性を向上させことができる。

【0023】

シリコン基板110は、用途に応じて適宜選択することができるが、GaN系の場合、GaNの高温安定層は六方晶であり、両者の格子定数からみた適合性という点で、(111)面を使用するのがより好ましい。

【0024】

また、上記第1超格子積層体121の総厚は、3μm以下であるのが好ましい。総厚が3μmを超えると、積層体中の応力を十分緩和出来ずに、III族窒化物積層体130に割れが発生するおそれがあるためである。

【0025】

歪超格子積層体120上に成長されるIII族窒化物積層体130は、GaN層であるのが好ましく、AlGaN層とすることもできる。このIII族窒化物積層体130の厚さは、0.25〜2.0μmの範囲であるのが好ましい。

【0026】

なお、III族窒化物積層体130は、図1および図2に示したように単層でもよく、また、図には示されないが、複数のIII族窒化物層を積層した積層体としてもよい。例えばGaN層の上にAlGaN層を設けた構成とすることができる。

【0027】

なお、図1および図2は、代表的な実施形態の例を示したものであって、本発明はこの実施形態に限定されるものではない。例えば、各層の間に本発明の効果に悪影響を与えない程度の中間層を挿入したり、他の超格子層を挿入したり、組成に傾斜をつけたりすることもできる。また、基盤の表面に、窒化膜、炭化膜、Al層などを形成することもできる。

【実施例】

【0028】

(実施例1)

図2に示すように、4インチのシリコン単結晶基板110(厚さ:625μm)の(111)面上に、MOCVD法を用いて、バッファ層140としてAlN層(厚さ:100nm)およびAl0.3Ga0.7N層(厚さ:3μm)を形成し、歪超格子積層体120として、第1超格子積層体121(AlN層,厚さ:5nmおよびGaN層,厚さ:20nmを120組、総厚:3μm)および第2超格子積層体122(AlN層,厚さ:10nmおよびAl0.15Ga0.85N層,厚さ:30nmを75組、総厚:3μm)を順に形成し、その上に、III族窒化物積層体としてGaN層130(厚さ:1μm)を形成してIII族窒化物積層基板100を作製した。

【0029】

(実施例2)

上記バッファ層140を形成しないこと以外は、実施例1と同様の方法によりIII族窒化物積層基板100を作製した。

【0030】

(比較例1)

歪超格子積層体120として、第2超格子積層体 (AlN層,厚さ:10nmおよびAl0.15Ga0.85N層,厚さ:30nmを75組、総厚:3μm)および第1超格子積層体 (AlN層,厚さ:5nmおよびGaN層,厚さ:20nmを120組、総厚:3μm)を順に形成したこと以外は、実施例1と同様の方法によりIII族窒化物積層基板を作製した。

【0031】

(比較例2)

歪超格子積層体120として、第1超格子積層体121(AlN層,厚さ:5nmおよびGaN層,厚さ:20nmを40組、総厚:1μm)および第2超格子積層体122(AlN層,厚さ:10nmおよびAl0.15Ga0.85N層,厚さ:30nmを125組、総厚:5μm)を順に形成したこと以外は、実施例1と同様の方法によりIII族窒化物積層基板100を作製した。

【0032】

(比較例3)

歪超格子積層体120として、第2超格子積層体122(AlN層,厚さ:10nmおよびAl0.15Ga0.85N層,厚さ:30nmを125組、総厚:5μm)および第1超格子積層体121(AlN層,厚さ:5nmおよびGaN層,厚さ:20nmを40組、総厚:1μm)を順に形成したこと以外は、実施例1と同様の方法によりIII族窒化物積層基板を作製した。

【0033】

(比較例4)

歪超格子積層体120として、第2超格子積層体(AlN層,厚さ:5nmおよびAl0.15Ga0.85N層,厚さ:20nmを240組、総厚:6μm)を形成したこと以外は、実施例1と同様の方法によりIII族窒化物積層基板を作製した。

【0034】

(結晶性評価)

上記実施例1〜2および比較例1〜4について、X線回折装置(フィリップス社製、X’Peart-MRD)を用い、歪超格子積層体上に形成したGaN層の(0004)面および(20-24)面のX線ロッキングカーブを測定した。結果を表1に示す。

【0035】

【表1】

【0036】

表1から、本発明に従う実施例1および実施例2は、(20-24)面の半値幅の値が小さく、結晶性がよいことがわかり、また、割れの発生もないことがわかる。一方、比較例2は、半値幅の値は小さく、結晶性は良いものの、割れが発生してしまっていることがわかる。

【0037】

(評価2)

図3および図4にそれぞれ示すように、上記実施例1および実施例2について、歪超格子積層体220上に、n型GaN層231、活性層232、p型AlGaN層233およびp型GaN層234を形成し、これらを一対の電極250a,250bで挟んだ発光素子を作製し、垂直方向の電流-電圧特性を調べた。

【0038】

実施例1では、注入電流:20mAでの動作電圧が7.0V、直列抵抗が100Ωであったが、実施例2では、動作電圧が4.0V、直列抵抗が30Ωとなり、実施例1に比べて実施例2では動作電圧および直列抵抗を低減することができ、電圧ドロップを抑制できることが分かる。

【産業上の利用可能性】

【0039】

本発明によれば、シリコン基板上に適切な歪超格子積層体を設けることにより、その上に積層するIII族窒化物半導体の割れの発生を抑制し、かつ結晶性を向上させることができる。

【符号の説明】

【0040】

100 III族窒化物積層基板

110 シリコン基板

120 歪超格子積層体

121 第1超格子積層体

122 第2超格子積層体

130 III族窒化物半導体

【技術分野】

【0001】

本発明は、III族窒化物積層基板に関し、特に、電子デバイス等に用いられるIII族窒化物積層基板に関する。

【背景技術】

【0002】

一般に、Al、Ga、InなどのIII族元素と窒素との化合物であるIII族窒化物半導体は、発光素子やHEMT等の電子デバイスに広く用いられている。このようなデバイスの特性は、III族窒化物半導体の結晶性に大きく影響されるため、結晶性の高いIII族窒化物半導体が求められている。

【0003】

III族窒化物半導体の成長用基板としては、サファイアを用いるのが一般的であったが、近年、安価で比較的放熱性が良い等の理由から、シリコン基板を用いる技術が開発されている。このようなシリコン基板は、上記サファイア基板と比較してIII族窒化物半導体との格子定数差が大きいため、結晶性の高いIII族窒化物半導体を得ることは困難であった。

【0004】

特許文献1には、シリコン基板とIII族窒化物半導体との間にAl組成の低いAlGaN層とAl組成の高いAlGaN層とを交互に積層した超格子積層体を設けることにより、表面が平坦で割れのないIII族窒化物半導体を得る技術が開示されているが、このIII族窒化物半導体の結晶性については、何ら考慮されていなかった。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2007−67077号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の目的は、III族窒化物半導体の割れの発生を抑制し、かつ結晶性の高いIII族窒化物積層基板を提供することにある。

【課題を解決するための手段】

【0007】

上記目的を達成するため、本発明の要旨構成は以下のとおりである。

(1)シリコン基板と、該シリコン基板上に形成した歪超格子積層体と、該歪超格子積層体上に成長したIII族窒化物積層体とを具えるIII族窒化物積層基板であって、

前記歪超格子積層体は、少なくとも前記シリコン基板側から順に第1超格子積層体と第2超格子積層体とを有し、前記第1超格子積層体は、AlN層とGaN層とを交互に積層してなり、前記第2超格子積層体は、AlN層とAlxGa1-xN(0<x<1)層とを交互に積層してなり、かつ前記第1超格子積層体の総厚が1μmを超えることを特徴とするIII族窒化物積層基板。

【0008】

(2)前記歪超格子積層体は、前記シリコン基板上にバッファ層を介して形成される上記(1)に記載のIII族窒化物積層基板。

【0009】

(3)前記歪超格子積層体は、前記シリコン基板上に直接形成される上記(1)に記載のIII族窒化物積層基板。

【0010】

(4)前記第1超格子積層体の前記AlN層および前記GaN層の組数は、50〜120の範囲である上記(1)、(2)または(3)に記載のIII族窒化物積層基板。

【0011】

(5)前記第2超格子積層体のAl組成比xは、0<x<0.4の範囲である上記(1)〜(4)のいずれか一に記載のIII族窒化物積層基板。

【0012】

(6)前記第2超格子積層体の前記AlN層および前記AlxGa1-xN(0<x<1)層の組数は、50〜120の範囲である上記(1)〜(5)のいずれか一に記載のIII族窒化物積層基板。

【発明の効果】

【0013】

本発明によれば、シリコン基板上に適切な歪超格子積層体を設けることにより、その上に積層するIII族窒化物半導体の割れの発生を抑制し、かつ結晶性を向上させることができる。

【図面の簡単な説明】

【0014】

【図1】図1は、本発明に従うIII族窒化物積層基板の実施形態の模式的断面図を示す。

【図2】図2は、本発明に従うIII族窒化物積層基板の他の実施形態の模式的断面図を示す。

【図3】図3は、本発明に従うIII族窒化物積層基板の他の実施形態の模式的断面図を示す。

【図4】図4は、本発明に従うIII族窒化物積層基板の他の実施形態の模式的断面図を示す。

【発明を実施するための形態】

【0015】

次に、本発明のIII族窒化物積層基板の実施形態について図面を参照しながら説明する。図1は、本発明に従うIII族窒化物積層基板の断面構造を模式的に示したものであって、説明の便宜上、厚さ方向が誇張して描かれている。

【0016】

本発明に従うIII族窒化物積層基板100は、一例として図1に示すように、シリコン基板110と、このシリコン基板110上に形成した歪超格子積層体120と、この歪超格子積層体120上に成長したIII族窒化物積層体130とを具え、歪超格子積層体120は、少なくともシリコン基板110側から順に第1超格子積層体121と第2超格子積層体122とを有し、第1超格子積層体121は、AlN層121aとGaN層121bとを交互に積層してなり、第2超格子積層体122は、AlN層122aとAlxGa1-xN(0<x<1)層122bとを交互に積層してなり、かつ第1超格子積層体121の総厚が1μmを超えることを特徴とし、かかる構成を有することにより、III族窒化物半導体130の割れの発生を抑制し、かつ結晶性を向上させることができるものである。

【0017】

ここで、III族窒化物半導体130の結晶性とは、III族窒化物半導体130の特定の結晶面のX線ロッキングカーブの半値幅で評価されるものとする。特に、III族窒化物半導体130がGaN層の場合には、C軸方向のずれとらせん転位密度を(0004)面のロッキングカーブで評価し、A軸方向のずれと刃状転位密度を(20-24)面のロッキングカーブで評価する。

【0018】

HEMT等の縦方向に電流を流さないデバイスに対して、歪超格子積層体120は、一例として図2に示すように、シリコン基板110上にバッファ層140を介して形成することができる。シリコン基板上でIII族窒化物半導体層の結晶核生成とその後の平滑なエピタキシャル成長をしやすくするためである。このバッファ層140は、例えばAlN層、またはこのAlN層上にAlyGa1-yN(0<y<1)層を形成したものとすることができる。これはAlN層がGaとSiの反応を抑制し、いわゆるメルトバックエッチングを抑えやすくし、かつAlN層成長時の凹凸を、その上に形成したAlyGa1-yN(0<y<1)層により平滑にするためである。また、上記AlN層の厚さは、5〜200nmの範囲であるのが好ましく、上記AlyGa1-yN層の厚さは100nm以下とするのが好ましい。上記AlN層の厚さが5nm未満だと、上記メルトバックエッチングを引き起こし多結晶化するなど、デバイスの作製に供するには不適切な状態となるおそれがあり、上記AlN層の厚さが200nm超えおよび/または上記AlyGa1-yN層の厚さが100nmを超えると、反りが大きくなったり割れが発生しやすくなったりするおそれがあるためである。

【0019】

これに対し、縦方向に電流を流すデバイスに対しては、歪超格子積層体120は、シリコン基板110上に直接形成することもできる。この場合、成長面に対して垂直方向に余計な抵抗が入らないため、電流降下を抑制することができる。ただし、この場合の第1超格子積層体121の最初の層はAlN層121aとする。

【0020】

III族窒化物積層体130に割れが発生するのを抑制するため、第1超格子積層体121の総厚は1μmより大きく、第1超格子積層体121のAlN層121aおよびGaN層121bの組数は、50〜120の範囲であるのが好ましい。組数が50未満だと、割れが発生したりIII族窒化物積層体130の結晶性が悪化するおそれがあり、組数が120を超えると、積層体中の応力が大きくなることで反りが大きくなったり割れが発生するおそれがあるためである。また、上記AlN層121aの各々の厚さは4〜6nmの範囲であるのがより好ましく、GaN層121bの各々の厚さは17〜25nmの範囲であるのがより好ましい。上記AlN層121aの厚さが4nm未満および/または上記GaN層121bの厚さが17nm未満だと、積層体中の応力を十分緩和出来ないことにより転位密度の増大、すなわち結晶性の悪化となるおそれがあり、上記AlN層121aの厚さが6nm超えおよび/または上記GaN層121bの厚さが25nmを超えると、やはり積層体中の応力を十分緩和出来ずに反りが大きくなったり、積層体中に割れが入ったりするおそれがあるためである。

【0021】

また、III族窒化物積層体130に割れが発生するのを抑制するため、第2超格子積層体122のAl組成比xは、0<x<0.4の範囲であるのが好ましく、0.05<x<0.4の範囲であるのがより好ましい。Al組成比xが0だと第1超格子積層を適性組数以上積んだ場合と同じく、積層体中の応力が大きくなることで反りが大きくなったり割れが発生したりするおそれがあり、Al組成比xが0.4を超えるとやはり結晶性の悪化、反り増大につながるおそれがあるためである。

【0022】

さらに、III族窒化物積層体130に割れが発生するのを抑制するため、第2超格子積層体122のAlN層122aおよびAlxGa1-xN(0<x<1)層122bの組数は、50〜120の範囲であるのが好ましい。組数が50未満だと、積層体中の応力を十分緩和出来ないことにより転位密度の増大、すなわち結晶性の悪化となるおそれがあり、組数が120を超えると、やはり積層体中の応力を十分緩和出来ずに反りが大きくなったり、積層体中に割れが入ったりするおそれがあるためである。また、AlN層122aの各々の厚さは5〜15nmの範囲であるのがより好ましく、AlxGa1-xN(0<x<1)層122bの厚さは20〜40nmの範囲であるのがより好ましい。上記AlN層122aの厚さが5nm未満および/または上記AlxGa1-xN(0<x<1)層122bの厚さが20nm未満だと、積層体中の応力を十分緩和出来ないことにより転位密度の増大、すなわち結晶性の悪化となるおそれがあり、上記AlN層122aの厚さが15nm超えおよび/または上記AlxGa1-xN(0<x<1)層122bの厚さが40nmを超えると、やはり積層体中の応力を十分緩和出来ずに反りが大きくなったり、積層体中に割れが入ったりするおそれがあるためである。

上記の第1超格子積層体121および第2超格子積層体122の構成により、シリコン基板110とIII族窒化物積層体130との間の格子定数差、熱膨張係数差により積層内に発生する応力を、歪超格子積層体120で緩和し、転位の発生・増殖を抑えることにより、結晶性を向上させことができる。

【0023】

シリコン基板110は、用途に応じて適宜選択することができるが、GaN系の場合、GaNの高温安定層は六方晶であり、両者の格子定数からみた適合性という点で、(111)面を使用するのがより好ましい。

【0024】

また、上記第1超格子積層体121の総厚は、3μm以下であるのが好ましい。総厚が3μmを超えると、積層体中の応力を十分緩和出来ずに、III族窒化物積層体130に割れが発生するおそれがあるためである。

【0025】

歪超格子積層体120上に成長されるIII族窒化物積層体130は、GaN層であるのが好ましく、AlGaN層とすることもできる。このIII族窒化物積層体130の厚さは、0.25〜2.0μmの範囲であるのが好ましい。

【0026】

なお、III族窒化物積層体130は、図1および図2に示したように単層でもよく、また、図には示されないが、複数のIII族窒化物層を積層した積層体としてもよい。例えばGaN層の上にAlGaN層を設けた構成とすることができる。

【0027】

なお、図1および図2は、代表的な実施形態の例を示したものであって、本発明はこの実施形態に限定されるものではない。例えば、各層の間に本発明の効果に悪影響を与えない程度の中間層を挿入したり、他の超格子層を挿入したり、組成に傾斜をつけたりすることもできる。また、基盤の表面に、窒化膜、炭化膜、Al層などを形成することもできる。

【実施例】

【0028】

(実施例1)

図2に示すように、4インチのシリコン単結晶基板110(厚さ:625μm)の(111)面上に、MOCVD法を用いて、バッファ層140としてAlN層(厚さ:100nm)およびAl0.3Ga0.7N層(厚さ:3μm)を形成し、歪超格子積層体120として、第1超格子積層体121(AlN層,厚さ:5nmおよびGaN層,厚さ:20nmを120組、総厚:3μm)および第2超格子積層体122(AlN層,厚さ:10nmおよびAl0.15Ga0.85N層,厚さ:30nmを75組、総厚:3μm)を順に形成し、その上に、III族窒化物積層体としてGaN層130(厚さ:1μm)を形成してIII族窒化物積層基板100を作製した。

【0029】

(実施例2)

上記バッファ層140を形成しないこと以外は、実施例1と同様の方法によりIII族窒化物積層基板100を作製した。

【0030】

(比較例1)

歪超格子積層体120として、第2超格子積層体 (AlN層,厚さ:10nmおよびAl0.15Ga0.85N層,厚さ:30nmを75組、総厚:3μm)および第1超格子積層体 (AlN層,厚さ:5nmおよびGaN層,厚さ:20nmを120組、総厚:3μm)を順に形成したこと以外は、実施例1と同様の方法によりIII族窒化物積層基板を作製した。

【0031】

(比較例2)

歪超格子積層体120として、第1超格子積層体121(AlN層,厚さ:5nmおよびGaN層,厚さ:20nmを40組、総厚:1μm)および第2超格子積層体122(AlN層,厚さ:10nmおよびAl0.15Ga0.85N層,厚さ:30nmを125組、総厚:5μm)を順に形成したこと以外は、実施例1と同様の方法によりIII族窒化物積層基板100を作製した。

【0032】

(比較例3)

歪超格子積層体120として、第2超格子積層体122(AlN層,厚さ:10nmおよびAl0.15Ga0.85N層,厚さ:30nmを125組、総厚:5μm)および第1超格子積層体121(AlN層,厚さ:5nmおよびGaN層,厚さ:20nmを40組、総厚:1μm)を順に形成したこと以外は、実施例1と同様の方法によりIII族窒化物積層基板を作製した。

【0033】

(比較例4)

歪超格子積層体120として、第2超格子積層体(AlN層,厚さ:5nmおよびAl0.15Ga0.85N層,厚さ:20nmを240組、総厚:6μm)を形成したこと以外は、実施例1と同様の方法によりIII族窒化物積層基板を作製した。

【0034】

(結晶性評価)

上記実施例1〜2および比較例1〜4について、X線回折装置(フィリップス社製、X’Peart-MRD)を用い、歪超格子積層体上に形成したGaN層の(0004)面および(20-24)面のX線ロッキングカーブを測定した。結果を表1に示す。

【0035】

【表1】

【0036】

表1から、本発明に従う実施例1および実施例2は、(20-24)面の半値幅の値が小さく、結晶性がよいことがわかり、また、割れの発生もないことがわかる。一方、比較例2は、半値幅の値は小さく、結晶性は良いものの、割れが発生してしまっていることがわかる。

【0037】

(評価2)

図3および図4にそれぞれ示すように、上記実施例1および実施例2について、歪超格子積層体220上に、n型GaN層231、活性層232、p型AlGaN層233およびp型GaN層234を形成し、これらを一対の電極250a,250bで挟んだ発光素子を作製し、垂直方向の電流-電圧特性を調べた。

【0038】

実施例1では、注入電流:20mAでの動作電圧が7.0V、直列抵抗が100Ωであったが、実施例2では、動作電圧が4.0V、直列抵抗が30Ωとなり、実施例1に比べて実施例2では動作電圧および直列抵抗を低減することができ、電圧ドロップを抑制できることが分かる。

【産業上の利用可能性】

【0039】

本発明によれば、シリコン基板上に適切な歪超格子積層体を設けることにより、その上に積層するIII族窒化物半導体の割れの発生を抑制し、かつ結晶性を向上させることができる。

【符号の説明】

【0040】

100 III族窒化物積層基板

110 シリコン基板

120 歪超格子積層体

121 第1超格子積層体

122 第2超格子積層体

130 III族窒化物半導体

【特許請求の範囲】

【請求項1】

シリコン基板と、該シリコン基板上に形成した歪超格子積層体と、該歪超格子積層体上に成長したIII族窒化物積層体とを具えるIII族窒化物積層基板であって、

前記歪超格子積層体は、少なくとも前記シリコン基板側から順に第1超格子積層体と第2超格子積層体とを有し、

前記第1超格子積層体は、AlN層とGaN層とを交互に積層してなり、

前記第2超格子積層体は、AlN層とAlxGa1-xN(0<x<1)層とを交互に積層してなり、かつ

前記第1超格子積層体の総厚が1μmを超えることを特徴とするIII族窒化物積層基板。

【請求項2】

前記歪超格子積層体は、前記シリコン基板上に、バッファ層を介して形成される請求項1に記載のIII族窒化物積層基板。

【請求項3】

前記歪超格子積層体は、前記シリコン基板上に、直接形成される請求項1に記載のIII族窒化物積層基板。

【請求項4】

前記第1超格子積層体のAlN層およびGaN層の組数は、50〜120の範囲である請求項1、2または3に記載のIII族窒化物積層基板。

【請求項5】

前記第2超格子積層体のAl組成比xは、0<x<0.4の範囲である請求項1〜4のいずれか一項に記載のIII族窒化物積層基板。

【請求項6】

前記第2超格子積層体のAlN層およびAlxGa1-xN(0<x<1)層の組数は、50〜120の範囲である請求項1〜5のいずれか一項に記載のIII族窒化物積層基板。

【請求項1】

シリコン基板と、該シリコン基板上に形成した歪超格子積層体と、該歪超格子積層体上に成長したIII族窒化物積層体とを具えるIII族窒化物積層基板であって、

前記歪超格子積層体は、少なくとも前記シリコン基板側から順に第1超格子積層体と第2超格子積層体とを有し、

前記第1超格子積層体は、AlN層とGaN層とを交互に積層してなり、

前記第2超格子積層体は、AlN層とAlxGa1-xN(0<x<1)層とを交互に積層してなり、かつ

前記第1超格子積層体の総厚が1μmを超えることを特徴とするIII族窒化物積層基板。

【請求項2】

前記歪超格子積層体は、前記シリコン基板上に、バッファ層を介して形成される請求項1に記載のIII族窒化物積層基板。

【請求項3】

前記歪超格子積層体は、前記シリコン基板上に、直接形成される請求項1に記載のIII族窒化物積層基板。

【請求項4】

前記第1超格子積層体のAlN層およびGaN層の組数は、50〜120の範囲である請求項1、2または3に記載のIII族窒化物積層基板。

【請求項5】

前記第2超格子積層体のAl組成比xは、0<x<0.4の範囲である請求項1〜4のいずれか一項に記載のIII族窒化物積層基板。

【請求項6】

前記第2超格子積層体のAlN層およびAlxGa1-xN(0<x<1)層の組数は、50〜120の範囲である請求項1〜5のいずれか一項に記載のIII族窒化物積層基板。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2011−100772(P2011−100772A)

【公開日】平成23年5月19日(2011.5.19)

【国際特許分類】

【出願番号】特願2009−252982(P2009−252982)

【出願日】平成21年11月4日(2009.11.4)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成20年度採択課題、文部科学省、知的クラスター創成事業「東海広域ナノテクものづくりクラスター構想」委託研究、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(506334182)DOWAエレクトロニクス株式会社 (336)

【出願人】(304021277)国立大学法人 名古屋工業大学 (784)

【Fターム(参考)】

【公開日】平成23年5月19日(2011.5.19)

【国際特許分類】

【出願日】平成21年11月4日(2009.11.4)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成20年度採択課題、文部科学省、知的クラスター創成事業「東海広域ナノテクものづくりクラスター構想」委託研究、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(506334182)DOWAエレクトロニクス株式会社 (336)

【出願人】(304021277)国立大学法人 名古屋工業大学 (784)

【Fターム(参考)】

[ Back to top ]