III族窒化物系電界効果トランジスタおよびその製造方法

【課題】オン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】本発明のIII族窒化物系電界効果トランジスタは、下地半導体層上に第1窒化物半導体層および第2窒化物半導体層が順次積層された窒化物半導体積層体と、窒化物半導体積層体の上面に接する、ソース電極およびドレイン電極と、ソース電極およびドレイン電極の間の窒化物半導体積層体における、第1窒化物半導体層の一部および第2窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域上に形成された窒化物半導体膜と、リセス領域の内壁面、および第2窒化物半導体層の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを有し、第2窒化物半導体層は、第1窒化物半導体層に比べて広い禁制帯幅を有し、窒化物半導体膜の上面は、第1窒化物半導体層の上面よりも低いことを特徴とする。

【解決手段】本発明のIII族窒化物系電界効果トランジスタは、下地半導体層上に第1窒化物半導体層および第2窒化物半導体層が順次積層された窒化物半導体積層体と、窒化物半導体積層体の上面に接する、ソース電極およびドレイン電極と、ソース電極およびドレイン電極の間の窒化物半導体積層体における、第1窒化物半導体層の一部および第2窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域上に形成された窒化物半導体膜と、リセス領域の内壁面、および第2窒化物半導体層の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを有し、第2窒化物半導体層は、第1窒化物半導体層に比べて広い禁制帯幅を有し、窒化物半導体膜の上面は、第1窒化物半導体層の上面よりも低いことを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、III族窒化物系電界効果トランジスタおよびその製造方法に関し、特に窒化物系半導体を用いたIII族窒化物系電界効果トランジスタおよびその製造方法に関する。

【背景技術】

【0002】

窒化物系半導体は、破壊電界強度、熱伝導度、および飽和電子速度の特性が高い値を有することから、窒化物系半導体を用いたIII族窒化物系電界効果トランジスタは、小型であり、かつ低オン抵抗で、しかも耐圧性に優れるという特徴を有する。このような特徴を有するIII族窒化物系電界効果トランジスタは、高効率電力変換デバイスおよび高周波パワーデバイスへの応用が期待されている。

【0003】

III族窒化物系電界効果トランジスタは、GaN層とAlGaN層とを積層して用いる。このようにGaN層とAlGaN層とを積層させることにより、これらの二層の間に自発分極およびピエゾ分極が生じる。これらの分極に起因して生じる分極電界により、ヘテロ界面に二次元電子ガス(2−DEG:2-Dimensional Electron Gas)が形成され、高い濃度のシートキャリアが発生する。これによりオン抵抗が低く、耐圧性に優れたノーマリオン型のIII族窒化物系電界効果トランジスタを作製することができる。

【0004】

一方、過電流を抑制するとともに、回路構成をシンプルなものにするという観点から、高いしきい値電圧を有するノーマリオフ型のIII族窒化物系電界効果トランジスタが望まれている。特許文献1は、III族窒化物系電界効果トランジスタにノーマリオフ動作を付与する技術が開示されている。

【0005】

特許文献1では、電子走行層と電子供給層とをリセスした上で、このリセスした領域にp型化領域を成長させることによりノーマリオフ動作を得ている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−071270号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

特許文献1では、ゲート電極にプラス電圧を印加したときに、ゲート電極下に反転層キャリアを形成させることにより、反転層キャリアと二次元電子ガスとを接続させることを以って、III族窒化物系電界効果トランジスタがオンするようになっている。

【0008】

しかし、リセス領域の側壁とゲート電極の底部(すなわちゲート電極と絶縁層との接触面)とが垂直であることから、リセス領域の側壁においてはゲート電極からの電界が均一にかからず、ゲート電極から遠ざかるほどゲート電極からの電界が弱まる。したがって、リセス領域の側壁において、ゲート電極から遠ざかるほど反転層キャリア数が少なくなり、オン抵抗が増大してしまうという問題があった。

【0009】

本発明は、このような現状に鑑みてなされたものであり、リセス領域における電子移動度が高く、かつオン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明のIII族窒化物系電界効果トランジスタは、下地半導体層と、下地半導体層上に、第1窒化物半導体層および第2窒化物半導体層が順次積層された窒化物半導体積層体と、窒化物半導体積層体の上面に接する、ソース電極およびドレイン電極と、ソース電極およびドレイン電極の間の窒化物半導体積層体における、第1窒化物半導体層の一部および第2窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域上に形成された窒化物半導体膜と、窒化物半導体膜の上面、リセス領域の内壁面、および第2窒化物半導体層の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを有し、第2窒化物半導体層は、第1窒化物半導体層に比べて広い禁制帯幅を有し、窒化物半導体膜の上面は、第1窒化物半導体層の上面よりも低いことを特徴とする。

【0011】

窒化物半導体膜は、p型窒化物半導体またはi型窒化物半導体からなることが好ましく、窒化物半導体膜に含まれる正孔濃度は、1×1017cm-3以下であることが好ましい。

【0012】

第1窒化物半導体層および窒化物半導体膜は、GaNからなることが好ましい。

窒化物半導体膜は、InxGa1-xN(0<x≦1)からなることが好ましく、その厚みは、30nm以上であることが好ましい。

【0013】

窒化物半導体積層体は、第1窒化物半導体層の第2窒化物半導体層と接する面とは反対側の面に、下地窒化物半導体層を有することが好ましい。

【0014】

また、リセス領域は、ドライエッチング工程により作製され、窒化物半導体膜は、リセス領域の内面に再成長法を用いて作製されることが好ましい。

【0015】

本発明のIII族窒化物系電界効果トランジスタの製造方法は、下地半導体層上に第1窒化物半導体層、および第2窒化物半導体層を形成する工程と、第2窒化物半導体層の一部上に選択成長マスクを形成する工程と、選択成長マスクが形成されていない領域における、第2窒化物半導体層の全部、および第1窒化物半導体層の上部を除去し、第1窒化物半導体層の一部を露出させてリセス領域を形成する工程と、リセス領域上に、窒化物半導体膜を形成する工程と、第2窒化物半導体層上の選択成長マスクを除去する工程と、窒化物半導体膜の上面、リセス領域の内壁面、および第2窒化物半導体層の上面に絶縁膜を形成する工程とを含むことを特徴とする。選択成長マスクを形成させる工程の後に、選択成長マスク上にレジストを形成する工程を含むことが好ましい。

【発明の効果】

【0016】

本発明によれば、リセス領域における電子移動度が高く、かつオン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供することができる。

【図面の簡単な説明】

【0017】

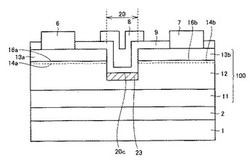

【図1】本発明のIII族窒化物系電界効果トランジスタの一例を示す模式的な断面図である。

【図2】基板上に窒化物半導体積層体を形成した後の状態を示す模式的な断面図である。

【図3】窒化物半導体積層体上に選択成長マスクを形成した後の状態を示す模式的な断面図である。

【図4】窒化物半導体積層体にリセス領域を形成した後の状態を示す模式的な断面図である。

【図5】リセス領域の内面に窒化物半導体膜を形成した後の状態を示す模式的な断面図である。

【図6】窒化物半導体膜の上面、リセス領域の内壁面、および第2窒化物半導体層の上面に絶縁膜を形成した後の状態を示す模式的な断面図である。

【図7】絶縁膜にコンタクト領域を形成した後の状態を示す模式的な断面図である。

【図8】ソース電極およびドレイン電極を形成した後の状態を示す模式的な断面図である。

【図9】比較例1のIII族窒化物系電界効果トランジスタの製造工程の一部を示す模式的な断面図である。

【図10】比較例1のIII族窒化物系電界効果トランジスタを示す模式的な断面図である。

【発明を実施するための形態】

【0018】

以下、本発明の実施の形態を図面を用いて説明する。図面や以下の記述中で示す構成は、例示であって、本発明の範囲は、図面や以下の記述中で示すものに限定されない。本願の図面において、同一の参照番号は、同一部分または相当部分を表している。また、本願の図面において、長さ、幅、厚さ等の寸法関係は図面の明瞭化と簡略化のために適宜に変更されており、実際の寸法関係を表してはいない。

【0019】

(実施の形態1)

<III族窒化物系電界効果トランジスタ>

図1は、本実施の形態のIII族窒化物系電界効果トランジスタの模式的な断面図である。本実施の形態のIII族窒化物系電界効果トランジスタは、図1に示されるように、基板1上に下地半導体層2が形成される。そして、当該下地半導体層2上に下地窒化物半導体層11、第1窒化物半導体層12、および第2窒化物半導体層13a、13bがこの順に積層される。なお、下地窒化物半導体層11、第1窒化物半導体層12、および第2窒化物半導体層13a、13bのことを窒化物半導体積層体100と呼ぶものとし、第1窒化物半導体層12と第2窒化物半導体層13a、13bとの界面のことをヘテロ接合界面16a、16bと呼ぶものとする。

【0020】

なお、図1においては、下地半導体層2および下地窒化物半導体層11が形成される場合を示しているが、下地半導体層2および下地窒化物半導体層11が形成されていなくても本発明の範囲を逸脱するものではない。

【0021】

ここで、第2窒化物半導体層13a、13bの禁制帯幅は、第1窒化物半導体層12の禁制帯幅よりも広いため、第1窒化物半導体層12と第2窒化物半導体層13aとのヘテロ接合界面16aには、正の分極電荷により第1窒化物半導体層12側に二次元電子ガス14aが発生する。同様に、第1窒化物半導体層12と第2窒化物半導体層13bとのヘテロ接合界面16bには、正の分極電荷により第1窒化物半導体層12側に二次元電子ガス14bが発生する。

【0022】

また、第2窒化物半導体層13aの上面に接するようにソース電極6を設ける。一方、第2窒化物半導体層13bの上面に接するようにドレイン電極7を設ける。ここで、ソース電極6およびドレイン電極7は、第2窒化物半導体層13a、13bにオーミックコンタクトしている。

【0023】

そして、ソース電極6およびドレイン電極7の間の窒化物半導体積層体100の一部に、第1窒化物半導体層12および第2窒化物半導体層13a、13bを形成しない領域がある。この領域のことをリセス領域20と呼ぶ。当該リセス領域20の第1窒化物半導体層12上に窒化物半導体膜23が形成される。そして、窒化物半導体膜23の上面、リセス領域20の内壁面、および第2窒化物半導体層13a、13bの上面に絶縁膜9が形成される。ここで、窒化物半導体膜23と絶縁膜9との界面(すなわち、リセス領域20の底面)のことをリセス界面20cという。そして、リセス領域20の絶縁膜9上にゲート電極8が形成される。

【0024】

本実施の形態のIII族窒化物系電界効果トランジスタは、窒化物半導体膜23の上面が、第1窒化物半導体層12の上面よりも低い位置であることを特徴とする。このように窒化物半導体膜23の上面が、第1窒化物半導体層12の上面よりも低いことにより、リセス領域20における移動度低下が抑えられることとなるため、III族窒化物系電界効果トランジスタのオン抵抗を高くなりにくくすることができる。以下においては、本実施の形態のIII族窒化物系電界効果トランジスタの動作を説明する。

【0025】

<III族窒化物系電界効果トランジスタの動作>

本実施の形態のIII族窒化物系電界効果トランジスタは、ノーマリオフ型の電界効果トランジスタである。すなわち、本実施の形態のIII族窒化物系電界効果トランジスタは、ソース電極6側の二次元電子ガス14aとドレイン電極7側の二次元電子ガス14bとがリセス領域20により分離されている。このため、ゲート電極8に電圧を印加しない状態、または0Vを印加した状態では、ソース電極6およびドレイン電極7の間に電圧を印加してもチャネルに電流が流れにくくなっている。

【0026】

一方、ゲート電極8に正の電圧を印加すると、絶縁膜9と接する第1窒化物半導体層12に電子が蓄積される。当該電子によりソース電極6側の二次元電子ガス14aとドレイン電極7側の二次元電子ガス14bとが電気的に接続される。この状態で、ソース電極6およびドレイン電極7に電圧を印加すると、チャネルに電流が流れ、オン動作が生じる。

【0027】

本実施の形態のIII族窒化物系電界効果トランジスタは、オン時におけるリセス界面20cの抵抗が低減し、損失の小さいオン動作が可能となる。これは、リセス界面20cにおける移動度の増大と反転層電子濃度の増大とに起因する。

【0028】

<基板>

本実施の形態において、基板1は、電界効果トランジスタに用いられる基板であれば、従来公知のものを用いることができる。このような基板1の材料としては、たとえばSi、GaN、SiC、AlN、GaAs、ZnO等を挙げることができる。

【0029】

<下地窒化物半導体層>

本実施の形態のIII族窒化物系電界効果トランジスタにおいて、窒化物半導体積層体100は、第1窒化物半導体層12の第2窒化物半導体層13a、13bと接する面とは反対側の面に、下地窒化物半導体層11を有することが好ましい。すなわち、基板1と第1窒化物半導体層12との間には下地窒化物半導体層11を形成することが好ましい。このような下地窒化物半導体層11としては、GaN、AlGaN、InGaN、AlInN、AlGaInN等のアンドープまたはドーピングされた窒化物半導体を用いることが好ましく、GaNよりも障壁の高いAl1-xGaxN(0<x≦1)であることがより好ましい。

【0030】

下地窒化物半導体層11は、p型窒化物半導体またはi型窒化物半導体となるように不純物をドーピングしてもよい。ここで、下地窒化物半導体層11に用いられる材料としてAlGaNを用いる場合、Alの原子数とGaの原子数との比は、特に限定されることなくいかなる比率であってもよく、たとえばアンドープAl0.05Ga0.95Nを用いることができる。

【0031】

本実施の形態において、下地窒化物半導体層11は、第1窒化物半導体層12よりもバンドギャップが大きいことが好ましい。このように第1窒化物半導体層12よりもバンドギャップが大きい下地窒化物半導体層11を設けることにより、第1窒化物半導体層12と下地窒化物半導体層11とのヘテロ接合界面に負の分極電荷を発生させることができる。そして、そのヘテロ接合界面における導電帯が不連続であることにより、電子に対して障壁を形成することができる。

【0032】

これによりオフ動作時にソース電極6とドレイン電極7との間に高いバイアス電圧を印加しても、ヘテロ接合界面16a、16bから下方に離れた領域の電子が流れる経路を遮断することができ、以ってソース電極6とドレイン電極7との間に流れるリーク電流を抑制することができる。

【0033】

<下地半導体層>

本実施の形態において、基板1と下地窒化物半導体層11との間に下地半導体層2を設けることが好ましい。このように下地半導体層2を設けることにより、基板1の結晶格子と、下地窒化物半導体層11の結晶格子との歪みを緩和することができる。なお、基板1が下地半導体層と同等の役割を示すものであれば、基板1を下地半導体層とみなして下地半導体層を形成しなくてもよい。すなわち、基板1上に直接下地窒化物半導体層11を積層させたものも本発明の範囲に含まれる。

【0034】

このような下地半導体層2は、単層または複数層のいずれであってもよい。下地半導体層2が単層である場合、その材料としてはたとえばAlN、GaN、AlGaN等を用いることができる。一方、下地半導体層2が複数層である場合、下地半導体層2にはAlN/GaN多重層、AlGaN/GaN多重層等を用いることができる。下地半導体層2は、薄いアンドープAlN層上に厚いアンドープGaN層を積層した多重層であることが好ましい。なお、「GaN/AlN」と表記する場合、上面がGaNであり、下面がAlNであることを示す。

【0035】

<窒化物半導体膜>

本実施の形態のIII族窒化物系電界効果トランジスタにおいて、窒化物半導体膜23は、リセス領域20の第1窒化物半導体層12上に形成されるものである。このように窒化物半導体膜23を形成することにより、オン時におけるリセス界面20cの抵抗が低減し、損失の小さいオン動作が可能となる。このような窒化物半導体膜23としては、GaN、AlGaN、InGaN、AlInN、AlGaInN等のアンドープまたはドーピングされた窒化物半導体を用いることが好ましく、In1-xGaxN(0<x≦1)であることがより好ましい。

【0036】

また、窒化物半導体膜23がp型窒化物半導体またはi型窒化物半導体のいずれかになるように不純物をドーピングすることがより好ましい。このように窒化物半導体膜23に不純物をドーピングすることにより、所望の閾値電圧に制御することができる。電界効果トランジスタの閾値電圧を高めるという観点から、窒化物半導体膜23は、p型窒化物半導体であることが好ましい。

【0037】

しかも、窒化物半導体膜23にp型不純物をドーピングすることにより、オフ動作時に、空乏層が窒化物半導体積層体100の上下に延びることとなり、III族窒化物系電界効果トランジスタの耐圧性を向上させることができる。

【0038】

ここで、窒化物半導体膜23をドーピングするためのp型不純物は、窒化物半導体をp型化またはi型化することができる不純物であればいかなるドーパントをも用いることができ、たとえばMg、Zn、C、Fe等を用いることができる。

【0039】

また、窒化物半導体膜23に含まれる正孔濃度は、1×1017cm-3以下であることが好ましい。このような正孔濃度にすることにより、閾値電圧を所望の値に制御できるとともに、III族窒化物系電界効果トランジスタのオフ動作時の耐圧性を向上させることができる。しかも、窒化物半導体膜23に上記の濃度で正孔を含むことにより、リセス界面20cを走行するキャリアの散乱を極力抑えることができる。

【0040】

また、窒化物半導体膜23は、その厚みが30nm以上であることが好ましい。これは、窒化物半導体膜23の厚みを30nm以上とすることにより、窒化物半導体膜23と絶縁膜9との界面に形成されるキャリアの移動が、窒化物半導体膜23と第1窒化物半導体層12との界面ラフネスに影響されにくくなり、キャリア移動度がより向上するためである。

【0041】

このような窒化物半導体膜23は、リセス領域20がドライエッチングにより形成された後に、当該リセス領域の内面に窒化物半導体膜が再成長法を用いて作製されることが好ましい。このようにして窒化物半導体膜23を形成することにより、ドライエッチングで粗くなった第1窒化物半導体層12の表面を窒化物半導体膜23で覆うことができる。窒化物半導体膜23と絶縁膜9との界面ラフネスの値は、ヘテロ接合界面16a、16bと同程度であることが好ましい。

【0042】

<第1窒化物半導体層>

本実施の形態において、第1窒化物半導体層12は、窒化物半導体膜23と同じ禁制帯幅を有することが好ましく、窒化物半導体膜23がGaNからなる場合、第1窒化物半導体層12もGaNからなることが好ましい。このような第1窒化物半導体層12としては、単層または多層の窒化物半導体のいずれであってもよい。第1窒化物半導体層12が単層の窒化物半導体からなる場合、アンドープのAlGaNまたはドーピングされたAlGaN、AlInN、AlGaInN等を用いてもよい。

【0043】

一方、第1窒化物半導体層12が多層の窒化物半導体からなる場合、Al組成比およびドーピング濃度の異なる複数のAlGaN層を含む多重AlGaN層、GaN/Al0.25Ga0.75N/AlN、GaN/AlGaN、InGaN/AlGaN、InGaN/AlGaN/AlN等を用いてもよい。なお、多層の窒化物半導体を構成する各層にはドーピングされた他の窒化物半導体を用いることもできる。

【0044】

<第2窒化物半導体層>

本実施の形態において、第2窒化物半導体層13a、13bは、第1窒化物半導体層12の禁制帯幅に比べて広い禁制帯幅を有する障壁層である。このような第2窒化物半導体層13a、13bは、多重窒化物半導体層であることが好ましく、多重窒化物半導体層を構成する各層の材料としてはGaN、AlGaN、InGaN、AlInN、AlGaInN等のアンドープまたはドーピングされた窒化物半導体等を用いることができる。第2窒化物半導体層13a、13bは、たとえば上側から順にアンドープのGaN/Al0.25Ga0.75N/AlNをそれぞれ1nm/22nm/1nmの厚みで含むものを用いることができる。

【0045】

<ソース電極、ドレイン電極>

本実施の形態において、ソース電極6およびドレイン電極7は、単層または多層の金属層により形成されることが好ましい。ソース電極6およびドレイン電極7に用いられる電極材料としては、Ti/Al、Ni/Au、Ti/Au、Pt/Au、Ni/Au、W、WNx、WSix等を挙げることができる。

【0046】

<ゲート電極>

本実施の形態において、ゲート電極8は、絶縁膜9と下地窒化物半導体層11とが接するリセス界面20cにおける電子の濃度を制御する電極である。ゲート電極8に印加するバイアス電圧を調整することにより、リセス界面20cにおける電子の濃度を制御することができ、チャネル形成を制御することができる。ゲート電極8に用いられる金属材料としては、Ti/Al、Ni/Au、Ti/Au、Pt/Au、Ni/Au、W、WNx、WSix等を挙げることができる。

【0047】

<絶縁膜>

本実施の形態において、窒化物半導体膜23の上面、リセス領域20の内壁面、および第2窒化物半導体層13a、13bの上面に絶縁膜9が形成される。このようにして形成された絶縁膜9は、単層膜に限られず多層膜とすることも可能である。すなわち絶縁膜9を単層膜で構成する場合、SiO2、SiNx、Al2O3、HfO2、ZrO2、TiO2、TaOx、MgO、Ga2O3、MgF2等を用いることができる。絶縁膜9としてSiO2を用いることにより、絶縁膜9が安定しやすくなる。また、絶縁膜9としてSiNxを用いることにより、リセス界面20cにおける電子移動度を高めることができる。

【0048】

絶縁膜9を複数膜で構成する場合、SiNx/SiO2、SiO2/SiNx、SiNx/SiO2/SiNx等の構成を用いることができる。なお、「SiO2/SiNx」と表記する場合、上面がSiO2であり、下面がSiNxであることを示す。絶縁膜9としてSiO2/SiNxからなる複数膜を用いることにより、リセス界面20cと接するSiNxによりコラプス現象を抑制しやすく、さらに高い電子移動度を得ることができ、その上層のSiO2により安定性を得ることができる。

【0049】

<リセス領域>

本実施の形態では、リセス領域20は、窒化物半導体積層体100にドライエッチングにより作製されることが好ましい。このようにして作製されたリセス領域20上に窒化物半導体膜23を形成する。なお、本実施の形態ではリセス領域20の側面は、第1窒化物半導体層12の表面に対して垂直に形成したものを示しているが、このような形態のみに限られるものではなく、リセス領域20の側面が下地窒化物半導体層11、第1窒化物半導体層12の表面に対し傾斜してもよい。

【0050】

(製造方法)

以下に本実施の形態のIII族窒化物系電界効果トランジスタの製造方法の概略を説明する。本実施の形態のIII族窒化物系電界効果トランジスタは、下地半導体層2上に第1窒化物半導体層12、および第2窒化物半導体層13を形成する工程と(図2)、第2窒化物半導体層13の一部上に選択成長マスク50を形成する工程と(図3)、選択成長マスク50が形成されていない領域における、第2窒化物半導体層13a、13bの全部、および第1窒化物半導体層12の上部を除去し、第1窒化物半導体層12の一部を露出させてリセス領域を形成する工程と(図4)、リセス領域20上に窒化物半導体膜23を形成する工程と(図5)、第2窒化物半導体層13a、13b上の選択成長マスク50を除去する工程と、窒化物半導体膜23の上面、リセス領域20の内壁面、および第2窒化物半導体層13aの上面に絶縁膜9を形成する工程と(図6)をこの順に含むことにより製造することができる。以下にこれらの各工程を詳細に説明する。

【0051】

図2は、基板上に窒化物半導体層積層体を形成した後の状態を示す模式的な断面図である。本実施の形態においては、図2に示されるように、基板1上に有機金属化学気相堆積(MOCVD:Metal Organic Chemical Vapor Deposition)法を用いて、下地半導体層2、および窒化物半導体積層体100をこの順に積層する。ここで、窒化物半導体積層体100は、下地窒化物半導体層11、第1窒化物半導体層12、および第2窒化物半導体層13がこの順に積層されたものである。

【0052】

ここで、窒化物半導体積層体100は、たとえばトリメチルガリウム(TMG:TriMethyl Gallium)、トリメチルアンモニウム(TMA)、アンモニア(NH3)を用いたMOCVD法、分子線エピタキシー(MBE:Molecular Beam Epitaxy)法、ハライド気相成長(HVPE:Hydride Vapor Phase Epitaxy)法等により形成することができる。

【0053】

図3は、第2窒化物半導体層13の一部の上に選択成長マスクおよびレジストを形成した後の基板を示す模式的な断面図である。次に、CVD法を用いて第2窒化物半導体層13上に保護膜を形成する。そして、当該保護膜の必要な部分上にレジスト51を形成した後に、保護膜の不要な部分をフォトリソグラフィ技術を用いて除去することにより、図3に示されるような選択成長マスク50を形成する。このようにして第2窒化物半導体層13上に選択成長マスク50およびレジスト51を形成する。かかるレジスト51は、剥離せずに残しておくことが好ましい。なお、選択成長マスク50は、CVD法を用いて形成する場合のみに限られるものではなく、スパッタ法等を用いて形成してもよい。

【0054】

ここで、選択成長マスク50に用いられる材料としては、SiO2、SiNx等を用いることができる他、SiO2/SiNxの2層構造のものを用いてもよい。ここで、選択成長マスク50としてSiO2および/またはSiNxを用いた場合、フッ酸またはフッ化アンモニウムで希釈したフッ酸等により保護膜として不要な部分を容易にエッチングで除去することができる。

【0055】

図4は、窒化物半導体積層体にリセス領域を形成した後の状態を示す模式的な断面図である。次に、図4に示されるように、第2窒化物半導体層13上のうちの選択成長マスク50が形成されていない部分の窒化物半導体積層体100の一部をエッチングで除去することにより、窒化物半導体積層体100にリセス領域20を形成する。

【0056】

本実施の形態では、第2窒化物半導体層13の全てと第1窒化物半導体層12の上部とをエッチングで除去することにより、リセス領域20を形成する。ここで、エッチングで除去する第1窒化物半導体層12の厚みをT1とする。このT1は第1窒化物半導体層12の厚み以下の厚みであればいかなる厚みであっても良い。そして、当該リセス領域20を形成した後に、レジスト51を除去する。

【0057】

図5は、リセス領域内の第1窒化物半導体層の上面に窒化物半導体膜を形成した後の状態を示す模式的な断面図である。本実施の形態では、図5に示されるように、リセス領域20の内面に位置する第1窒化物半導体層12の上面に対し、MOCVD法を用いて再成長を行なうことにより窒化物半導体膜23を形成する。ここで、窒化物半導体膜23の上面が、第1窒化物半導体層12の上面を超えないように、厚さT2の窒化物半導体膜23を形成することを特徴とする。すなわち、上記の第1窒化物半導体層12のエッチング深さT1と、窒化物半導体膜23の厚みT2との関係は、0<T2<T1を満たす範囲であればよい。

【0058】

上記で窒化物半導体膜23を形成した後に、選択成長マスク50を除去する。次に、窒化物半導体膜23の上面、リセス領域20の内壁面、および第2窒化物半導体層13a、13bの上面を硫酸/過酸化水素水で洗浄し、さらに塩酸/過酸化水素水で洗浄する。

【0059】

図6は、窒化物半導体膜の上面、リセス領域の内壁面、および第2窒化物半導体層の上面に絶縁膜を形成した後の状態を示す模式的な断面図である。本実施の形態では、図6に示されるように、リセス領域20の内面および第2窒化物半導体層13a、13bの上面に対し、CVD法を用いて絶縁膜9を形成する。

【0060】

このようにして絶縁膜9を形成したときに、第1窒化物半導体層12と、絶縁膜9とが接する界面をリセス界面20cと呼ぶものとする。このリセス界面20cがドライエッチングでダメージを受けていないことにより、リセス界面20cでの高い移動度を得ることができ、オン時におけるリセス界面20cの抵抗を低減させることができる。

【0061】

図7は、絶縁膜にコンタクト領域を形成した後の状態を示す模式的な断面図である。図7に示されるように、第2窒化物半導体層13a、13bの上面のうちのソース電極およびドレイン電極が形成される部分の絶縁膜9を、フォトリソグラフィ技術により除去し、コンタクト領域25を形成する。そして、窒素雰囲気の下で400℃〜1100℃でアニールを行なうことにより、絶縁膜9と窒化物半導体積層体100とが接する面の界面準位を低減させることができる。

【0062】

図8は、ソース電極およびドレイン電極を形成した後の状態を示す模式的な断面図である。上記のアニールを行なった後、図8に示されるように、第2窒化物半導体層13a、13b上の絶縁膜9を除去したコンタクト領域上に、フォトリソグラフィ技術とEB蒸着法とを用いてソース電極6およびドレイン電極7を形成する。

【0063】

そして、熱処理による合金化によりソース電極6およびドレイン電極7と、チャネルとをオーミックコンタクトさせる。なお、オーミックコンタクトを得る方法としては、熱処理による合金化する方法のみに限られるものではなく、トンネル電流機構によりオーミックコンタクトを形成する方法、コンタクト領域25にSi等のn型不純物をイオン注入等により高濃度にドーピングした上で、当該コンタクト領域25にソース電極6およびドレイン電極7を形成する方法等を用いることができる。

【0064】

次に、フォトリソグラフィ技術とEB蒸着法とを用いることにより、絶縁膜上にNi/Auからなるゲート電極8を形成する。以上の各工程により、図1に示されるように、本実施の形態のIII族窒化物系電界効果トランジスタを作製することができる。

【0065】

従来のIII族窒化物系電界効果トランジスタは、第2窒化物半導体層および第1窒化物半導体層の一部をドライエッチングにより除去して、リセス領域を形成していた。このためリセス界面における第1窒化物半導体層がドライエッチングによりダメージ損傷を受けることもあり、第1窒化物半導体層の表面ラフネスが大きいこともあった。その結果、第1窒化物半導体層と絶縁膜との界面において移動度低下が起こり、III族窒化物系電界効果トランジスタのオン抵抗が高くなるという問題があった。

【0066】

本実施の形態のIII族窒化物系電界効果トランジスタにおいては、ドライエッチングによりダメージ損傷を受けた領域を窒化物半導体膜23で覆うことができる。これにより、リセス領域における窒化物半導体膜の移動度が低下することなく、III族窒化物系電界効果トランジスタのオン抵抗を高くなりにくくすることができる。

【0067】

(実施の形態2)

本実施の形態のIII族窒化物系電界効果トランジスタは、実施の形態1の窒化物半導体膜としてp型窒化物半導体を用いる他は、実施の形態1と同様の構成のIII族窒化物系電界効果トランジスタである。

【0068】

(製造方法)

本実施の形態のIII族窒化物系電界効果トランジスタの製造方法は、窒化物半導体膜23としてp型窒化物半導体を形成することが異なる他は、実施の形態1と同様の製造方法により、III族窒化物系電界効果トランジスタを作製する。

【0069】

このようにp型窒化物半導体からなる窒化物半導体膜23を用いることにより、閾値電圧を向上させることができ、p型濃度により閾値電圧を制御することができる。

【0070】

また、窒化物半導体膜23に含まれるp型ドーパントを活性化させるためのアニールを行なうことが好ましい。このようにアニールを行なうことにより窒化物半導体膜23に含まれるp型ドーパントを活性化させることにより、閾値電圧を向上させることができる。

【0071】

(実施の形態3)

本実施の形態のIII族窒化物系電界効果トランジスタは、窒化物半導体膜23の禁制帯幅が第1窒化物半導体層12の禁制帯幅よりも小さいことを特徴とする。このように第1窒化物半導体層12の禁制帯幅よりも小さい窒化物半導体膜23を用いることにより、p型化の活性化率が上昇し、より少ないp型不純物の濃度でより高いp型キャリア濃度を得ることができる。

【0072】

なお、上記のような第1窒化物半導体層12の組成比、厚み、およびキャリア濃度によっては、窒化物半導体膜23と第1窒化物半導体層12とのヘテロ接合界面にキャリアが形成される可能性があるものの、III族窒化物系電界効果トランジスタの全体のキャリア濃度が増大するのでより好ましい。

【0073】

(製造方法)

本実施の形態のIII族窒化物系電界効果トランジスタの製造方法は、第1窒化物半導体層12の禁制帯幅よりも小さい窒化物半導体膜23を形成することが異なる他は、実施の形態1と同様の製造方法により、III族窒化物系電界効果トランジスタを作製する。

【実施例1】

【0074】

以下のように、実施例1のIII族窒化物系電界効果トランジスタを作製する。

本実施例においては、まず、Siからなる基板1を準備する。そして、図2に示されるように、当該基板1上に、有機金属化学気相堆積(MOCVD:Metal Organic Chemical Vapor Deposition)法を用いて、薄いアンドープAlN層および厚いアンドープGaNの多重窒化物半導体層からなる下地半導体層2と、窒化物半導体積層体100とを積層する。当該窒化物半導体積層体100は、厚さ1000nmのアンドープAl0.05Ga0.95Nからなる下地窒化物半導体層11と、厚さ100nmのアンドープGaN層からなる第1窒化物半導体層12と、上から順に厚さがそれぞれ1nm/22nm/1nmのアンドープGaN/Al0.25Ga0.75N/AlNという3層構造からなる第2窒化物半導体層13とをこの順に積層したものである。

【0075】

次に、CVD法を用いて、第2窒化物半導体層13上にSiO2膜を形成する。そして、SiO2膜上にレジスト51を形成し、フォトリソグラフィ技術を用いてリセス領域となる部分のSiO2膜を除去する。そして、図3に示されるように、SiO2膜のうちの除去されなかった部分が選択成長マスク50となる。なお、フォトリソグラフィ技術を用いて作製したレジスト51は剥離することなく残している。

【0076】

次に、図4に示されるように、選択成長マスク50が形成されずに第2窒化物半導体層13が露出している部分に対し、誘導結合プラズマ(ICP:Inductively coupled plasma)エッチング装置を用いて第2窒化物半導体層13、および第1窒化物半導体層12のうちの上部の厚みT1(T1は50nm)を除去することにより、リセス領域20を形成し、その後レジスト51を除去する。

【0077】

次に、図5に示されるように、選択成長マスク50が形成されずに第1窒化物半導体層12が露出している領域上に、MOCVD法を用いて厚みT2(T2は30nm)のアンドープGaNからなる窒化物半導体膜23を再成長により形成する。そして、選択成長マスク50を除去する。

【0078】

次に、窒化物半導体膜23の上面、リセス領域20の内壁面、および第2窒化物半導体層13a、13bの上面を硫酸/過酸化水素水で洗浄し、さらに塩酸/過酸化水素水で洗浄する。そして、図6に示されるように、リセス領域20の内面および第2窒化物半導体層13a、13bの上面に対し、CVD法を用いて厚さ30nmのSiO2からなる絶縁膜9を形成する。

【0079】

そして、図7に示されるように、第2窒化物半導体層13a、13bの上面のうちのソース電極およびドレイン電極が形成される部分の絶縁膜9をフォトリソグラフィ技術により除去し、コンタクト領域25を作製する。そして、窒素雰囲気の下で1000度でアニールを行なうことにより、絶縁膜9と窒化物半導体積層体100との接する面の界面準位を低減させる。

【0080】

その後、図8に示されるように、第2窒化物半導体層13a、13bのコンタクト領域25に、フォトリソグラフィ技術とEB蒸着法とを用いてTi/Alからなるソース電極6、およびソース電極6と同一組成のドレイン電極7を形成する。そして、真空雰囲気で800℃、1分間熱処理を行なうことにより、ソース電極6およびドレイン電極7を二次元電子ガス14a、14bとオーミックコンタクトさせる。

【0081】

次に、フォトリソグラフィ技術とEB蒸着法とを用いることにより、絶縁膜9上にNi/Auからなるゲート電極8を形成する。以上の工程により、本実施例のIII族窒化物系電界効果トランジスタを作製する。

【0082】

上記のようにして作製する実施例1のIII族窒化物系電界効果トランジスタにおいて、リセス界面20cと接する窒化物半導体膜23は、ドライエッチングによるダメージがないため、リセス界面20cにおいて高い移動度が得られ、オン時におけるリセス界面20cの抵抗を低下させることができる。これは、リセス界面20cにおける移動度の増大と、反転層電子濃度の増大に起因するものと考えられる。

【実施例2】

【0083】

本実施例は、実施例1のIII族窒化物系電界効果トランジスタの窒化物半導体膜23として1×1019cm-3の濃度でMgがドーピングされたp型GaN層を用いる他は、実施例1と同一の構成のIII族窒化物系電界効果トランジスタである。p型GaNからなる下地窒化物半導体層11には、p型不純物のMgが1×1019cm-3の濃度でドーピングされているが、GaN中ではMgの活性化率が低いのでp型GaNの正孔濃度は1×1017cm-3になる。

【0084】

(製造方法)

本実施例のIII族窒化物系電界効果トランジスタは、窒化物半導体膜23として、1×1019cm-3の濃度でMgがドーピングされたp型GaN層を形成すること、および絶縁膜を形成する前にp型ドーパントを活性化させるためのアニールをすることを除いては、実施例1と同様の製造方法によりIII族窒化物系電界効果トランジスタを製造する。

【実施例3】

【0085】

実施例3は、実施例1のIII族窒化物系電界効果トランジスタの窒化物半導体膜23として1×1018cm-3の濃度でMgがドーピングされたp型In0.1Ga0.9Nを用いる他は、実施例1と同一の構成のIII族窒化物系電界効果トランジスタである。ここで、下地窒化物半導体層に含まれる正孔濃度は、1×1017cm-3である。これにより下地窒化物半導体層11のp型化の活性化率が上昇し、より少ないp型不純物の濃度で同程度のp型キャリア濃度を得ることができる。

【0086】

(製造方法)

本実施例のIII族窒化物系電界効果トランジスタは、窒化物半導体膜として、1×1018cm-3の濃度でMgがドーピングされたp型In0.1Ga0.9N層を形成したこと、および第2窒化物半導体層13a、13bを形成した後にp型ドーパントを活性化させるためのアニールをすることを除いては、実施例1と同様の製造方法によりIII族窒化物系電界効果トランジスタを製造する。

【0087】

(比較例1)

比較例1は、実施例1のIII族窒化物系電界効果トランジスタにおいて、窒化物半導体膜23を形成しないこと以外は、実施例1と同一の構成のIII族窒化物系電界効果トランジスタである。よって、比較例1のIII族窒化物系電界効果トランジスタの製造方法は、実施例1のリセス領域を形成する工程(図4)までは同一であるので、この工程以降を説明する。

【0088】

図9は、リセス領域の内面、および第2窒化物半導体層上に絶縁膜を形成した後の状態を示す模式的な断面図である。本比較例では、図9に示されるように、エッチングによりリセス領域を形成した後に、窒化物半導体膜を形成せずに絶縁膜9を形成する。

【0089】

図10は、比較例1のIII族窒化物系電界効果トランジスタを示す模式的な断面図である。上記のように絶縁膜9を形成した後は、実施例1と同様の方法により、図10に示されるIII族窒化物系電界効果トランジスタを作製する。

【0090】

比較例1のIII族窒化物系電界効果トランジスタは、エッチングによりリセス領域20を形成後に絶縁膜を形成しているため、リセス界面20cと接する絶縁膜9の界面に、ドライエッチングによるダメージがある。このため、リセス界面において移動度低下が生じることとなり、III族窒化物系電界効果トランジスタのオン抵抗は高い値となる。

【0091】

以上の説明からも明らかなように、実施例1〜3の本発明に係るIII族窒化物系電界効果トランジスタは、比較例1のIII族窒化物系電界効果トランジスタに比し、オン抵抗が低下していることが明らかである。このことから、ドライエッチングによりIII族窒化物系電界効果トランジスタのリセス領域を形成した後に、リセス領域上に窒化物半導体膜を形成することにより、そのオン抵抗を低下させることができることが明らかとなる。

【0092】

以上のように本発明の実施の形態および実施例について説明を行なったが、上述の各実施の形態および実施例の構成を適宜組み合わせることも当初から予定している。

【0093】

今回開示された実施の形態および実施例はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0094】

1 基板、2 下地半導体層、6 ソース電極、7 ドレイン電極、8 ゲート電極、9 絶縁膜、11 下地窒化物半導体層、12 第1窒化物半導体層、13,13a,13b 第2窒化物半導体層、14a,14b 二次元電子ガス、16a,16b ヘテロ接合界面、20 リセス領域、20c リセス界面、23 窒化物半導体膜、25 コンタクト領域、50 選択成長マスク、100 窒化物半導体積層体。

【技術分野】

【0001】

本発明は、III族窒化物系電界効果トランジスタおよびその製造方法に関し、特に窒化物系半導体を用いたIII族窒化物系電界効果トランジスタおよびその製造方法に関する。

【背景技術】

【0002】

窒化物系半導体は、破壊電界強度、熱伝導度、および飽和電子速度の特性が高い値を有することから、窒化物系半導体を用いたIII族窒化物系電界効果トランジスタは、小型であり、かつ低オン抵抗で、しかも耐圧性に優れるという特徴を有する。このような特徴を有するIII族窒化物系電界効果トランジスタは、高効率電力変換デバイスおよび高周波パワーデバイスへの応用が期待されている。

【0003】

III族窒化物系電界効果トランジスタは、GaN層とAlGaN層とを積層して用いる。このようにGaN層とAlGaN層とを積層させることにより、これらの二層の間に自発分極およびピエゾ分極が生じる。これらの分極に起因して生じる分極電界により、ヘテロ界面に二次元電子ガス(2−DEG:2-Dimensional Electron Gas)が形成され、高い濃度のシートキャリアが発生する。これによりオン抵抗が低く、耐圧性に優れたノーマリオン型のIII族窒化物系電界効果トランジスタを作製することができる。

【0004】

一方、過電流を抑制するとともに、回路構成をシンプルなものにするという観点から、高いしきい値電圧を有するノーマリオフ型のIII族窒化物系電界効果トランジスタが望まれている。特許文献1は、III族窒化物系電界効果トランジスタにノーマリオフ動作を付与する技術が開示されている。

【0005】

特許文献1では、電子走行層と電子供給層とをリセスした上で、このリセスした領域にp型化領域を成長させることによりノーマリオフ動作を得ている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−071270号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

特許文献1では、ゲート電極にプラス電圧を印加したときに、ゲート電極下に反転層キャリアを形成させることにより、反転層キャリアと二次元電子ガスとを接続させることを以って、III族窒化物系電界効果トランジスタがオンするようになっている。

【0008】

しかし、リセス領域の側壁とゲート電極の底部(すなわちゲート電極と絶縁層との接触面)とが垂直であることから、リセス領域の側壁においてはゲート電極からの電界が均一にかからず、ゲート電極から遠ざかるほどゲート電極からの電界が弱まる。したがって、リセス領域の側壁において、ゲート電極から遠ざかるほど反転層キャリア数が少なくなり、オン抵抗が増大してしまうという問題があった。

【0009】

本発明は、このような現状に鑑みてなされたものであり、リセス領域における電子移動度が高く、かつオン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明のIII族窒化物系電界効果トランジスタは、下地半導体層と、下地半導体層上に、第1窒化物半導体層および第2窒化物半導体層が順次積層された窒化物半導体積層体と、窒化物半導体積層体の上面に接する、ソース電極およびドレイン電極と、ソース電極およびドレイン電極の間の窒化物半導体積層体における、第1窒化物半導体層の一部および第2窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域上に形成された窒化物半導体膜と、窒化物半導体膜の上面、リセス領域の内壁面、および第2窒化物半導体層の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを有し、第2窒化物半導体層は、第1窒化物半導体層に比べて広い禁制帯幅を有し、窒化物半導体膜の上面は、第1窒化物半導体層の上面よりも低いことを特徴とする。

【0011】

窒化物半導体膜は、p型窒化物半導体またはi型窒化物半導体からなることが好ましく、窒化物半導体膜に含まれる正孔濃度は、1×1017cm-3以下であることが好ましい。

【0012】

第1窒化物半導体層および窒化物半導体膜は、GaNからなることが好ましい。

窒化物半導体膜は、InxGa1-xN(0<x≦1)からなることが好ましく、その厚みは、30nm以上であることが好ましい。

【0013】

窒化物半導体積層体は、第1窒化物半導体層の第2窒化物半導体層と接する面とは反対側の面に、下地窒化物半導体層を有することが好ましい。

【0014】

また、リセス領域は、ドライエッチング工程により作製され、窒化物半導体膜は、リセス領域の内面に再成長法を用いて作製されることが好ましい。

【0015】

本発明のIII族窒化物系電界効果トランジスタの製造方法は、下地半導体層上に第1窒化物半導体層、および第2窒化物半導体層を形成する工程と、第2窒化物半導体層の一部上に選択成長マスクを形成する工程と、選択成長マスクが形成されていない領域における、第2窒化物半導体層の全部、および第1窒化物半導体層の上部を除去し、第1窒化物半導体層の一部を露出させてリセス領域を形成する工程と、リセス領域上に、窒化物半導体膜を形成する工程と、第2窒化物半導体層上の選択成長マスクを除去する工程と、窒化物半導体膜の上面、リセス領域の内壁面、および第2窒化物半導体層の上面に絶縁膜を形成する工程とを含むことを特徴とする。選択成長マスクを形成させる工程の後に、選択成長マスク上にレジストを形成する工程を含むことが好ましい。

【発明の効果】

【0016】

本発明によれば、リセス領域における電子移動度が高く、かつオン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供することができる。

【図面の簡単な説明】

【0017】

【図1】本発明のIII族窒化物系電界効果トランジスタの一例を示す模式的な断面図である。

【図2】基板上に窒化物半導体積層体を形成した後の状態を示す模式的な断面図である。

【図3】窒化物半導体積層体上に選択成長マスクを形成した後の状態を示す模式的な断面図である。

【図4】窒化物半導体積層体にリセス領域を形成した後の状態を示す模式的な断面図である。

【図5】リセス領域の内面に窒化物半導体膜を形成した後の状態を示す模式的な断面図である。

【図6】窒化物半導体膜の上面、リセス領域の内壁面、および第2窒化物半導体層の上面に絶縁膜を形成した後の状態を示す模式的な断面図である。

【図7】絶縁膜にコンタクト領域を形成した後の状態を示す模式的な断面図である。

【図8】ソース電極およびドレイン電極を形成した後の状態を示す模式的な断面図である。

【図9】比較例1のIII族窒化物系電界効果トランジスタの製造工程の一部を示す模式的な断面図である。

【図10】比較例1のIII族窒化物系電界効果トランジスタを示す模式的な断面図である。

【発明を実施するための形態】

【0018】

以下、本発明の実施の形態を図面を用いて説明する。図面や以下の記述中で示す構成は、例示であって、本発明の範囲は、図面や以下の記述中で示すものに限定されない。本願の図面において、同一の参照番号は、同一部分または相当部分を表している。また、本願の図面において、長さ、幅、厚さ等の寸法関係は図面の明瞭化と簡略化のために適宜に変更されており、実際の寸法関係を表してはいない。

【0019】

(実施の形態1)

<III族窒化物系電界効果トランジスタ>

図1は、本実施の形態のIII族窒化物系電界効果トランジスタの模式的な断面図である。本実施の形態のIII族窒化物系電界効果トランジスタは、図1に示されるように、基板1上に下地半導体層2が形成される。そして、当該下地半導体層2上に下地窒化物半導体層11、第1窒化物半導体層12、および第2窒化物半導体層13a、13bがこの順に積層される。なお、下地窒化物半導体層11、第1窒化物半導体層12、および第2窒化物半導体層13a、13bのことを窒化物半導体積層体100と呼ぶものとし、第1窒化物半導体層12と第2窒化物半導体層13a、13bとの界面のことをヘテロ接合界面16a、16bと呼ぶものとする。

【0020】

なお、図1においては、下地半導体層2および下地窒化物半導体層11が形成される場合を示しているが、下地半導体層2および下地窒化物半導体層11が形成されていなくても本発明の範囲を逸脱するものではない。

【0021】

ここで、第2窒化物半導体層13a、13bの禁制帯幅は、第1窒化物半導体層12の禁制帯幅よりも広いため、第1窒化物半導体層12と第2窒化物半導体層13aとのヘテロ接合界面16aには、正の分極電荷により第1窒化物半導体層12側に二次元電子ガス14aが発生する。同様に、第1窒化物半導体層12と第2窒化物半導体層13bとのヘテロ接合界面16bには、正の分極電荷により第1窒化物半導体層12側に二次元電子ガス14bが発生する。

【0022】

また、第2窒化物半導体層13aの上面に接するようにソース電極6を設ける。一方、第2窒化物半導体層13bの上面に接するようにドレイン電極7を設ける。ここで、ソース電極6およびドレイン電極7は、第2窒化物半導体層13a、13bにオーミックコンタクトしている。

【0023】

そして、ソース電極6およびドレイン電極7の間の窒化物半導体積層体100の一部に、第1窒化物半導体層12および第2窒化物半導体層13a、13bを形成しない領域がある。この領域のことをリセス領域20と呼ぶ。当該リセス領域20の第1窒化物半導体層12上に窒化物半導体膜23が形成される。そして、窒化物半導体膜23の上面、リセス領域20の内壁面、および第2窒化物半導体層13a、13bの上面に絶縁膜9が形成される。ここで、窒化物半導体膜23と絶縁膜9との界面(すなわち、リセス領域20の底面)のことをリセス界面20cという。そして、リセス領域20の絶縁膜9上にゲート電極8が形成される。

【0024】

本実施の形態のIII族窒化物系電界効果トランジスタは、窒化物半導体膜23の上面が、第1窒化物半導体層12の上面よりも低い位置であることを特徴とする。このように窒化物半導体膜23の上面が、第1窒化物半導体層12の上面よりも低いことにより、リセス領域20における移動度低下が抑えられることとなるため、III族窒化物系電界効果トランジスタのオン抵抗を高くなりにくくすることができる。以下においては、本実施の形態のIII族窒化物系電界効果トランジスタの動作を説明する。

【0025】

<III族窒化物系電界効果トランジスタの動作>

本実施の形態のIII族窒化物系電界効果トランジスタは、ノーマリオフ型の電界効果トランジスタである。すなわち、本実施の形態のIII族窒化物系電界効果トランジスタは、ソース電極6側の二次元電子ガス14aとドレイン電極7側の二次元電子ガス14bとがリセス領域20により分離されている。このため、ゲート電極8に電圧を印加しない状態、または0Vを印加した状態では、ソース電極6およびドレイン電極7の間に電圧を印加してもチャネルに電流が流れにくくなっている。

【0026】

一方、ゲート電極8に正の電圧を印加すると、絶縁膜9と接する第1窒化物半導体層12に電子が蓄積される。当該電子によりソース電極6側の二次元電子ガス14aとドレイン電極7側の二次元電子ガス14bとが電気的に接続される。この状態で、ソース電極6およびドレイン電極7に電圧を印加すると、チャネルに電流が流れ、オン動作が生じる。

【0027】

本実施の形態のIII族窒化物系電界効果トランジスタは、オン時におけるリセス界面20cの抵抗が低減し、損失の小さいオン動作が可能となる。これは、リセス界面20cにおける移動度の増大と反転層電子濃度の増大とに起因する。

【0028】

<基板>

本実施の形態において、基板1は、電界効果トランジスタに用いられる基板であれば、従来公知のものを用いることができる。このような基板1の材料としては、たとえばSi、GaN、SiC、AlN、GaAs、ZnO等を挙げることができる。

【0029】

<下地窒化物半導体層>

本実施の形態のIII族窒化物系電界効果トランジスタにおいて、窒化物半導体積層体100は、第1窒化物半導体層12の第2窒化物半導体層13a、13bと接する面とは反対側の面に、下地窒化物半導体層11を有することが好ましい。すなわち、基板1と第1窒化物半導体層12との間には下地窒化物半導体層11を形成することが好ましい。このような下地窒化物半導体層11としては、GaN、AlGaN、InGaN、AlInN、AlGaInN等のアンドープまたはドーピングされた窒化物半導体を用いることが好ましく、GaNよりも障壁の高いAl1-xGaxN(0<x≦1)であることがより好ましい。

【0030】

下地窒化物半導体層11は、p型窒化物半導体またはi型窒化物半導体となるように不純物をドーピングしてもよい。ここで、下地窒化物半導体層11に用いられる材料としてAlGaNを用いる場合、Alの原子数とGaの原子数との比は、特に限定されることなくいかなる比率であってもよく、たとえばアンドープAl0.05Ga0.95Nを用いることができる。

【0031】

本実施の形態において、下地窒化物半導体層11は、第1窒化物半導体層12よりもバンドギャップが大きいことが好ましい。このように第1窒化物半導体層12よりもバンドギャップが大きい下地窒化物半導体層11を設けることにより、第1窒化物半導体層12と下地窒化物半導体層11とのヘテロ接合界面に負の分極電荷を発生させることができる。そして、そのヘテロ接合界面における導電帯が不連続であることにより、電子に対して障壁を形成することができる。

【0032】

これによりオフ動作時にソース電極6とドレイン電極7との間に高いバイアス電圧を印加しても、ヘテロ接合界面16a、16bから下方に離れた領域の電子が流れる経路を遮断することができ、以ってソース電極6とドレイン電極7との間に流れるリーク電流を抑制することができる。

【0033】

<下地半導体層>

本実施の形態において、基板1と下地窒化物半導体層11との間に下地半導体層2を設けることが好ましい。このように下地半導体層2を設けることにより、基板1の結晶格子と、下地窒化物半導体層11の結晶格子との歪みを緩和することができる。なお、基板1が下地半導体層と同等の役割を示すものであれば、基板1を下地半導体層とみなして下地半導体層を形成しなくてもよい。すなわち、基板1上に直接下地窒化物半導体層11を積層させたものも本発明の範囲に含まれる。

【0034】

このような下地半導体層2は、単層または複数層のいずれであってもよい。下地半導体層2が単層である場合、その材料としてはたとえばAlN、GaN、AlGaN等を用いることができる。一方、下地半導体層2が複数層である場合、下地半導体層2にはAlN/GaN多重層、AlGaN/GaN多重層等を用いることができる。下地半導体層2は、薄いアンドープAlN層上に厚いアンドープGaN層を積層した多重層であることが好ましい。なお、「GaN/AlN」と表記する場合、上面がGaNであり、下面がAlNであることを示す。

【0035】

<窒化物半導体膜>

本実施の形態のIII族窒化物系電界効果トランジスタにおいて、窒化物半導体膜23は、リセス領域20の第1窒化物半導体層12上に形成されるものである。このように窒化物半導体膜23を形成することにより、オン時におけるリセス界面20cの抵抗が低減し、損失の小さいオン動作が可能となる。このような窒化物半導体膜23としては、GaN、AlGaN、InGaN、AlInN、AlGaInN等のアンドープまたはドーピングされた窒化物半導体を用いることが好ましく、In1-xGaxN(0<x≦1)であることがより好ましい。

【0036】

また、窒化物半導体膜23がp型窒化物半導体またはi型窒化物半導体のいずれかになるように不純物をドーピングすることがより好ましい。このように窒化物半導体膜23に不純物をドーピングすることにより、所望の閾値電圧に制御することができる。電界効果トランジスタの閾値電圧を高めるという観点から、窒化物半導体膜23は、p型窒化物半導体であることが好ましい。

【0037】

しかも、窒化物半導体膜23にp型不純物をドーピングすることにより、オフ動作時に、空乏層が窒化物半導体積層体100の上下に延びることとなり、III族窒化物系電界効果トランジスタの耐圧性を向上させることができる。

【0038】

ここで、窒化物半導体膜23をドーピングするためのp型不純物は、窒化物半導体をp型化またはi型化することができる不純物であればいかなるドーパントをも用いることができ、たとえばMg、Zn、C、Fe等を用いることができる。

【0039】

また、窒化物半導体膜23に含まれる正孔濃度は、1×1017cm-3以下であることが好ましい。このような正孔濃度にすることにより、閾値電圧を所望の値に制御できるとともに、III族窒化物系電界効果トランジスタのオフ動作時の耐圧性を向上させることができる。しかも、窒化物半導体膜23に上記の濃度で正孔を含むことにより、リセス界面20cを走行するキャリアの散乱を極力抑えることができる。

【0040】

また、窒化物半導体膜23は、その厚みが30nm以上であることが好ましい。これは、窒化物半導体膜23の厚みを30nm以上とすることにより、窒化物半導体膜23と絶縁膜9との界面に形成されるキャリアの移動が、窒化物半導体膜23と第1窒化物半導体層12との界面ラフネスに影響されにくくなり、キャリア移動度がより向上するためである。

【0041】

このような窒化物半導体膜23は、リセス領域20がドライエッチングにより形成された後に、当該リセス領域の内面に窒化物半導体膜が再成長法を用いて作製されることが好ましい。このようにして窒化物半導体膜23を形成することにより、ドライエッチングで粗くなった第1窒化物半導体層12の表面を窒化物半導体膜23で覆うことができる。窒化物半導体膜23と絶縁膜9との界面ラフネスの値は、ヘテロ接合界面16a、16bと同程度であることが好ましい。

【0042】

<第1窒化物半導体層>

本実施の形態において、第1窒化物半導体層12は、窒化物半導体膜23と同じ禁制帯幅を有することが好ましく、窒化物半導体膜23がGaNからなる場合、第1窒化物半導体層12もGaNからなることが好ましい。このような第1窒化物半導体層12としては、単層または多層の窒化物半導体のいずれであってもよい。第1窒化物半導体層12が単層の窒化物半導体からなる場合、アンドープのAlGaNまたはドーピングされたAlGaN、AlInN、AlGaInN等を用いてもよい。

【0043】

一方、第1窒化物半導体層12が多層の窒化物半導体からなる場合、Al組成比およびドーピング濃度の異なる複数のAlGaN層を含む多重AlGaN層、GaN/Al0.25Ga0.75N/AlN、GaN/AlGaN、InGaN/AlGaN、InGaN/AlGaN/AlN等を用いてもよい。なお、多層の窒化物半導体を構成する各層にはドーピングされた他の窒化物半導体を用いることもできる。

【0044】

<第2窒化物半導体層>

本実施の形態において、第2窒化物半導体層13a、13bは、第1窒化物半導体層12の禁制帯幅に比べて広い禁制帯幅を有する障壁層である。このような第2窒化物半導体層13a、13bは、多重窒化物半導体層であることが好ましく、多重窒化物半導体層を構成する各層の材料としてはGaN、AlGaN、InGaN、AlInN、AlGaInN等のアンドープまたはドーピングされた窒化物半導体等を用いることができる。第2窒化物半導体層13a、13bは、たとえば上側から順にアンドープのGaN/Al0.25Ga0.75N/AlNをそれぞれ1nm/22nm/1nmの厚みで含むものを用いることができる。

【0045】

<ソース電極、ドレイン電極>

本実施の形態において、ソース電極6およびドレイン電極7は、単層または多層の金属層により形成されることが好ましい。ソース電極6およびドレイン電極7に用いられる電極材料としては、Ti/Al、Ni/Au、Ti/Au、Pt/Au、Ni/Au、W、WNx、WSix等を挙げることができる。

【0046】

<ゲート電極>

本実施の形態において、ゲート電極8は、絶縁膜9と下地窒化物半導体層11とが接するリセス界面20cにおける電子の濃度を制御する電極である。ゲート電極8に印加するバイアス電圧を調整することにより、リセス界面20cにおける電子の濃度を制御することができ、チャネル形成を制御することができる。ゲート電極8に用いられる金属材料としては、Ti/Al、Ni/Au、Ti/Au、Pt/Au、Ni/Au、W、WNx、WSix等を挙げることができる。

【0047】

<絶縁膜>

本実施の形態において、窒化物半導体膜23の上面、リセス領域20の内壁面、および第2窒化物半導体層13a、13bの上面に絶縁膜9が形成される。このようにして形成された絶縁膜9は、単層膜に限られず多層膜とすることも可能である。すなわち絶縁膜9を単層膜で構成する場合、SiO2、SiNx、Al2O3、HfO2、ZrO2、TiO2、TaOx、MgO、Ga2O3、MgF2等を用いることができる。絶縁膜9としてSiO2を用いることにより、絶縁膜9が安定しやすくなる。また、絶縁膜9としてSiNxを用いることにより、リセス界面20cにおける電子移動度を高めることができる。

【0048】

絶縁膜9を複数膜で構成する場合、SiNx/SiO2、SiO2/SiNx、SiNx/SiO2/SiNx等の構成を用いることができる。なお、「SiO2/SiNx」と表記する場合、上面がSiO2であり、下面がSiNxであることを示す。絶縁膜9としてSiO2/SiNxからなる複数膜を用いることにより、リセス界面20cと接するSiNxによりコラプス現象を抑制しやすく、さらに高い電子移動度を得ることができ、その上層のSiO2により安定性を得ることができる。

【0049】

<リセス領域>

本実施の形態では、リセス領域20は、窒化物半導体積層体100にドライエッチングにより作製されることが好ましい。このようにして作製されたリセス領域20上に窒化物半導体膜23を形成する。なお、本実施の形態ではリセス領域20の側面は、第1窒化物半導体層12の表面に対して垂直に形成したものを示しているが、このような形態のみに限られるものではなく、リセス領域20の側面が下地窒化物半導体層11、第1窒化物半導体層12の表面に対し傾斜してもよい。

【0050】

(製造方法)

以下に本実施の形態のIII族窒化物系電界効果トランジスタの製造方法の概略を説明する。本実施の形態のIII族窒化物系電界効果トランジスタは、下地半導体層2上に第1窒化物半導体層12、および第2窒化物半導体層13を形成する工程と(図2)、第2窒化物半導体層13の一部上に選択成長マスク50を形成する工程と(図3)、選択成長マスク50が形成されていない領域における、第2窒化物半導体層13a、13bの全部、および第1窒化物半導体層12の上部を除去し、第1窒化物半導体層12の一部を露出させてリセス領域を形成する工程と(図4)、リセス領域20上に窒化物半導体膜23を形成する工程と(図5)、第2窒化物半導体層13a、13b上の選択成長マスク50を除去する工程と、窒化物半導体膜23の上面、リセス領域20の内壁面、および第2窒化物半導体層13aの上面に絶縁膜9を形成する工程と(図6)をこの順に含むことにより製造することができる。以下にこれらの各工程を詳細に説明する。

【0051】

図2は、基板上に窒化物半導体層積層体を形成した後の状態を示す模式的な断面図である。本実施の形態においては、図2に示されるように、基板1上に有機金属化学気相堆積(MOCVD:Metal Organic Chemical Vapor Deposition)法を用いて、下地半導体層2、および窒化物半導体積層体100をこの順に積層する。ここで、窒化物半導体積層体100は、下地窒化物半導体層11、第1窒化物半導体層12、および第2窒化物半導体層13がこの順に積層されたものである。

【0052】

ここで、窒化物半導体積層体100は、たとえばトリメチルガリウム(TMG:TriMethyl Gallium)、トリメチルアンモニウム(TMA)、アンモニア(NH3)を用いたMOCVD法、分子線エピタキシー(MBE:Molecular Beam Epitaxy)法、ハライド気相成長(HVPE:Hydride Vapor Phase Epitaxy)法等により形成することができる。

【0053】

図3は、第2窒化物半導体層13の一部の上に選択成長マスクおよびレジストを形成した後の基板を示す模式的な断面図である。次に、CVD法を用いて第2窒化物半導体層13上に保護膜を形成する。そして、当該保護膜の必要な部分上にレジスト51を形成した後に、保護膜の不要な部分をフォトリソグラフィ技術を用いて除去することにより、図3に示されるような選択成長マスク50を形成する。このようにして第2窒化物半導体層13上に選択成長マスク50およびレジスト51を形成する。かかるレジスト51は、剥離せずに残しておくことが好ましい。なお、選択成長マスク50は、CVD法を用いて形成する場合のみに限られるものではなく、スパッタ法等を用いて形成してもよい。

【0054】

ここで、選択成長マスク50に用いられる材料としては、SiO2、SiNx等を用いることができる他、SiO2/SiNxの2層構造のものを用いてもよい。ここで、選択成長マスク50としてSiO2および/またはSiNxを用いた場合、フッ酸またはフッ化アンモニウムで希釈したフッ酸等により保護膜として不要な部分を容易にエッチングで除去することができる。

【0055】

図4は、窒化物半導体積層体にリセス領域を形成した後の状態を示す模式的な断面図である。次に、図4に示されるように、第2窒化物半導体層13上のうちの選択成長マスク50が形成されていない部分の窒化物半導体積層体100の一部をエッチングで除去することにより、窒化物半導体積層体100にリセス領域20を形成する。

【0056】

本実施の形態では、第2窒化物半導体層13の全てと第1窒化物半導体層12の上部とをエッチングで除去することにより、リセス領域20を形成する。ここで、エッチングで除去する第1窒化物半導体層12の厚みをT1とする。このT1は第1窒化物半導体層12の厚み以下の厚みであればいかなる厚みであっても良い。そして、当該リセス領域20を形成した後に、レジスト51を除去する。

【0057】

図5は、リセス領域内の第1窒化物半導体層の上面に窒化物半導体膜を形成した後の状態を示す模式的な断面図である。本実施の形態では、図5に示されるように、リセス領域20の内面に位置する第1窒化物半導体層12の上面に対し、MOCVD法を用いて再成長を行なうことにより窒化物半導体膜23を形成する。ここで、窒化物半導体膜23の上面が、第1窒化物半導体層12の上面を超えないように、厚さT2の窒化物半導体膜23を形成することを特徴とする。すなわち、上記の第1窒化物半導体層12のエッチング深さT1と、窒化物半導体膜23の厚みT2との関係は、0<T2<T1を満たす範囲であればよい。

【0058】

上記で窒化物半導体膜23を形成した後に、選択成長マスク50を除去する。次に、窒化物半導体膜23の上面、リセス領域20の内壁面、および第2窒化物半導体層13a、13bの上面を硫酸/過酸化水素水で洗浄し、さらに塩酸/過酸化水素水で洗浄する。

【0059】

図6は、窒化物半導体膜の上面、リセス領域の内壁面、および第2窒化物半導体層の上面に絶縁膜を形成した後の状態を示す模式的な断面図である。本実施の形態では、図6に示されるように、リセス領域20の内面および第2窒化物半導体層13a、13bの上面に対し、CVD法を用いて絶縁膜9を形成する。

【0060】

このようにして絶縁膜9を形成したときに、第1窒化物半導体層12と、絶縁膜9とが接する界面をリセス界面20cと呼ぶものとする。このリセス界面20cがドライエッチングでダメージを受けていないことにより、リセス界面20cでの高い移動度を得ることができ、オン時におけるリセス界面20cの抵抗を低減させることができる。

【0061】

図7は、絶縁膜にコンタクト領域を形成した後の状態を示す模式的な断面図である。図7に示されるように、第2窒化物半導体層13a、13bの上面のうちのソース電極およびドレイン電極が形成される部分の絶縁膜9を、フォトリソグラフィ技術により除去し、コンタクト領域25を形成する。そして、窒素雰囲気の下で400℃〜1100℃でアニールを行なうことにより、絶縁膜9と窒化物半導体積層体100とが接する面の界面準位を低減させることができる。

【0062】

図8は、ソース電極およびドレイン電極を形成した後の状態を示す模式的な断面図である。上記のアニールを行なった後、図8に示されるように、第2窒化物半導体層13a、13b上の絶縁膜9を除去したコンタクト領域上に、フォトリソグラフィ技術とEB蒸着法とを用いてソース電極6およびドレイン電極7を形成する。

【0063】

そして、熱処理による合金化によりソース電極6およびドレイン電極7と、チャネルとをオーミックコンタクトさせる。なお、オーミックコンタクトを得る方法としては、熱処理による合金化する方法のみに限られるものではなく、トンネル電流機構によりオーミックコンタクトを形成する方法、コンタクト領域25にSi等のn型不純物をイオン注入等により高濃度にドーピングした上で、当該コンタクト領域25にソース電極6およびドレイン電極7を形成する方法等を用いることができる。

【0064】

次に、フォトリソグラフィ技術とEB蒸着法とを用いることにより、絶縁膜上にNi/Auからなるゲート電極8を形成する。以上の各工程により、図1に示されるように、本実施の形態のIII族窒化物系電界効果トランジスタを作製することができる。

【0065】

従来のIII族窒化物系電界効果トランジスタは、第2窒化物半導体層および第1窒化物半導体層の一部をドライエッチングにより除去して、リセス領域を形成していた。このためリセス界面における第1窒化物半導体層がドライエッチングによりダメージ損傷を受けることもあり、第1窒化物半導体層の表面ラフネスが大きいこともあった。その結果、第1窒化物半導体層と絶縁膜との界面において移動度低下が起こり、III族窒化物系電界効果トランジスタのオン抵抗が高くなるという問題があった。

【0066】

本実施の形態のIII族窒化物系電界効果トランジスタにおいては、ドライエッチングによりダメージ損傷を受けた領域を窒化物半導体膜23で覆うことができる。これにより、リセス領域における窒化物半導体膜の移動度が低下することなく、III族窒化物系電界効果トランジスタのオン抵抗を高くなりにくくすることができる。

【0067】

(実施の形態2)

本実施の形態のIII族窒化物系電界効果トランジスタは、実施の形態1の窒化物半導体膜としてp型窒化物半導体を用いる他は、実施の形態1と同様の構成のIII族窒化物系電界効果トランジスタである。

【0068】

(製造方法)

本実施の形態のIII族窒化物系電界効果トランジスタの製造方法は、窒化物半導体膜23としてp型窒化物半導体を形成することが異なる他は、実施の形態1と同様の製造方法により、III族窒化物系電界効果トランジスタを作製する。

【0069】

このようにp型窒化物半導体からなる窒化物半導体膜23を用いることにより、閾値電圧を向上させることができ、p型濃度により閾値電圧を制御することができる。

【0070】

また、窒化物半導体膜23に含まれるp型ドーパントを活性化させるためのアニールを行なうことが好ましい。このようにアニールを行なうことにより窒化物半導体膜23に含まれるp型ドーパントを活性化させることにより、閾値電圧を向上させることができる。

【0071】

(実施の形態3)

本実施の形態のIII族窒化物系電界効果トランジスタは、窒化物半導体膜23の禁制帯幅が第1窒化物半導体層12の禁制帯幅よりも小さいことを特徴とする。このように第1窒化物半導体層12の禁制帯幅よりも小さい窒化物半導体膜23を用いることにより、p型化の活性化率が上昇し、より少ないp型不純物の濃度でより高いp型キャリア濃度を得ることができる。

【0072】

なお、上記のような第1窒化物半導体層12の組成比、厚み、およびキャリア濃度によっては、窒化物半導体膜23と第1窒化物半導体層12とのヘテロ接合界面にキャリアが形成される可能性があるものの、III族窒化物系電界効果トランジスタの全体のキャリア濃度が増大するのでより好ましい。

【0073】

(製造方法)

本実施の形態のIII族窒化物系電界効果トランジスタの製造方法は、第1窒化物半導体層12の禁制帯幅よりも小さい窒化物半導体膜23を形成することが異なる他は、実施の形態1と同様の製造方法により、III族窒化物系電界効果トランジスタを作製する。

【実施例1】

【0074】

以下のように、実施例1のIII族窒化物系電界効果トランジスタを作製する。

本実施例においては、まず、Siからなる基板1を準備する。そして、図2に示されるように、当該基板1上に、有機金属化学気相堆積(MOCVD:Metal Organic Chemical Vapor Deposition)法を用いて、薄いアンドープAlN層および厚いアンドープGaNの多重窒化物半導体層からなる下地半導体層2と、窒化物半導体積層体100とを積層する。当該窒化物半導体積層体100は、厚さ1000nmのアンドープAl0.05Ga0.95Nからなる下地窒化物半導体層11と、厚さ100nmのアンドープGaN層からなる第1窒化物半導体層12と、上から順に厚さがそれぞれ1nm/22nm/1nmのアンドープGaN/Al0.25Ga0.75N/AlNという3層構造からなる第2窒化物半導体層13とをこの順に積層したものである。

【0075】

次に、CVD法を用いて、第2窒化物半導体層13上にSiO2膜を形成する。そして、SiO2膜上にレジスト51を形成し、フォトリソグラフィ技術を用いてリセス領域となる部分のSiO2膜を除去する。そして、図3に示されるように、SiO2膜のうちの除去されなかった部分が選択成長マスク50となる。なお、フォトリソグラフィ技術を用いて作製したレジスト51は剥離することなく残している。

【0076】

次に、図4に示されるように、選択成長マスク50が形成されずに第2窒化物半導体層13が露出している部分に対し、誘導結合プラズマ(ICP:Inductively coupled plasma)エッチング装置を用いて第2窒化物半導体層13、および第1窒化物半導体層12のうちの上部の厚みT1(T1は50nm)を除去することにより、リセス領域20を形成し、その後レジスト51を除去する。

【0077】

次に、図5に示されるように、選択成長マスク50が形成されずに第1窒化物半導体層12が露出している領域上に、MOCVD法を用いて厚みT2(T2は30nm)のアンドープGaNからなる窒化物半導体膜23を再成長により形成する。そして、選択成長マスク50を除去する。

【0078】

次に、窒化物半導体膜23の上面、リセス領域20の内壁面、および第2窒化物半導体層13a、13bの上面を硫酸/過酸化水素水で洗浄し、さらに塩酸/過酸化水素水で洗浄する。そして、図6に示されるように、リセス領域20の内面および第2窒化物半導体層13a、13bの上面に対し、CVD法を用いて厚さ30nmのSiO2からなる絶縁膜9を形成する。

【0079】

そして、図7に示されるように、第2窒化物半導体層13a、13bの上面のうちのソース電極およびドレイン電極が形成される部分の絶縁膜9をフォトリソグラフィ技術により除去し、コンタクト領域25を作製する。そして、窒素雰囲気の下で1000度でアニールを行なうことにより、絶縁膜9と窒化物半導体積層体100との接する面の界面準位を低減させる。

【0080】

その後、図8に示されるように、第2窒化物半導体層13a、13bのコンタクト領域25に、フォトリソグラフィ技術とEB蒸着法とを用いてTi/Alからなるソース電極6、およびソース電極6と同一組成のドレイン電極7を形成する。そして、真空雰囲気で800℃、1分間熱処理を行なうことにより、ソース電極6およびドレイン電極7を二次元電子ガス14a、14bとオーミックコンタクトさせる。

【0081】

次に、フォトリソグラフィ技術とEB蒸着法とを用いることにより、絶縁膜9上にNi/Auからなるゲート電極8を形成する。以上の工程により、本実施例のIII族窒化物系電界効果トランジスタを作製する。

【0082】

上記のようにして作製する実施例1のIII族窒化物系電界効果トランジスタにおいて、リセス界面20cと接する窒化物半導体膜23は、ドライエッチングによるダメージがないため、リセス界面20cにおいて高い移動度が得られ、オン時におけるリセス界面20cの抵抗を低下させることができる。これは、リセス界面20cにおける移動度の増大と、反転層電子濃度の増大に起因するものと考えられる。

【実施例2】

【0083】

本実施例は、実施例1のIII族窒化物系電界効果トランジスタの窒化物半導体膜23として1×1019cm-3の濃度でMgがドーピングされたp型GaN層を用いる他は、実施例1と同一の構成のIII族窒化物系電界効果トランジスタである。p型GaNからなる下地窒化物半導体層11には、p型不純物のMgが1×1019cm-3の濃度でドーピングされているが、GaN中ではMgの活性化率が低いのでp型GaNの正孔濃度は1×1017cm-3になる。

【0084】

(製造方法)

本実施例のIII族窒化物系電界効果トランジスタは、窒化物半導体膜23として、1×1019cm-3の濃度でMgがドーピングされたp型GaN層を形成すること、および絶縁膜を形成する前にp型ドーパントを活性化させるためのアニールをすることを除いては、実施例1と同様の製造方法によりIII族窒化物系電界効果トランジスタを製造する。

【実施例3】

【0085】

実施例3は、実施例1のIII族窒化物系電界効果トランジスタの窒化物半導体膜23として1×1018cm-3の濃度でMgがドーピングされたp型In0.1Ga0.9Nを用いる他は、実施例1と同一の構成のIII族窒化物系電界効果トランジスタである。ここで、下地窒化物半導体層に含まれる正孔濃度は、1×1017cm-3である。これにより下地窒化物半導体層11のp型化の活性化率が上昇し、より少ないp型不純物の濃度で同程度のp型キャリア濃度を得ることができる。

【0086】

(製造方法)

本実施例のIII族窒化物系電界効果トランジスタは、窒化物半導体膜として、1×1018cm-3の濃度でMgがドーピングされたp型In0.1Ga0.9N層を形成したこと、および第2窒化物半導体層13a、13bを形成した後にp型ドーパントを活性化させるためのアニールをすることを除いては、実施例1と同様の製造方法によりIII族窒化物系電界効果トランジスタを製造する。

【0087】

(比較例1)

比較例1は、実施例1のIII族窒化物系電界効果トランジスタにおいて、窒化物半導体膜23を形成しないこと以外は、実施例1と同一の構成のIII族窒化物系電界効果トランジスタである。よって、比較例1のIII族窒化物系電界効果トランジスタの製造方法は、実施例1のリセス領域を形成する工程(図4)までは同一であるので、この工程以降を説明する。

【0088】

図9は、リセス領域の内面、および第2窒化物半導体層上に絶縁膜を形成した後の状態を示す模式的な断面図である。本比較例では、図9に示されるように、エッチングによりリセス領域を形成した後に、窒化物半導体膜を形成せずに絶縁膜9を形成する。

【0089】

図10は、比較例1のIII族窒化物系電界効果トランジスタを示す模式的な断面図である。上記のように絶縁膜9を形成した後は、実施例1と同様の方法により、図10に示されるIII族窒化物系電界効果トランジスタを作製する。

【0090】

比較例1のIII族窒化物系電界効果トランジスタは、エッチングによりリセス領域20を形成後に絶縁膜を形成しているため、リセス界面20cと接する絶縁膜9の界面に、ドライエッチングによるダメージがある。このため、リセス界面において移動度低下が生じることとなり、III族窒化物系電界効果トランジスタのオン抵抗は高い値となる。

【0091】

以上の説明からも明らかなように、実施例1〜3の本発明に係るIII族窒化物系電界効果トランジスタは、比較例1のIII族窒化物系電界効果トランジスタに比し、オン抵抗が低下していることが明らかである。このことから、ドライエッチングによりIII族窒化物系電界効果トランジスタのリセス領域を形成した後に、リセス領域上に窒化物半導体膜を形成することにより、そのオン抵抗を低下させることができることが明らかとなる。

【0092】

以上のように本発明の実施の形態および実施例について説明を行なったが、上述の各実施の形態および実施例の構成を適宜組み合わせることも当初から予定している。

【0093】

今回開示された実施の形態および実施例はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0094】

1 基板、2 下地半導体層、6 ソース電極、7 ドレイン電極、8 ゲート電極、9 絶縁膜、11 下地窒化物半導体層、12 第1窒化物半導体層、13,13a,13b 第2窒化物半導体層、14a,14b 二次元電子ガス、16a,16b ヘテロ接合界面、20 リセス領域、20c リセス界面、23 窒化物半導体膜、25 コンタクト領域、50 選択成長マスク、100 窒化物半導体積層体。

【特許請求の範囲】

【請求項1】

下地半導体層と、

前記下地半導体層上に、第1窒化物半導体層および第2窒化物半導体層が順次積層された窒化物半導体積層体と、

前記窒化物半導体積層体の上面に接する、ソース電極およびドレイン電極と、

前記ソース電極および前記ドレイン電極の間の前記窒化物半導体積層体における、前記第1窒化物半導体層の一部および前記第2窒化物半導体層が形成されていない領域であるリセス領域と、

前記リセス領域上に形成された窒化物半導体膜と、

前記窒化物半導体膜の上面、前記リセス領域の内壁面、および前記第2窒化物半導体層の上面に形成された絶縁膜と、

前記絶縁膜上に形成されたゲート電極とを有し、

前記第2窒化物半導体層は、前記第1窒化物半導体層に比べて広い禁制帯幅を有し、

前記窒化物半導体膜の上面は、前記第1窒化物半導体層の上面よりも低い、III族窒化物系電界効果トランジスタ。

【請求項2】

前記窒化物半導体膜は、p型窒化物半導体またはi型窒化物半導体からなる、請求項1に記載のIII族窒化物系電界効果トランジスタ。

【請求項3】

前記窒化物半導体膜に含まれる正孔濃度は、1×1017cm-3以下である、請求項2に記載のIII族窒化物系電界効果トランジスタ。

【請求項4】

前記第1窒化物半導体層および前記窒化物半導体膜は、GaNからなる、請求項1〜3のいずれかに記載のIII族窒化物系電界効果トランジスタ。

【請求項5】

前記窒化物半導体膜は、InxGa1-xN(0<x≦1)からなる、請求項1〜3のいずれかに記載のIII族窒化物系電界効果トランジスタ。

【請求項6】

前記窒化物半導体膜の厚みは、30nm以上である、請求項1〜5のいずれかに記載のIII族窒化物系電界効果トランジスタ。

【請求項7】

前記窒化物半導体積層体は、前記第1窒化物半導体層の前記第2窒化物半導体層と接する面とは反対側の面に、下地窒化物半導体層を有する、請求項1〜6のいずれかに記載のIII族窒化物系電界効果トランジスタ。

【請求項8】

前記リセス領域は、ドライエッチングにより作製され、

前記窒化物半導体膜は、前記リセス領域の内面に再成長法を用いて作製される、請求項1〜7のいずれかに記載のIII族窒化物系電界効果トランジスタ。

【請求項9】

下地半導体層上に第1窒化物半導体層、および第2窒化物半導体層を形成する工程と、

前記第2窒化物半導体層の一部上に選択成長マスクを形成する工程と、

前記選択成長マスクが形成されていない領域における、前記第2窒化物半導体層の全部、および前記第1窒化物半導体層の上部を除去し、前記第1窒化物半導体層の一部を露出させてリセス領域を形成する工程と、

前記リセス領域上に、窒化物半導体膜を形成する工程と、

前記第2窒化物半導体層上の前記選択成長マスクを除去する工程と、

前記窒化物半導体膜の上面、前記リセス領域の内壁面、および前記第2窒化物半導体層の上面に絶縁膜を形成する工程とを含む、III族窒化物系電界効果トランジスタの製造方法。

【請求項10】

前記選択成長マスクを形成させる工程の後に、

前記選択成長マスク上にレジストを形成する工程を含む、請求項9に記載のIII族窒化物系電界効果トランジスタの製造方法。

【請求項1】

下地半導体層と、

前記下地半導体層上に、第1窒化物半導体層および第2窒化物半導体層が順次積層された窒化物半導体積層体と、

前記窒化物半導体積層体の上面に接する、ソース電極およびドレイン電極と、

前記ソース電極および前記ドレイン電極の間の前記窒化物半導体積層体における、前記第1窒化物半導体層の一部および前記第2窒化物半導体層が形成されていない領域であるリセス領域と、

前記リセス領域上に形成された窒化物半導体膜と、

前記窒化物半導体膜の上面、前記リセス領域の内壁面、および前記第2窒化物半導体層の上面に形成された絶縁膜と、

前記絶縁膜上に形成されたゲート電極とを有し、

前記第2窒化物半導体層は、前記第1窒化物半導体層に比べて広い禁制帯幅を有し、

前記窒化物半導体膜の上面は、前記第1窒化物半導体層の上面よりも低い、III族窒化物系電界効果トランジスタ。

【請求項2】

前記窒化物半導体膜は、p型窒化物半導体またはi型窒化物半導体からなる、請求項1に記載のIII族窒化物系電界効果トランジスタ。

【請求項3】

前記窒化物半導体膜に含まれる正孔濃度は、1×1017cm-3以下である、請求項2に記載のIII族窒化物系電界効果トランジスタ。

【請求項4】

前記第1窒化物半導体層および前記窒化物半導体膜は、GaNからなる、請求項1〜3のいずれかに記載のIII族窒化物系電界効果トランジスタ。

【請求項5】

前記窒化物半導体膜は、InxGa1-xN(0<x≦1)からなる、請求項1〜3のいずれかに記載のIII族窒化物系電界効果トランジスタ。

【請求項6】

前記窒化物半導体膜の厚みは、30nm以上である、請求項1〜5のいずれかに記載のIII族窒化物系電界効果トランジスタ。

【請求項7】

前記窒化物半導体積層体は、前記第1窒化物半導体層の前記第2窒化物半導体層と接する面とは反対側の面に、下地窒化物半導体層を有する、請求項1〜6のいずれかに記載のIII族窒化物系電界効果トランジスタ。

【請求項8】

前記リセス領域は、ドライエッチングにより作製され、

前記窒化物半導体膜は、前記リセス領域の内面に再成長法を用いて作製される、請求項1〜7のいずれかに記載のIII族窒化物系電界効果トランジスタ。

【請求項9】

下地半導体層上に第1窒化物半導体層、および第2窒化物半導体層を形成する工程と、

前記第2窒化物半導体層の一部上に選択成長マスクを形成する工程と、

前記選択成長マスクが形成されていない領域における、前記第2窒化物半導体層の全部、および前記第1窒化物半導体層の上部を除去し、前記第1窒化物半導体層の一部を露出させてリセス領域を形成する工程と、

前記リセス領域上に、窒化物半導体膜を形成する工程と、

前記第2窒化物半導体層上の前記選択成長マスクを除去する工程と、

前記窒化物半導体膜の上面、前記リセス領域の内壁面、および前記第2窒化物半導体層の上面に絶縁膜を形成する工程とを含む、III族窒化物系電界効果トランジスタの製造方法。

【請求項10】

前記選択成長マスクを形成させる工程の後に、

前記選択成長マスク上にレジストを形成する工程を含む、請求項9に記載のIII族窒化物系電界効果トランジスタの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2011−82415(P2011−82415A)

【公開日】平成23年4月21日(2011.4.21)

【国際特許分類】

【出願番号】特願2009−234917(P2009−234917)

【出願日】平成21年10月9日(2009.10.9)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成23年4月21日(2011.4.21)

【国際特許分類】

【出願日】平成21年10月9日(2009.10.9)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]