III/V半導体

【課題】SiあるいはGaP技術をベースとする集積回路にモノリシックに集積化される、新しいIII/V半導体を用いた、発光ダイオードおよびレーザダイオードの半導体構造及び製造方法、あるいはまた、モジュレータ構造および検出器構造への使用法を提供する。

【解決手段】ドープされたSiあるいはドープされたGaPをベースとするキャリア層A、およびそこに配設されたIII/V半導体Dを備え、組成GaxInyNaAsbPcSbdを有するモノリシック集積回路構造であって、ここで、x=70−100モル−%、y=0−30モル−%、a=0.5−15モル−%、b=67.5−99.5モル−%、c=0−32.0モル−%およびd=0−15モル−%、xとyの合計は、常に100モル−%であり、a、b、cおよびdの合計は、常に100モル−%であり、そして、一方のxとyの合計と他方のaないしdの合計の比率は、実質的に1:1である。

【解決手段】ドープされたSiあるいはドープされたGaPをベースとするキャリア層A、およびそこに配設されたIII/V半導体Dを備え、組成GaxInyNaAsbPcSbdを有するモノリシック集積回路構造であって、ここで、x=70−100モル−%、y=0−30モル−%、a=0.5−15モル−%、b=67.5−99.5モル−%、c=0−32.0モル−%およびd=0−15モル−%、xとyの合計は、常に100モル−%であり、a、b、cおよびdの合計は、常に100モル−%であり、そして、一方のxとyの合計と他方のaないしdの合計の比率は、実質的に1:1である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、新しいIII/V半導体、このような半導体からなる半導体層、このような半導体層を備えるモノリシックに集積化された半導体構造、このような半導体のあるいはこのような半導体層の使用法およびこのような半導体層の製造のための方法に関する。

【背景技術】

【0002】

コンピュータ技術の分野において、高信頼性および高い柔軟性と関連したより高い処理能力および信号伝導能力に対する絶え間なく増大する要求がある。従来、チップ技術は、集積化密度および動作速度あるいはサイクル周波数に関して急速な進歩を遂げてきた。更に進行するこの傾向によって、高速なチップの接続に対する問題が起こっている。高速接続と関連した重要な点は、信頼性、コスト、オンチップドライバサイズおよび性能、混信、符号歪およびチップ設計の柔軟性の欠如である。オプトエレクトロニクス部品および光導波路を使用したチップ間の接続は、多くの接続問題に対する一解決策である。光接続は、極めて高い帯域幅を有し、混信および他の干渉に対して比較的に反応しない。光接続のこれらの特性を用いて、光チャネルによって互いに高速チップを接続して、接続密度、電流消費、干渉および混信に関する相当な改良を達成することが、可能になるであろう。

【0003】

通常、高集積回路はSi技術に基づく。珪素はしかし間接遷移型半導体であり、Si技術を使用した効率的なオプトエレクトロニクス部品の製造はその結果としてほとんど可能でない。効率的なオプトエレクトロニクス部品は、しかし、これらの半導体がしばしば直接遷移型半導体であり、その結果として、高効率で光を発し、および吸収するので、III/V半導体の技術、たとえばGaAs技術を用いて製造されることができる。

集積回路を製造するために、一般に、エピタキシャル工程が、使用される。次に、もしSi技術をベースとする層とIII/V半導体の技術をベースとする層との間のコンタクトがなされるならば、それぞれの材料の格子定数が異なることが問題である(これは、また、Si基板の代わりにGaP基板にあてはまる)。これは、Si(あるいはGaP)基板上でのIII/V半導体のエピタキシャル成長中に、転位が形成される結果として有する。このような転位は、しかし、機能層厚が現在原子寸法のオーダーであるのでより一層、かなりの程度に、全部の半導体構造の機能を妨げる。高層厚の場合、格子定数の差は、基板の曲がりにつながりさえする。この理由は基本的に、高堆積温度によって、III/V半導体のエピタキシャル成長がSiあるいはGaP半導体上に生じるが、しかし、転位の生成はより高くない堆積温度ですでに始まることである。次いでこの半導体構造が、室温まで冷却すると、異なる熱膨張係数によって引き起こされる格子定数の差が、上記の応力および転位につながる。

【0004】

上記の問題をなくすために、様々なアプローチが存在する。文献EP0380815 B1において、GaAs層が、Si基板上に堆積されることができ、かつ所定の位置に規定された微小割れを形成することができ、したがって、Si基板の転位が回避され、少なくともしかし減少される、ことが記載されている。この技術は、しかし原子スケールの微小割れの制御性を欠いているという理由で高集積回路に適していない。

文献EP0297483は、Si基板上にSi技術をベースとする集積回路が設けられた、ハイブリッド集積化半導体構造を記載している。更に、GaAs技術の光学活性素子が、Si基板上に形成される。集積回路と光学活性素子との間の電気的接続は、しかし直接のコンタクトによってあるいはSi基板によって確立されるのではなく、むしろ電気ワイヤ接続によって確立される。この技術も、また高集積回路の用途に適していない。

文献DE10355357から、III/V半導体をベースとする光学活性素子による層状構造に対して、たとえば引張応力を受ける適応層によって格子定数によって引き起こされる転位を補償することが公知である。その限りにおいて公知の手段によって、電子的特性のモデリングもまた可能であり、したがって、今までアクセス可能でない発光波長がアクセス可能になる。

文献US2004/0135136 A1から、多数の異なるIII/V半導体が公知技術であるが、それらは常に層であり、Si基板上への施着に適していない。類似の考察が、文献EP1257026 A2、US6,233,264 B1、US2004/0084667 A2、Merz他、IEE Proc.−Optoelectron. 151(5):346−351 (2004)、US6,072,196、EP1553670 A2、US5,825,796、Ishizuka他Journal of Crystal Growth 272:760−764(2004))およびUS2004/0161009 A1にあてはまる。

文献EP0896406 A2には、GaPあるいはSi基板(および他のもの)上の光活性III/V半導体の層が記載され、これらの層はIII属成分としてInだけを含む。実際、このような層はInP基板に適しているだけであり、SiあるいはGaP基板上に望ましくないほど多くの転位および欠陥を形成する。文献US5,937,274は、非常に一般的な方法で異なる基板上の異なる層を記載する。

その結果、特に高集積回路の分野にとって、Si技術をベースとする、かつIII/V半導体をベースとするサブアセンブリーあるいは層列を互いにモノリシックに接続することが必要であることは、続いている。

【発明の開示】

【発明が解決しようとする課題】

【0005】

Si技術あるいはGaP技術の基板上にIII/V半導体をベースとする光学活性素子を形成するための手段を提案することが、本発明の一技術目的であり、光学活性素子への、そして、そこからの、SiベースのあるいはGaPベースのサブアセンブリーの電気的な信号の伝導が集積的に、すなわち層の接触によって、形成され、III/V半導体内に、あるいは下になっている層に対するその境界面に、非発光性再結合中心を形成する転位が事実上ない。直接接触する、すなわち層接触による、Si基板あるいはGaP基板上の安定発光およびレーザ素子を提案することが、本発明の更なる一技術目的である。Si技術ベースのプロセッサ回路からデータ電流を直接、すなわちワイヤボンド接続線なしで、光信号として送る、モノリシックに集積化された半導体構造を提供することが、本発明の別の技術目的である。更に、またそれによって発された光学信号が変調され、および/または検出されることができる、モノリシックに集積化された半導体構造を提案することも、本発明の一目的である。

(本発明および実施態様の基本)

【0006】

この技術目的を達成するために、本発明はSiあるいはGaP基板および組成GaxInyNaAsbPcSbdを有するIII/V半導体を備えた請求項1に記載のモノリシックに集積化された半導体構造を教示し、ここで、x=70−100モル−%、y=0−30モル−%、a=0.5−15モル−%、b=67.5−99.5モル−%、c=0−32.0モル−%およびd=0−15モル−%、xとyの合計は、常に100モル−%であり、a、b、cおよびdの合計は、常に100モル−%であり、そして、一方のxとyの合計と他方のaないしdの合計の比率は、実質的に1:1である。好ましくは、y=1−30モル−%、そして、c=1−32.0モル−%およびこのような半導体自体。

Pのない系の場合、Pの様に、これらの元素がN混和によって引き起こされる局所的歪界を最小限に抑えるので、Inおよび/またはSbが含まれるべきである。

以下の組成を有するIII/V半導体が、特に好ましい:

a) x=70−100モル−%、y=0−30モル−%、a=0.5−10モル−%、b=70−98.5モル−%、c=1−29.5モル−%、あるいは

b) x=85−99モル−%、y=1−15モル−%、a=0.5−10モル−%、b=70−98.5モル−%、c=1−29.5モル−%、あるいは

c) x=85−99モル−%、y=1−15モル−%、a=0.5−10モル−%、b=70−98.5モル−%、c=0−32モル−%およびd=1−10モル−%。

特に、x=>70−100モル−%、a=>1.3あるいは>1.7モル−%(任意選択でy>0あるいは1モル−%と関連して)、c=0−32モル−%および/またはb=60−99.5モル−%。好ましくは、またc=あるいは4−8モル−%の間である。好ましくは、またa=4あるいは5.5−11モル−%である。

本発明の混晶系GaInNAsPSbに従う半導体類が特徴づけられ、一方では、おそらく窒素および/燐の追加の組成のために、格子に適合され、あるいは圧迫して応力を加えられた層列が、転位を生じさせずに、GaPおよび/またはSi基板上に形成されることができる。他方では、燐含有量に関連して>0.5モル−%の窒素濃度から始まって、Γ点において、窒素のない混晶系の伝導帯状態と窒素の混合によって引き起こされる電子レベルの相互作用が起こり、それは、Γ点の基本エネルギーギャップの事実上の赤方偏移につながり、したがって、GaInNAsPSb材料系の直接遷移型半導体としての特性を強化する。たとえば、a=1−10モル−%、b=60−95モル−%およびc=2−15モル−%、好ましくはa=3−5モル−%、b=85−95モル−%およびc=4−8モル−%に対して、明確に1.8eV未満、さらに1.4eV以下までの基本エネルギーギャップという結果になる。これによって、本発明に従うこの半導体系の組成によるエネルギーギャップの大幅な影響が明白になる。

【0007】

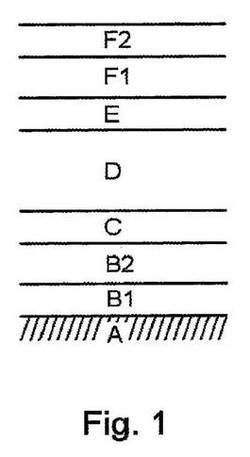

詳細には、本発明は以下の層状構造を備えるモノリシックに集積化された半導体構造に関する:

A)ドープされたまたはドープされていないSiあるいはGaPをベースとするキャリア層、

B)任意選択として、ドープされたSi、ドープされたGaPあるいはドープされた(AlGa)Pから成る第1の電流伝導層、

C)任意選択として、第1の適応層、および

D)本発明に従う半導体層を備える光学活性素子。

層D)に対して、以下の層が続くことができる:E)任意選択で第2の適応層、およびF)ドープされたSiあるいはドープされたGaPあるいはドープされた(AlGa)Pから成る第2の電流伝導層。(AlGa)Pの場合には、Alの比率は、20−100モル−%とすることができ、およびAlとGaの比率の合計は、常に100モル−%である。層B)は、p形あるいはn形不純物ドープとすることができる。層F)が存在する場合には、もし層B)がn形不純物ドープであるならば、層F)はp形不純物ドープとすることができ、そして、その逆も同じである。

通常は、この光学素子は層状構造(D1−D2−D3)nを有し、ここで層D2は、本発明に従う半導体の量子ウェル層であり、層D1およびD3は、バリヤー層であり、そしてn=1−15である。このような光学活性素子によって、発光ダイオードとレーザダイオードが構築されることができる。端子層D1あるいはD3の1つに続いて、バリヤー層D4が、形成されることができる。バリヤー層は組成Gap−InqNrPsAstを有する半導体とすることが推奨されることができ、ここで、p=85−100モル−%、q=0−15モル−%、r=0−15モル−%、s=60−100モル−%およびt=0−40モル−%、pとqの合計は、常に100モル−%であり、r、sおよびtの合計は、常に100モル−%であり、そして、一方のpとqの合計と他方のrないしtの合計との比率は実質的に1:1であり、そして、バリヤー層は好ましくは5−50nmの層厚を有する。好ましい範囲は、次通りである:p=90−100モル−%、q=0−10モル−%、r=0−10モル−%、s=70−100モル−%およびt=0−30モル−%。層厚に対しては、2−20nmの範囲が好ましい。適応層は、組成GapInqNrPsAstを有する半導体とすることができ、ここで、p=90−100モル−%、q=0−10モル−%、r=0−10モル−%、s=70−100モル−%およびt=0−30モル−%、pとqの合計は、常に100モル−%であり、r、sとtの合計は、常に100モル−%であり、そして、一方のpとqの合計と他方のrないしtの合計との比率は実質的に1:1であり、そして、適応層は、好ましくは50−500nmの層厚を有する。

【0008】

本発明に従うモノリシックに集積化された半導体構造において、キャリア層と光学活性素子との間に配設される電流伝導層および/またはバリヤー層は、同時に、適応層であることができる。

光学活性素子の下におよび/または上に、光学活性素子に光学的に接続される、少なくとも一つの光導波路層が設けられることができる。このようにして、データ電流は、キャリア上の異なる場所で発光する光学活性素子から光受信機への光学信号として導かれることができる。他の素子、例えばファイバ等が光信号を伝導するために追加的にあるいは代わりとして使われることができることが理解される。

層A)とD)との間に、および/または層F)の外側に、少なくとも一つの周期的な反射構造が設けられた、発光ダイオードあるいはまた垂直発光レーザダイオードが、製造されることができる。

好ましくは、光学活性素子は、700−1,100nmの範囲の基本発光波長を有する。

本発明は、更に発光ダイオード(LED)、VCSEL(垂直共振器面発光レーザ)レーザダイオードあるいはVECSEL(垂直外部共振器面発光レーザ)レーザダイオードおよびモジュレータあるいは検出器構造の製造のための本発明に従う半導体あるいは本発明に従う半導体層の使用法に関する。

【0009】

最後に、本発明は以下の諸ステップを備える本発明に従う半導体層の製造のための方法に関する:ドープされたあるいはドープされていないSiあるいはGaPをベースとする基板が、MOVPE(金属有機気相エピタキシー)装置内にもたらされ、任意選択で、基板の表面は、少なくとも一つのエピタキシャルコーティング工程において、最初に、それぞれ少なくとも1つの適応層、1つのバリヤー層、1つの電流伝導層、1つの導波路層および/または1つの反射構造を設けられ、キャリヤーガスが、規定された濃度の遊離体と共にロードされ、ロードされたキャリヤーガスは、規定された持続期間の曝露の間、300℃ないし700℃の範囲内の温度まで加熱された基板の表面上に、あるいは基板上の一番上の層の表面上に伝導され、そして、半導体層が基板の表面上にあるいは基板上の一番上の層の表面上に所定の層厚でエピタキシャル形成されるように、遊離体の合計濃度および曝露の持続期間が互いに調節される。

好ましくは、以下の遊離体が、MOVPE技術のために使われる:C1−C5 トリアルキルガリウム、Ga遊離体として、特にトリエチルガリウム(Ga(C2H5)3)および/または、トリメチルガリウム(Ga(CH3)3)、C1−C5 トリアルキルインジウム、In遊離体として、特にトリメチルインジウム(In(CH3)3))、アンモニア(NH3)、モノ(C1−C8)アルキルヒドラジン、N遊離体として、特に第三ブチルヒドラジン(t−(C4H9)−NH−NH2)および/または1,1−ジ(C1−C5)アルキルヒドラジン、N遊離体として、特に1,1−ジ−メチルヒドラジン((CH3)2−N−NH2)、アルシン(AsH3)および/またはC1−C5 アルキルアルシン、As遊離体として、特に第三ブチルアルシン(t−(C4H9)−AsH2)、フォスフィン(PH3)および/またはC1−C5 アルキルフォスフィン、P遊離体として、特に第三ブチルフォスフィン(t−(C4H9)−PH2)、そして、C1−C5 トリアルキルアンチモン、Sb遊離体として、特にトリメチルアンチモン((CH3)3Sb)および/または、トリエチルアンチモン((C2H5)3Sb)、ここで、C3−C5アルキル基は、直鎖あるいは分岐とすることができる。

好ましくは、遊離体は以下のモル比率で使用される:As遊離体/III属遊離体 5−300、P遊離体/III属遊離体 0−500、N遊離体/As遊離体 0.1−10、任意選択でSb遊離体/As遊離体 0−1、ここで基板の表面温度は、500℃から630℃までの範囲に調節され、キャリヤーガスおよび遊離体の全圧は、10から1,000hPaまで、あるいは200hPaまでの範囲に調節され、キャリヤーガスの分圧に対する全ての遊離体の分圧の合計の比率は、0.005と0.1の間にあり、そして、成膜速度は0.1μm/hないし10μm/hである。特に、以下の比率が、使用されることができる:As遊離体/III属遊離体 10−100、たとえば10−30、P遊離体/III属遊離体 1−100、たとえば1−10、N遊離体/As遊離体 1−10、たとえば3−8。表面温度は、好ましくは500℃から650℃まで、特に550℃ないし600℃の範囲内とすることができる。キャリヤーガスおよび遊離体の全圧は、20hPaから100hPaまでの範囲内とすることができる。キャリヤーガスの分圧に対する全ての遊離体の分圧の比率は、0.01から0.05までの範囲内とすることができる。成膜速度は、0.1μm/hないし5μm/h、特に0.5μm/hないし3μm/hとすることができる。

【0010】

原則として、遊離体の正確な濃度は、MOVPE工程のそれぞれの遊離体の熱分解特性に依存する。層の成長速度は、III属遊離体の濃度によって決められる。Ga、および該当する場合In遊離体、の様々な分解特性をベースとして、当業者に公知のように、選択された堆積温度(基板の表面温度)に従い、適切な遊離体濃度が調節され、それは、本発明に従う半導体層内のそれぞれの元素の所望のIII属濃度につながる。V属遊離体あるいはIII/V半導体の成長表面の種類の公知の温度に依存した調和しない気化のため、MOVPE堆積内のそれぞれのV属遊離体濃度は、超過の選択された堆積温度の関数として本発明に従う半導体層内の所望の濃度に慎重に調節されるべきである。これは、当業者にとって容易に達成可能である。より高い堆積温度あるいは容易に分解されることができない遊離体に対して、該当する場合、より高いV/III比率であるが、また、上述より高いN/As比率が選択されなければならない。低い堆積温度に対して、対応して、逆の挙動があてはまる。

MOVPEに対する代替法として、もちろん他のエピタキシャル法、例えばMBE(分子線エピタキシー)、また、ガス供給源、特にV属成分の含有下で(ガス供給源MBE、GS−MBE)、CBE(化学線エピタキシー)あるいはまた、MOMBE(金属有機分子線エピタキシー)もまた、使用されることができる。これらの方法は、通常で当然公知のエピタキシー装置によって実施されることができ、およびそれぞれ適切で当然公知の遊離体および供給源が、使用されなければならない。それぞれの条件は、当業者によって容易に調節されることができる。

本発明に従う半導体構造の製造のための方法は、請求項22ないし33に記載される。

(定義)

【0011】

直接遷移型半導体は、バンド構造内の価電子帯最大値および伝導帯最小値が同じ結晶パルスベクトルで互いの反対側に位置する半導体である。それに対して対照的に、間接遷移型半導体にとって、価電子帯最大値および伝導帯最小値は、同じ結晶パルスベクトルで、互いの反対側に位置せず、異なる結晶パルスベクトルで位置する。

モノリシック半導体構造は、異なる機能半導体部分の電気コンタクトが互いに直接に接続される(好ましくはエピタキシャル)層によって生じる構造である。それに対して対照的に、ハイブリッド半導体構造では、異なる機能半導体部分の電気的コンタクトは、補助接続、例えばワイヤ接続などによって達成される。

n形不純物ドープの半導体では、電気伝導は余分な価電子を有するドナー原子のために電子によって達成される。シリコンのn形不純物ドープに対して、たとえば窒素、燐、ヒ素およびアンチモンが、使われることができる。GaPあるいは(AlGa)P半導体のn形不純物ドープに対して、たとえば、シリコンおよびテルルが、使われることができる。p形不純物ドープの半導体では、電気伝導はアクセプタ原子の結合のために正孔によって生じる。シリコンのアクセプタは、硼素、アルミニウム、ガリウムおよびインジウムである。アクセプタとしてたとえばマグネシウム、亜鉛あるいは炭素が、GaPあるいは(AlGa)Pに対して使われることができる。

もしドナーあるいはアクセプタ原子の濃度が105cm−3より下であるならば、半導体は一般的にドープされていない。ドープされた半導体は、通常1015cm−3より上の濃度を有する。

規定された電力を供給するのに充分な電気伝導度が与えられる程度まで、電流伝導層はドープされた半導体から成る。

【0012】

本発明に従うIII/V半導体は、一般的に圧迫して応力を加えられる。バンド構造の格子適応およびモデリングのために、バリヤー層が設けられ、それは引張応力を加えられることができる。それによって、III/V半導体の応力の補償が、達成される。

本発明に従う光学活性素子は、エネルギーを光放射に変換して、後者を放射して、光放射を変調しておよび/または光放射を吸収して、それを電気信号に変換する。レーザダイオードに対して、層周期nの総数は、一般的に1−5である。発光ダイオードに対して、nはしかし15までとすることができる。モジュレータあるいは検出器構造に対して、nは実質的により高くなることができて、50以上までの値を有することができる。

適応層は、SiあるいはGaP基板上のIII/V半導体をベースとする、本発明に従う半導体層あるいは半導体構造の応力の補償の役に立つ。適応層は、光発光に寄与しない。

量子ウェル層は、また、量子フィルムと呼ばれる。バリヤー層との2側面接触によって、電荷担体の運動は、閉じ込められ、そして、電荷担体は、エピタキシャル層の場合、一次元の含有内にある(主に2空間次元内の運動)。本発明に従う層状構造を有する光学活性素子は、また、多重量子ウェル(MQW)構造と呼ばれる。量子ウェル層とバリヤー層との間のエピタキシャル応力によって、基本バンドギャップに関する電子的特性が、影響される可能性がある。

【0013】

光導波路層は、広範囲にわたって従来技術から公知である。例のみとして、参照が文献「半導体光電子工学:物理および技術(Semiconductor Optoelectronics: Physics and Technology)」、J.Singh、マグロウヒル社、ニューヨーク(1995)になされる。

周期的な反射構造が、絶縁体および/またはエピタキシャル(λ/4)多層鏡である。それらは、いわゆる分布Bragg反射器(DBR)であり、光学活性素子によって放射される光を反射し、したがって、レーザ共振器内の高反射端部鏡を表す。それに関して、参照が文献「垂直共振器面発光レーザ:設計、製造、特性試験および応用例(Vertical−cavity Surface−emitting Lasers: Design, Fabrication, Characterization and Application)」、編集:C.Wilmsen他、ケンブリッジ大学出版、ケンブリッジ(1999)になされる。このような周期的な反射構造は、また、電流伝導の目的でpあるいはn形不純物ドープとすることができる。次いで、これらの周期的な反射構造は、同時に、電流伝導層の機能を受け入れる。

本発明に従うIII/V半導体は、一般的に室温であるいは動作温度で準安定である。これは、それぞれの温度での状態の熱力学のために、少なくとも2つの異なる相への減衰が生じない限り、安定な均質の相は存在しないことを意味する。この減衰は、しかし動力学的に阻害される。動力学の阻害を克服するためには、作用するのに高温が必要とされ、このために、このような準安定相は、比較的低基板温度で、概して700℃より下でだけエピタキシャル堆積することができる。低下した温度での堆積の後、本発明に従う半導体層のアニール工程が、非発光性再結合中心の減少のために、概して700℃ないし850℃の温度範囲内で実行されることができる。平衡アニール工程、同じく例えば急速熱アニール(RTA)などの不平衡法が、たとえば直ちにMOVPE反応装置内で、実行されることができる。異なる相への減衰が観測されないように、それぞれのアニール温度は選択されるべきである。

本発明に従って使用するキャリア層は、一般的にGaPあるいはSi単結晶である。このような単結晶の表面は従来の方法で不純物を取り除かれることができて、エピタキシャル堆積のために準備されることができることが理解される。この状況では、参照が文献A.Ishizaka他、Electrochem. Soc. 33:666 (1986)になされる。

用語「実質的に1:1」は、0.8:1.2−1.2:0.8の範囲、特に0.9:1.1−1.1:0.9の範囲、好ましくは0.95:1.05−1.05:0.95の範囲、そして、もちろんまた、厳密に1:1の範囲を備える。

(本発明の実施態様)

【0014】

実施例1:本発明に従う半導体層の製造

通常の前処理の後、Siウェーハ(製造業者:Wacker、Virginia Semiconductor)が、MOVPE装置(タイプAIX200−GFR、製造業者Aixtron)内に配置される。まず、以下の実施例では更に詳細に記載されるように、エピタキシャル層がSiウェーハ上に従来の方法で堆積される。このように得られた表面に、次いで、本発明に従うIII/V半導体の層が、堆積される。このために、不活性ガスフロー(H2)が、様々な遊離体と共にロードされている。以下の遊離体が、使用される:トリメチルガリウムあるいはトリエチルガリウム、トリアルキルインジウム(適用可能な限り)、1,1−ジメチルヒドラジン、第三ブチルアルシン、第三ブチルフォスフィン、およびトリメチルアンチモン(適用可能な限り)。全てのこれらの遊離体は、たとえばAkzo Nobel HPMOから入手可能である。

例示的な組成Ga(N0.037As0.883P0.08)を有する本発明に従う半導体層の製造に対して、以下の条件が、50hPaの合計リアクタ圧力で選択された:分圧TEGa(トリエチルガリウム) 0.007hPa、TBAs(第三ブチルアルシン)0.142hPa、TBP(第三ブチルフォスフィン)0.035hPa、そして、UDMHy(ジメチルヒドラジン)0.85hPa。そこから、以下の比率:比率As/Ga 20、比率P/Ga 5および比率N/As 6、という結果になる。

50hPaの全圧を有するロードされたH2キャリヤーガスは、次いで、575℃まで加熱されたコーティングされた基板の表面の上に、22秒の間、導かれる。7.0nmの厚さを有する本発明に従う層が、得られる。本発明に従う半導体層に対する曝露期間の終了の後、MOVPE系は、それぞれのバリヤー層あるいは適応層の堆積条件に合うよう調節される。

【0015】

実施例2:光学活性素子の製造

実施例1のMOVPE装置において、最初に、以下の実施例に記載される層が、従来の方法でSiウェーハ上にエピタキシャル成長される。その後に、交互に、バリヤー層および量子ウェル層が各々堆積され、そして、バリヤー層の堆積は完了を示す。この周期的な層状構造は、全体で5つの量子ウェル層を備える。量子ウェル層として、実施例1に従う層が、使われる。全ての量子ウェル層は、同じ組成を有する。バリヤー層として、GaPが使われる。全てのバリヤー層は、同じ組成を有する。量子ウェル層は、それぞれ2nmと20nmの間の厚さを有する。バリヤー層は、5nmと500nmの間の厚さを有する。

【0016】

実施例3:本発明に従うモノリシックな集積化半導体構造

本発明に従うモノリシックな集積化半導体構造が、図1内に示される。製造のために、層B1)ないしF2)がSiウェーハA上に続いてエピタキシャル成長される。層B1)は、p形不純物ドープのGaPである。亜鉛あるいはマグネシウムが、ドーピング元素として使われる。ドーピング濃度は、概して1・1018cm−3である。層B1)の層厚は、5−300nmである。層B1)はコンタクト層であり、また電流導電性である。その後に、p形不純物ドープの(AlGa)Pから形成される層B2)が形成される。ドーピングは、概して1・1018cm−3のドーピング濃度で、亜鉛あるいはマグネシウムによってなされる。アルミニウム濃度は、III属元素の総量に関して15モル−%を超える。標準値は、15−45モル−%の範囲内にある。代替法としてp形不純物ドープの(AlGa)(NP)も、上記があてはまるドーピングおよびアルミニウム含有量に関して、また、使われることができる。窒素の比率は、V属元素の総量に関して、0−4モル−%である。層厚は、500nmと1,500nmの間にある。層B2)は導波路層であり、同時に、電流伝導層として作用する層である。その上に配設される層C)は、ドープされていないGaPから成る。層厚は、50−100nmである。それは、バリヤー層に類似した別の閉じ込めヘテロ接合である。更に、層C)は、適応層として作用する。より良い視認性のために、その上に配設される光学活性素子D)は、単一層として示される。実際には、層D)は、実施例2に従う層状構造である。層E)は、層C)に対応する。代替法として、両方の層は、また、Ga(NP)、(GaIn)(NP)あるいは(GaIn)(NaSP)層として適応されることができる。V属元素に関する窒素比率は、0−10モル−%とすることができる。後者の層の場合、III属元素の総量に関するInの比率は、0−15モル−%とすることができる。層F1)は層B2)に対応し、および、層F2)は層B1)に対応し、その違いは層F1)およびF2)がn形不純物ドープである点である。ドーピング元素として、概して2・1018cm−3のドーピング濃度を有するテルルが、使用される。層E)、F1)およびF2)の層厚は、層C)、B2)およびB1)の層厚に一致する(光学活性素子に関して反射対称の順序で)。

出力カップリングの程度を向上させるために、光学活性素子としての発光ダイオードに対して、加えて、異なるアルミニウム含有量を有する(AlGa)/P/(AlGa)/P周期的反射構造(DBR構造)が、光学活性素子の下に位置する電流伝導層内に組み込まれることができる。連続した層のアルミニウム比率は、異なっており、III属元素の総量に関して、それぞれ0−60モル−%あるいは40−100モル−%である。代替法として、個々の(AlGa)(NP)層がまた、これらのDBR構造の応力の補償のために使われることができ、Al含有量は、上記のように選択され、およびN含有量は、V属元素の総量に関して0−4モル−%である。

光学活性素子としての面発光レーザダイオード(VCSEL)に対して、光学活性素子は、上のタイプの反射構造によって、上からも下からも囲まれる。電流供給手段に対して、これらの2つのDBR鏡構造体は、n形不純物ドープあるいはp形不純物ドープであることができ、あるいはさらにいわゆる内部キャビティー電流コンタクトが、構造内全体に導入され、前記コンタクトは、ドープされていない状態で2DBR鏡を製造することを可能にしている。

【0017】

実施例4:本発明に従う半導体の基本エネルギーギャップ

V属元素の総量に関して4モル−%の窒素、90モル−%のヒ素および6モル−%の燐を備えた実施例1に従って製造された半導体層が、光ルミネセンス励起分光学によって調査された。結果は、図2内に示される。基本エネルギーギャップは、約1.4eVである。この値は、明らかに窒素相互作用なしでモデル化された1.8eVの値より低くおよび、本発明に従う半導体系内の他の素子の更なる比率と協調して窒素の混合によるエネルギーギャップの大幅な影響を示す。

【0018】

実施例5:本発明に従う光学活性素子の転位のない構造

実施例2に従って製造された光学活性素子が、高解像度X線回折(HR−XRD)および透過電子顕微鏡(TEM)によって調査された。

図3は、動的X線回折理論(図3底部)に従う理論的なプロファイルと比較した、実験的なHR−XRDプロファイル(図3最上部)を示す。個々の回折反射の観測された鮮明度および実験的回折プロファイルと理論的回折プロファイルのほぼ完璧な一致は、転位の発生のない広い面積にわたって顕著な構造の層品質を確認する。

図4は、TEM暗視野像を示す。本発明に従う5元層が、暗い層として見られることができる。より明るい層は、Ga(NP)バリヤー層である。全ての3つの層が明らかに解像され、そして、結晶構造内に大面積欠陥は見られることができない。図5の高解像度TEM画像内に、ほぼ原子的にはっきりした境界面がバリヤー層に対する本発明に従う(暗い)5元層の遷移にあり、前記境界面は転位などがない。

【0019】

実施例6:特に小さい基本エネルギーギャップを備えた半導体

実施例に類似して製造される異なる半導体層であって、しかし5.5ないし11モル−%(いつものように、V属素子の総量に関して)の範囲の窒素を含有する前記層は、20℃における光ルミネセンス分光法を用いた調査において、1.2eV未満の、さらに1.1eV未満の、基本直接エネルギーギャップを示し、それは、シリコンのエネルギーギャップ(1.124eV)を下回る。シリコンのそれを下回るエネルギーギャップを有する半導体層は、特に発光ダイオードおよびレーザダイオードの製造のために、Si/SiO2ベースの導波路構造に集積化される。特にこれらの発光エネルギーに対して、すなわちこの導波路構造において、光信号の吸収がなく、およびしたがって減衰がない。

【図面の簡単な説明】

【0020】

【図1】本発明によるモノリシックな集積化半導体構造

【図2】実施例1により製造された半導体のエネルギ・ギャップと光ルミネセンス励起の関係

【図3】実施例2により製造された光学活性素子のX線回折

【図4】本発明による5元層を示すTEM暗視野像

【図5】高解像度TEM画像

【技術分野】

【0001】

本発明は、新しいIII/V半導体、このような半導体からなる半導体層、このような半導体層を備えるモノリシックに集積化された半導体構造、このような半導体のあるいはこのような半導体層の使用法およびこのような半導体層の製造のための方法に関する。

【背景技術】

【0002】

コンピュータ技術の分野において、高信頼性および高い柔軟性と関連したより高い処理能力および信号伝導能力に対する絶え間なく増大する要求がある。従来、チップ技術は、集積化密度および動作速度あるいはサイクル周波数に関して急速な進歩を遂げてきた。更に進行するこの傾向によって、高速なチップの接続に対する問題が起こっている。高速接続と関連した重要な点は、信頼性、コスト、オンチップドライバサイズおよび性能、混信、符号歪およびチップ設計の柔軟性の欠如である。オプトエレクトロニクス部品および光導波路を使用したチップ間の接続は、多くの接続問題に対する一解決策である。光接続は、極めて高い帯域幅を有し、混信および他の干渉に対して比較的に反応しない。光接続のこれらの特性を用いて、光チャネルによって互いに高速チップを接続して、接続密度、電流消費、干渉および混信に関する相当な改良を達成することが、可能になるであろう。

【0003】

通常、高集積回路はSi技術に基づく。珪素はしかし間接遷移型半導体であり、Si技術を使用した効率的なオプトエレクトロニクス部品の製造はその結果としてほとんど可能でない。効率的なオプトエレクトロニクス部品は、しかし、これらの半導体がしばしば直接遷移型半導体であり、その結果として、高効率で光を発し、および吸収するので、III/V半導体の技術、たとえばGaAs技術を用いて製造されることができる。

集積回路を製造するために、一般に、エピタキシャル工程が、使用される。次に、もしSi技術をベースとする層とIII/V半導体の技術をベースとする層との間のコンタクトがなされるならば、それぞれの材料の格子定数が異なることが問題である(これは、また、Si基板の代わりにGaP基板にあてはまる)。これは、Si(あるいはGaP)基板上でのIII/V半導体のエピタキシャル成長中に、転位が形成される結果として有する。このような転位は、しかし、機能層厚が現在原子寸法のオーダーであるのでより一層、かなりの程度に、全部の半導体構造の機能を妨げる。高層厚の場合、格子定数の差は、基板の曲がりにつながりさえする。この理由は基本的に、高堆積温度によって、III/V半導体のエピタキシャル成長がSiあるいはGaP半導体上に生じるが、しかし、転位の生成はより高くない堆積温度ですでに始まることである。次いでこの半導体構造が、室温まで冷却すると、異なる熱膨張係数によって引き起こされる格子定数の差が、上記の応力および転位につながる。

【0004】

上記の問題をなくすために、様々なアプローチが存在する。文献EP0380815 B1において、GaAs層が、Si基板上に堆積されることができ、かつ所定の位置に規定された微小割れを形成することができ、したがって、Si基板の転位が回避され、少なくともしかし減少される、ことが記載されている。この技術は、しかし原子スケールの微小割れの制御性を欠いているという理由で高集積回路に適していない。

文献EP0297483は、Si基板上にSi技術をベースとする集積回路が設けられた、ハイブリッド集積化半導体構造を記載している。更に、GaAs技術の光学活性素子が、Si基板上に形成される。集積回路と光学活性素子との間の電気的接続は、しかし直接のコンタクトによってあるいはSi基板によって確立されるのではなく、むしろ電気ワイヤ接続によって確立される。この技術も、また高集積回路の用途に適していない。

文献DE10355357から、III/V半導体をベースとする光学活性素子による層状構造に対して、たとえば引張応力を受ける適応層によって格子定数によって引き起こされる転位を補償することが公知である。その限りにおいて公知の手段によって、電子的特性のモデリングもまた可能であり、したがって、今までアクセス可能でない発光波長がアクセス可能になる。

文献US2004/0135136 A1から、多数の異なるIII/V半導体が公知技術であるが、それらは常に層であり、Si基板上への施着に適していない。類似の考察が、文献EP1257026 A2、US6,233,264 B1、US2004/0084667 A2、Merz他、IEE Proc.−Optoelectron. 151(5):346−351 (2004)、US6,072,196、EP1553670 A2、US5,825,796、Ishizuka他Journal of Crystal Growth 272:760−764(2004))およびUS2004/0161009 A1にあてはまる。

文献EP0896406 A2には、GaPあるいはSi基板(および他のもの)上の光活性III/V半導体の層が記載され、これらの層はIII属成分としてInだけを含む。実際、このような層はInP基板に適しているだけであり、SiあるいはGaP基板上に望ましくないほど多くの転位および欠陥を形成する。文献US5,937,274は、非常に一般的な方法で異なる基板上の異なる層を記載する。

その結果、特に高集積回路の分野にとって、Si技術をベースとする、かつIII/V半導体をベースとするサブアセンブリーあるいは層列を互いにモノリシックに接続することが必要であることは、続いている。

【発明の開示】

【発明が解決しようとする課題】

【0005】

Si技術あるいはGaP技術の基板上にIII/V半導体をベースとする光学活性素子を形成するための手段を提案することが、本発明の一技術目的であり、光学活性素子への、そして、そこからの、SiベースのあるいはGaPベースのサブアセンブリーの電気的な信号の伝導が集積的に、すなわち層の接触によって、形成され、III/V半導体内に、あるいは下になっている層に対するその境界面に、非発光性再結合中心を形成する転位が事実上ない。直接接触する、すなわち層接触による、Si基板あるいはGaP基板上の安定発光およびレーザ素子を提案することが、本発明の更なる一技術目的である。Si技術ベースのプロセッサ回路からデータ電流を直接、すなわちワイヤボンド接続線なしで、光信号として送る、モノリシックに集積化された半導体構造を提供することが、本発明の別の技術目的である。更に、またそれによって発された光学信号が変調され、および/または検出されることができる、モノリシックに集積化された半導体構造を提案することも、本発明の一目的である。

(本発明および実施態様の基本)

【0006】

この技術目的を達成するために、本発明はSiあるいはGaP基板および組成GaxInyNaAsbPcSbdを有するIII/V半導体を備えた請求項1に記載のモノリシックに集積化された半導体構造を教示し、ここで、x=70−100モル−%、y=0−30モル−%、a=0.5−15モル−%、b=67.5−99.5モル−%、c=0−32.0モル−%およびd=0−15モル−%、xとyの合計は、常に100モル−%であり、a、b、cおよびdの合計は、常に100モル−%であり、そして、一方のxとyの合計と他方のaないしdの合計の比率は、実質的に1:1である。好ましくは、y=1−30モル−%、そして、c=1−32.0モル−%およびこのような半導体自体。

Pのない系の場合、Pの様に、これらの元素がN混和によって引き起こされる局所的歪界を最小限に抑えるので、Inおよび/またはSbが含まれるべきである。

以下の組成を有するIII/V半導体が、特に好ましい:

a) x=70−100モル−%、y=0−30モル−%、a=0.5−10モル−%、b=70−98.5モル−%、c=1−29.5モル−%、あるいは

b) x=85−99モル−%、y=1−15モル−%、a=0.5−10モル−%、b=70−98.5モル−%、c=1−29.5モル−%、あるいは

c) x=85−99モル−%、y=1−15モル−%、a=0.5−10モル−%、b=70−98.5モル−%、c=0−32モル−%およびd=1−10モル−%。

特に、x=>70−100モル−%、a=>1.3あるいは>1.7モル−%(任意選択でy>0あるいは1モル−%と関連して)、c=0−32モル−%および/またはb=60−99.5モル−%。好ましくは、またc=あるいは4−8モル−%の間である。好ましくは、またa=4あるいは5.5−11モル−%である。

本発明の混晶系GaInNAsPSbに従う半導体類が特徴づけられ、一方では、おそらく窒素および/燐の追加の組成のために、格子に適合され、あるいは圧迫して応力を加えられた層列が、転位を生じさせずに、GaPおよび/またはSi基板上に形成されることができる。他方では、燐含有量に関連して>0.5モル−%の窒素濃度から始まって、Γ点において、窒素のない混晶系の伝導帯状態と窒素の混合によって引き起こされる電子レベルの相互作用が起こり、それは、Γ点の基本エネルギーギャップの事実上の赤方偏移につながり、したがって、GaInNAsPSb材料系の直接遷移型半導体としての特性を強化する。たとえば、a=1−10モル−%、b=60−95モル−%およびc=2−15モル−%、好ましくはa=3−5モル−%、b=85−95モル−%およびc=4−8モル−%に対して、明確に1.8eV未満、さらに1.4eV以下までの基本エネルギーギャップという結果になる。これによって、本発明に従うこの半導体系の組成によるエネルギーギャップの大幅な影響が明白になる。

【0007】

詳細には、本発明は以下の層状構造を備えるモノリシックに集積化された半導体構造に関する:

A)ドープされたまたはドープされていないSiあるいはGaPをベースとするキャリア層、

B)任意選択として、ドープされたSi、ドープされたGaPあるいはドープされた(AlGa)Pから成る第1の電流伝導層、

C)任意選択として、第1の適応層、および

D)本発明に従う半導体層を備える光学活性素子。

層D)に対して、以下の層が続くことができる:E)任意選択で第2の適応層、およびF)ドープされたSiあるいはドープされたGaPあるいはドープされた(AlGa)Pから成る第2の電流伝導層。(AlGa)Pの場合には、Alの比率は、20−100モル−%とすることができ、およびAlとGaの比率の合計は、常に100モル−%である。層B)は、p形あるいはn形不純物ドープとすることができる。層F)が存在する場合には、もし層B)がn形不純物ドープであるならば、層F)はp形不純物ドープとすることができ、そして、その逆も同じである。

通常は、この光学素子は層状構造(D1−D2−D3)nを有し、ここで層D2は、本発明に従う半導体の量子ウェル層であり、層D1およびD3は、バリヤー層であり、そしてn=1−15である。このような光学活性素子によって、発光ダイオードとレーザダイオードが構築されることができる。端子層D1あるいはD3の1つに続いて、バリヤー層D4が、形成されることができる。バリヤー層は組成Gap−InqNrPsAstを有する半導体とすることが推奨されることができ、ここで、p=85−100モル−%、q=0−15モル−%、r=0−15モル−%、s=60−100モル−%およびt=0−40モル−%、pとqの合計は、常に100モル−%であり、r、sおよびtの合計は、常に100モル−%であり、そして、一方のpとqの合計と他方のrないしtの合計との比率は実質的に1:1であり、そして、バリヤー層は好ましくは5−50nmの層厚を有する。好ましい範囲は、次通りである:p=90−100モル−%、q=0−10モル−%、r=0−10モル−%、s=70−100モル−%およびt=0−30モル−%。層厚に対しては、2−20nmの範囲が好ましい。適応層は、組成GapInqNrPsAstを有する半導体とすることができ、ここで、p=90−100モル−%、q=0−10モル−%、r=0−10モル−%、s=70−100モル−%およびt=0−30モル−%、pとqの合計は、常に100モル−%であり、r、sとtの合計は、常に100モル−%であり、そして、一方のpとqの合計と他方のrないしtの合計との比率は実質的に1:1であり、そして、適応層は、好ましくは50−500nmの層厚を有する。

【0008】

本発明に従うモノリシックに集積化された半導体構造において、キャリア層と光学活性素子との間に配設される電流伝導層および/またはバリヤー層は、同時に、適応層であることができる。

光学活性素子の下におよび/または上に、光学活性素子に光学的に接続される、少なくとも一つの光導波路層が設けられることができる。このようにして、データ電流は、キャリア上の異なる場所で発光する光学活性素子から光受信機への光学信号として導かれることができる。他の素子、例えばファイバ等が光信号を伝導するために追加的にあるいは代わりとして使われることができることが理解される。

層A)とD)との間に、および/または層F)の外側に、少なくとも一つの周期的な反射構造が設けられた、発光ダイオードあるいはまた垂直発光レーザダイオードが、製造されることができる。

好ましくは、光学活性素子は、700−1,100nmの範囲の基本発光波長を有する。

本発明は、更に発光ダイオード(LED)、VCSEL(垂直共振器面発光レーザ)レーザダイオードあるいはVECSEL(垂直外部共振器面発光レーザ)レーザダイオードおよびモジュレータあるいは検出器構造の製造のための本発明に従う半導体あるいは本発明に従う半導体層の使用法に関する。

【0009】

最後に、本発明は以下の諸ステップを備える本発明に従う半導体層の製造のための方法に関する:ドープされたあるいはドープされていないSiあるいはGaPをベースとする基板が、MOVPE(金属有機気相エピタキシー)装置内にもたらされ、任意選択で、基板の表面は、少なくとも一つのエピタキシャルコーティング工程において、最初に、それぞれ少なくとも1つの適応層、1つのバリヤー層、1つの電流伝導層、1つの導波路層および/または1つの反射構造を設けられ、キャリヤーガスが、規定された濃度の遊離体と共にロードされ、ロードされたキャリヤーガスは、規定された持続期間の曝露の間、300℃ないし700℃の範囲内の温度まで加熱された基板の表面上に、あるいは基板上の一番上の層の表面上に伝導され、そして、半導体層が基板の表面上にあるいは基板上の一番上の層の表面上に所定の層厚でエピタキシャル形成されるように、遊離体の合計濃度および曝露の持続期間が互いに調節される。

好ましくは、以下の遊離体が、MOVPE技術のために使われる:C1−C5 トリアルキルガリウム、Ga遊離体として、特にトリエチルガリウム(Ga(C2H5)3)および/または、トリメチルガリウム(Ga(CH3)3)、C1−C5 トリアルキルインジウム、In遊離体として、特にトリメチルインジウム(In(CH3)3))、アンモニア(NH3)、モノ(C1−C8)アルキルヒドラジン、N遊離体として、特に第三ブチルヒドラジン(t−(C4H9)−NH−NH2)および/または1,1−ジ(C1−C5)アルキルヒドラジン、N遊離体として、特に1,1−ジ−メチルヒドラジン((CH3)2−N−NH2)、アルシン(AsH3)および/またはC1−C5 アルキルアルシン、As遊離体として、特に第三ブチルアルシン(t−(C4H9)−AsH2)、フォスフィン(PH3)および/またはC1−C5 アルキルフォスフィン、P遊離体として、特に第三ブチルフォスフィン(t−(C4H9)−PH2)、そして、C1−C5 トリアルキルアンチモン、Sb遊離体として、特にトリメチルアンチモン((CH3)3Sb)および/または、トリエチルアンチモン((C2H5)3Sb)、ここで、C3−C5アルキル基は、直鎖あるいは分岐とすることができる。

好ましくは、遊離体は以下のモル比率で使用される:As遊離体/III属遊離体 5−300、P遊離体/III属遊離体 0−500、N遊離体/As遊離体 0.1−10、任意選択でSb遊離体/As遊離体 0−1、ここで基板の表面温度は、500℃から630℃までの範囲に調節され、キャリヤーガスおよび遊離体の全圧は、10から1,000hPaまで、あるいは200hPaまでの範囲に調節され、キャリヤーガスの分圧に対する全ての遊離体の分圧の合計の比率は、0.005と0.1の間にあり、そして、成膜速度は0.1μm/hないし10μm/hである。特に、以下の比率が、使用されることができる:As遊離体/III属遊離体 10−100、たとえば10−30、P遊離体/III属遊離体 1−100、たとえば1−10、N遊離体/As遊離体 1−10、たとえば3−8。表面温度は、好ましくは500℃から650℃まで、特に550℃ないし600℃の範囲内とすることができる。キャリヤーガスおよび遊離体の全圧は、20hPaから100hPaまでの範囲内とすることができる。キャリヤーガスの分圧に対する全ての遊離体の分圧の比率は、0.01から0.05までの範囲内とすることができる。成膜速度は、0.1μm/hないし5μm/h、特に0.5μm/hないし3μm/hとすることができる。

【0010】

原則として、遊離体の正確な濃度は、MOVPE工程のそれぞれの遊離体の熱分解特性に依存する。層の成長速度は、III属遊離体の濃度によって決められる。Ga、および該当する場合In遊離体、の様々な分解特性をベースとして、当業者に公知のように、選択された堆積温度(基板の表面温度)に従い、適切な遊離体濃度が調節され、それは、本発明に従う半導体層内のそれぞれの元素の所望のIII属濃度につながる。V属遊離体あるいはIII/V半導体の成長表面の種類の公知の温度に依存した調和しない気化のため、MOVPE堆積内のそれぞれのV属遊離体濃度は、超過の選択された堆積温度の関数として本発明に従う半導体層内の所望の濃度に慎重に調節されるべきである。これは、当業者にとって容易に達成可能である。より高い堆積温度あるいは容易に分解されることができない遊離体に対して、該当する場合、より高いV/III比率であるが、また、上述より高いN/As比率が選択されなければならない。低い堆積温度に対して、対応して、逆の挙動があてはまる。

MOVPEに対する代替法として、もちろん他のエピタキシャル法、例えばMBE(分子線エピタキシー)、また、ガス供給源、特にV属成分の含有下で(ガス供給源MBE、GS−MBE)、CBE(化学線エピタキシー)あるいはまた、MOMBE(金属有機分子線エピタキシー)もまた、使用されることができる。これらの方法は、通常で当然公知のエピタキシー装置によって実施されることができ、およびそれぞれ適切で当然公知の遊離体および供給源が、使用されなければならない。それぞれの条件は、当業者によって容易に調節されることができる。

本発明に従う半導体構造の製造のための方法は、請求項22ないし33に記載される。

(定義)

【0011】

直接遷移型半導体は、バンド構造内の価電子帯最大値および伝導帯最小値が同じ結晶パルスベクトルで互いの反対側に位置する半導体である。それに対して対照的に、間接遷移型半導体にとって、価電子帯最大値および伝導帯最小値は、同じ結晶パルスベクトルで、互いの反対側に位置せず、異なる結晶パルスベクトルで位置する。

モノリシック半導体構造は、異なる機能半導体部分の電気コンタクトが互いに直接に接続される(好ましくはエピタキシャル)層によって生じる構造である。それに対して対照的に、ハイブリッド半導体構造では、異なる機能半導体部分の電気的コンタクトは、補助接続、例えばワイヤ接続などによって達成される。

n形不純物ドープの半導体では、電気伝導は余分な価電子を有するドナー原子のために電子によって達成される。シリコンのn形不純物ドープに対して、たとえば窒素、燐、ヒ素およびアンチモンが、使われることができる。GaPあるいは(AlGa)P半導体のn形不純物ドープに対して、たとえば、シリコンおよびテルルが、使われることができる。p形不純物ドープの半導体では、電気伝導はアクセプタ原子の結合のために正孔によって生じる。シリコンのアクセプタは、硼素、アルミニウム、ガリウムおよびインジウムである。アクセプタとしてたとえばマグネシウム、亜鉛あるいは炭素が、GaPあるいは(AlGa)Pに対して使われることができる。

もしドナーあるいはアクセプタ原子の濃度が105cm−3より下であるならば、半導体は一般的にドープされていない。ドープされた半導体は、通常1015cm−3より上の濃度を有する。

規定された電力を供給するのに充分な電気伝導度が与えられる程度まで、電流伝導層はドープされた半導体から成る。

【0012】

本発明に従うIII/V半導体は、一般的に圧迫して応力を加えられる。バンド構造の格子適応およびモデリングのために、バリヤー層が設けられ、それは引張応力を加えられることができる。それによって、III/V半導体の応力の補償が、達成される。

本発明に従う光学活性素子は、エネルギーを光放射に変換して、後者を放射して、光放射を変調しておよび/または光放射を吸収して、それを電気信号に変換する。レーザダイオードに対して、層周期nの総数は、一般的に1−5である。発光ダイオードに対して、nはしかし15までとすることができる。モジュレータあるいは検出器構造に対して、nは実質的により高くなることができて、50以上までの値を有することができる。

適応層は、SiあるいはGaP基板上のIII/V半導体をベースとする、本発明に従う半導体層あるいは半導体構造の応力の補償の役に立つ。適応層は、光発光に寄与しない。

量子ウェル層は、また、量子フィルムと呼ばれる。バリヤー層との2側面接触によって、電荷担体の運動は、閉じ込められ、そして、電荷担体は、エピタキシャル層の場合、一次元の含有内にある(主に2空間次元内の運動)。本発明に従う層状構造を有する光学活性素子は、また、多重量子ウェル(MQW)構造と呼ばれる。量子ウェル層とバリヤー層との間のエピタキシャル応力によって、基本バンドギャップに関する電子的特性が、影響される可能性がある。

【0013】

光導波路層は、広範囲にわたって従来技術から公知である。例のみとして、参照が文献「半導体光電子工学:物理および技術(Semiconductor Optoelectronics: Physics and Technology)」、J.Singh、マグロウヒル社、ニューヨーク(1995)になされる。

周期的な反射構造が、絶縁体および/またはエピタキシャル(λ/4)多層鏡である。それらは、いわゆる分布Bragg反射器(DBR)であり、光学活性素子によって放射される光を反射し、したがって、レーザ共振器内の高反射端部鏡を表す。それに関して、参照が文献「垂直共振器面発光レーザ:設計、製造、特性試験および応用例(Vertical−cavity Surface−emitting Lasers: Design, Fabrication, Characterization and Application)」、編集:C.Wilmsen他、ケンブリッジ大学出版、ケンブリッジ(1999)になされる。このような周期的な反射構造は、また、電流伝導の目的でpあるいはn形不純物ドープとすることができる。次いで、これらの周期的な反射構造は、同時に、電流伝導層の機能を受け入れる。

本発明に従うIII/V半導体は、一般的に室温であるいは動作温度で準安定である。これは、それぞれの温度での状態の熱力学のために、少なくとも2つの異なる相への減衰が生じない限り、安定な均質の相は存在しないことを意味する。この減衰は、しかし動力学的に阻害される。動力学の阻害を克服するためには、作用するのに高温が必要とされ、このために、このような準安定相は、比較的低基板温度で、概して700℃より下でだけエピタキシャル堆積することができる。低下した温度での堆積の後、本発明に従う半導体層のアニール工程が、非発光性再結合中心の減少のために、概して700℃ないし850℃の温度範囲内で実行されることができる。平衡アニール工程、同じく例えば急速熱アニール(RTA)などの不平衡法が、たとえば直ちにMOVPE反応装置内で、実行されることができる。異なる相への減衰が観測されないように、それぞれのアニール温度は選択されるべきである。

本発明に従って使用するキャリア層は、一般的にGaPあるいはSi単結晶である。このような単結晶の表面は従来の方法で不純物を取り除かれることができて、エピタキシャル堆積のために準備されることができることが理解される。この状況では、参照が文献A.Ishizaka他、Electrochem. Soc. 33:666 (1986)になされる。

用語「実質的に1:1」は、0.8:1.2−1.2:0.8の範囲、特に0.9:1.1−1.1:0.9の範囲、好ましくは0.95:1.05−1.05:0.95の範囲、そして、もちろんまた、厳密に1:1の範囲を備える。

(本発明の実施態様)

【0014】

実施例1:本発明に従う半導体層の製造

通常の前処理の後、Siウェーハ(製造業者:Wacker、Virginia Semiconductor)が、MOVPE装置(タイプAIX200−GFR、製造業者Aixtron)内に配置される。まず、以下の実施例では更に詳細に記載されるように、エピタキシャル層がSiウェーハ上に従来の方法で堆積される。このように得られた表面に、次いで、本発明に従うIII/V半導体の層が、堆積される。このために、不活性ガスフロー(H2)が、様々な遊離体と共にロードされている。以下の遊離体が、使用される:トリメチルガリウムあるいはトリエチルガリウム、トリアルキルインジウム(適用可能な限り)、1,1−ジメチルヒドラジン、第三ブチルアルシン、第三ブチルフォスフィン、およびトリメチルアンチモン(適用可能な限り)。全てのこれらの遊離体は、たとえばAkzo Nobel HPMOから入手可能である。

例示的な組成Ga(N0.037As0.883P0.08)を有する本発明に従う半導体層の製造に対して、以下の条件が、50hPaの合計リアクタ圧力で選択された:分圧TEGa(トリエチルガリウム) 0.007hPa、TBAs(第三ブチルアルシン)0.142hPa、TBP(第三ブチルフォスフィン)0.035hPa、そして、UDMHy(ジメチルヒドラジン)0.85hPa。そこから、以下の比率:比率As/Ga 20、比率P/Ga 5および比率N/As 6、という結果になる。

50hPaの全圧を有するロードされたH2キャリヤーガスは、次いで、575℃まで加熱されたコーティングされた基板の表面の上に、22秒の間、導かれる。7.0nmの厚さを有する本発明に従う層が、得られる。本発明に従う半導体層に対する曝露期間の終了の後、MOVPE系は、それぞれのバリヤー層あるいは適応層の堆積条件に合うよう調節される。

【0015】

実施例2:光学活性素子の製造

実施例1のMOVPE装置において、最初に、以下の実施例に記載される層が、従来の方法でSiウェーハ上にエピタキシャル成長される。その後に、交互に、バリヤー層および量子ウェル層が各々堆積され、そして、バリヤー層の堆積は完了を示す。この周期的な層状構造は、全体で5つの量子ウェル層を備える。量子ウェル層として、実施例1に従う層が、使われる。全ての量子ウェル層は、同じ組成を有する。バリヤー層として、GaPが使われる。全てのバリヤー層は、同じ組成を有する。量子ウェル層は、それぞれ2nmと20nmの間の厚さを有する。バリヤー層は、5nmと500nmの間の厚さを有する。

【0016】

実施例3:本発明に従うモノリシックな集積化半導体構造

本発明に従うモノリシックな集積化半導体構造が、図1内に示される。製造のために、層B1)ないしF2)がSiウェーハA上に続いてエピタキシャル成長される。層B1)は、p形不純物ドープのGaPである。亜鉛あるいはマグネシウムが、ドーピング元素として使われる。ドーピング濃度は、概して1・1018cm−3である。層B1)の層厚は、5−300nmである。層B1)はコンタクト層であり、また電流導電性である。その後に、p形不純物ドープの(AlGa)Pから形成される層B2)が形成される。ドーピングは、概して1・1018cm−3のドーピング濃度で、亜鉛あるいはマグネシウムによってなされる。アルミニウム濃度は、III属元素の総量に関して15モル−%を超える。標準値は、15−45モル−%の範囲内にある。代替法としてp形不純物ドープの(AlGa)(NP)も、上記があてはまるドーピングおよびアルミニウム含有量に関して、また、使われることができる。窒素の比率は、V属元素の総量に関して、0−4モル−%である。層厚は、500nmと1,500nmの間にある。層B2)は導波路層であり、同時に、電流伝導層として作用する層である。その上に配設される層C)は、ドープされていないGaPから成る。層厚は、50−100nmである。それは、バリヤー層に類似した別の閉じ込めヘテロ接合である。更に、層C)は、適応層として作用する。より良い視認性のために、その上に配設される光学活性素子D)は、単一層として示される。実際には、層D)は、実施例2に従う層状構造である。層E)は、層C)に対応する。代替法として、両方の層は、また、Ga(NP)、(GaIn)(NP)あるいは(GaIn)(NaSP)層として適応されることができる。V属元素に関する窒素比率は、0−10モル−%とすることができる。後者の層の場合、III属元素の総量に関するInの比率は、0−15モル−%とすることができる。層F1)は層B2)に対応し、および、層F2)は層B1)に対応し、その違いは層F1)およびF2)がn形不純物ドープである点である。ドーピング元素として、概して2・1018cm−3のドーピング濃度を有するテルルが、使用される。層E)、F1)およびF2)の層厚は、層C)、B2)およびB1)の層厚に一致する(光学活性素子に関して反射対称の順序で)。

出力カップリングの程度を向上させるために、光学活性素子としての発光ダイオードに対して、加えて、異なるアルミニウム含有量を有する(AlGa)/P/(AlGa)/P周期的反射構造(DBR構造)が、光学活性素子の下に位置する電流伝導層内に組み込まれることができる。連続した層のアルミニウム比率は、異なっており、III属元素の総量に関して、それぞれ0−60モル−%あるいは40−100モル−%である。代替法として、個々の(AlGa)(NP)層がまた、これらのDBR構造の応力の補償のために使われることができ、Al含有量は、上記のように選択され、およびN含有量は、V属元素の総量に関して0−4モル−%である。

光学活性素子としての面発光レーザダイオード(VCSEL)に対して、光学活性素子は、上のタイプの反射構造によって、上からも下からも囲まれる。電流供給手段に対して、これらの2つのDBR鏡構造体は、n形不純物ドープあるいはp形不純物ドープであることができ、あるいはさらにいわゆる内部キャビティー電流コンタクトが、構造内全体に導入され、前記コンタクトは、ドープされていない状態で2DBR鏡を製造することを可能にしている。

【0017】

実施例4:本発明に従う半導体の基本エネルギーギャップ

V属元素の総量に関して4モル−%の窒素、90モル−%のヒ素および6モル−%の燐を備えた実施例1に従って製造された半導体層が、光ルミネセンス励起分光学によって調査された。結果は、図2内に示される。基本エネルギーギャップは、約1.4eVである。この値は、明らかに窒素相互作用なしでモデル化された1.8eVの値より低くおよび、本発明に従う半導体系内の他の素子の更なる比率と協調して窒素の混合によるエネルギーギャップの大幅な影響を示す。

【0018】

実施例5:本発明に従う光学活性素子の転位のない構造

実施例2に従って製造された光学活性素子が、高解像度X線回折(HR−XRD)および透過電子顕微鏡(TEM)によって調査された。

図3は、動的X線回折理論(図3底部)に従う理論的なプロファイルと比較した、実験的なHR−XRDプロファイル(図3最上部)を示す。個々の回折反射の観測された鮮明度および実験的回折プロファイルと理論的回折プロファイルのほぼ完璧な一致は、転位の発生のない広い面積にわたって顕著な構造の層品質を確認する。

図4は、TEM暗視野像を示す。本発明に従う5元層が、暗い層として見られることができる。より明るい層は、Ga(NP)バリヤー層である。全ての3つの層が明らかに解像され、そして、結晶構造内に大面積欠陥は見られることができない。図5の高解像度TEM画像内に、ほぼ原子的にはっきりした境界面がバリヤー層に対する本発明に従う(暗い)5元層の遷移にあり、前記境界面は転位などがない。

【0019】

実施例6:特に小さい基本エネルギーギャップを備えた半導体

実施例に類似して製造される異なる半導体層であって、しかし5.5ないし11モル−%(いつものように、V属素子の総量に関して)の範囲の窒素を含有する前記層は、20℃における光ルミネセンス分光法を用いた調査において、1.2eV未満の、さらに1.1eV未満の、基本直接エネルギーギャップを示し、それは、シリコンのエネルギーギャップ(1.124eV)を下回る。シリコンのそれを下回るエネルギーギャップを有する半導体層は、特に発光ダイオードおよびレーザダイオードの製造のために、Si/SiO2ベースの導波路構造に集積化される。特にこれらの発光エネルギーに対して、すなわちこの導波路構造において、光信号の吸収がなく、およびしたがって減衰がない。

【図面の簡単な説明】

【0020】

【図1】本発明によるモノリシックな集積化半導体構造

【図2】実施例1により製造された半導体のエネルギ・ギャップと光ルミネセンス励起の関係

【図3】実施例2により製造された光学活性素子のX線回折

【図4】本発明による5元層を示すTEM暗視野像

【図5】高解像度TEM画像

【特許請求の範囲】

【請求項1】

モノリシックな集積化半導体構造であって、以下の層状構造、すなわち、

A)ドープされたあるいはドープされていないSiあるいはGaPをベースとするキャリア層、

B)任意選択として、ドープされたSi、ドープされたGaPあるいはドープされた(AlGa)Pから成る第1の電流伝導層、

C)任意選択として、第1の適応層、および

D)組成GaxInyNaAsbPcSbdを有するIII/V半導体から形成される半導体層を備える光学活性素子、の層状構造を備え、ここで、x=70−100モル−%、y=0−30モル−%、a=0.5−15モル−%、b=67.5−99.5モル−%、c=0−39.5モル−%およびd=0−15モル−%、xとyの合計は、常に100モル−%であり、a、b、cおよびdの合計は、常に100モル−%であり、そして、一方のxとyの合計と他方のaないしdの合計の比率は、実質的に1:1である、ことを特徴とする半導体構造。

【請求項2】

層D)のあとに続く下記の層状構造、すなわち

E)任意選択で第2の適応層、および

F)ドープされたSi、ドープされたGaPあるいはドープされた(AlGa)Pから成る第2の電流伝導層、の層状構造を備える、ことを特徴とする請求項1に記載の半導体構造。

【請求項3】

前記層B)は、p形不純物ドープあるいはn形不純物ドープである、ことを特徴とする請求項1あるいは2に記載の半導体構造。

【請求項4】

c=1ないし32.0モル−%である、ことを特徴とする請求項1ないし3のうち1つに記載の半導体構造。

【請求項5】

前記半導体は、直接遷移型半導体である、ことを特徴とする請求項1ないし4のうち1つに記載の半導体構造。

【請求項6】

もし前記層B)がn形不純物ドープであるならば、前記層F)はp形不純物ドープであり、そして、もし前記層B)がp形不純物ドープであるならば、前記層F)はn形不純物ドープである、ことを特徴とする請求項2ないし5のうち1つに記載の半導体構造。

【請求項7】

前記光学活性素子は、層状構造(D1−D2−D3)nを有し、ここで前記層D2は、前記半導体の量子ウェル層であり、前記層D1およびD3は、バリヤー層であり、そしてn=1−50、特に1−15である、ことを特徴とする請求項1ないし6のうち1つに記載の半導体構造。

【請求項8】

前記端子層D1あるいはD3の1つに続いて、バリヤー層D4が設けられる、ことを特徴とする請求項7に記載の半導体構造。

【請求項9】

前記バリヤー層は、組成GapInqNrPsAstを有する半導体であり、ここで、p=85−100モル−%、q=0−15モル−%、r=0−15モル−%、s=60−100モル−%およびt=0−40モル−%、pとqの合計は、常に100モル−%であり、r、sおよびtの合計は、常に100モル−%であり、そして、一方のpとqの合計と他方のrないしtの合計との比率は実質的に1:1であり、そして、前記バリヤー層は好ましくは5−50nmの層厚を有する、ことを特徴とする請求項7あるいは8に記載の半導体構造。

【請求項10】

前記第1のおよび/または前記第2の適応層は、組成GapInqNrPsAstを有する半導体であり、ここで、p=90−100モル−%、q=0−10モル−%、r=0−10モル−%、s=70−100モル−%およびt=0−30モル−%、pとqの合計は、常に100モル−%であり、r、sとtの合計は、常に100モル−%であり、そして、一方のpとqの合計と他方のrないしtの合計との比率は実質的に1:1であり、そして、前記適応層は、好ましくは50−500nmの層厚を有する、ことを特徴とする請求項1ないし9のうち1つに記載の半導体構造。

【請求項11】

前記キャリア層と前記光学活性素子との間に配設される電流伝導層および/またはバリヤー層は、同時に、適応層である、ことを特徴とする請求項1ないし10のうち1つに記載の半導体構造。

【請求項12】

前記光学活性素子の下におよび/または上に、少なくとも一つの光導波路層が設けられ、前記光学活性素子に光学的に接続される、ことを特徴とする請求項1ないし11のうち1つに記載の半導体構造。

【請求項13】

前記層A)とD)および/または前記層F)の外側との間に、少なくとも一つの周期的な反射構造が設けられる、ことを特徴とする請求項1ないし12のうち1つに記載の半導体構造。

【請求項14】

前記光学活性素子は、700nm−1,100nmの範囲の基本発光波長を有する、ことを特徴とする請求項1ないし13のうち1つに記載の半導体構造。

【請求項15】

請求項7ないし14のうち1つに記載の、モノリシックな集積化半導体構造の製造のための方法であって、

ドープされたあるいはドープされていないSiあるいはGaPをベースとするキャリア層A上に、

任意選択で、ドープされたSi、ドープされたGaPあるいはドープされた(AlGa)Pからなる第1の電流伝導層Bがエピタキシャル成長され、

任意選択で、第1の適応層Cがエピタキシャル成長され、そして、

請求項1ないし5の1つに記載の半導体を備える半導体層を含む光学活性素子を形成する多重層構造Dが、エピタキシャル成長される、ことを特徴とする方法。

【請求項16】

前記光学活性素子上に、任意選択で、第2の適応層Eがエピタキシャル成長され、そして、前記光学活性素子あるいは前記第2の適応層上に、ドープされたSiあるいはドープされたGaPあるいはドープされた(AlGa)Pからなる第2の電流伝導層Fが、エピタキシャル成長される、ことを特徴とする請求項15に記載の方法。

【請求項17】

前記層Bは、p形不純物ドープあるいはn形不純物ドープである、ことを特徴とする請求項15あるいは16に記載の方法。

【請求項18】

もし前記層B)がn形不純物ドープであるならば、前記層F)はp形不純物ドープであり、そして、もし前記層B)がp形不純物ドープであるならば、前記層F)はn形不純物ドープである、ことを特徴とする請求項17に記載の方法。

【請求項19】

前記光学要素は、層D1、D2およびD3のエピタキシャル成長によって形成され、前記エピタキシャル工程の順序は、前記層状構造が、(D1−D2−D3)nとなるように遂行され、前記層D2は、請求項1ないし4のうち1つに記載の半導体の量子ウェル層であり、前記層D1およびD3は、バリヤー層であり、そしてn=1−50、特に1−15である、ことを特徴とする請求項15ないし18のうち1つに記載の方法。

【請求項20】

前記端子層D1あるいはD3の1つに続いて、バリヤー層D4が、エピタキシャル成長される、ことを特徴とする請求項19に記載の方法。

【請求項21】

前記バリヤー層は、組成GapInqNrPsAstを有する半導体であり、ここで、p=85−100モル−%、q=0−15モル−%、r=0−15モル−%、s=60−100モル−%およびt=0−40モル−%、pとqの合計は、常に100モル−%であり、r、sおよびtの合計は、常に100モル−%であり、そして、一方のpとqの合計と他方のrないしtの合計との比率は実質的に1:1であり、そして、前記バリヤー層は好ましくは5−50nmの層厚を有する、ことを特徴とする請求項19あるいは20に記載の方法。

【請求項22】

前記第1のおよび/または第2の適応層は、組成GapInqNrPsAstを有する半導体であり、ここで、p=90−100モル−%、q=0−10モル−%、r=0−10モル−%、s=70−100モル−%およびt=0−30モル−%、pとqの合計は、常に100モル−%であり、r、sとtの合計は、常に100モル−%であり、そして、一方のpとqの合計と他方のrないしtの合計との比率は実質的に1:1であり、そして、前記適応層は、好ましくは50−500nmの層厚を有する、ことを特徴とする請求項15ないし21のうち1つに記載の方法。

【請求項23】

前記キャリア層と前記光学活性素子との間に配設される電流伝導層および/またはバリヤー層は、同時に、適応層である、ことを特徴とする請求項15ないし22のうち1つに記載の方法。

【請求項24】

前記光学活性素子の下におよび/または上に、少なくとも一つの光導波路層が設けられ、前記光学活性素子に光学的に接続される、ことを特徴とする請求項15ないし23のうち1つに記載の方法。

【請求項25】

前記層A)とD)および/または前記層F)の外側との間に、少なくとも一つの周期的な反射構造が設けられる、ことを特徴とする請求項15ないし24のうち1つに記載の方法。

【請求項26】

前記光学活性素子は、700−1,100nmの範囲の基本発光波長を有する、ことを特徴とする請求項15ないし25のうち1つに記載の方法。

【請求項27】

組成GaxInyNaAsbPcSbdを有するIII/V半導体であって、ここで、x=70−100モル−%、y=0−30モル−%、a=0.5−15モル−%、b=67.5−99.5モル−%、c=0−39.5モル−%およびd=0−15モル−%、xとyの合計は、常に100モル−%であり、a、b、cおよびdの合計は、常に100モル−%であり、そして、一方のxとyの合計と他方のaないしdの合計の比率は、実質的に1:1である、ことを特徴とするIII/V半導体。

【請求項28】

c=1ないし32.0モル−%である、ことを特徴とする請求項27に記載のIII/V半導体。

【請求項29】

前記半導体は、直接遷移型半導体である、ことを特徴とする請求項27または28に記載のIII/V半導体。

【請求項30】

前記半導体層の前記層厚は、1−50nm、好ましくは2−20nmの範囲内にある、ことを特徴とする請求項27ないし29のうち1つに記載の半導体を備える半導体層。

【請求項31】

発光ダイオード、VCSELレーザダイオード、VECSELレーザダイオード、モジュレータ構造あるいは検出器構造の製造のための、請求項27ないし29のうち1つに記載の半導体の使用法あるいは請求項30に記載の半導体層の使用法。

【請求項32】

請求項31に記載の半導体層の製造の方法であって、以下の工程、すなわち、

ドープされたあるいはドープされていないSiあるいはGaPをベースとする基板が、MOVPE装置にもたらされ、

任意選択で、前記基板の表面は、少なくとも一つのエピタキシャルコーティング工程において、最初に、それぞれ少なくとも1つの適応層、1つのバリヤー層、1つの電流伝導層、1つの導波路層および/または1つの反射構造を設けられ、

不活性キャリヤーガスが、規定された濃度の遊離体と共にロードされ、

前記ロードされたキャリヤーガスは、規定された持続期間の曝露の間、300℃ないし700℃の範囲内の温度まで加熱された前記基板の表面の上に、あるいは前記基板上の一番上の層の表面上に伝導され、そして、前記半導体層が前記基板の表面上に、あるいは前記基板上の一番上の層の表面上に、与えられた層厚でエピタキシャル形成されるように、前記遊離体の合計濃度および前記曝露の持続期間が互いに調節される、工程を含む方法。

【請求項33】

請求項32に記載の方法であって、以下の遊離体、すなわち、

C1−C5 トリアルキルガリウム、Ga遊離体として、特にトリエチルガリウム(Ga(C2H5)3)および/または、トリメチルガリウム(Ga(CH3)3)、

任意選択でC1−C5 トリアルキルインジウム、In遊離体として、特にトリメチルインジウム(In(CH3)3))、

アンモニア(NH3)、モノ(C1−C8)アルキルヒドラジン、N遊離体として、特に第三ブチルヒドラジン(t−(C4H9)−NH−NH2)および/または1,1−ジ(C1−C5)アルキルヒドラジン、N遊離体として、特に1,1−ジ−メチルヒドラジン((CH3)2−N−NH2)、

アルシン(AsH3)および/またはC1−C5 アルキルアルシン、As遊離体として、特に第三ブチルアルシン(t−(C4H9)−AsH2)、

フォスフィン(PH3)および/またはC1−C5 アルキルフォスフィン、P遊離体として、特に第三ブチルフォスフィン(t−(C4H9)−PH2)、そして、

任意選択でC1−C5 トリアルキルアンチモン、Sb遊離体として、特にトリメチルアンチモン((CH3)3Sb)および/または、トリエチルアンチモン((C2H5)3Sb)、が使用され、

ここで、C3−C5アルキル基は、直鎖あるいは分岐とすることができる、ことを特徴とする方法。

【請求項34】

請求項33に記載の方法であって、前記遊離体は、以下のモル比率、すなわち、

As遊離体/III属遊離体 5−300、

P遊離体/III属遊離体 0−500、

N遊離体/As遊離体 0.1−10、

任意選択でSb遊離体/As遊離体 0−1、で使用され、

ここで前記基板の表面温度は、500℃から630℃までの範囲に調節され、キャリヤーガスおよび遊離体の全圧は、10hPaから200hPaまでの範囲に調節され、前記キャリヤーガスの分圧に対する前記遊離体の分圧の合計の比率は、0.005と0.1の間にあり、そして、成膜速度は0.1μm/hないし10μm/hである、ことを特徴とする方法。

【請求項35】

請求項32ないし34のうち1つに記載の方法によって得られる半導体層。

【請求項36】

請求項15ないし25のうち1つに記載の方法によって得られる集積化されたモノリシックな半導体構造。

【請求項1】

モノリシックな集積化半導体構造であって、以下の層状構造、すなわち、

A)ドープされたあるいはドープされていないSiあるいはGaPをベースとするキャリア層、

B)任意選択として、ドープされたSi、ドープされたGaPあるいはドープされた(AlGa)Pから成る第1の電流伝導層、

C)任意選択として、第1の適応層、および

D)組成GaxInyNaAsbPcSbdを有するIII/V半導体から形成される半導体層を備える光学活性素子、の層状構造を備え、ここで、x=70−100モル−%、y=0−30モル−%、a=0.5−15モル−%、b=67.5−99.5モル−%、c=0−39.5モル−%およびd=0−15モル−%、xとyの合計は、常に100モル−%であり、a、b、cおよびdの合計は、常に100モル−%であり、そして、一方のxとyの合計と他方のaないしdの合計の比率は、実質的に1:1である、ことを特徴とする半導体構造。

【請求項2】

層D)のあとに続く下記の層状構造、すなわち

E)任意選択で第2の適応層、および

F)ドープされたSi、ドープされたGaPあるいはドープされた(AlGa)Pから成る第2の電流伝導層、の層状構造を備える、ことを特徴とする請求項1に記載の半導体構造。

【請求項3】

前記層B)は、p形不純物ドープあるいはn形不純物ドープである、ことを特徴とする請求項1あるいは2に記載の半導体構造。

【請求項4】

c=1ないし32.0モル−%である、ことを特徴とする請求項1ないし3のうち1つに記載の半導体構造。

【請求項5】

前記半導体は、直接遷移型半導体である、ことを特徴とする請求項1ないし4のうち1つに記載の半導体構造。

【請求項6】

もし前記層B)がn形不純物ドープであるならば、前記層F)はp形不純物ドープであり、そして、もし前記層B)がp形不純物ドープであるならば、前記層F)はn形不純物ドープである、ことを特徴とする請求項2ないし5のうち1つに記載の半導体構造。

【請求項7】

前記光学活性素子は、層状構造(D1−D2−D3)nを有し、ここで前記層D2は、前記半導体の量子ウェル層であり、前記層D1およびD3は、バリヤー層であり、そしてn=1−50、特に1−15である、ことを特徴とする請求項1ないし6のうち1つに記載の半導体構造。

【請求項8】

前記端子層D1あるいはD3の1つに続いて、バリヤー層D4が設けられる、ことを特徴とする請求項7に記載の半導体構造。

【請求項9】

前記バリヤー層は、組成GapInqNrPsAstを有する半導体であり、ここで、p=85−100モル−%、q=0−15モル−%、r=0−15モル−%、s=60−100モル−%およびt=0−40モル−%、pとqの合計は、常に100モル−%であり、r、sおよびtの合計は、常に100モル−%であり、そして、一方のpとqの合計と他方のrないしtの合計との比率は実質的に1:1であり、そして、前記バリヤー層は好ましくは5−50nmの層厚を有する、ことを特徴とする請求項7あるいは8に記載の半導体構造。

【請求項10】

前記第1のおよび/または前記第2の適応層は、組成GapInqNrPsAstを有する半導体であり、ここで、p=90−100モル−%、q=0−10モル−%、r=0−10モル−%、s=70−100モル−%およびt=0−30モル−%、pとqの合計は、常に100モル−%であり、r、sとtの合計は、常に100モル−%であり、そして、一方のpとqの合計と他方のrないしtの合計との比率は実質的に1:1であり、そして、前記適応層は、好ましくは50−500nmの層厚を有する、ことを特徴とする請求項1ないし9のうち1つに記載の半導体構造。

【請求項11】

前記キャリア層と前記光学活性素子との間に配設される電流伝導層および/またはバリヤー層は、同時に、適応層である、ことを特徴とする請求項1ないし10のうち1つに記載の半導体構造。

【請求項12】

前記光学活性素子の下におよび/または上に、少なくとも一つの光導波路層が設けられ、前記光学活性素子に光学的に接続される、ことを特徴とする請求項1ないし11のうち1つに記載の半導体構造。

【請求項13】

前記層A)とD)および/または前記層F)の外側との間に、少なくとも一つの周期的な反射構造が設けられる、ことを特徴とする請求項1ないし12のうち1つに記載の半導体構造。

【請求項14】

前記光学活性素子は、700nm−1,100nmの範囲の基本発光波長を有する、ことを特徴とする請求項1ないし13のうち1つに記載の半導体構造。

【請求項15】

請求項7ないし14のうち1つに記載の、モノリシックな集積化半導体構造の製造のための方法であって、

ドープされたあるいはドープされていないSiあるいはGaPをベースとするキャリア層A上に、

任意選択で、ドープされたSi、ドープされたGaPあるいはドープされた(AlGa)Pからなる第1の電流伝導層Bがエピタキシャル成長され、

任意選択で、第1の適応層Cがエピタキシャル成長され、そして、

請求項1ないし5の1つに記載の半導体を備える半導体層を含む光学活性素子を形成する多重層構造Dが、エピタキシャル成長される、ことを特徴とする方法。

【請求項16】

前記光学活性素子上に、任意選択で、第2の適応層Eがエピタキシャル成長され、そして、前記光学活性素子あるいは前記第2の適応層上に、ドープされたSiあるいはドープされたGaPあるいはドープされた(AlGa)Pからなる第2の電流伝導層Fが、エピタキシャル成長される、ことを特徴とする請求項15に記載の方法。

【請求項17】

前記層Bは、p形不純物ドープあるいはn形不純物ドープである、ことを特徴とする請求項15あるいは16に記載の方法。

【請求項18】

もし前記層B)がn形不純物ドープであるならば、前記層F)はp形不純物ドープであり、そして、もし前記層B)がp形不純物ドープであるならば、前記層F)はn形不純物ドープである、ことを特徴とする請求項17に記載の方法。

【請求項19】

前記光学要素は、層D1、D2およびD3のエピタキシャル成長によって形成され、前記エピタキシャル工程の順序は、前記層状構造が、(D1−D2−D3)nとなるように遂行され、前記層D2は、請求項1ないし4のうち1つに記載の半導体の量子ウェル層であり、前記層D1およびD3は、バリヤー層であり、そしてn=1−50、特に1−15である、ことを特徴とする請求項15ないし18のうち1つに記載の方法。

【請求項20】

前記端子層D1あるいはD3の1つに続いて、バリヤー層D4が、エピタキシャル成長される、ことを特徴とする請求項19に記載の方法。

【請求項21】

前記バリヤー層は、組成GapInqNrPsAstを有する半導体であり、ここで、p=85−100モル−%、q=0−15モル−%、r=0−15モル−%、s=60−100モル−%およびt=0−40モル−%、pとqの合計は、常に100モル−%であり、r、sおよびtの合計は、常に100モル−%であり、そして、一方のpとqの合計と他方のrないしtの合計との比率は実質的に1:1であり、そして、前記バリヤー層は好ましくは5−50nmの層厚を有する、ことを特徴とする請求項19あるいは20に記載の方法。

【請求項22】

前記第1のおよび/または第2の適応層は、組成GapInqNrPsAstを有する半導体であり、ここで、p=90−100モル−%、q=0−10モル−%、r=0−10モル−%、s=70−100モル−%およびt=0−30モル−%、pとqの合計は、常に100モル−%であり、r、sとtの合計は、常に100モル−%であり、そして、一方のpとqの合計と他方のrないしtの合計との比率は実質的に1:1であり、そして、前記適応層は、好ましくは50−500nmの層厚を有する、ことを特徴とする請求項15ないし21のうち1つに記載の方法。

【請求項23】

前記キャリア層と前記光学活性素子との間に配設される電流伝導層および/またはバリヤー層は、同時に、適応層である、ことを特徴とする請求項15ないし22のうち1つに記載の方法。

【請求項24】

前記光学活性素子の下におよび/または上に、少なくとも一つの光導波路層が設けられ、前記光学活性素子に光学的に接続される、ことを特徴とする請求項15ないし23のうち1つに記載の方法。

【請求項25】

前記層A)とD)および/または前記層F)の外側との間に、少なくとも一つの周期的な反射構造が設けられる、ことを特徴とする請求項15ないし24のうち1つに記載の方法。

【請求項26】

前記光学活性素子は、700−1,100nmの範囲の基本発光波長を有する、ことを特徴とする請求項15ないし25のうち1つに記載の方法。

【請求項27】

組成GaxInyNaAsbPcSbdを有するIII/V半導体であって、ここで、x=70−100モル−%、y=0−30モル−%、a=0.5−15モル−%、b=67.5−99.5モル−%、c=0−39.5モル−%およびd=0−15モル−%、xとyの合計は、常に100モル−%であり、a、b、cおよびdの合計は、常に100モル−%であり、そして、一方のxとyの合計と他方のaないしdの合計の比率は、実質的に1:1である、ことを特徴とするIII/V半導体。

【請求項28】

c=1ないし32.0モル−%である、ことを特徴とする請求項27に記載のIII/V半導体。

【請求項29】

前記半導体は、直接遷移型半導体である、ことを特徴とする請求項27または28に記載のIII/V半導体。

【請求項30】

前記半導体層の前記層厚は、1−50nm、好ましくは2−20nmの範囲内にある、ことを特徴とする請求項27ないし29のうち1つに記載の半導体を備える半導体層。

【請求項31】

発光ダイオード、VCSELレーザダイオード、VECSELレーザダイオード、モジュレータ構造あるいは検出器構造の製造のための、請求項27ないし29のうち1つに記載の半導体の使用法あるいは請求項30に記載の半導体層の使用法。

【請求項32】

請求項31に記載の半導体層の製造の方法であって、以下の工程、すなわち、

ドープされたあるいはドープされていないSiあるいはGaPをベースとする基板が、MOVPE装置にもたらされ、

任意選択で、前記基板の表面は、少なくとも一つのエピタキシャルコーティング工程において、最初に、それぞれ少なくとも1つの適応層、1つのバリヤー層、1つの電流伝導層、1つの導波路層および/または1つの反射構造を設けられ、

不活性キャリヤーガスが、規定された濃度の遊離体と共にロードされ、

前記ロードされたキャリヤーガスは、規定された持続期間の曝露の間、300℃ないし700℃の範囲内の温度まで加熱された前記基板の表面の上に、あるいは前記基板上の一番上の層の表面上に伝導され、そして、前記半導体層が前記基板の表面上に、あるいは前記基板上の一番上の層の表面上に、与えられた層厚でエピタキシャル形成されるように、前記遊離体の合計濃度および前記曝露の持続期間が互いに調節される、工程を含む方法。

【請求項33】

請求項32に記載の方法であって、以下の遊離体、すなわち、

C1−C5 トリアルキルガリウム、Ga遊離体として、特にトリエチルガリウム(Ga(C2H5)3)および/または、トリメチルガリウム(Ga(CH3)3)、

任意選択でC1−C5 トリアルキルインジウム、In遊離体として、特にトリメチルインジウム(In(CH3)3))、

アンモニア(NH3)、モノ(C1−C8)アルキルヒドラジン、N遊離体として、特に第三ブチルヒドラジン(t−(C4H9)−NH−NH2)および/または1,1−ジ(C1−C5)アルキルヒドラジン、N遊離体として、特に1,1−ジ−メチルヒドラジン((CH3)2−N−NH2)、

アルシン(AsH3)および/またはC1−C5 アルキルアルシン、As遊離体として、特に第三ブチルアルシン(t−(C4H9)−AsH2)、

フォスフィン(PH3)および/またはC1−C5 アルキルフォスフィン、P遊離体として、特に第三ブチルフォスフィン(t−(C4H9)−PH2)、そして、

任意選択でC1−C5 トリアルキルアンチモン、Sb遊離体として、特にトリメチルアンチモン((CH3)3Sb)および/または、トリエチルアンチモン((C2H5)3Sb)、が使用され、

ここで、C3−C5アルキル基は、直鎖あるいは分岐とすることができる、ことを特徴とする方法。

【請求項34】

請求項33に記載の方法であって、前記遊離体は、以下のモル比率、すなわち、

As遊離体/III属遊離体 5−300、

P遊離体/III属遊離体 0−500、

N遊離体/As遊離体 0.1−10、

任意選択でSb遊離体/As遊離体 0−1、で使用され、

ここで前記基板の表面温度は、500℃から630℃までの範囲に調節され、キャリヤーガスおよび遊離体の全圧は、10hPaから200hPaまでの範囲に調節され、前記キャリヤーガスの分圧に対する前記遊離体の分圧の合計の比率は、0.005と0.1の間にあり、そして、成膜速度は0.1μm/hないし10μm/hである、ことを特徴とする方法。

【請求項35】

請求項32ないし34のうち1つに記載の方法によって得られる半導体層。

【請求項36】

請求項15ないし25のうち1つに記載の方法によって得られる集積化されたモノリシックな半導体構造。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−102209(P2013−102209A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2013−11977(P2013−11977)

【出願日】平成25年1月25日(2013.1.25)

【分割の表示】特願2007−551544(P2007−551544)の分割

【原出願日】平成18年1月26日(2006.1.26)

【出願人】(507158983)フィリップス ウニベルジテート マールブルグ (2)

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成25年1月25日(2013.1.25)

【分割の表示】特願2007−551544(P2007−551544)の分割

【原出願日】平成18年1月26日(2006.1.26)

【出願人】(507158983)フィリップス ウニベルジテート マールブルグ (2)

【Fターム(参考)】

[ Back to top ]