ISFETおよびISFETアレイ

【課題】センサ感度を向上したISFETおよびこのISFETセルを適用したISFETアレイを提供する。

【解決手段】第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域12と、ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、ウェル領域12上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に、ドレイン領域16に隣接して配置されたトランスファゲート電極20と、ゲート絶縁膜18に接触する液体試料26と、液体試料26中に配置された参照電極24とを備えるISFET2およびこのISFETセルを適用したISFETアレイ4。

【解決手段】第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域12と、ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、ウェル領域12上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に、ドレイン領域16に隣接して配置されたトランスファゲート電極20と、ゲート絶縁膜18に接触する液体試料26と、液体試料26中に配置された参照電極24とを備えるISFET2およびこのISFETセルを適用したISFETアレイ4。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ISFETおよびISFETアレイに関し、特に、検出感度を向上したISFETおよびISFETアレイに関する。

【背景技術】

【0002】

従来のイオン感応性電界効果トランジスタ(ISFET:Ion Sesitive Field Effect Transistor)からなるイオンセンサとして、バックゲートとソースとの間、およびバックゲートとドレインとの間に発生するバックゲート光電流を取り出すためのゲート電極を備え、このバックゲート光電流を用いて、ISFETのソースやドレインにおいて発生する光電流を補正する構成が開示されている(例えば、特許文献1参照。)。

【0003】

また、上記ISFETを2次元的に複数個配置し、pHの2次元分布を測定するものとして、水素イオン濃度分布測定装置がある(例えば、特許文献2参照。)。

【0004】

一方、特許文献2に係るISFETアレイを改良し、ISFETアレイセル毎にISFETの切り替えスイッチ用MOSFETを備えるISFETアレイも開示されている(例えば、特許文献3参照。)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−164359号公報

【特許文献2】特開平05−33745号公報

【特許文献3】特許第4137239号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1に係るISFETでは、バルクに流れる電流で光読み出しを行うため、ノイズ情報が光読み出し電流に含まれる。また、アレイ化を図る場合、バルクに流れる電流で光読み出しを行うため、pウェル領域を互いに隣接セル間で分離する必要があり、構造が複雑となり、アレイ化が難しい。

【0007】

特許文献2に係るISFETアレイでは、一回測定して、次に測定するまで、安定化するのに時間を要する。

【0008】

従来の技術では、ISFETをアレイ化した場合、画素選択されていない時に画素が駆動していないため、測定値が安定しにくい。また、ISFETセルが選択回路により選択されてからオン状態になって動作が安定化するまでに時間がかかる。

【0009】

本発明の目的は、検出感度を向上したISFETおよび当該ISFETセルを適用したISFETアレイを提供することにある。

【課題を解決するための手段】

【0010】

本発明の一態様によれば、第1導電型を有する半導体基板と、前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域と、前記ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、前記ソース領域と、前記ウェル領域と、前記ドレイン領域上に配置されたゲート絶縁膜と、前記ゲート絶縁膜上に、前記ドレイン領域に隣接して配置されたトランスファゲート電極と、前記ゲート絶縁膜に接触する液体試料と、前記液体試料中に配置された参照電極とを備えるISFETが提供される。

【0011】

本発明の他の態様によれば、第1導電型を有する半導体基板と、前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域と、前記第1ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、前記第1ウェル領域上に配置されたゲート絶縁膜と、前記ゲート絶縁膜上に配置されたイオン感応膜と、前記ソース領域と前記ドレイン領域間に接続される蓄積キャパシタと、前記イオン感応膜に接触する液体試料と、前記液体試料中に配置された参照電極とを備えるISFETが提供される。

【0012】

本発明の他の態様によれば、第1導電型を有する半導体基板と、前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域と、前記第1ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、前記第1ウェル領域上に配置されたゲート絶縁膜と、前記ソース領域と前記ドレイン領域間の前記ゲート絶縁膜上に配置されたゲートプラグ電極と、前記ドレイン領域上に配置されたドレインプラグ電極と、前記ソース領域と前記前記ドレインプラグ電極間に接続され、積層電極構造からなる蓄積キャパシタと、前記ゲートプラグ電極上に配置された遮光膜と、前記遮光膜上に配置されたイオン感応膜と、前記イオン感応膜に接触する液体試料と、前記液体試料中に配置された参照電極とを備えるISFETが提供される。

【0013】

本発明の他の態様によれば、行方向に延伸する複数のワード線と、前記ワード線に直交し、列方向に延伸する複数のビット線と、前記複数のワード線に対してそれぞれドレインが接続された複数の垂直選択トランジスタと、前記複数の垂直選択トランジスタのそれぞれゲートが接続された垂直走査回路と、前記複数のビット線に対して、それぞれソースが接続された水平選択トランジスタと、前記複数の水平トランジスタのそれぞれゲートが接続された水平走査回路と、前記ワード線と前記ビット線の交差部に配置されたISFETセルとを備え、前記ISFETセルは、第1導電型を有する半導体基板と、前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域と、前記ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、前記ウェル領域上に配置されたゲート絶縁膜と、前記ゲート絶縁膜上に、前記ドレイン領域に隣接して配置されたトランスファゲート電極と、前記ゲート絶縁膜に接触する液体試料と、前記液体試料中に配置された参照電極とを備えるISFETアレイが提供される。

【0014】

本発明の他の態様によれば、行方向に延伸する複数のワード線と、前記ワード線に直交し、列方向に延伸する複数のビット線と、前記複数のワード線に対してそれぞれドレインが接続された複数の垂直選択トランジスタと、前記複数の垂直選択トランジスタのそれぞれゲートが接続された垂直走査回路と、前記複数のビット線に対して、それぞれソースが接続された水平選択トランジスタと、前記複数の水平トランジスタのそれぞれゲートが接続された水平走査回路と、前記ワード線と前記ビット線の交差部に配置されたISFETセルとを備え、前記ISFETセルは、第1導電型を有する半導体基板と、前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域と、前記第1ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、前記第1ウェル領域上に配置されたゲート絶縁膜と、前記ゲート絶縁膜上に配置されたイオン感応膜と、前記ソース領域と前記ドレイン領域間に接続される蓄積キャパシタと、前記イオン感応膜に接触する液体試料と、前記液体試料中に配置された参照電極とを備えるISFETアレイが提供される。

【発明の効果】

【0015】

本発明によれば、検出感度を向上したISFETおよび当該ISFETセルを適用したISFETアレイを提供することができる。

【図面の簡単な説明】

【0016】

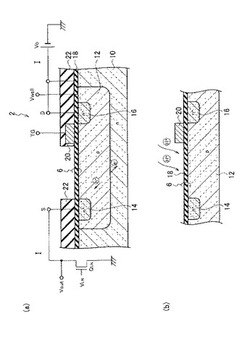

【図1】(a)第1の実施の形態に係るISFETの模式的断面構造図、(b)図1(a)のイオン検出部の拡大された模式的断面構造図。

【図2】第1の実施の形態に係るISFETを適用したイオン検出動作の模式的説明図。

【図3】第1の実施の形態に係るISFETのイオン検出動作を説明する回路構成図。

【図4】第1の実施の形態に係るISFETの模式的平面パターン構成図。

【図5】第1の実施の形態に係るISFETの光検出時のエネルギーポテンシャルダイヤグラム。

【図6】第1の実施の形態に係るISFETのイオン検出時のエネルギーポテンシャルダイヤグラム。

【図7】第1の実施の形態に係るISFETをアレイ状に配列したISFETアレイ上に試料セルが搭載された様子を表す模式的鳥瞰構造図。

【図8】図7に対応するISFETアレイを用いて検出したpH分布の様子を表す模式的鳥瞰構造図。

【図9】第1の実施の形態に係るISFETをアレイ状に配列したISFETアレイの模式的回路ブロック構成図。

【図10】第2の実施の形態に係るISFETの模式的断面構造図。

【図11】(a)第2の実施の形態に係るISFETの模式的回路構成図、(b)図11(a)の簡易な回路表示図。

【図12】(a)第2の実施の形態に係るISFETにおいて、選択回路オン状態における動作説明図、(b)第2の実施の形態に係るISFETにおいて、選択回路オフ状態における動作説明図。

【図13】第2の実施の形態に係るISFETをアレイ状に配列したISFETアレイの模式的回路ブロック構成図。

【図14】図13の動作モードの説明図。

【図15】第3の実施の形態に係るISFETの模式的断面構造であって、イオン検出動作の模式的説明図。

【図16】第3の実施の形態に係るISFETの模式的回路構成図。

【図17】第3の実施の形態に係るISFETをアレイ状に配列したISFETアレイの模式的回路ブロック構成図。

【図18】第4の実施の形態に係るISFETの模式的断面構造であって、イオン検出動作の模式的説明図。

【図19】第5の実施の形態に係るISFETの模式的断面構造であって、イオン検出動作の模式的説明図。

【発明を実施するための形態】

【0017】

次に、図面を参照して、本発明の第1〜第5の実施の形態を説明する。以下の図面の記載において、同一又は類似の部分には同一又は類似の符号を付している。ただし、図面は模式的なものであり、厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なることに留意すべきである。したがって、具体的な厚みや寸法は以下の説明を参酌して判断すべきものである。又、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。

【0018】

又、以下に示す第1〜第5の実施の形態は、この発明の技術的思想を具体化するための装置や方法を例示するものであって、この発明の実施の形態は、構成部品の材質、形状、構造、配置等を下記のものに特定するものでない。この発明の実施の形態は、特許請求の範囲において、種々の変更を加えることができる。

【0019】

[第1の実施の形態]

(ISFET)

第1の実施の形態に係るISFET2の模式的断面構造は、図1(a)に示すように表され、図1(a)のイオン検出部の拡大された模式的断面構造は、図1(b)に示すように表される。

【0020】

また、第1の実施の形態に係るISFET2を適用したイオン検出動作時の構成は、図2に示すように表される。さらに、第1の実施の形態に係るISFET2のイオン検出動作を説明する回路構成は、図3に示すように表される。ここで、図1(a)および図2は、後述する図4のI−I線に沿う模式的断面構造に相当している。

【0021】

第1の実施の形態に係るISFET2は、図1(a)に示すように、第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域12と、ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、ウェル領域12上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に、ドレイン領域16に隣接して配置されたトランスファゲート電極20とを備える。

【0022】

ここで、イオン検出部6は、図1(b)に示すように、ソース領域14とドレイン領域16間のウェル領域12と、ウェル領域12上に配置されたゲート絶縁膜18からなる。ここで、ゲート絶縁膜18には、例えば、タンタルオキサイド、アルミナ、若しくはシリコン窒化膜を適用することができる。若しくは、シリコン熱酸化膜上にシリコン窒化膜を積層した構造、シリコン熱酸化膜上にタンタルオキサイドを成膜した構造でも良い。さらに、シリコン熱酸化膜、シリコン窒化膜、タンタルオキサイドの順に積層した構造のゲート絶縁膜(イオン感応膜)はシリコン窒化膜による防水性、タンタルオキサイドの優れた感度、ドリフト特性の面から、尚良い。ゲート絶縁膜18上に付着した、例えば、H+イオンなどによって、ゲート絶縁膜18下のウェル領域12に形成されるチャネル領域の電位が変化する。この結果、ソース領域14とドレイン領域16間の電流導通状態が変調され、この電流値を検出することによって、例えば、pH値などを検出することができる。

【0023】

第1の実施の形態に係るISFET2を適用したイオン検出動作時の構成は、図2に示すように表される。イオン検出部6のゲート絶縁膜18には、液体試料26が接触しており、液体試料26中には、参照電極24が配置されている。

【0024】

参照電極24は、ガラス封止されたキャピラリー電極構造を備え、当該キャピラリー電極には、一定の参照電圧VREFが供給される。また、ガラス材料としては、耐酸性、耐熱性、耐水性の良好な、例えば、石英などによって形成可能である。

【0025】

イオン感応膜を透過した光を下のSi基板内のpn接合で検知するため、感応膜は、目的の波長領域の光を透過する材料であれば良い。可視光の場合はシリコン窒素化膜、タンタルオキサイドなどが挙げられる。

【0026】

また、第1の実施の形態に係るISFET2は、ドレイン領域16に接続された電源電圧VDと、ソース領域14に接続されたMOSFETQLNとを備えていても良い。

【0027】

第1の実施の形態に係るISFET2は、図3に示すように、イオン検出部6のイオン検出トランジスタQiと、トランスファゲートTGによるトランスファゲートトランジスタQGの直列回路で構成され、トランスファゲートトランジスタQGのドレイン領域16に電源電圧VDが接続され、イオン検出トランジスタQiのソース領域14には、MOSFETQLNが接続される。

【0028】

図3に示すように、第1の実施の形態に係るISFET2において、イオン検出トランジスタQiのゲート上の参照電極REFGには参照電圧VREFが印加されている。イオン検出トランジスタQiのゲート部がイオン検出部6に相当し、液体界面のポテンシャルによる入力イオン信号を受信する。出力信号は、イオン検出トランジスタQiに直列接続されたMOSFETQLNのドレインから、ソースフォロアの出力電圧Voutとして得る。この結果、MOSFETQLNのドレイン端子より得られるソースフォロアの出力電圧Voutが、入力イオン信号に対して、リニアに応答する。

【0029】

(イオン検出動作)

第1の実施の形態に係るISFET2の模式的平面パターン構成は、図4に示すように表される。また、第1の実施の形態に係るISFETの光検出時のエネルギーポテンシャルダイヤグラムは、図5に示すように表され、イオン検出時のエネルギーポテンシャルダイヤグラムは、図6に示すように表される。

【0030】

第1の実施の形態に係るISFET2において、トランスファゲート電極20の電位は、リセット情報・光情報の検出時は、オフ状態のローレベル、pHイオン情報の検出時は、オン状態のハイレベルとし、トランスファゲート電極20の電位よってオン、オフ制御することができる。

【0031】

―リセット情報・光情報の検出―

リセット取得モードにおいては、図5に示すように、トランスファゲート電極20の電位をローレベルにして、トランスファゲートトランジスタQGをオフ状態にする。このとき、イオン検出部6からドレイン領域16へのキャリア(電子)の流れは、トランスファゲート電極(TG)直下のポテンシャルバリアによって、塞き止められる。この状態では、ソース領域14近傍の電子は半導体基板10側に流出し、一方、ソース領域14近傍の正孔は、ソース領域14に流入する。

【0032】

―イオン情報の検出―

次に、ISFETモードにおいては、図6に示すように、トランスファゲート電極20の電位をハイレベルにして、トランスファゲートトランジスタQGをオン状態にする。このとき、トランスファゲート電極(TG)直下のポテンシャルバリア高さが低下するため、イオン検出部6からドレイン領域16へのキャリア(電子)流入が引き起こされる。また、この状態では、ソース領域14近傍の電子は半導体基板10側に流出する。一方、ソース領域14近傍の正孔は、ソース領域14に流入する。

【0033】

したがって、リセット取得モードにおいて得られたリセット情報・光情報をISFETモードにおいては、得られたデータから差し引くことによって、正確なイオン情報を検出することができる。

【0034】

第1の実施の形態に係るISFET2においては、バックゲート(ウェル領域12)とソース領域14間、バックゲート(ウェル領域12)とドレイン領域16間に発生するバックゲート光電流を、トランスファゲート電極20のオン・オフ動作によって取り出すことができる。

【0035】

尚、第1の実施の形態に係るISFET2においては、トランスファゲート電極20およびドレイン領域16・ソース領域14上をパッシベーション膜22で被覆し、イオン検出部6のパッシベーション膜22を開口した構成とすることがイオン検出感度を向上する上で望ましい。

【0036】

また、第1の実施の形態に係るISFET2においては、トランスファゲート電極20に加える電圧を調節することにより、リセット情報、光情報を取得するモードと、pHを取得するモードを切り替えることができるため、正確なイオン情報を検出することができる。

【0037】

(ISFETアレイ)

第1の実施の形態に係るISFET2によって構成されたISFETセルCijを、半導体基板10上に、アレイ状に配列したISFETアレイ4上に試料セル100が搭載された様子を表す模式的鳥瞰構造は、図7に示すように表され、図7に対応するISFETアレイ4を用いて検出したpH分布200の様子を表す模式的鳥瞰構造は、図8に示すように表される。図7および図8に示すように、各々のISFETセルCijに対応して、各々のpH値pHijが検出される。

【0038】

第1の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4の模式的回路ブロック構成は、図9に示すように、行方向に延伸する複数のワード線WL1,WL2,…,WLmと、ワード線WL1,WL2,…,WLmに直交し、列方向に延伸する複数のビット線BL1,BL2,…,BLnと、複数のワード線線WL1,WL2,…,WLmに対してそれぞれドレインが接続された複数の垂直選択トランジスタQV1,QV2,…,QVmと、複数の垂直選択トランジスタQV1,QV2,…,QVmのそれぞれゲートが接続された垂直走査回路30と、複数のビット線BL1,BL2,…,BLnに対して、それぞれソースが接続された水平選択トランジスタQH1,QH2,…,QHnと、複数の水平選択トランジスタQH1,QH2,…,QHnのそれぞれゲートが接続された水平走査回路32と、ワード線WL1,WL2,…,WLmとビット線BL1,BL2,…,BLnの交差部に配置されたISFETセルCmnとを備える。

【0039】

ここで、ISFETセルCmnは、図9に示すように、イオン検出トランジスタQmnとトランスファゲートトランジスタQGとの直列回路からなる。

【0040】

ISFETセルCmnは、前述の図2に示すように、第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域12と、ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、ウェル領域12上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に、ドレイン領域16に隣接して配置されたトランスファゲート電極20と、ゲート絶縁膜18に接触する液体試料26と、液体試料26中に配置された参照電極24とを備える。

【0041】

ここで、各々のISFETセルCmnのゲート絶縁膜18には、例えば、タンタルオキサイド、若しくはシリコン窒化膜を適用することができる。各々のISFETセルCmnのゲート絶縁膜18上に付着した、例えば、H+イオンなどによって、ゲート絶縁膜18下のウェル領域12に形成されるチャネル領域の電位が変化する。この結果、ソース領域14とドレイン領域16間の電流導通状態が変調され、この電流値を検出することによって、例えば、pH値などを検出することができる。

【0042】

また、第1の実施の形態に係るISFETアレイ4は、複数の垂直選択トランジスタQV1,QV2,…,QVmのソースを共通接続して得られた出力端子と接地電位間に接続されたMOSFETQVNと、複数の水平選択トランジスタQH1,QH2,…,QHnのドレインを共通接続して得られた電源ラインに接続された電源電圧VDDと、トランスファゲート電極20を共通化したトランスファゲートラインに接続されたトランスファゲート電圧VTGとを備えていても良い。

【0043】

イオン感応膜を透過した光を下のSi基板内のPN接合で検知するため、感応膜は、目的の波長領域の光を透過する材料。可視光の場合はシリコン窒素化膜、タンタルオキサイドなどが挙げられる。

【0044】

また、第1の実施の形態に係るISFETアレイ4において、MOSFETQVNは、より簡単な構成を実現するためには、抵抗で置換しても良い。

【0045】

バックゲート(ウェル領域12)からリセットを読み出す場合は、アレイ化した場合、各ISFETセルCijでバックゲート(ウェル領域12)を互いに分離して、独立させる必要があるが、第1の実施の形態に係るISFETアレイ4においては、図9に示すように、トランスファゲート電極20を共通化して、トランスファゲート電位VTGを加えることができる。

【0046】

また、第1の実施の形態に係るISFETアレイ4においては、ISFETアレイ4が配置された半導体基板10上に試料セル100を配置し、リセット情報・光情報の検出時は、ISFETセルCijのトランスファゲート電極20のトランスファゲート電圧VTGをオフ状態のローレベルとし、pHイオン情報の検出時は、オン状態のハイレベルとし、トランスファゲート電極20のトランスファゲート電圧VTGによってオン、オフ制御することによって、リセット情報・光情報のイメージ情報と、pHイオン分布情報の両方を検出することができる。

【0047】

[第2の実施の形態]

(ISFET)

第2の実施の形態に係るISFETの模式的断面構造は、図10に示すように表される。また、第2の実施の形態に係るISFETの模式的回路構成は図11(a)に示すように表され、図11(a)の簡易な回路表示は、図11(b)に示すように表される。

【0048】

第2の実施の形態に係るISFET2は、図10〜図11に示すように、第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域12と、第1ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、第1ウェル領域上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に配置されたイオン感応膜19と、ソース領域14とドレイン領域16間に接続される蓄積キャパシタCSと、イオン感応膜19に接触する液体試料26と、液体試料26中に配置された参照電極24とを備える。

【0049】

また、第2の実施の形態に係るISFET2は、半導体基板10上に配置され、第1導電型を有する第2ウェル領域23と、第2ウェル領域23上に配置され、第1導電型を有する第2ウェルコンタクト領域13と、第2ウェル領域上に配置されたゲート絶縁膜18上に配置され、第2ウェル領域23との間で蓄積キャパシタCSを形成するキャパシタ電極21とを備えていても良い。

【0050】

また、第2の実施の形態に係るISFET2において、ドレイン領域16は、キャパシタ電極21に接続され、ソース領域14は、ウェルコンタクト領域13に接続され、ドレイン領域16とソース領域14間に並列に蓄積キャパシタCSを備えていても良い。

【0051】

ここで、イオン検出部6は、図10に示すように、ソース領域14とドレイン領域16間のウェル領域12と、ウェル領域12上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に配置されたイオン感応膜19からなる。ここで、ゲート絶縁膜18は、例えば、シリコン酸化膜、イオン感応膜19は、例えば、タンタルオキサイド、若しくはシリコン窒化膜などで形成することができる。イオン感応膜19上に付着した、例えば、H+イオンなどによって、ゲート絶縁膜18下のウェル領域12に形成されるチャネル領域の電位が変化する。この結果、ソース領域14とドレイン領域16間の電流導通状態が変調され、この電流値を検出することによって、例えば、pH値などを検出することができる。

【0052】

図10において、参照電極24はガラス封止されたキャピラリー電極構造を備え、当該キャピラリー電極には、一定の参照電圧VREFが供給されている。また、ガラス材料としては、耐酸性、耐熱性、耐水性の良好な、例えば、石英などによって形成可能である。

【0053】

尚、図10に示される構造は、CMOS形成技術を適用して形成可能である。図10において、LOCOS絶縁膜17の下部には、チャネルストッパ拡散層が形成されるが、図示を省略している。

【0054】

第2の実施の形態に係るISFET2は、図11に示すように、イオン検出トランジスタQmnと蓄積キャパシタCSとの並列回路からなる。

【0055】

イオン検出トランジスタQmnのドレインDとソースS間に電源電圧が印加されたオン状態における動作は、図12(a)に示すように表され、イオン検出トランジスタQmnが導通状態にあり、かつ蓄積キャパシタCSが電源電圧で充電された状態にある。イオン検出トランジスタQmnのドレインDとソースS間に電源電圧が印加されていないオフ状態における動作は、図12(b)に示すように表される。この場合においても、イオン検出トランジスタQmnは、蓄積キャパシタCSの蓄積電荷の放電電流によって、導通状態にあり、かつ蓄積キャパシタCSは、放電状態にある。

【0056】

第2の実施の形態に係るISFET2においては、イオン検出トランジスタQmnに対して、蓄積キャパシタCSを並列接続することにより、ドレインDとソースS間に電源電圧が印加されたオン状態では蓄積キャパシタCSが充電され、ドレインDとソースS間に電源電圧が印加されないオフ状態では蓄積キャパシタCSが放電することにより、常に駆動状態を保持することができ、安定性が向上する。

【0057】

(ISFETアレイ)

第2の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4の模式的回路ブロック構成は、図13に示すように表される。また、図13において、ISFETセルCmnにおける動作モードの説明は、図14に示すように表される。図13および図14から明らかなように、垂直選択トランジスタQVmと、水平選択トランジスタQHnによって選択されるISFETセルCmnのイオン検出トランジスタQmnは、垂直選択トランジスタQVmと、水平選択トランジスタQHnの両方が同時にON状態にあるとき、ON状態となる。垂直選択トランジスタQVmと、水平選択トランジスタQHnの両方が同時にOFF状態、若しくはいずれか一方がOFF状態にあるとき、OFF状態となる。

【0058】

第2の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4は、図13に示すように、行方向に延伸する複数のワード線WL1,WL2,…,WLmと、ワード線WL1,WL2,…,WLmに直交し、列方向に延伸する複数のビット線BL1,BL2,…,BLnと、複数のワード線WL1,WL2,…,WLmに対してそれぞれドレインが接続された複数の垂直選択トランジスタQV1,QV2,…,QVmと、複数の垂直選択トランジスタQV1,QV2,…,QVmのそれぞれゲートが接続された垂直走査回路30と、複数のビット線BL1,BL2,…,BLnに対して、それぞれソースが接続された水平選択トランジスタQH1,QH2,…,QHnと、複数の水平トランジスタQH1,QH2,…,QHnのそれぞれゲートが接続された水平走査回路32と、ワード線WL1,WL2,…,WLmとビット線BL1,BL2,…,BLnの交差部に配置されたISFETセルCmnとを備える。

【0059】

ここで、ISFETセルC11、C12、…、C1n、C21、C22、…、C2n、…、Cm1、Cm2、…、Cmnは、図11に示すように、それぞれイオン検出トランジスタQ11、Q12、…、Q1n、Q21、Q22、…、Q2n、…、Qm1、Qm2、…、Qmnと蓄積キャパシタCSとの並列回路からなる。

【0060】

ISFETセルC11、C12、…、C1n、C21、C22、…、C2n、…、Cm1、Cm2、…、Cmnは、前述の図10に示すように、第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域12と、第1ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、第1ウェル領域12上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に配置されたイオン感応膜19と、ソース領域14とドレイン領域16間に接続される蓄積キャパシタCSと、イオン感応膜19に接触する液体試料26と、液体試料26中に配置された参照電極24と備える。

【0061】

また、ISFETセルC11、C12、…、C1n、C21、C22、…、C2n、…、Cm1、Cm2、…、Cmnは、さらに、半導体基板10上に配置され、第1導電型を有する第2ウェル領域23と、第2ウェル領域23上に配置され、第1導電型を有する第2ウェルコンタクト領域13と、第2ウェル領域23上に配置されたゲート絶縁膜18上に配置され、第2ウェル領域23との間で蓄積キャパシタCSを形成するキャパシタ電極21とを備えていても良い。

【0062】

また、ドレイン領域16は、キャパシタ電極21に接続され、ソース領域14は、ウェルコンタクト領域13に接続され、ドレイン領域16とソース領域14間に並列に蓄積キャパシタCSを備えていても良い。

【0063】

第2の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4は、図13に示すように、複数の水平選択トランジスタQH1,QH2,…,QHnのドレインを共通接続して得られた出力端子と接地電位間に接続されたMOSFETQLNと、複数の垂直選択トランジスタQV1,QV2,…,QVmのソースを共通接続して得られた電源ラインに接続された電源電圧VDDとを備える。

【0064】

第2の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4は、複数の水平選択トランジスタQH1,QH2,…,QHnのドレインを共通接続して得られた電源ラインに接続された電源電圧VDDと、複数の垂直選択トランジスタQV1,QV2,…,QVmのソースを共通接続して得られた出力端子と接地電位間に接続されたMOSFETQLNとを備えていても良い。

【0065】

第2の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4においては、各画素のイオン検出トランジスタQ11、Q12、…、Q1n、Q21、Q22、…、Q2n、…、Qm1、Qm2、…、Qmnに対して、蓄積キャパシタCSを並列接続し、これにより、画素選択時に蓄積キャパシタCSが充電され、画素選択されていない時に蓄積キャパシタCSが放電することにより、常に駆動状態を保持することができ、ISFETアレイ4のアレイ動作を安定化することができる。すなわち、画素選択されていない時も蓄積キャパシタCSから電力供給されるため、駆動状態を保持可能であり、安定性が向上する。

【0066】

[第3の実施の形態]

(ISFET)

第3の実施の形態に係るISFETの模式的断面構造は、図15に示すように、ゲート絶縁膜18上に、ドレイン領域16に隣接して配置されたトランスファゲート電極20を備える。その他の構成は、図10に示した第2の実施の形態と同様であるため、重複説明は省略する。

【0067】

また、第3の実施の形態に係るISFETの模式的回路構成は、図16に示すように、イオン検出部6のイオン検出トランジスタQiと、トランスファゲートTGによるトランスファゲートトランジスタQGの直列回路と、トランスファゲートトランジスタQGのドレインとイオン検出トランジスタQiのソース間に接続された蓄積キャパシタCSとの並列回路で構成され、トランスファゲートトランジスタQGのドレイン領域16に電源電圧VDが接続され、イオン検出トランジスタQiのソース領域14には、MOSFETQLNが接続される。

【0068】

また、第3の実施の形態に係るISFETは、第1の実施の形態に係るISFETと、第2の実施の形態に係るISFETとの両方の動作モードを兼ね備えている。

【0069】

すなわち、第3の実施の形態に係るISFET2においては、トランスファゲート電極20に加える電圧を調節することにより、リセット情報、光情報を取得するモードと、pHを取得するモードを切り替えることができるため、正確なイオン情報を検出することができる。

【0070】

また、第3の実施の形態に係るISFET2においては、イオン検出トランジスタQmnとトランスファゲートトランジスタQGの直列構成に対して、蓄積キャパシタCSを並列接続することにより、ドレインDとソースS間に電源電圧が印加されたオン状態では蓄積キャパシタCSが充電され、ドレインDとソースS間に電源電圧が印加されないオフ状態では蓄積キャパシタCSが放電することにより、常に駆動状態を保持することができ、安定性が向上する。

【0071】

(ISFETアレイ)

第3の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4の模式的回路ブロック構成は、図17に示すように、行方向に延伸する複数のワード線WL1,WL2,…,WLmと、ワード線WL1,WL2,…,WLmに直交し、列方向に延伸する複数のビット線BL1,BL2,…,BLnと、複数のワード線WL1,WL2,…,WLmに対してそれぞれドレインが接続された複数の垂直選択トランジスタQV1,QV2,…,QVmと、複数の垂直選択トランジスタQV1,QV2,…,QVmのそれぞれゲートが接続された垂直走査回路30と、複数のビット線BL1,BL2,…,BLnに対して、それぞれソースが接続された水平選択トランジスタQH1,QH2,…,QHnと、複数の水平トランジスタQH1,QH2,…,QHnのそれぞれゲートが接続された水平走査回路32と、ワード線WL1,WL2,…,WLmとビット線BL1,BL2,…,BLnの交差部に配置されたISFETセルCmnとを備える。

【0072】

ここで、ISFETセルCmnは、図16に示すように、イオン検出トランジスタQiとトランスファゲートトランジスタQGの直列回路と、ドレインとソース間に接続された蓄積キャパシタCSとの並列回路で構成される。

【0073】

ここで、ISFETセルCmnは、第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域12と、第1ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、第1ウェル領域12上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に、ドレイン領域16に隣接して配置されたトランスファゲート電極20と、ゲート絶縁膜18上に配置されたイオン感応膜19と、ソース領域14とドレイン領域16間に接続される蓄積キャパシタCSと、イオン感応膜19に接触する液体試料26と、液体試料26中に配置された参照電極24とを備える。

【0074】

ISFETセルCmnは、さらに、半導体基板10上に配置され、第1導電型を有する第2ウェル領域23と、第2ウェル領域23上に配置され、第1導電型を有する第2ウェルコンタクト領域13と、第2ウェル領域23上のゲート絶縁膜18上に配置され、第2ウェル領域23との間で蓄積キャパシタCSを形成するキャパシタ電極21とを備えていても良い。

【0075】

また、ドレイン領域16は、キャパシタ電極21に接続され、ソース領域14は、ウェルコンタクト領域13に接続され、ドレイン領域16とソース領域14間に並列に蓄積キャパシタCSを備えていても良い。

【0076】

第3の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4は、図17に示すように、複数の水平選択トランジスタQH1,QH2,…,QHnのドレインを共通接続して得られた電源ラインに接続された電源電圧VDDと、複数の垂直選択トランジスタQV1,QV2,…,QVmのソースを共通接続して得られた出力端子と接地電位間に接続されたMOSFETQLNを備える。

【0077】

第3の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4は、複数の水平選択トランジスタQH1,QH2,…,QHnのドレインを共通接続して得られた出力端子と接地電位間に接続されたMOSFETQLNと、複数の垂直選択トランジスタQV1,QV2,…,QVmのソースを共通接続して得られた電源ラインに接続された電源電圧VDDとを備えていても良い。

【0078】

第3の実施の形態に係るISFETアレイ4においては、ISFETアレイ4が配置された半導体基板10上に試料セル100を配置し、リセット情報・光情報の検出時は、ISFETセルCijのトランスファゲート電極20のトランスファゲート電位VTGをオフ状態のローレベルとし、pHイオン情報の検出時は、オン状態のハイレベルとし、トランスファゲート電極20のトランスファゲート電位VTGによってオン、オフ制御することによって、リセット情報・光情報のイメージ情報と、pHイオン分布情報の両方を検出することができる。

【0079】

また、第3の実施の形態に係るISFETアレイ4においては、各画素のイオン検出トランジスタQmnとトランスファゲートトランジスタQGの直列回路に対して、蓄積キャパシタCSを並列接続し、これにより、画素選択時に蓄積キャパシタCSが充電され、画素選択されていない時に蓄積キャパシタCSが放電することにより、常に駆動状態を保持することができ、ISFETアレイ4のアレイ動作を安定化することができる。すなわち、画素選択されていない時も蓄積キャパシタCSから電力供給されるため、駆動状態を保持可能であり、安定性が向上する。

【0080】

[第4の実施の形態]

第4の実施の形態に係るISFET2は、図18に示すように、ソース領域、ドレイン領域、および第2ウェル領域上に配置されたパッシベーション膜22と、パッシベーション膜22上に配置された遮光膜50aとを備える。さらに、図18に示すように、遮光膜50a上にパッシベーション膜22aを備えていても良い。なお、遮光膜50aは、例えば、アルミニウムの薄膜層などで形成可能である。

【0081】

また、図18においては、第1ウェル領域12に形成された第1ウェルコンタクト領域45と、半導体基板10に対して形成された基板コンタクト領域43を備える。その他の構成は、図10に示す第2の実施の形態と同様であるため、重複説明は省略する。

【0082】

また、第4の実施の形態に係るISFET2も第2の実施の形態と同様に、図13と同様にISFETアレイ4を構成可能であるが、重複説明は省略する。

【0083】

第4の実施の形態によれば、イオン検出部以外の領域に遮光膜を備えるため、イオン検出感度を向上したISFETおよび当該ISFETセルを適用し、常時駆動によって安定化可能なISFETアレイを提供することができる。

【0084】

[第5の実施の形態]

第5の実施の形態に係るISFET2は、図19に示すように、第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域12と、第1ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、第1ウェル領域12上に配置されたゲート絶縁膜18と、ソース領域14とドレイン領域16間のゲート絶縁膜18上に配置されたゲートプラグ電極40と、ドレイン領域16上に配置されたドレインプラグ電極44と、ソース領域14とドレインプラグ電極44間に接続され、積層電極46・48からなる蓄積キャパシタCSと、ゲートプラグ電極40上に配置された遮光膜42と、遮光膜42上に配置されたイオン感応膜19と、イオン感応膜19に接触する液体試料26と、液体試料26中に配置された参照電極24とを備える。

【0085】

また、第5の実施の形態に係るISFET2は、図19に示すように、第1ウェル領域12および半導体基板10上のゲート絶縁膜18上に配置されたパッシベーション膜22と、パッシベーション膜22上に配置された遮光膜50aとを備える。遮光膜42・50aは、例えば、アルミニウムの薄膜層などで形成可能である。その他の構成は、図18に示す第4の実施の形態と同様であるため、重複説明は省略する。

【0086】

また、第5の実施の形態に係るISFET2も第2の実施の形態と同様に、図13と同様にISFETアレイ4を構成可能であるが、重複説明は省略する。

【0087】

第5の実施の形態に係るISFET2においては、遮光膜42・50aを備えるため、イオン情報の検出感度を向上することができる。

【0088】

また、第5の実施の形態に係るISFET2においては、蓄積キャパシタCSを積層構造により形成できるため、集積度を向上することができる。

【0089】

また、第5の実施の形態に係るISFET2においては、イオン検出部6を素子領域の全面に形成できるため、イオン情報の検出感度を向上することができる。

【0090】

以上説明したように、本実施の形態によれば、検出感度を向上したISFETおよび当該ISFETセルを適用し、常時駆動によって安定化可能なISFETアレイを提供することができる。

【0091】

(その他の実施の形態)

上記のように、本発明は第1〜第5の実施の形態によって記載したが、この開示の一部をなす論述および図面はこの発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施の形態、実施例および運用技術が明らかとなろう。

【0092】

このように、本発明はここでは記載していない様々な実施の形態等を含むことは勿論である。したがって、本発明の技術的範囲は上記の説明から妥当な特許請求の範囲に係る発明特定事項によってのみ定められるものである。

【産業上の利用可能性】

【0093】

本発明のISFETおよびISFETアレイは、細胞のpHセンサ、pHイオンの分布測定、水質調査、水質管理、環境測定、医療計測分野などに適用可能である。

【符号の説明】

【0094】

2…ISFET

4…ISFETアレイ

6…イオン検出部

10…半導体基板

12…pウェル層

13…nウェルコンタクト領域

14…ソース領域

16…ドレイン領域

17…LOCOS絶縁膜

18…ゲート絶縁膜

19…イオン感応膜

20…トランスファゲート電極(TG)

21、46、48…キャパシタ電極

22…パッシベーション膜

23…nウェル層

24…参照電極

26…液体試料

30…垂直走査回路

32…水平走査回路

40…ゲートプラグ電極

43…基板コンタクト領域

44…ドレインプラグ電極

45…pウェルコンタクト領域

42、50、50a…遮光膜

100…試料セル

200…pH分布

WL1,WL2,…,WLm…ワード線(垂直走査線)

BL1,BL2,…,BLn…ビット線(水平走査線)

QV1,QV2,…,QVm…垂直選択トランジスタ

QH1,QH2,…,QHn…水平選択トランジスタ

QLN…MOSFET

Qi、Q11、Q12、…、Q1n、Q21、Q22、…、Q2n、…、Qm1、Qm2、…、Qmn…イオン検出トランジスタ

QG…トランスファゲートトランジスタ

C11、C12、…、C1n、C21、C22、…、C2n、…、Cm1、Cm2、…、Cmn…ISFETセル

CS…蓄積キャパシタ

VREF…参照電圧

VD,VDD…電源電圧

Vout…出力電圧

VLN、VTG…ゲート電圧

VTG…トランスファゲート電圧

【技術分野】

【0001】

本発明は、ISFETおよびISFETアレイに関し、特に、検出感度を向上したISFETおよびISFETアレイに関する。

【背景技術】

【0002】

従来のイオン感応性電界効果トランジスタ(ISFET:Ion Sesitive Field Effect Transistor)からなるイオンセンサとして、バックゲートとソースとの間、およびバックゲートとドレインとの間に発生するバックゲート光電流を取り出すためのゲート電極を備え、このバックゲート光電流を用いて、ISFETのソースやドレインにおいて発生する光電流を補正する構成が開示されている(例えば、特許文献1参照。)。

【0003】

また、上記ISFETを2次元的に複数個配置し、pHの2次元分布を測定するものとして、水素イオン濃度分布測定装置がある(例えば、特許文献2参照。)。

【0004】

一方、特許文献2に係るISFETアレイを改良し、ISFETアレイセル毎にISFETの切り替えスイッチ用MOSFETを備えるISFETアレイも開示されている(例えば、特許文献3参照。)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−164359号公報

【特許文献2】特開平05−33745号公報

【特許文献3】特許第4137239号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1に係るISFETでは、バルクに流れる電流で光読み出しを行うため、ノイズ情報が光読み出し電流に含まれる。また、アレイ化を図る場合、バルクに流れる電流で光読み出しを行うため、pウェル領域を互いに隣接セル間で分離する必要があり、構造が複雑となり、アレイ化が難しい。

【0007】

特許文献2に係るISFETアレイでは、一回測定して、次に測定するまで、安定化するのに時間を要する。

【0008】

従来の技術では、ISFETをアレイ化した場合、画素選択されていない時に画素が駆動していないため、測定値が安定しにくい。また、ISFETセルが選択回路により選択されてからオン状態になって動作が安定化するまでに時間がかかる。

【0009】

本発明の目的は、検出感度を向上したISFETおよび当該ISFETセルを適用したISFETアレイを提供することにある。

【課題を解決するための手段】

【0010】

本発明の一態様によれば、第1導電型を有する半導体基板と、前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域と、前記ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、前記ソース領域と、前記ウェル領域と、前記ドレイン領域上に配置されたゲート絶縁膜と、前記ゲート絶縁膜上に、前記ドレイン領域に隣接して配置されたトランスファゲート電極と、前記ゲート絶縁膜に接触する液体試料と、前記液体試料中に配置された参照電極とを備えるISFETが提供される。

【0011】

本発明の他の態様によれば、第1導電型を有する半導体基板と、前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域と、前記第1ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、前記第1ウェル領域上に配置されたゲート絶縁膜と、前記ゲート絶縁膜上に配置されたイオン感応膜と、前記ソース領域と前記ドレイン領域間に接続される蓄積キャパシタと、前記イオン感応膜に接触する液体試料と、前記液体試料中に配置された参照電極とを備えるISFETが提供される。

【0012】

本発明の他の態様によれば、第1導電型を有する半導体基板と、前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域と、前記第1ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、前記第1ウェル領域上に配置されたゲート絶縁膜と、前記ソース領域と前記ドレイン領域間の前記ゲート絶縁膜上に配置されたゲートプラグ電極と、前記ドレイン領域上に配置されたドレインプラグ電極と、前記ソース領域と前記前記ドレインプラグ電極間に接続され、積層電極構造からなる蓄積キャパシタと、前記ゲートプラグ電極上に配置された遮光膜と、前記遮光膜上に配置されたイオン感応膜と、前記イオン感応膜に接触する液体試料と、前記液体試料中に配置された参照電極とを備えるISFETが提供される。

【0013】

本発明の他の態様によれば、行方向に延伸する複数のワード線と、前記ワード線に直交し、列方向に延伸する複数のビット線と、前記複数のワード線に対してそれぞれドレインが接続された複数の垂直選択トランジスタと、前記複数の垂直選択トランジスタのそれぞれゲートが接続された垂直走査回路と、前記複数のビット線に対して、それぞれソースが接続された水平選択トランジスタと、前記複数の水平トランジスタのそれぞれゲートが接続された水平走査回路と、前記ワード線と前記ビット線の交差部に配置されたISFETセルとを備え、前記ISFETセルは、第1導電型を有する半導体基板と、前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域と、前記ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、前記ウェル領域上に配置されたゲート絶縁膜と、前記ゲート絶縁膜上に、前記ドレイン領域に隣接して配置されたトランスファゲート電極と、前記ゲート絶縁膜に接触する液体試料と、前記液体試料中に配置された参照電極とを備えるISFETアレイが提供される。

【0014】

本発明の他の態様によれば、行方向に延伸する複数のワード線と、前記ワード線に直交し、列方向に延伸する複数のビット線と、前記複数のワード線に対してそれぞれドレインが接続された複数の垂直選択トランジスタと、前記複数の垂直選択トランジスタのそれぞれゲートが接続された垂直走査回路と、前記複数のビット線に対して、それぞれソースが接続された水平選択トランジスタと、前記複数の水平トランジスタのそれぞれゲートが接続された水平走査回路と、前記ワード線と前記ビット線の交差部に配置されたISFETセルとを備え、前記ISFETセルは、第1導電型を有する半導体基板と、前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域と、前記第1ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、前記第1ウェル領域上に配置されたゲート絶縁膜と、前記ゲート絶縁膜上に配置されたイオン感応膜と、前記ソース領域と前記ドレイン領域間に接続される蓄積キャパシタと、前記イオン感応膜に接触する液体試料と、前記液体試料中に配置された参照電極とを備えるISFETアレイが提供される。

【発明の効果】

【0015】

本発明によれば、検出感度を向上したISFETおよび当該ISFETセルを適用したISFETアレイを提供することができる。

【図面の簡単な説明】

【0016】

【図1】(a)第1の実施の形態に係るISFETの模式的断面構造図、(b)図1(a)のイオン検出部の拡大された模式的断面構造図。

【図2】第1の実施の形態に係るISFETを適用したイオン検出動作の模式的説明図。

【図3】第1の実施の形態に係るISFETのイオン検出動作を説明する回路構成図。

【図4】第1の実施の形態に係るISFETの模式的平面パターン構成図。

【図5】第1の実施の形態に係るISFETの光検出時のエネルギーポテンシャルダイヤグラム。

【図6】第1の実施の形態に係るISFETのイオン検出時のエネルギーポテンシャルダイヤグラム。

【図7】第1の実施の形態に係るISFETをアレイ状に配列したISFETアレイ上に試料セルが搭載された様子を表す模式的鳥瞰構造図。

【図8】図7に対応するISFETアレイを用いて検出したpH分布の様子を表す模式的鳥瞰構造図。

【図9】第1の実施の形態に係るISFETをアレイ状に配列したISFETアレイの模式的回路ブロック構成図。

【図10】第2の実施の形態に係るISFETの模式的断面構造図。

【図11】(a)第2の実施の形態に係るISFETの模式的回路構成図、(b)図11(a)の簡易な回路表示図。

【図12】(a)第2の実施の形態に係るISFETにおいて、選択回路オン状態における動作説明図、(b)第2の実施の形態に係るISFETにおいて、選択回路オフ状態における動作説明図。

【図13】第2の実施の形態に係るISFETをアレイ状に配列したISFETアレイの模式的回路ブロック構成図。

【図14】図13の動作モードの説明図。

【図15】第3の実施の形態に係るISFETの模式的断面構造であって、イオン検出動作の模式的説明図。

【図16】第3の実施の形態に係るISFETの模式的回路構成図。

【図17】第3の実施の形態に係るISFETをアレイ状に配列したISFETアレイの模式的回路ブロック構成図。

【図18】第4の実施の形態に係るISFETの模式的断面構造であって、イオン検出動作の模式的説明図。

【図19】第5の実施の形態に係るISFETの模式的断面構造であって、イオン検出動作の模式的説明図。

【発明を実施するための形態】

【0017】

次に、図面を参照して、本発明の第1〜第5の実施の形態を説明する。以下の図面の記載において、同一又は類似の部分には同一又は類似の符号を付している。ただし、図面は模式的なものであり、厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なることに留意すべきである。したがって、具体的な厚みや寸法は以下の説明を参酌して判断すべきものである。又、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。

【0018】

又、以下に示す第1〜第5の実施の形態は、この発明の技術的思想を具体化するための装置や方法を例示するものであって、この発明の実施の形態は、構成部品の材質、形状、構造、配置等を下記のものに特定するものでない。この発明の実施の形態は、特許請求の範囲において、種々の変更を加えることができる。

【0019】

[第1の実施の形態]

(ISFET)

第1の実施の形態に係るISFET2の模式的断面構造は、図1(a)に示すように表され、図1(a)のイオン検出部の拡大された模式的断面構造は、図1(b)に示すように表される。

【0020】

また、第1の実施の形態に係るISFET2を適用したイオン検出動作時の構成は、図2に示すように表される。さらに、第1の実施の形態に係るISFET2のイオン検出動作を説明する回路構成は、図3に示すように表される。ここで、図1(a)および図2は、後述する図4のI−I線に沿う模式的断面構造に相当している。

【0021】

第1の実施の形態に係るISFET2は、図1(a)に示すように、第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域12と、ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、ウェル領域12上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に、ドレイン領域16に隣接して配置されたトランスファゲート電極20とを備える。

【0022】

ここで、イオン検出部6は、図1(b)に示すように、ソース領域14とドレイン領域16間のウェル領域12と、ウェル領域12上に配置されたゲート絶縁膜18からなる。ここで、ゲート絶縁膜18には、例えば、タンタルオキサイド、アルミナ、若しくはシリコン窒化膜を適用することができる。若しくは、シリコン熱酸化膜上にシリコン窒化膜を積層した構造、シリコン熱酸化膜上にタンタルオキサイドを成膜した構造でも良い。さらに、シリコン熱酸化膜、シリコン窒化膜、タンタルオキサイドの順に積層した構造のゲート絶縁膜(イオン感応膜)はシリコン窒化膜による防水性、タンタルオキサイドの優れた感度、ドリフト特性の面から、尚良い。ゲート絶縁膜18上に付着した、例えば、H+イオンなどによって、ゲート絶縁膜18下のウェル領域12に形成されるチャネル領域の電位が変化する。この結果、ソース領域14とドレイン領域16間の電流導通状態が変調され、この電流値を検出することによって、例えば、pH値などを検出することができる。

【0023】

第1の実施の形態に係るISFET2を適用したイオン検出動作時の構成は、図2に示すように表される。イオン検出部6のゲート絶縁膜18には、液体試料26が接触しており、液体試料26中には、参照電極24が配置されている。

【0024】

参照電極24は、ガラス封止されたキャピラリー電極構造を備え、当該キャピラリー電極には、一定の参照電圧VREFが供給される。また、ガラス材料としては、耐酸性、耐熱性、耐水性の良好な、例えば、石英などによって形成可能である。

【0025】

イオン感応膜を透過した光を下のSi基板内のpn接合で検知するため、感応膜は、目的の波長領域の光を透過する材料であれば良い。可視光の場合はシリコン窒素化膜、タンタルオキサイドなどが挙げられる。

【0026】

また、第1の実施の形態に係るISFET2は、ドレイン領域16に接続された電源電圧VDと、ソース領域14に接続されたMOSFETQLNとを備えていても良い。

【0027】

第1の実施の形態に係るISFET2は、図3に示すように、イオン検出部6のイオン検出トランジスタQiと、トランスファゲートTGによるトランスファゲートトランジスタQGの直列回路で構成され、トランスファゲートトランジスタQGのドレイン領域16に電源電圧VDが接続され、イオン検出トランジスタQiのソース領域14には、MOSFETQLNが接続される。

【0028】

図3に示すように、第1の実施の形態に係るISFET2において、イオン検出トランジスタQiのゲート上の参照電極REFGには参照電圧VREFが印加されている。イオン検出トランジスタQiのゲート部がイオン検出部6に相当し、液体界面のポテンシャルによる入力イオン信号を受信する。出力信号は、イオン検出トランジスタQiに直列接続されたMOSFETQLNのドレインから、ソースフォロアの出力電圧Voutとして得る。この結果、MOSFETQLNのドレイン端子より得られるソースフォロアの出力電圧Voutが、入力イオン信号に対して、リニアに応答する。

【0029】

(イオン検出動作)

第1の実施の形態に係るISFET2の模式的平面パターン構成は、図4に示すように表される。また、第1の実施の形態に係るISFETの光検出時のエネルギーポテンシャルダイヤグラムは、図5に示すように表され、イオン検出時のエネルギーポテンシャルダイヤグラムは、図6に示すように表される。

【0030】

第1の実施の形態に係るISFET2において、トランスファゲート電極20の電位は、リセット情報・光情報の検出時は、オフ状態のローレベル、pHイオン情報の検出時は、オン状態のハイレベルとし、トランスファゲート電極20の電位よってオン、オフ制御することができる。

【0031】

―リセット情報・光情報の検出―

リセット取得モードにおいては、図5に示すように、トランスファゲート電極20の電位をローレベルにして、トランスファゲートトランジスタQGをオフ状態にする。このとき、イオン検出部6からドレイン領域16へのキャリア(電子)の流れは、トランスファゲート電極(TG)直下のポテンシャルバリアによって、塞き止められる。この状態では、ソース領域14近傍の電子は半導体基板10側に流出し、一方、ソース領域14近傍の正孔は、ソース領域14に流入する。

【0032】

―イオン情報の検出―

次に、ISFETモードにおいては、図6に示すように、トランスファゲート電極20の電位をハイレベルにして、トランスファゲートトランジスタQGをオン状態にする。このとき、トランスファゲート電極(TG)直下のポテンシャルバリア高さが低下するため、イオン検出部6からドレイン領域16へのキャリア(電子)流入が引き起こされる。また、この状態では、ソース領域14近傍の電子は半導体基板10側に流出する。一方、ソース領域14近傍の正孔は、ソース領域14に流入する。

【0033】

したがって、リセット取得モードにおいて得られたリセット情報・光情報をISFETモードにおいては、得られたデータから差し引くことによって、正確なイオン情報を検出することができる。

【0034】

第1の実施の形態に係るISFET2においては、バックゲート(ウェル領域12)とソース領域14間、バックゲート(ウェル領域12)とドレイン領域16間に発生するバックゲート光電流を、トランスファゲート電極20のオン・オフ動作によって取り出すことができる。

【0035】

尚、第1の実施の形態に係るISFET2においては、トランスファゲート電極20およびドレイン領域16・ソース領域14上をパッシベーション膜22で被覆し、イオン検出部6のパッシベーション膜22を開口した構成とすることがイオン検出感度を向上する上で望ましい。

【0036】

また、第1の実施の形態に係るISFET2においては、トランスファゲート電極20に加える電圧を調節することにより、リセット情報、光情報を取得するモードと、pHを取得するモードを切り替えることができるため、正確なイオン情報を検出することができる。

【0037】

(ISFETアレイ)

第1の実施の形態に係るISFET2によって構成されたISFETセルCijを、半導体基板10上に、アレイ状に配列したISFETアレイ4上に試料セル100が搭載された様子を表す模式的鳥瞰構造は、図7に示すように表され、図7に対応するISFETアレイ4を用いて検出したpH分布200の様子を表す模式的鳥瞰構造は、図8に示すように表される。図7および図8に示すように、各々のISFETセルCijに対応して、各々のpH値pHijが検出される。

【0038】

第1の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4の模式的回路ブロック構成は、図9に示すように、行方向に延伸する複数のワード線WL1,WL2,…,WLmと、ワード線WL1,WL2,…,WLmに直交し、列方向に延伸する複数のビット線BL1,BL2,…,BLnと、複数のワード線線WL1,WL2,…,WLmに対してそれぞれドレインが接続された複数の垂直選択トランジスタQV1,QV2,…,QVmと、複数の垂直選択トランジスタQV1,QV2,…,QVmのそれぞれゲートが接続された垂直走査回路30と、複数のビット線BL1,BL2,…,BLnに対して、それぞれソースが接続された水平選択トランジスタQH1,QH2,…,QHnと、複数の水平選択トランジスタQH1,QH2,…,QHnのそれぞれゲートが接続された水平走査回路32と、ワード線WL1,WL2,…,WLmとビット線BL1,BL2,…,BLnの交差部に配置されたISFETセルCmnとを備える。

【0039】

ここで、ISFETセルCmnは、図9に示すように、イオン検出トランジスタQmnとトランスファゲートトランジスタQGとの直列回路からなる。

【0040】

ISFETセルCmnは、前述の図2に示すように、第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域12と、ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、ウェル領域12上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に、ドレイン領域16に隣接して配置されたトランスファゲート電極20と、ゲート絶縁膜18に接触する液体試料26と、液体試料26中に配置された参照電極24とを備える。

【0041】

ここで、各々のISFETセルCmnのゲート絶縁膜18には、例えば、タンタルオキサイド、若しくはシリコン窒化膜を適用することができる。各々のISFETセルCmnのゲート絶縁膜18上に付着した、例えば、H+イオンなどによって、ゲート絶縁膜18下のウェル領域12に形成されるチャネル領域の電位が変化する。この結果、ソース領域14とドレイン領域16間の電流導通状態が変調され、この電流値を検出することによって、例えば、pH値などを検出することができる。

【0042】

また、第1の実施の形態に係るISFETアレイ4は、複数の垂直選択トランジスタQV1,QV2,…,QVmのソースを共通接続して得られた出力端子と接地電位間に接続されたMOSFETQVNと、複数の水平選択トランジスタQH1,QH2,…,QHnのドレインを共通接続して得られた電源ラインに接続された電源電圧VDDと、トランスファゲート電極20を共通化したトランスファゲートラインに接続されたトランスファゲート電圧VTGとを備えていても良い。

【0043】

イオン感応膜を透過した光を下のSi基板内のPN接合で検知するため、感応膜は、目的の波長領域の光を透過する材料。可視光の場合はシリコン窒素化膜、タンタルオキサイドなどが挙げられる。

【0044】

また、第1の実施の形態に係るISFETアレイ4において、MOSFETQVNは、より簡単な構成を実現するためには、抵抗で置換しても良い。

【0045】

バックゲート(ウェル領域12)からリセットを読み出す場合は、アレイ化した場合、各ISFETセルCijでバックゲート(ウェル領域12)を互いに分離して、独立させる必要があるが、第1の実施の形態に係るISFETアレイ4においては、図9に示すように、トランスファゲート電極20を共通化して、トランスファゲート電位VTGを加えることができる。

【0046】

また、第1の実施の形態に係るISFETアレイ4においては、ISFETアレイ4が配置された半導体基板10上に試料セル100を配置し、リセット情報・光情報の検出時は、ISFETセルCijのトランスファゲート電極20のトランスファゲート電圧VTGをオフ状態のローレベルとし、pHイオン情報の検出時は、オン状態のハイレベルとし、トランスファゲート電極20のトランスファゲート電圧VTGによってオン、オフ制御することによって、リセット情報・光情報のイメージ情報と、pHイオン分布情報の両方を検出することができる。

【0047】

[第2の実施の形態]

(ISFET)

第2の実施の形態に係るISFETの模式的断面構造は、図10に示すように表される。また、第2の実施の形態に係るISFETの模式的回路構成は図11(a)に示すように表され、図11(a)の簡易な回路表示は、図11(b)に示すように表される。

【0048】

第2の実施の形態に係るISFET2は、図10〜図11に示すように、第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域12と、第1ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、第1ウェル領域上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に配置されたイオン感応膜19と、ソース領域14とドレイン領域16間に接続される蓄積キャパシタCSと、イオン感応膜19に接触する液体試料26と、液体試料26中に配置された参照電極24とを備える。

【0049】

また、第2の実施の形態に係るISFET2は、半導体基板10上に配置され、第1導電型を有する第2ウェル領域23と、第2ウェル領域23上に配置され、第1導電型を有する第2ウェルコンタクト領域13と、第2ウェル領域上に配置されたゲート絶縁膜18上に配置され、第2ウェル領域23との間で蓄積キャパシタCSを形成するキャパシタ電極21とを備えていても良い。

【0050】

また、第2の実施の形態に係るISFET2において、ドレイン領域16は、キャパシタ電極21に接続され、ソース領域14は、ウェルコンタクト領域13に接続され、ドレイン領域16とソース領域14間に並列に蓄積キャパシタCSを備えていても良い。

【0051】

ここで、イオン検出部6は、図10に示すように、ソース領域14とドレイン領域16間のウェル領域12と、ウェル領域12上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に配置されたイオン感応膜19からなる。ここで、ゲート絶縁膜18は、例えば、シリコン酸化膜、イオン感応膜19は、例えば、タンタルオキサイド、若しくはシリコン窒化膜などで形成することができる。イオン感応膜19上に付着した、例えば、H+イオンなどによって、ゲート絶縁膜18下のウェル領域12に形成されるチャネル領域の電位が変化する。この結果、ソース領域14とドレイン領域16間の電流導通状態が変調され、この電流値を検出することによって、例えば、pH値などを検出することができる。

【0052】

図10において、参照電極24はガラス封止されたキャピラリー電極構造を備え、当該キャピラリー電極には、一定の参照電圧VREFが供給されている。また、ガラス材料としては、耐酸性、耐熱性、耐水性の良好な、例えば、石英などによって形成可能である。

【0053】

尚、図10に示される構造は、CMOS形成技術を適用して形成可能である。図10において、LOCOS絶縁膜17の下部には、チャネルストッパ拡散層が形成されるが、図示を省略している。

【0054】

第2の実施の形態に係るISFET2は、図11に示すように、イオン検出トランジスタQmnと蓄積キャパシタCSとの並列回路からなる。

【0055】

イオン検出トランジスタQmnのドレインDとソースS間に電源電圧が印加されたオン状態における動作は、図12(a)に示すように表され、イオン検出トランジスタQmnが導通状態にあり、かつ蓄積キャパシタCSが電源電圧で充電された状態にある。イオン検出トランジスタQmnのドレインDとソースS間に電源電圧が印加されていないオフ状態における動作は、図12(b)に示すように表される。この場合においても、イオン検出トランジスタQmnは、蓄積キャパシタCSの蓄積電荷の放電電流によって、導通状態にあり、かつ蓄積キャパシタCSは、放電状態にある。

【0056】

第2の実施の形態に係るISFET2においては、イオン検出トランジスタQmnに対して、蓄積キャパシタCSを並列接続することにより、ドレインDとソースS間に電源電圧が印加されたオン状態では蓄積キャパシタCSが充電され、ドレインDとソースS間に電源電圧が印加されないオフ状態では蓄積キャパシタCSが放電することにより、常に駆動状態を保持することができ、安定性が向上する。

【0057】

(ISFETアレイ)

第2の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4の模式的回路ブロック構成は、図13に示すように表される。また、図13において、ISFETセルCmnにおける動作モードの説明は、図14に示すように表される。図13および図14から明らかなように、垂直選択トランジスタQVmと、水平選択トランジスタQHnによって選択されるISFETセルCmnのイオン検出トランジスタQmnは、垂直選択トランジスタQVmと、水平選択トランジスタQHnの両方が同時にON状態にあるとき、ON状態となる。垂直選択トランジスタQVmと、水平選択トランジスタQHnの両方が同時にOFF状態、若しくはいずれか一方がOFF状態にあるとき、OFF状態となる。

【0058】

第2の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4は、図13に示すように、行方向に延伸する複数のワード線WL1,WL2,…,WLmと、ワード線WL1,WL2,…,WLmに直交し、列方向に延伸する複数のビット線BL1,BL2,…,BLnと、複数のワード線WL1,WL2,…,WLmに対してそれぞれドレインが接続された複数の垂直選択トランジスタQV1,QV2,…,QVmと、複数の垂直選択トランジスタQV1,QV2,…,QVmのそれぞれゲートが接続された垂直走査回路30と、複数のビット線BL1,BL2,…,BLnに対して、それぞれソースが接続された水平選択トランジスタQH1,QH2,…,QHnと、複数の水平トランジスタQH1,QH2,…,QHnのそれぞれゲートが接続された水平走査回路32と、ワード線WL1,WL2,…,WLmとビット線BL1,BL2,…,BLnの交差部に配置されたISFETセルCmnとを備える。

【0059】

ここで、ISFETセルC11、C12、…、C1n、C21、C22、…、C2n、…、Cm1、Cm2、…、Cmnは、図11に示すように、それぞれイオン検出トランジスタQ11、Q12、…、Q1n、Q21、Q22、…、Q2n、…、Qm1、Qm2、…、Qmnと蓄積キャパシタCSとの並列回路からなる。

【0060】

ISFETセルC11、C12、…、C1n、C21、C22、…、C2n、…、Cm1、Cm2、…、Cmnは、前述の図10に示すように、第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域12と、第1ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、第1ウェル領域12上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に配置されたイオン感応膜19と、ソース領域14とドレイン領域16間に接続される蓄積キャパシタCSと、イオン感応膜19に接触する液体試料26と、液体試料26中に配置された参照電極24と備える。

【0061】

また、ISFETセルC11、C12、…、C1n、C21、C22、…、C2n、…、Cm1、Cm2、…、Cmnは、さらに、半導体基板10上に配置され、第1導電型を有する第2ウェル領域23と、第2ウェル領域23上に配置され、第1導電型を有する第2ウェルコンタクト領域13と、第2ウェル領域23上に配置されたゲート絶縁膜18上に配置され、第2ウェル領域23との間で蓄積キャパシタCSを形成するキャパシタ電極21とを備えていても良い。

【0062】

また、ドレイン領域16は、キャパシタ電極21に接続され、ソース領域14は、ウェルコンタクト領域13に接続され、ドレイン領域16とソース領域14間に並列に蓄積キャパシタCSを備えていても良い。

【0063】

第2の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4は、図13に示すように、複数の水平選択トランジスタQH1,QH2,…,QHnのドレインを共通接続して得られた出力端子と接地電位間に接続されたMOSFETQLNと、複数の垂直選択トランジスタQV1,QV2,…,QVmのソースを共通接続して得られた電源ラインに接続された電源電圧VDDとを備える。

【0064】

第2の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4は、複数の水平選択トランジスタQH1,QH2,…,QHnのドレインを共通接続して得られた電源ラインに接続された電源電圧VDDと、複数の垂直選択トランジスタQV1,QV2,…,QVmのソースを共通接続して得られた出力端子と接地電位間に接続されたMOSFETQLNとを備えていても良い。

【0065】

第2の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4においては、各画素のイオン検出トランジスタQ11、Q12、…、Q1n、Q21、Q22、…、Q2n、…、Qm1、Qm2、…、Qmnに対して、蓄積キャパシタCSを並列接続し、これにより、画素選択時に蓄積キャパシタCSが充電され、画素選択されていない時に蓄積キャパシタCSが放電することにより、常に駆動状態を保持することができ、ISFETアレイ4のアレイ動作を安定化することができる。すなわち、画素選択されていない時も蓄積キャパシタCSから電力供給されるため、駆動状態を保持可能であり、安定性が向上する。

【0066】

[第3の実施の形態]

(ISFET)

第3の実施の形態に係るISFETの模式的断面構造は、図15に示すように、ゲート絶縁膜18上に、ドレイン領域16に隣接して配置されたトランスファゲート電極20を備える。その他の構成は、図10に示した第2の実施の形態と同様であるため、重複説明は省略する。

【0067】

また、第3の実施の形態に係るISFETの模式的回路構成は、図16に示すように、イオン検出部6のイオン検出トランジスタQiと、トランスファゲートTGによるトランスファゲートトランジスタQGの直列回路と、トランスファゲートトランジスタQGのドレインとイオン検出トランジスタQiのソース間に接続された蓄積キャパシタCSとの並列回路で構成され、トランスファゲートトランジスタQGのドレイン領域16に電源電圧VDが接続され、イオン検出トランジスタQiのソース領域14には、MOSFETQLNが接続される。

【0068】

また、第3の実施の形態に係るISFETは、第1の実施の形態に係るISFETと、第2の実施の形態に係るISFETとの両方の動作モードを兼ね備えている。

【0069】

すなわち、第3の実施の形態に係るISFET2においては、トランスファゲート電極20に加える電圧を調節することにより、リセット情報、光情報を取得するモードと、pHを取得するモードを切り替えることができるため、正確なイオン情報を検出することができる。

【0070】

また、第3の実施の形態に係るISFET2においては、イオン検出トランジスタQmnとトランスファゲートトランジスタQGの直列構成に対して、蓄積キャパシタCSを並列接続することにより、ドレインDとソースS間に電源電圧が印加されたオン状態では蓄積キャパシタCSが充電され、ドレインDとソースS間に電源電圧が印加されないオフ状態では蓄積キャパシタCSが放電することにより、常に駆動状態を保持することができ、安定性が向上する。

【0071】

(ISFETアレイ)

第3の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4の模式的回路ブロック構成は、図17に示すように、行方向に延伸する複数のワード線WL1,WL2,…,WLmと、ワード線WL1,WL2,…,WLmに直交し、列方向に延伸する複数のビット線BL1,BL2,…,BLnと、複数のワード線WL1,WL2,…,WLmに対してそれぞれドレインが接続された複数の垂直選択トランジスタQV1,QV2,…,QVmと、複数の垂直選択トランジスタQV1,QV2,…,QVmのそれぞれゲートが接続された垂直走査回路30と、複数のビット線BL1,BL2,…,BLnに対して、それぞれソースが接続された水平選択トランジスタQH1,QH2,…,QHnと、複数の水平トランジスタQH1,QH2,…,QHnのそれぞれゲートが接続された水平走査回路32と、ワード線WL1,WL2,…,WLmとビット線BL1,BL2,…,BLnの交差部に配置されたISFETセルCmnとを備える。

【0072】

ここで、ISFETセルCmnは、図16に示すように、イオン検出トランジスタQiとトランスファゲートトランジスタQGの直列回路と、ドレインとソース間に接続された蓄積キャパシタCSとの並列回路で構成される。

【0073】

ここで、ISFETセルCmnは、第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域12と、第1ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、第1ウェル領域12上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に、ドレイン領域16に隣接して配置されたトランスファゲート電極20と、ゲート絶縁膜18上に配置されたイオン感応膜19と、ソース領域14とドレイン領域16間に接続される蓄積キャパシタCSと、イオン感応膜19に接触する液体試料26と、液体試料26中に配置された参照電極24とを備える。

【0074】

ISFETセルCmnは、さらに、半導体基板10上に配置され、第1導電型を有する第2ウェル領域23と、第2ウェル領域23上に配置され、第1導電型を有する第2ウェルコンタクト領域13と、第2ウェル領域23上のゲート絶縁膜18上に配置され、第2ウェル領域23との間で蓄積キャパシタCSを形成するキャパシタ電極21とを備えていても良い。

【0075】

また、ドレイン領域16は、キャパシタ電極21に接続され、ソース領域14は、ウェルコンタクト領域13に接続され、ドレイン領域16とソース領域14間に並列に蓄積キャパシタCSを備えていても良い。

【0076】

第3の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4は、図17に示すように、複数の水平選択トランジスタQH1,QH2,…,QHnのドレインを共通接続して得られた電源ラインに接続された電源電圧VDDと、複数の垂直選択トランジスタQV1,QV2,…,QVmのソースを共通接続して得られた出力端子と接地電位間に接続されたMOSFETQLNを備える。

【0077】

第3の実施の形態に係るISFETをアレイ状に配列したISFETアレイ4は、複数の水平選択トランジスタQH1,QH2,…,QHnのドレインを共通接続して得られた出力端子と接地電位間に接続されたMOSFETQLNと、複数の垂直選択トランジスタQV1,QV2,…,QVmのソースを共通接続して得られた電源ラインに接続された電源電圧VDDとを備えていても良い。

【0078】

第3の実施の形態に係るISFETアレイ4においては、ISFETアレイ4が配置された半導体基板10上に試料セル100を配置し、リセット情報・光情報の検出時は、ISFETセルCijのトランスファゲート電極20のトランスファゲート電位VTGをオフ状態のローレベルとし、pHイオン情報の検出時は、オン状態のハイレベルとし、トランスファゲート電極20のトランスファゲート電位VTGによってオン、オフ制御することによって、リセット情報・光情報のイメージ情報と、pHイオン分布情報の両方を検出することができる。

【0079】

また、第3の実施の形態に係るISFETアレイ4においては、各画素のイオン検出トランジスタQmnとトランスファゲートトランジスタQGの直列回路に対して、蓄積キャパシタCSを並列接続し、これにより、画素選択時に蓄積キャパシタCSが充電され、画素選択されていない時に蓄積キャパシタCSが放電することにより、常に駆動状態を保持することができ、ISFETアレイ4のアレイ動作を安定化することができる。すなわち、画素選択されていない時も蓄積キャパシタCSから電力供給されるため、駆動状態を保持可能であり、安定性が向上する。

【0080】

[第4の実施の形態]

第4の実施の形態に係るISFET2は、図18に示すように、ソース領域、ドレイン領域、および第2ウェル領域上に配置されたパッシベーション膜22と、パッシベーション膜22上に配置された遮光膜50aとを備える。さらに、図18に示すように、遮光膜50a上にパッシベーション膜22aを備えていても良い。なお、遮光膜50aは、例えば、アルミニウムの薄膜層などで形成可能である。

【0081】

また、図18においては、第1ウェル領域12に形成された第1ウェルコンタクト領域45と、半導体基板10に対して形成された基板コンタクト領域43を備える。その他の構成は、図10に示す第2の実施の形態と同様であるため、重複説明は省略する。

【0082】

また、第4の実施の形態に係るISFET2も第2の実施の形態と同様に、図13と同様にISFETアレイ4を構成可能であるが、重複説明は省略する。

【0083】

第4の実施の形態によれば、イオン検出部以外の領域に遮光膜を備えるため、イオン検出感度を向上したISFETおよび当該ISFETセルを適用し、常時駆動によって安定化可能なISFETアレイを提供することができる。

【0084】

[第5の実施の形態]

第5の実施の形態に係るISFET2は、図19に示すように、第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域12と、第1ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、第1ウェル領域12上に配置されたゲート絶縁膜18と、ソース領域14とドレイン領域16間のゲート絶縁膜18上に配置されたゲートプラグ電極40と、ドレイン領域16上に配置されたドレインプラグ電極44と、ソース領域14とドレインプラグ電極44間に接続され、積層電極46・48からなる蓄積キャパシタCSと、ゲートプラグ電極40上に配置された遮光膜42と、遮光膜42上に配置されたイオン感応膜19と、イオン感応膜19に接触する液体試料26と、液体試料26中に配置された参照電極24とを備える。

【0085】

また、第5の実施の形態に係るISFET2は、図19に示すように、第1ウェル領域12および半導体基板10上のゲート絶縁膜18上に配置されたパッシベーション膜22と、パッシベーション膜22上に配置された遮光膜50aとを備える。遮光膜42・50aは、例えば、アルミニウムの薄膜層などで形成可能である。その他の構成は、図18に示す第4の実施の形態と同様であるため、重複説明は省略する。

【0086】

また、第5の実施の形態に係るISFET2も第2の実施の形態と同様に、図13と同様にISFETアレイ4を構成可能であるが、重複説明は省略する。

【0087】

第5の実施の形態に係るISFET2においては、遮光膜42・50aを備えるため、イオン情報の検出感度を向上することができる。

【0088】

また、第5の実施の形態に係るISFET2においては、蓄積キャパシタCSを積層構造により形成できるため、集積度を向上することができる。

【0089】

また、第5の実施の形態に係るISFET2においては、イオン検出部6を素子領域の全面に形成できるため、イオン情報の検出感度を向上することができる。

【0090】

以上説明したように、本実施の形態によれば、検出感度を向上したISFETおよび当該ISFETセルを適用し、常時駆動によって安定化可能なISFETアレイを提供することができる。

【0091】

(その他の実施の形態)

上記のように、本発明は第1〜第5の実施の形態によって記載したが、この開示の一部をなす論述および図面はこの発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施の形態、実施例および運用技術が明らかとなろう。

【0092】

このように、本発明はここでは記載していない様々な実施の形態等を含むことは勿論である。したがって、本発明の技術的範囲は上記の説明から妥当な特許請求の範囲に係る発明特定事項によってのみ定められるものである。

【産業上の利用可能性】

【0093】

本発明のISFETおよびISFETアレイは、細胞のpHセンサ、pHイオンの分布測定、水質調査、水質管理、環境測定、医療計測分野などに適用可能である。

【符号の説明】

【0094】

2…ISFET

4…ISFETアレイ

6…イオン検出部

10…半導体基板

12…pウェル層

13…nウェルコンタクト領域

14…ソース領域

16…ドレイン領域

17…LOCOS絶縁膜

18…ゲート絶縁膜

19…イオン感応膜

20…トランスファゲート電極(TG)

21、46、48…キャパシタ電極

22…パッシベーション膜

23…nウェル層

24…参照電極

26…液体試料

30…垂直走査回路

32…水平走査回路

40…ゲートプラグ電極

43…基板コンタクト領域

44…ドレインプラグ電極

45…pウェルコンタクト領域

42、50、50a…遮光膜

100…試料セル

200…pH分布

WL1,WL2,…,WLm…ワード線(垂直走査線)

BL1,BL2,…,BLn…ビット線(水平走査線)

QV1,QV2,…,QVm…垂直選択トランジスタ

QH1,QH2,…,QHn…水平選択トランジスタ

QLN…MOSFET

Qi、Q11、Q12、…、Q1n、Q21、Q22、…、Q2n、…、Qm1、Qm2、…、Qmn…イオン検出トランジスタ

QG…トランスファゲートトランジスタ

C11、C12、…、C1n、C21、C22、…、C2n、…、Cm1、Cm2、…、Cmn…ISFETセル

CS…蓄積キャパシタ

VREF…参照電圧

VD,VDD…電源電圧

Vout…出力電圧

VLN、VTG…ゲート電圧

VTG…トランスファゲート電圧

【特許請求の範囲】

【請求項1】

第1導電型を有する半導体基板と、

前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域と、

前記ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、

前記ソース領域と、前記ウェル領域と、前記ドレイン領域上に配置されたゲート絶縁膜と、

前記ゲート絶縁膜上に、前記ドレイン領域に隣接して配置されたトランスファゲート電極と、

前記ゲート絶縁膜に接触する液体試料と、

前記液体試料中に配置された参照電極と

を備えることを特徴とするISFET。

【請求項2】

前記ゲート絶縁膜上にイオン感応膜をさらに備えることを特徴とする請求項1に記載のISFET。

【請求項3】

前記トランスファゲート電極の電位は、リセット情報、光情報の検出時は、オフ状態のローレベル、pHイオン情報の検出時は、オン状態のハイレベルとし、前記トランスファゲート電極の電位よってオン、オフ制御することを特徴とする請求項1または2に記載のISFET。

【請求項4】

前記ドレイン領域に接続された電源電圧と、

前記ソース領域に接続されたMOSFETと

を備え、全体が前記液体試料の液体界面のポテンシャルによる入力信号に対するソースフォロア回路となり、前記MOSFETのドレイン端子より得られる出力が、前記入力信号に対して、リニアに出力応答することを特徴とする請求項1〜3のいずれか1に記載のISFET。

【請求項5】

第1導電型を有する半導体基板と、

前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域と、

前記第1ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、

前記第1ウェル領域上に配置されたゲート絶縁膜と、

前記ゲート絶縁膜上に配置されたイオン感応膜と、

前記ソース領域と前記ドレイン領域間に接続される蓄積キャパシタと、

前記イオン感応膜に接触する液体試料と、

前記液体試料中に配置された参照電極と

を備えることを特徴とするISFET。

【請求項6】

前記半導体基板上に配置され、第1導電型を有する第2ウェル領域と、

前記第2ウェル領域上に配置され、第1導電型を有する第2ウェルコンタクト領域と、

前記第2ウェル領域上の前記ゲート絶縁膜上に配置され、前記第2ウェル領域との間で前記蓄積キャパシタを形成するキャパシタ電極と

を備えることを特徴とする請求項5に記載のISFET。

【請求項7】

前記ドレイン領域は、前記キャパシタ電極に接続され、前記ソース領域は、前記ウェルコンタクト領域に接続され、前記ドレイン領域と前記ソース領域間に並列に前記蓄積キャパシタを備えることを特徴とする請求項6に記載のISFET。

【請求項8】

前記ゲート絶縁膜上に、前記ドレイン領域に隣接して配置されたトランスファゲート電極を備えることを特徴とする請求項6または7に記載のISFET。

【請求項9】

前記ソース領域、前記ドレイン領域、および前記第2ウェル領域上に配置されたパッシべーション膜と、前記パッシべーション膜上に配置された遮光膜とを備えることを特徴とする請求項8に記載のISFET。

【請求項10】

第1導電型を有する半導体基板と、

前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域と、

前記第1ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、

前記第1ウェル領域上に配置されたゲート絶縁膜と、

前記ソース領域と前記ドレイン領域間の前記ゲート絶縁膜上に配置されたゲートプラグ電極と、

前記ドレイン領域上に配置されたドレインプラグ電極と、

前記ソース領域と前記前記ドレインプラグ電極間に接続され、積層電極からなる蓄積キャパシタと、

前記ゲートプラグ電極上に配置された遮光膜と、

前記遮光膜上に配置されたイオン感応膜と、

前記イオン感応膜に接触する液体試料と、

前記液体試料中に配置された参照電極と

を備えることを特徴とするISFET。

【請求項11】

行方向に延伸する複数のワード線と、

前記ワード線に直交し、列方向に延伸する複数のビット線と、

前記複数のワード線に対してそれぞれドレインが接続された複数の垂直選択トランジスタと、

前記複数の垂直選択トランジスタのそれぞれゲートが接続された垂直走査回路と、

前記複数のビット線に対して、それぞれソースが接続された水平選択トランジスタと、

前記複数の水平トランジスタのそれぞれゲートが接続された水平走査回路と、

前記ワード線と前記ビット線の交差部に配置されたISFETセルと

を備え、

前記ISFETセルは、

第1導電型を有する半導体基板と、

前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域と、

前記ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、

前記ウェル領域上に配置されたゲート絶縁膜と、

前記ゲート絶縁膜上に、前記ドレイン領域に隣接して配置されたトランスファゲート電極と、

前記ゲート絶縁膜に接触する液体試料と、

前記液体試料中に配置された参照電極と

を備えることを特徴とするISFETアレイ。

【請求項12】

前記複数の垂直選択トランジスタのソースを共通接続して得られた出力端子と接地電位間に接続されたMOSFETと、

前記複数の水平選択トランジスタのドレインを共通接続して得られた電源ラインに接続された電源電圧と、

前記トランスファゲート電極を共通化したトランスファゲートラインに接続されたトランスファゲート電圧と

を備えることを特徴とする請求項11に記載のISFETアレイ。

【請求項13】

前記ゲート絶縁膜上にイオン感応膜をさらに備えることを特徴とする請求項11または12に記載のISFETアレイ。

【請求項14】

前記ISFETアレイが配置された半導体基板上に試料セルを配置し、リセット情報、光情報の検出時は、前記ISFETセルの前記トランスファゲート電極の電位をオフ状態のローレベルとし、pHイオン情報の検出時は、オン状態のハイレベルとし、前記トランスファゲート電極の電位よってオン、オフ制御することによって、リセット情報、光情報のイメージ情報と、pHイオン分布情報の両方を検出することを特徴とする請求項11〜13のいずれか1項に記載のISFETアレイ。

【請求項15】

行方向に延伸する複数のワード線と、

前記ワード線に直交し、列方向に延伸する複数のビット線と、

前記複数のワード線に対してそれぞれドレインが接続された複数の垂直選択トランジスタと、

前記複数の垂直選択トランジスタのそれぞれゲートが接続された垂直走査回路と、

前記複数のビット線に対して、それぞれソースが接続された水平選択トランジスタと、

前記複数の水平トランジスタのそれぞれゲートが接続された水平走査回路と、

前記ワード線と前記ビット線の交差部に配置されたISFETセルと

を備え、

前記ISFETセルは、

第1導電型を有する半導体基板と、

前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域と、

前記第1ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、

前記第1ウェル領域上に配置されたゲート絶縁膜と、

前記ゲート絶縁膜上に配置されたイオン感応膜と、

前記ソース領域と前記ドレイン領域間に接続される蓄積キャパシタと、

前記イオン感応膜に接触する液体試料と、

前記液体試料中に配置された参照電極と

を備えることを特徴とするISFETアレイ。

【請求項16】

前記ISFETセルは、さらに

前記半導体基板上に配置され、第1導電型を有する第2ウェル領域と、

前記第2ウェル領域上に配置され、第1導電型を有する第2ウェルコンタクト領域と、

前記第2ウェル領域上の前記ゲート絶縁膜上に配置され、前記第2ウェル領域との間で前記蓄積キャパシタを形成するキャパシタ電極と

を備えることを特徴とする請求項15に記載のISFETアレイ。

【請求項17】

前記ドレイン領域は、前記キャパシタ電極に接続され、前記ソース領域は、前記ウェルコンタクト領域に接続され、前記ドレイン領域と前記ソース領域間に並列に前記蓄積キャパシタを備えることを特徴とする請求項16に記載のISFETアレイ。

【請求項18】

前記ISFETセルは、さらに

前記ゲート絶縁膜上に、前記ドレイン領域に隣接して配置されたトランスファゲート電極を備えることを特徴とする請求項16または17に記載のISFETアレイ。

【請求項19】

前記複数の水平選択トランジスタのドレインを共通接続して得られた電源ラインに接続された電源電圧と、

前記複数の垂直選択トランジスタのソースを共通接続して得られた出力端子と接地電位間に接続されたMOSFETを備えることを特徴とする請求項15〜18いずれか1項に記載のISFETアレイ。

【請求項20】

前記複数の水平選択トランジスタのドレインを共通接続して得られた出力端子と接地電位間に接続されたMOSFETと、

前記複数の垂直選択トランジスタのソースを共通接続して得られた電源ラインに接続された電源電圧とを備えることを特徴とする請求項15〜18のいずれか1項に記載のISFETアレイ。

【請求項1】

第1導電型を有する半導体基板と、

前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域と、

前記ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、

前記ソース領域と、前記ウェル領域と、前記ドレイン領域上に配置されたゲート絶縁膜と、

前記ゲート絶縁膜上に、前記ドレイン領域に隣接して配置されたトランスファゲート電極と、

前記ゲート絶縁膜に接触する液体試料と、

前記液体試料中に配置された参照電極と

を備えることを特徴とするISFET。

【請求項2】

前記ゲート絶縁膜上にイオン感応膜をさらに備えることを特徴とする請求項1に記載のISFET。

【請求項3】

前記トランスファゲート電極の電位は、リセット情報、光情報の検出時は、オフ状態のローレベル、pHイオン情報の検出時は、オン状態のハイレベルとし、前記トランスファゲート電極の電位よってオン、オフ制御することを特徴とする請求項1または2に記載のISFET。

【請求項4】

前記ドレイン領域に接続された電源電圧と、

前記ソース領域に接続されたMOSFETと

を備え、全体が前記液体試料の液体界面のポテンシャルによる入力信号に対するソースフォロア回路となり、前記MOSFETのドレイン端子より得られる出力が、前記入力信号に対して、リニアに出力応答することを特徴とする請求項1〜3のいずれか1に記載のISFET。

【請求項5】

第1導電型を有する半導体基板と、

前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域と、

前記第1ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、

前記第1ウェル領域上に配置されたゲート絶縁膜と、

前記ゲート絶縁膜上に配置されたイオン感応膜と、

前記ソース領域と前記ドレイン領域間に接続される蓄積キャパシタと、

前記イオン感応膜に接触する液体試料と、

前記液体試料中に配置された参照電極と

を備えることを特徴とするISFET。

【請求項6】

前記半導体基板上に配置され、第1導電型を有する第2ウェル領域と、

前記第2ウェル領域上に配置され、第1導電型を有する第2ウェルコンタクト領域と、

前記第2ウェル領域上の前記ゲート絶縁膜上に配置され、前記第2ウェル領域との間で前記蓄積キャパシタを形成するキャパシタ電極と

を備えることを特徴とする請求項5に記載のISFET。

【請求項7】

前記ドレイン領域は、前記キャパシタ電極に接続され、前記ソース領域は、前記ウェルコンタクト領域に接続され、前記ドレイン領域と前記ソース領域間に並列に前記蓄積キャパシタを備えることを特徴とする請求項6に記載のISFET。

【請求項8】

前記ゲート絶縁膜上に、前記ドレイン領域に隣接して配置されたトランスファゲート電極を備えることを特徴とする請求項6または7に記載のISFET。

【請求項9】

前記ソース領域、前記ドレイン領域、および前記第2ウェル領域上に配置されたパッシべーション膜と、前記パッシべーション膜上に配置された遮光膜とを備えることを特徴とする請求項8に記載のISFET。

【請求項10】

第1導電型を有する半導体基板と、

前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域と、

前記第1ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、

前記第1ウェル領域上に配置されたゲート絶縁膜と、

前記ソース領域と前記ドレイン領域間の前記ゲート絶縁膜上に配置されたゲートプラグ電極と、

前記ドレイン領域上に配置されたドレインプラグ電極と、

前記ソース領域と前記前記ドレインプラグ電極間に接続され、積層電極からなる蓄積キャパシタと、

前記ゲートプラグ電極上に配置された遮光膜と、

前記遮光膜上に配置されたイオン感応膜と、

前記イオン感応膜に接触する液体試料と、

前記液体試料中に配置された参照電極と

を備えることを特徴とするISFET。

【請求項11】

行方向に延伸する複数のワード線と、

前記ワード線に直交し、列方向に延伸する複数のビット線と、

前記複数のワード線に対してそれぞれドレインが接続された複数の垂直選択トランジスタと、

前記複数の垂直選択トランジスタのそれぞれゲートが接続された垂直走査回路と、

前記複数のビット線に対して、それぞれソースが接続された水平選択トランジスタと、

前記複数の水平トランジスタのそれぞれゲートが接続された水平走査回路と、

前記ワード線と前記ビット線の交差部に配置されたISFETセルと

を備え、

前記ISFETセルは、

第1導電型を有する半導体基板と、

前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域と、

前記ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、

前記ウェル領域上に配置されたゲート絶縁膜と、

前記ゲート絶縁膜上に、前記ドレイン領域に隣接して配置されたトランスファゲート電極と、

前記ゲート絶縁膜に接触する液体試料と、

前記液体試料中に配置された参照電極と

を備えることを特徴とするISFETアレイ。

【請求項12】

前記複数の垂直選択トランジスタのソースを共通接続して得られた出力端子と接地電位間に接続されたMOSFETと、

前記複数の水平選択トランジスタのドレインを共通接続して得られた電源ラインに接続された電源電圧と、

前記トランスファゲート電極を共通化したトランスファゲートラインに接続されたトランスファゲート電圧と

を備えることを特徴とする請求項11に記載のISFETアレイ。

【請求項13】

前記ゲート絶縁膜上にイオン感応膜をさらに備えることを特徴とする請求項11または12に記載のISFETアレイ。

【請求項14】

前記ISFETアレイが配置された半導体基板上に試料セルを配置し、リセット情報、光情報の検出時は、前記ISFETセルの前記トランスファゲート電極の電位をオフ状態のローレベルとし、pHイオン情報の検出時は、オン状態のハイレベルとし、前記トランスファゲート電極の電位よってオン、オフ制御することによって、リセット情報、光情報のイメージ情報と、pHイオン分布情報の両方を検出することを特徴とする請求項11〜13のいずれか1項に記載のISFETアレイ。

【請求項15】

行方向に延伸する複数のワード線と、

前記ワード線に直交し、列方向に延伸する複数のビット線と、

前記複数のワード線に対してそれぞれドレインが接続された複数の垂直選択トランジスタと、

前記複数の垂直選択トランジスタのそれぞれゲートが接続された垂直走査回路と、

前記複数のビット線に対して、それぞれソースが接続された水平選択トランジスタと、

前記複数の水平トランジスタのそれぞれゲートが接続された水平走査回路と、

前記ワード線と前記ビット線の交差部に配置されたISFETセルと

を備え、

前記ISFETセルは、

第1導電型を有する半導体基板と、

前記半導体基板上に配置され、第1導電型と反対導電型の第2導電型を有する第1ウェル領域と、

前記第1ウェル領域上に配置され、第1導電型を有するソース領域およびドレイン領域と、

前記第1ウェル領域上に配置されたゲート絶縁膜と、

前記ゲート絶縁膜上に配置されたイオン感応膜と、

前記ソース領域と前記ドレイン領域間に接続される蓄積キャパシタと、

前記イオン感応膜に接触する液体試料と、

前記液体試料中に配置された参照電極と

を備えることを特徴とするISFETアレイ。

【請求項16】

前記ISFETセルは、さらに

前記半導体基板上に配置され、第1導電型を有する第2ウェル領域と、

前記第2ウェル領域上に配置され、第1導電型を有する第2ウェルコンタクト領域と、

前記第2ウェル領域上の前記ゲート絶縁膜上に配置され、前記第2ウェル領域との間で前記蓄積キャパシタを形成するキャパシタ電極と

を備えることを特徴とする請求項15に記載のISFETアレイ。

【請求項17】

前記ドレイン領域は、前記キャパシタ電極に接続され、前記ソース領域は、前記ウェルコンタクト領域に接続され、前記ドレイン領域と前記ソース領域間に並列に前記蓄積キャパシタを備えることを特徴とする請求項16に記載のISFETアレイ。

【請求項18】

前記ISFETセルは、さらに

前記ゲート絶縁膜上に、前記ドレイン領域に隣接して配置されたトランスファゲート電極を備えることを特徴とする請求項16または17に記載のISFETアレイ。

【請求項19】

前記複数の水平選択トランジスタのドレインを共通接続して得られた電源ラインに接続された電源電圧と、

前記複数の垂直選択トランジスタのソースを共通接続して得られた出力端子と接地電位間に接続されたMOSFETを備えることを特徴とする請求項15〜18いずれか1項に記載のISFETアレイ。

【請求項20】

前記複数の水平選択トランジスタのドレインを共通接続して得られた出力端子と接地電位間に接続されたMOSFETと、

前記複数の垂直選択トランジスタのソースを共通接続して得られた電源ラインに接続された電源電圧とを備えることを特徴とする請求項15〜18のいずれか1項に記載のISFETアレイ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2012−202864(P2012−202864A)

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願番号】特願2011−68491(P2011−68491)

【出願日】平成23年3月25日(2011.3.25)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願日】平成23年3月25日(2011.3.25)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]