MOSトランジスタ

【課題】 再現性の高い工程を用いて低抵抗のゲート電極を有するGOLD構造を構成できるようにし、それにより、微細化が可能であるとともに信頼性の高いMOSトランジスタを提供する。

【解決手段】 半導体基板1に形成したソース及びドレイン領域10a,10bと、酸化膜3bを介して形成したゲート電極5と、前記ソース及びドレイン領域10a,10bとチャネル形成領域30の間に前記ソース及びドレイン領域10a,10bを取り囲むソース及びドレイン低濃度領域6a’,6b’とを有するMOSトランジスタにおいて、前記酸化膜3bを介して前記ソース及びドレイン低濃度領域6a’,6b’に接する導電性である2つのサイドスペーサ9aと、前記ゲート電極5及び前記サイドスペーサ9a上に形成された導電性薄膜15とを有する。

【解決手段】 半導体基板1に形成したソース及びドレイン領域10a,10bと、酸化膜3bを介して形成したゲート電極5と、前記ソース及びドレイン領域10a,10bとチャネル形成領域30の間に前記ソース及びドレイン領域10a,10bを取り囲むソース及びドレイン低濃度領域6a’,6b’とを有するMOSトランジスタにおいて、前記酸化膜3bを介して前記ソース及びドレイン低濃度領域6a’,6b’に接する導電性である2つのサイドスペーサ9aと、前記ゲート電極5及び前記サイドスペーサ9a上に形成された導電性薄膜15とを有する。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は、MOSトランジスタに係り、特に、トランジスタ特性のバラツキの少ない、信頼性の高いMOSトランジスタに好適なゲート電極構造に関するものである。

【0002】

【従来の技術】従来、MOSトランジスタのソース・ドレイン構造は、初期においては、単純なシングルドレイン構造であったが、高耐圧性の必要などの理由により、Double−Doped−Drain構造(単に、DDD構造ともいう)、Lightly−Doped−Drain構造(単に、LDD構造ともいう)が採用されるようになってきている。

【0003】DDD構造、LDD構造はともに、ソース・ドレイン高濃度領域を取り囲んで、同じ伝導型のソース・ドレイン低濃度領域(単に、LDDともいう)を設けることにより、ゲート・ドレイン間に高電界領域が生じないようにしたものである。しかしながら、LDD構造もトランジスタの高密度化のために、短チャネル化が進むにつれて、LDD上のゲート酸化膜にホットキャリアがトラップされる現象が顕著となり、しきい値(Vth)や伝達コンダクタンス(gm)が経時的に変動を引き起こし、信頼性が低下するという問題が出てきた。

【0004】そこで、この問題を解決するために、LDD構造におけるソース・ドレイン低濃度領域上にまでゲート電極を延長し、LDD上のゲート酸化膜中に注入されるホットキャリアによる電位をゲート電極の電位によって中和して、しきい値(Vth)や伝達コンダクタンス(gm)の変動を抑制することが可能なGate−OverLapped−Drain構造(以下,単にGOLD構造ともいう)が提案された。

【0005】以下、逆T字型GOLD構造(単に、IT−GOLD構造ともいう)のMOSトランジスタを概略製造工程とともに説明する。図4は、従来例のMOSトランジスタを示す断面構成図であリ、図5は、従来例のMOSトランジスタを製造するための概略工程図である。

【0006】図4において、50BはIT−GOLD構造のMOSトランジスタを示し、半導体基板1上に、トランジスタ素子分離用のフィールド酸化膜2aが形成されており、この間にコンタクトホール24a,24bを通して、配線電極25a,25bに接続したソース・ドレイン高濃度領域10a,10bが逆T字型のゲート電極5aを挟んで配置されており、ソース・ドレイン高濃度領域10a,10bを取り囲んで、ソース・ドレイン低濃度領域6a’,6b’が形成されており、ソース・ドレイン領域6a’,6b’の一部はゲート酸化膜3aを介してゲート電極5aの下に配置されている。所定の配線電極25a,25bの絶縁用に層間絶縁膜23が形成されている。ゲート電極5a下の基板1のソース・ドレイン低濃度領域6a’,6b’で挟まれた部分はチャネル形成領域30となる。

【0007】図5を参照して、このMOSトランジスタ50Bの概略製造方法を説明する。まず、図5の(a)に示すように、半導体基板1上にバッファ酸化膜を形成し、このバッファ酸化膜の所定箇所をシリコン窒化膜にてマスクして、フィールド酸化膜2を形成し、その後バッファ酸化膜とシリコン窒化膜を除去して、所定ゲート酸化膜3を形成した後、ポリシリコンなどからなる導電性薄膜4を形成する。

【0008】次に、図5の(b)に示すように、導電性薄膜4のゲート電極となる部分以外を適度にエッチングし、ゲート電極5部分を形成する。このとき、導電性薄膜4を全てエッチングしてしまうのではなく、適当な膜厚(例えば10〜100nm)だけ残して薄い導電性薄膜20を形成する。その後、フィールド酸化膜2とゲート電極5をマスクにして、薄い導電性薄膜20とゲート酸化膜3を介してイオン注入を行い、ソース・ドレイン低濃度領域6a,6bを形成する。ゲート電極5の下部のソース・ドレイン低濃度領域6a,6bに挟まれた基板1の部分はチャネル形成領域30となる。

【0009】次に、図5の(c)に示すように、ゲート電極5及び導電性薄膜20を蔽って、シリコン酸化膜からなる絶縁性薄膜21を形成する。

【0010】次に、図5の(d)に示すように、絶縁性薄膜21を反応性イオンエッチング法(以下、単にRIEともいう)などの異方性エッチング法を用いてエッチングして、ゲート電極5の側面にサイドスペーサ22を形成する。このエッチング工程で、薄い導電性薄膜20もエッチングする。このとき、サイドスペーサ22の下の導電性薄膜20は導電性薄膜20’として残るから、同じ材質のゲート電極5と一体になって、逆T字型をしたゲート電極5aが形成され、フィールド酸化膜2は、フィールド酸化膜2aとなる。このようにして形成されたサイドスペーサ22及びフィールド酸化膜2aをマスクとして,セルフアライン(自己整合)でイオン注入を行い、ソース・ドレイン低濃度領域6a,6b中にソース・ドレイン高濃度領域10a,10bを形成する。ソース・ドレイン低濃度領域6a,6bは縮小して、ソース・ドレイン低濃度領域6a’,6b’となる。

【0011】次に、図5の(e)に示すように、全面に層間絶縁膜23を形成し、ソース・ドレイン高濃度領域10a,10bに通じるコンタクトホール24a,24bを設け、全面にアルミを形成し,これを所定形状に加工して、配線電極25a,25bを形成し、IT−GOLD構造を有するMOSトランジスタ50Bを得る。

【0012】このIT−GOLD構造の場合、ゲート電極5aの薄い部分である導電性薄膜20’がソース・ドレイン低濃度領域(LDD)6a,6b上に存在するため、LDD表面のキャリア密度をゲート電極5aによって制御でき、ホットキャリアによって生じるトランジスタ特性の変動を抑制し、信頼性を向上することができる。

【0013】

【発明が解決しようとする課題】ところで、IT−GOLD構造は、デバイスの信頼性向上に大いに効果があるが、その製造方法が極めて難しく、安定でバラツキの少ないMOSトランジスタを効率良く生産することが困難であるという問題点がある。

【0014】特に、上述の図5の(b)で示した、導電性薄膜4をエッチングして、ゲート電極5をそのままに残し、他の部分を厚さの薄い例えば50nmから100nmの範囲における特定の値を有する導電性薄膜20に形成する工程の制御が極めて難しく、基本的にエッチング量のモニターが困難であるので、エッチング時間管理でエッチング量を管理するのであるが、エッチング装置使用状況、エッチング条件などのエッチングの再現性に関する管理が大変であり、簡単に導電性薄膜20の膜厚が変動してしまう。

【0015】すなわち、過剰にエッチングして、薄い導電性薄膜20の領域が形成されなかった場合には、通常のLDD構造となり、GOLD構造の効果が得られない。一方、エッチング量が少なく、導電性薄膜20の領域の膜厚が厚くなった場合には、LDD領域へのイオン注入量が少なくなり、LDD領域の直列抵抗が大きくなり、相互コンダクタンスが減少するなどして、MOSトランジスタ特性の劣化が生じる。さらに、基板(ウエハ)内で導電性薄膜20領域の膜厚の均一性が悪い場合、ウエハ内のMOSトランジスタ特性のばらつきを引き起こすので、これらの課題の解決が求められていた。

【0016】そこで本発明は、上記課題を解決して、MOSトランジスタにおいて、再現性の高い工程を用いて低抵抗のゲート電極を有するGOLD構造を構成できるようにし、それにより、微細化が可能であるとともに信頼性の高いMOSトランジスタを提供することを目的とするものである。

【0017】

【課題を解決するための手段】上記目的を達成するための手段として、第1の発明は、半導体基板と、前記半導体基板中に所定間隔離れて形成したソース及びドレイン高濃度領域と、前記ソース及びドレイン高濃度領域の間の前記半導体基板上に酸化膜を介して形成した導電性のゲート電極と、前記ゲート電極の下部の前記半導体基板部分をチャネル形成領域として、前記ソース及びドレイン高濃度領域と前記チャネル形成領域の間に前記ソース及びドレイン高濃度領域を取り囲んでそれぞれ形成したソース及びドレイン低濃度領域とを有するMOSトランジスタにおいて、前記酸化膜を介して前記ソース及びドレイン低濃度領域に接する導電性である2つのサイドスペーサと、前記ゲート電極及び前記サイドスペーサ上に形成されており、前記ゲート電極と前記サイドスペーサとを電気的に接続する導電性薄膜とを有することを特徴とするMOSトランジスタである。

【0018】また、第2の発明は、第1の発明において、前記導電性薄膜をチタンジシリサイドから構成したことを特徴とするものである。

【0019】

【発明の実施の形態】以下、本発明の実施の形態につき、好ましい実施例により、図面を参照して説明する。なお、説明の簡便のため、構成要素について、従来例と同一のものには同一の参照符号を付しその説明を省略する。

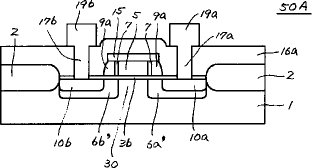

【0020】<実施例>図1は本発明のMOSトランジスタの実施例を示す断面構成図であリ、図2は本発明のMOSトランジスタの実施例を製造するための第1の概略工程図であリ、図3は本発明のMOSトランジスタの実施例を製造するための第2の概略工程図である。

【0021】図1に示すように、本発明の実施例であるMOSトランジスタ50Aは、半導体基板1上に、トランジスタ素子分離用のフィールド酸化膜2が形成されており、この間にコンタクトホール17a,17bを通して、配線電極19a,19bに接続したソース・ドレイン高濃度領域10a,10bが左右にサイドスペーサ9aを有するゲート電極5を挟んで配置されており、ソース・ドレイン高濃度領域10a,10bを取り囲んで、ソース・ドレイン低濃度領域6a’,6b’が形成されており、ソース・ドレイン領域6a’,6b’の一部はゲート酸化膜3bを介してサイドスペーサ9aの下に配置されている。ここで、サイドスペーサ9aは導電性を示し、同じく導電性を示すチタンシリサイド膜15を介してゲート電極5に接続されている。また、所定の配線電極19a,19bの絶縁用に層間絶縁膜16aが形成されている。ゲート電極5の下部のソース・ドレイン低濃度領域6a,6bに挟まれた基板1の部分はチャネル形成領域30となる。

【0022】以下、本実施例のMOSトランジスタについて、NMOSトランジスタを例に、その製造方法を説明する。まず、図2の(a)に示すように、p型シリコン基板1上に、熱酸化により,厚さ13nmのバッファ酸化膜を形成し、このバッファ酸化膜の上に、厚さ140nmの図示しないシリコン窒化膜を熱CVD法により形成し、このシリコン窒化膜をフォトリソ加工及びエッチング加工により所定パターン形状にしたものをマスクとして、バッファ酸化膜を選択的に熱酸化して、厚さ400nmのフィールド酸化膜2を形成する。その後、シリコン窒化膜とバッファ酸化膜を除去する。次に、熱酸化により、精密に厚さを9nmに制御したゲート酸化膜3と、減圧CVD法により、厚さ200nmのリンドープドポリシリコンからなる導電性薄膜4を順次全面に形成する。

【0023】次に、図2の(b)に示すように、フォトレジストを塗布して、所定パターン形状に露光現像して、図示しないフォトレジストパターンを形成し,これをマスクにして、例えば、塩素系のガスを用いるRIE法による異方性エッチングにより、ゲート電極5のみを残して、導電性薄膜4を除去する。次に、フィールド酸化膜2及びゲート電極をマスクとして、ゲート酸膜を通して、リンを加速電圧50keV、ドーズ量2×1013cm-2でイオン注入・ドライブインして、深さ200nmであるソース・ドレイン低濃度領域6a,6bを形成する。ゲート電極5の下部のソース・ドレイン低濃度領域6a,6bに挟まれた基板1の部分はチャネル形成領域30となる。

【0024】次に、図2の(c)に示すように、熱酸化により厚さ10nmであるシリコン酸化膜7を形成する。酸化膜7は、ゲート電極5の側面及び上面に形成される。

【0025】次に、図2の(d)に示すように、減圧CVD法により、厚さ200nmであるリンドープドポリシリコン膜8を全面に形成する。

【0026】次に、図2の(e)に示すように、例えば塩素系ガスを用いるRIE法による異方性エッチングを行い、ポリシリコン膜8を除去し、ゲート電極5の側面に酸化膜7を介してサイドスペーサ9を形成する。サイドスペーサ9の下部は、ゲート酸化膜を介して、ソース・ドレイン低濃度領域6a,6bに接している。

【0027】次に、図2の(f)に示すように、フィールド酸化膜2、ゲート電極5、ゲート電極5の側面に形成されている酸化膜7及びサイドスペーサ9をマスクとして、ゲート酸化膜3を通して、自己整合的にソース・ドレイン低濃度領域6a,6bの一部に、ヒ素を加速電圧50keV、ドーズ量2×1015cm-2で、イオン注入・ドライブインして深さ100nmであるソース・ドレイン高濃度領域10a,10bを形成する。ここで、ソース・ドレイン低濃度領域6a,6bは、ソース・ドレイン低濃度領域6a’,6b’に縮小し、LDD構造が得られる。

【0028】次に、図3の(g)に示すように、全面に、シランと酸素の混合ガスにP(リン)とB(ボロン)を添加したガスを用いた常圧CVD法により、厚さ500nmのBoron−Phosphorus−Silicate−Glass(単にBPSGともいう)膜からなる層間絶縁膜11を形成し、900℃30分間窒素雰囲気でBPSG膜のフォローを行い、平坦化する。

【0029】次に、図3の(h)に示すように、ケミカル・メカニカル・ポリッシング(単に、CMPともいう)により、例えばエッチング時間の制御により、層間絶縁膜11をエッチングして、ゲート電極5の上部の酸化膜7及びサイドスペーサ9aの上部も除去して、ポリシリコンからなる露出面12を得る。エッチングされて、サイドスペーサ9はサイドスペーサ9aに、層間絶縁膜11は層間絶縁膜11aに、酸化膜7は酸化膜7aとなる。

【0030】次に、図3の(i)に示すように、露出面12の表面に形成される、図示しない自然酸化膜を希フッ酸溶液を用いて除去した後、連続スパッタリング法により、厚さ50nmのTi(Co,Niなどでもよい)からなる高融点金属膜13、及び、Tiの酸化を防止するための厚さ100nmの窒化チタン(TiN)からなる保護膜14を形成する。

【0031】次に、図3の(j)に示すように、高速熱処理装置(ラピッド・サーマル・プロセッサであり、単にRTPともいう)を用いて、600度C程度、窒素雰囲気中で、熱処理する。このとき、高融点金属膜13のTiはゲート電極5及びサイドスペーサ9aのポリシリコンと反応し、チタンシリサイド(TiSi)を形成する。この時、TiがBPSG膜と接する場合には、Tiは未反応のまま残る。続いて、硫酸洗浄により、保護膜14及び未反応のTi(すなわち層間絶縁膜11a上の高融点金属膜の部分)を除去した後、RTPで今度は800℃程度、アルゴン雰囲気で数十秒間熱処理を行うことによって、低抵抗で安定なチタンジシリサイド(TiSi2)膜15がゲート電極5からサイドスペーサ9aにわたって形成される。これにより、ゲート電極5と導電性のサイドスペーサ9がチタンシリサイド膜15を介して電気的に導通がとれるようになる。

【0032】次に、図3の(k)に示すように、CVD法により厚さ500nmのシリコン酸化膜からなる層間絶縁膜16を形成する。層間絶縁膜11aと層間絶縁膜16が合わさって、層間絶縁膜16aが形成される。

【0033】次に、図3の(l)に示すように、ソース・ドレイン高濃度領域10a,10b上の層間絶縁膜16aにフォトリソ加工を施して、コンタクトホール17a,17bを形成後、アルミ膜を形成し、フォトリソ加工により、コンタクトホールを通してソース・ドレイン高濃度領域に接続する所定形状の配線電極19a,19bを形成し、本実施例のMOSトランジスタ50Aを得る。

【0034】このMOSトランジスタ50Aにおいては、ゲート電極5と導電性のサイドスペーサ9aはチタンシリサイド膜15を介して電気的に接続されており、サイドスペーサ9aの下面は、ゲート酸化膜3bを介して、ソース・ドレイン低濃度領域に接しており、上述のGOLD構造を構成している。このように構成したことにより、ソース・ドレイン低濃度領域のイオン注入は、従来のLDD構造と同じく均一な膜厚のゲート酸化膜を介して注入されるため、従来のGOLD構造と比較してウエハ内でのトランジスタ特性のばらつきを小さくすることができる。

【0035】また、実質的にポリサイドゲート構造となるため、ゲート電極の低抵抗化が実現でき、配線による信号の遅延を防止でき、しかも、トランジスタの微細化に対応できる。また、サイドスペーサの材質としてポリシリコンを用いた場合には、サイドスペーサの選択エッチング時にゲート酸化膜がエッチングストッパとして機能するから、活性領域のシリコン基板が露出することがなく、サイドスペーサエッチング時に、汚染等を受けず、特性バラツキの少ないMOSトランジスタ10Aを得ることができる。

【0036】さらに、上述の各製造工程は、きわめて、一般的で制御性の良好なものであり、したがって、MOSトランジスタ10Aを精度よく製造することができる。以上NMOSトランジスタを例に説明したが、PMOSトランジスタに適用できることはいうまでもない。

【0037】

【発明の効果】以上説明したように、本発明のMOSトランジスタは、請求項1及び2によれば、酸化膜を介してソース及びドレイン低濃度領域に接する導電性である2つのサイドスペーサと、ゲート電極及び前記サイドスペーサ上に形成されており、前記ゲート電極と前記サイドスペーサとを電気的に接続する導電性薄膜とを有することにより、再現性の高い工程を用いて低抵抗のゲート電極を有するGOLD構造を構成できるようにし、それにより、微細化が可能であるとともに信頼性の高いMOSトランジスタを提供することができるという効果がある。

【図面の簡単な説明】

【図1】本発明のMOSトランジスタの実施例を示す断面構成図である。

【図2】本発明のMOSトランジスタの実施例を製造するための第1の概略工程図である。

【図3】本発明のMOSトランジスタの実施例を製造するための第2の概略工程図である。

【図4】従来例のMOSトランジスタを示す断面構成図である。

【図5】従来例のMOSトランジスタを製造するための概略工程図である。

【符号の説明】

1…半導体(シリコン)基板、2…フィールド酸化膜、3,3a,3b…ゲート酸化膜、4…導電性薄膜、5,5a…ゲート電極、6a,6a’,6b,6b’…ソース・ドレイン低濃度領域、7…酸化膜、8…ポリシリコン膜、9,9a…サイドスペーサ、10a,10b…ソース・ドレイン高濃度領域、11,11a…層間絶縁膜、12…(ゲート電極部の)ポリシリコン露出面、13…高融点金属膜、14…保護膜(TiN:窒化チタン)、15…チタンジシリサイド(TiSi2)膜、16…層間絶縁膜、17a,17b…コンタクトホール、19a,19b…配線電極、20…(薄い)導電性薄膜、21…絶縁性薄膜、22…サイドスペーサ、23…層間絶縁膜、24a,24b…コンタクトホール、25a,25b…配線電極、30…チャネル形成領域、50A,50B…MOSトランジスタ。

【0001】

【発明の属する技術分野】本発明は、MOSトランジスタに係り、特に、トランジスタ特性のバラツキの少ない、信頼性の高いMOSトランジスタに好適なゲート電極構造に関するものである。

【0002】

【従来の技術】従来、MOSトランジスタのソース・ドレイン構造は、初期においては、単純なシングルドレイン構造であったが、高耐圧性の必要などの理由により、Double−Doped−Drain構造(単に、DDD構造ともいう)、Lightly−Doped−Drain構造(単に、LDD構造ともいう)が採用されるようになってきている。

【0003】DDD構造、LDD構造はともに、ソース・ドレイン高濃度領域を取り囲んで、同じ伝導型のソース・ドレイン低濃度領域(単に、LDDともいう)を設けることにより、ゲート・ドレイン間に高電界領域が生じないようにしたものである。しかしながら、LDD構造もトランジスタの高密度化のために、短チャネル化が進むにつれて、LDD上のゲート酸化膜にホットキャリアがトラップされる現象が顕著となり、しきい値(Vth)や伝達コンダクタンス(gm)が経時的に変動を引き起こし、信頼性が低下するという問題が出てきた。

【0004】そこで、この問題を解決するために、LDD構造におけるソース・ドレイン低濃度領域上にまでゲート電極を延長し、LDD上のゲート酸化膜中に注入されるホットキャリアによる電位をゲート電極の電位によって中和して、しきい値(Vth)や伝達コンダクタンス(gm)の変動を抑制することが可能なGate−OverLapped−Drain構造(以下,単にGOLD構造ともいう)が提案された。

【0005】以下、逆T字型GOLD構造(単に、IT−GOLD構造ともいう)のMOSトランジスタを概略製造工程とともに説明する。図4は、従来例のMOSトランジスタを示す断面構成図であリ、図5は、従来例のMOSトランジスタを製造するための概略工程図である。

【0006】図4において、50BはIT−GOLD構造のMOSトランジスタを示し、半導体基板1上に、トランジスタ素子分離用のフィールド酸化膜2aが形成されており、この間にコンタクトホール24a,24bを通して、配線電極25a,25bに接続したソース・ドレイン高濃度領域10a,10bが逆T字型のゲート電極5aを挟んで配置されており、ソース・ドレイン高濃度領域10a,10bを取り囲んで、ソース・ドレイン低濃度領域6a’,6b’が形成されており、ソース・ドレイン領域6a’,6b’の一部はゲート酸化膜3aを介してゲート電極5aの下に配置されている。所定の配線電極25a,25bの絶縁用に層間絶縁膜23が形成されている。ゲート電極5a下の基板1のソース・ドレイン低濃度領域6a’,6b’で挟まれた部分はチャネル形成領域30となる。

【0007】図5を参照して、このMOSトランジスタ50Bの概略製造方法を説明する。まず、図5の(a)に示すように、半導体基板1上にバッファ酸化膜を形成し、このバッファ酸化膜の所定箇所をシリコン窒化膜にてマスクして、フィールド酸化膜2を形成し、その後バッファ酸化膜とシリコン窒化膜を除去して、所定ゲート酸化膜3を形成した後、ポリシリコンなどからなる導電性薄膜4を形成する。

【0008】次に、図5の(b)に示すように、導電性薄膜4のゲート電極となる部分以外を適度にエッチングし、ゲート電極5部分を形成する。このとき、導電性薄膜4を全てエッチングしてしまうのではなく、適当な膜厚(例えば10〜100nm)だけ残して薄い導電性薄膜20を形成する。その後、フィールド酸化膜2とゲート電極5をマスクにして、薄い導電性薄膜20とゲート酸化膜3を介してイオン注入を行い、ソース・ドレイン低濃度領域6a,6bを形成する。ゲート電極5の下部のソース・ドレイン低濃度領域6a,6bに挟まれた基板1の部分はチャネル形成領域30となる。

【0009】次に、図5の(c)に示すように、ゲート電極5及び導電性薄膜20を蔽って、シリコン酸化膜からなる絶縁性薄膜21を形成する。

【0010】次に、図5の(d)に示すように、絶縁性薄膜21を反応性イオンエッチング法(以下、単にRIEともいう)などの異方性エッチング法を用いてエッチングして、ゲート電極5の側面にサイドスペーサ22を形成する。このエッチング工程で、薄い導電性薄膜20もエッチングする。このとき、サイドスペーサ22の下の導電性薄膜20は導電性薄膜20’として残るから、同じ材質のゲート電極5と一体になって、逆T字型をしたゲート電極5aが形成され、フィールド酸化膜2は、フィールド酸化膜2aとなる。このようにして形成されたサイドスペーサ22及びフィールド酸化膜2aをマスクとして,セルフアライン(自己整合)でイオン注入を行い、ソース・ドレイン低濃度領域6a,6b中にソース・ドレイン高濃度領域10a,10bを形成する。ソース・ドレイン低濃度領域6a,6bは縮小して、ソース・ドレイン低濃度領域6a’,6b’となる。

【0011】次に、図5の(e)に示すように、全面に層間絶縁膜23を形成し、ソース・ドレイン高濃度領域10a,10bに通じるコンタクトホール24a,24bを設け、全面にアルミを形成し,これを所定形状に加工して、配線電極25a,25bを形成し、IT−GOLD構造を有するMOSトランジスタ50Bを得る。

【0012】このIT−GOLD構造の場合、ゲート電極5aの薄い部分である導電性薄膜20’がソース・ドレイン低濃度領域(LDD)6a,6b上に存在するため、LDD表面のキャリア密度をゲート電極5aによって制御でき、ホットキャリアによって生じるトランジスタ特性の変動を抑制し、信頼性を向上することができる。

【0013】

【発明が解決しようとする課題】ところで、IT−GOLD構造は、デバイスの信頼性向上に大いに効果があるが、その製造方法が極めて難しく、安定でバラツキの少ないMOSトランジスタを効率良く生産することが困難であるという問題点がある。

【0014】特に、上述の図5の(b)で示した、導電性薄膜4をエッチングして、ゲート電極5をそのままに残し、他の部分を厚さの薄い例えば50nmから100nmの範囲における特定の値を有する導電性薄膜20に形成する工程の制御が極めて難しく、基本的にエッチング量のモニターが困難であるので、エッチング時間管理でエッチング量を管理するのであるが、エッチング装置使用状況、エッチング条件などのエッチングの再現性に関する管理が大変であり、簡単に導電性薄膜20の膜厚が変動してしまう。

【0015】すなわち、過剰にエッチングして、薄い導電性薄膜20の領域が形成されなかった場合には、通常のLDD構造となり、GOLD構造の効果が得られない。一方、エッチング量が少なく、導電性薄膜20の領域の膜厚が厚くなった場合には、LDD領域へのイオン注入量が少なくなり、LDD領域の直列抵抗が大きくなり、相互コンダクタンスが減少するなどして、MOSトランジスタ特性の劣化が生じる。さらに、基板(ウエハ)内で導電性薄膜20領域の膜厚の均一性が悪い場合、ウエハ内のMOSトランジスタ特性のばらつきを引き起こすので、これらの課題の解決が求められていた。

【0016】そこで本発明は、上記課題を解決して、MOSトランジスタにおいて、再現性の高い工程を用いて低抵抗のゲート電極を有するGOLD構造を構成できるようにし、それにより、微細化が可能であるとともに信頼性の高いMOSトランジスタを提供することを目的とするものである。

【0017】

【課題を解決するための手段】上記目的を達成するための手段として、第1の発明は、半導体基板と、前記半導体基板中に所定間隔離れて形成したソース及びドレイン高濃度領域と、前記ソース及びドレイン高濃度領域の間の前記半導体基板上に酸化膜を介して形成した導電性のゲート電極と、前記ゲート電極の下部の前記半導体基板部分をチャネル形成領域として、前記ソース及びドレイン高濃度領域と前記チャネル形成領域の間に前記ソース及びドレイン高濃度領域を取り囲んでそれぞれ形成したソース及びドレイン低濃度領域とを有するMOSトランジスタにおいて、前記酸化膜を介して前記ソース及びドレイン低濃度領域に接する導電性である2つのサイドスペーサと、前記ゲート電極及び前記サイドスペーサ上に形成されており、前記ゲート電極と前記サイドスペーサとを電気的に接続する導電性薄膜とを有することを特徴とするMOSトランジスタである。

【0018】また、第2の発明は、第1の発明において、前記導電性薄膜をチタンジシリサイドから構成したことを特徴とするものである。

【0019】

【発明の実施の形態】以下、本発明の実施の形態につき、好ましい実施例により、図面を参照して説明する。なお、説明の簡便のため、構成要素について、従来例と同一のものには同一の参照符号を付しその説明を省略する。

【0020】<実施例>図1は本発明のMOSトランジスタの実施例を示す断面構成図であリ、図2は本発明のMOSトランジスタの実施例を製造するための第1の概略工程図であリ、図3は本発明のMOSトランジスタの実施例を製造するための第2の概略工程図である。

【0021】図1に示すように、本発明の実施例であるMOSトランジスタ50Aは、半導体基板1上に、トランジスタ素子分離用のフィールド酸化膜2が形成されており、この間にコンタクトホール17a,17bを通して、配線電極19a,19bに接続したソース・ドレイン高濃度領域10a,10bが左右にサイドスペーサ9aを有するゲート電極5を挟んで配置されており、ソース・ドレイン高濃度領域10a,10bを取り囲んで、ソース・ドレイン低濃度領域6a’,6b’が形成されており、ソース・ドレイン領域6a’,6b’の一部はゲート酸化膜3bを介してサイドスペーサ9aの下に配置されている。ここで、サイドスペーサ9aは導電性を示し、同じく導電性を示すチタンシリサイド膜15を介してゲート電極5に接続されている。また、所定の配線電極19a,19bの絶縁用に層間絶縁膜16aが形成されている。ゲート電極5の下部のソース・ドレイン低濃度領域6a,6bに挟まれた基板1の部分はチャネル形成領域30となる。

【0022】以下、本実施例のMOSトランジスタについて、NMOSトランジスタを例に、その製造方法を説明する。まず、図2の(a)に示すように、p型シリコン基板1上に、熱酸化により,厚さ13nmのバッファ酸化膜を形成し、このバッファ酸化膜の上に、厚さ140nmの図示しないシリコン窒化膜を熱CVD法により形成し、このシリコン窒化膜をフォトリソ加工及びエッチング加工により所定パターン形状にしたものをマスクとして、バッファ酸化膜を選択的に熱酸化して、厚さ400nmのフィールド酸化膜2を形成する。その後、シリコン窒化膜とバッファ酸化膜を除去する。次に、熱酸化により、精密に厚さを9nmに制御したゲート酸化膜3と、減圧CVD法により、厚さ200nmのリンドープドポリシリコンからなる導電性薄膜4を順次全面に形成する。

【0023】次に、図2の(b)に示すように、フォトレジストを塗布して、所定パターン形状に露光現像して、図示しないフォトレジストパターンを形成し,これをマスクにして、例えば、塩素系のガスを用いるRIE法による異方性エッチングにより、ゲート電極5のみを残して、導電性薄膜4を除去する。次に、フィールド酸化膜2及びゲート電極をマスクとして、ゲート酸膜を通して、リンを加速電圧50keV、ドーズ量2×1013cm-2でイオン注入・ドライブインして、深さ200nmであるソース・ドレイン低濃度領域6a,6bを形成する。ゲート電極5の下部のソース・ドレイン低濃度領域6a,6bに挟まれた基板1の部分はチャネル形成領域30となる。

【0024】次に、図2の(c)に示すように、熱酸化により厚さ10nmであるシリコン酸化膜7を形成する。酸化膜7は、ゲート電極5の側面及び上面に形成される。

【0025】次に、図2の(d)に示すように、減圧CVD法により、厚さ200nmであるリンドープドポリシリコン膜8を全面に形成する。

【0026】次に、図2の(e)に示すように、例えば塩素系ガスを用いるRIE法による異方性エッチングを行い、ポリシリコン膜8を除去し、ゲート電極5の側面に酸化膜7を介してサイドスペーサ9を形成する。サイドスペーサ9の下部は、ゲート酸化膜を介して、ソース・ドレイン低濃度領域6a,6bに接している。

【0027】次に、図2の(f)に示すように、フィールド酸化膜2、ゲート電極5、ゲート電極5の側面に形成されている酸化膜7及びサイドスペーサ9をマスクとして、ゲート酸化膜3を通して、自己整合的にソース・ドレイン低濃度領域6a,6bの一部に、ヒ素を加速電圧50keV、ドーズ量2×1015cm-2で、イオン注入・ドライブインして深さ100nmであるソース・ドレイン高濃度領域10a,10bを形成する。ここで、ソース・ドレイン低濃度領域6a,6bは、ソース・ドレイン低濃度領域6a’,6b’に縮小し、LDD構造が得られる。

【0028】次に、図3の(g)に示すように、全面に、シランと酸素の混合ガスにP(リン)とB(ボロン)を添加したガスを用いた常圧CVD法により、厚さ500nmのBoron−Phosphorus−Silicate−Glass(単にBPSGともいう)膜からなる層間絶縁膜11を形成し、900℃30分間窒素雰囲気でBPSG膜のフォローを行い、平坦化する。

【0029】次に、図3の(h)に示すように、ケミカル・メカニカル・ポリッシング(単に、CMPともいう)により、例えばエッチング時間の制御により、層間絶縁膜11をエッチングして、ゲート電極5の上部の酸化膜7及びサイドスペーサ9aの上部も除去して、ポリシリコンからなる露出面12を得る。エッチングされて、サイドスペーサ9はサイドスペーサ9aに、層間絶縁膜11は層間絶縁膜11aに、酸化膜7は酸化膜7aとなる。

【0030】次に、図3の(i)に示すように、露出面12の表面に形成される、図示しない自然酸化膜を希フッ酸溶液を用いて除去した後、連続スパッタリング法により、厚さ50nmのTi(Co,Niなどでもよい)からなる高融点金属膜13、及び、Tiの酸化を防止するための厚さ100nmの窒化チタン(TiN)からなる保護膜14を形成する。

【0031】次に、図3の(j)に示すように、高速熱処理装置(ラピッド・サーマル・プロセッサであり、単にRTPともいう)を用いて、600度C程度、窒素雰囲気中で、熱処理する。このとき、高融点金属膜13のTiはゲート電極5及びサイドスペーサ9aのポリシリコンと反応し、チタンシリサイド(TiSi)を形成する。この時、TiがBPSG膜と接する場合には、Tiは未反応のまま残る。続いて、硫酸洗浄により、保護膜14及び未反応のTi(すなわち層間絶縁膜11a上の高融点金属膜の部分)を除去した後、RTPで今度は800℃程度、アルゴン雰囲気で数十秒間熱処理を行うことによって、低抵抗で安定なチタンジシリサイド(TiSi2)膜15がゲート電極5からサイドスペーサ9aにわたって形成される。これにより、ゲート電極5と導電性のサイドスペーサ9がチタンシリサイド膜15を介して電気的に導通がとれるようになる。

【0032】次に、図3の(k)に示すように、CVD法により厚さ500nmのシリコン酸化膜からなる層間絶縁膜16を形成する。層間絶縁膜11aと層間絶縁膜16が合わさって、層間絶縁膜16aが形成される。

【0033】次に、図3の(l)に示すように、ソース・ドレイン高濃度領域10a,10b上の層間絶縁膜16aにフォトリソ加工を施して、コンタクトホール17a,17bを形成後、アルミ膜を形成し、フォトリソ加工により、コンタクトホールを通してソース・ドレイン高濃度領域に接続する所定形状の配線電極19a,19bを形成し、本実施例のMOSトランジスタ50Aを得る。

【0034】このMOSトランジスタ50Aにおいては、ゲート電極5と導電性のサイドスペーサ9aはチタンシリサイド膜15を介して電気的に接続されており、サイドスペーサ9aの下面は、ゲート酸化膜3bを介して、ソース・ドレイン低濃度領域に接しており、上述のGOLD構造を構成している。このように構成したことにより、ソース・ドレイン低濃度領域のイオン注入は、従来のLDD構造と同じく均一な膜厚のゲート酸化膜を介して注入されるため、従来のGOLD構造と比較してウエハ内でのトランジスタ特性のばらつきを小さくすることができる。

【0035】また、実質的にポリサイドゲート構造となるため、ゲート電極の低抵抗化が実現でき、配線による信号の遅延を防止でき、しかも、トランジスタの微細化に対応できる。また、サイドスペーサの材質としてポリシリコンを用いた場合には、サイドスペーサの選択エッチング時にゲート酸化膜がエッチングストッパとして機能するから、活性領域のシリコン基板が露出することがなく、サイドスペーサエッチング時に、汚染等を受けず、特性バラツキの少ないMOSトランジスタ10Aを得ることができる。

【0036】さらに、上述の各製造工程は、きわめて、一般的で制御性の良好なものであり、したがって、MOSトランジスタ10Aを精度よく製造することができる。以上NMOSトランジスタを例に説明したが、PMOSトランジスタに適用できることはいうまでもない。

【0037】

【発明の効果】以上説明したように、本発明のMOSトランジスタは、請求項1及び2によれば、酸化膜を介してソース及びドレイン低濃度領域に接する導電性である2つのサイドスペーサと、ゲート電極及び前記サイドスペーサ上に形成されており、前記ゲート電極と前記サイドスペーサとを電気的に接続する導電性薄膜とを有することにより、再現性の高い工程を用いて低抵抗のゲート電極を有するGOLD構造を構成できるようにし、それにより、微細化が可能であるとともに信頼性の高いMOSトランジスタを提供することができるという効果がある。

【図面の簡単な説明】

【図1】本発明のMOSトランジスタの実施例を示す断面構成図である。

【図2】本発明のMOSトランジスタの実施例を製造するための第1の概略工程図である。

【図3】本発明のMOSトランジスタの実施例を製造するための第2の概略工程図である。

【図4】従来例のMOSトランジスタを示す断面構成図である。

【図5】従来例のMOSトランジスタを製造するための概略工程図である。

【符号の説明】

1…半導体(シリコン)基板、2…フィールド酸化膜、3,3a,3b…ゲート酸化膜、4…導電性薄膜、5,5a…ゲート電極、6a,6a’,6b,6b’…ソース・ドレイン低濃度領域、7…酸化膜、8…ポリシリコン膜、9,9a…サイドスペーサ、10a,10b…ソース・ドレイン高濃度領域、11,11a…層間絶縁膜、12…(ゲート電極部の)ポリシリコン露出面、13…高融点金属膜、14…保護膜(TiN:窒化チタン)、15…チタンジシリサイド(TiSi2)膜、16…層間絶縁膜、17a,17b…コンタクトホール、19a,19b…配線電極、20…(薄い)導電性薄膜、21…絶縁性薄膜、22…サイドスペーサ、23…層間絶縁膜、24a,24b…コンタクトホール、25a,25b…配線電極、30…チャネル形成領域、50A,50B…MOSトランジスタ。

【特許請求の範囲】

【請求項1】半導体基板と、前記半導体基板中に所定間隔離れて形成したソース及びドレイン高濃度領域と、前記ソース及びドレイン高濃度領域の間の前記半導体基板上に酸化膜を介して形成した導電性のゲート電極と、前記ゲート電極の下部の前記半導体基板部分をチャネル形成領域として、前記ソース及びドレイン高濃度領域と前記チャネル形成領域の間に前記ソース及びドレイン高濃度領域を取り囲んでそれぞれ形成したソース及びドレイン低濃度領域とを有するMOSトランジスタにおいて、前記酸化膜を介して前記ソース及びドレイン低濃度領域に接する導電性である2つのサイドスペーサと、前記ゲート電極及び前記サイドスペーサ上に形成されており、前記ゲート電極と前記サイドスペーサとを電気的に接続する導電性薄膜とを有することを特徴とするMOSトランジスタ。

【請求項2】前記導電性薄膜をチタンジシリサイドから構成したことを特徴とする請求項1に記載のMOSトランジスタ。

【請求項1】半導体基板と、前記半導体基板中に所定間隔離れて形成したソース及びドレイン高濃度領域と、前記ソース及びドレイン高濃度領域の間の前記半導体基板上に酸化膜を介して形成した導電性のゲート電極と、前記ゲート電極の下部の前記半導体基板部分をチャネル形成領域として、前記ソース及びドレイン高濃度領域と前記チャネル形成領域の間に前記ソース及びドレイン高濃度領域を取り囲んでそれぞれ形成したソース及びドレイン低濃度領域とを有するMOSトランジスタにおいて、前記酸化膜を介して前記ソース及びドレイン低濃度領域に接する導電性である2つのサイドスペーサと、前記ゲート電極及び前記サイドスペーサ上に形成されており、前記ゲート電極と前記サイドスペーサとを電気的に接続する導電性薄膜とを有することを特徴とするMOSトランジスタ。

【請求項2】前記導電性薄膜をチタンジシリサイドから構成したことを特徴とする請求項1に記載のMOSトランジスタ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2002−222946(P2002−222946A)

【公開日】平成14年8月9日(2002.8.9)

【国際特許分類】

【出願番号】特願2001−19644(P2001−19644)

【出願日】平成13年1月29日(2001.1.29)

【出願人】(000004329)日本ビクター株式会社 (3,896)

【Fターム(参考)】

【公開日】平成14年8月9日(2002.8.9)

【国際特許分類】

【出願日】平成13年1月29日(2001.1.29)

【出願人】(000004329)日本ビクター株式会社 (3,896)

【Fターム(参考)】

[ Back to top ]