NANDフラッシュメモリおよびNANDフラッシュメモリへのデータ書込方法

【課題】ソケットとの接触不良によるインバリッドマークへの意図しない書き込みを防止する。

【解決手段】I/Oライン8−1〜8−Nにスイッチ11−1〜11−Nを介して抵抗(プルアップ抵抗)12−1〜12−Nの一端を接続し、プルアップ抵抗12−1〜12−Nの他端を所定の電源電位Vccに接続する。コントローラ1に、スイッチ11−1〜11−NのON/OFFモードを設定するROM書きモード設定用レジスタ10を設け、ソケットを使用してのメモリアレイ2へのプログラムの書き込み時に、スイッチ11−1〜11−NをONモードとする。

【解決手段】I/Oライン8−1〜8−Nにスイッチ11−1〜11−Nを介して抵抗(プルアップ抵抗)12−1〜12−Nの一端を接続し、プルアップ抵抗12−1〜12−Nの他端を所定の電源電位Vccに接続する。コントローラ1に、スイッチ11−1〜11−NのON/OFFモードを設定するROM書きモード設定用レジスタ10を設け、ソケットを使用してのメモリアレイ2へのプログラムの書き込み時に、スイッチ11−1〜11−NをONモードとする。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、接触不良による誤書き込み防止機能を備えたNANDフラッシュメモリおよびNANDフラッシュメモリへのデータ書込方法に関するものである。

【背景技術】

【0002】

電子機器等のプログラム格納用途において、従来はNORフラッシュメモリを使用する場合が多かった。しかしながら、製品のコスト削減の要求等から、NOR型のフラッシュメモリに代わり、ビット単価の安いNANDフラッシュメモリにプログラムコードを格納する機器が増加している。

【0003】

NANDフラッシュメモリは、NORフラッシュメモリと比較して、内部構造が簡単でビット単価を下げやすいという特徴があるが、その構造ゆえに欠陥のあるブロックをInvalidブロック(インバリッドブロック)とし、このインバリッドブロックを先天的または後天的に一定数内で許容している。そのため、メモリ内の所定の場所に特定パターンをプログラムすることにより、そのブロックがインバリッドブロックであることを示すように規則を決めて使用する必要がある。

【0004】

このインバリッドブロックを示す規則は、NANDフラッシュメモリの品種により異なるが、多くのNANDフラッシュメモリでは、ブロック内の先頭ページのスペアエリアの先頭1ワードに消去状態であるFFFFh以外のデータが書き込まれている場合に、インバリッドブロックと扱うように決められている(例えば、特許文献1,2,3参照)。インバリッドブロックの数量はNANDフラッシュメモリの容量や品種により許容数が規定され、また先頭ブロック(ブロック0)は出荷時にはインバリッドではないことを保証する等、インバリッドブロックの発生箇所が規定されているものも存在する。

【0005】

図8に一般的なNANDフラッシュメモリの構成図を示す。このNANDフラッシュメモリ100は、CPU等のホストデバイス(図示せず)とのインタフェースを担うコントローラ1と、メモリアレイ2と、メモリアレイ2とホストデバイスとの間でデータの入出力を行うバッファ3とから構成される。

【0006】

メモリアレイ2は、基本的な書き込み単位をページ4とし、基本的な消去単位をブロック5として構成される。ブロック5は複数のページ4の集合とされる。ページ4は、通常のデータエリア6とスペアエリア7とで構成され、通常は、データエリア6はプログラムコードなどの情報(プログラムデータ)の格納用途として、スペアエリア7はデータエリア6のデータ管理のための情報(管理データ)の格納用途として使用される。

【0007】

NANDフラッシュメモリ100は仕様上、完全に消去できない、もしくはビットエラーにより書き込みができない、インバリッドブロックが存在、もしくは使用中に発生する可能性がある。装置のソフトウェアではこれを検知し、以降は使用不可とする管理が必要となる。インバリッドブロックの検知方法としては、多くの場合、ブロック5内の先頭ページのスペアエリア7の先頭ワード(インバリッドマーク)が「FFFFh(消去状態)」か否かで判定され、FFFFh以外の場合にはインバリッドブロックと判定される。

【0008】

図9にNANDフラッシュメモリ100のブロック図を示す。同図において、8−1〜8−Nはメモリアレイ2へのデータ入出力用のライン(I/Oライン)、9−1〜9−Mはコントローラ1への制御信号用のラインである。このNANDフラッシュメモリ100では、ブロック5内のインバリッドマークへのデータの書き込み時、I/Oライン8−1〜8−NへのI/O信号を「H」レベルとし、インバリッドマークへ「FFFFh(消去状態)」を書き込むようにする。この際、ブロック5内のインバリッドマークへFFFFh以外のデータが書き込まれれば、そのブロック5をインバリッドブロックと判定する。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2003−022689号公報

【特許文献2】特開2009−087094号公報

【特許文献2】特開平10−261774号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

電子機器等を量産する場合は、フラッシュメモリにプログラムをROMライタで事前に書き込んでから、基板上に搭載する方法が一般的である。ROMライタは、ソケットを介してフラッシュメモリと接触を取るため、ソケットの汚れや老朽化による接触不良を完全に回避することは不可能である。

【0011】

すなわち、ソケットはフラッシュメモリの端子と機械的に接触させることで導通をとるため、例えば埃等の異物や汚れ等により、接触不良が発生する可能性がある。接触不良に関しては、書き込み前から接触不良が発生している場合には、書き込みを行う前に検出することが可能であるが、実際には微小な異物や軽微な汚れや振動等の影響により、書き込み中に接触不良が顕在化することが起こり得る。

【0012】

NOR型のフラッシュメモリの場合には、接触不良が発生した場合は、ソケットとフラッシュメモリの端子を清掃等して接触を取り直した後、消去することで再書き込みが可能となる。しかしながら、NAND型フラッシュメモリの書き込み中に接触不良が発生した場合には、インバリッドマークへ意図しない書き込みが行われる可能性がある。

【0013】

例えば、図9において、I/Oライン8−1〜8−NへのI/O信号を「H」レベルとし、ブロック5内のインバリッドマークへ「FFFFh(消去状態)」を書き込むものとする。この「FFFFh(消去状態)」の書き込み時に、I/Oライン8−1に埃等の異物や汚れ等により接触不良が発生した場合、NANDフラッシュメモリ100から見ると不定な信号となるが、多くの場合にはリーク電流によりI/Oライン8−1のI/O信号が「L」レベルに近づく。このため、ブロック5内のインバリッドマークには、FFFFh以外のデータが書き込まれてしまう。

【0014】

このようなインバリッドマークへの意図しない書き込みにより、本来の使えるはずの領域が使えないというだけではなく、その発生箇所や発生数によっては、NANDフラッシュメモリが不良品と判定されるため、ROMライタで再書き込みができなくなる場合がある。

【0015】

本発明は、このような課題を解決するためになされたもので、その目的とするところは、ソケットとの接触不良によるインバリッドマークへの意図しない書き込みを防止することが可能なNANDフラッシュメモリおよびNANDフラッシュメモリへのデータ書込方法を提供することにある。

【課題を解決するための手段】

【0016】

このような目的を達成するために、本発明に係るNANDフラッシュメモリは、メモリと、このメモリへの第1〜第N(N≧2)のデータ入出力用のラインと、この第1〜第Nのデータ入出力用のラインに第1〜第Nのスイッチング手段を介してその一端が接続されその他端が所定の電源電位に接続された第1〜第Nの抵抗と、第1〜第Nのスイッチング手段を介する第1〜第Nの抵抗と第1〜第Nのデータ入出力用のラインとの間の接続の有効/無効を設定する設定手段とを設けたことを特徴とする。

【0017】

この発明において、第1〜第Nのデータ入出力用のラインには、第1〜第Nのスイッチング手段を介して第1〜第Nの抵抗の一端が接続され、第1〜第Nの抵抗の他端は所定の電源電位に接続される。ここで、第1〜第Nのスイッチング手段を介する第1〜第Nの抵抗と第1〜第Nのデータ入出力用のラインとの間の接続の有効/無効は、設定手段によって設定される。例えば、本発明では、ソケットを使用するために接触不良の発生を完全に避けることができないような場合、第1〜第Nの抵抗と第1〜第Nのデータ入出力用のラインとの間の接続を有効とする。

【0018】

第1〜第Nの抵抗と第1〜第Nのデータ入出力用のラインとの間の接続を有効とすると、埃等の異物や汚れ等によりデータ入出力用のラインに接触不良が発生しても、そのデータ入出力用のラインの電位が抵抗を介してプルアップされるので、そのデータ入出力用のラインに加えられる「H」レベルの信号が「L」レベルに変化してしまうことがない。これにより、第1〜第Nのデータ入出力用のラインへの信号を「H」レベルとした場合、第1〜第Nのデータ入出力用のライン上の信号を必ず「H」レベルとしてメモリに書き込むことができ、ソケットとの接触不良によるインバリッドマークへの意図しない書き込みを防止することが可能となる。

【発明の効果】

【0019】

本発明によれば、第1〜第Nのデータ入出力用のラインに第1〜第Nのスイッチング手段を介して第1〜第Nの抵抗の一端を接続し、この第1〜第Nの抵抗の他端を所定の電源電位に接続し、第1〜第Nのスイッチング手段を介する第1〜第Nの抵抗と第1〜第Nのデータ入出力用のラインとの間の接続の有効/無効を設定できるようにしたので、例えば、ソケットを使用するために接触不良の発生を完全に避けることができないような場合、第1〜第Nの抵抗と第1〜第Nのデータ入出力用のラインとの間の接続を有効とすることにより、ソケットとの接触不良によるインバリッドマークへの意図しない書き込みを防止することが可能となる。

【図面の簡単な説明】

【0020】

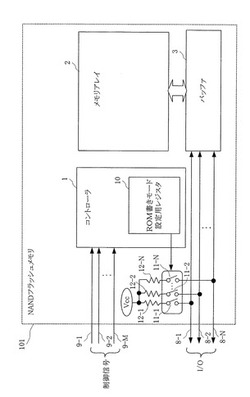

【図1】本発明に係るNANDフラッシュメモリの一実施例をソケットにセットしてホストデバイス(ROMライタ)からプログラムの書き込みを行うようにした場合の概略を示す図である。

【図2】本発明に係るNANDフラッシュメモリの一実施例のブロック図である。

【図3】このNANDフラッシュメモリにおいてインバリッドマークへの書き込みを行う直前にI/Oラインに接触不良が発生した場合のデータの書き込み動作を説明するためのタイムチャートである。

【図4】通常モード設定時(ROM書きモード解除時)に接触不良が発生した場合の図3に対応するタイムチャートである。

【図5】ROM書きモードの設定を外部端子の入力レベルによって行うようにした例を示す図である。

【図6】制御信号用のラインへプルアップ抵抗/プルダウン抵抗を追加した例を示す図である。

【図7】図6に示したNANDフラッシュメモリにおいてROM書きモードの設定を外部端子の入力レベルによって行うようにした例を示す図である。

【図8】一般的なNANDフラッシュメモリの構成図である。

【図9】一般的なNANDフラッシュメモリのブロック図である。

【発明を実施するための形態】

【0021】

以下、本発明を実施例に基づき詳細に説明する。図1はこの発明に係るNANDフラッシュメモリの一実施例をソケットにセットしてホストデバイス(ROMライタ)からプログラムの書き込みを行うようにした場合の概略を示す図である。同図において、図8と同一符号は図8を参照して説明した構成要素と同一或いは同等構成要素を示し、その説明は省略する。

【0022】

図1において、本実施例のNANDフラッシュメモリには符号101を付し、従来のNANDフラッシュメモリ100と区別しているが、コントローラ1とメモリアレイ2とバッファ3とをその主要な構成要素とし、メモリアレイ2においてページ4がデータエリア6とスペアエリア7とを備えている点では同じである。このNANDフラッシュメモリ101をソケット200にセットし、ホストデバイス(ROMライタ)300からプログラムの書き込みを行う。

【0023】

図2にNANDフラッシュメモリ101のブロック図を示す。このNANDフラッシュメモリ101においては、I/Oライン8−1〜8−Nにスイッチ11−1〜11−Nを介して抵抗(プルアップ抵抗)12−1〜12−Nの一端を接続し、プルアップ抵抗12−1〜12−Nの他端を所定の電源電位Vccに接続している。

【0024】

また、コントローラ1に、スイッチ11−1〜11−NのON/OFFモードを設定するROM書きモード設定用レジスタ10を設けている。ROM書きモード設定用レジスタ10は、ソケット200を使用してのメモリアレイ2へのプログラムの書き込み時、このプログラムの書き込みを行うホストデバイス300からの指令を受けて、スイッチ11−1〜11−NをONモード(ROM書きモード)に設定する。すなわち、スイッチ11−1〜11−NをONとして、プルアップ抵抗12−1〜12−NとI/Oライン8−1〜8−Nとの間の接続を有効とする。なお、この場合のホストデバイス300からの指令は、コントローラ1への制御信号として与えられる。

【0025】

このNANDフラッシュメモリ101において、メモリアレイ2が本発明でいうメモリに相当し、I/Oライン8−1〜8−Nが第1〜第Nのデータ入出力用のラインに相当し、スイッチ11−1〜11−Nが第1〜第Nのスイッチング手段に相当し、抵抗12−1〜12−Nが第1〜第Nの抵抗に相当し、ROM書きモード設定用レジスタ10が設定手段に相当する。

【0026】

〔ROM書きモード設定時〕

ホストデバイス300は、ソケット200を使用してのNANDフラッシュメモリ101のメモリアレイ2へのプログラムの書き込みに際し、コントローラ1に設けられているROM書きモード設定用レジスタ10へ指令を送り、スイッチ11−1〜11−NをONモード(ROM書きモード)に設定する。これにより、スイッチ11−1〜11−NがONとされ、プルアップ抵抗12−1〜12−NとI/Oライン8−1〜8−Nとの間の接続が有効とされる。

【0027】

〔接触不良が発生していない場合〕

そして、ホストデバイス300は、I/Oライン8−1〜8−NへのI/O信号を「H」/「L」レベルに変化させ、メモリアレイ2のデータエリア6にプログラムコードを書き込んで行く。このプログラムの書き込み中、ホストデバイス300は、I/Oライン8−1〜8−NへのI/O信号を全て「H」レベルとし、ブロック5内の先頭ページのスペアエリア7の先頭ワード(インバリッドマーク)へ「FFFFh(消去状態)」を書き込む。

【0028】

〔接触不良が発生した場合〕

図3にインバリッドマークへの書き込みを行う直前のt2時点でI/Oライン8−1に接触不良が発生した場合のタイムチャートを示す。なお、この例では、NANDフラッシュメモリ101として、16bit品を想定している。

【0029】

図3において、I/O(0)〜I/O(15)はI/Oライン8−1〜8−N(N=16)上のI/O信号を示し、WRBは書き込み信号を示す。書き込み信号WRBは、ホストデバイス300からのコントローラ1への制御信号として与えられ、書き込み信号WRBの立ち上がりタイミングで、I/Oライン8−1〜8−N上のI/O信号がラッチされる。

【0030】

Dataはラッチされたデータを表し、一時的にバッファ3に取り込まれた後、メモリアレイ2に格納される。Addrees(n−1),Addrees(n),Addrees(n+1),Addrees(n+2)は、メモリアレイ2におけるアドレスを示す。Addrees(n−1)までがブロック5内のデータエリア6とし、Addrees(n)以降がブロック5内の先頭ページのスペアエリア7の先頭ワードとする。

【0031】

図3において、書き込み信号WRBはt1,t3,t4,t5点で立ち上がっており、この書き込み信号WRBの立ち上がりタイミングt1,t3,t4,t5でI/Oライン8−1〜8−N上のI/O信号がラッチされる。この例では、t1,t3,t4,t5点において、ホストデバイス300からのI/Oライン8−1〜8−NへのI/O信号は全て「H」レベルとされているものとする。また、t2点において、埃等の異物や汚れ等により、I/Oライン8−1に接触不良が発生したものとする。

【0032】

この場合、t1点では、I/Oライン8−1には接触不良が発生しておらず、I/Oライン8−1〜8−N上のI/O信号は全て「H」レベルとされている。したがって、書き込み信号WRBの立ち上がりタイミングt1でI/Oライン8−1〜8−N上のI/O信号がラッチされた場合、そのラッチされたデータは「FFFFh(消去状態)」となり、メモリアレイ2におけるAddrees(n−1)には「FFFFh」がデータとして書き込まれる。

【0033】

t2点で、I/Oライン8−1に接触不良が発生すると、I/Oライン8−1がプルアップ抵抗12−1を介して所定の電源電位Vccに接続されているので、このプルアップ抵抗12−1を介してI/Oライン8−1の電位が「H」レベルを保つ。したがって、書き込み信号WRBの立ち上がりタイミングt3でI/Oライン8−1〜8−N上のI/O信号がラッチされた場合、そのラッチされたデータは「FFFFh(消去状態)」となり、メモリアレイ2におけるAddrees(n)には「FFFFh」がデータとして書き込まれる。

【0034】

同様にして、書き込み信号WRBの立ち上がりタイミングt4,t5でI/Oライン8−1〜8−N上のI/O信号がラッチされた場合、そのラッチされたデータは何れも「FFFFh(消去状態)」となり、メモリアレイ2におけるAddrees(n+1),Addrees(n+2)には「FFFFh」がデータとして書き込まれる。したがって、このブロックは、インバリッドブロックと判定されることはない。

【0035】

上述では、t2点でI/Oライン8−1に接触不良が発生したものとしたが、他のI/Oラインにおいて接触不良が発生した場合でも同様である。このようにして、本実施例では、埃等の異物や汚れ等によりI/Oライン8−1〜8−Nに接触不良が発生しても、I/Oライン8−1〜8−Nに加えられる「H」レベルの信号が「L」レベルに変化してしまうことがなく、ソケット200との接触不良によるインバリッドマークへの意図しない書き込みが防止されるものとなる。なお、接触不良時に本来「L」レベルである信号を「H」レベルとして書き込んでしまう可能性はあるが、この場合は未書き込みであることと同義であり、再書き込み時に影響を与えない。

【0036】

〔通常モード設定時(ROM書きモード解除時)〕

図4は通常モード設定時(ROM書きモード解除時)に接触不良が発生した場合の図3に対応するタイムチャートである。通常、ROM書きモード設定用レジスタ10は、スイッチ11−1〜11−NをOFFモードとする。この場合、スイッチ11−1〜11−NはOFFとされ、プルアップ抵抗12−1〜12−NとI/Oライン8−1〜8−Nとの間の接続は無効とされる。

【0037】

図4において、t1点では、I/Oライン8−1には接触不良は発生しておらず、I/Oライン8−1〜8−N上のI/O信号は全て「H」レベルとされている。したがって、書き込み信号WRBの立ち上がりタイミングt1でI/Oライン8−1〜8−N上のI/O信号がラッチされた場合、そのラッチされたデータは「FFFFh(消去状態)」となり、メモリアレイ2におけるAddrees(n−1)には「FFFFh」がデータとして書き込まれる。

【0038】

t2点で、I/Oライン8−1に接触不良が発生すると、I/Oライン8−1はプルアップ抵抗12−1を介して所定の電源電位Vccに接続されていないので、リーク電流により「L」レベルに近づく。したがって、書き込み信号WRBの立ち上がりタイミングt3でI/Oライン8−1〜8−N上のI/O信号がラッチされた場合、そのラッチされたデータは「FFFFh(消去状態)」とならず、メモリアレイ2におけるAddrees(n)には「FFFFh」以外のデータが書き込まれる。

【0039】

同様にして、書き込み信号WRBの立ち上がりタイミングt4,t5でI/Oライン8−1〜8−N上のI/O信号がラッチされた場合、そのラッチされたデータは何れも「FFFFh(消去状態)」とならず、メモリアレイ2におけるAddrees(n+1),Addrees(n+2)には「FFFFh」以外のデータが書き込まれる。したがって、このブロックはインバリッドブロックと判定されることになる。

【0040】

通常モード設定時(ROM書きモード解除時)は、接触不良に有効なプルアップ抵抗12−1〜12−NをI/Oライン8−1〜8−Nへ接続しないため、ROM書きモード時のような消費電流の増加はなく、伝送信号への影響もない。

【0041】

〔ROM書きモードの設定を外部端子の入力レベルにより行う方法〕

なお、上述した実施例では、ホストデバイス300よりROM書きモード設定用レジスタ10へ指令を送ってROM書きモードへの設定を行うようにしたが、図5に示すように、外部入力端子の1つとしてモード判定用端子13を設け、このモード判定用端子13への入力レベルに応じてスイッチ11−1〜11−NのON/OFFモードの設定を行うようにしてもよい。

【0042】

〔NANDフラッシュメモリのプログラムコマンドに追加する方法〕

また、既存の書き込みのコマンド(Page Program等)に加え、ROM書きモードでのプログラムコマンドを追加するようにしてもよい。このコマンドを使用して書き込む場合は、プログラムサイクルの間はROM書きモードと同じ動作を継続するようにする。

【0043】

〔制御信号用のラインへのプルアップ抵抗/プルダウン抵抗の追加〕

また、上述した実施例では、I/Oライン8−1〜8−Nにスイッチ11−1〜11−Nを介してプルアップ抵抗12−1〜12−Nの一端を接続し、プルアップ抵抗12−1〜12−Nの他端を所定の電源電位Vccに接続するようにしたが、これと同様の構成を制御信号用のライン9−1〜9−Mに追加するようにしてもよい。

【0044】

例えば、図6に示すように、制御信号用のライン9−1,9−2にスイッチ14−1,14−2を介して抵抗(プルアップ抵抗)15−1,15−2の一端を接続し、制御信号用のライン9−Mにスイッチ14−Mを介して抵抗(プルダウン抵抗)15−Mの一端を接続し、プルアップ抵抗15−1,15−2の他端を所定の電源電位Vccに接続し、プルダウン抵抗15−Mの他端を接地電位GNDに接続するようにし、スイッチ14−1〜14−MのON/OFFモードをスイッチ11−1〜11−Nと同様にしてROM書きモード設定用レジスタ10によって設定するようにする。

【0045】

このようにすることによって、制御信号用のライン9−1〜9−Mに接触不良が生じた場合、想定しないプログラムが行われる可能性を排除することが可能となる。例えば、制御信号用のライン9−1を書き込み信号WRBのラインとした場合、制御信号用のライン9−1に接触不良が生じると、書き込み信号WRBが「H」レベルを保ち、データの書き込みそのものが行われないようになる。なお、制御信号用のライン9−1〜9−Mの何れのラインを電源電位Vccに接続するか、接地電位GNDに接続するかは、その制御信号用のライン9−1〜9−Mへの制御信号の種類によって適切に定めるものとする。

【0046】

図6に示したNANDフラッシュメモリ101において、メモリアレイ2が本発明でいうメモリに相当し、I/Oライン8−1〜8−Nが第1〜第Nのデータ入出力用のラインに相当し、制御信号用のライン9−1〜9−Mが第1〜第Mの制御信号用のラインに相当し、スイッチ11−1〜11−Nが第1〜第Nのスイッチング手段に相当し、スイッチ14−1〜14−Mが第1〜第Mのスイッチング手段に相当し、抵抗12−1〜12−Nが第1〜第Nの抵抗に相当し、抵抗15−1〜15−Mが第1〜第Mの抵抗に相当し、ROM書きモード設定用レジスタ10が設定手段に相当する。

【0047】

図6に示したNANDフラッシュメモリ101においても、図7に示すように、外部外部入力端子の1つとしてモード判定用端子13を設け、このモード判定用端子13への入力レベルに応じてスイッチ11−1〜11−Nおよびスイッチ15−1〜15−MのON/OFFモードの設定を行うようにしてもよい。

【産業上の利用可能性】

【0048】

本発明のNANDフラッシュメモリおよびNANDフラッシュメモリへのデータ書込方法は、接触不良による誤書き込み防止機能を備えたNANDフラッシュメモリおよびNANDフラッシュメモリへのデータ書込方法として、様々な分野で利用することが可能である。

【符号の説明】

【0049】

1…コントローラ、2…メモリアレイ、3…バッファ、4…ページ、5…ブロック、6…データエリア、7…スペアエリア、8−1〜8−N…データ入出力用のライン(I/Oライン)、9−1〜9−M…制御信号用のライン、10…ROM書きモード設定用レジスタ、11−1〜11−N…スイッチ(第1〜第Nのスイッチ)、12−1〜12−N…抵抗(第1〜第Nの抵抗)、13…モード判定用端子、14−1〜14−M…スイッチ(第1〜第Mのスイッチ)、15−1〜15−M…抵抗(第1〜第Mの抵抗)、101…NANDフラッシュメモリ、200…ソケット、300…ホストデバイス(ROMライタ)。

【技術分野】

【0001】

この発明は、接触不良による誤書き込み防止機能を備えたNANDフラッシュメモリおよびNANDフラッシュメモリへのデータ書込方法に関するものである。

【背景技術】

【0002】

電子機器等のプログラム格納用途において、従来はNORフラッシュメモリを使用する場合が多かった。しかしながら、製品のコスト削減の要求等から、NOR型のフラッシュメモリに代わり、ビット単価の安いNANDフラッシュメモリにプログラムコードを格納する機器が増加している。

【0003】

NANDフラッシュメモリは、NORフラッシュメモリと比較して、内部構造が簡単でビット単価を下げやすいという特徴があるが、その構造ゆえに欠陥のあるブロックをInvalidブロック(インバリッドブロック)とし、このインバリッドブロックを先天的または後天的に一定数内で許容している。そのため、メモリ内の所定の場所に特定パターンをプログラムすることにより、そのブロックがインバリッドブロックであることを示すように規則を決めて使用する必要がある。

【0004】

このインバリッドブロックを示す規則は、NANDフラッシュメモリの品種により異なるが、多くのNANDフラッシュメモリでは、ブロック内の先頭ページのスペアエリアの先頭1ワードに消去状態であるFFFFh以外のデータが書き込まれている場合に、インバリッドブロックと扱うように決められている(例えば、特許文献1,2,3参照)。インバリッドブロックの数量はNANDフラッシュメモリの容量や品種により許容数が規定され、また先頭ブロック(ブロック0)は出荷時にはインバリッドではないことを保証する等、インバリッドブロックの発生箇所が規定されているものも存在する。

【0005】

図8に一般的なNANDフラッシュメモリの構成図を示す。このNANDフラッシュメモリ100は、CPU等のホストデバイス(図示せず)とのインタフェースを担うコントローラ1と、メモリアレイ2と、メモリアレイ2とホストデバイスとの間でデータの入出力を行うバッファ3とから構成される。

【0006】

メモリアレイ2は、基本的な書き込み単位をページ4とし、基本的な消去単位をブロック5として構成される。ブロック5は複数のページ4の集合とされる。ページ4は、通常のデータエリア6とスペアエリア7とで構成され、通常は、データエリア6はプログラムコードなどの情報(プログラムデータ)の格納用途として、スペアエリア7はデータエリア6のデータ管理のための情報(管理データ)の格納用途として使用される。

【0007】

NANDフラッシュメモリ100は仕様上、完全に消去できない、もしくはビットエラーにより書き込みができない、インバリッドブロックが存在、もしくは使用中に発生する可能性がある。装置のソフトウェアではこれを検知し、以降は使用不可とする管理が必要となる。インバリッドブロックの検知方法としては、多くの場合、ブロック5内の先頭ページのスペアエリア7の先頭ワード(インバリッドマーク)が「FFFFh(消去状態)」か否かで判定され、FFFFh以外の場合にはインバリッドブロックと判定される。

【0008】

図9にNANDフラッシュメモリ100のブロック図を示す。同図において、8−1〜8−Nはメモリアレイ2へのデータ入出力用のライン(I/Oライン)、9−1〜9−Mはコントローラ1への制御信号用のラインである。このNANDフラッシュメモリ100では、ブロック5内のインバリッドマークへのデータの書き込み時、I/Oライン8−1〜8−NへのI/O信号を「H」レベルとし、インバリッドマークへ「FFFFh(消去状態)」を書き込むようにする。この際、ブロック5内のインバリッドマークへFFFFh以外のデータが書き込まれれば、そのブロック5をインバリッドブロックと判定する。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2003−022689号公報

【特許文献2】特開2009−087094号公報

【特許文献2】特開平10−261774号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

電子機器等を量産する場合は、フラッシュメモリにプログラムをROMライタで事前に書き込んでから、基板上に搭載する方法が一般的である。ROMライタは、ソケットを介してフラッシュメモリと接触を取るため、ソケットの汚れや老朽化による接触不良を完全に回避することは不可能である。

【0011】

すなわち、ソケットはフラッシュメモリの端子と機械的に接触させることで導通をとるため、例えば埃等の異物や汚れ等により、接触不良が発生する可能性がある。接触不良に関しては、書き込み前から接触不良が発生している場合には、書き込みを行う前に検出することが可能であるが、実際には微小な異物や軽微な汚れや振動等の影響により、書き込み中に接触不良が顕在化することが起こり得る。

【0012】

NOR型のフラッシュメモリの場合には、接触不良が発生した場合は、ソケットとフラッシュメモリの端子を清掃等して接触を取り直した後、消去することで再書き込みが可能となる。しかしながら、NAND型フラッシュメモリの書き込み中に接触不良が発生した場合には、インバリッドマークへ意図しない書き込みが行われる可能性がある。

【0013】

例えば、図9において、I/Oライン8−1〜8−NへのI/O信号を「H」レベルとし、ブロック5内のインバリッドマークへ「FFFFh(消去状態)」を書き込むものとする。この「FFFFh(消去状態)」の書き込み時に、I/Oライン8−1に埃等の異物や汚れ等により接触不良が発生した場合、NANDフラッシュメモリ100から見ると不定な信号となるが、多くの場合にはリーク電流によりI/Oライン8−1のI/O信号が「L」レベルに近づく。このため、ブロック5内のインバリッドマークには、FFFFh以外のデータが書き込まれてしまう。

【0014】

このようなインバリッドマークへの意図しない書き込みにより、本来の使えるはずの領域が使えないというだけではなく、その発生箇所や発生数によっては、NANDフラッシュメモリが不良品と判定されるため、ROMライタで再書き込みができなくなる場合がある。

【0015】

本発明は、このような課題を解決するためになされたもので、その目的とするところは、ソケットとの接触不良によるインバリッドマークへの意図しない書き込みを防止することが可能なNANDフラッシュメモリおよびNANDフラッシュメモリへのデータ書込方法を提供することにある。

【課題を解決するための手段】

【0016】

このような目的を達成するために、本発明に係るNANDフラッシュメモリは、メモリと、このメモリへの第1〜第N(N≧2)のデータ入出力用のラインと、この第1〜第Nのデータ入出力用のラインに第1〜第Nのスイッチング手段を介してその一端が接続されその他端が所定の電源電位に接続された第1〜第Nの抵抗と、第1〜第Nのスイッチング手段を介する第1〜第Nの抵抗と第1〜第Nのデータ入出力用のラインとの間の接続の有効/無効を設定する設定手段とを設けたことを特徴とする。

【0017】

この発明において、第1〜第Nのデータ入出力用のラインには、第1〜第Nのスイッチング手段を介して第1〜第Nの抵抗の一端が接続され、第1〜第Nの抵抗の他端は所定の電源電位に接続される。ここで、第1〜第Nのスイッチング手段を介する第1〜第Nの抵抗と第1〜第Nのデータ入出力用のラインとの間の接続の有効/無効は、設定手段によって設定される。例えば、本発明では、ソケットを使用するために接触不良の発生を完全に避けることができないような場合、第1〜第Nの抵抗と第1〜第Nのデータ入出力用のラインとの間の接続を有効とする。

【0018】

第1〜第Nの抵抗と第1〜第Nのデータ入出力用のラインとの間の接続を有効とすると、埃等の異物や汚れ等によりデータ入出力用のラインに接触不良が発生しても、そのデータ入出力用のラインの電位が抵抗を介してプルアップされるので、そのデータ入出力用のラインに加えられる「H」レベルの信号が「L」レベルに変化してしまうことがない。これにより、第1〜第Nのデータ入出力用のラインへの信号を「H」レベルとした場合、第1〜第Nのデータ入出力用のライン上の信号を必ず「H」レベルとしてメモリに書き込むことができ、ソケットとの接触不良によるインバリッドマークへの意図しない書き込みを防止することが可能となる。

【発明の効果】

【0019】

本発明によれば、第1〜第Nのデータ入出力用のラインに第1〜第Nのスイッチング手段を介して第1〜第Nの抵抗の一端を接続し、この第1〜第Nの抵抗の他端を所定の電源電位に接続し、第1〜第Nのスイッチング手段を介する第1〜第Nの抵抗と第1〜第Nのデータ入出力用のラインとの間の接続の有効/無効を設定できるようにしたので、例えば、ソケットを使用するために接触不良の発生を完全に避けることができないような場合、第1〜第Nの抵抗と第1〜第Nのデータ入出力用のラインとの間の接続を有効とすることにより、ソケットとの接触不良によるインバリッドマークへの意図しない書き込みを防止することが可能となる。

【図面の簡単な説明】

【0020】

【図1】本発明に係るNANDフラッシュメモリの一実施例をソケットにセットしてホストデバイス(ROMライタ)からプログラムの書き込みを行うようにした場合の概略を示す図である。

【図2】本発明に係るNANDフラッシュメモリの一実施例のブロック図である。

【図3】このNANDフラッシュメモリにおいてインバリッドマークへの書き込みを行う直前にI/Oラインに接触不良が発生した場合のデータの書き込み動作を説明するためのタイムチャートである。

【図4】通常モード設定時(ROM書きモード解除時)に接触不良が発生した場合の図3に対応するタイムチャートである。

【図5】ROM書きモードの設定を外部端子の入力レベルによって行うようにした例を示す図である。

【図6】制御信号用のラインへプルアップ抵抗/プルダウン抵抗を追加した例を示す図である。

【図7】図6に示したNANDフラッシュメモリにおいてROM書きモードの設定を外部端子の入力レベルによって行うようにした例を示す図である。

【図8】一般的なNANDフラッシュメモリの構成図である。

【図9】一般的なNANDフラッシュメモリのブロック図である。

【発明を実施するための形態】

【0021】

以下、本発明を実施例に基づき詳細に説明する。図1はこの発明に係るNANDフラッシュメモリの一実施例をソケットにセットしてホストデバイス(ROMライタ)からプログラムの書き込みを行うようにした場合の概略を示す図である。同図において、図8と同一符号は図8を参照して説明した構成要素と同一或いは同等構成要素を示し、その説明は省略する。

【0022】

図1において、本実施例のNANDフラッシュメモリには符号101を付し、従来のNANDフラッシュメモリ100と区別しているが、コントローラ1とメモリアレイ2とバッファ3とをその主要な構成要素とし、メモリアレイ2においてページ4がデータエリア6とスペアエリア7とを備えている点では同じである。このNANDフラッシュメモリ101をソケット200にセットし、ホストデバイス(ROMライタ)300からプログラムの書き込みを行う。

【0023】

図2にNANDフラッシュメモリ101のブロック図を示す。このNANDフラッシュメモリ101においては、I/Oライン8−1〜8−Nにスイッチ11−1〜11−Nを介して抵抗(プルアップ抵抗)12−1〜12−Nの一端を接続し、プルアップ抵抗12−1〜12−Nの他端を所定の電源電位Vccに接続している。

【0024】

また、コントローラ1に、スイッチ11−1〜11−NのON/OFFモードを設定するROM書きモード設定用レジスタ10を設けている。ROM書きモード設定用レジスタ10は、ソケット200を使用してのメモリアレイ2へのプログラムの書き込み時、このプログラムの書き込みを行うホストデバイス300からの指令を受けて、スイッチ11−1〜11−NをONモード(ROM書きモード)に設定する。すなわち、スイッチ11−1〜11−NをONとして、プルアップ抵抗12−1〜12−NとI/Oライン8−1〜8−Nとの間の接続を有効とする。なお、この場合のホストデバイス300からの指令は、コントローラ1への制御信号として与えられる。

【0025】

このNANDフラッシュメモリ101において、メモリアレイ2が本発明でいうメモリに相当し、I/Oライン8−1〜8−Nが第1〜第Nのデータ入出力用のラインに相当し、スイッチ11−1〜11−Nが第1〜第Nのスイッチング手段に相当し、抵抗12−1〜12−Nが第1〜第Nの抵抗に相当し、ROM書きモード設定用レジスタ10が設定手段に相当する。

【0026】

〔ROM書きモード設定時〕

ホストデバイス300は、ソケット200を使用してのNANDフラッシュメモリ101のメモリアレイ2へのプログラムの書き込みに際し、コントローラ1に設けられているROM書きモード設定用レジスタ10へ指令を送り、スイッチ11−1〜11−NをONモード(ROM書きモード)に設定する。これにより、スイッチ11−1〜11−NがONとされ、プルアップ抵抗12−1〜12−NとI/Oライン8−1〜8−Nとの間の接続が有効とされる。

【0027】

〔接触不良が発生していない場合〕

そして、ホストデバイス300は、I/Oライン8−1〜8−NへのI/O信号を「H」/「L」レベルに変化させ、メモリアレイ2のデータエリア6にプログラムコードを書き込んで行く。このプログラムの書き込み中、ホストデバイス300は、I/Oライン8−1〜8−NへのI/O信号を全て「H」レベルとし、ブロック5内の先頭ページのスペアエリア7の先頭ワード(インバリッドマーク)へ「FFFFh(消去状態)」を書き込む。

【0028】

〔接触不良が発生した場合〕

図3にインバリッドマークへの書き込みを行う直前のt2時点でI/Oライン8−1に接触不良が発生した場合のタイムチャートを示す。なお、この例では、NANDフラッシュメモリ101として、16bit品を想定している。

【0029】

図3において、I/O(0)〜I/O(15)はI/Oライン8−1〜8−N(N=16)上のI/O信号を示し、WRBは書き込み信号を示す。書き込み信号WRBは、ホストデバイス300からのコントローラ1への制御信号として与えられ、書き込み信号WRBの立ち上がりタイミングで、I/Oライン8−1〜8−N上のI/O信号がラッチされる。

【0030】

Dataはラッチされたデータを表し、一時的にバッファ3に取り込まれた後、メモリアレイ2に格納される。Addrees(n−1),Addrees(n),Addrees(n+1),Addrees(n+2)は、メモリアレイ2におけるアドレスを示す。Addrees(n−1)までがブロック5内のデータエリア6とし、Addrees(n)以降がブロック5内の先頭ページのスペアエリア7の先頭ワードとする。

【0031】

図3において、書き込み信号WRBはt1,t3,t4,t5点で立ち上がっており、この書き込み信号WRBの立ち上がりタイミングt1,t3,t4,t5でI/Oライン8−1〜8−N上のI/O信号がラッチされる。この例では、t1,t3,t4,t5点において、ホストデバイス300からのI/Oライン8−1〜8−NへのI/O信号は全て「H」レベルとされているものとする。また、t2点において、埃等の異物や汚れ等により、I/Oライン8−1に接触不良が発生したものとする。

【0032】

この場合、t1点では、I/Oライン8−1には接触不良が発生しておらず、I/Oライン8−1〜8−N上のI/O信号は全て「H」レベルとされている。したがって、書き込み信号WRBの立ち上がりタイミングt1でI/Oライン8−1〜8−N上のI/O信号がラッチされた場合、そのラッチされたデータは「FFFFh(消去状態)」となり、メモリアレイ2におけるAddrees(n−1)には「FFFFh」がデータとして書き込まれる。

【0033】

t2点で、I/Oライン8−1に接触不良が発生すると、I/Oライン8−1がプルアップ抵抗12−1を介して所定の電源電位Vccに接続されているので、このプルアップ抵抗12−1を介してI/Oライン8−1の電位が「H」レベルを保つ。したがって、書き込み信号WRBの立ち上がりタイミングt3でI/Oライン8−1〜8−N上のI/O信号がラッチされた場合、そのラッチされたデータは「FFFFh(消去状態)」となり、メモリアレイ2におけるAddrees(n)には「FFFFh」がデータとして書き込まれる。

【0034】

同様にして、書き込み信号WRBの立ち上がりタイミングt4,t5でI/Oライン8−1〜8−N上のI/O信号がラッチされた場合、そのラッチされたデータは何れも「FFFFh(消去状態)」となり、メモリアレイ2におけるAddrees(n+1),Addrees(n+2)には「FFFFh」がデータとして書き込まれる。したがって、このブロックは、インバリッドブロックと判定されることはない。

【0035】

上述では、t2点でI/Oライン8−1に接触不良が発生したものとしたが、他のI/Oラインにおいて接触不良が発生した場合でも同様である。このようにして、本実施例では、埃等の異物や汚れ等によりI/Oライン8−1〜8−Nに接触不良が発生しても、I/Oライン8−1〜8−Nに加えられる「H」レベルの信号が「L」レベルに変化してしまうことがなく、ソケット200との接触不良によるインバリッドマークへの意図しない書き込みが防止されるものとなる。なお、接触不良時に本来「L」レベルである信号を「H」レベルとして書き込んでしまう可能性はあるが、この場合は未書き込みであることと同義であり、再書き込み時に影響を与えない。

【0036】

〔通常モード設定時(ROM書きモード解除時)〕

図4は通常モード設定時(ROM書きモード解除時)に接触不良が発生した場合の図3に対応するタイムチャートである。通常、ROM書きモード設定用レジスタ10は、スイッチ11−1〜11−NをOFFモードとする。この場合、スイッチ11−1〜11−NはOFFとされ、プルアップ抵抗12−1〜12−NとI/Oライン8−1〜8−Nとの間の接続は無効とされる。

【0037】

図4において、t1点では、I/Oライン8−1には接触不良は発生しておらず、I/Oライン8−1〜8−N上のI/O信号は全て「H」レベルとされている。したがって、書き込み信号WRBの立ち上がりタイミングt1でI/Oライン8−1〜8−N上のI/O信号がラッチされた場合、そのラッチされたデータは「FFFFh(消去状態)」となり、メモリアレイ2におけるAddrees(n−1)には「FFFFh」がデータとして書き込まれる。

【0038】

t2点で、I/Oライン8−1に接触不良が発生すると、I/Oライン8−1はプルアップ抵抗12−1を介して所定の電源電位Vccに接続されていないので、リーク電流により「L」レベルに近づく。したがって、書き込み信号WRBの立ち上がりタイミングt3でI/Oライン8−1〜8−N上のI/O信号がラッチされた場合、そのラッチされたデータは「FFFFh(消去状態)」とならず、メモリアレイ2におけるAddrees(n)には「FFFFh」以外のデータが書き込まれる。

【0039】

同様にして、書き込み信号WRBの立ち上がりタイミングt4,t5でI/Oライン8−1〜8−N上のI/O信号がラッチされた場合、そのラッチされたデータは何れも「FFFFh(消去状態)」とならず、メモリアレイ2におけるAddrees(n+1),Addrees(n+2)には「FFFFh」以外のデータが書き込まれる。したがって、このブロックはインバリッドブロックと判定されることになる。

【0040】

通常モード設定時(ROM書きモード解除時)は、接触不良に有効なプルアップ抵抗12−1〜12−NをI/Oライン8−1〜8−Nへ接続しないため、ROM書きモード時のような消費電流の増加はなく、伝送信号への影響もない。

【0041】

〔ROM書きモードの設定を外部端子の入力レベルにより行う方法〕

なお、上述した実施例では、ホストデバイス300よりROM書きモード設定用レジスタ10へ指令を送ってROM書きモードへの設定を行うようにしたが、図5に示すように、外部入力端子の1つとしてモード判定用端子13を設け、このモード判定用端子13への入力レベルに応じてスイッチ11−1〜11−NのON/OFFモードの設定を行うようにしてもよい。

【0042】

〔NANDフラッシュメモリのプログラムコマンドに追加する方法〕

また、既存の書き込みのコマンド(Page Program等)に加え、ROM書きモードでのプログラムコマンドを追加するようにしてもよい。このコマンドを使用して書き込む場合は、プログラムサイクルの間はROM書きモードと同じ動作を継続するようにする。

【0043】

〔制御信号用のラインへのプルアップ抵抗/プルダウン抵抗の追加〕

また、上述した実施例では、I/Oライン8−1〜8−Nにスイッチ11−1〜11−Nを介してプルアップ抵抗12−1〜12−Nの一端を接続し、プルアップ抵抗12−1〜12−Nの他端を所定の電源電位Vccに接続するようにしたが、これと同様の構成を制御信号用のライン9−1〜9−Mに追加するようにしてもよい。

【0044】

例えば、図6に示すように、制御信号用のライン9−1,9−2にスイッチ14−1,14−2を介して抵抗(プルアップ抵抗)15−1,15−2の一端を接続し、制御信号用のライン9−Mにスイッチ14−Mを介して抵抗(プルダウン抵抗)15−Mの一端を接続し、プルアップ抵抗15−1,15−2の他端を所定の電源電位Vccに接続し、プルダウン抵抗15−Mの他端を接地電位GNDに接続するようにし、スイッチ14−1〜14−MのON/OFFモードをスイッチ11−1〜11−Nと同様にしてROM書きモード設定用レジスタ10によって設定するようにする。

【0045】

このようにすることによって、制御信号用のライン9−1〜9−Mに接触不良が生じた場合、想定しないプログラムが行われる可能性を排除することが可能となる。例えば、制御信号用のライン9−1を書き込み信号WRBのラインとした場合、制御信号用のライン9−1に接触不良が生じると、書き込み信号WRBが「H」レベルを保ち、データの書き込みそのものが行われないようになる。なお、制御信号用のライン9−1〜9−Mの何れのラインを電源電位Vccに接続するか、接地電位GNDに接続するかは、その制御信号用のライン9−1〜9−Mへの制御信号の種類によって適切に定めるものとする。

【0046】

図6に示したNANDフラッシュメモリ101において、メモリアレイ2が本発明でいうメモリに相当し、I/Oライン8−1〜8−Nが第1〜第Nのデータ入出力用のラインに相当し、制御信号用のライン9−1〜9−Mが第1〜第Mの制御信号用のラインに相当し、スイッチ11−1〜11−Nが第1〜第Nのスイッチング手段に相当し、スイッチ14−1〜14−Mが第1〜第Mのスイッチング手段に相当し、抵抗12−1〜12−Nが第1〜第Nの抵抗に相当し、抵抗15−1〜15−Mが第1〜第Mの抵抗に相当し、ROM書きモード設定用レジスタ10が設定手段に相当する。

【0047】

図6に示したNANDフラッシュメモリ101においても、図7に示すように、外部外部入力端子の1つとしてモード判定用端子13を設け、このモード判定用端子13への入力レベルに応じてスイッチ11−1〜11−Nおよびスイッチ15−1〜15−MのON/OFFモードの設定を行うようにしてもよい。

【産業上の利用可能性】

【0048】

本発明のNANDフラッシュメモリおよびNANDフラッシュメモリへのデータ書込方法は、接触不良による誤書き込み防止機能を備えたNANDフラッシュメモリおよびNANDフラッシュメモリへのデータ書込方法として、様々な分野で利用することが可能である。

【符号の説明】

【0049】

1…コントローラ、2…メモリアレイ、3…バッファ、4…ページ、5…ブロック、6…データエリア、7…スペアエリア、8−1〜8−N…データ入出力用のライン(I/Oライン)、9−1〜9−M…制御信号用のライン、10…ROM書きモード設定用レジスタ、11−1〜11−N…スイッチ(第1〜第Nのスイッチ)、12−1〜12−N…抵抗(第1〜第Nの抵抗)、13…モード判定用端子、14−1〜14−M…スイッチ(第1〜第Mのスイッチ)、15−1〜15−M…抵抗(第1〜第Mの抵抗)、101…NANDフラッシュメモリ、200…ソケット、300…ホストデバイス(ROMライタ)。

【特許請求の範囲】

【請求項1】

メモリと、

このメモリへの第1〜第N(N≧2)のデータ入出力用のラインと、

この第1〜第Nのデータ入出力用のラインに第1〜第Nのスイッチング手段を介してその一端が接続されその他端が所定の電源電位に接続された第1〜第Nの抵抗と、

前記第1〜第Nのスイッチング手段を介する前記第1〜第Nの抵抗と前記第1〜第Nのデータ入出力用のラインとの間の接続の有効/無効を設定する設定手段と

を備えることを特徴とするNANDフラッシュメモリ。

【請求項2】

請求項1に記載されたNANDフラッシュメモリにおいて、

前記設定手段は、

ソケットを使用しての前記メモリへのデータの書き込み時に、前記第1〜第Nのスイッチング手段を介する前記第1〜第Nの抵抗と前記第1〜第Nのデータ入出力用のラインとの間の接続を有効とする

ことを特徴とするNANDフラッシュメモリ。

【請求項3】

請求項1に記載されたNANDフラッシュメモリにおいて、

前記設定手段は、

ソケットを使用しての前記メモリへのデータの書き込み時、このデータの書き込みを行うホストデバイスからの指令を受けて、前記第1〜第Nのスイッチング手段を介する前記第1〜第Nの抵抗と前記第1〜第Nのデータ入出力用のラインとの間の接続を有効とする

ことを特徴とするNANDフラッシュメモリ。

【請求項4】

請求項1に記載されたNANDフラッシュメモリにおいて、

外部入力端子の1つとしてモード判定用端子を備え、

前記設定手段は、

前記モード判定用端子への入力レベルに応じて、前記第1〜第Nのスイッチング手段を介する前記第1〜第Nの抵抗と前記第1〜第Nのデータ入出力用のラインとの間の接続の有効/無効の設定を行う

ことを特徴とするNANDフラッシュメモリ。

【請求項5】

請求項1に記載されたNANDフラッシュメモリにおいて、

前記設定手段は、

前記メモリへのデータの書き込みが所定のコマンドを使用して行われる場合、前記第1〜第Nのスイッチング手段を介する前記第1〜第Nの抵抗と前記第1〜第Nのデータ入出力用のラインとの間の接続を有効とする

ことを特徴とするNANDフラッシュメモリ。

【請求項6】

請求項1〜5の何れか1項に記載されたNANDフラッシュメモリにおいて、

第1〜第M(M≧2)の制御信号用の入力ラインと、

この第1〜第Mの制御信号用のラインに第1〜第Mのスイッチング手段を介してその一端が接続されその他端が所定の電源電位或いは接地電位に接続された第1〜第Mの抵抗とを備え、

前記設定手段は、

前記第1〜第Nのスイッチング手段を介する前記第1〜第Nの抵抗と前記第1〜第Nのデータ入出力用のラインとの間の接続の有効/無効の設定と同様に、前記第1〜第Mのスイッチング手段を介する前記第1〜第Mの抵抗と前記第1〜第Mの制御信号用のラインとの間の接続の有効/無効の設定を行う

ことを特徴とするNANDフラッシュメモリ。

【請求項7】

メモリへの第1〜第N(N≧2)のデータ入出力用のラインに第1〜第Nのスイッチング手段を介して第1〜第Nの抵抗の一端を接続し、

この第1〜第Nの抵抗の他端を所定の電源電位に接続し、

ソケットを使用しての前記メモリへのデータの書き込み時に、前記第1〜第Nのスイッチング手段を介する前記第1〜第Nの抵抗と前記第1〜第Nのデータ入出力用のラインとの間の接続を有効とする

ことを特徴とするNANDフラッシュメモリへのデータ書込方法。

【請求項1】

メモリと、

このメモリへの第1〜第N(N≧2)のデータ入出力用のラインと、

この第1〜第Nのデータ入出力用のラインに第1〜第Nのスイッチング手段を介してその一端が接続されその他端が所定の電源電位に接続された第1〜第Nの抵抗と、

前記第1〜第Nのスイッチング手段を介する前記第1〜第Nの抵抗と前記第1〜第Nのデータ入出力用のラインとの間の接続の有効/無効を設定する設定手段と

を備えることを特徴とするNANDフラッシュメモリ。

【請求項2】

請求項1に記載されたNANDフラッシュメモリにおいて、

前記設定手段は、

ソケットを使用しての前記メモリへのデータの書き込み時に、前記第1〜第Nのスイッチング手段を介する前記第1〜第Nの抵抗と前記第1〜第Nのデータ入出力用のラインとの間の接続を有効とする

ことを特徴とするNANDフラッシュメモリ。

【請求項3】

請求項1に記載されたNANDフラッシュメモリにおいて、

前記設定手段は、

ソケットを使用しての前記メモリへのデータの書き込み時、このデータの書き込みを行うホストデバイスからの指令を受けて、前記第1〜第Nのスイッチング手段を介する前記第1〜第Nの抵抗と前記第1〜第Nのデータ入出力用のラインとの間の接続を有効とする

ことを特徴とするNANDフラッシュメモリ。

【請求項4】

請求項1に記載されたNANDフラッシュメモリにおいて、

外部入力端子の1つとしてモード判定用端子を備え、

前記設定手段は、

前記モード判定用端子への入力レベルに応じて、前記第1〜第Nのスイッチング手段を介する前記第1〜第Nの抵抗と前記第1〜第Nのデータ入出力用のラインとの間の接続の有効/無効の設定を行う

ことを特徴とするNANDフラッシュメモリ。

【請求項5】

請求項1に記載されたNANDフラッシュメモリにおいて、

前記設定手段は、

前記メモリへのデータの書き込みが所定のコマンドを使用して行われる場合、前記第1〜第Nのスイッチング手段を介する前記第1〜第Nの抵抗と前記第1〜第Nのデータ入出力用のラインとの間の接続を有効とする

ことを特徴とするNANDフラッシュメモリ。

【請求項6】

請求項1〜5の何れか1項に記載されたNANDフラッシュメモリにおいて、

第1〜第M(M≧2)の制御信号用の入力ラインと、

この第1〜第Mの制御信号用のラインに第1〜第Mのスイッチング手段を介してその一端が接続されその他端が所定の電源電位或いは接地電位に接続された第1〜第Mの抵抗とを備え、

前記設定手段は、

前記第1〜第Nのスイッチング手段を介する前記第1〜第Nの抵抗と前記第1〜第Nのデータ入出力用のラインとの間の接続の有効/無効の設定と同様に、前記第1〜第Mのスイッチング手段を介する前記第1〜第Mの抵抗と前記第1〜第Mの制御信号用のラインとの間の接続の有効/無効の設定を行う

ことを特徴とするNANDフラッシュメモリ。

【請求項7】

メモリへの第1〜第N(N≧2)のデータ入出力用のラインに第1〜第Nのスイッチング手段を介して第1〜第Nの抵抗の一端を接続し、

この第1〜第Nの抵抗の他端を所定の電源電位に接続し、

ソケットを使用しての前記メモリへのデータの書き込み時に、前記第1〜第Nのスイッチング手段を介する前記第1〜第Nの抵抗と前記第1〜第Nのデータ入出力用のラインとの間の接続を有効とする

ことを特徴とするNANDフラッシュメモリへのデータ書込方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2011−113591(P2011−113591A)

【公開日】平成23年6月9日(2011.6.9)

【国際特許分類】

【出願番号】特願2009−267248(P2009−267248)

【出願日】平成21年11月25日(2009.11.25)

【出願人】(390010179)埼玉日本電気株式会社 (1,228)

【Fターム(参考)】

【公開日】平成23年6月9日(2011.6.9)

【国際特許分類】

【出願日】平成21年11月25日(2009.11.25)

【出願人】(390010179)埼玉日本電気株式会社 (1,228)

【Fターム(参考)】

[ Back to top ]