NANDフラッシュメモリのリフレッシュ方法

【課題】デバイスのコントローラに過大な負荷を掛ることのない、NAND型フラッシュメモリデバイスのリフレッシュ方法の提供。

【解決手段】ホストが有する所定のインターフェースを介して指定されたアドレスをNANDフラッシュメモリの論理ブロックアドレスとして、該論理ブロックアドレスに対応する物理ブロックに対してデータの書き込みや読み出しを実行するNAND型フラシュメモリデバイスに対し、前記ホストが、該ホストと前記NAND型フラッシュメモリデバイスとの間で定義されてなるリフレッシュコマンドを前記NAND型フラッシュメモリデバイスに発行し、前記NANDフラッシュメモリのコントローラに前記リフレッシュコマンドを解釈するコマンド解釈手段を設けておき、該コマンド解釈手段による解釈に基づき前記リフレッシュを実行する。

【解決手段】ホストが有する所定のインターフェースを介して指定されたアドレスをNANDフラッシュメモリの論理ブロックアドレスとして、該論理ブロックアドレスに対応する物理ブロックに対してデータの書き込みや読み出しを実行するNAND型フラシュメモリデバイスに対し、前記ホストが、該ホストと前記NAND型フラッシュメモリデバイスとの間で定義されてなるリフレッシュコマンドを前記NAND型フラッシュメモリデバイスに発行し、前記NANDフラッシュメモリのコントローラに前記リフレッシュコマンドを解釈するコマンド解釈手段を設けておき、該コマンド解釈手段による解釈に基づき前記リフレッシュを実行する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、NANDフラッシュメモリのリフレッシュ方法及びNAND型フラッシュメモリデバイスに関する。

【背景技術】

【0002】

NANDフラッシュメモリとそのコントローラをワンパッケージにしたNAND型フラッシュメモリデバイスが知られている。このデバイスは、ホストICが有する所定のインターフェースと電気的、機械的に接続されて使用される。インターフェースは、例えば、NANDインターフェース、IDEインターフェース、USBインターフェースなどである。このNANDフラッシュメモリデバイスは、ホストICのインターフェースから発行されるwriteコマンドやreadコマンドで指定されたアドレスをNANDフラッシュメモリの論理ブロックアドレスとして、その論理ブロックアドレスに対応する物理ブロックアドレスをコントローラ内に存在する論理ブロック−物理ブロック管理テーブル(アドレス管理テーブル)を参照して割り出し、割り出された物理ブロックアドレスにデータを書き込んだり、データの読み出しを実行している。また、NANDフラッシュメモリ特有のエラー訂正回路もコントローラに具備されており、データ読み出したときに、データ書き込み時のエラーがあったことが判明した場合は、エラー訂正回路により訂正済みのデータがホストICに送出される。

【0003】

コントローラをデバイスICに同梱することにより、ホストICに、論理ブロック−物理ブロック管理テーブルやエラー訂正回路が不要となり、様々な用途に使用されており、今後も多くの用途が期待されている。

【0004】

例えば、メモリに音楽データを記録し、ホストICが専らこのデータを読み出し再生する音楽プレーヤが市販されており、また各種業務用ゲーム機に使用できるが、NANDフラッシュメモリの場合、データの読み出しを頻繁に行うと、リードディスターブエラー(read disturb error)により、データの一部が変化してしまう場合がある。このリードディスターブエラーは、データの読み出し対象となった選択セルからデータが読み出される際、非選択セル(データ読み出し対象となっていないページのセル)の浮遊ゲートに電荷が注入されてしまい、これにより非選択セルが弱くプログラムされたのと同じ状態になるために生じるものであり、読み出し回数が増えるに従い、より多くのメモリセルが影響を受ける。さらには、書き込み時のエラーと異なり、エラー訂正回路によるデータエラーの訂正が効かないといった深刻な問題を生じ得る。

【0005】

このリードディスターブエラーに対処するため、該エラーが生じない特別な回路を予め用意したり、電荷の減少したセル単体を個別に探し出して電荷を注入しエラーデータが読み出されないようにする方法などが提案されているが、回路や処理が複雑で高価となり、実用的ではない。

【特許文献1】特開10−228783

【特許文献2】特開2002−150783

【特許文献3】特開2004−326867

【特許文献4】特許第3641066号

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明は、このような問題点に鑑みてなされたものであり、その目的は、NAND型フラッシュメモリデバイスのリードディスターブエラーを有効に防止し得るリフレッシュ方法を提供することにある。特に、デバイスのコントローラに過大な負荷を掛ることのないリフレッシュ方法を提供することを目的とする。その他の目的は、明細書、図面、特に特許請求の範囲から自ずと明らかとなろう。

【課題を解決するための手段】

【0007】

上記課題解決のため、本発明は、請求項記載の解決手段を提供する。

【発明を実施するための最良の形態】

【0008】

以下、本発明を実施するための最良の形態について図面を用いて説明するが、本発明は特許請求の範囲内において種々の形態を採ることができ、下記実施形態に限定されないことはいうまでもない。

【0009】

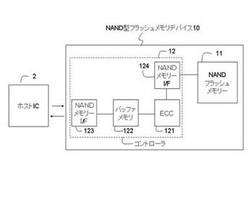

図1は、NAND型フラッシュメモリデバイスの内部ブロックと、その使用環境(システム)例を表している。尚、本願で「NAND型フラッシュメモリデバイス」とは、NANDフラッシュメモリとコントローラを包含する概念であり、また「システム」とは、以下に述べるホストICと前記NAND型フラッシュメモリデバイスを包含し、所定の目的のために動作する構成をいう。

【0010】

図示するように、NAND型フラッシュメモリデバイス10(必要に応じてデバイス10という)は、ホストIC2とNANDインターフェースで接続されて使用される。NAND型フラッシュメモリデバイス10は、NANDフラッシュメモリ11と、ホストIC2の指令に基づき該NANDフラッシュメモリ11からデータの読み出しや書き込みを実行するコントローラ12を具備する。NANDフラッシュメモリ11とコントローラ12は、それぞれのダイ(die)が基板上で結線され、ワンパッケージICとして構成されている。

【0011】

NANDインターフェース123は、ホストIC2のNANDインターフェース(図示せず)と各種信号線で結合され、データの書き込み指令や読み出し指令を受け、また読み出したデータをホストIC2に送出する。バッファメモリ122はホストIC2から送出された書き込み用データをNANDフラッシュメモリ11に書き込む際の緩衝手段である。ECC121はエラー訂正回路であり、書き込み時にエラー訂正符号を作出するエンコーダ(図示せず)とNANDフラッシュメモリ11から読み出されたデータに含まれるエラー訂正符号をデコードするデコーダ(図示せず)を含む。データ書き込み時はエンコーダによりエラー訂正符号を作出する。書き込み指令を受けたデータはセクターのデータ部に、エラー訂正符号は冗長部に、NANDインターフェース124を介して書き込まれる。

【0012】

一方、ホストIC2から指令を受けて読み出されたデータはNANDインターフェース124を介してECC121に送られ、ここで冗長部に記憶していたエラー訂正符号がデコードされ、エラーがあった場合は該エラー訂正符号を用いて訂正されて後、バッファメモリ122及びNANDインターフェース123を介してホストIC2に送出される。

【0013】

尚、本NAND型フラッシュメモリデバイス10は、ホストIC2からの書き込みコマンド(writeコマンドという)、または読み出しコマンド(readコマンドという)で指定されたアドレスを、NANDフラッシュメモリ11の論理ブロックアドレスとして、その論理ブロックアドレスに対応する物理ブロックアドレスを、論理ブロックアドレスと物理ブロックアドレスの関係が記録されているアドレス管理テーブル(図示せず)から割り出して、該割り出された物理ブロックにデータを書き込み、或いはデータを読み出す。

【0014】

尚、writeコマンドやreadコマンドは、システムの標準コマンドであり、該コマンドを表す所定のコマンドコードが、アドレスやデータととともに、NANDインターフェースの有するI/O端子からNAND型フラッシュメモリデバイス10に送出される。

【0015】

(リフレッシュコマンド)

ホストIC2とNAND型フラッシュメモリデバイス10との間で、リフレッシュコマンドであることを示すコマンドコードとして、例えば55h(hは16進法であることを表す)を定義する。コントラー12の制御プログラム(ファームウエア)には、該コマンドを解釈するコマンド解釈手段と該解釈に基づきリフレッシュを実行するためのルーチンプログラムを組み込んでおく。

【0016】

(ファームウエアによるリフレッシュ)

リフレッシュ対象はユーザデータ領域、即ち、論理ブロックと対応付けされる全ての論理ブロックとすることができる(ただし予備の空きブロックを除く)。本発明のリフレッシュは、専らホストIC2からの指令に基づくものとする。この指令は、システム(例えば音楽プレーヤ)の電源がonされたときに実行することができる。一度に全部の論理ブロックアドレスを指定してもよいが、NANDフラッシュメモリの容量が大きいときは、予めユーザデータ領域を複数の領域(リージョン/region)に分割定義しておき、リージョンごとにリフレッシュを実行しても良い。例えば、ユーザデータ領域として、論理ブロック番号が0から7999までの8000あったとする(この他前記予備ブロックが別に設けられているものとする)。論理ブロック番号0から999までを第1リージョン、続いて1000から1999までを第2リージョン、2000から2999までを第3リージョン、以降同じく、・・・7000から7999までを第8リージョンとしたとき、電源がonされるごとに、第1リージョンから第2リージョン、第3リージョンと順にリフレッシュしてもよい。

【0017】

ホストIC2からリレッシュコマンドが発行されたとき、コントローラ12は、指定された論理ブロック番号に対応する物理ブロック番号から、NANDインターフェース124を介してデータを読み出す。読み出したデータはエラー訂正回路(ECC121)で訂正した後一旦バッファメモリ122に待避させる。続いてNANDフラッシュメモリ11の前記予備ブロックに、ECC121を介して1ページずつデータを転送し書き込む。1ブロック分のデータ転送が終了したら、データを書き写す前のブロック(当初データが書かれていたリフレッシュ対象となったブロック)のデータを消去し、アドレス管理テーブルを最新の対応関係に更新する。これを1リージョン分、そのリージョンを構成する全ブロックについて実行する。当該時点でリフラッシュを完了したリージョン番号を、コントローラ12の所定の箇所またはNANDフラッシュメモリ11の管理領域に不揮発的に記憶させておく。次回電源on時は、このリージョン情報を元に、次のリージョンをリフレッシュし、以降これを繰り返し実行すればよい。

【0018】

上記で、1リージョンを1000のブロックとしたが、これよりも小さくしてよいことは言うまでもない。リージョンごと大きさが異なっても良い。また、リフレッシュ対象となったブロックのデータを、コントローラ12側に読み出すことなく、NANDフラッシュメモリ11内のバッファ(図示せず)に一時待避させ、空きブロックに書き込んでもよい。また、電源をonしたときではなく、offとしたときに実行しても良い。たとえば、ユーザがシステムの電源をoffとしたとき(たとえば電源ボタンをoffとする動作をしたとき)、電源on時に点灯するLEDを消灯させるが、内部動作でリフレッシュを実行してからシステムを休止させてもよい。リフレッシュ実行時にユーザが再度電源をonしたときは、リフレッシュを終了してからユーザの設定(例えばユーザの指定した曲の演奏)に従えばよい。このように設定しても、リフレッシュ時間が短ければユーザが支障を感じることはない。

【0019】

また電池が内蔵されている音楽プレーヤなどのシステムにおいては、ユーザが電源onするか否かに拘わらず、ホストIC2が管理する内部タイマー(図示せず)の動作により、毎日一定時刻に、または一定時間間隔ごとにリフレッシュを実行するようシステムを構築してもよい。このときも、リフレッシュ実行中にユーザが電源をonし、曲の演奏(プレイという)を指示したとしても、リフレッシュが有効に終了してからユーザの指示に従えばよい。

【0020】

ホストIC2からの要求に基づくメディアアクセス(データ読み出し)実行中にタイマーイベントが発生した場合であって、リフレッシュ対象物理ブロックが複数存在する場合、ファームウエアにより、リフレッシュを、物理ブロック単位で、一定の規則的(regular)なタイムインターバルで実行することが好ましい。例えば、1物理ブロックあたりのリフレッシュ時間はせいぜい100ms(ミリ秒)程度であるから、リフレッシュ間隔(一の物理ブロックのリフレッシュ開始から次の物理ブロックのリフレッシュ開始まで)を、例えば1秒に設定する。即ち、1秒おきに、メディアアクセスに割り込んで、物理ブロック単位で、リフレッシュを時分割処理する。このようにすれば、リフレッシュ対象ブロックが複数存在する場合でも、ホストIC2に対するデータ転送中にデータが途切れ、ユーザに不快感を与えたりするなど、プレイに支障が生じることがない。特に、NANDフラッシュメモリ11に記憶されているデータが音楽や動画などのコンテンツであり、多数の物理ブロックがリフレッシュ対象であったとしても、物理ブロックごと時分割にリフレッシュを実行すれば、プレイ中のデータ転送レート一定に保持することができる。

【0021】

また常時電源がonされているようなシステムにおいては、システムが稼動しない時間帯を見計らって、毎日一定時刻にリフレッシュを実行するよう構成してもよい。

【0022】

さらに、前記リージョンごとのホストIC2からのread回数を、該ホストIC2がカウント・記憶しておき、予め設定した閾値を超えたリージョンのみ(実際にはそのリージョンを構成する物理ブロック)をリフレッシュしても良い。また、NANDフラッシュメモリ11の論理ブロック番号(ユーザデータ領域)ごとのホストIC2からのread回数を、該ホストIC2がカウント・記憶しておき、read回数が予め設定した閾値を超えた論理ブロックに対応する物理ブロックをリフレッシュしてもよい。この2例の場合、システム稼動上readが頻繁に発生することが予め分かっている、一つ又は複数のリージョン若しくは論理ブロックのread回数をカウント・記憶しておき、read回数が予め設定した閾値を超えたリージョンや論理ブロックに対応する物理ブロックをリフレッシュするのでもよい。

【0023】

上記の例では、リフレッシュコマンドを、該コマンドを表す前記コマンドコードに続けて、リフレッシュすべきリージョン番号で指定し(便宜上、リージョンリフレッシュコマンドという)、或いは、リフレッシュを開始すべき論理ブロック番号とリフレッシュすべき論理ブロック数を指定することにより発行すること(便宜上、ブロックリフレシュコマンドという)が好ましいが、NAND型フラッシュメモリデバイス2で使用されているSector Readコマンドの例に倣い、リフレッシュコマンドコードに続けて、リフレッシュすべきNANDフラッシュメモリ11の論理セクターアドレス(読み出し開始アドレス)とセクター長(読み出すべきセクター数)で指定してもよい(便宜上、論理セクターアドレス指定リフレッシュコマンドという)。尚ここでいう論理セクターアドレスは、そのセクターを含む論理ページアドレスと論理ブロック番号を含む。

【0024】

たとえば、上記リージョンや論理ブロック以外に、一つ又は複数の適宜なデータオブジェクト(ファイル)に対するread回数をホストIC2がカウント・記憶しておき、予め設定した閾値を超えたデータオブジェクトを記憶している論理ブロックに対応する物理ブロックをリフレッシュするようにしてもよい。この場合も、readが頻繁に発生することが予め分かっている一つ又は複数のデータオブジェクトに対するread回数をホストIC2がカウント・記憶しておき、予め設定した閾値を超えたデータオブジェクトを構成する論理ブロックに対応する物理ブロックをリフレッシュする。データオブジェクトの場合、そのデータは所定の論理ブロックの途中のセクターから記憶され、さらに他の論理ブロックの途中まで記憶されている場合がある。このようにリフレッシュを、論理セクターアドレスとセクター長で指定すれば、リフレッシュ対象をデータオブジェクトで指定する場合に好適である。しかしこの場合でも、リフレッシュは、そのオブジェクトデータを含む全ブロックが対象となることはいうまでもない。

【0025】

上記の例の他、NANDフラッシュメモリ11の論理ページアドレスとページ長で指定しても良い(便宜上、論理ページアドレス指定リフレッシュコマンドという)。

【0026】

(変形例)

上記の実施例では、ホストIC2とデバイス10をNANDインターフェースで接続しているが、コマンドコードとアドレスによりデータの読み出しや書き込みを実行するインターフェースであれば、IDEインターフェースやUSBインターフェース、その他どのようなインターフェースでも良い。

【0027】

また、コントローラ21とNANDフラッシュメモリ22はそれぞれ独立に構成してもよい。例えば、NANDフラッシュメモリ22をmicroSDカードのように、その一つの辺に電極を配した薄板のカード状に構成し、コントローラ21(IC)と接続されているソケットに、挿抜可能に構成しても良い。このようにすれば、該メモリ22に故障が生じた場合、新しいものと差し替えて使用することができ、その後も当該システムを有効に活用することができる。

【0028】

また、上述した4つのコマンドのコマンドコードは同一でも良いし、互いに異なるように定義してもよい。

【0029】

さらには、ホストをパーソナルコンピュータ(PC)で構成し、NAND型フラッシュメモリデバイス10とホストを、本願目的を達成する所定のインターフェースによって着脱式に接続してもよい。例えば、デバイス10をUSBインターフェース準拠のEXPRESS CARDやメモリカードインターフェース準拠の各種メモリカードで構成してもよい。 但し、この場合リフレッシュ実行中にユーザが知らないでデバイス10をホストから抜き取るとメモリが破損する場合があるので、デバイス10を使用中に実行することが望ましい。

【0030】

(発明の効果)

以上述べたように、本発明によれば、システムの種類に臨機応変に対応してリフレッシュ可能なNAND型フラッシュメモリデバイス及びそのシステムを提供することができる。また、本発明により、データの読み出しが頻繁に実行されるシステムにおいて、従来の各種インターフェース準拠のNAND型フラッシュメモリデバイスのファームウエアを一部改良するのみで、複雑な回路を設けることなく、NANDフラッシュメモリのリフレッシュを効率よく実行することができ、リードディスターブエラーがなく、安全且つ適切なシステムの運用を図ることができる。

【図面の簡単な説明】

【0031】

【図1】本発明のNAND型フラッシュメモリデバイス内部ブロック例とシステムの概観例である。

【図2】リフレッシュを実行するNANDフラッシュメモリのリージョン例である。

【符号の説明】

【0032】

2:ホストIC、10:NAND型フラッシュメモリデバイス、11:NANDフラッシュメモリ、12:コントローラ、

【技術分野】

【0001】

本発明は、NANDフラッシュメモリのリフレッシュ方法及びNAND型フラッシュメモリデバイスに関する。

【背景技術】

【0002】

NANDフラッシュメモリとそのコントローラをワンパッケージにしたNAND型フラッシュメモリデバイスが知られている。このデバイスは、ホストICが有する所定のインターフェースと電気的、機械的に接続されて使用される。インターフェースは、例えば、NANDインターフェース、IDEインターフェース、USBインターフェースなどである。このNANDフラッシュメモリデバイスは、ホストICのインターフェースから発行されるwriteコマンドやreadコマンドで指定されたアドレスをNANDフラッシュメモリの論理ブロックアドレスとして、その論理ブロックアドレスに対応する物理ブロックアドレスをコントローラ内に存在する論理ブロック−物理ブロック管理テーブル(アドレス管理テーブル)を参照して割り出し、割り出された物理ブロックアドレスにデータを書き込んだり、データの読み出しを実行している。また、NANDフラッシュメモリ特有のエラー訂正回路もコントローラに具備されており、データ読み出したときに、データ書き込み時のエラーがあったことが判明した場合は、エラー訂正回路により訂正済みのデータがホストICに送出される。

【0003】

コントローラをデバイスICに同梱することにより、ホストICに、論理ブロック−物理ブロック管理テーブルやエラー訂正回路が不要となり、様々な用途に使用されており、今後も多くの用途が期待されている。

【0004】

例えば、メモリに音楽データを記録し、ホストICが専らこのデータを読み出し再生する音楽プレーヤが市販されており、また各種業務用ゲーム機に使用できるが、NANDフラッシュメモリの場合、データの読み出しを頻繁に行うと、リードディスターブエラー(read disturb error)により、データの一部が変化してしまう場合がある。このリードディスターブエラーは、データの読み出し対象となった選択セルからデータが読み出される際、非選択セル(データ読み出し対象となっていないページのセル)の浮遊ゲートに電荷が注入されてしまい、これにより非選択セルが弱くプログラムされたのと同じ状態になるために生じるものであり、読み出し回数が増えるに従い、より多くのメモリセルが影響を受ける。さらには、書き込み時のエラーと異なり、エラー訂正回路によるデータエラーの訂正が効かないといった深刻な問題を生じ得る。

【0005】

このリードディスターブエラーに対処するため、該エラーが生じない特別な回路を予め用意したり、電荷の減少したセル単体を個別に探し出して電荷を注入しエラーデータが読み出されないようにする方法などが提案されているが、回路や処理が複雑で高価となり、実用的ではない。

【特許文献1】特開10−228783

【特許文献2】特開2002−150783

【特許文献3】特開2004−326867

【特許文献4】特許第3641066号

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明は、このような問題点に鑑みてなされたものであり、その目的は、NAND型フラッシュメモリデバイスのリードディスターブエラーを有効に防止し得るリフレッシュ方法を提供することにある。特に、デバイスのコントローラに過大な負荷を掛ることのないリフレッシュ方法を提供することを目的とする。その他の目的は、明細書、図面、特に特許請求の範囲から自ずと明らかとなろう。

【課題を解決するための手段】

【0007】

上記課題解決のため、本発明は、請求項記載の解決手段を提供する。

【発明を実施するための最良の形態】

【0008】

以下、本発明を実施するための最良の形態について図面を用いて説明するが、本発明は特許請求の範囲内において種々の形態を採ることができ、下記実施形態に限定されないことはいうまでもない。

【0009】

図1は、NAND型フラッシュメモリデバイスの内部ブロックと、その使用環境(システム)例を表している。尚、本願で「NAND型フラッシュメモリデバイス」とは、NANDフラッシュメモリとコントローラを包含する概念であり、また「システム」とは、以下に述べるホストICと前記NAND型フラッシュメモリデバイスを包含し、所定の目的のために動作する構成をいう。

【0010】

図示するように、NAND型フラッシュメモリデバイス10(必要に応じてデバイス10という)は、ホストIC2とNANDインターフェースで接続されて使用される。NAND型フラッシュメモリデバイス10は、NANDフラッシュメモリ11と、ホストIC2の指令に基づき該NANDフラッシュメモリ11からデータの読み出しや書き込みを実行するコントローラ12を具備する。NANDフラッシュメモリ11とコントローラ12は、それぞれのダイ(die)が基板上で結線され、ワンパッケージICとして構成されている。

【0011】

NANDインターフェース123は、ホストIC2のNANDインターフェース(図示せず)と各種信号線で結合され、データの書き込み指令や読み出し指令を受け、また読み出したデータをホストIC2に送出する。バッファメモリ122はホストIC2から送出された書き込み用データをNANDフラッシュメモリ11に書き込む際の緩衝手段である。ECC121はエラー訂正回路であり、書き込み時にエラー訂正符号を作出するエンコーダ(図示せず)とNANDフラッシュメモリ11から読み出されたデータに含まれるエラー訂正符号をデコードするデコーダ(図示せず)を含む。データ書き込み時はエンコーダによりエラー訂正符号を作出する。書き込み指令を受けたデータはセクターのデータ部に、エラー訂正符号は冗長部に、NANDインターフェース124を介して書き込まれる。

【0012】

一方、ホストIC2から指令を受けて読み出されたデータはNANDインターフェース124を介してECC121に送られ、ここで冗長部に記憶していたエラー訂正符号がデコードされ、エラーがあった場合は該エラー訂正符号を用いて訂正されて後、バッファメモリ122及びNANDインターフェース123を介してホストIC2に送出される。

【0013】

尚、本NAND型フラッシュメモリデバイス10は、ホストIC2からの書き込みコマンド(writeコマンドという)、または読み出しコマンド(readコマンドという)で指定されたアドレスを、NANDフラッシュメモリ11の論理ブロックアドレスとして、その論理ブロックアドレスに対応する物理ブロックアドレスを、論理ブロックアドレスと物理ブロックアドレスの関係が記録されているアドレス管理テーブル(図示せず)から割り出して、該割り出された物理ブロックにデータを書き込み、或いはデータを読み出す。

【0014】

尚、writeコマンドやreadコマンドは、システムの標準コマンドであり、該コマンドを表す所定のコマンドコードが、アドレスやデータととともに、NANDインターフェースの有するI/O端子からNAND型フラッシュメモリデバイス10に送出される。

【0015】

(リフレッシュコマンド)

ホストIC2とNAND型フラッシュメモリデバイス10との間で、リフレッシュコマンドであることを示すコマンドコードとして、例えば55h(hは16進法であることを表す)を定義する。コントラー12の制御プログラム(ファームウエア)には、該コマンドを解釈するコマンド解釈手段と該解釈に基づきリフレッシュを実行するためのルーチンプログラムを組み込んでおく。

【0016】

(ファームウエアによるリフレッシュ)

リフレッシュ対象はユーザデータ領域、即ち、論理ブロックと対応付けされる全ての論理ブロックとすることができる(ただし予備の空きブロックを除く)。本発明のリフレッシュは、専らホストIC2からの指令に基づくものとする。この指令は、システム(例えば音楽プレーヤ)の電源がonされたときに実行することができる。一度に全部の論理ブロックアドレスを指定してもよいが、NANDフラッシュメモリの容量が大きいときは、予めユーザデータ領域を複数の領域(リージョン/region)に分割定義しておき、リージョンごとにリフレッシュを実行しても良い。例えば、ユーザデータ領域として、論理ブロック番号が0から7999までの8000あったとする(この他前記予備ブロックが別に設けられているものとする)。論理ブロック番号0から999までを第1リージョン、続いて1000から1999までを第2リージョン、2000から2999までを第3リージョン、以降同じく、・・・7000から7999までを第8リージョンとしたとき、電源がonされるごとに、第1リージョンから第2リージョン、第3リージョンと順にリフレッシュしてもよい。

【0017】

ホストIC2からリレッシュコマンドが発行されたとき、コントローラ12は、指定された論理ブロック番号に対応する物理ブロック番号から、NANDインターフェース124を介してデータを読み出す。読み出したデータはエラー訂正回路(ECC121)で訂正した後一旦バッファメモリ122に待避させる。続いてNANDフラッシュメモリ11の前記予備ブロックに、ECC121を介して1ページずつデータを転送し書き込む。1ブロック分のデータ転送が終了したら、データを書き写す前のブロック(当初データが書かれていたリフレッシュ対象となったブロック)のデータを消去し、アドレス管理テーブルを最新の対応関係に更新する。これを1リージョン分、そのリージョンを構成する全ブロックについて実行する。当該時点でリフラッシュを完了したリージョン番号を、コントローラ12の所定の箇所またはNANDフラッシュメモリ11の管理領域に不揮発的に記憶させておく。次回電源on時は、このリージョン情報を元に、次のリージョンをリフレッシュし、以降これを繰り返し実行すればよい。

【0018】

上記で、1リージョンを1000のブロックとしたが、これよりも小さくしてよいことは言うまでもない。リージョンごと大きさが異なっても良い。また、リフレッシュ対象となったブロックのデータを、コントローラ12側に読み出すことなく、NANDフラッシュメモリ11内のバッファ(図示せず)に一時待避させ、空きブロックに書き込んでもよい。また、電源をonしたときではなく、offとしたときに実行しても良い。たとえば、ユーザがシステムの電源をoffとしたとき(たとえば電源ボタンをoffとする動作をしたとき)、電源on時に点灯するLEDを消灯させるが、内部動作でリフレッシュを実行してからシステムを休止させてもよい。リフレッシュ実行時にユーザが再度電源をonしたときは、リフレッシュを終了してからユーザの設定(例えばユーザの指定した曲の演奏)に従えばよい。このように設定しても、リフレッシュ時間が短ければユーザが支障を感じることはない。

【0019】

また電池が内蔵されている音楽プレーヤなどのシステムにおいては、ユーザが電源onするか否かに拘わらず、ホストIC2が管理する内部タイマー(図示せず)の動作により、毎日一定時刻に、または一定時間間隔ごとにリフレッシュを実行するようシステムを構築してもよい。このときも、リフレッシュ実行中にユーザが電源をonし、曲の演奏(プレイという)を指示したとしても、リフレッシュが有効に終了してからユーザの指示に従えばよい。

【0020】

ホストIC2からの要求に基づくメディアアクセス(データ読み出し)実行中にタイマーイベントが発生した場合であって、リフレッシュ対象物理ブロックが複数存在する場合、ファームウエアにより、リフレッシュを、物理ブロック単位で、一定の規則的(regular)なタイムインターバルで実行することが好ましい。例えば、1物理ブロックあたりのリフレッシュ時間はせいぜい100ms(ミリ秒)程度であるから、リフレッシュ間隔(一の物理ブロックのリフレッシュ開始から次の物理ブロックのリフレッシュ開始まで)を、例えば1秒に設定する。即ち、1秒おきに、メディアアクセスに割り込んで、物理ブロック単位で、リフレッシュを時分割処理する。このようにすれば、リフレッシュ対象ブロックが複数存在する場合でも、ホストIC2に対するデータ転送中にデータが途切れ、ユーザに不快感を与えたりするなど、プレイに支障が生じることがない。特に、NANDフラッシュメモリ11に記憶されているデータが音楽や動画などのコンテンツであり、多数の物理ブロックがリフレッシュ対象であったとしても、物理ブロックごと時分割にリフレッシュを実行すれば、プレイ中のデータ転送レート一定に保持することができる。

【0021】

また常時電源がonされているようなシステムにおいては、システムが稼動しない時間帯を見計らって、毎日一定時刻にリフレッシュを実行するよう構成してもよい。

【0022】

さらに、前記リージョンごとのホストIC2からのread回数を、該ホストIC2がカウント・記憶しておき、予め設定した閾値を超えたリージョンのみ(実際にはそのリージョンを構成する物理ブロック)をリフレッシュしても良い。また、NANDフラッシュメモリ11の論理ブロック番号(ユーザデータ領域)ごとのホストIC2からのread回数を、該ホストIC2がカウント・記憶しておき、read回数が予め設定した閾値を超えた論理ブロックに対応する物理ブロックをリフレッシュしてもよい。この2例の場合、システム稼動上readが頻繁に発生することが予め分かっている、一つ又は複数のリージョン若しくは論理ブロックのread回数をカウント・記憶しておき、read回数が予め設定した閾値を超えたリージョンや論理ブロックに対応する物理ブロックをリフレッシュするのでもよい。

【0023】

上記の例では、リフレッシュコマンドを、該コマンドを表す前記コマンドコードに続けて、リフレッシュすべきリージョン番号で指定し(便宜上、リージョンリフレッシュコマンドという)、或いは、リフレッシュを開始すべき論理ブロック番号とリフレッシュすべき論理ブロック数を指定することにより発行すること(便宜上、ブロックリフレシュコマンドという)が好ましいが、NAND型フラッシュメモリデバイス2で使用されているSector Readコマンドの例に倣い、リフレッシュコマンドコードに続けて、リフレッシュすべきNANDフラッシュメモリ11の論理セクターアドレス(読み出し開始アドレス)とセクター長(読み出すべきセクター数)で指定してもよい(便宜上、論理セクターアドレス指定リフレッシュコマンドという)。尚ここでいう論理セクターアドレスは、そのセクターを含む論理ページアドレスと論理ブロック番号を含む。

【0024】

たとえば、上記リージョンや論理ブロック以外に、一つ又は複数の適宜なデータオブジェクト(ファイル)に対するread回数をホストIC2がカウント・記憶しておき、予め設定した閾値を超えたデータオブジェクトを記憶している論理ブロックに対応する物理ブロックをリフレッシュするようにしてもよい。この場合も、readが頻繁に発生することが予め分かっている一つ又は複数のデータオブジェクトに対するread回数をホストIC2がカウント・記憶しておき、予め設定した閾値を超えたデータオブジェクトを構成する論理ブロックに対応する物理ブロックをリフレッシュする。データオブジェクトの場合、そのデータは所定の論理ブロックの途中のセクターから記憶され、さらに他の論理ブロックの途中まで記憶されている場合がある。このようにリフレッシュを、論理セクターアドレスとセクター長で指定すれば、リフレッシュ対象をデータオブジェクトで指定する場合に好適である。しかしこの場合でも、リフレッシュは、そのオブジェクトデータを含む全ブロックが対象となることはいうまでもない。

【0025】

上記の例の他、NANDフラッシュメモリ11の論理ページアドレスとページ長で指定しても良い(便宜上、論理ページアドレス指定リフレッシュコマンドという)。

【0026】

(変形例)

上記の実施例では、ホストIC2とデバイス10をNANDインターフェースで接続しているが、コマンドコードとアドレスによりデータの読み出しや書き込みを実行するインターフェースであれば、IDEインターフェースやUSBインターフェース、その他どのようなインターフェースでも良い。

【0027】

また、コントローラ21とNANDフラッシュメモリ22はそれぞれ独立に構成してもよい。例えば、NANDフラッシュメモリ22をmicroSDカードのように、その一つの辺に電極を配した薄板のカード状に構成し、コントローラ21(IC)と接続されているソケットに、挿抜可能に構成しても良い。このようにすれば、該メモリ22に故障が生じた場合、新しいものと差し替えて使用することができ、その後も当該システムを有効に活用することができる。

【0028】

また、上述した4つのコマンドのコマンドコードは同一でも良いし、互いに異なるように定義してもよい。

【0029】

さらには、ホストをパーソナルコンピュータ(PC)で構成し、NAND型フラッシュメモリデバイス10とホストを、本願目的を達成する所定のインターフェースによって着脱式に接続してもよい。例えば、デバイス10をUSBインターフェース準拠のEXPRESS CARDやメモリカードインターフェース準拠の各種メモリカードで構成してもよい。 但し、この場合リフレッシュ実行中にユーザが知らないでデバイス10をホストから抜き取るとメモリが破損する場合があるので、デバイス10を使用中に実行することが望ましい。

【0030】

(発明の効果)

以上述べたように、本発明によれば、システムの種類に臨機応変に対応してリフレッシュ可能なNAND型フラッシュメモリデバイス及びそのシステムを提供することができる。また、本発明により、データの読み出しが頻繁に実行されるシステムにおいて、従来の各種インターフェース準拠のNAND型フラッシュメモリデバイスのファームウエアを一部改良するのみで、複雑な回路を設けることなく、NANDフラッシュメモリのリフレッシュを効率よく実行することができ、リードディスターブエラーがなく、安全且つ適切なシステムの運用を図ることができる。

【図面の簡単な説明】

【0031】

【図1】本発明のNAND型フラッシュメモリデバイス内部ブロック例とシステムの概観例である。

【図2】リフレッシュを実行するNANDフラッシュメモリのリージョン例である。

【符号の説明】

【0032】

2:ホストIC、10:NAND型フラッシュメモリデバイス、11:NANDフラッシュメモリ、12:コントローラ、

【特許請求の範囲】

【請求項1】

ホストが有する所定のインターフェースを介して指定されたアドレスをNANDフラッシュメモリの論理ブロックアドレスとして、該論理ブロックアドレスに対応する物理ブロックに対してデータの書き込みや読み出しを実行するNAND型フラシュメモリデバイスに対し、

前記ホストが、該ホストと前記NAND型フラッシュメモリデバイスとの間で定義されてなるリフレッシュコマンドを前記NAND型フラッシュメモリデバイスに発行し、前記NANDフラッシュメモリに対して前記ホストから指令されたデータの読み出しや書き込みを実行するコントローラに前記リフレッシュコマンドを解釈するコマンド解釈手段を設けておき、該コマンド解釈手段による解釈に基づき前記リフレッシュを実行することを特徴とするNAND型フラッシュメモリのリフレッシュ方法。

【請求項2】

ユーザがシステム電源onの動作をするたびに前記リフレッシュを実行することを特徴とする請求項1記載のNAND型フラッシュメモリのリフレッシュ方法。

【請求項3】

電池内蔵型のシステムにおいて、ユーザのシステム電源on動作の有無に拘わらず、ホストICが有するタイマー機能により、一定時刻若しくは一定時間ごとに前記リフレッシュコマンドを発行して前記リフレッシュを実行することを特徴とする請求項1記載のNAND型フラッシュメモリのリフレッシュ方法。

【請求項4】

リフレッシュは、NANDフラッシュメモリの全論理ブロックアドレスを予め所定の大きさに分割・定義してなるリージョンを1単位として実行することを特徴とする請求項1乃至請求項3いずれか1項記載のNAND型フラッシュメモリのリフレッシュ方法。

【請求項5】

リフレッシュは、論理ブロックを1単位として実行することを特徴とする請求項1乃至請求項3いずれか1項記載のNAND型フラッシュメモリのリフレッシュ方法。

【請求項6】

リフレッシュは、NANDフラッシュメモリに記憶されているファイルを単位として実行することを特徴とする請求項1乃至請求項3いずれか1項記載のNAND型フラッシュメモリ。

【請求項7】

前記リフレッシュコマンドは、コマンドコードとリフレッシュを実行すべき前記リージョン番号からなり、該リフレッシュコマンドを前記ホストの前記インターフェースの端子を介して前記NANDフラッシュメモリのコントローラに送出し、該コントローラが該リージョンを構成する論理ブロックに対応する物理ブロックを、アドレス管理テーブルから割り出しリフレッシュを実行することを特徴とする請求項4記載のNAND型フラッシュメモリのリフレッシュ方法。

【請求項8】

前記リフレッシュコマンドは、コマンドコードとリフレッシュを開始すべき前記NANDフラッシュメモリの論理ブロック番号と論理ブロック数からなり、該リフレッシュコマンドを前記ホストの前記インターフェースの端子を介して前記NANDフラッシュメモリのコントローラに送出し、該コントローラが前記論理ブロック番号に対応する物理ブロック番号をアドレス管理テーブルから割り出しリフレッシュを実行することを特徴とする請求項5記載のNAND型フラッシュメモリのリフレッシュ方法。

【請求項9】

前記リフレッシュコマンドは、コマンドコードと前記ファイルデータを記憶している論理セクターアドレスとセクター長からなり、該リフレッシュコマンドを前記ホストの前記インターフェースの端子を介して前記NANDフラッシュメモリのコントローラに送出し、該コントローラが該論理セクターアドレスに対応する物理ブロックをアドレス管理テーブルから割り出しリフレッシュを実行することを特徴とする請求項6記載のNAND型フラッシュメモリのリフレッシュ方法。

【請求項10】

前記リフレッシュコマンドは、コマンドコードと論理ページアドレスとページ長からなり、該リフレッシュコマンドを前記ホストの前記インターフェースの端子を介して前記NANDフラッシュメモリのコントローラに送出し、該コントローラが該論理ページアドレスに対応する物理ブロックをアドレス管理テーブルから割り出しリフレッシュを実行することを特徴とする請求項1乃至請求項3、若しくは請求項6のいずれか1項記載のNANDフラッシュメモリのリフレッシュ方法。

【請求項11】

ホストからの要求に基づくメディアアクセス実行中にタイマーイベントが発生した場合であって、リフレッシュ対象物理ブロックが複数存在する場合、ファームウエアにより、リフレッシュを、物理ブロック単位で、一定の規則的(regular)なタイムインターバルで実行することを特徴とする請求項3記載のリフレッシュ方法。

【請求項12】

前記インターフェースは、NANDインターフェース、IDEインターフェース、USBインターフェース若しくはメモリインターフェースのいずれかであることを特徴とする請求項1乃至請求項11いずれか1項記載のリフレッシュ方法。

【請求項13】

前記NANDフラッシュメモリと前記コントローラは、ワンパッケージICで構成されていることを特徴とする請求項1乃至請求項12いずれか1項記載のリフレッシュ方法。

【請求項14】

ホストICのNANDインターフェースを介して指定されたアドレスをNANDフラッシュメモリの論理ブロックアドレスとして、該論理ブロックアドレスに対応する物理ブロックに対してデータの書き込みや読み出しを実行するNAND型フラシュメモリデバイスであって、

該NAND型フラッシュメモリデバイスは、NANDフラッシュメモリと、該NANDフラッシュメモリに対し前記ホストICからの指令に基づきデータの書き込みや読み出しを実行するコントローラを具備するワンパッケージICで構成されており、

前記ホストICからの指令に基づき、前記コントローラが、前記NANDフラッシュメモリに記憶されているデータをリフレッシュするように構成されていることを特徴とするNAND型フラシュメモリデバイス。

【請求項1】

ホストが有する所定のインターフェースを介して指定されたアドレスをNANDフラッシュメモリの論理ブロックアドレスとして、該論理ブロックアドレスに対応する物理ブロックに対してデータの書き込みや読み出しを実行するNAND型フラシュメモリデバイスに対し、

前記ホストが、該ホストと前記NAND型フラッシュメモリデバイスとの間で定義されてなるリフレッシュコマンドを前記NAND型フラッシュメモリデバイスに発行し、前記NANDフラッシュメモリに対して前記ホストから指令されたデータの読み出しや書き込みを実行するコントローラに前記リフレッシュコマンドを解釈するコマンド解釈手段を設けておき、該コマンド解釈手段による解釈に基づき前記リフレッシュを実行することを特徴とするNAND型フラッシュメモリのリフレッシュ方法。

【請求項2】

ユーザがシステム電源onの動作をするたびに前記リフレッシュを実行することを特徴とする請求項1記載のNAND型フラッシュメモリのリフレッシュ方法。

【請求項3】

電池内蔵型のシステムにおいて、ユーザのシステム電源on動作の有無に拘わらず、ホストICが有するタイマー機能により、一定時刻若しくは一定時間ごとに前記リフレッシュコマンドを発行して前記リフレッシュを実行することを特徴とする請求項1記載のNAND型フラッシュメモリのリフレッシュ方法。

【請求項4】

リフレッシュは、NANDフラッシュメモリの全論理ブロックアドレスを予め所定の大きさに分割・定義してなるリージョンを1単位として実行することを特徴とする請求項1乃至請求項3いずれか1項記載のNAND型フラッシュメモリのリフレッシュ方法。

【請求項5】

リフレッシュは、論理ブロックを1単位として実行することを特徴とする請求項1乃至請求項3いずれか1項記載のNAND型フラッシュメモリのリフレッシュ方法。

【請求項6】

リフレッシュは、NANDフラッシュメモリに記憶されているファイルを単位として実行することを特徴とする請求項1乃至請求項3いずれか1項記載のNAND型フラッシュメモリ。

【請求項7】

前記リフレッシュコマンドは、コマンドコードとリフレッシュを実行すべき前記リージョン番号からなり、該リフレッシュコマンドを前記ホストの前記インターフェースの端子を介して前記NANDフラッシュメモリのコントローラに送出し、該コントローラが該リージョンを構成する論理ブロックに対応する物理ブロックを、アドレス管理テーブルから割り出しリフレッシュを実行することを特徴とする請求項4記載のNAND型フラッシュメモリのリフレッシュ方法。

【請求項8】

前記リフレッシュコマンドは、コマンドコードとリフレッシュを開始すべき前記NANDフラッシュメモリの論理ブロック番号と論理ブロック数からなり、該リフレッシュコマンドを前記ホストの前記インターフェースの端子を介して前記NANDフラッシュメモリのコントローラに送出し、該コントローラが前記論理ブロック番号に対応する物理ブロック番号をアドレス管理テーブルから割り出しリフレッシュを実行することを特徴とする請求項5記載のNAND型フラッシュメモリのリフレッシュ方法。

【請求項9】

前記リフレッシュコマンドは、コマンドコードと前記ファイルデータを記憶している論理セクターアドレスとセクター長からなり、該リフレッシュコマンドを前記ホストの前記インターフェースの端子を介して前記NANDフラッシュメモリのコントローラに送出し、該コントローラが該論理セクターアドレスに対応する物理ブロックをアドレス管理テーブルから割り出しリフレッシュを実行することを特徴とする請求項6記載のNAND型フラッシュメモリのリフレッシュ方法。

【請求項10】

前記リフレッシュコマンドは、コマンドコードと論理ページアドレスとページ長からなり、該リフレッシュコマンドを前記ホストの前記インターフェースの端子を介して前記NANDフラッシュメモリのコントローラに送出し、該コントローラが該論理ページアドレスに対応する物理ブロックをアドレス管理テーブルから割り出しリフレッシュを実行することを特徴とする請求項1乃至請求項3、若しくは請求項6のいずれか1項記載のNANDフラッシュメモリのリフレッシュ方法。

【請求項11】

ホストからの要求に基づくメディアアクセス実行中にタイマーイベントが発生した場合であって、リフレッシュ対象物理ブロックが複数存在する場合、ファームウエアにより、リフレッシュを、物理ブロック単位で、一定の規則的(regular)なタイムインターバルで実行することを特徴とする請求項3記載のリフレッシュ方法。

【請求項12】

前記インターフェースは、NANDインターフェース、IDEインターフェース、USBインターフェース若しくはメモリインターフェースのいずれかであることを特徴とする請求項1乃至請求項11いずれか1項記載のリフレッシュ方法。

【請求項13】

前記NANDフラッシュメモリと前記コントローラは、ワンパッケージICで構成されていることを特徴とする請求項1乃至請求項12いずれか1項記載のリフレッシュ方法。

【請求項14】

ホストICのNANDインターフェースを介して指定されたアドレスをNANDフラッシュメモリの論理ブロックアドレスとして、該論理ブロックアドレスに対応する物理ブロックに対してデータの書き込みや読み出しを実行するNAND型フラシュメモリデバイスであって、

該NAND型フラッシュメモリデバイスは、NANDフラッシュメモリと、該NANDフラッシュメモリに対し前記ホストICからの指令に基づきデータの書き込みや読み出しを実行するコントローラを具備するワンパッケージICで構成されており、

前記ホストICからの指令に基づき、前記コントローラが、前記NANDフラッシュメモリに記憶されているデータをリフレッシュするように構成されていることを特徴とするNAND型フラシュメモリデバイス。

【図1】

【図2】

【図2】

【公開番号】特開2010−15191(P2010−15191A)

【公開日】平成22年1月21日(2010.1.21)

【国際特許分類】

【出願番号】特願2008−167149(P2008−167149)

【出願日】平成20年6月26日(2008.6.26)

【特許番号】特許第4267682号(P4267682)

【特許公報発行日】平成21年5月27日(2009.5.27)

【出願人】(594096966)株式会社ハギワラシスコム (32)

【Fターム(参考)】

【公開日】平成22年1月21日(2010.1.21)

【国際特許分類】

【出願日】平成20年6月26日(2008.6.26)

【特許番号】特許第4267682号(P4267682)

【特許公報発行日】平成21年5月27日(2009.5.27)

【出願人】(594096966)株式会社ハギワラシスコム (32)

【Fターム(参考)】

[ Back to top ]