OLEDデバイスのための電流駆動型配置の提供

【課題】電流型アクティブマトリックスOLEDを改良すること。

【解決手段】電流型アクティブ・マトリックスOLEDデバイスの製造方法は、基板の上方に、半導体層と、導電層と、その半導体層と導電層の間に挟まれた絶縁層を設け;上記半導体層または上記導電層の上方に有機発光ダイオードを画素ごとに設け;第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、上記半導体層の中に形成されたチャネル領域と、上記導電層の中に形成されたゲートとを備える第1のトランジスタを画素ごとに形成する操作を含んでいる。この方法は、第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第2のトランジスタを画素ごとに形成し;パルス式レーザーを用いて半導体層の特定の領域をアニーリングする操作も含んでいる。

【解決手段】電流型アクティブ・マトリックスOLEDデバイスの製造方法は、基板の上方に、半導体層と、導電層と、その半導体層と導電層の間に挟まれた絶縁層を設け;上記半導体層または上記導電層の上方に有機発光ダイオードを画素ごとに設け;第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、上記半導体層の中に形成されたチャネル領域と、上記導電層の中に形成されたゲートとを備える第1のトランジスタを画素ごとに形成する操作を含んでいる。この方法は、第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第2のトランジスタを画素ごとに形成し;パルス式レーザーを用いて半導体層の特定の領域をアニーリングする操作も含んでいる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、有機エレクトロルミネッセンス・デバイスに関する。より詳細には、本発明は、有機エレクトロルミネッセンス・デバイスのための電流型アクティブ・マトリックス画素回路に関する。

【背景技術】

【0002】

有機エレクトロルミネッセンス(EL)デバイスは、最も簡単な形態では、正孔を注入するためのアノードと、電子を注入するためのカソードと、これら電極の間に挟まれていて、電荷再結合をサポートすることによって光を発生させる有機媒体とで構成されている。このデバイスは、一般に、有機発光ダイオードまたはOLEDとも呼ばれている。基本的な有機EL素子がアメリカ合衆国特許第4,356,429号に記載されている。例えばテレビ、コンピュータのモニタ、携帯電話のディスプレイ、ディジタル・カメラのディスプレイとして有用な画素化されたディスプレイ装置を構成するには、個々の有機EL素子をマトリックス状の画素アレイとして配置するとよい。これらの画素がすべて同じ色の光を出すようにして単色デバイスを製造すること、または赤、緑、青(RGB)デバイスのようにこれらの画素が多数の色を出せるようにすることができる。

【0003】

最も簡単な画素化OLEDデバイスは、パッシブ・マトリックスの構成で駆動される。パッシブ・マトリックスでは、有機EL材料が、直交配置された2組の電極(行と列)の間に挟まれている。パッシブ・マトリックス駆動の有機ELデバイスの一例が、アメリカ合衆国特許第5,276,380号に開示されている。しかし画素化されたデバイスを製造するこの方法にはいくつかの欠点がある。第1に、ある1つの時刻には1つの行(または列)だけが発光する。したがって所定のフレームに平均として望む明るさを実現するには、その行を、平均として望む明るさに行の数を掛けた値に等しい瞬間的な明るさで光らせねばならない。その結果として、フレーム全体を連続的に光らせることのできる画素の場合と比べて電圧がより高くなり、長期の信頼性が低下する。第2に、瞬間的な高電流と長くて狭い電極(したがって抵抗値が大きい)を組み合わせると、デバイスの一端から他端に向かっての電圧低下が顕著になる。デバイスの両端でのこの電圧差は、明るさの一様性に好ましくない影響を与える。これら2つの効果は、ディスプレイのサイズが大きくなるほど、そして行と列の数が増えるほど悪い影響を与えるため、パッシブ・マトリックス型の設計は、比較的小さくて解像度が低いディスプレイに限定される。

【0004】

こうした問題点を解決して性能がより優れたデバイスを製造するため、最近設計されたELEDデバイスは、一般に、アクティブ・マトリックス(AM)回路によって駆動される。アクティブ・マトリックスの構成では、各画素が多数の回路素子(例えばトランジスタ、キャパシタ、信号線)によって駆動される。この回路により、複数の行の画素が同時に光っている状態になるため、各画素に必要とされる明るさのピークが小さくなる。

【0005】

初期のアクティブ・マトリックス型デバイス(例えばアメリカ合衆国特許第5,550,066号、第6,281,634号、第6,456,013号)では、電圧駆動型の画素回路を使用している。電圧駆動型のアクティブ・マトリックス回路は、電圧データ信号を利用して画素の明るさのレベルを制御する。電圧信号は、各画素の中にある1つ以上の駆動用トランジスタによって電流に変換される。駆動用トランジスタは、ソース端子とドレイン端子が有機EL素子と電力接続線(または電力線)の間に電気的に接続されたトランジスタであり、ゲート端子に印加される電圧に応答して有機El素子を流れる電流を調節している。

【0006】

このようなOLEDデバイスは、一般に、大きな基板上に大量生産される。そのとき1枚の基板上にはいくつかのパネルが同時に製造される。したがってトランジスタは、半導体材料(例えばシリコン)からなる薄膜層の中に構成される。シリコンからなる薄膜層の中に構成されるトランジスタは、一般に薄膜トランジスタ(TFT)として知られている。このシリコンは、一般にアモルファス膜として堆積される。シリコンの移動度を大きくするため、シリコンをアニールして多結晶シリコン(ポリシリコンとしても知られる)にすることができる。アニーリングを行なうための一般的な1つの方法は、シリコン層にレーザーを照射するというものである。このようなレーザー・アニーリング法の1つは、エキシマ・レーザー・アニーリング(ELA)として知られている。レーザーでアニーリングした薄膜トランジスタの一例がアメリカ合衆国特許第6,548,867号に記載されている。

【0007】

しかしトランジスタを薄膜として製造する場合には、トランジスタ間の特性の差が大きい。OLEDデバイスでは、有機El素子の明るさは、有機El素子を通過する電流密度によって制御される。画素のトランジスタの特性(例えば移動度、閾値電圧)が変化すると、有機El素子を通過する電流に直接影響が出る可能性があり、すると画素の明るさに影響が及ぶ。OLEDデバイスの一端と他端で差があると、デバイスの明るさまたは色が不均一になる可能性がある。

【0008】

トランジスタ製造プロセスで生じる所定の変動を有するOLEDデバイスで明るさをより一様にするため、新しい設計法が導入されている。それは、電流駆動型アクティブ・マトリックス画素回路である。電流駆動型アクティブ・マトリックス画素回路は、電流データ信号を利用して画素の明るさのレベルを制御する。電流駆動型アクティブ・マトリックス画素回路では、電圧型アクティブ・マトリックス回路で用いられている電圧信号とは異なり、データ信号は電流信号の形態である。

【0009】

電流型アクティブ・マトリックス画素回路の例は、アメリカ合衆国特許第6,501,466号、第6,535,185号、第6,753,654号、アメリカ合衆国特許出願公開2004/0144978 A2に開示されている電流ミラー型画素回路である。電流ミラー型画素では、各画素の第1のトランジスタ(すなわち変換用トランジスタ)に第1の電流を流す電流データ源を利用する。この第1のトランジスタのゲート端子は、第2のトランジスタのゲート端子に電気的に接続されている。第2のトランジスタは、ソース端子またはドレイン端子が有機EL素子に電気的に接続されていて、駆動用トランジスタとして機能する。有機EL素子へのこの電気的接続は、アメリカ合衆国特許第6,501,466号に記載されているように直接行なうこと、またはアメリカ合衆国特許出願公開2004/0144978 A2に記載されているように別のトランジスタを介して間接的に行なうことができる。第1のトランジスタを通じて供給される電流は、第1のトランジスタと第2のトランジスタのゲート端子が互いに接続されていることで第2のトランジスタにも再現されるため、第2の電流が確立する。この第2の電流は、第1の電流と等しくすること、または第1の電流に対してある割合に設定することができる。

【0010】

この電流ミラー設計法を利用することにより、画素間での特性(例えば駆動用トランジスタの閾値電圧や移動度)の違いを厳格に制御する必要性が減る。このようにすると、薄膜トランジスタ製造技術を利用しやすくなり、大面積のデバイスの製造が容易になる。しかし1つの画素内で、駆動用トランジスタと、ゲート端子がその駆動用トランジスタのゲート端子に接続されたトランジスタとの間で特性に差があると、やはり明るさに変動が生じる可能性がある。OLEDデバイスにおけるこの明るさの変動を減らすには、各画素内のこれら2つのトランジスタ間の違いを少なくする必要がある。したがって違いがより少なくなる改善された画素設計法が必要とされている。

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明の1つの目的は、画素の明るさの一様性が改善された電流型アクティブ・マトリックスOLEDデバイスを製造することである。

【課題を解決するための手段】

【0012】

その目的は、電流型アクティブ・マトリックスOLEDデバイスの製造方法であって、

a)基板の上方に半導体層を設け;

b)その基板の上方に導電層を設け;

c)上記半導体層と上記導電層の間に絶縁層を設け;

d)各画素を発光させるため、上記半導体層または上記導電層の上方に有機発光ダイオードを設け;

e)第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、上記半導体層の中に形成されたチャネル領域と、上記導電層の中に形成されたゲートとを備える第1のトランジスタを画素ごとに形成し;

f)上記第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第2のトランジスタを画素ごとに形成し;

g)上記第1のトランジスタと上記第2のトランジスタを形成する前、または形成した後に、供給源から供給されて1個以上のレーザー・パルスを発生させるパルス式レーザーを用いた照射により、上記半導体層のうちで、その第1のトランジスタのチャネル領域の一部に関係する領域と、その第2のトランジスタのチャネル領域の一部に関係する領域をアニーリングする操作を含む方法によって達成される。

【図面の簡単な説明】

【0013】

【図1】電流型アクティブ・マトリックスOLEDデバイスを駆動するための従来の概略回路図である。

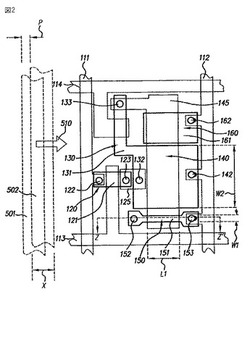

【図2】本発明によるレイアウトの第1の実施態様に従う回路レイアウトを1つの画素について示した図である。

【図3】本発明による図2のOLEDデバイスの線Z-Z'に沿った断面図である。

【図4】本発明によるレイアウトの第2の実施態様に従う概略回路を1つの画素について示した図である。

【図5】本発明によるレイアウトの第2の実施態様に従う回路レイアウトを1つの画素について示した図である。

【図6】本発明によるレイアウトの第3の実施態様に従う概略回路を1つの画素について示した図である。

【図7】本発明によるレイアウトの第3の実施態様に従う回路レイアウトを1つの画素について示した図である。

【発明を実施するための形態】

【0014】

図1は、OLEDデバイスを駆動するための従来の電流型アクティブ・マトリックス回路である。より詳細には、この図は、アクティブ・マトリックス電流ミラー型回路を示している。アメリカ合衆国特許第6,501,466号を参照のこと。この回路は、画素(例えば画素10)が行と列のマトリックス配置にされている。各画素は、デバイス内にあって刺激を受けて独立に発光することのできる1つの領域である。これらの画素は、どれも同じ色の光を出せるようにして単色デバイスを形成すること、または異なる色の光を出せるようにしてマルチカラー・デバイス(例えばRGBデバイス)を形成することができる。それぞれの列には、電流源(例えば電流源170)に接続されたデータ線(例えばデータ線111)が含まれている。この電流源は、画素と同じ基板上に製造すること、またはその基板外に製造してデータ線111に接続することができる。それぞれの列には、電力線(例えば電力線112)も含まれている。あるいは隣り合った画素列が1本の電力線を共有する配置も可能である。さらに別の配置では、電力線をデータ線と垂直にすること、または電力線を行の方向にすることができる。それぞれの行には、第1の走査線(例えば第1の走査線113)と第2の走査線(例えば第2の走査線114)が含まれている。各画素には、4つのトランジスタと、1つのキャパシタと、1つの有機発光ダイオードがさらに含まれている。例えば画素10には、選択用トランジスタ120と、スイッチング用トランジスタ130と、変換用トランジスタ140と、駆動用トランジスタ150と、記憶用キャパシタ160と、有機発光ダイオード230が含まれている。

【0015】

選択用トランジスタ120は、ゲート端子が第1の走査線113に電気的に接続され、ソース端子またはドレイン端子がデータ線111に電気的に接続されている。この選択用トランジスタの機能は、第1の走査線への適切な電圧によってこの選択用トランジスタがオンにされたとき、電流信号の形態で供給されるデータがデータ線から他の回路素子へと移れるようにすることである。そうなることで、駆動用トランジスタを流れる電流、したがって有機発光ダイオードを流れる電流が調節されて、画素の明るさが調節される。選択用トランジスタは、入力トランジスタと呼ぶこともできる。

【0016】

スイッチング用トランジスタ130は、図示してあるように、ゲート端子が第2の走査線114に電気的に接続され、第2の端子が選択用トランジスタ120に電気的に接続され、第3の端子が、記憶用キャパシタ160と、駆動用トランジスタ150のゲート端子と、変換用トランジスタ140のゲート端子に電気的に接続されている。スイッチング用トランジスタの目的は、データ信号が画素に書き込まれているときに駆動用トランジスタおよび変換用トランジスタのゲート端子と記憶用キャパシタに充電して望む明るさにできるようにすることである。これは、第2の走査線を利用してスイッチング用トランジスタのゲート端子に適切な電圧を印加することでこのスイッチング用トランジスタをオンにすることによって実現される。スイッチング用トランジスタは、データ信号が書き込まれると、第2の走査線に適切な電圧を印加することによってオフにされるため、記憶用キャパシタと、変換用トランジスタおよび駆動用トランジスタのゲート端子に貯えられた電圧が分離される。スイッチング用トランジスタは、消去用トランジスタと呼ぶこともできる。

【0017】

変換用トランジスタ140は、ゲート端子が、記憶用キャパシタ160と、駆動用トランジスタ150のゲート端子と、スイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。図示してあるように、この変換用トランジスタの第2の端子は電力線112に電気的に接続され、第3の端子は、選択用トランジスタ120とスイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。変換用トランジスタの目的は、この変換用トランジスタのゲートを駆動用トランジスタのゲートに電気的に接続することにより、データ線から供給される電流を通過させ、その電流が駆動用トランジスタに再現されるようにすることである。変換用トランジスタと駆動用トランジスタの特徴が同じであれば、このミラー電流は、データ線によって供給される電流とほぼ同じになろう。特徴としては、トランジスタのチャネル長、チャネル幅、ゲート絶縁層の厚さなどがある。しかし駆動用トランジスタを流れる電流は、同じではなくて、データ線の電流に対して所定の比の関係になっていることが好ましい。例えばデータ線からより大きな電流が供給されて記憶用キャパシタとそれ以外のキャパシタ(例えば寄生キャパシタ)が素早く充電され、そのことによって画素の明るさを望ましいレベルにするのに必要な時間が短くなるようにすることが好ましい。これは、変換用トランジスタと駆動用トランジスタの1つ以上の特徴(例えばチャネル長、チャネル幅、ゲート絶縁層の厚さ)に関して比を調節することによって実現される。例えば変換用トランジスタのゲート幅が駆動用トランジスタのゲート幅よりも10倍広くされていて、他の特徴は同じだと、有機発光ダイオードが画素の望ましい明るさを実現するのに必要とするよりもほぼ10倍大きな電流を用いて画素データを書き込むことができる。明るさを望ましいレベルに調節し、選択用トランジスタとスイッチング用トランジスタをオフにすると、変換用トランジスタの中を電流が流れなくなるため、変換用トランジスタはもはや電流ミラー機能を果たさなくなる。しかし駆動用トランジスタのゲート端子の電圧は記憶用キャパシタに記憶されていて、しかもその電圧はスイッチング用トランジスタによって分離されているため、変換用トランジスタが必要な電流を供給することで画素は望ましい明るさの光を出し続ける。この状態は、次の画素フレームの間に画素が再び調節されるまで続く。

【0018】

駆動用トランジスタ150は、ゲート端子が、記憶用キャパシタ160と、変換用トランジスタ140のゲート端子と、スイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。図示してあるように、駆動用トランジスタは第2の端子が電力線112に電気的に接続され、第3の端子が有機発光ダイオード230に電気的に接続されている。駆動用トランジスタの目的は、データ線からのデータ信号に応答して有機発光ダイオードの中を流れる電流を調節することである。この場合、調節された電流は、上記のように、変換用トランジスタにより、データ線から供給された電流に対して所定の比になるようにできる。駆動用トランジスタは、電力トランジスタと呼ぶこともできる。

【0019】

各画素(例えば画素10)には、有機発光ダイオード(例えば有機発光ダイオード230)が含まれている。このダイオードは、第1の電極と第2の電極の間に配置された複数の有機発光層からなる。第1の電極は、駆動用トランジスタ150に接続されている。第2の電極250は、すべての画素に共通であることが好ましい。1つ以上の有機発光層を画素ごとに個別にパターニングすること、またはすべての画素に共通にすることができる。

【0020】

第1の走査線113と第2の走査線114を利用してそれぞれ選択用トランジスタ120とスイッチング用トランジスタ130をオンにすると、デバイスのフレームの書き込み期間にデータ線111からのデータ信号に応答して画素の明るさを調節することができる。明るさのレベルが決まると、第1の走査線と第2の走査線を通じ、これら走査線に関係する画素行の選択用トランジスタとスイッチング用トランジスタをオフにする。次に、データ線信号が次の行にとって望ましいレベルに調節された後、その行の第1の走査線と第2の走査線がアクティブにされる。このプロセスが各画素行について繰り返される。この構成では、選択用トランジスタはNMOS型トランジスタとして図示してあり、変換用トランジスタ、駆動用トランジスタ、スイッチング用トランジスタは、PMOS型トランジスタとして図示してある。しかし本発明がこの場合に限定されることはなく、当業者であればこれらトランジスタの型を変更することができる。特に選択用トランジスタとスイッチング用トランジスタの両方がNMOS型トランジスタまたはPMOS型トランジスタにされている別の設計では、1本の走査線が第1の走査線と第2の走査線の両方の機能を果たすことができる。このような設計は、アメリカ合衆国特許第6,535,185号に示してある。

【0021】

図2は、本発明によるレイアウトの第1の実施態様に従う電流型アクティブ・マトリックス回路レイアウトを1つの画素について示した図である。図2には、さまざまな回路素子(例えば選択用トランジスタ120、スイッチング用トランジスタ130、変換用トランジスタ140、駆動用トランジスタ150、記憶用キャパシタ160、データ線111、電力線112、第1の走査線113、第2の走査線114)の構成と配置が示してある。有機発光ダイオード(第1の電極と第2の電極を含む)は、図2には図示されていない。

【0022】

トランジスタ(例えば選択用トランジスタ120、スイッチング用トランジスタ130、変換用トランジスタ140、駆動用トランジスタ150)は、半導体層から形成される。この半導体層はシリコンであることが好ましい。この半導体層は、アモルファス、結晶、多結晶のいずれでもよいが、キャリアの移動度を大きくするため多結晶または結晶であることが好ましい。アモルファス膜の場合、正孔の移動度が非常に小さくてPMOS型トランジスタの実用性はNMOS型よりも劣るため、すべてのトランジスタをNMOS型にする必要がある。多結晶半導体または結晶半導体という好ましい場合には、図1に示したようにNMOS型トランジスタとPMOS型トランジスタの両方を使用することができる。半導体層は、1つ以上のサブ層で構成することができる。そのサブ層は、ドープされていても、真性でもよい。半導体層は、パターニングして複数の領域にする(例えば半導体領域121、半導体領域131、半導体領域151)。これら領域は、従来から知られている方法でパターニング(例えばフォトレジストのフォトリソグラフィ・パターニング)した後、溶液またはプラズマでエッチングする。これら領域またはその一部には、パターニングして複数の領域にする前または後に、選択的にN型またはP型をさらにドープすることができる。これは、公知のドーピング法(例えばイオン注入)を利用して実現される。

【0023】

半導体層を形成する1つの方法は、アモルファス状態の半導体層を堆積させ、その半導体層をレーザーでアニーリングすることによって結晶化させる操作を含んでいる。レーザーによるこの結晶化法は、レーザー・パルスを発生させるレーザー源を用意し、そのレーザー源を基板に対してステップ式に移動させることによって実現できる。このような結晶化法に役立つ多彩なレーザー源が知られている。典型的な1つのレーザー源は、レーザー(例えばXeClレーザー)と、レーザーを整形されたビームにするための一群の光学素子(例えばレンズ)とを備えている。このようなステップ式レーザー・アニーリング法は、アメリカ合衆国特許第6,548,867号に記載されている。レーザー・パルスはパルス幅Xの長方形にされ、ステップ運動がピッチPで起こる。連続したこのような2つのパルスを図2にレーザー・パルス501およびレーザー・パルス502として示してある。レーザー・パルス501とレーザー・パルス502は、レーザーの走査方向510に移動するパルス列のうちでサンプルとして示した2つのパルスである。レーザー・パルス501とレーザー・パルス502の前後に多数のパルス(図示せず)が使用されて、基板上のすべての画素のすべての半導体領域が結晶化する。レーザー・パルスは、1つの画素よりも長いことが好ましい。そのため1つのパルスの全長は図示していない。レーザー・パルスのステップを互いに一部重ね合わせ、半導体層のアニールされた領域が複数のレーザー・パルスを受けるようにすることが好ましい。そのためには、ピッチはレーザー・パルスの幅よりも小さいことが好ましい。レーザーをパルスにして基板を横断して移動させるとき、レーザーのエネルギーが一定に維持されることが好ましいが、それでもいくらかの変動が生じる可能性がある。このような変動は、薄膜トランジスタの性質に影響を与えるであろう。レーザー・エネルギーの変動は、1つのパルス内でパルスの長さに沿って起こる可能性もある。

【0024】

選択用トランジスタ120は、半導体領域121から形成される。選択用トランジスタ120のゲートは、第1の走査線113の一部を、半導体領域121の一部の上方に延長することによって形成される。第1の走査線113と第2の走査線114は、第1の導電体層の中に形成されてパターニングされる。第1の導電体層と半導体層の間には絶縁層(図示せず)が配置されていて、トランジスタのゲート誘電体を形成している。選択用トランジスタ120のソース領域とドレイン領域は、第1の走査線113を延長することによって形成したゲートのどちらかの側の半導体領域121にドーピングすることによって形成できる。

【0025】

データ線111と電力線112は、第2の導電体層から公知の方法を利用して形成されてパターニングされる。第2の導電体層と第1の導電体層の間には別の絶縁層(図示せず)が配置されている。第1の導電体層と第2の導電体層の中に形成された線はこの絶縁層によって電気的接触なしに交差することが可能になるため、画素マトリックスルの行と列を形成できる。選択用トランジスタ120は、半導体領域121とデータ線111の間にある絶縁層内にビア122を形成することによってデータ線111に接続される。このビアは、公知の方法(例えばフォトリソグラフィによるパターニングとエッチング)で形成される。

【0026】

スイッチング用トランジスタ130は、半導体領域131から形成される。スイッチング用トランジスタ130のゲートは、図示したように、第2の走査線114の一部を、半導体領域131の一部の上方に延長することによって形成される。ソース領域とドレイン領域は、このゲート領域のどちらかの側の半導体領域131の一部にドーピングすることによって形成できる。ビア123を通じて半導体領域121に接続されるとともに、ビア132を通じて半導体領域131に接続された導電体ブリッジ125を用いることにより、スイッチング用トランジスタ130と選択用トランジスタ120が接続される。この導電体ブリッジは、例えば第2の導電体層の中に形成することができる。この2つのトランジスタは異なる型(NMOSとPMOS)であるため導電体ブリッジが好ましいが、本発明をうまく実現する上で導電体ブリッジが常に必要とされるわけではない。変換用トランジスタ140も半導体領域131の一部から形成されるため、ここでは変換用トランジスタ140へも接続されている。あるいは別の導電体ブリッジを用いてこのような接続にすることもできる。すると変換用トランジスタを独立した半導体領域として分離することができる。スイッチング用トランジスタ130は、ビア133を通じてゲート導電体145に電気的に接続されている。ゲート導電体145は、記憶用キャパシタ160の一方の側を形成するとともに、変換用トランジスタ140と駆動用トランジスタ150のゲート電極も形成する。このようにして、記憶用キャパシタ160と、変換用トランジスタ140および駆動用トランジスタ150のゲート電極との間に電気的接続が形成される。ゲート導電体145は、選択用トランジスタ120およびスイッチング用トランジスタ130のゲートと同じ層に形成されることが好ましい。すなわちゲート導電体145は、例えば第1の導電体層の中に構成されることが好ましい。

【0027】

記憶用キャパシタ160は、図示してあるように、半導体領域161とゲート導電体145の間に構成されることが好ましい。すなわち記憶用キャパシタは、第1の導電体層と半導体層から形成され、誘電体層(図示せず)がこれらの層の間に配置される。この構成では、半導体領域161はビア162を通じて電力線112に電気的に接続されている。あるいは記憶用キャパシタは、他の層(例えば第1の導電体層、第2の導電体層)から形成することもできる。この別の構成では、キャパシタの一方の側は、電力線の一部を延長することによって形成できるため、電力線に電気的に接続され、ビアを形成する必要がなくなる。

【0028】

上に説明したように、変換用トランジスタ140は半導体領域131から形成され、そのゲートは、ゲート導電体145から形成される。ソース領域とドレイン領域は、ゲート導電体145のどちらかの側で半導体領域131の一部にドーピングすることによって形成できる。図示してあるように、ビア142を通じて変換用トランジスタ140と電力線112が電気的に接続される。

【0029】

駆動用トランジスタ150は半導体領域151から形成され、そのゲートは、ゲート導電体145から形成される。ソース領域とドレイン領域は、ゲート導電体145のどちらかの側で半導体領域151の一部にドーピングすることによって形成できる。図示してあるように、ビア153を通じて駆動用トランジスタ150と電力線112が電気的に接続される。駆動用トランジスタ150も、ビア152を通じて有機発光ダイオードの第1の電極(図示せず)に電気的に接続されている。有機発光ダイオードの第1の電極(図示せず)は、第2の導電体層の上方に配置された第3の導電体層から構成されることが好ましい。第3の導電体層と第2の導電体層は、誘電体層(図示せず)によって分離されている。ビア152はこの誘電体層に形成された開口部であるため、電気的接触が可能になる。

【0030】

各トランジスタは、チャネル領域がゲート端子の下に来るように形成されて、そのトランジスタのソースとドレインを接続する。このチャネル領域は長さと幅を有する。ソース端子とゲート端子の間に印加される電圧差に応答して電流がこのチャネルを流れる。この電流は、チャネルの幅が大きくなるのにほぼ正比例して増加し、チャネルの長さが長くなるのに比例して減少する。トランジスタを飽和領域で作動させると、この電流はほぼ式(1)に従う。

ISD = (1/2)×μ×(W/L)×Cゲート×(VGS - VTH)2 (式1)

ただし、

ISDは、ソース端子とドレイン端子の間を流れる電流であり;

μは、キャリア(電子または正孔)の移動度であり;

Wは、チャネル幅であり;

Lは、チャネル長であり;

Cゲートは、チャネル領域の上方にあるゲートの単位面積当たりの容量であり;

VGSは、ゲート端子とソース端子の電圧差であり;

VTHは、トランジスタの閾値電圧である。

【0031】

有機発光ダイオードを流れる電流は、駆動用トランジスタ150によって調節される。駆動用トランジスタ150は、L1と表記されるチャネル長と、W1と表記されるチャネル幅を有する。同様に、変換用トランジスタ140は、W2と表記されるチャネル幅を持ち、駆動用トランジスタ150と同じチャネル長L1を持つことが図示してある。駆動用トランジスタ150と変換用トランジスタ140を流れる電流は、同じであるか、特定の比となるように設計することができる。

【0032】

ある電流比を実現するには、式1に従って流れる電流を決める1つ以上のパラメータ(例えばチャネル長またはチャネル幅)が、変換用トランジスタと駆動用トランジスタで異なっている必要がある。図2に示してあるように、変換用トランジスタと駆動用トランジスタのチャネル幅は異なる値にできる一方で、チャネル長は同じにされている。この構成では、他のパラメータ(例えば移動度、閾値電圧、チャネル領域の上方にあるゲートの単位面積当たりの容量)を同じにすることが好ましい。したがってこれら2つのトランジスタの半導体領域の性質の差が最小であることが重要である。

【0033】

変換用トランジスタ140と駆動用トランジスタ150の間でチャネル領域の半導体領域の差を小さくするには、半導体層をレーザーを用いてアニーリングするとき、これら2つの領域を同じレーザー・パルスまたはレーザー・パルス列で結晶化させる必要がある。この場合、変換用トランジスタ140と駆動用トランジスタ150のチャネル領域がレーザー・パルスに対してどのように位置するかを決めるにあたり、両方がパルスの長さの中に収まって同時に同じパルス列でアニールされるようにする。変換用トランジスタ140と駆動用トランジスタ150のチャネル領域は、パルス列が走査方向510で示したようにチャネル領域を横断するようにも配置される。このパルス列は、ほぼ同時に両方のチャネル領域に到達し、ほぼ同時に両方のチャネル領域のアニーリングを終了させる。これは、図示したチャネル領域を、例えばチャネル領域の長さまたは幅がレーザー・パルスと直角になるように配置するとともに、チャネル領域が互いにほぼ揃うように配置することによって実現できる。変換用トランジスタ140のチャネル領域と駆動用トランジスタ150のチャネル領域のこの並び方を実現するには、変換用トランジスタ140と駆動用トランジスタ150の長さまたは幅のどちらかを同じにすることが好ましい。図2の実施態様に示してあるように、変換用トランジスタ140と駆動用トランジスタ150のチャネル領域のチャネル長は同じにされている一方で、これら領域のチャネル幅は違えてある。チャネル領域の100%が正確に同じパルス列でアニールされることが好ましいが、これらチャネル領域を、各チャネル領域の少なくとも一部(50%を超えることが好ましい)が同じパルス列によって同時にアニールされるように配置することによってもいくらかの利益がある。さらに、レーザー・パルスのエネルギーの変動に対する感度をレーザー・パルスの長さ方向で小さくするには、図示したように駆動用トランジスタ150と変換用トランジスタ140を互いに近づけて配置することで駆動用トランジスタ150と変換用トランジスタ140のチャネル領域間のスペースを小さくすることが好ましい。

【0034】

図2のデバイスの線Z-Z'に沿った断面図を図3に示してある。この図は、駆動用トランジスタ150の断面図である。駆動用トランジスタ150は基板200の上に形成されている。基板200には多くの材料を使用できる。例えば、ガラス、プラスチック、セラミック、金属ホイルなどである。基板はさらに、1つ以上の障壁層(図示せず)で覆うことができる。基板が導電性である場合には、さらに誘電体層(図示せず)で覆うことができる。デバイスを作動させたときに画素から出る光を基板を通して見るのであれば、基板は透明でなくてはならない。この構成は、ボトム・エミッション型デバイスとして知られている。この場合、基板のための材料として、ガラスまたは透明なプラスチックが好ましい。デバイスを作動させたときに画素から出る光を基板と向かい合った方向から見るのであれば、不透明な基板を使用できる。この構成は、トップ・エミッション型デバイスとして知られている。図3に示した実施態様はトップ・エミッション型デバイスであるが、本発明がこの場合に限定されることはない。

【0035】

基板200の上方には第1の半導体層が設けられており、その半導体層から半導体領域151が形成される。半導体領域151の上方には、第1の誘電体層212が、フォトリソグラフィやエッチングなどの方法によって形成される。この誘電体層は、二酸化ケイ素、窒化ケイ素、またはこれらの組み合わせであることが好ましい。この誘電体層は、誘電性材料からなるいくつかのサブ層から形成することもできる。第1の誘電体層212の上方には第1の導電体層が設けられていて、その導電体層から、フォトリソグラフィやエッチングなどの方法により、ゲート導電体145と第1の走査線113が形成される。この導電体層は、従来技術で知られているように、例えば金属(クロムなど)にすることができる。ゲート導電体145と第1の走査線113の上方には、第2の誘電体層213が形成されている。この誘電体層は、例えば二酸化ケイ素、窒化ケイ素、またはこれらの組み合わせにすることができる。第2の誘電体層213の上方には第2の導電体層が設けられていて、その導電体層から、フォトリソグラフィやエッチングなどの方法により、電力線112が形成される。この導電体層は、従来技術で知られているように、例えば金属(アルミニウム合金など)にすることができる。電力線112は、誘電体層に開けられたビアを通じて半導体領域151と電気的に接触する。第2の導電体層の上方には、第3の誘電体層214が形成されている。

【0036】

第3の誘電体層の上方には、第1の電極260が形成されている。第1の電極260は、トップ・エミッション型デバイスでは反射率が大きいことが好ましい。その場合、第1の電極は金属層(AlまたはAg)にすることができる。あるいは第1の電極は、反射層(例えばAlまたはAg)の上方の多数のサブ層(例えば透明なインジウム-スズ酸化物(ITO))で構成することもできる。あるいは第1の電極を吸光性にすることもできる。このデバイスはトップ・エミッション型デバイスであるため、光はデバイスから基板200と向かい合う方向に出る。したがって第1の電極260を回路素子(例えば駆動用トランジスタ150)の上方に形成することができる。この構成だと、基板の利用可能な表面積が最も効率的に利用される。あるいはボトム・エミッション型デバイスを構成する場合には、第1の電極は透明でなければならず、ITOなどの材料で構成することができる。この場合には、第1の電極は、不透明で基板の方向への発光を阻止する他の回路素子の上方ではない領域に形成せねばならないことにも注意されたい。

【0037】

第1の電極260の上方では、アメリカ合衆国特許第6,246,179号に記載されているような画素間誘電体層220を用いて第1の電極の縁部を覆うことで、この領域で短絡が起こったり強電場が発生したりしないようにすることが好ましい。画素間誘電体層220が好ましいとはいえ、本発明をうまく実現するのに必要というわけではない。

【0038】

各画素は、有機EL媒体240をさらに備えており、その有機EL媒体から有機発光ダイオードが形成される。有機EL媒体240層には本発明をうまく実現できる多数の構成がある。画素間の有機EL媒体をパターニングせずにすむよう、あらゆる画素によって利用される波長の光を出す広帯域光源または白色光源が好ましい。この場合には、マルチカラー・デバイス用として光の通路に画素用のカラー・フィルタ(図示せず)を設け、白色光または広帯域光から望ましい色を出させることができる。広帯域光または白色光を出す有機EL媒体層のいくつかの実施例が、例えばアメリカ合衆国特許第6,696,177号に記載されている。しかし本発明は、各画素がそれぞれの画素用に別々にパターニングされた1つ以上の有機EL媒体層を備えていて、個々の画素が異なる色を出す場合でもうまくいく。有機EL媒体240は、いくつかの層で構成される。それは例えば、正孔注入層241と、正孔注入層241の上方に配置された正孔輸送層242と、正孔輸送層242の上方に配置された発光層243と、発光層243の上方に配置された電子輸送層245である。層の数がより少なかったりより多かったりする有機EL媒体240の別の構成を利用して本発明をうまく実現することもできる。これら有機EL媒体層は、一般に、有機材料からなる。その有機材料は、従来技術で知られているように、小分子材料またはポリマー材料である。これら有機EL媒体層は、公知のいくつかの方法で堆積させることができる。例えば、真空チェンバー内での蒸着、ドナー基板からのレーザー転写、インク・ジェット印刷装置を用いた溶媒からの堆積などの方法がある。

【0039】

有機EL媒体240の上方には、第2の電極250が形成されている。トップ・エミッション型デバイスでは、この電極は非常に透明になっている必要がある。その場合には、導電性かつ透明な材料(例えばインジウム-スズ酸化物(ITO))が、第2の電極250として好ましい。しかしデバイスがボトム・エミッション型デバイスである別の実施態様では、反射性材料(例えばアルミニウム(Al)やマグネシウム銀(MgAg)を用いることができる。

【0040】

有機EL媒体240は、第1の電極260と第2の電極250の間を流れる電流によって刺激されると、光270を出す。図3に示してあるように、光270は、デバイスから基板200とは反対方向に出て行くため、トップ・エミッション型デバイスとして動作する。

【0041】

図4は、OLEDデバイスを駆動するための電流型アクティブ・マトリックス回路である。より詳細には、この図は、本発明によるレイアウトの第2の実施態様に従うアクティブ・マトリックス電流ミラー型回路を示している。レイアウトのこの第2の実施態様では、回路はやはり画素が行と列に配列されたマトリックスの配置にすることができる。図4には1つの画素に関する回路部分が示してあるが、レイアウトの第1の実施態様に関してすでに説明したように、この構成を多数の行と列に拡張することができる。各画素は、デバイスのうちで独立に刺激して発光させることのできる領域である。各列には、電流源(例えば電流源170)に接続されたデータ線(例えばデータ線111)が含まれている。この電流源は、画素と同じ基板上に製造すること、またはその基板外に製造してデータ線111に接続することができる。各列には、電力線(例えば電力線112)も含まれている。あるいは隣り合った画素列が1本の電力線を共有する配置にすることもできる。さらに別の配置では、電力線をデータ線と垂直にすること、または電力線を行の方向にすることができる。それぞれの行には、第1の走査線(例えば第1の走査線113)と第2の走査線(例えば第2の走査線114)が含まれている。各画素には、5つのトランジスタと、1つのキャパシタと、1つの有機発光ダイオードがさらに含まれている。図示した画素には、例えば、選択用トランジスタ120と、スイッチング用トランジスタ130と、第1の変換用トランジスタ140aと、第2の変換用トランジスタ140bと、駆動用トランジスタ150と、記憶用キャパシタ160と、有機発光ダイオード230が含まれている。

【0042】

選択用トランジスタ120は、ゲート端子が第1の走査線113に電気的に接続され、ソース端子またはドレイン端子がデータ線111に電気的に接続されている。この選択用トランジスタの機能は、第1の走査線への適切な電圧によってこの選択用トランジスタがオンにされたとき、電流信号の形態で供給されるデータがデータ線から他の回路素子へと移れるようにすることである。そうなることで、駆動用トランジスタを流れる電流、したがって有機発光ダイオードを流れる電流が調節されて、画素の明るさが調節される。選択用トランジスタは、入力トランジスタと呼ぶこともできる。

【0043】

スイッチング用トランジスタ130は、図示してあるように、ゲート端子が第2の走査線114に電気的に接続され、第2の端子が選択用トランジスタ120に電気的に接続され、第3の端子が、記憶用キャパシタ160と、駆動用トランジスタ150のゲート端子と、第1の変換用トランジスタ140aのゲート端子と、第2の変換用トランジスタ140bのゲート端子に電気的に接続されている。スイッチング用トランジスタの目的は、データ信号が画素に書き込まれているときに駆動用トランジスタおよび変換用トランジスタのゲート端子と記憶用キャパシタに充電して望む明るさにできるようにすることである。これは、第2の走査線を利用してスイッチング用トランジスタのゲート端子に適切な電圧を印加することでこのスイッチング用トランジスタをオンにすることによって実現される。スイッチング用トランジスタは、データ信号が書き込まれると、第2の走査線に適切な電圧を印加することによってオフにされるため、記憶用キャパシタと、変換用トランジスタおよび駆動用トランジスタのゲート端子に貯えられた電圧が分離される。スイッチング用トランジスタは、消去用トランジスタと呼ぶこともできる。

【0044】

レイアウトの第2の実施態様では、レイアウトの第1の実施態様の変換用トランジスタが、第1の変換用トランジスタ140aと第2の変換用トランジスタ140bで置き換えられている。第1の変換用トランジスタ140aと第2の変換用トランジスタ140bは、ソース端子同士とドレイン端子同士が電気的に並列に接続されている。第1の変換用トランジスタ140aと第2の変換用トランジスタ140bのゲート端子同士も電気的に接続されている。このようになっているため、レイアウトのこの第2の実施態様では、第1の変換用トランジスタ140aと第2の変換用トランジスタ140bが合わさって、レイアウトの第1の実施態様の変換用トランジスタの機能を果たす。

【0045】

第1の変換用トランジスタ140aと第2の変換用トランジスタ140bは、図示してあるように、ゲート端子が、記憶用キャパシタ160と、駆動用トランジスタ150のゲート端子と、スイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。第1の変換用トランジスタ140aと第2の変換用トランジスタ140bは、図示してあるように、電力線112と、選択用トランジスタ120と、スイッチング用トランジスタ130にも電気的に接続されている。これら変換用トランジスタの目的は、その変換用トランジスタのゲートを駆動用トランジスタのゲートに電気的に接続することにより、データ線から供給される電流を通過させ、その電流が駆動用トランジスタに再現されるようにすることである。

【0046】

レイアウトの第1の実施態様と同様、変換用トランジスタを通過する電流は、駆動用トランジスタを流れる電流と同じにすること、または駆動用トランジスタを流れる電流に対して所定の比になっているようにすることができる。しかし駆動用トランジスタを流れる電流は、同じではなくて、データ線の電流に対して所定の比の関係になっていることが好ましい。例えばデータ線からより大きな電流が供給されて記憶用キャパシタとそれ以外のキャパシタ(例えば寄生キャパシタ)が素早く充電され、そのことによって画素の明るさを望ましいレベルにするのに必要な時間が短くなるようにすることが好ましい。これは、変換用トランジスタと駆動用トランジスタの1つ以上の特徴(例えばチャネル長、チャネル幅、ゲート絶縁層の厚さ)に関する比を調節することによって実現される。ここでは2つの変換用トランジスタが並列に接続されているため、もしその2つの変換用トランジスタのチャネル幅、チャネル長、ならびに他の特徴が同じであるならば、それぞれの変換用トランジスタが、これら変換用トランジスタを流れる全電流のほぼ半分を担うことになる。あるいはこれら2つの変換用トランジスタの特徴(例えばチャネル幅)を違えることにより、全電流がこれら変換用トランジスタの間で不均等に分配されるようにすることもできる。したがってこれら2つの変換用トランジスタと駆動用トランジスタの間を流れる電流の適切な比を確立する際には、これらの変換用トランジスタを合わせて考えるべきである。例えば第1の変換用トランジスタのゲート幅と第2の変換用トランジスタのゲート幅の両方が駆動用トランジスタのゲート幅よりも5倍広くされていて、他の特徴は同じだと、有機発光ダイオードが画素の望ましい明るさを実現するのに必要とするよりもほぼ10倍大きな電流を用いて画素データを書き込むことができる。明るさを望ましいレベルに調節し、選択用トランジスタとスイッチング用トランジスタをオフにすると、変換用トランジスタの中を電流が流れなくなるため、変換用トランジスタはもはや電流ミラー機能を果たさなくなる。しかし駆動用トランジスタのゲート端子の電圧は記憶用キャパシタに記憶されていて、しかもその電圧はスイッチング用トランジスタによって分離されているため、変換用トランジスタが必要な電流を供給することで画素は望ましい明るさの光を出し続ける。この状態は、次の画素フレームの間に画素が再び調節されるまで続く。

【0047】

駆動用トランジスタ150は、ゲート端子が、記憶用キャパシタ160と、第1の変換用トランジスタ140aのゲート端子と、第2の変換用トランジスタ140bのゲート端子と、スイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。図示してあるように、駆動用トランジスタは、第2の端子が電力線112に電気的に接続され、第3の端子が有機発光ダイオード230に電気的に接続されている。駆動用トランジスタの目的は、データ線からのデータ信号に応答して有機発光ダイオードの中を流れる電流を調節することである。この場合、調節された電流は、上記のように、変換用トランジスタにより、データ線から供給された電流に対して所定の比になるようにできる。駆動用トランジスタは、電力トランジスタと呼ぶこともできる。

【0048】

各画素には、有機発光ダイオード(例えば有機発光ダイオード230)が含まれている。このダイオードは、第1の電極と第2の電極の間に配置された複数の有機発光層からなる。第1の電極は、駆動用トランジスタ150に接続されている。第2の電極250は、すべての画素に共通であることが好ましい。1つ以上の有機発光層を画素ごとに個別にパターニングすること、またはすべての画素に共通にすることができる。

【0049】

第1の走査線113と第2の走査線114を利用してそれぞれ選択用トランジスタ120とスイッチング用トランジスタ130をオンにすると、デバイスのフレームの書き込み期間にデータ線111からのデータ信号に応答して画素の明るさを調節することができる。明るさのレベルが決まると、第1の走査線と第2の走査線を通じ、これら走査線に関係する画素行の選択用トランジスタとスイッチング用トランジスタをオフにする。次に、データ線信号が次の行にとって望ましいレベルに調節された後、その行の第1の走査線と第2の走査線がアクティブにされる。このプロセスが各画素行について繰り返される。この構成では、選択用トランジスタはNMOS型トランジスタとして図示してあり、変換用トランジスタ、駆動用トランジスタ、スイッチング用トランジスタは、PMOS型トランジスタとして図示してある。しかし本発明がこの場合に限定されることはなく、当業者であればこれらトランジスタの型を変更することができる。特に選択用トランジスタとスイッチング用トランジスタの両方がNMOS型トランジスタまたはPMOS型トランジスタにされている別の設計では、1本の走査線が第1の走査線と第2の走査線の両方の機能を果たすことができる。

【0050】

図5は、本発明によるレイアウトの第2の実施態様に従う回路レイアウトを1つの画素について示した図の一例である。図5には、さまざまな回路素子(例えば選択用トランジスタ120、スイッチング用トランジスタ130、第1の変換用トランジスタ140a、第2の変換用トランジスタ140b、駆動用トランジスタ150、記憶用キャパシタ160、データ線111、電力線112、第1の走査線113、第2の走査線114)の構成と配置が示してある。有機発光ダイオード(第1の電極と第2の電極を含む)は、図5には図示されていない。

【0051】

図5に示してあるように、駆動用トランジスタ150は、ゲート導電体145の下方のチャネル領域が幅W1と長さL1を持つように構成されている。第1の変換用トランジスタ140aは、ゲート導電体145の下方のチャネル領域が幅W3と長さL1を持つように構成されている。第2の変換用トランジスタ140bは、ゲート導電体145の下方のチャネル領域が幅W4と長さL1を持つように構成されている。

【0052】

レイアウトのこの第2の実施態様によれば、第1の変換用トランジスタ140aのチャネル領域と第2の変換用トランジスタ140bのチャネル領域は、その間に配置された駆動用トランジスタ150のチャネル領域とは離れている。このレイアウトを実現するには、変換用トランジスタを2つの異なる半導体領域から形成するとよい。例えば第1の変換用トランジスタ140aを半導体領域131aから形成し、第2の変換用トランジスタ140bを半導体領域141bから形成する。第1の変換用トランジスタ140aと、第2の変換用トランジスタ140bと、選択用トランジスタ120と、スイッチング用トランジスタ130の間を、導電体ブリッジ125aを用いて電気的に接続する。この導電体ブリッジ125aは、ビア143aを通じて半導体領域131aに電気的に接続され、ビア143bを通じて半導体領域141bに電気的に接続されている。第1の変換用トランジスタ140aと電力線112がビア142aを通じて電気的に接続される。第2の変換用トランジスタ140bと電力線112がビア142bを通じて電気的に接続される。ゲート導電体145は、第1の変換用トランジスタ140aと、第2の変換用トランジスタ140bと、駆動用トランジスタ150のゲート電極として機能する。

【0053】

本発明によるレイアウトのこの第2の実施態様において第1の変換用トランジスタ140aのチャネル領域と第2の変換用トランジスタ140bのチャネル領域の間に駆動用トランジスタ150のチャネル領域を配置することにより、回路は層(例えば半導体層や、半導体層とゲートの間にある絶縁層)の物理的性質の局所的な変動に対してより強くなる。物理的性質(例えばゲート絶縁体の厚さ、結晶粒子の大きさ)は、トランジスタの電気的性質(例えば閾値電圧、キャリアの移動度)に直接影響を与える。すなわち第1の変換用トランジスタ140aのチャネル領域と第2の変換用トランジスタ140bのチャネル領域の間に駆動用トランジスタ150のチャネル領域を配置することにより、駆動用トランジスタ150の性質が、第1の変換用トランジスタ140aと第2の変換用トランジスタ140bの性質の中間の値に近づく。第1の変換用トランジスタ140aと第2の変換用トランジスタ140bは電気的に並列に接続されていて、ゲート同士も電気的に接続されているため、これらの変換用トランジスタからの全電流、またはその一部は、すでに説明したように、データ信号が画素行に書き込まれるときに駆動用トランジスタ150に再現される。レイアウトのこの第2の実施態様に従って駆動用トランジスタ150が第1の変換用トランジスタ140aと第2の変換用トランジスタ140bのほぼ中間の値を持つように構成することで、このような性質の変動に対する全体的な強さが向上する。

【0054】

すでに説明したようにレーザーでアニールすることによって半導体層を結晶化させる場合には、本発明によるレイアウトの第2の実施態様を実施することによって強さも向上する。しかし本発明によるレイアウトの第2の実施態様がこの場合に限定されることはない。レーザーでアニールすることによって半導体層を結晶化させる場合、レーザー・パルスに変動があると半導体層の性質に影響が及ぶため、レーザー・パルスの変動に対する回路の強さを改善することが望ましい。レーザー・パルス(例えばレーザー・パルス501と502)のエネルギー変動に対する回路の感度を小さくするには、図示してあるように、第1の変換用トランジスタ140aのチャネル領域と、駆動用トランジスタ150のチャネル領域と、第2の変換用トランジスタ140bのチャネル領域をレーザー・パルスと平行に配置することも好ましい。第1の変換用トランジスタ140aのチャネル領域と第2の変換用トランジスタ140bのチャネル領域の間に駆動用トランジスタ150のチャネル領域をこのような平行な関係で配置すると、第1の変換用トランジスタ140aのチャネル領域と第2の変換用トランジスタ140bのチャネル領域が受け取るレーザーのエネルギーのほぼ平均値が駆動用トランジスタ150のチャネル領域に与えられるため、パルスの長さ方向でのレーザーのエネルギー変動に対する強さが向上する。

【0055】

レーザーを利用して半導体層をアニールするときに第1の変換用トランジスタ140aと第2の変換用トランジスタ140bと駆動用トランジスタ150のチャネル領域の半導体領域間の差をさらに小さくするには、その半導体領域を同じ1つのレーザー・パルスまたはレーザー・パルス列で結晶化させる必要がある。その場合、第1の変換用トランジスタ140aのチャネル領域と、第2の変換用トランジスタ140bのチャネル領域と、駆動用トランジスタ150のチャネル領域を、レーザー・パルスに対し、どのチャネル領域も1つのパルス内に収まり、同時に同じパルス列によってアニールされるように配置する。第1の変換用トランジスタ140aのチャネル領域と、第2の変換用トランジスタ140bのチャネル領域と、駆動用トランジスタ150のチャネル領域は、パルス列が走査方向510で示したようにチャネル領域を横断するにつれて、そのパルス列がすべてのチャネル領域にほぼ同時に到達し、ほぼ同時にチャネル領域のアニーリングが終了するようにも配置する。これは、図示したチャネル領域を、例えばチャネル領域の長さまたは幅がレーザー・パルスと直角になるようにするとともに、チャネル領域が互いにほぼ揃うように配置することによって実現できる。第1の変換用トランジスタ140aのチャネル領域と、第2の変換用トランジスタ140bのチャネル領域と、駆動用トランジスタ150のチャネル領域のこの並び方を実現するには、第1の変換用トランジスタ140aと第2の変換用トランジスタ140bと駆動用トランジスタ150の長さまたは幅のどちらかを同じにすることが好ましい。図5の実施態様に示してあるように、第1の変換用トランジスタ140aと第2の変換用トランジスタ140bと駆動用トランジスタ150のチャネル領域のチャネル長は同じにされている一方で、これら領域のチャネル幅は違えてある。チャネル領域が正確に同じパルス列でアニールされることが好ましいが、これらチャネル領域を、各チャネル領域の少なくとも一部(50%を超えることが好ましい)が同じパルス列によって同時にアニールされるように配置することによってもいくらかの利益がある。

【0056】

図6は、OLEDデバイスを駆動するための別の電流型アクティブ・マトリックス回路である。より詳細には、この図は、本発明によるレイアウトの第3の実施態様に従うアクティブ・マトリックス電流ミラー型回路を示している。レイアウトのこの第3の実施態様では、回路はやはり画素が行と列に配列されたマトリックスの配置にすることができる。図6には1つの画素に関する回路部分が示してあるが、レイアウトの第1の実施態様に関してすでに説明したように、この構成を多数の行と列に拡張することができる。各画素は、デバイスのうちで独立に刺激して発光させることのできる領域である。各列には、電流源(例えば電流源170)に接続されたデータ線(例えばデータ線111)が含まれている。この電流源は、画素と同じ基板上に製造すること、またはその基板外に製造してデータ線111に接続することができる。各列には、電力線(例えば電力線112)も含まれている。あるいは隣り合った画素列が1本の電力線を共有する配置にすることもできる。さらに別の配置では、電力線をデータ線と垂直にすること、または電力線を行の方向にすることができる。それぞれの行には、第1の走査線(例えば第1の走査線113)と第2の走査線(例えば第2の走査線114)が含まれている。各画素には、5つのトランジスタと、1つのキャパシタと、1つの有機発光ダイオードがさらに含まれている。図示した画素には、例えば、選択用トランジスタ120と、スイッチング用トランジスタ130と、変換用トランジスタ140と、第1の駆動用トランジスタ150aと、第2の駆動用トランジスタ150bと、記憶用キャパシタ160と、有機発光ダイオード230が含まれている。

【0057】

選択用トランジスタ120は、ゲート端子が第1の走査線113に電気的に接続され、ソース端子またはドレイン端子がデータ線111に電気的に接続されている。この選択用トランジスタの機能は、第1の走査線への適切な電圧によってこの選択用トランジスタがオンにされたとき、電流信号の形態で供給されるデータがデータ線から他の回路素子へと移れるようにすることである。そうなることで、駆動用トランジスタを流れる電流、したがって有機発光ダイオードを流れる電流が調節されて、画素の明るさが調節される。選択用トランジスタは、入力トランジスタと呼ぶこともできる。

【0058】

スイッチング用トランジスタ130は、図示してあるように、ゲート端子が第2の走査線114に電気的に接続され、第2の端子が選択用トランジスタ120に電気的に接続され、第3の端子が、記憶用キャパシタ160と、第1の駆動用トランジスタ150aのゲート端子と、第2の駆動用トランジスタ150bのゲート端子と、変換用トランジスタ140のゲート端子に電気的に接続されている。スイッチング用トランジスタの目的は、データ信号が画素に書き込まれているときに駆動用トランジスタおよび変換用トランジスタのゲート端子と記憶用キャパシタに充電して望む明るさにできるようにすることである。これは、第2の走査線を利用してスイッチング用トランジスタのゲート端子に適切な電圧を印加することでこのスイッチング用トランジスタをオンにすることによって実現される。スイッチング用トランジスタは、データ信号が書き込まれると、第2の走査線に適切な電圧を印加することによってオフにされるため、記憶用キャパシタと、変換用トランジスタおよび駆動用トランジスタのゲート端子に貯えられた電圧が分離される。スイッチング用トランジスタは、消去用トランジスタと呼ぶこともできる。

【0059】

レイアウトの第1の実施態様の駆動用トランジスタは、レイアウトのこの第3の実施態様では、第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bで置き換えられている。第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bは、ソース端子同士とドレイン端子同士が電気的に並列に接続されている。第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bのゲート端子も電気的に接続されている。このようになっているため、レイアウトのこの第3の実施態様では、第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bが合わさって、レイアウトの第1の実施態様の駆動用トランジスタの機能を果たす。

【0060】

第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bは、ゲート端子が記憶用キャパシタ160と、変換用トランジスタのゲート端子と、スイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bは、図示してあるように、第2の端子が電力線112に電気的に接続され、第3の端子が有機発光ダイオード230に電気的に接続されている。これら駆動用トランジスタの目的は、データ線からのデータ信号に応答して有機発光ダイオードの中を流れる電流を調節することである。この場合、調節された電流は、下記のように、変換用トランジスタにより、データ線から供給された電流に対して所定の比になるようにできる。駆動用トランジスタは、電力トランジスタと呼ぶこともできる。

【0061】

変換用トランジスタ140は、ゲート端子が、記憶用キャパシタ160と、第1の駆動用トランジスタ150aおよび第2の駆動用トランジスタ150bのゲート端子と、スイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。図示してあるように、変換用トランジスタの第2の端子は電力線112に電気的に接続され、第3の端子は選択用トランジスタ120とスイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。変換用トランジスタの目的は、この変換用トランジスタのゲートを駆動用トランジスタのゲートに電気的に接続することにより、データ線から供給される電流を通過させ、その電流が駆動用トランジスタに再現されるようにすることである。

【0062】

レイアウトの第1の実施態様と同様、変換用トランジスタを通過する電流は、駆動用トランジスタを流れる電流と同じにすること、または駆動用トランジスタを流れる電流に対して所定の比になっているようにすることができる。しかし駆動用トランジスタを流れる電流は、同じではなくて、データ線の電流に対して所定の比の関係になっていることが好ましい。例えばデータ線からより大きな電流が供給されて記憶用キャパシタとそれ以外のキャパシタ(例えば寄生キャパシタ)が素早く充電され、そのことによって画素の明るさを望ましいレベルにするのに必要な時間が短くなるようにすることが好ましい。これは、変換用トランジスタと駆動用トランジスタの1つ以上の特徴(例えばチャネル長、チャネル幅、ゲート絶縁層の厚さ)に関して比を調節することによって実現される。ここでは2つの駆動用トランジスタが並列に接続されているため、もしその2つの駆動用トランジスタのチャネル幅、チャネル長、ならびに他の特徴が同じであるならば、それぞれの駆動用トランジスタが、これら駆動用トランジスタを流れる全電流のほぼ半分を担うことになる。あるいはこれら2つの駆動用トランジスタの特徴(例えばチャネル幅)を違えることにより、全電流がこれら駆動用トランジスタの間で不均等に分配されるようにすることもできる。したがって変換用トランジスタとこれら2つの駆動用トランジスタの間を流れる電流の適切な比を確立する際には、これらの駆動用トランジスタを合わせて考えるべきである。例えば第1の駆動用トランジスタのゲート幅と第2の駆動用トランジスタのゲート幅の両方が変換用トランジスタのゲート幅よりも5倍広くされていて、他の特徴は同じだと、有機発光ダイオードが画素の望ましい明るさを実現するのに必要とするよりもほぼ10倍大きな電流を用いて画素データを書き込むことができる。明るさを望ましいレベルに調節し、選択用トランジスタとスイッチング用トランジスタをオフにすると、変換用トランジスタの中を電流が流れなくなるため、変換用トランジスタはもはや電流ミラー機能を果たさなくなる。しかし駆動用トランジスタのゲート端子の電圧は記憶用キャパシタに記憶されていてい、しかもその電圧はスイッチング用トランジスタによって分離されているため、変換用トランジスタが必要な電流を供給することで画素は望ましい明るさの光を出し続ける。この状態は、次の画素フレームの間に画素が再び調節されるまで続く。

【0063】

各画素には、有機発光ダイオード(例えば有機発光ダイオード230)が含まれている。このダイオードは、第1の電極と第2の電極の間に配置された複数の有機発光層からなる。第1の電極は、第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bに接続されている。第2の電極250は、すべての画素に共通であることが好ましい。1つ以上の有機発光層を画素ごとに個別にパターニングすること、またはすべての画素に共通にすることができる。

【0064】

第1の走査線113と第2の走査線114を利用してそれぞれ選択用トランジスタ120とスイッチング用トランジスタ130をオンにすると、デバイスのフレームの書き込み期間にデータ線111からのデータ信号に応答して画素の明るさを調節することができる。明るさのレベルが決まると、第1の走査線と第2の走査線を通じ、これら走査線に関係する画素行の選択用トランジスタとスイッチング用トランジスタをオフにする。次に、データ線信号が次の行にとって望ましいレベルに調節された後、その行の第1の走査線と第2の走査線がアクティブにされる。このプロセスが各画素行について繰り返される。この構成では、選択用トランジスタはNMOS型トランジスタとして図示してあり、変換用トランジスタ、駆動用トランジスタ、スイッチング用トランジスタは、PMOS型トランジスタとして図示してある。しかし本発明がこの場合に限定されることはなく、当業者であればこれらトランジスタの型を変更することができる。特に選択用トランジスタとスイッチング用トランジスタの両方がNMOS型トランジスタまたはPMOS型トランジスタにされている別の設計では、1本の走査線が第1の走査線と第2の走査線の両方の機能を果たすことができる。

【0065】

図7は、本発明によるレイアウトの第3の実施態様に従う回路レイアウトを1つの画素について示した図の一例である。図7には、さまざまな回路素子(例えば選択用トランジスタ120、スイッチング用トランジスタ130、変換用トランジスタ140、第1の駆動用トランジスタ150a、第2の駆動用トランジスタ150b、記憶用キャパシタ160、データ線111、電力線112、第1の走査線113、第2の走査線114)の構成と配置が示してある。有機発光ダイオード(第1の電極と第2の電極を含む)は、図7には図示されていない。

【0066】

図7に示してあるように、変換用トランジスタ140は、ゲート導電体145の下方のチャネル領域が幅W2と長さL1を持つように構成されている。第1の駆動用トランジスタ150aは、ゲート導電体145の下方のチャネル領域が幅W5と長さL1を持つように構成されている。第2の駆動用トランジスタ150bは、ゲート導電体145の下方のチャネル領域が幅W6と長さL1を持つように構成されている。

【0067】

レイアウトのこの第3の実施態様によれば、第1の駆動用トランジスタ150aのチャネル領域と第2の駆動用トランジスタ150bのチャネル領域は、その間に配置された変換用トランジスタ140のチャネル領域とは離れている。このレイアウトを実現するには、駆動用トランジスタを2つの異なる半導体領域から形成するとよい。例えば第1の駆動用トランジスタ150aを半導体領域151aから形成し、第2の駆動用トランジスタ150bを半導体領域151bから形成する。第1の駆動用トランジスタ150aと電力線112をビア153aを通じて電気的に接続する。第2の駆動用トランジスタ150bと電力線112をビア153bを通じて電気的に接続する。第1の駆動用トランジスタ150bと有機発光ダイオード(図示せず)の第1の電極をビア152aを通じて電気的に接続する。第2の駆動用トランジスタ150bと有機発光ダイオード(図示せず)の第1の電極をビア152bを通じて電気的に接続する。ゲート導電体145は、第1の駆動用トランジスタ150aと、第2の駆動用トランジスタ150bと、変換用トランジスタ140のゲート電極として機能する。

【0068】

本発明によるレイアウトのこの第3の実施態様に従って第1の駆動用トランジスタ150aのチャネル領域と第2の駆動用トランジスタ150bのチャネル領域の間に変換用トランジスタ140のチャネル領域を配置することにより、回路は層(例えば半導体層や、半導体層とゲートの間にある絶縁層)の物理的性質の局所的な変動に対してより強くなる。物理的性質(例えばゲート絶縁体の厚さ、結晶粒子の大きさ)は、トランジスタの電気的性質(例えば閾値電圧、キャリアの移動度)に直接影響を与える。すなわち第1の駆動用トランジスタ150aのチャネル領域と第2の駆動用トランジスタ150bのチャネル領域の間に変換用トランジスタ140のチャネル領域を配置することにより、変換用トランジスタ140の性質が、第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bの性質の中間の値に近づく。第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bは電気的に並列に接続されていて、ゲート同士も電気的に接続されているため、これらの変換用トランジスタからの電流、またはその一部は、すでに説明したように、データ信号が画素行に書き込まれるときにこれら駆動用トランジスタに再現されて分割される。レイアウトのこの第3の実施態様に従って変換用トランジスタ140が第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bのほぼ中間の値を持つように構成することで、このような性質の変動に対する全体的な強さが向上する。

【0069】

すでに説明したようにレーザーでアニールすることによって半導体層を結晶化させる場合には、本発明によるレイアウトの第3の実施態様を実施することによって強さも向上する。しかし本発明によるレイアウトの第3の実施態様がこの場合に限定されることはない。レーザーでアニールすることによって半導体層を結晶化させる場合、レーザー・パルスに変動があると半導体層の性質に影響が及ぶため、レーザー・パルスの変動に対する回路の強さを改善することが望ましい。レーザー・パルス(例えばレーザー・パルス501と502)のエネルギー変動に対する回路の感度を小さくするには、図示してあるように、第1の駆動用トランジスタ150aのチャネル領域と、変換用トランジスタ140のチャネル領域と、第2の駆動用トランジスタ150bのチャネル領域をレーザー・パルスと平行に配置することも好ましい。第1の駆動用トランジスタ150aのチャネル領域と第2の駆動用トランジスタ150bのチャネル領域の間に変換用トランジスタ140のチャネル領域をこのような平行な関係で配置すると、第1の駆動用トランジスタ150aのチャネル領域と第2の駆動用トランジスタ150bのチャネル領域が受け取るレーザーのエネルギーのほぼ平均値が変換用トランジスタ140のチャネル領域に与えられるため、パルスの長さ方向でのレーザーのエネルギー変動に対する強さが向上する。

【0070】

レーザーを利用して半導体層をアニールするときに第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bと変換用トランジスタ140のチャネル領域の半導体領域間の差をさらに小さくするには、その半導体領域を同じ1つのレーザー・パルスまたはレーザー・パルス列で結晶化させる必要がある。その場合、第1の駆動用トランジスタ150aのチャネル領域と、第2の駆動用トランジスタ150bのチャネル領域と、変換用トランジスタ140のチャネル領域を、レーザー・パルスに対し、どのチャネル領域も1つのパルス内に収まり、同時に同じパルス列によってアニールされるように配置する。変換用トランジスタ140のチャネル領域と、第1の駆動用トランジスタ150aのチャネル領域と、第2の駆動用トランジスタ150bのチャネル領域は、パルス列が走査方向510で示したようにチャネル領域を横断するにつれて、そのパルス列がすべてのチャネル領域にほぼ同時に到達し、ほぼ同時にチャネル領域のアニーリングが終了するようにも配置する。これは、図示したチャネル領域を、例えばチャネル領域の長さまたは幅がレーザー・パルスと直角になるように配置するとともに、チャネル領域が互いにほぼ揃うように配置することによって実現できる。第1の駆動用トランジスタ150aのチャネル領域と、第2の駆動用トランジスタ150bのチャネル領域と、変換用トランジスタ140のチャネル領域のこの並び方を実現するには、第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bと変換用トランジスタ140の長さまたは幅のどちらかを同じにすることが好ましい。図7の実施態様に示してあるように、第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bと変換用トランジスタ140のチャネル領域のチャネル長は同じにされている一方で、これら領域のチャネル幅は違えてある。チャネル領域が正確に同じパルス列でアニールされることが好ましいが、これらチャネル領域を、各チャネル領域の少なくとも一部(50%を超えることが好ましい)が同じパルス列によって同時にアニールされるように配置することによってもいくらかの利益がある。

【0071】

レイアウトの第2の実施態様に関する説明は、2つの変換用トランジスタの間に駆動用トランジスタが配置された場合であった。当業者であれば、この考え方を、3つ以上の変換用トランジスタがあって、その変換用トランジスタのうちの少なくとも2つの間に少なくとも1つの駆動用トランジスタが配置されている場合に拡張することができよう。このような実施態様も、本発明の範囲に含まれると考えられる。レイアウトの第3の実施態様に関する説明は、2つの駆動用トランジスタの間に変換用トランジスタが配置された場合であった。当業者であれば、この考え方を、3つ以上の駆動用トランジスタがあって、その駆動用トランジスタのうちの少なくとも2つの間に少なくとも1つの変換用トランジスタが配置されている場合に拡張することができよう。このような実施態様も、本発明の範囲に含まれると考えられる。当業者であれば、2つ以上の駆動用トランジスタと2つ以上の変換用トランジスタの組み合わせも利用できる。このような組み合わせも、本発明の範囲に含まれると考えられる。上記の構成のどれを利用しても、トランジスタ間の特性の差に対してより強くすることができる。

【符号の説明】

【0072】

10 画素

111 データ線

112 電力線

113 第1の走査線

114 第2の走査線

120 選択用トランジスタ

121 半導体領域

122 ビア

123 ビア

125 導電体ブリッジ

125a 導電体ブリッジ

130 スイッチング用トランジスタ

131 半導体領域

131a 半導体領域

132 ビア

133 ビア

140 変換用トランジスタ

140a 第1の変換用トランジスタ

140b 第2の変換用トランジスタ

141b 半導体領域

142 ビア

142a ビア

142b ビア

143a ビア

143b ビア

145 ゲート導電体

150 駆動用トランジスタ

150a 第1の駆動用トランジスタ

150b 第2の駆動用トランジスタ

151 半導体領域

151a 半導体領域

151b 半導体領域

152 ビア

152a ビア

152b ビア

153 ビア

153a ビア

153b ビア

160 記憶用キャパシタ

161 半導体領域

162 ビア

170 電流源

200 基板

212 第1の誘電体層

213 第2の誘電体層

214 第3の誘電体層

230 有機発光ダイオード

240 有機EL媒体

241 正孔注入層

242 正孔輸送層

243 発光層

245 電子輸送層

250 第2の電極

260 第1の電極

270 光

501 レーザー・パルス

502 レーザー・パルス

510 レーザーの走査方向

【技術分野】

【0001】

本発明は、有機エレクトロルミネッセンス・デバイスに関する。より詳細には、本発明は、有機エレクトロルミネッセンス・デバイスのための電流型アクティブ・マトリックス画素回路に関する。

【背景技術】

【0002】

有機エレクトロルミネッセンス(EL)デバイスは、最も簡単な形態では、正孔を注入するためのアノードと、電子を注入するためのカソードと、これら電極の間に挟まれていて、電荷再結合をサポートすることによって光を発生させる有機媒体とで構成されている。このデバイスは、一般に、有機発光ダイオードまたはOLEDとも呼ばれている。基本的な有機EL素子がアメリカ合衆国特許第4,356,429号に記載されている。例えばテレビ、コンピュータのモニタ、携帯電話のディスプレイ、ディジタル・カメラのディスプレイとして有用な画素化されたディスプレイ装置を構成するには、個々の有機EL素子をマトリックス状の画素アレイとして配置するとよい。これらの画素がすべて同じ色の光を出すようにして単色デバイスを製造すること、または赤、緑、青(RGB)デバイスのようにこれらの画素が多数の色を出せるようにすることができる。

【0003】

最も簡単な画素化OLEDデバイスは、パッシブ・マトリックスの構成で駆動される。パッシブ・マトリックスでは、有機EL材料が、直交配置された2組の電極(行と列)の間に挟まれている。パッシブ・マトリックス駆動の有機ELデバイスの一例が、アメリカ合衆国特許第5,276,380号に開示されている。しかし画素化されたデバイスを製造するこの方法にはいくつかの欠点がある。第1に、ある1つの時刻には1つの行(または列)だけが発光する。したがって所定のフレームに平均として望む明るさを実現するには、その行を、平均として望む明るさに行の数を掛けた値に等しい瞬間的な明るさで光らせねばならない。その結果として、フレーム全体を連続的に光らせることのできる画素の場合と比べて電圧がより高くなり、長期の信頼性が低下する。第2に、瞬間的な高電流と長くて狭い電極(したがって抵抗値が大きい)を組み合わせると、デバイスの一端から他端に向かっての電圧低下が顕著になる。デバイスの両端でのこの電圧差は、明るさの一様性に好ましくない影響を与える。これら2つの効果は、ディスプレイのサイズが大きくなるほど、そして行と列の数が増えるほど悪い影響を与えるため、パッシブ・マトリックス型の設計は、比較的小さくて解像度が低いディスプレイに限定される。

【0004】

こうした問題点を解決して性能がより優れたデバイスを製造するため、最近設計されたELEDデバイスは、一般に、アクティブ・マトリックス(AM)回路によって駆動される。アクティブ・マトリックスの構成では、各画素が多数の回路素子(例えばトランジスタ、キャパシタ、信号線)によって駆動される。この回路により、複数の行の画素が同時に光っている状態になるため、各画素に必要とされる明るさのピークが小さくなる。

【0005】

初期のアクティブ・マトリックス型デバイス(例えばアメリカ合衆国特許第5,550,066号、第6,281,634号、第6,456,013号)では、電圧駆動型の画素回路を使用している。電圧駆動型のアクティブ・マトリックス回路は、電圧データ信号を利用して画素の明るさのレベルを制御する。電圧信号は、各画素の中にある1つ以上の駆動用トランジスタによって電流に変換される。駆動用トランジスタは、ソース端子とドレイン端子が有機EL素子と電力接続線(または電力線)の間に電気的に接続されたトランジスタであり、ゲート端子に印加される電圧に応答して有機El素子を流れる電流を調節している。

【0006】

このようなOLEDデバイスは、一般に、大きな基板上に大量生産される。そのとき1枚の基板上にはいくつかのパネルが同時に製造される。したがってトランジスタは、半導体材料(例えばシリコン)からなる薄膜層の中に構成される。シリコンからなる薄膜層の中に構成されるトランジスタは、一般に薄膜トランジスタ(TFT)として知られている。このシリコンは、一般にアモルファス膜として堆積される。シリコンの移動度を大きくするため、シリコンをアニールして多結晶シリコン(ポリシリコンとしても知られる)にすることができる。アニーリングを行なうための一般的な1つの方法は、シリコン層にレーザーを照射するというものである。このようなレーザー・アニーリング法の1つは、エキシマ・レーザー・アニーリング(ELA)として知られている。レーザーでアニーリングした薄膜トランジスタの一例がアメリカ合衆国特許第6,548,867号に記載されている。

【0007】

しかしトランジスタを薄膜として製造する場合には、トランジスタ間の特性の差が大きい。OLEDデバイスでは、有機El素子の明るさは、有機El素子を通過する電流密度によって制御される。画素のトランジスタの特性(例えば移動度、閾値電圧)が変化すると、有機El素子を通過する電流に直接影響が出る可能性があり、すると画素の明るさに影響が及ぶ。OLEDデバイスの一端と他端で差があると、デバイスの明るさまたは色が不均一になる可能性がある。

【0008】

トランジスタ製造プロセスで生じる所定の変動を有するOLEDデバイスで明るさをより一様にするため、新しい設計法が導入されている。それは、電流駆動型アクティブ・マトリックス画素回路である。電流駆動型アクティブ・マトリックス画素回路は、電流データ信号を利用して画素の明るさのレベルを制御する。電流駆動型アクティブ・マトリックス画素回路では、電圧型アクティブ・マトリックス回路で用いられている電圧信号とは異なり、データ信号は電流信号の形態である。

【0009】

電流型アクティブ・マトリックス画素回路の例は、アメリカ合衆国特許第6,501,466号、第6,535,185号、第6,753,654号、アメリカ合衆国特許出願公開2004/0144978 A2に開示されている電流ミラー型画素回路である。電流ミラー型画素では、各画素の第1のトランジスタ(すなわち変換用トランジスタ)に第1の電流を流す電流データ源を利用する。この第1のトランジスタのゲート端子は、第2のトランジスタのゲート端子に電気的に接続されている。第2のトランジスタは、ソース端子またはドレイン端子が有機EL素子に電気的に接続されていて、駆動用トランジスタとして機能する。有機EL素子へのこの電気的接続は、アメリカ合衆国特許第6,501,466号に記載されているように直接行なうこと、またはアメリカ合衆国特許出願公開2004/0144978 A2に記載されているように別のトランジスタを介して間接的に行なうことができる。第1のトランジスタを通じて供給される電流は、第1のトランジスタと第2のトランジスタのゲート端子が互いに接続されていることで第2のトランジスタにも再現されるため、第2の電流が確立する。この第2の電流は、第1の電流と等しくすること、または第1の電流に対してある割合に設定することができる。

【0010】

この電流ミラー設計法を利用することにより、画素間での特性(例えば駆動用トランジスタの閾値電圧や移動度)の違いを厳格に制御する必要性が減る。このようにすると、薄膜トランジスタ製造技術を利用しやすくなり、大面積のデバイスの製造が容易になる。しかし1つの画素内で、駆動用トランジスタと、ゲート端子がその駆動用トランジスタのゲート端子に接続されたトランジスタとの間で特性に差があると、やはり明るさに変動が生じる可能性がある。OLEDデバイスにおけるこの明るさの変動を減らすには、各画素内のこれら2つのトランジスタ間の違いを少なくする必要がある。したがって違いがより少なくなる改善された画素設計法が必要とされている。

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明の1つの目的は、画素の明るさの一様性が改善された電流型アクティブ・マトリックスOLEDデバイスを製造することである。

【課題を解決するための手段】

【0012】

その目的は、電流型アクティブ・マトリックスOLEDデバイスの製造方法であって、

a)基板の上方に半導体層を設け;

b)その基板の上方に導電層を設け;

c)上記半導体層と上記導電層の間に絶縁層を設け;

d)各画素を発光させるため、上記半導体層または上記導電層の上方に有機発光ダイオードを設け;

e)第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、上記半導体層の中に形成されたチャネル領域と、上記導電層の中に形成されたゲートとを備える第1のトランジスタを画素ごとに形成し;

f)上記第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第2のトランジスタを画素ごとに形成し;

g)上記第1のトランジスタと上記第2のトランジスタを形成する前、または形成した後に、供給源から供給されて1個以上のレーザー・パルスを発生させるパルス式レーザーを用いた照射により、上記半導体層のうちで、その第1のトランジスタのチャネル領域の一部に関係する領域と、その第2のトランジスタのチャネル領域の一部に関係する領域をアニーリングする操作を含む方法によって達成される。

【図面の簡単な説明】

【0013】

【図1】電流型アクティブ・マトリックスOLEDデバイスを駆動するための従来の概略回路図である。

【図2】本発明によるレイアウトの第1の実施態様に従う回路レイアウトを1つの画素について示した図である。

【図3】本発明による図2のOLEDデバイスの線Z-Z'に沿った断面図である。

【図4】本発明によるレイアウトの第2の実施態様に従う概略回路を1つの画素について示した図である。

【図5】本発明によるレイアウトの第2の実施態様に従う回路レイアウトを1つの画素について示した図である。

【図6】本発明によるレイアウトの第3の実施態様に従う概略回路を1つの画素について示した図である。

【図7】本発明によるレイアウトの第3の実施態様に従う回路レイアウトを1つの画素について示した図である。

【発明を実施するための形態】

【0014】

図1は、OLEDデバイスを駆動するための従来の電流型アクティブ・マトリックス回路である。より詳細には、この図は、アクティブ・マトリックス電流ミラー型回路を示している。アメリカ合衆国特許第6,501,466号を参照のこと。この回路は、画素(例えば画素10)が行と列のマトリックス配置にされている。各画素は、デバイス内にあって刺激を受けて独立に発光することのできる1つの領域である。これらの画素は、どれも同じ色の光を出せるようにして単色デバイスを形成すること、または異なる色の光を出せるようにしてマルチカラー・デバイス(例えばRGBデバイス)を形成することができる。それぞれの列には、電流源(例えば電流源170)に接続されたデータ線(例えばデータ線111)が含まれている。この電流源は、画素と同じ基板上に製造すること、またはその基板外に製造してデータ線111に接続することができる。それぞれの列には、電力線(例えば電力線112)も含まれている。あるいは隣り合った画素列が1本の電力線を共有する配置も可能である。さらに別の配置では、電力線をデータ線と垂直にすること、または電力線を行の方向にすることができる。それぞれの行には、第1の走査線(例えば第1の走査線113)と第2の走査線(例えば第2の走査線114)が含まれている。各画素には、4つのトランジスタと、1つのキャパシタと、1つの有機発光ダイオードがさらに含まれている。例えば画素10には、選択用トランジスタ120と、スイッチング用トランジスタ130と、変換用トランジスタ140と、駆動用トランジスタ150と、記憶用キャパシタ160と、有機発光ダイオード230が含まれている。

【0015】

選択用トランジスタ120は、ゲート端子が第1の走査線113に電気的に接続され、ソース端子またはドレイン端子がデータ線111に電気的に接続されている。この選択用トランジスタの機能は、第1の走査線への適切な電圧によってこの選択用トランジスタがオンにされたとき、電流信号の形態で供給されるデータがデータ線から他の回路素子へと移れるようにすることである。そうなることで、駆動用トランジスタを流れる電流、したがって有機発光ダイオードを流れる電流が調節されて、画素の明るさが調節される。選択用トランジスタは、入力トランジスタと呼ぶこともできる。

【0016】

スイッチング用トランジスタ130は、図示してあるように、ゲート端子が第2の走査線114に電気的に接続され、第2の端子が選択用トランジスタ120に電気的に接続され、第3の端子が、記憶用キャパシタ160と、駆動用トランジスタ150のゲート端子と、変換用トランジスタ140のゲート端子に電気的に接続されている。スイッチング用トランジスタの目的は、データ信号が画素に書き込まれているときに駆動用トランジスタおよび変換用トランジスタのゲート端子と記憶用キャパシタに充電して望む明るさにできるようにすることである。これは、第2の走査線を利用してスイッチング用トランジスタのゲート端子に適切な電圧を印加することでこのスイッチング用トランジスタをオンにすることによって実現される。スイッチング用トランジスタは、データ信号が書き込まれると、第2の走査線に適切な電圧を印加することによってオフにされるため、記憶用キャパシタと、変換用トランジスタおよび駆動用トランジスタのゲート端子に貯えられた電圧が分離される。スイッチング用トランジスタは、消去用トランジスタと呼ぶこともできる。

【0017】

変換用トランジスタ140は、ゲート端子が、記憶用キャパシタ160と、駆動用トランジスタ150のゲート端子と、スイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。図示してあるように、この変換用トランジスタの第2の端子は電力線112に電気的に接続され、第3の端子は、選択用トランジスタ120とスイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。変換用トランジスタの目的は、この変換用トランジスタのゲートを駆動用トランジスタのゲートに電気的に接続することにより、データ線から供給される電流を通過させ、その電流が駆動用トランジスタに再現されるようにすることである。変換用トランジスタと駆動用トランジスタの特徴が同じであれば、このミラー電流は、データ線によって供給される電流とほぼ同じになろう。特徴としては、トランジスタのチャネル長、チャネル幅、ゲート絶縁層の厚さなどがある。しかし駆動用トランジスタを流れる電流は、同じではなくて、データ線の電流に対して所定の比の関係になっていることが好ましい。例えばデータ線からより大きな電流が供給されて記憶用キャパシタとそれ以外のキャパシタ(例えば寄生キャパシタ)が素早く充電され、そのことによって画素の明るさを望ましいレベルにするのに必要な時間が短くなるようにすることが好ましい。これは、変換用トランジスタと駆動用トランジスタの1つ以上の特徴(例えばチャネル長、チャネル幅、ゲート絶縁層の厚さ)に関して比を調節することによって実現される。例えば変換用トランジスタのゲート幅が駆動用トランジスタのゲート幅よりも10倍広くされていて、他の特徴は同じだと、有機発光ダイオードが画素の望ましい明るさを実現するのに必要とするよりもほぼ10倍大きな電流を用いて画素データを書き込むことができる。明るさを望ましいレベルに調節し、選択用トランジスタとスイッチング用トランジスタをオフにすると、変換用トランジスタの中を電流が流れなくなるため、変換用トランジスタはもはや電流ミラー機能を果たさなくなる。しかし駆動用トランジスタのゲート端子の電圧は記憶用キャパシタに記憶されていて、しかもその電圧はスイッチング用トランジスタによって分離されているため、変換用トランジスタが必要な電流を供給することで画素は望ましい明るさの光を出し続ける。この状態は、次の画素フレームの間に画素が再び調節されるまで続く。

【0018】

駆動用トランジスタ150は、ゲート端子が、記憶用キャパシタ160と、変換用トランジスタ140のゲート端子と、スイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。図示してあるように、駆動用トランジスタは第2の端子が電力線112に電気的に接続され、第3の端子が有機発光ダイオード230に電気的に接続されている。駆動用トランジスタの目的は、データ線からのデータ信号に応答して有機発光ダイオードの中を流れる電流を調節することである。この場合、調節された電流は、上記のように、変換用トランジスタにより、データ線から供給された電流に対して所定の比になるようにできる。駆動用トランジスタは、電力トランジスタと呼ぶこともできる。

【0019】

各画素(例えば画素10)には、有機発光ダイオード(例えば有機発光ダイオード230)が含まれている。このダイオードは、第1の電極と第2の電極の間に配置された複数の有機発光層からなる。第1の電極は、駆動用トランジスタ150に接続されている。第2の電極250は、すべての画素に共通であることが好ましい。1つ以上の有機発光層を画素ごとに個別にパターニングすること、またはすべての画素に共通にすることができる。

【0020】

第1の走査線113と第2の走査線114を利用してそれぞれ選択用トランジスタ120とスイッチング用トランジスタ130をオンにすると、デバイスのフレームの書き込み期間にデータ線111からのデータ信号に応答して画素の明るさを調節することができる。明るさのレベルが決まると、第1の走査線と第2の走査線を通じ、これら走査線に関係する画素行の選択用トランジスタとスイッチング用トランジスタをオフにする。次に、データ線信号が次の行にとって望ましいレベルに調節された後、その行の第1の走査線と第2の走査線がアクティブにされる。このプロセスが各画素行について繰り返される。この構成では、選択用トランジスタはNMOS型トランジスタとして図示してあり、変換用トランジスタ、駆動用トランジスタ、スイッチング用トランジスタは、PMOS型トランジスタとして図示してある。しかし本発明がこの場合に限定されることはなく、当業者であればこれらトランジスタの型を変更することができる。特に選択用トランジスタとスイッチング用トランジスタの両方がNMOS型トランジスタまたはPMOS型トランジスタにされている別の設計では、1本の走査線が第1の走査線と第2の走査線の両方の機能を果たすことができる。このような設計は、アメリカ合衆国特許第6,535,185号に示してある。

【0021】

図2は、本発明によるレイアウトの第1の実施態様に従う電流型アクティブ・マトリックス回路レイアウトを1つの画素について示した図である。図2には、さまざまな回路素子(例えば選択用トランジスタ120、スイッチング用トランジスタ130、変換用トランジスタ140、駆動用トランジスタ150、記憶用キャパシタ160、データ線111、電力線112、第1の走査線113、第2の走査線114)の構成と配置が示してある。有機発光ダイオード(第1の電極と第2の電極を含む)は、図2には図示されていない。

【0022】

トランジスタ(例えば選択用トランジスタ120、スイッチング用トランジスタ130、変換用トランジスタ140、駆動用トランジスタ150)は、半導体層から形成される。この半導体層はシリコンであることが好ましい。この半導体層は、アモルファス、結晶、多結晶のいずれでもよいが、キャリアの移動度を大きくするため多結晶または結晶であることが好ましい。アモルファス膜の場合、正孔の移動度が非常に小さくてPMOS型トランジスタの実用性はNMOS型よりも劣るため、すべてのトランジスタをNMOS型にする必要がある。多結晶半導体または結晶半導体という好ましい場合には、図1に示したようにNMOS型トランジスタとPMOS型トランジスタの両方を使用することができる。半導体層は、1つ以上のサブ層で構成することができる。そのサブ層は、ドープされていても、真性でもよい。半導体層は、パターニングして複数の領域にする(例えば半導体領域121、半導体領域131、半導体領域151)。これら領域は、従来から知られている方法でパターニング(例えばフォトレジストのフォトリソグラフィ・パターニング)した後、溶液またはプラズマでエッチングする。これら領域またはその一部には、パターニングして複数の領域にする前または後に、選択的にN型またはP型をさらにドープすることができる。これは、公知のドーピング法(例えばイオン注入)を利用して実現される。

【0023】

半導体層を形成する1つの方法は、アモルファス状態の半導体層を堆積させ、その半導体層をレーザーでアニーリングすることによって結晶化させる操作を含んでいる。レーザーによるこの結晶化法は、レーザー・パルスを発生させるレーザー源を用意し、そのレーザー源を基板に対してステップ式に移動させることによって実現できる。このような結晶化法に役立つ多彩なレーザー源が知られている。典型的な1つのレーザー源は、レーザー(例えばXeClレーザー)と、レーザーを整形されたビームにするための一群の光学素子(例えばレンズ)とを備えている。このようなステップ式レーザー・アニーリング法は、アメリカ合衆国特許第6,548,867号に記載されている。レーザー・パルスはパルス幅Xの長方形にされ、ステップ運動がピッチPで起こる。連続したこのような2つのパルスを図2にレーザー・パルス501およびレーザー・パルス502として示してある。レーザー・パルス501とレーザー・パルス502は、レーザーの走査方向510に移動するパルス列のうちでサンプルとして示した2つのパルスである。レーザー・パルス501とレーザー・パルス502の前後に多数のパルス(図示せず)が使用されて、基板上のすべての画素のすべての半導体領域が結晶化する。レーザー・パルスは、1つの画素よりも長いことが好ましい。そのため1つのパルスの全長は図示していない。レーザー・パルスのステップを互いに一部重ね合わせ、半導体層のアニールされた領域が複数のレーザー・パルスを受けるようにすることが好ましい。そのためには、ピッチはレーザー・パルスの幅よりも小さいことが好ましい。レーザーをパルスにして基板を横断して移動させるとき、レーザーのエネルギーが一定に維持されることが好ましいが、それでもいくらかの変動が生じる可能性がある。このような変動は、薄膜トランジスタの性質に影響を与えるであろう。レーザー・エネルギーの変動は、1つのパルス内でパルスの長さに沿って起こる可能性もある。

【0024】

選択用トランジスタ120は、半導体領域121から形成される。選択用トランジスタ120のゲートは、第1の走査線113の一部を、半導体領域121の一部の上方に延長することによって形成される。第1の走査線113と第2の走査線114は、第1の導電体層の中に形成されてパターニングされる。第1の導電体層と半導体層の間には絶縁層(図示せず)が配置されていて、トランジスタのゲート誘電体を形成している。選択用トランジスタ120のソース領域とドレイン領域は、第1の走査線113を延長することによって形成したゲートのどちらかの側の半導体領域121にドーピングすることによって形成できる。

【0025】

データ線111と電力線112は、第2の導電体層から公知の方法を利用して形成されてパターニングされる。第2の導電体層と第1の導電体層の間には別の絶縁層(図示せず)が配置されている。第1の導電体層と第2の導電体層の中に形成された線はこの絶縁層によって電気的接触なしに交差することが可能になるため、画素マトリックスルの行と列を形成できる。選択用トランジスタ120は、半導体領域121とデータ線111の間にある絶縁層内にビア122を形成することによってデータ線111に接続される。このビアは、公知の方法(例えばフォトリソグラフィによるパターニングとエッチング)で形成される。

【0026】

スイッチング用トランジスタ130は、半導体領域131から形成される。スイッチング用トランジスタ130のゲートは、図示したように、第2の走査線114の一部を、半導体領域131の一部の上方に延長することによって形成される。ソース領域とドレイン領域は、このゲート領域のどちらかの側の半導体領域131の一部にドーピングすることによって形成できる。ビア123を通じて半導体領域121に接続されるとともに、ビア132を通じて半導体領域131に接続された導電体ブリッジ125を用いることにより、スイッチング用トランジスタ130と選択用トランジスタ120が接続される。この導電体ブリッジは、例えば第2の導電体層の中に形成することができる。この2つのトランジスタは異なる型(NMOSとPMOS)であるため導電体ブリッジが好ましいが、本発明をうまく実現する上で導電体ブリッジが常に必要とされるわけではない。変換用トランジスタ140も半導体領域131の一部から形成されるため、ここでは変換用トランジスタ140へも接続されている。あるいは別の導電体ブリッジを用いてこのような接続にすることもできる。すると変換用トランジスタを独立した半導体領域として分離することができる。スイッチング用トランジスタ130は、ビア133を通じてゲート導電体145に電気的に接続されている。ゲート導電体145は、記憶用キャパシタ160の一方の側を形成するとともに、変換用トランジスタ140と駆動用トランジスタ150のゲート電極も形成する。このようにして、記憶用キャパシタ160と、変換用トランジスタ140および駆動用トランジスタ150のゲート電極との間に電気的接続が形成される。ゲート導電体145は、選択用トランジスタ120およびスイッチング用トランジスタ130のゲートと同じ層に形成されることが好ましい。すなわちゲート導電体145は、例えば第1の導電体層の中に構成されることが好ましい。

【0027】

記憶用キャパシタ160は、図示してあるように、半導体領域161とゲート導電体145の間に構成されることが好ましい。すなわち記憶用キャパシタは、第1の導電体層と半導体層から形成され、誘電体層(図示せず)がこれらの層の間に配置される。この構成では、半導体領域161はビア162を通じて電力線112に電気的に接続されている。あるいは記憶用キャパシタは、他の層(例えば第1の導電体層、第2の導電体層)から形成することもできる。この別の構成では、キャパシタの一方の側は、電力線の一部を延長することによって形成できるため、電力線に電気的に接続され、ビアを形成する必要がなくなる。

【0028】

上に説明したように、変換用トランジスタ140は半導体領域131から形成され、そのゲートは、ゲート導電体145から形成される。ソース領域とドレイン領域は、ゲート導電体145のどちらかの側で半導体領域131の一部にドーピングすることによって形成できる。図示してあるように、ビア142を通じて変換用トランジスタ140と電力線112が電気的に接続される。

【0029】

駆動用トランジスタ150は半導体領域151から形成され、そのゲートは、ゲート導電体145から形成される。ソース領域とドレイン領域は、ゲート導電体145のどちらかの側で半導体領域151の一部にドーピングすることによって形成できる。図示してあるように、ビア153を通じて駆動用トランジスタ150と電力線112が電気的に接続される。駆動用トランジスタ150も、ビア152を通じて有機発光ダイオードの第1の電極(図示せず)に電気的に接続されている。有機発光ダイオードの第1の電極(図示せず)は、第2の導電体層の上方に配置された第3の導電体層から構成されることが好ましい。第3の導電体層と第2の導電体層は、誘電体層(図示せず)によって分離されている。ビア152はこの誘電体層に形成された開口部であるため、電気的接触が可能になる。

【0030】

各トランジスタは、チャネル領域がゲート端子の下に来るように形成されて、そのトランジスタのソースとドレインを接続する。このチャネル領域は長さと幅を有する。ソース端子とゲート端子の間に印加される電圧差に応答して電流がこのチャネルを流れる。この電流は、チャネルの幅が大きくなるのにほぼ正比例して増加し、チャネルの長さが長くなるのに比例して減少する。トランジスタを飽和領域で作動させると、この電流はほぼ式(1)に従う。

ISD = (1/2)×μ×(W/L)×Cゲート×(VGS - VTH)2 (式1)

ただし、

ISDは、ソース端子とドレイン端子の間を流れる電流であり;

μは、キャリア(電子または正孔)の移動度であり;

Wは、チャネル幅であり;

Lは、チャネル長であり;

Cゲートは、チャネル領域の上方にあるゲートの単位面積当たりの容量であり;

VGSは、ゲート端子とソース端子の電圧差であり;

VTHは、トランジスタの閾値電圧である。

【0031】

有機発光ダイオードを流れる電流は、駆動用トランジスタ150によって調節される。駆動用トランジスタ150は、L1と表記されるチャネル長と、W1と表記されるチャネル幅を有する。同様に、変換用トランジスタ140は、W2と表記されるチャネル幅を持ち、駆動用トランジスタ150と同じチャネル長L1を持つことが図示してある。駆動用トランジスタ150と変換用トランジスタ140を流れる電流は、同じであるか、特定の比となるように設計することができる。

【0032】

ある電流比を実現するには、式1に従って流れる電流を決める1つ以上のパラメータ(例えばチャネル長またはチャネル幅)が、変換用トランジスタと駆動用トランジスタで異なっている必要がある。図2に示してあるように、変換用トランジスタと駆動用トランジスタのチャネル幅は異なる値にできる一方で、チャネル長は同じにされている。この構成では、他のパラメータ(例えば移動度、閾値電圧、チャネル領域の上方にあるゲートの単位面積当たりの容量)を同じにすることが好ましい。したがってこれら2つのトランジスタの半導体領域の性質の差が最小であることが重要である。

【0033】

変換用トランジスタ140と駆動用トランジスタ150の間でチャネル領域の半導体領域の差を小さくするには、半導体層をレーザーを用いてアニーリングするとき、これら2つの領域を同じレーザー・パルスまたはレーザー・パルス列で結晶化させる必要がある。この場合、変換用トランジスタ140と駆動用トランジスタ150のチャネル領域がレーザー・パルスに対してどのように位置するかを決めるにあたり、両方がパルスの長さの中に収まって同時に同じパルス列でアニールされるようにする。変換用トランジスタ140と駆動用トランジスタ150のチャネル領域は、パルス列が走査方向510で示したようにチャネル領域を横断するようにも配置される。このパルス列は、ほぼ同時に両方のチャネル領域に到達し、ほぼ同時に両方のチャネル領域のアニーリングを終了させる。これは、図示したチャネル領域を、例えばチャネル領域の長さまたは幅がレーザー・パルスと直角になるように配置するとともに、チャネル領域が互いにほぼ揃うように配置することによって実現できる。変換用トランジスタ140のチャネル領域と駆動用トランジスタ150のチャネル領域のこの並び方を実現するには、変換用トランジスタ140と駆動用トランジスタ150の長さまたは幅のどちらかを同じにすることが好ましい。図2の実施態様に示してあるように、変換用トランジスタ140と駆動用トランジスタ150のチャネル領域のチャネル長は同じにされている一方で、これら領域のチャネル幅は違えてある。チャネル領域の100%が正確に同じパルス列でアニールされることが好ましいが、これらチャネル領域を、各チャネル領域の少なくとも一部(50%を超えることが好ましい)が同じパルス列によって同時にアニールされるように配置することによってもいくらかの利益がある。さらに、レーザー・パルスのエネルギーの変動に対する感度をレーザー・パルスの長さ方向で小さくするには、図示したように駆動用トランジスタ150と変換用トランジスタ140を互いに近づけて配置することで駆動用トランジスタ150と変換用トランジスタ140のチャネル領域間のスペースを小さくすることが好ましい。

【0034】

図2のデバイスの線Z-Z'に沿った断面図を図3に示してある。この図は、駆動用トランジスタ150の断面図である。駆動用トランジスタ150は基板200の上に形成されている。基板200には多くの材料を使用できる。例えば、ガラス、プラスチック、セラミック、金属ホイルなどである。基板はさらに、1つ以上の障壁層(図示せず)で覆うことができる。基板が導電性である場合には、さらに誘電体層(図示せず)で覆うことができる。デバイスを作動させたときに画素から出る光を基板を通して見るのであれば、基板は透明でなくてはならない。この構成は、ボトム・エミッション型デバイスとして知られている。この場合、基板のための材料として、ガラスまたは透明なプラスチックが好ましい。デバイスを作動させたときに画素から出る光を基板と向かい合った方向から見るのであれば、不透明な基板を使用できる。この構成は、トップ・エミッション型デバイスとして知られている。図3に示した実施態様はトップ・エミッション型デバイスであるが、本発明がこの場合に限定されることはない。

【0035】

基板200の上方には第1の半導体層が設けられており、その半導体層から半導体領域151が形成される。半導体領域151の上方には、第1の誘電体層212が、フォトリソグラフィやエッチングなどの方法によって形成される。この誘電体層は、二酸化ケイ素、窒化ケイ素、またはこれらの組み合わせであることが好ましい。この誘電体層は、誘電性材料からなるいくつかのサブ層から形成することもできる。第1の誘電体層212の上方には第1の導電体層が設けられていて、その導電体層から、フォトリソグラフィやエッチングなどの方法により、ゲート導電体145と第1の走査線113が形成される。この導電体層は、従来技術で知られているように、例えば金属(クロムなど)にすることができる。ゲート導電体145と第1の走査線113の上方には、第2の誘電体層213が形成されている。この誘電体層は、例えば二酸化ケイ素、窒化ケイ素、またはこれらの組み合わせにすることができる。第2の誘電体層213の上方には第2の導電体層が設けられていて、その導電体層から、フォトリソグラフィやエッチングなどの方法により、電力線112が形成される。この導電体層は、従来技術で知られているように、例えば金属(アルミニウム合金など)にすることができる。電力線112は、誘電体層に開けられたビアを通じて半導体領域151と電気的に接触する。第2の導電体層の上方には、第3の誘電体層214が形成されている。

【0036】

第3の誘電体層の上方には、第1の電極260が形成されている。第1の電極260は、トップ・エミッション型デバイスでは反射率が大きいことが好ましい。その場合、第1の電極は金属層(AlまたはAg)にすることができる。あるいは第1の電極は、反射層(例えばAlまたはAg)の上方の多数のサブ層(例えば透明なインジウム-スズ酸化物(ITO))で構成することもできる。あるいは第1の電極を吸光性にすることもできる。このデバイスはトップ・エミッション型デバイスであるため、光はデバイスから基板200と向かい合う方向に出る。したがって第1の電極260を回路素子(例えば駆動用トランジスタ150)の上方に形成することができる。この構成だと、基板の利用可能な表面積が最も効率的に利用される。あるいはボトム・エミッション型デバイスを構成する場合には、第1の電極は透明でなければならず、ITOなどの材料で構成することができる。この場合には、第1の電極は、不透明で基板の方向への発光を阻止する他の回路素子の上方ではない領域に形成せねばならないことにも注意されたい。

【0037】

第1の電極260の上方では、アメリカ合衆国特許第6,246,179号に記載されているような画素間誘電体層220を用いて第1の電極の縁部を覆うことで、この領域で短絡が起こったり強電場が発生したりしないようにすることが好ましい。画素間誘電体層220が好ましいとはいえ、本発明をうまく実現するのに必要というわけではない。

【0038】

各画素は、有機EL媒体240をさらに備えており、その有機EL媒体から有機発光ダイオードが形成される。有機EL媒体240層には本発明をうまく実現できる多数の構成がある。画素間の有機EL媒体をパターニングせずにすむよう、あらゆる画素によって利用される波長の光を出す広帯域光源または白色光源が好ましい。この場合には、マルチカラー・デバイス用として光の通路に画素用のカラー・フィルタ(図示せず)を設け、白色光または広帯域光から望ましい色を出させることができる。広帯域光または白色光を出す有機EL媒体層のいくつかの実施例が、例えばアメリカ合衆国特許第6,696,177号に記載されている。しかし本発明は、各画素がそれぞれの画素用に別々にパターニングされた1つ以上の有機EL媒体層を備えていて、個々の画素が異なる色を出す場合でもうまくいく。有機EL媒体240は、いくつかの層で構成される。それは例えば、正孔注入層241と、正孔注入層241の上方に配置された正孔輸送層242と、正孔輸送層242の上方に配置された発光層243と、発光層243の上方に配置された電子輸送層245である。層の数がより少なかったりより多かったりする有機EL媒体240の別の構成を利用して本発明をうまく実現することもできる。これら有機EL媒体層は、一般に、有機材料からなる。その有機材料は、従来技術で知られているように、小分子材料またはポリマー材料である。これら有機EL媒体層は、公知のいくつかの方法で堆積させることができる。例えば、真空チェンバー内での蒸着、ドナー基板からのレーザー転写、インク・ジェット印刷装置を用いた溶媒からの堆積などの方法がある。

【0039】

有機EL媒体240の上方には、第2の電極250が形成されている。トップ・エミッション型デバイスでは、この電極は非常に透明になっている必要がある。その場合には、導電性かつ透明な材料(例えばインジウム-スズ酸化物(ITO))が、第2の電極250として好ましい。しかしデバイスがボトム・エミッション型デバイスである別の実施態様では、反射性材料(例えばアルミニウム(Al)やマグネシウム銀(MgAg)を用いることができる。

【0040】

有機EL媒体240は、第1の電極260と第2の電極250の間を流れる電流によって刺激されると、光270を出す。図3に示してあるように、光270は、デバイスから基板200とは反対方向に出て行くため、トップ・エミッション型デバイスとして動作する。

【0041】

図4は、OLEDデバイスを駆動するための電流型アクティブ・マトリックス回路である。より詳細には、この図は、本発明によるレイアウトの第2の実施態様に従うアクティブ・マトリックス電流ミラー型回路を示している。レイアウトのこの第2の実施態様では、回路はやはり画素が行と列に配列されたマトリックスの配置にすることができる。図4には1つの画素に関する回路部分が示してあるが、レイアウトの第1の実施態様に関してすでに説明したように、この構成を多数の行と列に拡張することができる。各画素は、デバイスのうちで独立に刺激して発光させることのできる領域である。各列には、電流源(例えば電流源170)に接続されたデータ線(例えばデータ線111)が含まれている。この電流源は、画素と同じ基板上に製造すること、またはその基板外に製造してデータ線111に接続することができる。各列には、電力線(例えば電力線112)も含まれている。あるいは隣り合った画素列が1本の電力線を共有する配置にすることもできる。さらに別の配置では、電力線をデータ線と垂直にすること、または電力線を行の方向にすることができる。それぞれの行には、第1の走査線(例えば第1の走査線113)と第2の走査線(例えば第2の走査線114)が含まれている。各画素には、5つのトランジスタと、1つのキャパシタと、1つの有機発光ダイオードがさらに含まれている。図示した画素には、例えば、選択用トランジスタ120と、スイッチング用トランジスタ130と、第1の変換用トランジスタ140aと、第2の変換用トランジスタ140bと、駆動用トランジスタ150と、記憶用キャパシタ160と、有機発光ダイオード230が含まれている。

【0042】

選択用トランジスタ120は、ゲート端子が第1の走査線113に電気的に接続され、ソース端子またはドレイン端子がデータ線111に電気的に接続されている。この選択用トランジスタの機能は、第1の走査線への適切な電圧によってこの選択用トランジスタがオンにされたとき、電流信号の形態で供給されるデータがデータ線から他の回路素子へと移れるようにすることである。そうなることで、駆動用トランジスタを流れる電流、したがって有機発光ダイオードを流れる電流が調節されて、画素の明るさが調節される。選択用トランジスタは、入力トランジスタと呼ぶこともできる。

【0043】

スイッチング用トランジスタ130は、図示してあるように、ゲート端子が第2の走査線114に電気的に接続され、第2の端子が選択用トランジスタ120に電気的に接続され、第3の端子が、記憶用キャパシタ160と、駆動用トランジスタ150のゲート端子と、第1の変換用トランジスタ140aのゲート端子と、第2の変換用トランジスタ140bのゲート端子に電気的に接続されている。スイッチング用トランジスタの目的は、データ信号が画素に書き込まれているときに駆動用トランジスタおよび変換用トランジスタのゲート端子と記憶用キャパシタに充電して望む明るさにできるようにすることである。これは、第2の走査線を利用してスイッチング用トランジスタのゲート端子に適切な電圧を印加することでこのスイッチング用トランジスタをオンにすることによって実現される。スイッチング用トランジスタは、データ信号が書き込まれると、第2の走査線に適切な電圧を印加することによってオフにされるため、記憶用キャパシタと、変換用トランジスタおよび駆動用トランジスタのゲート端子に貯えられた電圧が分離される。スイッチング用トランジスタは、消去用トランジスタと呼ぶこともできる。

【0044】

レイアウトの第2の実施態様では、レイアウトの第1の実施態様の変換用トランジスタが、第1の変換用トランジスタ140aと第2の変換用トランジスタ140bで置き換えられている。第1の変換用トランジスタ140aと第2の変換用トランジスタ140bは、ソース端子同士とドレイン端子同士が電気的に並列に接続されている。第1の変換用トランジスタ140aと第2の変換用トランジスタ140bのゲート端子同士も電気的に接続されている。このようになっているため、レイアウトのこの第2の実施態様では、第1の変換用トランジスタ140aと第2の変換用トランジスタ140bが合わさって、レイアウトの第1の実施態様の変換用トランジスタの機能を果たす。

【0045】

第1の変換用トランジスタ140aと第2の変換用トランジスタ140bは、図示してあるように、ゲート端子が、記憶用キャパシタ160と、駆動用トランジスタ150のゲート端子と、スイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。第1の変換用トランジスタ140aと第2の変換用トランジスタ140bは、図示してあるように、電力線112と、選択用トランジスタ120と、スイッチング用トランジスタ130にも電気的に接続されている。これら変換用トランジスタの目的は、その変換用トランジスタのゲートを駆動用トランジスタのゲートに電気的に接続することにより、データ線から供給される電流を通過させ、その電流が駆動用トランジスタに再現されるようにすることである。

【0046】

レイアウトの第1の実施態様と同様、変換用トランジスタを通過する電流は、駆動用トランジスタを流れる電流と同じにすること、または駆動用トランジスタを流れる電流に対して所定の比になっているようにすることができる。しかし駆動用トランジスタを流れる電流は、同じではなくて、データ線の電流に対して所定の比の関係になっていることが好ましい。例えばデータ線からより大きな電流が供給されて記憶用キャパシタとそれ以外のキャパシタ(例えば寄生キャパシタ)が素早く充電され、そのことによって画素の明るさを望ましいレベルにするのに必要な時間が短くなるようにすることが好ましい。これは、変換用トランジスタと駆動用トランジスタの1つ以上の特徴(例えばチャネル長、チャネル幅、ゲート絶縁層の厚さ)に関する比を調節することによって実現される。ここでは2つの変換用トランジスタが並列に接続されているため、もしその2つの変換用トランジスタのチャネル幅、チャネル長、ならびに他の特徴が同じであるならば、それぞれの変換用トランジスタが、これら変換用トランジスタを流れる全電流のほぼ半分を担うことになる。あるいはこれら2つの変換用トランジスタの特徴(例えばチャネル幅)を違えることにより、全電流がこれら変換用トランジスタの間で不均等に分配されるようにすることもできる。したがってこれら2つの変換用トランジスタと駆動用トランジスタの間を流れる電流の適切な比を確立する際には、これらの変換用トランジスタを合わせて考えるべきである。例えば第1の変換用トランジスタのゲート幅と第2の変換用トランジスタのゲート幅の両方が駆動用トランジスタのゲート幅よりも5倍広くされていて、他の特徴は同じだと、有機発光ダイオードが画素の望ましい明るさを実現するのに必要とするよりもほぼ10倍大きな電流を用いて画素データを書き込むことができる。明るさを望ましいレベルに調節し、選択用トランジスタとスイッチング用トランジスタをオフにすると、変換用トランジスタの中を電流が流れなくなるため、変換用トランジスタはもはや電流ミラー機能を果たさなくなる。しかし駆動用トランジスタのゲート端子の電圧は記憶用キャパシタに記憶されていて、しかもその電圧はスイッチング用トランジスタによって分離されているため、変換用トランジスタが必要な電流を供給することで画素は望ましい明るさの光を出し続ける。この状態は、次の画素フレームの間に画素が再び調節されるまで続く。

【0047】

駆動用トランジスタ150は、ゲート端子が、記憶用キャパシタ160と、第1の変換用トランジスタ140aのゲート端子と、第2の変換用トランジスタ140bのゲート端子と、スイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。図示してあるように、駆動用トランジスタは、第2の端子が電力線112に電気的に接続され、第3の端子が有機発光ダイオード230に電気的に接続されている。駆動用トランジスタの目的は、データ線からのデータ信号に応答して有機発光ダイオードの中を流れる電流を調節することである。この場合、調節された電流は、上記のように、変換用トランジスタにより、データ線から供給された電流に対して所定の比になるようにできる。駆動用トランジスタは、電力トランジスタと呼ぶこともできる。

【0048】

各画素には、有機発光ダイオード(例えば有機発光ダイオード230)が含まれている。このダイオードは、第1の電極と第2の電極の間に配置された複数の有機発光層からなる。第1の電極は、駆動用トランジスタ150に接続されている。第2の電極250は、すべての画素に共通であることが好ましい。1つ以上の有機発光層を画素ごとに個別にパターニングすること、またはすべての画素に共通にすることができる。

【0049】

第1の走査線113と第2の走査線114を利用してそれぞれ選択用トランジスタ120とスイッチング用トランジスタ130をオンにすると、デバイスのフレームの書き込み期間にデータ線111からのデータ信号に応答して画素の明るさを調節することができる。明るさのレベルが決まると、第1の走査線と第2の走査線を通じ、これら走査線に関係する画素行の選択用トランジスタとスイッチング用トランジスタをオフにする。次に、データ線信号が次の行にとって望ましいレベルに調節された後、その行の第1の走査線と第2の走査線がアクティブにされる。このプロセスが各画素行について繰り返される。この構成では、選択用トランジスタはNMOS型トランジスタとして図示してあり、変換用トランジスタ、駆動用トランジスタ、スイッチング用トランジスタは、PMOS型トランジスタとして図示してある。しかし本発明がこの場合に限定されることはなく、当業者であればこれらトランジスタの型を変更することができる。特に選択用トランジスタとスイッチング用トランジスタの両方がNMOS型トランジスタまたはPMOS型トランジスタにされている別の設計では、1本の走査線が第1の走査線と第2の走査線の両方の機能を果たすことができる。

【0050】

図5は、本発明によるレイアウトの第2の実施態様に従う回路レイアウトを1つの画素について示した図の一例である。図5には、さまざまな回路素子(例えば選択用トランジスタ120、スイッチング用トランジスタ130、第1の変換用トランジスタ140a、第2の変換用トランジスタ140b、駆動用トランジスタ150、記憶用キャパシタ160、データ線111、電力線112、第1の走査線113、第2の走査線114)の構成と配置が示してある。有機発光ダイオード(第1の電極と第2の電極を含む)は、図5には図示されていない。

【0051】

図5に示してあるように、駆動用トランジスタ150は、ゲート導電体145の下方のチャネル領域が幅W1と長さL1を持つように構成されている。第1の変換用トランジスタ140aは、ゲート導電体145の下方のチャネル領域が幅W3と長さL1を持つように構成されている。第2の変換用トランジスタ140bは、ゲート導電体145の下方のチャネル領域が幅W4と長さL1を持つように構成されている。

【0052】

レイアウトのこの第2の実施態様によれば、第1の変換用トランジスタ140aのチャネル領域と第2の変換用トランジスタ140bのチャネル領域は、その間に配置された駆動用トランジスタ150のチャネル領域とは離れている。このレイアウトを実現するには、変換用トランジスタを2つの異なる半導体領域から形成するとよい。例えば第1の変換用トランジスタ140aを半導体領域131aから形成し、第2の変換用トランジスタ140bを半導体領域141bから形成する。第1の変換用トランジスタ140aと、第2の変換用トランジスタ140bと、選択用トランジスタ120と、スイッチング用トランジスタ130の間を、導電体ブリッジ125aを用いて電気的に接続する。この導電体ブリッジ125aは、ビア143aを通じて半導体領域131aに電気的に接続され、ビア143bを通じて半導体領域141bに電気的に接続されている。第1の変換用トランジスタ140aと電力線112がビア142aを通じて電気的に接続される。第2の変換用トランジスタ140bと電力線112がビア142bを通じて電気的に接続される。ゲート導電体145は、第1の変換用トランジスタ140aと、第2の変換用トランジスタ140bと、駆動用トランジスタ150のゲート電極として機能する。

【0053】

本発明によるレイアウトのこの第2の実施態様において第1の変換用トランジスタ140aのチャネル領域と第2の変換用トランジスタ140bのチャネル領域の間に駆動用トランジスタ150のチャネル領域を配置することにより、回路は層(例えば半導体層や、半導体層とゲートの間にある絶縁層)の物理的性質の局所的な変動に対してより強くなる。物理的性質(例えばゲート絶縁体の厚さ、結晶粒子の大きさ)は、トランジスタの電気的性質(例えば閾値電圧、キャリアの移動度)に直接影響を与える。すなわち第1の変換用トランジスタ140aのチャネル領域と第2の変換用トランジスタ140bのチャネル領域の間に駆動用トランジスタ150のチャネル領域を配置することにより、駆動用トランジスタ150の性質が、第1の変換用トランジスタ140aと第2の変換用トランジスタ140bの性質の中間の値に近づく。第1の変換用トランジスタ140aと第2の変換用トランジスタ140bは電気的に並列に接続されていて、ゲート同士も電気的に接続されているため、これらの変換用トランジスタからの全電流、またはその一部は、すでに説明したように、データ信号が画素行に書き込まれるときに駆動用トランジスタ150に再現される。レイアウトのこの第2の実施態様に従って駆動用トランジスタ150が第1の変換用トランジスタ140aと第2の変換用トランジスタ140bのほぼ中間の値を持つように構成することで、このような性質の変動に対する全体的な強さが向上する。

【0054】

すでに説明したようにレーザーでアニールすることによって半導体層を結晶化させる場合には、本発明によるレイアウトの第2の実施態様を実施することによって強さも向上する。しかし本発明によるレイアウトの第2の実施態様がこの場合に限定されることはない。レーザーでアニールすることによって半導体層を結晶化させる場合、レーザー・パルスに変動があると半導体層の性質に影響が及ぶため、レーザー・パルスの変動に対する回路の強さを改善することが望ましい。レーザー・パルス(例えばレーザー・パルス501と502)のエネルギー変動に対する回路の感度を小さくするには、図示してあるように、第1の変換用トランジスタ140aのチャネル領域と、駆動用トランジスタ150のチャネル領域と、第2の変換用トランジスタ140bのチャネル領域をレーザー・パルスと平行に配置することも好ましい。第1の変換用トランジスタ140aのチャネル領域と第2の変換用トランジスタ140bのチャネル領域の間に駆動用トランジスタ150のチャネル領域をこのような平行な関係で配置すると、第1の変換用トランジスタ140aのチャネル領域と第2の変換用トランジスタ140bのチャネル領域が受け取るレーザーのエネルギーのほぼ平均値が駆動用トランジスタ150のチャネル領域に与えられるため、パルスの長さ方向でのレーザーのエネルギー変動に対する強さが向上する。

【0055】

レーザーを利用して半導体層をアニールするときに第1の変換用トランジスタ140aと第2の変換用トランジスタ140bと駆動用トランジスタ150のチャネル領域の半導体領域間の差をさらに小さくするには、その半導体領域を同じ1つのレーザー・パルスまたはレーザー・パルス列で結晶化させる必要がある。その場合、第1の変換用トランジスタ140aのチャネル領域と、第2の変換用トランジスタ140bのチャネル領域と、駆動用トランジスタ150のチャネル領域を、レーザー・パルスに対し、どのチャネル領域も1つのパルス内に収まり、同時に同じパルス列によってアニールされるように配置する。第1の変換用トランジスタ140aのチャネル領域と、第2の変換用トランジスタ140bのチャネル領域と、駆動用トランジスタ150のチャネル領域は、パルス列が走査方向510で示したようにチャネル領域を横断するにつれて、そのパルス列がすべてのチャネル領域にほぼ同時に到達し、ほぼ同時にチャネル領域のアニーリングが終了するようにも配置する。これは、図示したチャネル領域を、例えばチャネル領域の長さまたは幅がレーザー・パルスと直角になるようにするとともに、チャネル領域が互いにほぼ揃うように配置することによって実現できる。第1の変換用トランジスタ140aのチャネル領域と、第2の変換用トランジスタ140bのチャネル領域と、駆動用トランジスタ150のチャネル領域のこの並び方を実現するには、第1の変換用トランジスタ140aと第2の変換用トランジスタ140bと駆動用トランジスタ150の長さまたは幅のどちらかを同じにすることが好ましい。図5の実施態様に示してあるように、第1の変換用トランジスタ140aと第2の変換用トランジスタ140bと駆動用トランジスタ150のチャネル領域のチャネル長は同じにされている一方で、これら領域のチャネル幅は違えてある。チャネル領域が正確に同じパルス列でアニールされることが好ましいが、これらチャネル領域を、各チャネル領域の少なくとも一部(50%を超えることが好ましい)が同じパルス列によって同時にアニールされるように配置することによってもいくらかの利益がある。

【0056】

図6は、OLEDデバイスを駆動するための別の電流型アクティブ・マトリックス回路である。より詳細には、この図は、本発明によるレイアウトの第3の実施態様に従うアクティブ・マトリックス電流ミラー型回路を示している。レイアウトのこの第3の実施態様では、回路はやはり画素が行と列に配列されたマトリックスの配置にすることができる。図6には1つの画素に関する回路部分が示してあるが、レイアウトの第1の実施態様に関してすでに説明したように、この構成を多数の行と列に拡張することができる。各画素は、デバイスのうちで独立に刺激して発光させることのできる領域である。各列には、電流源(例えば電流源170)に接続されたデータ線(例えばデータ線111)が含まれている。この電流源は、画素と同じ基板上に製造すること、またはその基板外に製造してデータ線111に接続することができる。各列には、電力線(例えば電力線112)も含まれている。あるいは隣り合った画素列が1本の電力線を共有する配置にすることもできる。さらに別の配置では、電力線をデータ線と垂直にすること、または電力線を行の方向にすることができる。それぞれの行には、第1の走査線(例えば第1の走査線113)と第2の走査線(例えば第2の走査線114)が含まれている。各画素には、5つのトランジスタと、1つのキャパシタと、1つの有機発光ダイオードがさらに含まれている。図示した画素には、例えば、選択用トランジスタ120と、スイッチング用トランジスタ130と、変換用トランジスタ140と、第1の駆動用トランジスタ150aと、第2の駆動用トランジスタ150bと、記憶用キャパシタ160と、有機発光ダイオード230が含まれている。

【0057】

選択用トランジスタ120は、ゲート端子が第1の走査線113に電気的に接続され、ソース端子またはドレイン端子がデータ線111に電気的に接続されている。この選択用トランジスタの機能は、第1の走査線への適切な電圧によってこの選択用トランジスタがオンにされたとき、電流信号の形態で供給されるデータがデータ線から他の回路素子へと移れるようにすることである。そうなることで、駆動用トランジスタを流れる電流、したがって有機発光ダイオードを流れる電流が調節されて、画素の明るさが調節される。選択用トランジスタは、入力トランジスタと呼ぶこともできる。

【0058】

スイッチング用トランジスタ130は、図示してあるように、ゲート端子が第2の走査線114に電気的に接続され、第2の端子が選択用トランジスタ120に電気的に接続され、第3の端子が、記憶用キャパシタ160と、第1の駆動用トランジスタ150aのゲート端子と、第2の駆動用トランジスタ150bのゲート端子と、変換用トランジスタ140のゲート端子に電気的に接続されている。スイッチング用トランジスタの目的は、データ信号が画素に書き込まれているときに駆動用トランジスタおよび変換用トランジスタのゲート端子と記憶用キャパシタに充電して望む明るさにできるようにすることである。これは、第2の走査線を利用してスイッチング用トランジスタのゲート端子に適切な電圧を印加することでこのスイッチング用トランジスタをオンにすることによって実現される。スイッチング用トランジスタは、データ信号が書き込まれると、第2の走査線に適切な電圧を印加することによってオフにされるため、記憶用キャパシタと、変換用トランジスタおよび駆動用トランジスタのゲート端子に貯えられた電圧が分離される。スイッチング用トランジスタは、消去用トランジスタと呼ぶこともできる。

【0059】

レイアウトの第1の実施態様の駆動用トランジスタは、レイアウトのこの第3の実施態様では、第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bで置き換えられている。第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bは、ソース端子同士とドレイン端子同士が電気的に並列に接続されている。第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bのゲート端子も電気的に接続されている。このようになっているため、レイアウトのこの第3の実施態様では、第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bが合わさって、レイアウトの第1の実施態様の駆動用トランジスタの機能を果たす。

【0060】

第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bは、ゲート端子が記憶用キャパシタ160と、変換用トランジスタのゲート端子と、スイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bは、図示してあるように、第2の端子が電力線112に電気的に接続され、第3の端子が有機発光ダイオード230に電気的に接続されている。これら駆動用トランジスタの目的は、データ線からのデータ信号に応答して有機発光ダイオードの中を流れる電流を調節することである。この場合、調節された電流は、下記のように、変換用トランジスタにより、データ線から供給された電流に対して所定の比になるようにできる。駆動用トランジスタは、電力トランジスタと呼ぶこともできる。

【0061】

変換用トランジスタ140は、ゲート端子が、記憶用キャパシタ160と、第1の駆動用トランジスタ150aおよび第2の駆動用トランジスタ150bのゲート端子と、スイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。図示してあるように、変換用トランジスタの第2の端子は電力線112に電気的に接続され、第3の端子は選択用トランジスタ120とスイッチング用トランジスタ130のソース端子またはドレイン端子に電気的に接続されている。変換用トランジスタの目的は、この変換用トランジスタのゲートを駆動用トランジスタのゲートに電気的に接続することにより、データ線から供給される電流を通過させ、その電流が駆動用トランジスタに再現されるようにすることである。

【0062】

レイアウトの第1の実施態様と同様、変換用トランジスタを通過する電流は、駆動用トランジスタを流れる電流と同じにすること、または駆動用トランジスタを流れる電流に対して所定の比になっているようにすることができる。しかし駆動用トランジスタを流れる電流は、同じではなくて、データ線の電流に対して所定の比の関係になっていることが好ましい。例えばデータ線からより大きな電流が供給されて記憶用キャパシタとそれ以外のキャパシタ(例えば寄生キャパシタ)が素早く充電され、そのことによって画素の明るさを望ましいレベルにするのに必要な時間が短くなるようにすることが好ましい。これは、変換用トランジスタと駆動用トランジスタの1つ以上の特徴(例えばチャネル長、チャネル幅、ゲート絶縁層の厚さ)に関して比を調節することによって実現される。ここでは2つの駆動用トランジスタが並列に接続されているため、もしその2つの駆動用トランジスタのチャネル幅、チャネル長、ならびに他の特徴が同じであるならば、それぞれの駆動用トランジスタが、これら駆動用トランジスタを流れる全電流のほぼ半分を担うことになる。あるいはこれら2つの駆動用トランジスタの特徴(例えばチャネル幅)を違えることにより、全電流がこれら駆動用トランジスタの間で不均等に分配されるようにすることもできる。したがって変換用トランジスタとこれら2つの駆動用トランジスタの間を流れる電流の適切な比を確立する際には、これらの駆動用トランジスタを合わせて考えるべきである。例えば第1の駆動用トランジスタのゲート幅と第2の駆動用トランジスタのゲート幅の両方が変換用トランジスタのゲート幅よりも5倍広くされていて、他の特徴は同じだと、有機発光ダイオードが画素の望ましい明るさを実現するのに必要とするよりもほぼ10倍大きな電流を用いて画素データを書き込むことができる。明るさを望ましいレベルに調節し、選択用トランジスタとスイッチング用トランジスタをオフにすると、変換用トランジスタの中を電流が流れなくなるため、変換用トランジスタはもはや電流ミラー機能を果たさなくなる。しかし駆動用トランジスタのゲート端子の電圧は記憶用キャパシタに記憶されていてい、しかもその電圧はスイッチング用トランジスタによって分離されているため、変換用トランジスタが必要な電流を供給することで画素は望ましい明るさの光を出し続ける。この状態は、次の画素フレームの間に画素が再び調節されるまで続く。

【0063】

各画素には、有機発光ダイオード(例えば有機発光ダイオード230)が含まれている。このダイオードは、第1の電極と第2の電極の間に配置された複数の有機発光層からなる。第1の電極は、第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bに接続されている。第2の電極250は、すべての画素に共通であることが好ましい。1つ以上の有機発光層を画素ごとに個別にパターニングすること、またはすべての画素に共通にすることができる。

【0064】

第1の走査線113と第2の走査線114を利用してそれぞれ選択用トランジスタ120とスイッチング用トランジスタ130をオンにすると、デバイスのフレームの書き込み期間にデータ線111からのデータ信号に応答して画素の明るさを調節することができる。明るさのレベルが決まると、第1の走査線と第2の走査線を通じ、これら走査線に関係する画素行の選択用トランジスタとスイッチング用トランジスタをオフにする。次に、データ線信号が次の行にとって望ましいレベルに調節された後、その行の第1の走査線と第2の走査線がアクティブにされる。このプロセスが各画素行について繰り返される。この構成では、選択用トランジスタはNMOS型トランジスタとして図示してあり、変換用トランジスタ、駆動用トランジスタ、スイッチング用トランジスタは、PMOS型トランジスタとして図示してある。しかし本発明がこの場合に限定されることはなく、当業者であればこれらトランジスタの型を変更することができる。特に選択用トランジスタとスイッチング用トランジスタの両方がNMOS型トランジスタまたはPMOS型トランジスタにされている別の設計では、1本の走査線が第1の走査線と第2の走査線の両方の機能を果たすことができる。

【0065】

図7は、本発明によるレイアウトの第3の実施態様に従う回路レイアウトを1つの画素について示した図の一例である。図7には、さまざまな回路素子(例えば選択用トランジスタ120、スイッチング用トランジスタ130、変換用トランジスタ140、第1の駆動用トランジスタ150a、第2の駆動用トランジスタ150b、記憶用キャパシタ160、データ線111、電力線112、第1の走査線113、第2の走査線114)の構成と配置が示してある。有機発光ダイオード(第1の電極と第2の電極を含む)は、図7には図示されていない。

【0066】

図7に示してあるように、変換用トランジスタ140は、ゲート導電体145の下方のチャネル領域が幅W2と長さL1を持つように構成されている。第1の駆動用トランジスタ150aは、ゲート導電体145の下方のチャネル領域が幅W5と長さL1を持つように構成されている。第2の駆動用トランジスタ150bは、ゲート導電体145の下方のチャネル領域が幅W6と長さL1を持つように構成されている。

【0067】

レイアウトのこの第3の実施態様によれば、第1の駆動用トランジスタ150aのチャネル領域と第2の駆動用トランジスタ150bのチャネル領域は、その間に配置された変換用トランジスタ140のチャネル領域とは離れている。このレイアウトを実現するには、駆動用トランジスタを2つの異なる半導体領域から形成するとよい。例えば第1の駆動用トランジスタ150aを半導体領域151aから形成し、第2の駆動用トランジスタ150bを半導体領域151bから形成する。第1の駆動用トランジスタ150aと電力線112をビア153aを通じて電気的に接続する。第2の駆動用トランジスタ150bと電力線112をビア153bを通じて電気的に接続する。第1の駆動用トランジスタ150bと有機発光ダイオード(図示せず)の第1の電極をビア152aを通じて電気的に接続する。第2の駆動用トランジスタ150bと有機発光ダイオード(図示せず)の第1の電極をビア152bを通じて電気的に接続する。ゲート導電体145は、第1の駆動用トランジスタ150aと、第2の駆動用トランジスタ150bと、変換用トランジスタ140のゲート電極として機能する。

【0068】

本発明によるレイアウトのこの第3の実施態様に従って第1の駆動用トランジスタ150aのチャネル領域と第2の駆動用トランジスタ150bのチャネル領域の間に変換用トランジスタ140のチャネル領域を配置することにより、回路は層(例えば半導体層や、半導体層とゲートの間にある絶縁層)の物理的性質の局所的な変動に対してより強くなる。物理的性質(例えばゲート絶縁体の厚さ、結晶粒子の大きさ)は、トランジスタの電気的性質(例えば閾値電圧、キャリアの移動度)に直接影響を与える。すなわち第1の駆動用トランジスタ150aのチャネル領域と第2の駆動用トランジスタ150bのチャネル領域の間に変換用トランジスタ140のチャネル領域を配置することにより、変換用トランジスタ140の性質が、第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bの性質の中間の値に近づく。第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bは電気的に並列に接続されていて、ゲート同士も電気的に接続されているため、これらの変換用トランジスタからの電流、またはその一部は、すでに説明したように、データ信号が画素行に書き込まれるときにこれら駆動用トランジスタに再現されて分割される。レイアウトのこの第3の実施態様に従って変換用トランジスタ140が第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bのほぼ中間の値を持つように構成することで、このような性質の変動に対する全体的な強さが向上する。

【0069】

すでに説明したようにレーザーでアニールすることによって半導体層を結晶化させる場合には、本発明によるレイアウトの第3の実施態様を実施することによって強さも向上する。しかし本発明によるレイアウトの第3の実施態様がこの場合に限定されることはない。レーザーでアニールすることによって半導体層を結晶化させる場合、レーザー・パルスに変動があると半導体層の性質に影響が及ぶため、レーザー・パルスの変動に対する回路の強さを改善することが望ましい。レーザー・パルス(例えばレーザー・パルス501と502)のエネルギー変動に対する回路の感度を小さくするには、図示してあるように、第1の駆動用トランジスタ150aのチャネル領域と、変換用トランジスタ140のチャネル領域と、第2の駆動用トランジスタ150bのチャネル領域をレーザー・パルスと平行に配置することも好ましい。第1の駆動用トランジスタ150aのチャネル領域と第2の駆動用トランジスタ150bのチャネル領域の間に変換用トランジスタ140のチャネル領域をこのような平行な関係で配置すると、第1の駆動用トランジスタ150aのチャネル領域と第2の駆動用トランジスタ150bのチャネル領域が受け取るレーザーのエネルギーのほぼ平均値が変換用トランジスタ140のチャネル領域に与えられるため、パルスの長さ方向でのレーザーのエネルギー変動に対する強さが向上する。

【0070】

レーザーを利用して半導体層をアニールするときに第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bと変換用トランジスタ140のチャネル領域の半導体領域間の差をさらに小さくするには、その半導体領域を同じ1つのレーザー・パルスまたはレーザー・パルス列で結晶化させる必要がある。その場合、第1の駆動用トランジスタ150aのチャネル領域と、第2の駆動用トランジスタ150bのチャネル領域と、変換用トランジスタ140のチャネル領域を、レーザー・パルスに対し、どのチャネル領域も1つのパルス内に収まり、同時に同じパルス列によってアニールされるように配置する。変換用トランジスタ140のチャネル領域と、第1の駆動用トランジスタ150aのチャネル領域と、第2の駆動用トランジスタ150bのチャネル領域は、パルス列が走査方向510で示したようにチャネル領域を横断するにつれて、そのパルス列がすべてのチャネル領域にほぼ同時に到達し、ほぼ同時にチャネル領域のアニーリングが終了するようにも配置する。これは、図示したチャネル領域を、例えばチャネル領域の長さまたは幅がレーザー・パルスと直角になるように配置するとともに、チャネル領域が互いにほぼ揃うように配置することによって実現できる。第1の駆動用トランジスタ150aのチャネル領域と、第2の駆動用トランジスタ150bのチャネル領域と、変換用トランジスタ140のチャネル領域のこの並び方を実現するには、第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bと変換用トランジスタ140の長さまたは幅のどちらかを同じにすることが好ましい。図7の実施態様に示してあるように、第1の駆動用トランジスタ150aと第2の駆動用トランジスタ150bと変換用トランジスタ140のチャネル領域のチャネル長は同じにされている一方で、これら領域のチャネル幅は違えてある。チャネル領域が正確に同じパルス列でアニールされることが好ましいが、これらチャネル領域を、各チャネル領域の少なくとも一部(50%を超えることが好ましい)が同じパルス列によって同時にアニールされるように配置することによってもいくらかの利益がある。

【0071】

レイアウトの第2の実施態様に関する説明は、2つの変換用トランジスタの間に駆動用トランジスタが配置された場合であった。当業者であれば、この考え方を、3つ以上の変換用トランジスタがあって、その変換用トランジスタのうちの少なくとも2つの間に少なくとも1つの駆動用トランジスタが配置されている場合に拡張することができよう。このような実施態様も、本発明の範囲に含まれると考えられる。レイアウトの第3の実施態様に関する説明は、2つの駆動用トランジスタの間に変換用トランジスタが配置された場合であった。当業者であれば、この考え方を、3つ以上の駆動用トランジスタがあって、その駆動用トランジスタのうちの少なくとも2つの間に少なくとも1つの変換用トランジスタが配置されている場合に拡張することができよう。このような実施態様も、本発明の範囲に含まれると考えられる。当業者であれば、2つ以上の駆動用トランジスタと2つ以上の変換用トランジスタの組み合わせも利用できる。このような組み合わせも、本発明の範囲に含まれると考えられる。上記の構成のどれを利用しても、トランジスタ間の特性の差に対してより強くすることができる。

【符号の説明】

【0072】

10 画素

111 データ線

112 電力線

113 第1の走査線

114 第2の走査線

120 選択用トランジスタ

121 半導体領域

122 ビア

123 ビア

125 導電体ブリッジ

125a 導電体ブリッジ

130 スイッチング用トランジスタ

131 半導体領域

131a 半導体領域

132 ビア

133 ビア

140 変換用トランジスタ

140a 第1の変換用トランジスタ

140b 第2の変換用トランジスタ

141b 半導体領域

142 ビア

142a ビア

142b ビア

143a ビア

143b ビア

145 ゲート導電体

150 駆動用トランジスタ

150a 第1の駆動用トランジスタ

150b 第2の駆動用トランジスタ

151 半導体領域

151a 半導体領域

151b 半導体領域

152 ビア

152a ビア

152b ビア

153 ビア

153a ビア

153b ビア

160 記憶用キャパシタ

161 半導体領域

162 ビア

170 電流源

200 基板

212 第1の誘電体層

213 第2の誘電体層

214 第3の誘電体層

230 有機発光ダイオード

240 有機EL媒体

241 正孔注入層

242 正孔輸送層

243 発光層

245 電子輸送層

250 第2の電極

260 第1の電極

270 光

501 レーザー・パルス

502 レーザー・パルス

510 レーザーの走査方向

【特許請求の範囲】

【請求項1】

電流型アクティブ・マトリックスOLEDデバイスの製造方法であって、

a)基板の上方に半導体層を設け;

b)その基板の上方に導電層を設け;

c)上記半導体層と上記導電層の間に絶縁層を設け;

d)各画素を発光させるため、上記半導体層または上記導電層の上方に有機発光ダイオードを設け;

e)第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、上記半導体層の中に形成されたチャネル領域と、上記導電層の中に形成されたゲートとを備える第1のトランジスタを画素ごとに形成し;

f)上記第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第2のトランジスタを画素ごとに形成し;

g)上記第1のトランジスタと上記第2のトランジスタを形成する前、または形成した後に、供給源から供給されて1個以上のレーザー・パルスを発生させるパルス式レーザーを用いた照射により、上記半導体層のうちで、その第1のトランジスタのチャネル領域の一部に関係する領域と、その第2のトランジスタのチャネル領域の一部に関係する領域をアニーリングする操作を含む方法。

【請求項2】

上記供給源と上記基板を相対運動させ、パルスが供給されたとき、上記第1のトランジスタのチャネル領域の上記一部と、上記第2のトランジスタのチャネル領域の上記一部が、同時に照射されるようにする、請求項1に記載の方法。

【請求項3】

1回に照射される部分の面積が、対応するチャネル領域の50%を超える、請求項1に記載の方法。

【請求項4】

1回に照射される部分の面積が、対応するチャネル領域の100%に等しい、請求項1に記載の方法。

【請求項5】

アクティブ・マトリックス回路によって駆動される画素を有するアクティブ・マトリックスOLEDデバイスであって、各画素が、

a)有機発光ダイオードと;

b)第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、ゲートとチャネル領域を備える第1のトランジスタと;

c)上記第1の電流に応答して上記有機発光ダイオードを流れる第2の電流を調節するため、ゲートとチャネル領域とを備える第2のトランジスタと第3のトランジスタを含んでおり、上記第1のトランジスタのチャネル領域の一部が、上記第2のトランジスタのチャネル領域と上記第3のトランジスタのチャネル領域の間に配置されている、アクティブ・マトリックスOLEDデバイス。

【請求項6】

上記第1のトランジスタのチャネル領域の上記一部の面積が、対応するチャネル領域の50%を超える、請求項5に記載のアクティブ・マトリックスOLEDデバイス。

【請求項7】

上記第1のトランジスタのチャネル領域の上記一部の面積が、対応するチャネル領域の100%に等しい、請求項5に記載のアクティブ・マトリックスOLEDデバイス。

【請求項8】

上記第1の電流と上記第2の電流の大きさが所定の比の関係にある、請求項5に記載のアクティブ・マトリックスOLEDデバイス。

【請求項9】

上記第1の電流が上記第2の電流よりも大きい、請求項5に記載のアクティブ・マトリックスOLEDデバイス。

【請求項10】

上記第1のトランジスタのゲートが、上記第2のトランジスタのゲートと上記第3のトランジスタのゲートに電気的に接続されている、請求項5に記載のアクティブ・マトリックスOLEDデバイス。

【請求項11】

上記第1のトランジスタのチャネル領域と、上記第2のトランジスタのチャネル領域と、上記第3のトランジスタのチャネル領域が、レーザーでアニールされた半導体層によって提供される、請求項5に記載のアクティブ・マトリックスOLEDデバイス。

【請求項12】

電流型アクティブ・マトリックスOLEDデバイスの製造方法であって、

a)基板の上方に半導体層を設け;

b)その基板の上方に導電層を設け;

c)上記半導体層と上記導電層の間に絶縁層を設け;

d)各画素を発光させるため、上記半導体層または上記導電層の上方に有機発光ダイオードを設け;

e)第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、上記半導体層の中に形成されたチャネル領域と、上記導電層の中に形成されたゲートとを備える第1のトランジスタを画素ごとに形成し;

f)上記第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第2のトランジスタと第3のトランジスタを画素ごとに形成し;

g)上記第1のトランジスタ、上記第2のトランジスタ、上記第3のトランジスタを形成する前、または形成した後に、供給源から供給されて1個以上のレーザー・パルスを発生させるパルス式レーザーを用いた照射により、上記半導体層のうちで、その第1のトランジスタのチャネル領域の一部に関係する領域と、その第2のトランジスタのチャネル領域の一部に関係する領域と、その第3のトランジスタのチャネル領域の一部に関係する領域をアニーリングする操作を含む方法。

【請求項13】

上記供給源と上記基板を相対運動させ、パルスが供給されたとき、上記第1のトランジスタと上記第2のトランジスタと上記第3のトランジスタのチャネル領域の上記一部が同時に照射されるようにする、請求項12に記載の方法。

【請求項14】

1回に照射される部分の面積が、対応するチャネル領域の50%を超える、請求項12に記載の方法。

【請求項15】

1回に照射される部分の面積が、対応するチャネル領域の100%に等しい、請求項12に記載の方法。

【請求項16】

アクティブ・マトリックス回路によって駆動される画素を有するアクティブ・マトリックスOLEDデバイスであって、各画素が、

a)有機発光ダイオードと;

b)第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、ゲートとチャネル領域をそれぞれが備える第1のトランジスタおよび第2のトランジスタと;

c)上記第1の電流に応答して上記有機発光ダイオードを流れる第2の電流を調節するため、ゲートとチャネル領域を備える第3のトランジスタとを含んでおり、上記第3のトランジスタのチャネル領域の一部が、上記第1のトランジスタのチャネル領域と上記第2のトランジスタのチャネル領域の間に配置されている、アクティブ・マトリックスOLEDデバイス。

【請求項17】

上記第3のトランジスタのチャネル領域の上記一部の面積が、対応するチャネル領域の50%を超える、請求項16に記載のアクティブ・マトリックスOLEDデバイス。

【請求項18】

上記第3のトランジスタのチャネル領域の上記一部の面積が、対応するチャネル領域の100%に等しい、請求項16に記載のアクティブ・マトリックスOLEDデバイス。

【請求項19】

上記第1の電流と上記第2の電流の大きさが所定の比の関係にある、請求項16に記載のアクティブ・マトリックスOLEDデバイス。

【請求項20】

上記第1の電流が上記第2の電流よりも大きい、請求項16に記載のアクティブ・マトリックスOLEDデバイス。

【請求項21】

上記第3のトランジスタのゲートが、上記第1のトランジスタのゲートと上記第2のトランジスタのゲートに電気的に接続されている、請求項16に記載のアクティブ・マトリックスOLEDデバイス。

【請求項22】

上記第1のトランジスタのチャネル領域と、上記第2のトランジスタのチャネル領域と、上記第3のトランジスタのチャネル領域が、レーザーでアニールされた半導体層によって提供される、請求項16に記載のアクティブ・マトリックスOLEDデバイス。

【請求項23】

電流型アクティブ・マトリックスOLEDデバイスの製造方法であって、

a)基板の上方に半導体層を設け;

b)その基板の上方に導電層を設け;

c)上記半導体層と上記導電層の間に絶縁層を設け;

d)各画素を発光させるため、上記半導体層または上記導電層の上方に有機発光ダイオードを設け;

e)第1の電流データとしての信号を受け取って対応する画素から出る光の明るさを調節するため、半導体層の中に形成されたチャネル領域と、導電層の中に形成されたゲートとをそれぞれが備える第1のトランジスタと第2のトランジスタを画素ごとに形成し;

f)上記第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第3のトランジスタを画素ごとに形成し;

g)上記第1のトランジスタ、上記第2のトランジスタ、上記第3のトランジスタを形成する前、または形成した後に、供給源から供給されて1個以上のレーザー・パルスを発生させるパルス式レーザーを用いた照射により、上記半導体層のうちで、その第1のトランジスタのチャネル領域の一部に関係する領域と、その第2のトランジスタのチャネル領域の一部に関係する領域と、その第3のトランジスタのチャネル領域の一部に関係する領域をアニーリングする操作を含む方法。

【請求項24】

上記供給源と上記基板を相対運動させ、パルスが供給されたとき、上記第1のトランジスタと上記第2のトランジスタと上記第3のトランジスタのチャネル領域の上記一部が同時に照射されるようにする、請求項23に記載の方法。

【請求項25】

1回に照射される部分の面積が、対応するチャネル領域の50%を超える、請求項23に記載の方法。

【請求項26】

1回に照射される部分の面積が、対応するチャネル領域の100%に等しい、請求項23に記載の方法。

【請求項1】

電流型アクティブ・マトリックスOLEDデバイスの製造方法であって、

a)基板の上方に半導体層を設け;

b)その基板の上方に導電層を設け;

c)上記半導体層と上記導電層の間に絶縁層を設け;

d)各画素を発光させるため、上記半導体層または上記導電層の上方に有機発光ダイオードを設け;

e)第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、上記半導体層の中に形成されたチャネル領域と、上記導電層の中に形成されたゲートとを備える第1のトランジスタを画素ごとに形成し;

f)上記第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第2のトランジスタを画素ごとに形成し;

g)上記第1のトランジスタと上記第2のトランジスタを形成する前、または形成した後に、供給源から供給されて1個以上のレーザー・パルスを発生させるパルス式レーザーを用いた照射により、上記半導体層のうちで、その第1のトランジスタのチャネル領域の一部に関係する領域と、その第2のトランジスタのチャネル領域の一部に関係する領域をアニーリングする操作を含む方法。

【請求項2】

上記供給源と上記基板を相対運動させ、パルスが供給されたとき、上記第1のトランジスタのチャネル領域の上記一部と、上記第2のトランジスタのチャネル領域の上記一部が、同時に照射されるようにする、請求項1に記載の方法。

【請求項3】

1回に照射される部分の面積が、対応するチャネル領域の50%を超える、請求項1に記載の方法。

【請求項4】

1回に照射される部分の面積が、対応するチャネル領域の100%に等しい、請求項1に記載の方法。

【請求項5】

アクティブ・マトリックス回路によって駆動される画素を有するアクティブ・マトリックスOLEDデバイスであって、各画素が、

a)有機発光ダイオードと;

b)第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、ゲートとチャネル領域を備える第1のトランジスタと;

c)上記第1の電流に応答して上記有機発光ダイオードを流れる第2の電流を調節するため、ゲートとチャネル領域とを備える第2のトランジスタと第3のトランジスタを含んでおり、上記第1のトランジスタのチャネル領域の一部が、上記第2のトランジスタのチャネル領域と上記第3のトランジスタのチャネル領域の間に配置されている、アクティブ・マトリックスOLEDデバイス。

【請求項6】

上記第1のトランジスタのチャネル領域の上記一部の面積が、対応するチャネル領域の50%を超える、請求項5に記載のアクティブ・マトリックスOLEDデバイス。

【請求項7】

上記第1のトランジスタのチャネル領域の上記一部の面積が、対応するチャネル領域の100%に等しい、請求項5に記載のアクティブ・マトリックスOLEDデバイス。

【請求項8】

上記第1の電流と上記第2の電流の大きさが所定の比の関係にある、請求項5に記載のアクティブ・マトリックスOLEDデバイス。

【請求項9】

上記第1の電流が上記第2の電流よりも大きい、請求項5に記載のアクティブ・マトリックスOLEDデバイス。

【請求項10】

上記第1のトランジスタのゲートが、上記第2のトランジスタのゲートと上記第3のトランジスタのゲートに電気的に接続されている、請求項5に記載のアクティブ・マトリックスOLEDデバイス。

【請求項11】

上記第1のトランジスタのチャネル領域と、上記第2のトランジスタのチャネル領域と、上記第3のトランジスタのチャネル領域が、レーザーでアニールされた半導体層によって提供される、請求項5に記載のアクティブ・マトリックスOLEDデバイス。

【請求項12】

電流型アクティブ・マトリックスOLEDデバイスの製造方法であって、

a)基板の上方に半導体層を設け;

b)その基板の上方に導電層を設け;

c)上記半導体層と上記導電層の間に絶縁層を設け;

d)各画素を発光させるため、上記半導体層または上記導電層の上方に有機発光ダイオードを設け;

e)第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、上記半導体層の中に形成されたチャネル領域と、上記導電層の中に形成されたゲートとを備える第1のトランジスタを画素ごとに形成し;

f)上記第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第2のトランジスタと第3のトランジスタを画素ごとに形成し;

g)上記第1のトランジスタ、上記第2のトランジスタ、上記第3のトランジスタを形成する前、または形成した後に、供給源から供給されて1個以上のレーザー・パルスを発生させるパルス式レーザーを用いた照射により、上記半導体層のうちで、その第1のトランジスタのチャネル領域の一部に関係する領域と、その第2のトランジスタのチャネル領域の一部に関係する領域と、その第3のトランジスタのチャネル領域の一部に関係する領域をアニーリングする操作を含む方法。

【請求項13】

上記供給源と上記基板を相対運動させ、パルスが供給されたとき、上記第1のトランジスタと上記第2のトランジスタと上記第3のトランジスタのチャネル領域の上記一部が同時に照射されるようにする、請求項12に記載の方法。

【請求項14】

1回に照射される部分の面積が、対応するチャネル領域の50%を超える、請求項12に記載の方法。

【請求項15】

1回に照射される部分の面積が、対応するチャネル領域の100%に等しい、請求項12に記載の方法。

【請求項16】

アクティブ・マトリックス回路によって駆動される画素を有するアクティブ・マトリックスOLEDデバイスであって、各画素が、

a)有機発光ダイオードと;

b)第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、ゲートとチャネル領域をそれぞれが備える第1のトランジスタおよび第2のトランジスタと;

c)上記第1の電流に応答して上記有機発光ダイオードを流れる第2の電流を調節するため、ゲートとチャネル領域を備える第3のトランジスタとを含んでおり、上記第3のトランジスタのチャネル領域の一部が、上記第1のトランジスタのチャネル領域と上記第2のトランジスタのチャネル領域の間に配置されている、アクティブ・マトリックスOLEDデバイス。

【請求項17】

上記第3のトランジスタのチャネル領域の上記一部の面積が、対応するチャネル領域の50%を超える、請求項16に記載のアクティブ・マトリックスOLEDデバイス。

【請求項18】

上記第3のトランジスタのチャネル領域の上記一部の面積が、対応するチャネル領域の100%に等しい、請求項16に記載のアクティブ・マトリックスOLEDデバイス。

【請求項19】

上記第1の電流と上記第2の電流の大きさが所定の比の関係にある、請求項16に記載のアクティブ・マトリックスOLEDデバイス。

【請求項20】

上記第1の電流が上記第2の電流よりも大きい、請求項16に記載のアクティブ・マトリックスOLEDデバイス。

【請求項21】

上記第3のトランジスタのゲートが、上記第1のトランジスタのゲートと上記第2のトランジスタのゲートに電気的に接続されている、請求項16に記載のアクティブ・マトリックスOLEDデバイス。

【請求項22】

上記第1のトランジスタのチャネル領域と、上記第2のトランジスタのチャネル領域と、上記第3のトランジスタのチャネル領域が、レーザーでアニールされた半導体層によって提供される、請求項16に記載のアクティブ・マトリックスOLEDデバイス。

【請求項23】

電流型アクティブ・マトリックスOLEDデバイスの製造方法であって、

a)基板の上方に半導体層を設け;

b)その基板の上方に導電層を設け;

c)上記半導体層と上記導電層の間に絶縁層を設け;

d)各画素を発光させるため、上記半導体層または上記導電層の上方に有機発光ダイオードを設け;

e)第1の電流データとしての信号を受け取って対応する画素から出る光の明るさを調節するため、半導体層の中に形成されたチャネル領域と、導電層の中に形成されたゲートとをそれぞれが備える第1のトランジスタと第2のトランジスタを画素ごとに形成し;

f)上記第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第3のトランジスタを画素ごとに形成し;

g)上記第1のトランジスタ、上記第2のトランジスタ、上記第3のトランジスタを形成する前、または形成した後に、供給源から供給されて1個以上のレーザー・パルスを発生させるパルス式レーザーを用いた照射により、上記半導体層のうちで、その第1のトランジスタのチャネル領域の一部に関係する領域と、その第2のトランジスタのチャネル領域の一部に関係する領域と、その第3のトランジスタのチャネル領域の一部に関係する領域をアニーリングする操作を含む方法。

【請求項24】

上記供給源と上記基板を相対運動させ、パルスが供給されたとき、上記第1のトランジスタと上記第2のトランジスタと上記第3のトランジスタのチャネル領域の上記一部が同時に照射されるようにする、請求項23に記載の方法。

【請求項25】

1回に照射される部分の面積が、対応するチャネル領域の50%を超える、請求項23に記載の方法。

【請求項26】

1回に照射される部分の面積が、対応するチャネル領域の100%に等しい、請求項23に記載の方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−12766(P2013−12766A)

【公開日】平成25年1月17日(2013.1.17)

【国際特許分類】

【出願番号】特願2012−188568(P2012−188568)

【出願日】平成24年8月29日(2012.8.29)

【分割の表示】特願2007−532424(P2007−532424)の分割

【原出願日】平成17年9月13日(2005.9.13)

【出願人】(510059907)グローバル オーエルイーディー テクノロジー リミティド ライアビリティ カンパニー (45)

【Fターム(参考)】

【公開日】平成25年1月17日(2013.1.17)

【国際特許分類】

【出願日】平成24年8月29日(2012.8.29)

【分割の表示】特願2007−532424(P2007−532424)の分割

【原出願日】平成17年9月13日(2005.9.13)

【出願人】(510059907)グローバル オーエルイーディー テクノロジー リミティド ライアビリティ カンパニー (45)

【Fターム(参考)】

[ Back to top ]