OOR試験用パターン挿入回路及びOOR試験用パターン挿入方法

【課題】本発明は、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターン挿入回路の提供を目的とする。

【解決手段】本願発明のOOR試験用パターン挿入回路は、OTU3フレームデータDT0〜DT3が入力され、MFASをバイナリ形式で表したときの最下位の2つのビット「a1a0」に配置されているLMのうちの一方のビット「a0」を「r0」に反転させる符号反転部32と、LMの他方のビット「a1」を同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータ「b1」と置換し、符号反転部32からの「r0」を一方のビットに配置して、2bitのOOR試験用パターン「b1r0」を生成するアラームパターン生成部33と、任意のレーンのLMをアラームパターン生成部33の生成するOOR試験用パターンに置換するアラームパターン挿入部34と、を備える。

【解決手段】本願発明のOOR試験用パターン挿入回路は、OTU3フレームデータDT0〜DT3が入力され、MFASをバイナリ形式で表したときの最下位の2つのビット「a1a0」に配置されているLMのうちの一方のビット「a0」を「r0」に反転させる符号反転部32と、LMの他方のビット「a1」を同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータ「b1」と置換し、符号反転部32からの「r0」を一方のビットに配置して、2bitのOOR試験用パターン「b1r0」を生成するアラームパターン生成部33と、任意のレーンのLMをアラームパターン生成部33の生成するOOR試験用パターンに置換するアラームパターン挿入部34と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、OTU3(Optical−channel Transport Unit 3)におけるOOR試験用パターン挿入回路及びOOR試験用パターン挿入方法に関する。

【背景技術】

【0002】

ITU−T勧告G.709には、LLD(Logical Lane Distribution)を用いて、OTU3フレームデータを伝送する方式について記載されている(例えば、非特許文献1参照。)。OTU3フレームデータをLLDを用いて伝送する場合、OTU3の信号列はLLDにおいて4つのレーンに振り分けられる。また、ITU−T勧告G.798には、OTUフレームデータをLLDを用いて伝送する際に、障害があった場合の障害箇所の特定のために様々なアラームが定義されており、その1つにOOR(Out of Recovery)がある(例えば、非特許文献2参照。)。

【0003】

図7に、LLDを用いたOTU3フレームデータのレーン振り分けの一例を示す。全てのレーンにMFAS(Multi Frame Alignment Signal)が挿入されるように、フレームがローテーションしつつ、各レーンに振り分けられる。MFASには、レーンを区別するためにLM(Lane Marker)が挿入される。

【0004】

図8にOTU3フレームにおけるLMの位置を示す。MFASは、10進数表示では0〜255の値、16進数表示では0x00〜0xFFの値、バイナリ表示では00000000〜11111111の値をとる。MFASは、フレーム毎に1インクリメントされる。MFAS「a7a6a5a4a3a2a1a0」の最下位2bit「a1a0」がLMとなる。

【0005】

4つの各レーンのLMはそれぞれ異なる値をもつことになる。受信側においては、正常にOTU3フレームデータを受信している場合には、レーンごとにOTU3フレームデータに埋め込まれた一定の値のLMを受信する。信号断や各レーン間のスキュー変動などでOTU3フレームデータに異常があった場合には、同じ値のLMを受信できなくなるために、OORとしてアラームを検出する。OORを検出する際の検出条件は、5フレーム連続で正常時と異なる値のLMの受信である。OORを解除する際の解除条件は、5フレーム連続で一定の値のLMの受信である。測定器の送信側機能として、受信側がOORの検出及び解除を正しく行えることを確認するために、LMの値の擾乱を起こす機能が必要となる。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】ITU−T G.709

【非特許文献2】ITU−T G.798

【発明の概要】

【発明が解決しようとする課題】

【0007】

OTU3フレームデータをLLDを用いて伝送する方法は新規技術であるため、OORの挿入機能も新規技術である。

【0008】

また、受信側がOORの検出及び解除を正しく行えることを確認するためには、送信側でLMを変更してOTU3フレームに埋め込むことになる。その際には以下の条件を満たす必要がある。

第1の条件は、LMのみ、すなわちMFASの下位2bitのみが変更されていることである。

第2の条件は、検出条件数(5フレーム)以内に正常時に受信していたLMが含まれないことである。

第3の条件は、同じLMが解除条件数(5フレーム)以上連続しないことである。

第4の条件は、レーン番号とLMが一致するとは限らないことである。すなわち第0レーンのLMが0とは限らず、例えば第0レーンのLMが1で他のレーンに0のLMが割り当てられている可能性がある。

【0009】

受信側がOORの検出及び解除を正しく行えることを確認するために、送信側で前記4つの条件を満たすLMを生成する方法として、範囲外の固定値に変更する方法が考えられる。しかし、LMはMFASの下位2bitを用いているため、0〜3の4値以外の値を用いることができない。このため、レーンも4つであることから、範囲外の固定値に変更することはできない問題がある。

【0010】

また、値をインクリメントまたはデクリメントする方法が考えられる。しかし、LMは0〜3の4値以外の値を用いることができないため、5フレーム以内で正常時のLMになってしまう。このため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第2の条件を満たすことができず、受信側はOORの検出を正しく行えない問題がある。

【0011】

そこで、本発明は、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターン挿入回路、OTU3フレームデータ送信装置、OOR試験システム、OOR試験用パターン挿入方法、OTU3フレームデータ送信方法及びOOR試験方法の提供を目的とする。

【課題を解決するための手段】

【0012】

本願発明のOOR試験用パターン挿入回路は、マルチレーン構造を有するOTU3フレームデータのうちの任意のレーンのOTU3フレームデータが入力され、入力された前記OTU3フレームデータに含まれるMFASをバイナリ形式で表したときの最下位の2つのビットに配置されているLMのうちの一方のビットを反転させる符号反転部(32)と、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換し、前記符号反転部からの符号を前記一方のビットに配置して、2bitのOOR試験用パターンを生成するアラームパターン生成部(33)と、前記任意のレーンの前記LMを前記アラームパターン生成部の生成する前記OOR試験用パターンに置換するアラームパターン挿入部(34)と、を備える。

【0013】

符号反転部と、アラームパターン生成部と、を備えるため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記4つの条件を満たすOOR試験用パターンを生成することができる。アラームパターン挿入部を備えるため、OOR試験用パターンをOTU3フレームデータに挿入することができる。したがって、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターン挿入回路を提供することができる。

【0014】

本願発明のOOR試験用パターン挿入回路では、前記アラームパターン生成部は、前記LMの他方のビットを、前記MFASの下位第2ビット、下位第3ビット又は下位第4ビットのいずれかと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換してもよい。

本発明により、アラームパターン生成部は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記4つの条件を満たすOOR試験用パターンを生成することができる。

【0015】

本願発明のOOR試験用パターン挿入回路では、同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータを出力するビット生成部(35)をさらに備え、前記アラームパターン生成部は、前記LMの他方のビットを前記ビット生成部からの出力データと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換してもよい。

本発明により、アラームパターン生成部は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記4つの条件を満たすOOR試験用パターンを生成することができる。

【0016】

本願発明のOTU3フレームデータ送信装置は、前記OTU3フレームデータを生成するOTU3フレームデータ生成回路(11)と、前記OTU3フレームデータ生成回路からの前記OTU3フレームデータを第0レーンから第3レーンの4つのレーンに分配する分配回路(12)と、前記分配回路によって分配された前記OTU3フレームデータのうちの任意のレーンのOTU3フレームデータが入力され、入力された前記OTU3フレームデータに含まれる前記LMを前記OOR試験用パターンに置換する、本願発明のOOR試験用パターン挿入回路(13)と、前記OOR試験用パターン挿入回路によって前記LMが前記OOR試験用パターンに置換された前記OTU3フレームデータを伝送路に送信する送信回路(14)と、を備える。

【0017】

OTU3フレームデータ生成回路と、分配回路と、送信回路と、を備えるため、OTU3フレームデータを送信することができる。ここで、本願発明のOOR試験用パターン挿入回路を備えるため、OOR試験用パターンをOTU3フレームデータに挿入することができる。したがって、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOTU3フレームデータ送信装置を提供することができる。

【0018】

本願発明のOOR試験システムは、本願発明のOTU3フレームデータ送信装置(101)と、前記伝送路を介して伝送された前記OTU3フレームデータを受信し、当該受信によって得られた前記OTU3フレームデータのレーンごとの前記LMの位置に配置されているビット列が5回以上連続して同じ場合は同期状態となり、前記LMの位置に配置されているビット列と同期しているビット列とが5回以上連続して異なる場合は同期状態が外れてOORのアラームを出力するOTU3フレームデータを受信する被測定対象(102)と、を備える。

【0019】

本願発明のOTU3フレームデータ送信装置と、OTU3フレームデータを受信する被測定対象と、を備えるため、OOR試験用パターンを挿入したOTU3フレームデータを送信して、被測定対象である受信側がOORの検出及び解除を正しく行えることを確認することができる。したがって、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験システムを提供することができる。

【0020】

本願発明のOOR試験用パターン挿入方法は、マルチレーン構造を有するOTU3フレームデータのうちの任意のレーンのOTU3フレームデータに含まれるMFASをバイナリ形式で表したときの最下位の2つのビットに配置されているLMのうちの一方のビットを反転させて前記一方のビットに配置するとともに、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換して、2bitのOOR試験用パターンを生成するアラームパターン生成手順(S302)と、前記任意のレーンの前記LMを前記アラームパターン生成手順で生成した前記OOR試験用パターンに置換するアラームパターン挿入手順(S303)と、を順に有する。

【0021】

アラームパターン生成手順と、アラームパターン挿入手順と、を有するため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記4つの条件を満たすOOR試験用パターンを生成してOTU3フレームデータに挿入することができる。したがって、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターン挿入方法を提供することができる。

【0022】

本願発明のOOR試験用パターン挿入方法では、前記アラームパターン生成手順において、前記LMの他方のビットを、前記MFASの下位第2ビット、下位第3ビット又は下位第4ビットのいずれかと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換してもよい。

本発明により、アラームパターン生成手順において、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記4つの条件を満たすOOR試験用パターンを生成することができる。

【0023】

本願発明のOOR試験用パターン挿入方法では、前記アラームパターン生成手順において、同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータを生成し、前記LMの他方のビットを生成したデータと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換してもよい。

本発明により、アラームパターン生成手順において、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記4つの条件を満たすOOR試験用パターンを生成することができる。

【0024】

本願発明のOTU3フレームデータ送信方法は、本願発明のOOR試験用パターン挿入方法と、前記アラームパターン生成手順の前に、前記OTU3フレームデータを生成するOTU3フレームデータ生成手順(S101)と、前記アラームパターン挿入手順の後に、前記アラームパターン挿入手順によって前記LMが前記OOR試験用パターンに置換された前記OTU3フレームデータを伝送路に送信する送信手順(S104)と、を有する。

【0025】

OTU3フレームデータ生成手順と、送信手順と、を有するため、OTU3フレームデータを送信することができる。ここで、本願発明のOOR試験用パターン挿入方法を有するため、OOR試験用パターンをOTU3フレームデータに挿入することができる。したがって、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOTU3フレームデータ送信方法を提供することができる。

【0026】

本願発明のOOR試験方法は、本願発明のOTU3フレームデータ送信方法と、前記OTU3フレームデータ送信方法によって送信された前記OTU3フレームデータを受信する受信手順(S201)と、前記受信手順によって得られた前記OTU3フレームデータのレーンごとの前記LMの位置に配置されているビット列が5回以上連続して同じ場合は同期状態となり、前記LMの位置に配置されているビット列と同期しているビット列とが5回以上連続して異なる場合は同期状態がはずれてOORのアラームを出力するOOR判定手順(S202)と、を順に有する。

【0027】

本願発明のOTU3フレームデータ送信方法と、受信手順と、OOR判定手順と、を有するため、OOR試験用パターンを挿入したOTU3フレームデータを送信して、受信側がOORの検出及び解除を正しく行えることを確認することができる。したがって、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験方法を提供することができる。

【0028】

なお、上記各発明は、可能な限り組み合わせることができる。

【発明の効果】

【0029】

本発明によれば、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターン挿入回路、OTU3フレームデータ送信装置、OOR試験システム、OOR試験用パターン挿入方法、OTU3フレームデータ送信方法及びOOR試験方法を提供することができる。

【図面の簡単な説明】

【0030】

【図1】実施形態1に係るOOR試験システムの一例を示す。

【図2】実施形態1に係るOOR試験方法の一例を示す。

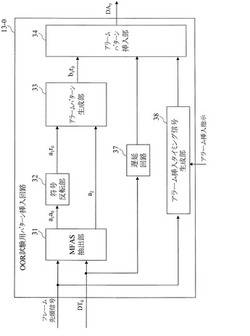

【図3】OOR試験用パターン挿入回路の第1形態を示す。

【図4】MFASとOOR試験用パターンの具体例を示す。

【図5】OOR判定回路25−0の一例を示す。

【図6】OOR試験用パターン挿入回路の第2形態を示す。

【図7】LLDを用いたOTU3フレームデータのレーン振り分けの一例を示す。

【図8】OTU3フレームにおけるLMの位置を示す。

【発明を実施するための形態】

【0031】

添付の図面を参照して本発明の実施形態を説明する。以下に説明する実施形態は本発明の実施の例であり、本発明は、以下の実施形態に制限されるものではない。なお、本明細書及び図面において符号が同じ構成要素は、相互に同一のものを示すものとする。

【0032】

(実施形態1)

図1に、本実施形態に係るOOR試験システムの一例を示す。本実施形態に係るOOR試験システムは、OTU3フレームデータ送信装置101と、OTU3フレームデータを受信する被測定対象102と、を備える。OTU3フレームデータを受信する被測定対象102は、OTU3フレームデータを受信する装置又はデバイスである。

【0033】

OTU3フレームデータ送信装置101は、OTU3フレームデータ生成回路11と、分配回路12と、OOR試験用パターン挿入回路13と、送信回路14と、を備える。OTU3フレームデータを受信する被測定対象102は、受信回路21と、フレーム検出回路22と、集約回路23と、OTU3フレームデータ解析回路24と、OOR判定回路25と、を備える。

【0034】

図2に、本実施形態に係るOOR試験方法の一例を示す。本実施形態に係るOOR試験方法は、OTU3フレームデータ送信方法S100と、受信手順S201と、OOR判定手順S202と、を順に有する。OTU3フレームデータ送信方法S100は、OTU3フレームデータ生成手順S101と、本実施形態に係るOOR試験用パターン挿入方法S300と、送信手順S104と、を順に有する。OOR試験用パターン挿入方法S300は、アラームパターン生成手順S302と、アラームパターン挿入手順S303と、を順に有する。

【0035】

OTU3フレームデータ生成手順S101では、OTU3フレームデータ生成回路11が、OTU3フレームデータDTを生成する。例えば、データが入力され、データを予め定められた長さのフレームに分割して、フレームごとにMFASを付す。このときに、MFASを1つずつインクリメントする。これにより、OTU3フレームデータ生成回路11は、OTU3フレームデータDTを生成する。

【0036】

分配回路12は、OTU3フレームデータ生成回路11からのOTU3フレームデータDTを第0レーンから第3レーンの4つのレーンに分配する。例えば、分配回路12は、OTU3フレームデータDTをフレームごとのOTU3フレームデータDT0〜DT3に分割する。そして、分配回路12は、OTU3フレームデータDT0を第0レーンに分配し、OTU3フレームデータDT1を第1レーンに分配し、OTU3フレームデータDT2を第2レーンに分配し、OTU3フレームデータDT3を第3レーンに分配する。

【0037】

アラームパターン生成手順S302では、OOR試験用パターン挿入回路13が、OTU3フレームデータDT0〜DT3のLMを用いてOOR試験用パターンを生成する。例えば、OOR試験用パターン挿入回路13は、レーンごとにOOR試験用パターン挿入回路13−0〜13−3を備える。OOR試験用パターン挿入回路13−0〜13−3は、それぞれ、OTU3フレームデータDT0〜DT3のLMを用いてOOR試験用パターンを生成する。

【0038】

例えば、OOR試験用パターン挿入回路13−0が、OTU3フレームデータDT0に含まれるMFASをバイナリ形式で表したときの最下位の2つのビットに配置されているLMのうちの一方のビットを反転させて一方のビットに配置するとともに、MFASの下位2bitに配置されているLMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換して、2bitのOOR試験用パターンを生成する。同符号の連続が4回以下となるようにとは、例えば、符号「0」のデータと置換し、その次は符号「0」のデータと置換し、その次は符号「0」のデータと置換し、その次は符号「0」のデータと置換した場合、その次は符号「1」のデータとなるようにという意味である。

【0039】

図3に、OOR試験用パターン挿入回路13−0の第1形態を示す。図3に示すOOR試験用パターン挿入回路13−0は、MFAS抽出部31と、符号反転部32と、アラームパターン生成部33と、アラームパターン挿入部34と、遅延回路37と、アラーム挿入タイミング信号生成部38と、を備える。

【0040】

MFAS抽出部31には、フレーム先頭信号とOTU3フレームデータDT0が入力される。そして、MFAS抽出部31は、フレーム先頭信号に従って、OTU3フレームデータDT0からMFASを抽出する。そして、MFASをバイナリ形式で表した8つのビット「a7a6a5a4a3a2a1a0」を取得し、最下位の2つのビット「a1a0」を符号反転部32に出力する。

【0041】

符号反転部32は、2つのビット「a1a0」のうちの一方のビットを反転させる。例えば、一方のビットが第0ビットa0、他方のビットが第1ビットa1である場合、ビットa0を反転させ、反転させたビットr0をアラームパターン生成部33に出力する。反転とは、例えば、ビットa0の符号が「1」であればビットr0の符号は「0」となり、ビットa0の符号が「0」であればビットr0の符号は「1」となる。

【0042】

図4に、MFASとOOR試験用パターンの具体例を示す。第0レーンにLM「0」、第1レーンにLM「1」、第2レーンにLM「2」、第3レーンにLM「3」が割り振られている。なお、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第4条件で説明したとおり、これは一例であって、第0レーンにLM「0」が割り振られているとは限らず、第0レーンのLMは、「1」であってもよいし、「2」であってもよいし、「3」であってもよい。

【0043】

第0レーンのMFASは「0」、「4」、「8」、・・・「252」となる。これらMFASをバイナリ形式で表すと、「00000000」、「00000100」、「00001000」、・・・「11111100」である。このように、MFASをバイナリ形式で表したときの最下位の2つのビットは全て「00」であり、LM「0」が割り振られている。この場合、ビットa0は「0」であり、これを反転させたビットr0は「1」となる。

【0044】

アラームパターン生成部33は、LMの他方のビットa1をビットb1に置換し、ビットr0をビットa0の位置に配置して、2bitのOOR試験用パターンを生成する。ここで、ビットa1からビットb1への置換は、同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換する。これによって、OOR試験用パターン「b1r0」を生成する。

【0045】

例えば、図4に示す第0レーンのMFASの下位第2ビットa2は、「0」、「1」、「0」、「1」、・・・「1」のように、同符号の連続が1回以下となる。このため、ビットa1をMFASの下位第2ビットa2に置換することによって、LMの他方のビットa1を同符号の連続が1回以下となるように符号「0」のデータ又は符号「1」のデータと置換することができる。これにより、「01」、「11」、「01」、「11」、・・・「11」、すなわち値「1」と「3」の繰り返しとなるOOR試験用パターン「b1r0」を生成することができる。

【0046】

このように、LMが0から3であること、及びMFASが0から255でOTU3フレーム毎に1インクリメントすることを利用しており、あるレーンにおけるLMの下位第0ビットa0を反転した値r0とMFASの下位第2ビットa2の値b1を組み合わせてOOR試験用パターン「b1r0」を生成する。

【0047】

図2に示すアラームパターン挿入手順S303では、アラームパターン挿入部34に、OTU3フレームデータDT0及びOOR試験用パターン「b1r0」が入力される。このとき、遅延回路37が、OTU3フレームデータDT0及びOOR試験用パターン「b1r0」の入力タイミングを調整する。また、アラーム挿入タイミング信号生成部38が、アラーム挿入指示に従って、OTU3フレームデータDT0のアラームパターンに置換するLMの位置を示すタイミング信号をアラームパターン挿入部34に出力する。そして、アラームパターン挿入部34が、アラーム挿入タイミング信号生成部38からのタイミング信号に従って、OTU3フレームデータDT0のLM「a1a0」をOOR試験用パターン「b1r0」に置換してOTU3フレームデータDA0を出力する。

【0048】

OTU3フレームデータDA0のMFASは「a7a6a5a4a3a2b1r0」となっているため、LMのみ、すなわちMFASの下位2bitのみが変更されている。このため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件を満たす。また、図4に示すMFASにおいて、第0レーンのOOR試験用パターン「b1r0」は、値「1」と値「3」の繰り返しであり、正常時に受信していたLM「0」が含まれないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第2の条件を満たす。また、同じLMが連続しないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第3の条件を満たす。さらに、第0レーンにLM「1」の割り振られている場合も同様に正常時のLM「1」とは異なる値「0」と値「2」を繰り返すOOR試験用パターンとなり、第0レーンにLM「2」が割り振られている場合も同様に正常時のLM「2」とは異なる値「1」と値「3」を繰り返すOOR試験用パターンとなり、第0レーンにLM「3」が割り振られている場合も同様に正常時のLM「3」とは異なる値「0」と値「2」を繰り返すOOR試験用パターンとなるため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第4の条件を満たす。

【0049】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たすOTU3フレームデータDA0を出力することができる。

【0050】

図1に示すOOR試験用パターン挿入回路13−1,13−2及び13−3は、それぞれ、OOR試験用パターン挿入回路13−0と同様にして、正常時のLMとは異なる2値を繰り返すOOR試験用パターンが挿入されたOTU3フレームデータDA1,DA2及びDA3を出力することができる。

【0051】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たすOTU3フレームデータDA0〜DA3を出力することができる。

【0052】

送信手順S104では、OOR試験用パターン挿入回路13によってLMがOOR試験用パターンに置換されたOTU3フレームデータDA0〜DA3が送信回路14に入力される。そして、送信回路14は、OTU3フレームデータDA0〜DA3を伝送路に送信する。

【0053】

受信手順S201では、OTU3フレームデータ送信装置101から出力されたOTU3フレームデータを受信する。例えば、受信回路21が、OTU3フレームデータを受信し、第0レーンから第3レーンのそれぞれのレーンにOTU3フレームデータDR0〜DR3を出力する。フレーム検出回路22は、受信回路21からのOTU3フレームデータDR0〜DR3のフレームの先頭を検出してフレーム間のデスキューなどのフレーム処理を行う。このとき、各レーンに備わるフレーム検出回路22−0〜22−3が、レーンごとにフレーム処理を行う。集約回路23は、フレーム検出回路22からのOTU3フレームデータDD0〜DD3を集約してOTU3フレームデータDDを構築する。OTU3フレームデータ解析回路24は、集約回路23からのOTU3フレームデータDDを解析する。

【0054】

OOR判定手順S202では、OOR判定回路25が、受信手順S201で受信したOTU3フレームデータDR0〜DR3のOORの検出及び解除を行う。例えば、OOR判定回路25は、OTU3フレームデータDD0のOORの検出及び解除を行うOOR判定回路25−0と、OTU3フレームデータDD1のOORの検出及び解除を行うOOR判定回路25−1と、OTU3フレームデータDD2のOORの検出及び解除を行うOOR判定回路25−2と、OTU3フレームデータDD3のOORの検出及び解除を行うOOR判定回路25−3と、を備える。

【0055】

図5に、OOR判定回路25−0の一例を示す。OOR判定回路25−0は、MFAS抽出部51と、連続性検出部52と、を備える。フレーム検出回路22−0からMFAS抽出部51に、フレーム先頭信号及びOTU3フレームデータDD0が入力される。MFAS抽出部51は、OTU3フレームデータDD0からLMの位置に配置されているビット列を抽出する。連続性検出部52は、MFAS抽出部51からのLMの位置に配置されているビット列が5回以上連続して同じ場合は同期状態となり、LMの位置に配置されているビット列と同期しているビット列とが5回以上連続して異なる場合は同期状態がはずれてOORのアラームを出力する。

【0056】

例えば、正常なLMである「00」のビット列が5回以上連続している状態では、同期状態となる。その後、ビット列が「01」となっても同期状態を維持している。そして、「01」の後に、「11」、「01」、「11」、「01」と続き、検出条件数(5フレーム)に至る。すると、同期状態がはずれてOORのアラームを出力する。本実施形態では、第0レーンのDD0のLMの位置に配置されているビット列は、OOR試験用パターンが挿入されているときには値「1」と値「3」の繰り返しであり、正常時に受信していたLM「0」が含まれない。このため、検出条件数が5フレームの場合、送信側でOOR試験用パターンを5回以上挿入すれば、OOR判定回路25−0はOORのアラームを出力する。

【0057】

OOR判定回路25−1〜25−3についてもOOR判定回路25−0と同様に、送信側でOOR試験用パターンを5回以上挿入すれば、OOR判定回路25−1〜25−3はOORのアラームを出力する。

【0058】

以上説明したように、OOR試験用パターン挿入回路13及びOOR試験用パターン挿入方法S300は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たすOTU3フレームデータDA0〜DA3を出力することができる。したがって、OTU3フレームデータ送信装置101及びOTU3フレームデータ送信方法S100は、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターンをOTU3フレームデータDT0〜DT3に挿入したOTU3フレームデータDA0〜DA3を送信することができる。

【0059】

また、本実施形態に係るOOR試験システムはOTU3フレームデータ送信装置101を備え、本実施形態に係るOOR試験方法はOTU3フレームデータ送信方法S100を有する。したがって、本実施形態に係るOOR試験システム及びOOR試験方法は、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターンをOTU3フレームデータDT0〜DT3に挿入したOTU3フレームデータDA0〜DA3を送受信して、OORの検出及び解除を正しく行えることを確認することができる。

【0060】

なお、アラームパターン生成手順S302において第0レーンのアラームパターン生成部33が反転させる一方のビットはMFASの下位第1ビットa1であってもよい。この場合、他方のビットがMFASの下位第0ビットa0となる。例えば、ビットa1を反転させてビット「r1」を生成する。また、ビットa0を、同符号の連続が4回以下となるようにビットb0に置換する。これにより、2bitのOOR試験用パターン「r1b0」を生成する。図4に示すMFASであれば、OOR試験用パターン「r1b0」は「2」と「3」の繰り返しとなる。このように、OOR試験用パターンが「r1b0」であっても、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。第1レーンから第3レーンのOOR試験用パターンについても同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。

【0061】

また、本実施形態では、すべてのレーンにOOR試験用パターン挿入回路13−0,13−1,13−2,13−3を備える構成としたが、これに限定されない。例えば、各レーンに共通のOOR試験用パターン挿入回路を1つ備え、OOR試験用パターン挿入回路をいずれかのレーンに挿入可能にしてもよい。本実施形態に係るOOR試験用パターン挿入回路は、入力されたMFASを用いてOOR試験用パターンを生成するため、いずれのレーンに挿入しても適切なOOR試験用パターンを生成することができる。

【0062】

また、本実施形態では、検出条件数及び解除条件数が5フレームである場合について説明したが、これに限定されない。例えば、検出条件数及び解除条件数は4フレーム以下であってもよい。本実施形態では、ビットa1をMFASの下位第2ビットa2に置換することによって、正常時のLM「0」とは異なる値「1」と値「3」を繰り返すOOR試験用パターンを生成することができる。このため、検出条件数及び解除条件数が2フレームの場合であっても、受信側がOORの検出及び解除を正しく行えることを確認することができる。したがって、検出条件数及び解除条件数が4以下に設定されている場合であっても、受信側がOORの検出及び解除を正しく行えることを確認することができる。

【0063】

(実施形態2)

本実施形態に係るOOR試験システムは、図3に示すアラームパターン生成部33が、LMの他方のビットa1を、MFASの下位第3ビットa3と置換することによって、LMの他方のビットa1を同符号の連続が2回以下となるように符号「0」のデータ又は符号「1」のデータと置換する。

【0064】

例えば、図4に示す第0レーンのMFASの下位第3ビットは、「0」、「0」、「1」、「1」、「0」、「0」、「1」、「1」、・・・「1」のように、同符号の連続が2回以下となる。このため、ビットa1をMFASの下位第3ビットa3に置換することによって、LMの他方のビットa1を同符号の連続が2回以下となるように符号「0」のデータ又は符号「1」のデータと置換することができる。

【0065】

この場合、第0レーンのOOR試験用パターン「b1r0」は、「01」、「01」、「11」、「11」、「01」、「01」、「11」、「11」、・・・「11」のように、「1」、「1」、「3」、「3」の繰り返しとなる。このため、同じLMが2回以内となっており、3回以上連続しない。このように、正常時に受信していたLM「0」が含まれないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第2の条件を満たす。また、同じLMが3回以上連続しないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第3の条件を満たす。さらに、第0レーンにLM「1」又はLM「2」又はLM「3」が割り振られている場合も同様に、正常時のLMとは異なる2値となり、同じ値が2回以内となっており、3回以上連続しない。このため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第4の条件を満たす。

【0066】

OOR試験用パターン挿入回路13−1,13−2及び13−3は、それぞれ、OOR試験用パターン挿入回路13−0と同様にして、正常時のLMとは異なる2値となり、同じ値が2回以内となっており、3回以上連続しないOOR試験用パターンが挿入されたOTU3フレームデータDA1,DA2及びDA3を出力することができる。

【0067】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たすOTU3フレームデータDA0〜DA3を出力することができる。

【0068】

なお、アラームパターン生成手順S302においてアラームパターン生成部33が反転させる一方のビットはMFASの下位第1ビットa1であってもよい。この場合、他方のビットがMFASの下位第0ビットa0となる。例えば、ビットa1を反転させてビット「r1」を生成する。また、ビットa0を、同符号の連続が4回以下となるようにビットb0に置換する。これにより、2bitのOOR試験用パターン「r1b0」を生成する。図4に示すMFASであれば、第0レーンの場合、OOR試験用パターン「r1b0」は「2」、「2」、「3」、「3」の繰り返しとなる。このように、OOR試験用パターンが「r1b0」であっても、OOR試験用パターンが「b1r0」の場合と同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。第1レーンから第3レーンのOOR試験用パターンについても同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。

【0069】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300を用いた場合も、実施形態1と同様に、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターンをOTU3フレームデータDT0〜DT3に挿入したOTU3フレームデータDA0〜DA3を出力することができる。

【0070】

(実施形態3)

本実施形態に係るOOR試験システムは、図3に示すアラームパターン生成部33が、LMの他方のビットa1を、MFASの下位第4ビットa4と置換することによって、LMの他方のビットa1を同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換する。

【0071】

例えば、図4に示す第0レーンのMFASの下位第4ビットは、「0」、「0」、「0」、「0」、「1」、「1」、「1」、「1」、「0」、・・・「1」のように、同符号の連続が4回以下となる。このため、ビットa1をMFASの下位第4ビットに置換することによって、LMの他方のビットa1を同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換することができる。

【0072】

この場合、第0レーンのOOR試験用パターン「b1r0」は、「01」、「01」、「01」、「01」、「11」、「11」、「11」、「11」、「01」、「01」、「01」、「01」、「11」、・・・「11」のように、「1」、「1」、「1」、「1」、「3」、「3」、「3」、「3」の繰り返しとなる。このため、同じLMが4回以内となっており、5回以上連続しない。このように、正常時に受信していたLM「0」が含まれないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第2の条件を満たす。また、同じLMが5回以上連続しないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第3の条件を満たす。さらに、第0レーンにLM「1」又はLM「2」又はLM「3」が割り振られている場合も同様に、正常時のLMとは異なる2値となり、同じ値が4回以内となっており、5回以上連続しない。このため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第4の条件を満たす。

【0073】

OOR試験用パターン挿入回路13−1,13−2及び13−3は、それぞれ、OOR試験用パターン挿入回路13−0と同様にして、正常時のLMとは異なる2値となり、同じ値が4回以内となっており、5回以上連続しないOOR試験用パターンが挿入されたOTU3フレームデータDA1,DA2及びDA3を出力することができる。

【0074】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たすOTU3フレームデータDA0〜DA3を出力することができる。

【0075】

なお、アラームパターン生成手順S302においてアラームパターン生成部33が反転させる一方のビットはMFASの下位第1ビットa1であってもよい。この場合、他方のビットがMFASの下位第0ビットa0となる。例えば、ビットa1を反転させてビット「r1」を生成する。また、ビットa0を、同符号の連続が4回以下となるようにビットb0に置換する。これにより、2bitのOOR試験用パターン「r1b0」を生成する。図4に示すMFASであれば、第0レーンの場合、OOR試験用パターン「r1b0」は「2」、「2」、「2」、「2」、「3」、「3」、「3」、「3」の繰り返しとなる。このように、OOR試験用パターンが「r1b0」であっても、OOR試験用パターンが「b1r0」の場合と同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。第1レーンから第3レーンのOOR試験用パターンについても同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。

【0076】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300を用いた場合も、実施形態1と同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するためのOOR試験用パターンをOTU3フレームデータDT0〜DT3に挿入したOTU3フレームデータDA0〜DA3を出力することができる。

【0077】

(実施形態4)

本実施形態に係るOOR試験システムは、図3に示すOOR試験用パターン挿入回路13−0の第1形態に代えて、OOR試験用パターン挿入回路13−0の第2形態を備える。そして、図2に示すアラームパターン生成手順S302において、OOR試験用パターン挿入回路13−0の第2形態が、OTU3フレームデータDT0〜DT3のLMを用いてOOR試験用パターンを生成する。図6に、OOR試験用パターン挿入回路の第2形態を示す。

【0078】

図6に示すOOR試験用パターン挿入回路13−0は、MFAS抽出部31と、符号反転部32と、アラームパターン生成部36と、アラームパターン挿入部34と、ビット生成部35と、遅延回路37と、アラーム挿入タイミング信号生成部38と、を備える。MFAS抽出部31、符号反転部32、アラームパターン生成部36、アラームパターン挿入部34、遅延回路37及びアラーム挿入タイミング信号生成部38については、実施形態1で説明したとおりである。

【0079】

バイナリ形式で表したMFASが「a7a6a5a4a3a2a1a0」であり、LMの一方のビットがMFASの下位第0ビットa0、LMの他方のビットがMFASの下位第1ビットa1である場合、符号反転部32は、ビットa0を反転させ、反転させたビットr0をアラームパターン生成部36に出力する。

【0080】

ビット生成部35は、同符号の連続が4回以下となるようなビットb1を出力する。例えば、ビット生成部35は、「0」、「1」、「0」、「1」、・・・「1」のように、同符号の連続が1回以下となるようなビット列を出力する。

【0081】

アラームパターン生成部36は、LMの他方のビットa1をビットb1に置換し、ビットr0をビットa0の位置に配置して、2bitのOOR試験用パターン「b1r0」を生成する。

【0082】

例えば、ビットb1は「0」、「1」、「0」、「1」、・・・「1」のように、同符号の連続が1回以下となるようなビット列である。このため、ビットa1をビットb1に置換することによって、LMの他方のビットa1を同符号の連続が1回以下となるように符号「0」のデータ又は符号「1」のデータと置換することができる。

【0083】

図2に示すアラームパターン挿入手順S303では、アラームパターン挿入部34が、OTU3フレームデータDT0のLM「a1a0」をアラームパターン生成手順S302で生成したOOR試験用パターン「b1r0」に置換する。これにより、アラームパターン挿入部34からOTU3フレームデータDA0が出力される。

【0084】

OTU3フレームデータDA0のMFASは「a7a6a5a4a3a2b1r0」となっているため、LMのみ、すなわちMFASの下位2bitのみが変更されている。このため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件を満たす。また、図4に示すMFASにおいて、第0レーンのOOR試験用パターン「b1r0」は、値「1」と値「3」の繰り返しであり、正常時に受信していたLM「0」が含まれないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第2の条件を満たす。また、同じLMが連続しないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第3の条件を満たす。さらに、第0レーンにLM「1」又はLM「2」又はLM「3」が割り振られている場合も同様に、正常時のLMとは異なる2値を繰り返す。このため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第4の条件を満たす。

【0085】

OOR試験用パターン挿入回路13−1,13−2及び13−3は、それぞれ、OOR試験用パターン挿入回路13−0と同様にして、正常時のLMとは異なる2値を繰り返すOOR試験用パターンが挿入されたOTU3フレームデータDA1,DA2及びDA3を出力することができる。

【0086】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たすOTU3フレームデータDA0〜DA3を出力することができる。

【0087】

なお、アラームパターン生成手順S302においてアラームパターン生成部33が反転させる一方のビットはMFASの下位第1ビットa1であってもよい。この場合、他方のビットがMFASの下位第0ビットa0となる。例えば、ビットa1を反転させてビット「r1」を生成する。また、ビットa0を、同符号の連続が4回以下となるようにビットb0に置換する。これにより、2bitのOOR試験用パターン「r1b0」を生成する。図4に示すMFASであれば、第0レーンの場合、OOR試験用パターン「r1b0」は「2」と「3」の繰り返しとなる。このように、OOR試験用パターンが「r1b0」であっても、OOR試験用パターンが「b1r0」の場合と同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。第1レーンから第3レーンのOOR試験用パターンについても同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。

【0088】

また、ビット生成部35は、「0」、「0」、「1」、「1」、「0」、「0」、「1」、「1」、・・・「1」のように、同符号の連続が2回以下となるようなビット列を出力してもよい。また、ビット生成部35は、「0」、「0」、「0」、「1」、「1」、「1」、「0」、「0」、「0」、・・・「1」のように、同符号の連続が3回以下となるようなビット列を出力してもよい。また、ビット生成部35は、「0」、「0」、「0」、「0」、「1」、「1」、「1」、「1」、「0」、・・・「1」のように、同符号の連続が4回以下となるようなビット列を出力してもよい。これらの場合も、実施形態2及び3において説明したように、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たすことができる。

【0089】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300を用いた場合も、実施形態1と同様に、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターンをOTU3フレームデータDT0〜DT3に挿入したOTU3フレームデータDA0〜DA3を出力することができる。

【産業上の利用可能性】

【0090】

本発明は情報通信産業に適用することができる。

【符号の説明】

【0091】

11:OTU3フレームデータ生成回路

12:分配回路

13、13−0、13−1、13−2、13−3:OOR試験用パターン挿入回路

14:送信回路

21:受信回路

22:フレーム検出回路

23:集約回路

24:OTU3フレームデータ解析回路

25、25−0、25−1、25−2、25−3:OOR判定回路

31:MFAS抽出部

32:符号反転部

33、36:アラームパターン生成部

34:アラームパターン挿入部

35:ビット生成部

37:遅延回路

38:アラーム挿入タイミング信号生成部

51:MFAS抽出部

52:連続性検出部

101:OTU3フレームデータ送信装置

102:OTU3フレームデータを受信する被測定対象

【技術分野】

【0001】

本発明は、OTU3(Optical−channel Transport Unit 3)におけるOOR試験用パターン挿入回路及びOOR試験用パターン挿入方法に関する。

【背景技術】

【0002】

ITU−T勧告G.709には、LLD(Logical Lane Distribution)を用いて、OTU3フレームデータを伝送する方式について記載されている(例えば、非特許文献1参照。)。OTU3フレームデータをLLDを用いて伝送する場合、OTU3の信号列はLLDにおいて4つのレーンに振り分けられる。また、ITU−T勧告G.798には、OTUフレームデータをLLDを用いて伝送する際に、障害があった場合の障害箇所の特定のために様々なアラームが定義されており、その1つにOOR(Out of Recovery)がある(例えば、非特許文献2参照。)。

【0003】

図7に、LLDを用いたOTU3フレームデータのレーン振り分けの一例を示す。全てのレーンにMFAS(Multi Frame Alignment Signal)が挿入されるように、フレームがローテーションしつつ、各レーンに振り分けられる。MFASには、レーンを区別するためにLM(Lane Marker)が挿入される。

【0004】

図8にOTU3フレームにおけるLMの位置を示す。MFASは、10進数表示では0〜255の値、16進数表示では0x00〜0xFFの値、バイナリ表示では00000000〜11111111の値をとる。MFASは、フレーム毎に1インクリメントされる。MFAS「a7a6a5a4a3a2a1a0」の最下位2bit「a1a0」がLMとなる。

【0005】

4つの各レーンのLMはそれぞれ異なる値をもつことになる。受信側においては、正常にOTU3フレームデータを受信している場合には、レーンごとにOTU3フレームデータに埋め込まれた一定の値のLMを受信する。信号断や各レーン間のスキュー変動などでOTU3フレームデータに異常があった場合には、同じ値のLMを受信できなくなるために、OORとしてアラームを検出する。OORを検出する際の検出条件は、5フレーム連続で正常時と異なる値のLMの受信である。OORを解除する際の解除条件は、5フレーム連続で一定の値のLMの受信である。測定器の送信側機能として、受信側がOORの検出及び解除を正しく行えることを確認するために、LMの値の擾乱を起こす機能が必要となる。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】ITU−T G.709

【非特許文献2】ITU−T G.798

【発明の概要】

【発明が解決しようとする課題】

【0007】

OTU3フレームデータをLLDを用いて伝送する方法は新規技術であるため、OORの挿入機能も新規技術である。

【0008】

また、受信側がOORの検出及び解除を正しく行えることを確認するためには、送信側でLMを変更してOTU3フレームに埋め込むことになる。その際には以下の条件を満たす必要がある。

第1の条件は、LMのみ、すなわちMFASの下位2bitのみが変更されていることである。

第2の条件は、検出条件数(5フレーム)以内に正常時に受信していたLMが含まれないことである。

第3の条件は、同じLMが解除条件数(5フレーム)以上連続しないことである。

第4の条件は、レーン番号とLMが一致するとは限らないことである。すなわち第0レーンのLMが0とは限らず、例えば第0レーンのLMが1で他のレーンに0のLMが割り当てられている可能性がある。

【0009】

受信側がOORの検出及び解除を正しく行えることを確認するために、送信側で前記4つの条件を満たすLMを生成する方法として、範囲外の固定値に変更する方法が考えられる。しかし、LMはMFASの下位2bitを用いているため、0〜3の4値以外の値を用いることができない。このため、レーンも4つであることから、範囲外の固定値に変更することはできない問題がある。

【0010】

また、値をインクリメントまたはデクリメントする方法が考えられる。しかし、LMは0〜3の4値以外の値を用いることができないため、5フレーム以内で正常時のLMになってしまう。このため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第2の条件を満たすことができず、受信側はOORの検出を正しく行えない問題がある。

【0011】

そこで、本発明は、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターン挿入回路、OTU3フレームデータ送信装置、OOR試験システム、OOR試験用パターン挿入方法、OTU3フレームデータ送信方法及びOOR試験方法の提供を目的とする。

【課題を解決するための手段】

【0012】

本願発明のOOR試験用パターン挿入回路は、マルチレーン構造を有するOTU3フレームデータのうちの任意のレーンのOTU3フレームデータが入力され、入力された前記OTU3フレームデータに含まれるMFASをバイナリ形式で表したときの最下位の2つのビットに配置されているLMのうちの一方のビットを反転させる符号反転部(32)と、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換し、前記符号反転部からの符号を前記一方のビットに配置して、2bitのOOR試験用パターンを生成するアラームパターン生成部(33)と、前記任意のレーンの前記LMを前記アラームパターン生成部の生成する前記OOR試験用パターンに置換するアラームパターン挿入部(34)と、を備える。

【0013】

符号反転部と、アラームパターン生成部と、を備えるため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記4つの条件を満たすOOR試験用パターンを生成することができる。アラームパターン挿入部を備えるため、OOR試験用パターンをOTU3フレームデータに挿入することができる。したがって、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターン挿入回路を提供することができる。

【0014】

本願発明のOOR試験用パターン挿入回路では、前記アラームパターン生成部は、前記LMの他方のビットを、前記MFASの下位第2ビット、下位第3ビット又は下位第4ビットのいずれかと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換してもよい。

本発明により、アラームパターン生成部は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記4つの条件を満たすOOR試験用パターンを生成することができる。

【0015】

本願発明のOOR試験用パターン挿入回路では、同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータを出力するビット生成部(35)をさらに備え、前記アラームパターン生成部は、前記LMの他方のビットを前記ビット生成部からの出力データと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換してもよい。

本発明により、アラームパターン生成部は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記4つの条件を満たすOOR試験用パターンを生成することができる。

【0016】

本願発明のOTU3フレームデータ送信装置は、前記OTU3フレームデータを生成するOTU3フレームデータ生成回路(11)と、前記OTU3フレームデータ生成回路からの前記OTU3フレームデータを第0レーンから第3レーンの4つのレーンに分配する分配回路(12)と、前記分配回路によって分配された前記OTU3フレームデータのうちの任意のレーンのOTU3フレームデータが入力され、入力された前記OTU3フレームデータに含まれる前記LMを前記OOR試験用パターンに置換する、本願発明のOOR試験用パターン挿入回路(13)と、前記OOR試験用パターン挿入回路によって前記LMが前記OOR試験用パターンに置換された前記OTU3フレームデータを伝送路に送信する送信回路(14)と、を備える。

【0017】

OTU3フレームデータ生成回路と、分配回路と、送信回路と、を備えるため、OTU3フレームデータを送信することができる。ここで、本願発明のOOR試験用パターン挿入回路を備えるため、OOR試験用パターンをOTU3フレームデータに挿入することができる。したがって、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOTU3フレームデータ送信装置を提供することができる。

【0018】

本願発明のOOR試験システムは、本願発明のOTU3フレームデータ送信装置(101)と、前記伝送路を介して伝送された前記OTU3フレームデータを受信し、当該受信によって得られた前記OTU3フレームデータのレーンごとの前記LMの位置に配置されているビット列が5回以上連続して同じ場合は同期状態となり、前記LMの位置に配置されているビット列と同期しているビット列とが5回以上連続して異なる場合は同期状態が外れてOORのアラームを出力するOTU3フレームデータを受信する被測定対象(102)と、を備える。

【0019】

本願発明のOTU3フレームデータ送信装置と、OTU3フレームデータを受信する被測定対象と、を備えるため、OOR試験用パターンを挿入したOTU3フレームデータを送信して、被測定対象である受信側がOORの検出及び解除を正しく行えることを確認することができる。したがって、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験システムを提供することができる。

【0020】

本願発明のOOR試験用パターン挿入方法は、マルチレーン構造を有するOTU3フレームデータのうちの任意のレーンのOTU3フレームデータに含まれるMFASをバイナリ形式で表したときの最下位の2つのビットに配置されているLMのうちの一方のビットを反転させて前記一方のビットに配置するとともに、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換して、2bitのOOR試験用パターンを生成するアラームパターン生成手順(S302)と、前記任意のレーンの前記LMを前記アラームパターン生成手順で生成した前記OOR試験用パターンに置換するアラームパターン挿入手順(S303)と、を順に有する。

【0021】

アラームパターン生成手順と、アラームパターン挿入手順と、を有するため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記4つの条件を満たすOOR試験用パターンを生成してOTU3フレームデータに挿入することができる。したがって、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターン挿入方法を提供することができる。

【0022】

本願発明のOOR試験用パターン挿入方法では、前記アラームパターン生成手順において、前記LMの他方のビットを、前記MFASの下位第2ビット、下位第3ビット又は下位第4ビットのいずれかと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換してもよい。

本発明により、アラームパターン生成手順において、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記4つの条件を満たすOOR試験用パターンを生成することができる。

【0023】

本願発明のOOR試験用パターン挿入方法では、前記アラームパターン生成手順において、同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータを生成し、前記LMの他方のビットを生成したデータと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換してもよい。

本発明により、アラームパターン生成手順において、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記4つの条件を満たすOOR試験用パターンを生成することができる。

【0024】

本願発明のOTU3フレームデータ送信方法は、本願発明のOOR試験用パターン挿入方法と、前記アラームパターン生成手順の前に、前記OTU3フレームデータを生成するOTU3フレームデータ生成手順(S101)と、前記アラームパターン挿入手順の後に、前記アラームパターン挿入手順によって前記LMが前記OOR試験用パターンに置換された前記OTU3フレームデータを伝送路に送信する送信手順(S104)と、を有する。

【0025】

OTU3フレームデータ生成手順と、送信手順と、を有するため、OTU3フレームデータを送信することができる。ここで、本願発明のOOR試験用パターン挿入方法を有するため、OOR試験用パターンをOTU3フレームデータに挿入することができる。したがって、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOTU3フレームデータ送信方法を提供することができる。

【0026】

本願発明のOOR試験方法は、本願発明のOTU3フレームデータ送信方法と、前記OTU3フレームデータ送信方法によって送信された前記OTU3フレームデータを受信する受信手順(S201)と、前記受信手順によって得られた前記OTU3フレームデータのレーンごとの前記LMの位置に配置されているビット列が5回以上連続して同じ場合は同期状態となり、前記LMの位置に配置されているビット列と同期しているビット列とが5回以上連続して異なる場合は同期状態がはずれてOORのアラームを出力するOOR判定手順(S202)と、を順に有する。

【0027】

本願発明のOTU3フレームデータ送信方法と、受信手順と、OOR判定手順と、を有するため、OOR試験用パターンを挿入したOTU3フレームデータを送信して、受信側がOORの検出及び解除を正しく行えることを確認することができる。したがって、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験方法を提供することができる。

【0028】

なお、上記各発明は、可能な限り組み合わせることができる。

【発明の効果】

【0029】

本発明によれば、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターン挿入回路、OTU3フレームデータ送信装置、OOR試験システム、OOR試験用パターン挿入方法、OTU3フレームデータ送信方法及びOOR試験方法を提供することができる。

【図面の簡単な説明】

【0030】

【図1】実施形態1に係るOOR試験システムの一例を示す。

【図2】実施形態1に係るOOR試験方法の一例を示す。

【図3】OOR試験用パターン挿入回路の第1形態を示す。

【図4】MFASとOOR試験用パターンの具体例を示す。

【図5】OOR判定回路25−0の一例を示す。

【図6】OOR試験用パターン挿入回路の第2形態を示す。

【図7】LLDを用いたOTU3フレームデータのレーン振り分けの一例を示す。

【図8】OTU3フレームにおけるLMの位置を示す。

【発明を実施するための形態】

【0031】

添付の図面を参照して本発明の実施形態を説明する。以下に説明する実施形態は本発明の実施の例であり、本発明は、以下の実施形態に制限されるものではない。なお、本明細書及び図面において符号が同じ構成要素は、相互に同一のものを示すものとする。

【0032】

(実施形態1)

図1に、本実施形態に係るOOR試験システムの一例を示す。本実施形態に係るOOR試験システムは、OTU3フレームデータ送信装置101と、OTU3フレームデータを受信する被測定対象102と、を備える。OTU3フレームデータを受信する被測定対象102は、OTU3フレームデータを受信する装置又はデバイスである。

【0033】

OTU3フレームデータ送信装置101は、OTU3フレームデータ生成回路11と、分配回路12と、OOR試験用パターン挿入回路13と、送信回路14と、を備える。OTU3フレームデータを受信する被測定対象102は、受信回路21と、フレーム検出回路22と、集約回路23と、OTU3フレームデータ解析回路24と、OOR判定回路25と、を備える。

【0034】

図2に、本実施形態に係るOOR試験方法の一例を示す。本実施形態に係るOOR試験方法は、OTU3フレームデータ送信方法S100と、受信手順S201と、OOR判定手順S202と、を順に有する。OTU3フレームデータ送信方法S100は、OTU3フレームデータ生成手順S101と、本実施形態に係るOOR試験用パターン挿入方法S300と、送信手順S104と、を順に有する。OOR試験用パターン挿入方法S300は、アラームパターン生成手順S302と、アラームパターン挿入手順S303と、を順に有する。

【0035】

OTU3フレームデータ生成手順S101では、OTU3フレームデータ生成回路11が、OTU3フレームデータDTを生成する。例えば、データが入力され、データを予め定められた長さのフレームに分割して、フレームごとにMFASを付す。このときに、MFASを1つずつインクリメントする。これにより、OTU3フレームデータ生成回路11は、OTU3フレームデータDTを生成する。

【0036】

分配回路12は、OTU3フレームデータ生成回路11からのOTU3フレームデータDTを第0レーンから第3レーンの4つのレーンに分配する。例えば、分配回路12は、OTU3フレームデータDTをフレームごとのOTU3フレームデータDT0〜DT3に分割する。そして、分配回路12は、OTU3フレームデータDT0を第0レーンに分配し、OTU3フレームデータDT1を第1レーンに分配し、OTU3フレームデータDT2を第2レーンに分配し、OTU3フレームデータDT3を第3レーンに分配する。

【0037】

アラームパターン生成手順S302では、OOR試験用パターン挿入回路13が、OTU3フレームデータDT0〜DT3のLMを用いてOOR試験用パターンを生成する。例えば、OOR試験用パターン挿入回路13は、レーンごとにOOR試験用パターン挿入回路13−0〜13−3を備える。OOR試験用パターン挿入回路13−0〜13−3は、それぞれ、OTU3フレームデータDT0〜DT3のLMを用いてOOR試験用パターンを生成する。

【0038】

例えば、OOR試験用パターン挿入回路13−0が、OTU3フレームデータDT0に含まれるMFASをバイナリ形式で表したときの最下位の2つのビットに配置されているLMのうちの一方のビットを反転させて一方のビットに配置するとともに、MFASの下位2bitに配置されているLMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換して、2bitのOOR試験用パターンを生成する。同符号の連続が4回以下となるようにとは、例えば、符号「0」のデータと置換し、その次は符号「0」のデータと置換し、その次は符号「0」のデータと置換し、その次は符号「0」のデータと置換した場合、その次は符号「1」のデータとなるようにという意味である。

【0039】

図3に、OOR試験用パターン挿入回路13−0の第1形態を示す。図3に示すOOR試験用パターン挿入回路13−0は、MFAS抽出部31と、符号反転部32と、アラームパターン生成部33と、アラームパターン挿入部34と、遅延回路37と、アラーム挿入タイミング信号生成部38と、を備える。

【0040】

MFAS抽出部31には、フレーム先頭信号とOTU3フレームデータDT0が入力される。そして、MFAS抽出部31は、フレーム先頭信号に従って、OTU3フレームデータDT0からMFASを抽出する。そして、MFASをバイナリ形式で表した8つのビット「a7a6a5a4a3a2a1a0」を取得し、最下位の2つのビット「a1a0」を符号反転部32に出力する。

【0041】

符号反転部32は、2つのビット「a1a0」のうちの一方のビットを反転させる。例えば、一方のビットが第0ビットa0、他方のビットが第1ビットa1である場合、ビットa0を反転させ、反転させたビットr0をアラームパターン生成部33に出力する。反転とは、例えば、ビットa0の符号が「1」であればビットr0の符号は「0」となり、ビットa0の符号が「0」であればビットr0の符号は「1」となる。

【0042】

図4に、MFASとOOR試験用パターンの具体例を示す。第0レーンにLM「0」、第1レーンにLM「1」、第2レーンにLM「2」、第3レーンにLM「3」が割り振られている。なお、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第4条件で説明したとおり、これは一例であって、第0レーンにLM「0」が割り振られているとは限らず、第0レーンのLMは、「1」であってもよいし、「2」であってもよいし、「3」であってもよい。

【0043】

第0レーンのMFASは「0」、「4」、「8」、・・・「252」となる。これらMFASをバイナリ形式で表すと、「00000000」、「00000100」、「00001000」、・・・「11111100」である。このように、MFASをバイナリ形式で表したときの最下位の2つのビットは全て「00」であり、LM「0」が割り振られている。この場合、ビットa0は「0」であり、これを反転させたビットr0は「1」となる。

【0044】

アラームパターン生成部33は、LMの他方のビットa1をビットb1に置換し、ビットr0をビットa0の位置に配置して、2bitのOOR試験用パターンを生成する。ここで、ビットa1からビットb1への置換は、同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換する。これによって、OOR試験用パターン「b1r0」を生成する。

【0045】

例えば、図4に示す第0レーンのMFASの下位第2ビットa2は、「0」、「1」、「0」、「1」、・・・「1」のように、同符号の連続が1回以下となる。このため、ビットa1をMFASの下位第2ビットa2に置換することによって、LMの他方のビットa1を同符号の連続が1回以下となるように符号「0」のデータ又は符号「1」のデータと置換することができる。これにより、「01」、「11」、「01」、「11」、・・・「11」、すなわち値「1」と「3」の繰り返しとなるOOR試験用パターン「b1r0」を生成することができる。

【0046】

このように、LMが0から3であること、及びMFASが0から255でOTU3フレーム毎に1インクリメントすることを利用しており、あるレーンにおけるLMの下位第0ビットa0を反転した値r0とMFASの下位第2ビットa2の値b1を組み合わせてOOR試験用パターン「b1r0」を生成する。

【0047】

図2に示すアラームパターン挿入手順S303では、アラームパターン挿入部34に、OTU3フレームデータDT0及びOOR試験用パターン「b1r0」が入力される。このとき、遅延回路37が、OTU3フレームデータDT0及びOOR試験用パターン「b1r0」の入力タイミングを調整する。また、アラーム挿入タイミング信号生成部38が、アラーム挿入指示に従って、OTU3フレームデータDT0のアラームパターンに置換するLMの位置を示すタイミング信号をアラームパターン挿入部34に出力する。そして、アラームパターン挿入部34が、アラーム挿入タイミング信号生成部38からのタイミング信号に従って、OTU3フレームデータDT0のLM「a1a0」をOOR試験用パターン「b1r0」に置換してOTU3フレームデータDA0を出力する。

【0048】

OTU3フレームデータDA0のMFASは「a7a6a5a4a3a2b1r0」となっているため、LMのみ、すなわちMFASの下位2bitのみが変更されている。このため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件を満たす。また、図4に示すMFASにおいて、第0レーンのOOR試験用パターン「b1r0」は、値「1」と値「3」の繰り返しであり、正常時に受信していたLM「0」が含まれないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第2の条件を満たす。また、同じLMが連続しないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第3の条件を満たす。さらに、第0レーンにLM「1」の割り振られている場合も同様に正常時のLM「1」とは異なる値「0」と値「2」を繰り返すOOR試験用パターンとなり、第0レーンにLM「2」が割り振られている場合も同様に正常時のLM「2」とは異なる値「1」と値「3」を繰り返すOOR試験用パターンとなり、第0レーンにLM「3」が割り振られている場合も同様に正常時のLM「3」とは異なる値「0」と値「2」を繰り返すOOR試験用パターンとなるため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第4の条件を満たす。

【0049】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たすOTU3フレームデータDA0を出力することができる。

【0050】

図1に示すOOR試験用パターン挿入回路13−1,13−2及び13−3は、それぞれ、OOR試験用パターン挿入回路13−0と同様にして、正常時のLMとは異なる2値を繰り返すOOR試験用パターンが挿入されたOTU3フレームデータDA1,DA2及びDA3を出力することができる。

【0051】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たすOTU3フレームデータDA0〜DA3を出力することができる。

【0052】

送信手順S104では、OOR試験用パターン挿入回路13によってLMがOOR試験用パターンに置換されたOTU3フレームデータDA0〜DA3が送信回路14に入力される。そして、送信回路14は、OTU3フレームデータDA0〜DA3を伝送路に送信する。

【0053】

受信手順S201では、OTU3フレームデータ送信装置101から出力されたOTU3フレームデータを受信する。例えば、受信回路21が、OTU3フレームデータを受信し、第0レーンから第3レーンのそれぞれのレーンにOTU3フレームデータDR0〜DR3を出力する。フレーム検出回路22は、受信回路21からのOTU3フレームデータDR0〜DR3のフレームの先頭を検出してフレーム間のデスキューなどのフレーム処理を行う。このとき、各レーンに備わるフレーム検出回路22−0〜22−3が、レーンごとにフレーム処理を行う。集約回路23は、フレーム検出回路22からのOTU3フレームデータDD0〜DD3を集約してOTU3フレームデータDDを構築する。OTU3フレームデータ解析回路24は、集約回路23からのOTU3フレームデータDDを解析する。

【0054】

OOR判定手順S202では、OOR判定回路25が、受信手順S201で受信したOTU3フレームデータDR0〜DR3のOORの検出及び解除を行う。例えば、OOR判定回路25は、OTU3フレームデータDD0のOORの検出及び解除を行うOOR判定回路25−0と、OTU3フレームデータDD1のOORの検出及び解除を行うOOR判定回路25−1と、OTU3フレームデータDD2のOORの検出及び解除を行うOOR判定回路25−2と、OTU3フレームデータDD3のOORの検出及び解除を行うOOR判定回路25−3と、を備える。

【0055】

図5に、OOR判定回路25−0の一例を示す。OOR判定回路25−0は、MFAS抽出部51と、連続性検出部52と、を備える。フレーム検出回路22−0からMFAS抽出部51に、フレーム先頭信号及びOTU3フレームデータDD0が入力される。MFAS抽出部51は、OTU3フレームデータDD0からLMの位置に配置されているビット列を抽出する。連続性検出部52は、MFAS抽出部51からのLMの位置に配置されているビット列が5回以上連続して同じ場合は同期状態となり、LMの位置に配置されているビット列と同期しているビット列とが5回以上連続して異なる場合は同期状態がはずれてOORのアラームを出力する。

【0056】

例えば、正常なLMである「00」のビット列が5回以上連続している状態では、同期状態となる。その後、ビット列が「01」となっても同期状態を維持している。そして、「01」の後に、「11」、「01」、「11」、「01」と続き、検出条件数(5フレーム)に至る。すると、同期状態がはずれてOORのアラームを出力する。本実施形態では、第0レーンのDD0のLMの位置に配置されているビット列は、OOR試験用パターンが挿入されているときには値「1」と値「3」の繰り返しであり、正常時に受信していたLM「0」が含まれない。このため、検出条件数が5フレームの場合、送信側でOOR試験用パターンを5回以上挿入すれば、OOR判定回路25−0はOORのアラームを出力する。

【0057】

OOR判定回路25−1〜25−3についてもOOR判定回路25−0と同様に、送信側でOOR試験用パターンを5回以上挿入すれば、OOR判定回路25−1〜25−3はOORのアラームを出力する。

【0058】

以上説明したように、OOR試験用パターン挿入回路13及びOOR試験用パターン挿入方法S300は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たすOTU3フレームデータDA0〜DA3を出力することができる。したがって、OTU3フレームデータ送信装置101及びOTU3フレームデータ送信方法S100は、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターンをOTU3フレームデータDT0〜DT3に挿入したOTU3フレームデータDA0〜DA3を送信することができる。

【0059】

また、本実施形態に係るOOR試験システムはOTU3フレームデータ送信装置101を備え、本実施形態に係るOOR試験方法はOTU3フレームデータ送信方法S100を有する。したがって、本実施形態に係るOOR試験システム及びOOR試験方法は、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターンをOTU3フレームデータDT0〜DT3に挿入したOTU3フレームデータDA0〜DA3を送受信して、OORの検出及び解除を正しく行えることを確認することができる。

【0060】

なお、アラームパターン生成手順S302において第0レーンのアラームパターン生成部33が反転させる一方のビットはMFASの下位第1ビットa1であってもよい。この場合、他方のビットがMFASの下位第0ビットa0となる。例えば、ビットa1を反転させてビット「r1」を生成する。また、ビットa0を、同符号の連続が4回以下となるようにビットb0に置換する。これにより、2bitのOOR試験用パターン「r1b0」を生成する。図4に示すMFASであれば、OOR試験用パターン「r1b0」は「2」と「3」の繰り返しとなる。このように、OOR試験用パターンが「r1b0」であっても、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。第1レーンから第3レーンのOOR試験用パターンについても同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。

【0061】

また、本実施形態では、すべてのレーンにOOR試験用パターン挿入回路13−0,13−1,13−2,13−3を備える構成としたが、これに限定されない。例えば、各レーンに共通のOOR試験用パターン挿入回路を1つ備え、OOR試験用パターン挿入回路をいずれかのレーンに挿入可能にしてもよい。本実施形態に係るOOR試験用パターン挿入回路は、入力されたMFASを用いてOOR試験用パターンを生成するため、いずれのレーンに挿入しても適切なOOR試験用パターンを生成することができる。

【0062】

また、本実施形態では、検出条件数及び解除条件数が5フレームである場合について説明したが、これに限定されない。例えば、検出条件数及び解除条件数は4フレーム以下であってもよい。本実施形態では、ビットa1をMFASの下位第2ビットa2に置換することによって、正常時のLM「0」とは異なる値「1」と値「3」を繰り返すOOR試験用パターンを生成することができる。このため、検出条件数及び解除条件数が2フレームの場合であっても、受信側がOORの検出及び解除を正しく行えることを確認することができる。したがって、検出条件数及び解除条件数が4以下に設定されている場合であっても、受信側がOORの検出及び解除を正しく行えることを確認することができる。

【0063】

(実施形態2)

本実施形態に係るOOR試験システムは、図3に示すアラームパターン生成部33が、LMの他方のビットa1を、MFASの下位第3ビットa3と置換することによって、LMの他方のビットa1を同符号の連続が2回以下となるように符号「0」のデータ又は符号「1」のデータと置換する。

【0064】

例えば、図4に示す第0レーンのMFASの下位第3ビットは、「0」、「0」、「1」、「1」、「0」、「0」、「1」、「1」、・・・「1」のように、同符号の連続が2回以下となる。このため、ビットa1をMFASの下位第3ビットa3に置換することによって、LMの他方のビットa1を同符号の連続が2回以下となるように符号「0」のデータ又は符号「1」のデータと置換することができる。

【0065】

この場合、第0レーンのOOR試験用パターン「b1r0」は、「01」、「01」、「11」、「11」、「01」、「01」、「11」、「11」、・・・「11」のように、「1」、「1」、「3」、「3」の繰り返しとなる。このため、同じLMが2回以内となっており、3回以上連続しない。このように、正常時に受信していたLM「0」が含まれないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第2の条件を満たす。また、同じLMが3回以上連続しないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第3の条件を満たす。さらに、第0レーンにLM「1」又はLM「2」又はLM「3」が割り振られている場合も同様に、正常時のLMとは異なる2値となり、同じ値が2回以内となっており、3回以上連続しない。このため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第4の条件を満たす。

【0066】

OOR試験用パターン挿入回路13−1,13−2及び13−3は、それぞれ、OOR試験用パターン挿入回路13−0と同様にして、正常時のLMとは異なる2値となり、同じ値が2回以内となっており、3回以上連続しないOOR試験用パターンが挿入されたOTU3フレームデータDA1,DA2及びDA3を出力することができる。

【0067】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たすOTU3フレームデータDA0〜DA3を出力することができる。

【0068】

なお、アラームパターン生成手順S302においてアラームパターン生成部33が反転させる一方のビットはMFASの下位第1ビットa1であってもよい。この場合、他方のビットがMFASの下位第0ビットa0となる。例えば、ビットa1を反転させてビット「r1」を生成する。また、ビットa0を、同符号の連続が4回以下となるようにビットb0に置換する。これにより、2bitのOOR試験用パターン「r1b0」を生成する。図4に示すMFASであれば、第0レーンの場合、OOR試験用パターン「r1b0」は「2」、「2」、「3」、「3」の繰り返しとなる。このように、OOR試験用パターンが「r1b0」であっても、OOR試験用パターンが「b1r0」の場合と同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。第1レーンから第3レーンのOOR試験用パターンについても同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。

【0069】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300を用いた場合も、実施形態1と同様に、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターンをOTU3フレームデータDT0〜DT3に挿入したOTU3フレームデータDA0〜DA3を出力することができる。

【0070】

(実施形態3)

本実施形態に係るOOR試験システムは、図3に示すアラームパターン生成部33が、LMの他方のビットa1を、MFASの下位第4ビットa4と置換することによって、LMの他方のビットa1を同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換する。

【0071】

例えば、図4に示す第0レーンのMFASの下位第4ビットは、「0」、「0」、「0」、「0」、「1」、「1」、「1」、「1」、「0」、・・・「1」のように、同符号の連続が4回以下となる。このため、ビットa1をMFASの下位第4ビットに置換することによって、LMの他方のビットa1を同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換することができる。

【0072】

この場合、第0レーンのOOR試験用パターン「b1r0」は、「01」、「01」、「01」、「01」、「11」、「11」、「11」、「11」、「01」、「01」、「01」、「01」、「11」、・・・「11」のように、「1」、「1」、「1」、「1」、「3」、「3」、「3」、「3」の繰り返しとなる。このため、同じLMが4回以内となっており、5回以上連続しない。このように、正常時に受信していたLM「0」が含まれないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第2の条件を満たす。また、同じLMが5回以上連続しないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第3の条件を満たす。さらに、第0レーンにLM「1」又はLM「2」又はLM「3」が割り振られている場合も同様に、正常時のLMとは異なる2値となり、同じ値が4回以内となっており、5回以上連続しない。このため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第4の条件を満たす。

【0073】

OOR試験用パターン挿入回路13−1,13−2及び13−3は、それぞれ、OOR試験用パターン挿入回路13−0と同様にして、正常時のLMとは異なる2値となり、同じ値が4回以内となっており、5回以上連続しないOOR試験用パターンが挿入されたOTU3フレームデータDA1,DA2及びDA3を出力することができる。

【0074】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たすOTU3フレームデータDA0〜DA3を出力することができる。

【0075】

なお、アラームパターン生成手順S302においてアラームパターン生成部33が反転させる一方のビットはMFASの下位第1ビットa1であってもよい。この場合、他方のビットがMFASの下位第0ビットa0となる。例えば、ビットa1を反転させてビット「r1」を生成する。また、ビットa0を、同符号の連続が4回以下となるようにビットb0に置換する。これにより、2bitのOOR試験用パターン「r1b0」を生成する。図4に示すMFASであれば、第0レーンの場合、OOR試験用パターン「r1b0」は「2」、「2」、「2」、「2」、「3」、「3」、「3」、「3」の繰り返しとなる。このように、OOR試験用パターンが「r1b0」であっても、OOR試験用パターンが「b1r0」の場合と同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。第1レーンから第3レーンのOOR試験用パターンについても同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。

【0076】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300を用いた場合も、実施形態1と同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するためのOOR試験用パターンをOTU3フレームデータDT0〜DT3に挿入したOTU3フレームデータDA0〜DA3を出力することができる。

【0077】

(実施形態4)

本実施形態に係るOOR試験システムは、図3に示すOOR試験用パターン挿入回路13−0の第1形態に代えて、OOR試験用パターン挿入回路13−0の第2形態を備える。そして、図2に示すアラームパターン生成手順S302において、OOR試験用パターン挿入回路13−0の第2形態が、OTU3フレームデータDT0〜DT3のLMを用いてOOR試験用パターンを生成する。図6に、OOR試験用パターン挿入回路の第2形態を示す。

【0078】

図6に示すOOR試験用パターン挿入回路13−0は、MFAS抽出部31と、符号反転部32と、アラームパターン生成部36と、アラームパターン挿入部34と、ビット生成部35と、遅延回路37と、アラーム挿入タイミング信号生成部38と、を備える。MFAS抽出部31、符号反転部32、アラームパターン生成部36、アラームパターン挿入部34、遅延回路37及びアラーム挿入タイミング信号生成部38については、実施形態1で説明したとおりである。

【0079】

バイナリ形式で表したMFASが「a7a6a5a4a3a2a1a0」であり、LMの一方のビットがMFASの下位第0ビットa0、LMの他方のビットがMFASの下位第1ビットa1である場合、符号反転部32は、ビットa0を反転させ、反転させたビットr0をアラームパターン生成部36に出力する。

【0080】

ビット生成部35は、同符号の連続が4回以下となるようなビットb1を出力する。例えば、ビット生成部35は、「0」、「1」、「0」、「1」、・・・「1」のように、同符号の連続が1回以下となるようなビット列を出力する。

【0081】

アラームパターン生成部36は、LMの他方のビットa1をビットb1に置換し、ビットr0をビットa0の位置に配置して、2bitのOOR試験用パターン「b1r0」を生成する。

【0082】

例えば、ビットb1は「0」、「1」、「0」、「1」、・・・「1」のように、同符号の連続が1回以下となるようなビット列である。このため、ビットa1をビットb1に置換することによって、LMの他方のビットa1を同符号の連続が1回以下となるように符号「0」のデータ又は符号「1」のデータと置換することができる。

【0083】

図2に示すアラームパターン挿入手順S303では、アラームパターン挿入部34が、OTU3フレームデータDT0のLM「a1a0」をアラームパターン生成手順S302で生成したOOR試験用パターン「b1r0」に置換する。これにより、アラームパターン挿入部34からOTU3フレームデータDA0が出力される。

【0084】

OTU3フレームデータDA0のMFASは「a7a6a5a4a3a2b1r0」となっているため、LMのみ、すなわちMFASの下位2bitのみが変更されている。このため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件を満たす。また、図4に示すMFASにおいて、第0レーンのOOR試験用パターン「b1r0」は、値「1」と値「3」の繰り返しであり、正常時に受信していたLM「0」が含まれないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第2の条件を満たす。また、同じLMが連続しないため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第3の条件を満たす。さらに、第0レーンにLM「1」又はLM「2」又はLM「3」が割り振られている場合も同様に、正常時のLMとは異なる2値を繰り返す。このため、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第4の条件を満たす。

【0085】

OOR試験用パターン挿入回路13−1,13−2及び13−3は、それぞれ、OOR試験用パターン挿入回路13−0と同様にして、正常時のLMとは異なる2値を繰り返すOOR試験用パターンが挿入されたOTU3フレームデータDA1,DA2及びDA3を出力することができる。

【0086】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300は、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たすOTU3フレームデータDA0〜DA3を出力することができる。

【0087】

なお、アラームパターン生成手順S302においてアラームパターン生成部33が反転させる一方のビットはMFASの下位第1ビットa1であってもよい。この場合、他方のビットがMFASの下位第0ビットa0となる。例えば、ビットa1を反転させてビット「r1」を生成する。また、ビットa0を、同符号の連続が4回以下となるようにビットb0に置換する。これにより、2bitのOOR試験用パターン「r1b0」を生成する。図4に示すMFASであれば、第0レーンの場合、OOR試験用パターン「r1b0」は「2」と「3」の繰り返しとなる。このように、OOR試験用パターンが「r1b0」であっても、OOR試験用パターンが「b1r0」の場合と同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。第1レーンから第3レーンのOOR試験用パターンについても同様に、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たす。

【0088】

また、ビット生成部35は、「0」、「0」、「1」、「1」、「0」、「0」、「1」、「1」、・・・「1」のように、同符号の連続が2回以下となるようなビット列を出力してもよい。また、ビット生成部35は、「0」、「0」、「0」、「1」、「1」、「1」、「0」、「0」、「0」、・・・「1」のように、同符号の連続が3回以下となるようなビット列を出力してもよい。また、ビット生成部35は、「0」、「0」、「0」、「0」、「1」、「1」、「1」、「1」、「0」、・・・「1」のように、同符号の連続が4回以下となるようなビット列を出力してもよい。これらの場合も、実施形態2及び3において説明したように、受信側がOORの検出及び解除を正しく行えることを確認可能なLMを発生するための前記第1の条件から前記第4の条件を満たすことができる。

【0089】

したがって、本実施形態に係るOOR試験用パターン挿入回路13及び本実施形態に係るOOR試験用パターン挿入方法S300を用いた場合も、実施形態1と同様に、受信側がOORの検出及び解除を正しく行えることを確認するためにLMの擾乱を起こすOOR試験用パターンをOTU3フレームデータDT0〜DT3に挿入したOTU3フレームデータDA0〜DA3を出力することができる。

【産業上の利用可能性】

【0090】

本発明は情報通信産業に適用することができる。

【符号の説明】

【0091】

11:OTU3フレームデータ生成回路

12:分配回路

13、13−0、13−1、13−2、13−3:OOR試験用パターン挿入回路

14:送信回路

21:受信回路

22:フレーム検出回路

23:集約回路

24:OTU3フレームデータ解析回路

25、25−0、25−1、25−2、25−3:OOR判定回路

31:MFAS抽出部

32:符号反転部

33、36:アラームパターン生成部

34:アラームパターン挿入部

35:ビット生成部

37:遅延回路

38:アラーム挿入タイミング信号生成部

51:MFAS抽出部

52:連続性検出部

101:OTU3フレームデータ送信装置

102:OTU3フレームデータを受信する被測定対象

【特許請求の範囲】

【請求項1】

マルチレーン構造を有するOTU3(Optical−channel Transport Unit 3)フレームデータのうちの任意のレーンのOTU3フレームデータが入力され、入力された前記OTU3フレームデータに含まれるMFAS(Multi Frame Alignment Signal)をバイナリ形式で表したときの最下位の2つのビットに配置されているLM(Lane Marker)のうちの一方のビットを反転させる符号反転部(32)と、

前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換し、前記符号反転部からの符号を前記一方のビットに配置して、2bitのOOR(Out of Recovery)試験用パターンを生成するアラームパターン生成部(33)と、

前記任意のレーンの前記LMを前記アラームパターン生成部の生成する前記OOR試験用パターンに置換するアラームパターン挿入部(34)と、

を備えるOOR試験用パターン挿入回路。

【請求項2】

前記アラームパターン生成部は、前記LMの他方のビットを、前記MFASの下位第2ビット、下位第3ビット又は下位第4ビットのいずれかと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換することを特徴とする請求項1に記載のOOR試験用パターン挿入回路。

【請求項3】

同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータを出力するビット生成部(35)をさらに備え、

前記アラームパターン生成部は、前記LMの他方のビットを前記ビット生成部からの出力データと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換することを特徴とする請求項1に記載のOOR試験用パターン挿入回路。

【請求項4】

前記OTU3フレームデータを生成するOTU3フレームデータ生成回路(11)と、

前記OTU3フレームデータ生成回路からの前記OTU3フレームデータを第0レーンから第3レーンの4つのレーンに分配する分配回路(12)と、

前記分配回路によって分配された前記OTU3フレームデータのうちの任意のレーンのOTU3フレームデータが入力され、入力された前記OTU3フレームデータに含まれる前記LMを前記OOR試験用パターンに置換する、請求項1から3のいずれかに記載のOOR試験用パターン挿入回路(13)と、

前記OOR試験用パターン挿入回路によって前記LMが前記OOR試験用パターンに置換された前記OTU3フレームデータを伝送路に送信する送信回路(14)と、

を備えるOTU3フレームデータ送信装置。

【請求項5】

請求項4に記載のOTU3フレームデータ送信装置(101)と、

前記伝送路を介して伝送された前記OTU3フレームデータを受信し、当該受信によって得られた前記OTU3フレームデータのレーンごとの前記LMの位置に配置されているビット列が5回以上連続して同じ場合は同期状態となり、前記LMの位置に配置されているビット列と同期しているビット列とが5回以上連続して異なる場合は同期状態が外れてOORのアラームを出力するOTU3フレームデータを受信する被測定対象(102)と、

を備えるOOR試験システム。

【請求項6】

マルチレーン構造を有するOTU3フレームデータのうちの任意のレーンのOTU3フレームデータに含まれるMFASをバイナリ形式で表したときの最下位の2つのビットに配置されているLMのうちの一方のビットを反転させて前記一方のビットに配置するとともに、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換して、2bitのOOR試験用パターンを生成するアラームパターン生成手順(S302)と、

前記任意のレーンの前記LMを前記アラームパターン生成手順で生成した前記OOR試験用パターンに置換するアラームパターン挿入手順(S303)と、

を順に有するOOR試験用パターン挿入方法。

【請求項7】

前記アラームパターン生成手順において、前記LMの他方のビットを、前記MFASの下位第2ビット、下位第3ビット又は下位第4ビットのいずれかと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換することを特徴とする請求項6に記載のOOR試験用パターン挿入方法。

【請求項8】

前記アラームパターン生成手順において、同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータを生成し、前記LMの他方のビットを生成したデータと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換することを特徴とする請求項6に記載のOOR試験用パターン挿入方法。

【請求項9】

請求項6から8のいずれかに記載のOOR試験用パターン挿入方法と、

前記アラームパターン生成手順の前に、前記OTU3フレームデータを生成するOTU3フレームデータ生成手順(S101)と、

前記アラームパターン挿入手順の後に、前記アラームパターン挿入手順によって前記LMが前記OOR試験用パターンに置換された前記OTU3フレームデータを伝送路に送信する送信手順(S104)と、

を有するOTU3フレームデータ送信方法。

【請求項10】

請求項9に記載のOTU3フレームデータ送信方法と、

前記OTU3フレームデータ送信方法によって送信された前記OTU3フレームデータを受信する受信手順(S201)と、

前記受信手順によって得られた前記OTU3フレームデータのレーンごとの前記LMの位置に配置されているビット列が5回以上連続して同じ場合は同期状態となり、前記LMの位置に配置されているビット列と同期しているビット列とが5回以上連続して異なる場合は同期状態がはずれてOORのアラームを出力するOOR判定手順(S202)と、

を順に有するOOR試験方法。

【請求項1】

マルチレーン構造を有するOTU3(Optical−channel Transport Unit 3)フレームデータのうちの任意のレーンのOTU3フレームデータが入力され、入力された前記OTU3フレームデータに含まれるMFAS(Multi Frame Alignment Signal)をバイナリ形式で表したときの最下位の2つのビットに配置されているLM(Lane Marker)のうちの一方のビットを反転させる符号反転部(32)と、

前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換し、前記符号反転部からの符号を前記一方のビットに配置して、2bitのOOR(Out of Recovery)試験用パターンを生成するアラームパターン生成部(33)と、

前記任意のレーンの前記LMを前記アラームパターン生成部の生成する前記OOR試験用パターンに置換するアラームパターン挿入部(34)と、

を備えるOOR試験用パターン挿入回路。

【請求項2】

前記アラームパターン生成部は、前記LMの他方のビットを、前記MFASの下位第2ビット、下位第3ビット又は下位第4ビットのいずれかと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換することを特徴とする請求項1に記載のOOR試験用パターン挿入回路。

【請求項3】

同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータを出力するビット生成部(35)をさらに備え、

前記アラームパターン生成部は、前記LMの他方のビットを前記ビット生成部からの出力データと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換することを特徴とする請求項1に記載のOOR試験用パターン挿入回路。

【請求項4】

前記OTU3フレームデータを生成するOTU3フレームデータ生成回路(11)と、

前記OTU3フレームデータ生成回路からの前記OTU3フレームデータを第0レーンから第3レーンの4つのレーンに分配する分配回路(12)と、

前記分配回路によって分配された前記OTU3フレームデータのうちの任意のレーンのOTU3フレームデータが入力され、入力された前記OTU3フレームデータに含まれる前記LMを前記OOR試験用パターンに置換する、請求項1から3のいずれかに記載のOOR試験用パターン挿入回路(13)と、

前記OOR試験用パターン挿入回路によって前記LMが前記OOR試験用パターンに置換された前記OTU3フレームデータを伝送路に送信する送信回路(14)と、

を備えるOTU3フレームデータ送信装置。

【請求項5】

請求項4に記載のOTU3フレームデータ送信装置(101)と、

前記伝送路を介して伝送された前記OTU3フレームデータを受信し、当該受信によって得られた前記OTU3フレームデータのレーンごとの前記LMの位置に配置されているビット列が5回以上連続して同じ場合は同期状態となり、前記LMの位置に配置されているビット列と同期しているビット列とが5回以上連続して異なる場合は同期状態が外れてOORのアラームを出力するOTU3フレームデータを受信する被測定対象(102)と、

を備えるOOR試験システム。

【請求項6】

マルチレーン構造を有するOTU3フレームデータのうちの任意のレーンのOTU3フレームデータに含まれるMFASをバイナリ形式で表したときの最下位の2つのビットに配置されているLMのうちの一方のビットを反転させて前記一方のビットに配置するとともに、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換して、2bitのOOR試験用パターンを生成するアラームパターン生成手順(S302)と、

前記任意のレーンの前記LMを前記アラームパターン生成手順で生成した前記OOR試験用パターンに置換するアラームパターン挿入手順(S303)と、

を順に有するOOR試験用パターン挿入方法。

【請求項7】

前記アラームパターン生成手順において、前記LMの他方のビットを、前記MFASの下位第2ビット、下位第3ビット又は下位第4ビットのいずれかと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換することを特徴とする請求項6に記載のOOR試験用パターン挿入方法。

【請求項8】

前記アラームパターン生成手順において、同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータを生成し、前記LMの他方のビットを生成したデータと置換することによって、前記LMの他方のビットを同符号の連続が4回以下となるように符号「0」のデータ又は符号「1」のデータと置換することを特徴とする請求項6に記載のOOR試験用パターン挿入方法。

【請求項9】

請求項6から8のいずれかに記載のOOR試験用パターン挿入方法と、

前記アラームパターン生成手順の前に、前記OTU3フレームデータを生成するOTU3フレームデータ生成手順(S101)と、

前記アラームパターン挿入手順の後に、前記アラームパターン挿入手順によって前記LMが前記OOR試験用パターンに置換された前記OTU3フレームデータを伝送路に送信する送信手順(S104)と、

を有するOTU3フレームデータ送信方法。

【請求項10】

請求項9に記載のOTU3フレームデータ送信方法と、

前記OTU3フレームデータ送信方法によって送信された前記OTU3フレームデータを受信する受信手順(S201)と、

前記受信手順によって得られた前記OTU3フレームデータのレーンごとの前記LMの位置に配置されているビット列が5回以上連続して同じ場合は同期状態となり、前記LMの位置に配置されているビット列と同期しているビット列とが5回以上連続して異なる場合は同期状態がはずれてOORのアラームを出力するOOR判定手順(S202)と、

を順に有するOOR試験方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2012−95104(P2012−95104A)

【公開日】平成24年5月17日(2012.5.17)

【国際特許分類】

【出願番号】特願2010−240741(P2010−240741)

【出願日】平成22年10月27日(2010.10.27)

【出願人】(000000572)アンリツ株式会社 (838)

【Fターム(参考)】

【公開日】平成24年5月17日(2012.5.17)

【国際特許分類】

【出願日】平成22年10月27日(2010.10.27)

【出願人】(000000572)アンリツ株式会社 (838)

【Fターム(参考)】

[ Back to top ]