PCBコネクタ用オス端子及びその製造方法

【課題】主として車載用・民生用の電気配線に使用されるPCB端子であって、コネクタへの挿入に際しての挿入力の低減と、基板側への半田付け部の半田濡れ性の向上に優れたPCB端子及びその製造方法の提供である。

【解決手段】本発明は、嵌合部の摩擦係数が0.26以下で、半田付け部のエージング(PCT:105℃、相対湿度100%)後のゼロクロスタイムが5秒以下であることを特徴とするPCBコネクタ用オス端子及びその製造方法である。

【解決手段】本発明は、嵌合部の摩擦係数が0.26以下で、半田付け部のエージング(PCT:105℃、相対湿度100%)後のゼロクロスタイムが5秒以下であることを特徴とするPCBコネクタ用オス端子及びその製造方法である。

【発明の詳細な説明】

【技術分野】

【0001】

主として車載用・民生用の電気配線に使用されるPCBコネクタ用オス端子(以下PCB端子)であって、コネクタへの挿入に際しての嵌合部の挿入力の低減と、基板側への半田付け部の半田濡れ性の向上に優れたPCB端子及びその製造方法に関する。

【背景技術】

【0002】

各種コネクタに使用されるPCB端子は、車載用・民生用の用途があり、電線の通電確保の機能をもっている。図1にPCB端子の概略図を示す。PCB端子は基板側半田付け部5と、相手材とのコネクタとしての嵌合部4とからなる(図2)。PCB端子の嵌合部をコネクタに挿入することで通電が確保される。黄銅等の銅合金を母材とし、表面に、Snめっき層を形成したものが一般的である。Snめっきをする目的は、電気接触部の嵌合側では、低い接触抵抗を得、更に、表面に耐食性を付与することであり、一方、半田付け部では、回路基板への半田付け性をうるためである。

近年、PCB端子の小型化及び接続の高密度化に対する要求が高まっており、その対応として、端子の嵌合側では、接続する際の挿入力を小さくすることが求められる。最上層のSnは、軟質金属であるため、挿入時に容易に塑性変形し、嵌合に大きな挿入力が必要となる。端子の嵌合側の挿入力の低下のため、錫の層厚を薄くする対応が考えられるが、半田付け部の半田付け性が悪化するという問題がある。

上記問題の対策として、黄銅などの銅合金を母材とし、順次Ni,Cu,Snの順でめっきを積層し、リフロー処理で上層のSnをCu−Sn合金化することで、最上層の硬度を上昇させ、PCB端子の挿入力を低減させることができる(特許文献1参照)。しかし、この対策では、PCB端子の挿入力を低減させることができるが、半田付け部の濡れ性が低下してしまうという問題がある。

又、最上層のSn層に、リフロー処理によるCu−Sn合金化層を一部露出させることで、硬度を確保し、端子の挿入力を低減させる工夫がある(特許文献2参照)。しかし、この対策も、PCB端子の挿入力を低減させることができるが、半田濡れ性が低下してしまう。

又、最上層のSn層に、カーボンを含有させる試みもある(特許文献3参照)。しかし、この対策も、PCB端子の挿入力を低減させることができるが、半田濡れ性の低下のほかに、耐食性や曲げ加工性の低下という問題がある。

嵌合部の低挿入力と半田付け部の半田濡れ性の両立が可能なPCB端子が望まれている。

【0003】

【特許文献1】特許第3562719号公報

【特許文献2】特開2006−77307号公報

【特許文献3】特開2006−118054号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

本発明は、主として車載用・民生用の電気配線に使用されるPCB端子であって、コネクタへの挿入に際しての嵌合部の挿入力の低減と、基板側への半田付け部の半田濡れ性の向上に優れたPCB端子及びその製造方法を提供することを目的にする。

【課題を解決するための手段】

【0005】

前記課題を解決するため、本発明者らが鋭意検討を重ねた結果、以下の知見を得た。即ち、表面が、Ni−Cu−無光沢Snめっき及びNi−無光沢Snめっきのいずれかが施されたPCB端子であって、嵌合部が、リフロー処理を施したものであり、半田付け部が、リフロー処理されていないことで、低挿入と半田濡れを両立した端子を提供できるという知見である。

【0006】

本発明は、本発明者らによる前記知見に基づくものであり、前記課題を解決するための手段としては、以下の通りである。即ち、

<1> 嵌合部の摩擦係数が0.26以下で、半田付け部のエージング(PCT:105℃、相対湿度100%)後のゼロクロスタイムが5秒以下であることを特徴とするPCBコネクタ用オス端子。

<2> 嵌合部のSnめっきの光沢度が1.0以上であり、半田付け部のSnめっきの光沢度が1.0未満である<1>に記載のPCBコネクタ用オス端子。

<3> 嵌合部のSnめっきの光沢度が1.5以上であり、半田付け部のSnめっきの光沢度が0.6未満である<1>から<2>のいずれかに記載のPCBコネクタ用オス端子。

<4> 最表面に、Snめっきが施されたPCBコネクタ用オス端子であって、嵌合部が、リフロー処理を施したものであり、半田付け部が、無光沢Snめっきされ、かつリフロー処理されていない<1>から<3>のいずれかに記載のPCBコネクタ用オス端子。

<5> 最表面に、Snめっきが施され、嵌合部がリフロー処理され、半田付け部がリフロー処理されていないPCBコネクタ用オス端子の製造方法であって、リフロー処理炉の中で、温度差をつける事で半田付け部は、リフロー処理を施さず、嵌合部は、リフロー処理を施こすことを特徴とするPCBコネクタ用オス端子の製造方法。

【発明の効果】

【0007】

本発明によれば、主として車載用・民生用の電気配線に使用されるPCB端子であって、コネクタへの挿入に際しての挿入力の低減と、基板側への半田付け部の半田濡れ性の向上に優れたPCB端子及びその製造方法を提供することができる。

【発明を実施するための最良の形態】

【0008】

(Ni−SnめっきPCB端子及びその製造方法)

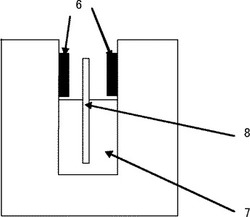

本発明によるNi−SnめっきPCB端子の製造方法は、まず、黄銅その他の銅系金属板の表面を電解脱脂、水洗、酸洗、水洗後,Niめっきする。Niめっきの表面を水洗後、無光沢Snめっきを行う。無光沢Snめっきは、めっき浴に光沢剤が添加されていないめっきである。Sn表面の表面処理後、水洗、乾燥後、嵌合側のみをリフロー処理する。嵌合側のみをリフロー処理する方法を、図3、図4及び図5に示すリフロー処理炉を例にして説明する。被めっき材8は、熱源6の間で加熱される。被めっき材の半田付け部の位置には冷却流体が存在している(図3)。冷却流体は、半田付け部5のみについて熱源5からの輻射熱およびそれに伴う被めっき材内部における熱伝導を遮蔽する(図3)。嵌合側4は、熱を遮断する物質がないため、熱源6からの輻射熱を受け、リフロー処理される。その結果、リフロー処理されていない半田付け部5と、リフロー処理された嵌合部4を持つNi−SnめっきPCB端子を得ることができる。

【0009】

(Ni−Cu−SnめっきPCB端子及びその製造方法)

本発明によるNi−Cu−SnめっきPCB端子の製造方法の第一の態様は、Niめっき層と、Snめっき層の間に、Cuめっきを行うことを除けば、Ni−SnPCB端子の製造方法と同様である。リフロー処理で、半田付け部5への熱を遮断、半田付け部のリフロー処理を避ける。リフロー処理されていない半田付け部5と、リフロー処理された嵌合部4を持つNi−Cu−SnめっきPCB端子を得ることができる。

【0010】

(リフロー処理Snめっきと無光沢かつリフロー処理無しSnめっきの相違点)

本発明の半田付け部めっきの最上層である無光沢かつリフロー処理無しSnめっきと従来技術であるリフロー処理Snめっきには、以下の相違点がある。リフロー処理Snめっきは、熱処理を受けるため、拡散合金層が生成し、結晶粒サイズは粗大化する。また、有機成分が揮発することで、めっき層に含まれるカーボン量が少ない。これに対し、リフロー処理無しSnめっきは、熱処理を受けないため、拡散合金層の生成は少なく、結晶粒サイズは小さく、また、めっき層に含まれるカーボン量は少ない。これらの要素を判断して、本発明の無光沢かつリフロー処理無しSnめっきと、従来技術であるリフロー処理Snめっきを判別することができる。

一般的に無光沢Snとリフロー処理Sn(光沢Sn)は外観の光沢で判別できる。無光沢Snは光沢が無く、リフロー処理Sn(光沢Sn)は光沢があるため一目瞭然である。ただし半光沢Snとは判別が難しい。本件では、光沢度でも定義する。本件でいう無光沢Snは光沢度が1未満であり、リフロー処理Sn(光沢Sn)は1以上である。

光沢度は、(株)日本電色工業製 デンシトメータND−1を使用した。

以上、これらをすべて踏まえた上で無光沢Snとリフロー処理Sn(光沢Sn)とを判別することができる。

【0011】

本発明のPCB端子は、嵌合部のSnめっきの光沢度が、1.0以上であり、好ましくは、1.5以上である。半田付け部のSnめっきの光沢度は、1.0未満であり、好ましくは、0.6未満である。嵌合部のSnめっきの光沢度が1.0未満だと、嵌合部のコネクタへの挿入力が大きくなり、半田付け部のSnめっきの光沢度が1.0以上だと、半田付け部の半田濡れ性が悪化するからである。

又、本発明のPCB端子は、嵌合部の摩擦係数が0.26以下で、半田付け部のエージング(PCT:105℃、相対湿度100%)後のゼロクロスタイムが5秒以下である。嵌合部のコネクタへの挿入力が小さく、半田付け部の半田濡れ性が良いPCB端子とするためである。

【実施例】

【0012】

以下、本発明の実施例について説明するが、本発明はこの実施例に何ら限定されるものではない。

【0013】

(実施例1)

めっき処理前のPCB端子サンプルを、Ni,無光沢Snの順にめっきした。Niめっき液は、常法のスルファミン酸ニッケル浴を使用し、電流密度2A/dm2とした。Niめっきの狙い膜厚は、0.4μmとした。無光沢Snめっき液は、常法のアルカノールスルフォン酸浴を使用し、電流密度は7A/dm2とした。無光沢Snめっきの狙い膜厚は、0.7μmとした。前記図1及び図2で示す方法で、嵌合部のみを400℃、10秒のリフロー処理した。リフロー処理されていない半田付け部と、リフロー処理された嵌合部を持つNi−SnめっきPCB端子を得た。

(実施例2)

めっき処理前のPCB端子サンプルを、Ni,Cu,無光沢Snの順にめっきした。Ni,無光沢Snのめっき液は実施例1と同じである。

Cuめっき液は、常法の硫酸銅浴を使用し、電流密度4A/dm2とした。Niめっきの狙い膜厚は、0.4μm、Cuめっきの狙い膜厚は、0.4μm、無光沢Snめっきの狙い膜厚は、0.7μmとした。前記図3〜図5で示す方法で、実施例1と同じ条件で嵌合部のみをリフロー処理した。リフロー処理されていない半田付け部と、リフロー処理された嵌合部を持つNi−Cu−SnめっきPCB端子を得た。

(比較例1)

めっき処理前のPCB端子サンプルを、Ni,Snの順にめっきした。Niめっきの狙い膜厚は、0.4μm、Snめっきの狙い膜厚は、0.7μmとした。めっきの条件は、実施例1と同じである。

Ni,Snの順にめっきしたPCB端子サンプルの全体をリフロー処理して、半田付け部と嵌合部共にリフロー処理されたNi−SnめっきPCB端子を得た。リフロー処理の温度、時間の条件は実施例1と同じである。

(比較例2)

Snめっきの狙い膜厚を、1.5μmとした以外は、比較例1と同じ条件で、半田付け部と嵌合部共にリフロー処理されたNi−SnめっきPCB端子を得た。

(比較例3)

Ni,Snの順にめっきしたPCB端子サンプルの全体をリフロー処理しなかったこと以外は、比較例1と同じ条件で、半田付け部と嵌合部共にリフロー処理されていないNi−SnめっきPCB端子を得た。

(比較例4)

めっき処理前のPCB端子サンプルを、Ni,Cu,無光沢Snの順にめっきし、全体をリフロー処理した以外は実施例2と同じ条件で、半田付け部と嵌合部共にリフロー処理されたNi−Cu−SnめっきPCB端子を得た。

(比較例5)

Snめっきの狙い膜厚を、1.5μmと厚くした以外は、比較例4と同じ条件で、半田付け部と嵌合部共にリフロー処理されたNi−Cu−SnめっきPCB端子を得た。

【0014】

(評価結果)

挿入力及び半田付け性の評価結果を表1に示す。

<評価基準>

摩擦係数 0.26以下 :○

0.26以上 :×

ゼロクロスタイム(初期評価)

2.0sec 未満:○

2.0sec 以上:×

ゼロクロスタイム(エージング後)

半田濡れする :〇

半田濡れしない :×

<初期半田条件>

半田:Sn−37Pb

200℃±1℃

フラックス:タムラ化研製 UFL−300R

<メニスコ条件>JIS C 0053

メニスコ試験機:株式会社レスカ製 SAT−5100

試験片サイズ:10×25mm

浸漬速度:20±5mm/s

浸漬時間:10±1s

浸漬深さ:2mm

<エージング条件>

PCT:楠本化成(株)製 PM250

105℃、相対湿度100%、8時間

<エージング後半田条件>

半田:Sn−37Pb

230℃±1℃

フラックス:タムラ化研製 ULF−300R

<メニスコ条件>JIS C 0053

メニスコ試験機:株式会社レスカ製 SAT−5100

試験片サイズ:10×25mm

浸漬速度:20±5mm/s

浸漬時間:10±1s

浸漬深さ:2mm

<摩擦係数の測定器>

(株)山崎精機研究所製 電気接点シュミレーターCRS−1

<使用サンプル>

ベース側(メス側)

圧子:DOWAメタルテック(株)製 NB109EH(厚さ0.25mm)に1μmのSnリフローめっきを施したものをインデント加工(R=3)

<測定条件>

摺動速度:60mm/min

接触荷重:3N

摺動距離:7mm

サンプリングデータ範囲:摺動距離2〜5mmの平均値

嵌合部と半田付け部の光沢度について測定した結果を表2に示す。リフロー処理された嵌合部の光沢度は、1.0以上で、リフロー処理されていない半田付け部の光沢度は、1.0未満であった。

【表1】

【表2】

【産業上の利用可能性】

【0015】

本発明は、主として車載用・民生用の電気配線に使用されるPCB端子であって、コネクタへの挿入に際しての嵌合部の挿入力の低減と、基板側への半田付け部の半田濡れ性の向上に優れたPCB端子及びその製造方法を提供することができる。

【図面の簡単な説明】

【0016】

【図1】図1は、PCB端子とコネクタの説明図である。

【図2】図2は、PCB端子の嵌合部と半田付け部の説明図である。

【図3】図3は、リフロー処理炉でロールtoロールで長手方向の断面図である。

【図4】図4は、リフロー処理炉でロールtoロールで長手方向上から見た図である。

【図5】図5は、リフロー処理炉でロールtoロールで長手方向横から見た図である。

【符号の説明】

【0017】

1.PCB端子の嵌合部

2.コネクタ

3.PCB端子の半田付け部

4.PCB端子の嵌合部

5.PCB端子の半田付け部

6.熱源

7.冷却流体

8.被めっき材

【技術分野】

【0001】

主として車載用・民生用の電気配線に使用されるPCBコネクタ用オス端子(以下PCB端子)であって、コネクタへの挿入に際しての嵌合部の挿入力の低減と、基板側への半田付け部の半田濡れ性の向上に優れたPCB端子及びその製造方法に関する。

【背景技術】

【0002】

各種コネクタに使用されるPCB端子は、車載用・民生用の用途があり、電線の通電確保の機能をもっている。図1にPCB端子の概略図を示す。PCB端子は基板側半田付け部5と、相手材とのコネクタとしての嵌合部4とからなる(図2)。PCB端子の嵌合部をコネクタに挿入することで通電が確保される。黄銅等の銅合金を母材とし、表面に、Snめっき層を形成したものが一般的である。Snめっきをする目的は、電気接触部の嵌合側では、低い接触抵抗を得、更に、表面に耐食性を付与することであり、一方、半田付け部では、回路基板への半田付け性をうるためである。

近年、PCB端子の小型化及び接続の高密度化に対する要求が高まっており、その対応として、端子の嵌合側では、接続する際の挿入力を小さくすることが求められる。最上層のSnは、軟質金属であるため、挿入時に容易に塑性変形し、嵌合に大きな挿入力が必要となる。端子の嵌合側の挿入力の低下のため、錫の層厚を薄くする対応が考えられるが、半田付け部の半田付け性が悪化するという問題がある。

上記問題の対策として、黄銅などの銅合金を母材とし、順次Ni,Cu,Snの順でめっきを積層し、リフロー処理で上層のSnをCu−Sn合金化することで、最上層の硬度を上昇させ、PCB端子の挿入力を低減させることができる(特許文献1参照)。しかし、この対策では、PCB端子の挿入力を低減させることができるが、半田付け部の濡れ性が低下してしまうという問題がある。

又、最上層のSn層に、リフロー処理によるCu−Sn合金化層を一部露出させることで、硬度を確保し、端子の挿入力を低減させる工夫がある(特許文献2参照)。しかし、この対策も、PCB端子の挿入力を低減させることができるが、半田濡れ性が低下してしまう。

又、最上層のSn層に、カーボンを含有させる試みもある(特許文献3参照)。しかし、この対策も、PCB端子の挿入力を低減させることができるが、半田濡れ性の低下のほかに、耐食性や曲げ加工性の低下という問題がある。

嵌合部の低挿入力と半田付け部の半田濡れ性の両立が可能なPCB端子が望まれている。

【0003】

【特許文献1】特許第3562719号公報

【特許文献2】特開2006−77307号公報

【特許文献3】特開2006−118054号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

本発明は、主として車載用・民生用の電気配線に使用されるPCB端子であって、コネクタへの挿入に際しての嵌合部の挿入力の低減と、基板側への半田付け部の半田濡れ性の向上に優れたPCB端子及びその製造方法を提供することを目的にする。

【課題を解決するための手段】

【0005】

前記課題を解決するため、本発明者らが鋭意検討を重ねた結果、以下の知見を得た。即ち、表面が、Ni−Cu−無光沢Snめっき及びNi−無光沢Snめっきのいずれかが施されたPCB端子であって、嵌合部が、リフロー処理を施したものであり、半田付け部が、リフロー処理されていないことで、低挿入と半田濡れを両立した端子を提供できるという知見である。

【0006】

本発明は、本発明者らによる前記知見に基づくものであり、前記課題を解決するための手段としては、以下の通りである。即ち、

<1> 嵌合部の摩擦係数が0.26以下で、半田付け部のエージング(PCT:105℃、相対湿度100%)後のゼロクロスタイムが5秒以下であることを特徴とするPCBコネクタ用オス端子。

<2> 嵌合部のSnめっきの光沢度が1.0以上であり、半田付け部のSnめっきの光沢度が1.0未満である<1>に記載のPCBコネクタ用オス端子。

<3> 嵌合部のSnめっきの光沢度が1.5以上であり、半田付け部のSnめっきの光沢度が0.6未満である<1>から<2>のいずれかに記載のPCBコネクタ用オス端子。

<4> 最表面に、Snめっきが施されたPCBコネクタ用オス端子であって、嵌合部が、リフロー処理を施したものであり、半田付け部が、無光沢Snめっきされ、かつリフロー処理されていない<1>から<3>のいずれかに記載のPCBコネクタ用オス端子。

<5> 最表面に、Snめっきが施され、嵌合部がリフロー処理され、半田付け部がリフロー処理されていないPCBコネクタ用オス端子の製造方法であって、リフロー処理炉の中で、温度差をつける事で半田付け部は、リフロー処理を施さず、嵌合部は、リフロー処理を施こすことを特徴とするPCBコネクタ用オス端子の製造方法。

【発明の効果】

【0007】

本発明によれば、主として車載用・民生用の電気配線に使用されるPCB端子であって、コネクタへの挿入に際しての挿入力の低減と、基板側への半田付け部の半田濡れ性の向上に優れたPCB端子及びその製造方法を提供することができる。

【発明を実施するための最良の形態】

【0008】

(Ni−SnめっきPCB端子及びその製造方法)

本発明によるNi−SnめっきPCB端子の製造方法は、まず、黄銅その他の銅系金属板の表面を電解脱脂、水洗、酸洗、水洗後,Niめっきする。Niめっきの表面を水洗後、無光沢Snめっきを行う。無光沢Snめっきは、めっき浴に光沢剤が添加されていないめっきである。Sn表面の表面処理後、水洗、乾燥後、嵌合側のみをリフロー処理する。嵌合側のみをリフロー処理する方法を、図3、図4及び図5に示すリフロー処理炉を例にして説明する。被めっき材8は、熱源6の間で加熱される。被めっき材の半田付け部の位置には冷却流体が存在している(図3)。冷却流体は、半田付け部5のみについて熱源5からの輻射熱およびそれに伴う被めっき材内部における熱伝導を遮蔽する(図3)。嵌合側4は、熱を遮断する物質がないため、熱源6からの輻射熱を受け、リフロー処理される。その結果、リフロー処理されていない半田付け部5と、リフロー処理された嵌合部4を持つNi−SnめっきPCB端子を得ることができる。

【0009】

(Ni−Cu−SnめっきPCB端子及びその製造方法)

本発明によるNi−Cu−SnめっきPCB端子の製造方法の第一の態様は、Niめっき層と、Snめっき層の間に、Cuめっきを行うことを除けば、Ni−SnPCB端子の製造方法と同様である。リフロー処理で、半田付け部5への熱を遮断、半田付け部のリフロー処理を避ける。リフロー処理されていない半田付け部5と、リフロー処理された嵌合部4を持つNi−Cu−SnめっきPCB端子を得ることができる。

【0010】

(リフロー処理Snめっきと無光沢かつリフロー処理無しSnめっきの相違点)

本発明の半田付け部めっきの最上層である無光沢かつリフロー処理無しSnめっきと従来技術であるリフロー処理Snめっきには、以下の相違点がある。リフロー処理Snめっきは、熱処理を受けるため、拡散合金層が生成し、結晶粒サイズは粗大化する。また、有機成分が揮発することで、めっき層に含まれるカーボン量が少ない。これに対し、リフロー処理無しSnめっきは、熱処理を受けないため、拡散合金層の生成は少なく、結晶粒サイズは小さく、また、めっき層に含まれるカーボン量は少ない。これらの要素を判断して、本発明の無光沢かつリフロー処理無しSnめっきと、従来技術であるリフロー処理Snめっきを判別することができる。

一般的に無光沢Snとリフロー処理Sn(光沢Sn)は外観の光沢で判別できる。無光沢Snは光沢が無く、リフロー処理Sn(光沢Sn)は光沢があるため一目瞭然である。ただし半光沢Snとは判別が難しい。本件では、光沢度でも定義する。本件でいう無光沢Snは光沢度が1未満であり、リフロー処理Sn(光沢Sn)は1以上である。

光沢度は、(株)日本電色工業製 デンシトメータND−1を使用した。

以上、これらをすべて踏まえた上で無光沢Snとリフロー処理Sn(光沢Sn)とを判別することができる。

【0011】

本発明のPCB端子は、嵌合部のSnめっきの光沢度が、1.0以上であり、好ましくは、1.5以上である。半田付け部のSnめっきの光沢度は、1.0未満であり、好ましくは、0.6未満である。嵌合部のSnめっきの光沢度が1.0未満だと、嵌合部のコネクタへの挿入力が大きくなり、半田付け部のSnめっきの光沢度が1.0以上だと、半田付け部の半田濡れ性が悪化するからである。

又、本発明のPCB端子は、嵌合部の摩擦係数が0.26以下で、半田付け部のエージング(PCT:105℃、相対湿度100%)後のゼロクロスタイムが5秒以下である。嵌合部のコネクタへの挿入力が小さく、半田付け部の半田濡れ性が良いPCB端子とするためである。

【実施例】

【0012】

以下、本発明の実施例について説明するが、本発明はこの実施例に何ら限定されるものではない。

【0013】

(実施例1)

めっき処理前のPCB端子サンプルを、Ni,無光沢Snの順にめっきした。Niめっき液は、常法のスルファミン酸ニッケル浴を使用し、電流密度2A/dm2とした。Niめっきの狙い膜厚は、0.4μmとした。無光沢Snめっき液は、常法のアルカノールスルフォン酸浴を使用し、電流密度は7A/dm2とした。無光沢Snめっきの狙い膜厚は、0.7μmとした。前記図1及び図2で示す方法で、嵌合部のみを400℃、10秒のリフロー処理した。リフロー処理されていない半田付け部と、リフロー処理された嵌合部を持つNi−SnめっきPCB端子を得た。

(実施例2)

めっき処理前のPCB端子サンプルを、Ni,Cu,無光沢Snの順にめっきした。Ni,無光沢Snのめっき液は実施例1と同じである。

Cuめっき液は、常法の硫酸銅浴を使用し、電流密度4A/dm2とした。Niめっきの狙い膜厚は、0.4μm、Cuめっきの狙い膜厚は、0.4μm、無光沢Snめっきの狙い膜厚は、0.7μmとした。前記図3〜図5で示す方法で、実施例1と同じ条件で嵌合部のみをリフロー処理した。リフロー処理されていない半田付け部と、リフロー処理された嵌合部を持つNi−Cu−SnめっきPCB端子を得た。

(比較例1)

めっき処理前のPCB端子サンプルを、Ni,Snの順にめっきした。Niめっきの狙い膜厚は、0.4μm、Snめっきの狙い膜厚は、0.7μmとした。めっきの条件は、実施例1と同じである。

Ni,Snの順にめっきしたPCB端子サンプルの全体をリフロー処理して、半田付け部と嵌合部共にリフロー処理されたNi−SnめっきPCB端子を得た。リフロー処理の温度、時間の条件は実施例1と同じである。

(比較例2)

Snめっきの狙い膜厚を、1.5μmとした以外は、比較例1と同じ条件で、半田付け部と嵌合部共にリフロー処理されたNi−SnめっきPCB端子を得た。

(比較例3)

Ni,Snの順にめっきしたPCB端子サンプルの全体をリフロー処理しなかったこと以外は、比較例1と同じ条件で、半田付け部と嵌合部共にリフロー処理されていないNi−SnめっきPCB端子を得た。

(比較例4)

めっき処理前のPCB端子サンプルを、Ni,Cu,無光沢Snの順にめっきし、全体をリフロー処理した以外は実施例2と同じ条件で、半田付け部と嵌合部共にリフロー処理されたNi−Cu−SnめっきPCB端子を得た。

(比較例5)

Snめっきの狙い膜厚を、1.5μmと厚くした以外は、比較例4と同じ条件で、半田付け部と嵌合部共にリフロー処理されたNi−Cu−SnめっきPCB端子を得た。

【0014】

(評価結果)

挿入力及び半田付け性の評価結果を表1に示す。

<評価基準>

摩擦係数 0.26以下 :○

0.26以上 :×

ゼロクロスタイム(初期評価)

2.0sec 未満:○

2.0sec 以上:×

ゼロクロスタイム(エージング後)

半田濡れする :〇

半田濡れしない :×

<初期半田条件>

半田:Sn−37Pb

200℃±1℃

フラックス:タムラ化研製 UFL−300R

<メニスコ条件>JIS C 0053

メニスコ試験機:株式会社レスカ製 SAT−5100

試験片サイズ:10×25mm

浸漬速度:20±5mm/s

浸漬時間:10±1s

浸漬深さ:2mm

<エージング条件>

PCT:楠本化成(株)製 PM250

105℃、相対湿度100%、8時間

<エージング後半田条件>

半田:Sn−37Pb

230℃±1℃

フラックス:タムラ化研製 ULF−300R

<メニスコ条件>JIS C 0053

メニスコ試験機:株式会社レスカ製 SAT−5100

試験片サイズ:10×25mm

浸漬速度:20±5mm/s

浸漬時間:10±1s

浸漬深さ:2mm

<摩擦係数の測定器>

(株)山崎精機研究所製 電気接点シュミレーターCRS−1

<使用サンプル>

ベース側(メス側)

圧子:DOWAメタルテック(株)製 NB109EH(厚さ0.25mm)に1μmのSnリフローめっきを施したものをインデント加工(R=3)

<測定条件>

摺動速度:60mm/min

接触荷重:3N

摺動距離:7mm

サンプリングデータ範囲:摺動距離2〜5mmの平均値

嵌合部と半田付け部の光沢度について測定した結果を表2に示す。リフロー処理された嵌合部の光沢度は、1.0以上で、リフロー処理されていない半田付け部の光沢度は、1.0未満であった。

【表1】

【表2】

【産業上の利用可能性】

【0015】

本発明は、主として車載用・民生用の電気配線に使用されるPCB端子であって、コネクタへの挿入に際しての嵌合部の挿入力の低減と、基板側への半田付け部の半田濡れ性の向上に優れたPCB端子及びその製造方法を提供することができる。

【図面の簡単な説明】

【0016】

【図1】図1は、PCB端子とコネクタの説明図である。

【図2】図2は、PCB端子の嵌合部と半田付け部の説明図である。

【図3】図3は、リフロー処理炉でロールtoロールで長手方向の断面図である。

【図4】図4は、リフロー処理炉でロールtoロールで長手方向上から見た図である。

【図5】図5は、リフロー処理炉でロールtoロールで長手方向横から見た図である。

【符号の説明】

【0017】

1.PCB端子の嵌合部

2.コネクタ

3.PCB端子の半田付け部

4.PCB端子の嵌合部

5.PCB端子の半田付け部

6.熱源

7.冷却流体

8.被めっき材

【特許請求の範囲】

【請求項1】

嵌合部の摩擦係数が0.26以下で、半田付け部のエージング(PCT:105℃、相対湿度100%)後のゼロクロスタイムが5秒以下であることを特徴とするPCBコネクタ用オス端子。

【請求項2】

嵌合部のSnめっきの光沢度が1.0以上であり、半田付け部のSnめっきの光沢度が1.0未満である請求項1に記載のPCBコネクタ用オス端子。

【請求項3】

嵌合部のSnめっきの光沢度が1.5以上であり、半田付け部のSnめっきの光沢度が0.6未満である請求項1から2のいずれかに記載のPCBコネクタ用オス端子。

【請求項4】

最表面に、Snめっきが施されたPCBコネクタ用オス端子であって、嵌合部が、リフロー処理を施したものであり、半田付け部が、無光沢Snめっきされ、かつリフロー処理されていない請求項1から3のいずれかに記載のPCBコネクタ用オス端子。

【請求項5】

最表面に、Snめっきが施され、嵌合部がリフロー処理され、半田付け部がリフロー処理されていないPCBコネクタ用オス端子の製造方法であって、リフロー処理炉の中で温度差をつける事で、半田付け部は、リフロー処理を施さず、嵌合部は、リフロー処理を施こすことを特徴とするPCBコネクタ用オス端子の製造方法。

【請求項1】

嵌合部の摩擦係数が0.26以下で、半田付け部のエージング(PCT:105℃、相対湿度100%)後のゼロクロスタイムが5秒以下であることを特徴とするPCBコネクタ用オス端子。

【請求項2】

嵌合部のSnめっきの光沢度が1.0以上であり、半田付け部のSnめっきの光沢度が1.0未満である請求項1に記載のPCBコネクタ用オス端子。

【請求項3】

嵌合部のSnめっきの光沢度が1.5以上であり、半田付け部のSnめっきの光沢度が0.6未満である請求項1から2のいずれかに記載のPCBコネクタ用オス端子。

【請求項4】

最表面に、Snめっきが施されたPCBコネクタ用オス端子であって、嵌合部が、リフロー処理を施したものであり、半田付け部が、無光沢Snめっきされ、かつリフロー処理されていない請求項1から3のいずれかに記載のPCBコネクタ用オス端子。

【請求項5】

最表面に、Snめっきが施され、嵌合部がリフロー処理され、半田付け部がリフロー処理されていないPCBコネクタ用オス端子の製造方法であって、リフロー処理炉の中で温度差をつける事で、半田付け部は、リフロー処理を施さず、嵌合部は、リフロー処理を施こすことを特徴とするPCBコネクタ用オス端子の製造方法。

【図1】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【図2】

【公開番号】特開2008−287942(P2008−287942A)

【公開日】平成20年11月27日(2008.11.27)

【国際特許分類】

【出願番号】特願2007−129869(P2007−129869)

【出願日】平成19年5月15日(2007.5.15)

【出願人】(506365131)DOWAメタルテック株式会社 (109)

【Fターム(参考)】

【公開日】平成20年11月27日(2008.11.27)

【国際特許分類】

【出願日】平成19年5月15日(2007.5.15)

【出願人】(506365131)DOWAメタルテック株式会社 (109)

【Fターム(参考)】

[ Back to top ]