PLLシンセサイザ

【課題】温度補償ループフィルタのキャパシタの容量値を小さくする。

【解決手段】PLLシンセサイザは,位相比較器PDと,ループフィルタLFと,電圧制御発振器VCOとを有する。さらに,温度補償ループとして,周波数制御電圧が制御電圧範囲から外れたときに比較信号30を出力する比較器CMPと,比較信号30を積分してMビットの第1のデジタル信号32を生成するデジタルフィルタDFと,第1のデジタル信号32を入力し,前記Mビットより少ないNビットで、前記第1のデジタル信号32に対応する第2のデジタル信号34を生成するΣΔ変調器12、10と,第2のデジタル信号34を電流信号36に変換する温度補償チャージポンプCPtと,前記電流信号36を温度補償制御電圧に変換する温度補償ループフィルタTFとを有し,電圧制御発振器VCOは温度補償制御電圧ftに基づいて出力クロックCKoutの周波数を制御する。

【解決手段】PLLシンセサイザは,位相比較器PDと,ループフィルタLFと,電圧制御発振器VCOとを有する。さらに,温度補償ループとして,周波数制御電圧が制御電圧範囲から外れたときに比較信号30を出力する比較器CMPと,比較信号30を積分してMビットの第1のデジタル信号32を生成するデジタルフィルタDFと,第1のデジタル信号32を入力し,前記Mビットより少ないNビットで、前記第1のデジタル信号32に対応する第2のデジタル信号34を生成するΣΔ変調器12、10と,第2のデジタル信号34を電流信号36に変換する温度補償チャージポンプCPtと,前記電流信号36を温度補償制御電圧に変換する温度補償ループフィルタTFとを有し,電圧制御発振器VCOは温度補償制御電圧ftに基づいて出力クロックCKoutの周波数を制御する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は,PLLシンセサイザに関する。

【背景技術】

【0002】

PLLシンセサイザは,基準クロックに位相同期した高周波クロックを生成するクロック生成回路であり,例えば,無線システムやプロセッサなどに内蔵される。

【0003】

PLLシンセサイザは,出力クロックの位相と基準クロックの位相とを比較する位相比較器と,位相比較器の位相結果に応じた制御電圧を生成するループフィルタと,その制御電圧に基づく周波数の出力クロックを生成する電圧制御発振器とを有する。そして,出力クロックは位相比較器にフィードバックされる。

【0004】

電圧制御発振器は,ループフィルタが生成する制御電圧に応じてその発振周波数が変化し,さらに,制御周波数バンドに応じて制御電圧による周波数制御範囲が変化する。制御周波数バンドにより周波数制御範囲を変更できるようにして,電圧制御発振器の周波数範囲を広くしている。

【0005】

さらに,電圧制御発振器は,温度変化によりその周波数が変動する。温度が変化したことにより制御電圧による周波数制御範囲を超えて周波数が変動する場合は,制御周波数バンドを変更する制御が行われる。制御周波数バンドを変更して周波数制御範囲を変更したとき,発振周波数がジャンプしてPLLが一時的にアンロック状態になる可能性がある。したがって,温度変化により制御周波数バンドが変更されることを防止することが必要になる。

【0006】

このような温度変化による制御周波数バンドの変更を避けるために,PLL回路は,メインのPLLループに加えて,温度補償ループを有する。温度補償ループは,メインのPLLループにより生成される制御電圧を基準電圧と比較し,その差分値に基づいてチャージポンプ回路と温度補償ループフィルタ(LPF)により温度補償電圧を生成する。そして,この温度補償電圧により,電圧制御発振器の発振周波数が微調整される。つまり,温度補償ループを設けることで,温度変化による発振周波数の変動を抑制することができる。

【0007】

PLL回路については,以下の特許文献1,2,3に記載されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開平10−322198号公報

【特許文献2】特開2007−259431号公報

【特許文献3】特開2006−526946号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかし,温度補償ループはその時定数を大きくして応答速度を遅くし,メインのPLLループによる制御と競合しないようにする必要がある。それと同時に,温度補償ループ内の温度補償ループフィルタは,チャージポンプ回路の出力の高周波成分をカットしてノイズ成分を除去することが求められる。その結果,温度補償ループフィルタ内のキャパシタの容量値を大きくしなければならず,PLL回路と同じ集積回路チップ内に内蔵することは困難であり,温度補償ループフィルタをチップの外に設けなければならない。

【0010】

さらに,温度補償ループフィルタの容量値を大きくしたため,システムのスリープ状態から起動するときに,そのループフィルタのキャパシタを充電する時間が長くなり,起動時間が長くなる。そのため,スリープ状態でもキャパシタの充電状態を保つために充電電流が消費され,スリープ状態での省電力化の妨げになっている。

【0011】

そこで,本発明の目的は,温度補償ループ内のループフィルタのキャパシタ容量値を小さくしたPLL回路を提供することにある。

【課題を解決するための手段】

【0012】

PLLシンセサイザの第1の側面は,出力クロックと基準クロックとの位相を比較する位相比較器と,

前記位相比較器の位相比較結果に応じて周波数制御電圧を生成するPLLループフィルタと,

前記周波数制御電圧に応じて制御された周波数を持つ前記出力クロックを生成する電圧制御発振器と,

前記周波数制御電圧が制御電圧範囲から外れたときにそれぞれ第1,第2のレベルを有する比較信号を出力する比較器と,

第1の制御クロックに同期して前記比較信号を積分してMビットの第1のデジタル信号を生成するデジタルフィルタと,

前記第1のデジタル信号を入力し,前記第1の制御クロックより高周波の第2の制御クロックに同期して,前記Mビットより少ないNビットの第2のデジタル信号であって前記第1のデジタル信号に対応する第2のデジタル信号を生成するΔΣ変調器と,

前記第2のデジタル信号を電流信号に変換する温度補償チャージポンプと,

前記電流信号により充放電されるキャパシタを有し,前記電流信号を温度補償制御電圧に変換する温度補償ループフィルタとを有し,

前記電圧制御発振器は前記温度補償制御電圧に基づいて前記出力クロックの周波数を制御する。

【発明の効果】

【0013】

第1の側面によれば,温度補償ループ内のループフィルタのキャパシタ容量値を小さくできる。

【図面の簡単な説明】

【0014】

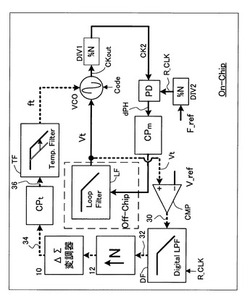

【図1】本実施の形態に関連するPLLシンセサイザの構成図である。

【図2】第1の実施の形態におけるPLLシンセサイザの構成図である

【図3】電圧制御発振器VCOの概略構成図である。

【図4】電圧制御発振器VCOの周波数の制御について説明する図である。

【図5】本実施の形態における温度補償ループの構成と信号とを示す図である。

【図6】デジタルフィルタDFの回路例を示す図である。

【図7】ΔΣ変調器の回路例を示す図である。

【図8】チャージポンプCPtと温度補償ループフィルタTFの回路例を示す図である。

【図9】チャージポンプCPtと温度補償ループフィルタTFの別の回路例を示す図である。

【図10】温度補償ループフィルタTFの周波数特性を説明する図である。

【図11】温度補償ループフィルタについて説明する図である。

【図12】PLLシンセサイザが復帰するときの動作について説明する図である。

【図13】第2の実施の形態におけるPLLシンセサイザの温度補償ループの構成図である。

【図14】第2の実施の形態におけるPLLシンセサイザの温度補償ループのスリープ状態からの復帰動作を示す図である。

【発明を実施するための形態】

【0015】

図1は,本実施の形態に関連するPLLシンセサイザの構成図である。PLLシンセサイザは,出力クロックCKoutを分周器DIV1で分周したクロックCK2と,基準クロックR-CLKとの位相を比較する位相比較器PDと,位相比較器PDの位相比較結果dPHを電流値に変換するチャージポンプ回路CPmと,チャージポンプ回路CPmが生成する電流を積分し高周波成分をカットして周波数制御電圧Vtを生成するループフィルタLFと,周波数制御電圧Vtに応じて制御された周波数を持つ出力クロックCKoutを生成する電圧制御発振器VCOとを有する。

【0016】

電圧制御発振器VCOには,図示しないシステム側から制御コードCodeが供給され,制御コードCodeに対応して,周波数制御電圧Vtで制御される周波数範囲が選択される。このフィードバックループがPLLのメインループである。

【0017】

上記のメインループ(図中実線)に加えて,図中破線で示された温度補償ループが設けられる。温度補償ループでは,周波数制御電圧Vtと基準電圧V_refとを比較し,基準電圧に基づく所定の制御電圧範囲から外れたときにそれぞれ第1,第2のレベルを有する比較信号を出力する比較器CMPと,周波数制御電圧Vtと基準電圧V_refとの差分に応じた電流を出力するチャージポンプ回路CPtとを有する。この比較器CMPとチャージポンプ回路CPtとによりOTA(Operational Transconductance Amplifier)が構成される。

【0018】

そして,温度補償ループフィルタTFがその電流を積分すると共に高周波成分をカットして温度補償制御電圧ftを出力する。温度補償ループフィルタTFは,比較的大きな容量のキャパシタを有し,上記の電流の積分と高周波成分のカットに加えて,メインループより温度補償ループの時定数を大きくしている。

【0019】

メインループのPLLループフィルタLFと,温度補償ループの温度補償ループフィルタTFは,共に大容量のキャパシタを有するため,PLLシンセサイザ回路が形成されるチップ10内には設けられないことが多く,チップ外20に設けられる。

【0020】

図2は,第1の実施の形態におけるPLLシンセサイザの構成図である。PLLシンセサイザは,図1と同様に,出力クロックCKoutを分周器DIV1で分周したクロックCK2と,基準クロックR-CLKとの位相を比較する位相比較器PDと,位相比較結果dPHを電流値に変換するチャージポンプ回路CPmと,その電流を積分し高周波成分をカットして周波数制御電圧Vtを生成するPLLループフィルタLFと,周波数制御電圧Vtに応じて出力クロックCKoutの周波数を制御する電圧制御発振器VCOとを有する。

【0021】

電圧制御発振器VCOは,システム側から供給される制御コードCodeに対応して,周波数制御電圧Vtで制御される周波数範囲が選択される。そして,その周波数範囲内で周波数制御電圧Vtに応じて出力クロックCKoutの周波数が制御される。このフィードバックループがPLLのメインループである。

【0022】

第1の実施の形態のPLLシンセサイザも,図中破線で示された温度補償ループを有する。この温度補償ループは,周波数制御電圧Vtが制御電圧範囲から外れたときにそれぞれ第1,第2のレベルを有する比較信号30を出力する比較器と,第1の制御クロックR_CLKに同期して比較信号30を積分してMビットの第1のデジタル信号32を生成するデジタルフィルタDFと,第1のデジタル信号32を入力し,第1の制御クロックR_CLKより高周波の第2の制御クロックに同期して,Mビットより少ないNビットの第2のデジタル信号34であって第1のデジタル信号に対応する第2のデジタル信号34を生成するΔΣ変調器12,10と,第2のデジタル信号34を電流信号36に変換する温度補償チャージポンプCPtと,電流信号36により充放電されるキャパシタを有し,電流信号を温度補償制御電圧ftに変換する温度補償ループフィルタTFとを有する。そして,電圧制御発振器VCOは,温度補償制御電圧ftに基づいて出力クロックCKoutの周波数を制御する。

【0023】

このPLLシンセサイザでは,温度補償ループフィルタTFのキャパシタ容量を小さくできるので,PLLシンセサイザの回路と同じチップ内に設けられている。ただし,PLLループフィルタLFは,キャパシタ容量が大きいためチップ外に設けられている。

【0024】

図3は,電圧制御発振器VCOの概略構成図である。電圧制御発振器VCOは,例えばLC発振回路で構成され,LC発振回路内のキャパシタの容量が制御コードCode,制御電圧Vt,温度補償制御電圧ftにより変更される。それにより,発振周波数が制御される。図3の例では,LC発振器内のキャパシタは,周波数制御電圧Vtにより容量値が可変制御される第1のキャパシタC1と,温度補償制御電圧ftにより容量値が可変制御される第2のキャパシタC2と,制御コードCodeによりスイッチを介して接続または非接続される第3のキャパシタ群C3_1〜C3_nとを有する。第3のキャパシタ群の容量値は比較的大きいのに対して,第1,第2のキャパシタC1,C2の容量値はそれよりも比較的小さい。

【0025】

図4は,電圧制御発振器VCOの周波数の制御について説明する図である。図4(A)は,温度補償ループがない場合の電圧制御発振器VCOの周波数制御を示す。制御コードCode(図中001,010,011)に応じて,周波数f0の制御範囲が切り替えられる。そして,周波数制御電圧Vtに応じて,制御コードCodeで設定された周波数制御範囲内で周波数f0が可変制御される。

【0026】

図4(A)中に示されるとおり,電圧制御発振器VCOが周波数Aで発振しているときに,温度の上昇で周波数Bに変動して制御コード010の周波数制御範囲外になると,制御コードが010から011に切り替えられ,周波数制御範囲が1段階上にシフトする。その結果,同じ周波数制御電圧Vtでは周波数がCとなり大きく変更したことでロックオフする場合がある。この場合,PLLメインループにより周波数制御電圧Vtが変更され,周波数Dに制御され,再度ロックオンする制御が行われる。

【0027】

図4(B)は,温度補償ループによる周波数制御が加わった電圧制御発振器VCOの周波数制御を示す。図4(B)の左側は,図4(A)と同じであり,制御コードと周波数制御電圧Vtとによる周波数制御を示している。この図において周波数制御電圧Vtは図中Va,Vbの間で制御されることが望ましいとする。そして,図4(B)の右側は,ある周波数制御範囲内において温度補償制御電圧ftによる周波数制御を示している。周波数Aで発振しているときに,温度上昇が生じて周波数が上昇しようとした場合,温度補償ループによりその周波数制御電圧Vtの変動を検出し,温度補償制御電圧ftにより発振器VCOのキャパシタC2の容量値を可変制御し,温度上昇により周波数が上昇しないようにする。その結果,周波数制御電圧Vtの制御範囲がVa,Vb間の範囲から外れないようにされる。

【0028】

このように,図2の温度補償付きPLLシンセサイザでは,電圧制御発振器VCOが,制御コードCodeと周波数制御電圧Vtとに加えて,温度補償制御電圧ftによってもその周波数制御が行われる。一般に,メインのループに比較して,温度補償ループの時定数は大きく設定されている。それにより,メインループの周波数制御と温度補償ループによる周波数制御とが干渉して競合することが回避される。

【0029】

図5は,本実施の形態における温度補償ループの構成と信号とを示す図である。図5を参照しながら,温度補償ループを構成する各回路について説明する。

【0030】

比較器は,周波数制御電圧Vtを基準電圧Vref+とVref-と比較する2つの比較器CMP1,CMP2を有する。比較器の出力30は,図5中(2)に示されるとおり,周波数制御電圧Vtが高い基準電圧Vref+を超えると第1のレベル(例えば+1)になり,低い基準電圧Vref-を超えると第2のレベル(図中破線,例えば−1)になる。

【0031】

図6は,デジタルフィルタDFの回路例を示す図である。デジタルフィルタDFは一種の積分器であり,比較器の出力30を増幅する増幅器40と,加算器41と,遅延回路42と,増幅器43とを有する。遅延回路42が増幅された比較器出力30を例えば基準クロックR_CLKの1周期分だけ遅延させ,加算器41が新たな比較器出力30に加算することで,積分値が生成される。このデジタルフィルタDFの出力32は,例えばMビットのデジタル信号である。

【0032】

図5中(3)にデジタルフィルタの出力32の波形の例が示されている。比較器出力30の+1に対して,基準クロックR_CLKに同期した積分値がデジタルフィルタDFのMビット出力32として出力される。このように,デジタルフィルタ32が比較器出力30を積分することで,比較器出力30の変化に対する応答性を遅くすることができ,温度補償ループの時定数を大きくすることができる。すなわち,図1において,温度補償ループ内の温度フィルタTFが有していた応答を遅くする機能が,このデジタルフィルタ32により実現される。

【0033】

図7は,ΔΣ変調器の回路例を示す図である。本実施の形態の温度補償ループ内に設けられるΔΣ変調器10,12は,デジタルフィルタDFのMビット出力32を,デジタルフィルタのクロックR_CLKよりも高い周波数dCLKでアップサンプリングし,Mビットより少ないビット数のNビットの高周波デジタル信号34に変換する。高周波デジタル信号34は擬似ランダムデジタル信号であり,時間軸上で平均するとデジタル信号32の値と等しくなる。

【0034】

高周波デジタル信号に変換することで,後段の温度補償ループフィルタのカットオフ周波数を高く設定でき,キャパシタの容量値を小さくできる。また,擬似ランダムデジタル信号に変換することでノイズシェーピングされ,低周波帯域での量子化ノイズを小さくすることができる。

【0035】

図7にはΔΣ変調器の一例として2次のΔΣ変調器が示されている。この変調器は,Mビットデジタル信号32をクロックdCLKでサンプリングする入力レジスタ50と,加算器51と,その加算器の加算値X+YをクロックdCLKでラッチするレジスタ52とを有し,レジスタ52のラッチした値は加算器51にフィードバックされる。この構成により,加算器51のキャリ信号C(1ビット)が生成される。さらに,変調器は,レジスタ52がラッチした値を加算する加算器53と,加算器53の加算値X+YをクロックdCLKでラッチするレジスタ54とを有し,レジスタ54がラッチした値は加算器53にフィードバックされる。さらに,加算器53のキャリ信号Cは,レジスタ55と減算器56からなる微分回路57によりその微分値が求められ,加算器58が微分値と加算器51のキャリ信号Cとを加算し,Nビット(2ビット)のデジタル出力34を出力する。

【0036】

このデジタル出力34は,Mビットのデジタル入力32よりも高周波であり,且つMビットより少ないNビットの擬似ランダムなデジタル信号である。図5の(4)に示されるとおり,ΔΣ変調器は,デジタル入力信号32をより高い周波数で且つ少ないビットのデジタル信号34に変換する回路であり,図5の(4)では2ビット(4量子点)のデジタル信号に変換されている。デジタル出力信号34は,デジタル入力信号32よりも高い周波数で変化していることが示されている。つまり,高周波で且つ低ビットのデジタル出力信号34は,低周波で高いビットのデジタル入力信号32を,高い周波数で変調したものである。

【0037】

図7には,ΔΣ変調器のアップサンプリング用の高周波クロックdCLKが,PLLメインループ内の分周器DIV1により生成される例が示されている。VCOの出力クロックCKoutが,分周器DIV1内の2つの分周器46,47により分周される。この前段の分周器46が出力するクロックdCLKが,ΔΣ変調器のサンプリングクロックdCLKとして利用される。そして,このクロックdCLKは,デジタルフィルタDFの同期クロックR_CLKよりも高周波である。

【0038】

図8は,チャージポンプCPtと温度補償ループフィルタTFの回路例を示す図である。図8のチャージポンプCPtは,1ビット入力に対応した回路であり,電流源I1,I2とスイッチSW1,SW2とからなる。入力34が「1」の場合はスイッチSW1が導通して電流I1が供給され,入力34が「0」の場合はスイッチSW2が導通して電流I2が引き抜かれる。つまり入力が「1」で正電流が発生し,入力「0」で負電流が発生する。

【0039】

温度補償ループフィルタTFの最も簡単な構成は,上記の電流を蓄積する単一のキャパシタである。ただし,図8に示したループフィルタTFは,抵抗R10,R11とキャパシタC10,C11,C12からなる。図8中に示されるとおり,入力が「1」の場合,チャージポンプCPtは正電流を発生し出力電圧ftが上昇し,入力が「0」の場合,チャージポンプCPtは負電流を発生し出力電圧ftが下降する。ループフィルタTFは,一種のローパスフィルタであり,チャージポンプが生成する電流の高周波成分をカットする。したがって,キャパシタC10, C11, C12の合計容量値が小さいほど,カットオフ周波数が高くなる。

【0040】

図9は,チャージポンプCPtと温度補償ループフィルタTFの別の回路例を示す図である。図9のチャージポンプCPtは,2ビット入力に対応した回路である。入力34が「1」の場合にスイッチSW1が導通し,入力34が「2」の場合にスイッチSW1,SW3が導通し,入力34が「0」の場合にはどのスイッチも導通せず,入力34が「−1」の場合にスイッチSW2が導通する。

【0041】

それに伴い,チャージポンプCPtは,入力が「2」なら正電流2×I1,入力が「1」なら正電流I1,入力が「0」なら電流は発生せず,入力が「−1」なら負電流I1をそれぞれ出力する。

【0042】

そして,図9の温度補償ループフィルタTFは,1つのキャパシタで構成されている。もちろん,図8に示した温度補償ループフィルタTFであってもよい。この場合も,キャパシタの容量値が小さいほど,カットオフ周波数が高くなる。

【0043】

ΔΣ変調器10,12を採用したことによりデジタルフィルタDFのデジタル出力32が高周波のデジタル信号34に変換されるので,図8,図9に示した温度補償ループフィルタTFのカットオフ周波数を,従来のフィルタよりも高く設定することができる。つまりカットすべきデジタルフィルタDFのデジタル出力32の高周波成分は,ΔΣ変調器によるアップサンプリングにより,より高周波帯に移されている。その結果,温度補償ループフィルタTFのカットオフ周波数も高くすることができ,温度補償ループフィルタTFの容量値を小さくすることができる。このことは,PLLシンセサイザと同じチップ内にこの温度補償ループフィルタTFを設けることが容易になることを意味する。

【0044】

図10は,温度補償ループフィルタTFの周波数特性を説明する図である。実線が従来の温度補償ループフィルタの特性である。それに対して,破線が本実施の形態における温度補償ループフィルタTFの特性である。破線のほうがカットオフ周波数がより高くなっていることが理解できる。

【0045】

上記のように,第1の実施の形態によれば,比較器の比較信号をデジタルフィルタDFにより積分してMビットのデジタル出力信号32に変換したことで,温度補償フィルタの応答性を遅くし時定数を大きくすることができる。さらに,デジタルフィルタのMビットのデジタル出力信号32が,ΔΣ変調器によりアップサンプリングされN(<M)ビットのデジタル出力信号34に変換されている。これにより,より高周波のデジタル出力信号34に変換されたことで,アナログフィルタである温度補償ループフィルタTFのカットオフ周波数を高く設定することが可能になり,その分,温度補償ループフィルタTFのキャパシタの容量値を小さくして,チップ内面積を小さくすることができる。

【0046】

[第2の実施の形態]

温度補償ループフィルタTFの容量値を小さくしたことで,スリープモード中の充電電流を削減することができるとともに,スリープモードから復帰したときのPLLシンセサイザのロックオンまでの時間を短縮することができる。以下,この点について説明する。

【0047】

図11は,温度補償ループフィルタについて説明する図である。図11(A)には,図1に示した温度補償ループ内のOTAと温度補償ループフィルタTFと,電圧制御発振器VCOが示されている。OTAは,比較器CMPとチャージポンプCPtの組み合わせであり,温度補償ループフィルタTFは図8,図9に示したキャパシタを有する回路である。

【0048】

図11(B)に示すように,PLLシンセサイザが通信装置に内蔵された場合,通信タイムスロット間ではスリープモードに制御される。スリープモードではPLLシンセサイザの動作は停止し出力クロックの生成は停止する。一方で,ループフィルタTFは,キャパシタにある程度の電荷が蓄積されないと通常動作時の周波数制御電圧ftを出力することができない。そこで,プリチャージ回路60を設けて,スリープモード中もループフィルタTF内のキャパシタに電流を供給することが必要になる。

【0049】

図12は,PLLシンセサイザが復帰するときの動作について説明する図である。図12(A)は,起動時またはスリープモードからの復帰時の動作を示している。起動時または復帰時において,プリチャージ回路60からループフィルタTF内のキャパシタにプリチャージし(時間t1),その後,PLLシンセサイザのメインループ及び温度補償ループによる周波数制御が行われる(時間t2)。その場合,時間t1+t2がPLLのロックアップまでの制限時間TLimitを超える場合がある。

【0050】

そこで,図12(B)に示されるように,スリープモード中もプリチャージ回路60からプリチャージ電流を継続して供給することで,復帰後はPLLシンセサイザの周波数制御によるロックまでの時間t2だけが必要になり,ロックアップまでの制限時間TLimitまでにロック状態にすることが可能になる。ただし,この場合は,スリープモード中もプリチャージ電流を供給する必要があり,スリープモードの省電力化に反することになる。

【0051】

図13は,第2の実施の形態におけるPLLシンセサイザの温度補償ループの構成図である。この温度補償ループの構成は,図5の温度補償ループに加えて,スリープ状態に入るときのデジタルフィルタDFのデジタル出力32を記憶するメモリ62と,スリープ状態から復帰するときにメモリ62に記憶されているデジタル出力32の値に応じて温度補償ループフィルタTF内のキャパシタをプリチャージするプリチャージ回路60とを有する。

【0052】

すなわち,スリープ状態に移行する時は,温度補償ループフィルタTF内のキャパシタには,デジタルフィルタDFのMビットのデジタル出力32の値に応じた電荷が充電されている。そこで,スリープ状態に移行するときはメモリ62にそのデジタル出力32を記憶する。メモリ62は,スリープ状態でも記憶データが消失しない不揮発性メモリである。スリープ状態中はプリチャージ回路60からプリチャージ電流がループフィルタTFに供給されることはない。

【0053】

そして,スリープモードから復帰するときに,プリチャージ回路60は,メモリ62に記憶されているデジタル出力32を読み出し,そのデジタル出力値に応じた電圧までループフィルタTF内のキャパシタを充電する。ループフィルタTF内のキャパシタの容量値は小さく構成されているので,このプリチャージに要する時間は短い。

【0054】

図14は,第2の実施の形態におけるPLLシンセサイザの温度補償ループのスリープ状態からの復帰動作を示す図である。図13で説明したとおり,第2の実施の形態では,スリープ状態においては温度補償ループフィルタTFへのプリチャージ電流の供給は行わない。その代わり,スリープ状態から復帰する時に,プリチャージ回路60は,メモリ62に記憶しておいたデジタル出力値に応じた電荷量を温度補償ループフィルタTFのキャパシタの供給する。ただし,キャパシタの容量が小さいので,図14に示すとおり,プリチャージ時間t1は短くできる。

【0055】

その結果,この短いプリチャージ時間t1とその後のPLLによる周波数制御によるロックオンまでの時間t2の合計は,ロックオンまでの制限時間TLimit未満にすることが可能になる。

【0056】

以上の通り,第2の実施の形態によれば,スリープ期間中のプリチャージ電流の消費がなくなり,省電力化を図ることができる。

【符号の説明】

【0057】

PD:位相比較器 CPm:メインループのチャージポンプ

LF:PLLループフィルタ VCO:電圧制御発振器

Vt:周波数制御電圧 DIV1:分周器

CKout:出力クロック CMP:比較器

DF:デジタルフィルタ 10,12:ΔΣ変調器

CPt:温度補償ループのチャージポンプ

TF:温度補償ループフィルタ ft:温度補償制御電圧

【技術分野】

【0001】

本発明は,PLLシンセサイザに関する。

【背景技術】

【0002】

PLLシンセサイザは,基準クロックに位相同期した高周波クロックを生成するクロック生成回路であり,例えば,無線システムやプロセッサなどに内蔵される。

【0003】

PLLシンセサイザは,出力クロックの位相と基準クロックの位相とを比較する位相比較器と,位相比較器の位相結果に応じた制御電圧を生成するループフィルタと,その制御電圧に基づく周波数の出力クロックを生成する電圧制御発振器とを有する。そして,出力クロックは位相比較器にフィードバックされる。

【0004】

電圧制御発振器は,ループフィルタが生成する制御電圧に応じてその発振周波数が変化し,さらに,制御周波数バンドに応じて制御電圧による周波数制御範囲が変化する。制御周波数バンドにより周波数制御範囲を変更できるようにして,電圧制御発振器の周波数範囲を広くしている。

【0005】

さらに,電圧制御発振器は,温度変化によりその周波数が変動する。温度が変化したことにより制御電圧による周波数制御範囲を超えて周波数が変動する場合は,制御周波数バンドを変更する制御が行われる。制御周波数バンドを変更して周波数制御範囲を変更したとき,発振周波数がジャンプしてPLLが一時的にアンロック状態になる可能性がある。したがって,温度変化により制御周波数バンドが変更されることを防止することが必要になる。

【0006】

このような温度変化による制御周波数バンドの変更を避けるために,PLL回路は,メインのPLLループに加えて,温度補償ループを有する。温度補償ループは,メインのPLLループにより生成される制御電圧を基準電圧と比較し,その差分値に基づいてチャージポンプ回路と温度補償ループフィルタ(LPF)により温度補償電圧を生成する。そして,この温度補償電圧により,電圧制御発振器の発振周波数が微調整される。つまり,温度補償ループを設けることで,温度変化による発振周波数の変動を抑制することができる。

【0007】

PLL回路については,以下の特許文献1,2,3に記載されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開平10−322198号公報

【特許文献2】特開2007−259431号公報

【特許文献3】特開2006−526946号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかし,温度補償ループはその時定数を大きくして応答速度を遅くし,メインのPLLループによる制御と競合しないようにする必要がある。それと同時に,温度補償ループ内の温度補償ループフィルタは,チャージポンプ回路の出力の高周波成分をカットしてノイズ成分を除去することが求められる。その結果,温度補償ループフィルタ内のキャパシタの容量値を大きくしなければならず,PLL回路と同じ集積回路チップ内に内蔵することは困難であり,温度補償ループフィルタをチップの外に設けなければならない。

【0010】

さらに,温度補償ループフィルタの容量値を大きくしたため,システムのスリープ状態から起動するときに,そのループフィルタのキャパシタを充電する時間が長くなり,起動時間が長くなる。そのため,スリープ状態でもキャパシタの充電状態を保つために充電電流が消費され,スリープ状態での省電力化の妨げになっている。

【0011】

そこで,本発明の目的は,温度補償ループ内のループフィルタのキャパシタ容量値を小さくしたPLL回路を提供することにある。

【課題を解決するための手段】

【0012】

PLLシンセサイザの第1の側面は,出力クロックと基準クロックとの位相を比較する位相比較器と,

前記位相比較器の位相比較結果に応じて周波数制御電圧を生成するPLLループフィルタと,

前記周波数制御電圧に応じて制御された周波数を持つ前記出力クロックを生成する電圧制御発振器と,

前記周波数制御電圧が制御電圧範囲から外れたときにそれぞれ第1,第2のレベルを有する比較信号を出力する比較器と,

第1の制御クロックに同期して前記比較信号を積分してMビットの第1のデジタル信号を生成するデジタルフィルタと,

前記第1のデジタル信号を入力し,前記第1の制御クロックより高周波の第2の制御クロックに同期して,前記Mビットより少ないNビットの第2のデジタル信号であって前記第1のデジタル信号に対応する第2のデジタル信号を生成するΔΣ変調器と,

前記第2のデジタル信号を電流信号に変換する温度補償チャージポンプと,

前記電流信号により充放電されるキャパシタを有し,前記電流信号を温度補償制御電圧に変換する温度補償ループフィルタとを有し,

前記電圧制御発振器は前記温度補償制御電圧に基づいて前記出力クロックの周波数を制御する。

【発明の効果】

【0013】

第1の側面によれば,温度補償ループ内のループフィルタのキャパシタ容量値を小さくできる。

【図面の簡単な説明】

【0014】

【図1】本実施の形態に関連するPLLシンセサイザの構成図である。

【図2】第1の実施の形態におけるPLLシンセサイザの構成図である

【図3】電圧制御発振器VCOの概略構成図である。

【図4】電圧制御発振器VCOの周波数の制御について説明する図である。

【図5】本実施の形態における温度補償ループの構成と信号とを示す図である。

【図6】デジタルフィルタDFの回路例を示す図である。

【図7】ΔΣ変調器の回路例を示す図である。

【図8】チャージポンプCPtと温度補償ループフィルタTFの回路例を示す図である。

【図9】チャージポンプCPtと温度補償ループフィルタTFの別の回路例を示す図である。

【図10】温度補償ループフィルタTFの周波数特性を説明する図である。

【図11】温度補償ループフィルタについて説明する図である。

【図12】PLLシンセサイザが復帰するときの動作について説明する図である。

【図13】第2の実施の形態におけるPLLシンセサイザの温度補償ループの構成図である。

【図14】第2の実施の形態におけるPLLシンセサイザの温度補償ループのスリープ状態からの復帰動作を示す図である。

【発明を実施するための形態】

【0015】

図1は,本実施の形態に関連するPLLシンセサイザの構成図である。PLLシンセサイザは,出力クロックCKoutを分周器DIV1で分周したクロックCK2と,基準クロックR-CLKとの位相を比較する位相比較器PDと,位相比較器PDの位相比較結果dPHを電流値に変換するチャージポンプ回路CPmと,チャージポンプ回路CPmが生成する電流を積分し高周波成分をカットして周波数制御電圧Vtを生成するループフィルタLFと,周波数制御電圧Vtに応じて制御された周波数を持つ出力クロックCKoutを生成する電圧制御発振器VCOとを有する。

【0016】

電圧制御発振器VCOには,図示しないシステム側から制御コードCodeが供給され,制御コードCodeに対応して,周波数制御電圧Vtで制御される周波数範囲が選択される。このフィードバックループがPLLのメインループである。

【0017】

上記のメインループ(図中実線)に加えて,図中破線で示された温度補償ループが設けられる。温度補償ループでは,周波数制御電圧Vtと基準電圧V_refとを比較し,基準電圧に基づく所定の制御電圧範囲から外れたときにそれぞれ第1,第2のレベルを有する比較信号を出力する比較器CMPと,周波数制御電圧Vtと基準電圧V_refとの差分に応じた電流を出力するチャージポンプ回路CPtとを有する。この比較器CMPとチャージポンプ回路CPtとによりOTA(Operational Transconductance Amplifier)が構成される。

【0018】

そして,温度補償ループフィルタTFがその電流を積分すると共に高周波成分をカットして温度補償制御電圧ftを出力する。温度補償ループフィルタTFは,比較的大きな容量のキャパシタを有し,上記の電流の積分と高周波成分のカットに加えて,メインループより温度補償ループの時定数を大きくしている。

【0019】

メインループのPLLループフィルタLFと,温度補償ループの温度補償ループフィルタTFは,共に大容量のキャパシタを有するため,PLLシンセサイザ回路が形成されるチップ10内には設けられないことが多く,チップ外20に設けられる。

【0020】

図2は,第1の実施の形態におけるPLLシンセサイザの構成図である。PLLシンセサイザは,図1と同様に,出力クロックCKoutを分周器DIV1で分周したクロックCK2と,基準クロックR-CLKとの位相を比較する位相比較器PDと,位相比較結果dPHを電流値に変換するチャージポンプ回路CPmと,その電流を積分し高周波成分をカットして周波数制御電圧Vtを生成するPLLループフィルタLFと,周波数制御電圧Vtに応じて出力クロックCKoutの周波数を制御する電圧制御発振器VCOとを有する。

【0021】

電圧制御発振器VCOは,システム側から供給される制御コードCodeに対応して,周波数制御電圧Vtで制御される周波数範囲が選択される。そして,その周波数範囲内で周波数制御電圧Vtに応じて出力クロックCKoutの周波数が制御される。このフィードバックループがPLLのメインループである。

【0022】

第1の実施の形態のPLLシンセサイザも,図中破線で示された温度補償ループを有する。この温度補償ループは,周波数制御電圧Vtが制御電圧範囲から外れたときにそれぞれ第1,第2のレベルを有する比較信号30を出力する比較器と,第1の制御クロックR_CLKに同期して比較信号30を積分してMビットの第1のデジタル信号32を生成するデジタルフィルタDFと,第1のデジタル信号32を入力し,第1の制御クロックR_CLKより高周波の第2の制御クロックに同期して,Mビットより少ないNビットの第2のデジタル信号34であって第1のデジタル信号に対応する第2のデジタル信号34を生成するΔΣ変調器12,10と,第2のデジタル信号34を電流信号36に変換する温度補償チャージポンプCPtと,電流信号36により充放電されるキャパシタを有し,電流信号を温度補償制御電圧ftに変換する温度補償ループフィルタTFとを有する。そして,電圧制御発振器VCOは,温度補償制御電圧ftに基づいて出力クロックCKoutの周波数を制御する。

【0023】

このPLLシンセサイザでは,温度補償ループフィルタTFのキャパシタ容量を小さくできるので,PLLシンセサイザの回路と同じチップ内に設けられている。ただし,PLLループフィルタLFは,キャパシタ容量が大きいためチップ外に設けられている。

【0024】

図3は,電圧制御発振器VCOの概略構成図である。電圧制御発振器VCOは,例えばLC発振回路で構成され,LC発振回路内のキャパシタの容量が制御コードCode,制御電圧Vt,温度補償制御電圧ftにより変更される。それにより,発振周波数が制御される。図3の例では,LC発振器内のキャパシタは,周波数制御電圧Vtにより容量値が可変制御される第1のキャパシタC1と,温度補償制御電圧ftにより容量値が可変制御される第2のキャパシタC2と,制御コードCodeによりスイッチを介して接続または非接続される第3のキャパシタ群C3_1〜C3_nとを有する。第3のキャパシタ群の容量値は比較的大きいのに対して,第1,第2のキャパシタC1,C2の容量値はそれよりも比較的小さい。

【0025】

図4は,電圧制御発振器VCOの周波数の制御について説明する図である。図4(A)は,温度補償ループがない場合の電圧制御発振器VCOの周波数制御を示す。制御コードCode(図中001,010,011)に応じて,周波数f0の制御範囲が切り替えられる。そして,周波数制御電圧Vtに応じて,制御コードCodeで設定された周波数制御範囲内で周波数f0が可変制御される。

【0026】

図4(A)中に示されるとおり,電圧制御発振器VCOが周波数Aで発振しているときに,温度の上昇で周波数Bに変動して制御コード010の周波数制御範囲外になると,制御コードが010から011に切り替えられ,周波数制御範囲が1段階上にシフトする。その結果,同じ周波数制御電圧Vtでは周波数がCとなり大きく変更したことでロックオフする場合がある。この場合,PLLメインループにより周波数制御電圧Vtが変更され,周波数Dに制御され,再度ロックオンする制御が行われる。

【0027】

図4(B)は,温度補償ループによる周波数制御が加わった電圧制御発振器VCOの周波数制御を示す。図4(B)の左側は,図4(A)と同じであり,制御コードと周波数制御電圧Vtとによる周波数制御を示している。この図において周波数制御電圧Vtは図中Va,Vbの間で制御されることが望ましいとする。そして,図4(B)の右側は,ある周波数制御範囲内において温度補償制御電圧ftによる周波数制御を示している。周波数Aで発振しているときに,温度上昇が生じて周波数が上昇しようとした場合,温度補償ループによりその周波数制御電圧Vtの変動を検出し,温度補償制御電圧ftにより発振器VCOのキャパシタC2の容量値を可変制御し,温度上昇により周波数が上昇しないようにする。その結果,周波数制御電圧Vtの制御範囲がVa,Vb間の範囲から外れないようにされる。

【0028】

このように,図2の温度補償付きPLLシンセサイザでは,電圧制御発振器VCOが,制御コードCodeと周波数制御電圧Vtとに加えて,温度補償制御電圧ftによってもその周波数制御が行われる。一般に,メインのループに比較して,温度補償ループの時定数は大きく設定されている。それにより,メインループの周波数制御と温度補償ループによる周波数制御とが干渉して競合することが回避される。

【0029】

図5は,本実施の形態における温度補償ループの構成と信号とを示す図である。図5を参照しながら,温度補償ループを構成する各回路について説明する。

【0030】

比較器は,周波数制御電圧Vtを基準電圧Vref+とVref-と比較する2つの比較器CMP1,CMP2を有する。比較器の出力30は,図5中(2)に示されるとおり,周波数制御電圧Vtが高い基準電圧Vref+を超えると第1のレベル(例えば+1)になり,低い基準電圧Vref-を超えると第2のレベル(図中破線,例えば−1)になる。

【0031】

図6は,デジタルフィルタDFの回路例を示す図である。デジタルフィルタDFは一種の積分器であり,比較器の出力30を増幅する増幅器40と,加算器41と,遅延回路42と,増幅器43とを有する。遅延回路42が増幅された比較器出力30を例えば基準クロックR_CLKの1周期分だけ遅延させ,加算器41が新たな比較器出力30に加算することで,積分値が生成される。このデジタルフィルタDFの出力32は,例えばMビットのデジタル信号である。

【0032】

図5中(3)にデジタルフィルタの出力32の波形の例が示されている。比較器出力30の+1に対して,基準クロックR_CLKに同期した積分値がデジタルフィルタDFのMビット出力32として出力される。このように,デジタルフィルタ32が比較器出力30を積分することで,比較器出力30の変化に対する応答性を遅くすることができ,温度補償ループの時定数を大きくすることができる。すなわち,図1において,温度補償ループ内の温度フィルタTFが有していた応答を遅くする機能が,このデジタルフィルタ32により実現される。

【0033】

図7は,ΔΣ変調器の回路例を示す図である。本実施の形態の温度補償ループ内に設けられるΔΣ変調器10,12は,デジタルフィルタDFのMビット出力32を,デジタルフィルタのクロックR_CLKよりも高い周波数dCLKでアップサンプリングし,Mビットより少ないビット数のNビットの高周波デジタル信号34に変換する。高周波デジタル信号34は擬似ランダムデジタル信号であり,時間軸上で平均するとデジタル信号32の値と等しくなる。

【0034】

高周波デジタル信号に変換することで,後段の温度補償ループフィルタのカットオフ周波数を高く設定でき,キャパシタの容量値を小さくできる。また,擬似ランダムデジタル信号に変換することでノイズシェーピングされ,低周波帯域での量子化ノイズを小さくすることができる。

【0035】

図7にはΔΣ変調器の一例として2次のΔΣ変調器が示されている。この変調器は,Mビットデジタル信号32をクロックdCLKでサンプリングする入力レジスタ50と,加算器51と,その加算器の加算値X+YをクロックdCLKでラッチするレジスタ52とを有し,レジスタ52のラッチした値は加算器51にフィードバックされる。この構成により,加算器51のキャリ信号C(1ビット)が生成される。さらに,変調器は,レジスタ52がラッチした値を加算する加算器53と,加算器53の加算値X+YをクロックdCLKでラッチするレジスタ54とを有し,レジスタ54がラッチした値は加算器53にフィードバックされる。さらに,加算器53のキャリ信号Cは,レジスタ55と減算器56からなる微分回路57によりその微分値が求められ,加算器58が微分値と加算器51のキャリ信号Cとを加算し,Nビット(2ビット)のデジタル出力34を出力する。

【0036】

このデジタル出力34は,Mビットのデジタル入力32よりも高周波であり,且つMビットより少ないNビットの擬似ランダムなデジタル信号である。図5の(4)に示されるとおり,ΔΣ変調器は,デジタル入力信号32をより高い周波数で且つ少ないビットのデジタル信号34に変換する回路であり,図5の(4)では2ビット(4量子点)のデジタル信号に変換されている。デジタル出力信号34は,デジタル入力信号32よりも高い周波数で変化していることが示されている。つまり,高周波で且つ低ビットのデジタル出力信号34は,低周波で高いビットのデジタル入力信号32を,高い周波数で変調したものである。

【0037】

図7には,ΔΣ変調器のアップサンプリング用の高周波クロックdCLKが,PLLメインループ内の分周器DIV1により生成される例が示されている。VCOの出力クロックCKoutが,分周器DIV1内の2つの分周器46,47により分周される。この前段の分周器46が出力するクロックdCLKが,ΔΣ変調器のサンプリングクロックdCLKとして利用される。そして,このクロックdCLKは,デジタルフィルタDFの同期クロックR_CLKよりも高周波である。

【0038】

図8は,チャージポンプCPtと温度補償ループフィルタTFの回路例を示す図である。図8のチャージポンプCPtは,1ビット入力に対応した回路であり,電流源I1,I2とスイッチSW1,SW2とからなる。入力34が「1」の場合はスイッチSW1が導通して電流I1が供給され,入力34が「0」の場合はスイッチSW2が導通して電流I2が引き抜かれる。つまり入力が「1」で正電流が発生し,入力「0」で負電流が発生する。

【0039】

温度補償ループフィルタTFの最も簡単な構成は,上記の電流を蓄積する単一のキャパシタである。ただし,図8に示したループフィルタTFは,抵抗R10,R11とキャパシタC10,C11,C12からなる。図8中に示されるとおり,入力が「1」の場合,チャージポンプCPtは正電流を発生し出力電圧ftが上昇し,入力が「0」の場合,チャージポンプCPtは負電流を発生し出力電圧ftが下降する。ループフィルタTFは,一種のローパスフィルタであり,チャージポンプが生成する電流の高周波成分をカットする。したがって,キャパシタC10, C11, C12の合計容量値が小さいほど,カットオフ周波数が高くなる。

【0040】

図9は,チャージポンプCPtと温度補償ループフィルタTFの別の回路例を示す図である。図9のチャージポンプCPtは,2ビット入力に対応した回路である。入力34が「1」の場合にスイッチSW1が導通し,入力34が「2」の場合にスイッチSW1,SW3が導通し,入力34が「0」の場合にはどのスイッチも導通せず,入力34が「−1」の場合にスイッチSW2が導通する。

【0041】

それに伴い,チャージポンプCPtは,入力が「2」なら正電流2×I1,入力が「1」なら正電流I1,入力が「0」なら電流は発生せず,入力が「−1」なら負電流I1をそれぞれ出力する。

【0042】

そして,図9の温度補償ループフィルタTFは,1つのキャパシタで構成されている。もちろん,図8に示した温度補償ループフィルタTFであってもよい。この場合も,キャパシタの容量値が小さいほど,カットオフ周波数が高くなる。

【0043】

ΔΣ変調器10,12を採用したことによりデジタルフィルタDFのデジタル出力32が高周波のデジタル信号34に変換されるので,図8,図9に示した温度補償ループフィルタTFのカットオフ周波数を,従来のフィルタよりも高く設定することができる。つまりカットすべきデジタルフィルタDFのデジタル出力32の高周波成分は,ΔΣ変調器によるアップサンプリングにより,より高周波帯に移されている。その結果,温度補償ループフィルタTFのカットオフ周波数も高くすることができ,温度補償ループフィルタTFの容量値を小さくすることができる。このことは,PLLシンセサイザと同じチップ内にこの温度補償ループフィルタTFを設けることが容易になることを意味する。

【0044】

図10は,温度補償ループフィルタTFの周波数特性を説明する図である。実線が従来の温度補償ループフィルタの特性である。それに対して,破線が本実施の形態における温度補償ループフィルタTFの特性である。破線のほうがカットオフ周波数がより高くなっていることが理解できる。

【0045】

上記のように,第1の実施の形態によれば,比較器の比較信号をデジタルフィルタDFにより積分してMビットのデジタル出力信号32に変換したことで,温度補償フィルタの応答性を遅くし時定数を大きくすることができる。さらに,デジタルフィルタのMビットのデジタル出力信号32が,ΔΣ変調器によりアップサンプリングされN(<M)ビットのデジタル出力信号34に変換されている。これにより,より高周波のデジタル出力信号34に変換されたことで,アナログフィルタである温度補償ループフィルタTFのカットオフ周波数を高く設定することが可能になり,その分,温度補償ループフィルタTFのキャパシタの容量値を小さくして,チップ内面積を小さくすることができる。

【0046】

[第2の実施の形態]

温度補償ループフィルタTFの容量値を小さくしたことで,スリープモード中の充電電流を削減することができるとともに,スリープモードから復帰したときのPLLシンセサイザのロックオンまでの時間を短縮することができる。以下,この点について説明する。

【0047】

図11は,温度補償ループフィルタについて説明する図である。図11(A)には,図1に示した温度補償ループ内のOTAと温度補償ループフィルタTFと,電圧制御発振器VCOが示されている。OTAは,比較器CMPとチャージポンプCPtの組み合わせであり,温度補償ループフィルタTFは図8,図9に示したキャパシタを有する回路である。

【0048】

図11(B)に示すように,PLLシンセサイザが通信装置に内蔵された場合,通信タイムスロット間ではスリープモードに制御される。スリープモードではPLLシンセサイザの動作は停止し出力クロックの生成は停止する。一方で,ループフィルタTFは,キャパシタにある程度の電荷が蓄積されないと通常動作時の周波数制御電圧ftを出力することができない。そこで,プリチャージ回路60を設けて,スリープモード中もループフィルタTF内のキャパシタに電流を供給することが必要になる。

【0049】

図12は,PLLシンセサイザが復帰するときの動作について説明する図である。図12(A)は,起動時またはスリープモードからの復帰時の動作を示している。起動時または復帰時において,プリチャージ回路60からループフィルタTF内のキャパシタにプリチャージし(時間t1),その後,PLLシンセサイザのメインループ及び温度補償ループによる周波数制御が行われる(時間t2)。その場合,時間t1+t2がPLLのロックアップまでの制限時間TLimitを超える場合がある。

【0050】

そこで,図12(B)に示されるように,スリープモード中もプリチャージ回路60からプリチャージ電流を継続して供給することで,復帰後はPLLシンセサイザの周波数制御によるロックまでの時間t2だけが必要になり,ロックアップまでの制限時間TLimitまでにロック状態にすることが可能になる。ただし,この場合は,スリープモード中もプリチャージ電流を供給する必要があり,スリープモードの省電力化に反することになる。

【0051】

図13は,第2の実施の形態におけるPLLシンセサイザの温度補償ループの構成図である。この温度補償ループの構成は,図5の温度補償ループに加えて,スリープ状態に入るときのデジタルフィルタDFのデジタル出力32を記憶するメモリ62と,スリープ状態から復帰するときにメモリ62に記憶されているデジタル出力32の値に応じて温度補償ループフィルタTF内のキャパシタをプリチャージするプリチャージ回路60とを有する。

【0052】

すなわち,スリープ状態に移行する時は,温度補償ループフィルタTF内のキャパシタには,デジタルフィルタDFのMビットのデジタル出力32の値に応じた電荷が充電されている。そこで,スリープ状態に移行するときはメモリ62にそのデジタル出力32を記憶する。メモリ62は,スリープ状態でも記憶データが消失しない不揮発性メモリである。スリープ状態中はプリチャージ回路60からプリチャージ電流がループフィルタTFに供給されることはない。

【0053】

そして,スリープモードから復帰するときに,プリチャージ回路60は,メモリ62に記憶されているデジタル出力32を読み出し,そのデジタル出力値に応じた電圧までループフィルタTF内のキャパシタを充電する。ループフィルタTF内のキャパシタの容量値は小さく構成されているので,このプリチャージに要する時間は短い。

【0054】

図14は,第2の実施の形態におけるPLLシンセサイザの温度補償ループのスリープ状態からの復帰動作を示す図である。図13で説明したとおり,第2の実施の形態では,スリープ状態においては温度補償ループフィルタTFへのプリチャージ電流の供給は行わない。その代わり,スリープ状態から復帰する時に,プリチャージ回路60は,メモリ62に記憶しておいたデジタル出力値に応じた電荷量を温度補償ループフィルタTFのキャパシタの供給する。ただし,キャパシタの容量が小さいので,図14に示すとおり,プリチャージ時間t1は短くできる。

【0055】

その結果,この短いプリチャージ時間t1とその後のPLLによる周波数制御によるロックオンまでの時間t2の合計は,ロックオンまでの制限時間TLimit未満にすることが可能になる。

【0056】

以上の通り,第2の実施の形態によれば,スリープ期間中のプリチャージ電流の消費がなくなり,省電力化を図ることができる。

【符号の説明】

【0057】

PD:位相比較器 CPm:メインループのチャージポンプ

LF:PLLループフィルタ VCO:電圧制御発振器

Vt:周波数制御電圧 DIV1:分周器

CKout:出力クロック CMP:比較器

DF:デジタルフィルタ 10,12:ΔΣ変調器

CPt:温度補償ループのチャージポンプ

TF:温度補償ループフィルタ ft:温度補償制御電圧

【特許請求の範囲】

【請求項1】

出力クロックと基準クロックとの位相を比較する位相比較器と,

前記位相比較器の位相比較結果に応じて周波数制御電圧を生成するPLLループフィルタと,

前記周波数制御電圧に応じて制御された周波数を持つ前記出力クロックを生成する電圧制御発振器と,

前記周波数制御電圧が制御電圧範囲から外れたときにそれぞれ第1,第2のレベルを有する比較信号を出力する比較器と,

第1の制御クロックに同期して前記比較信号を積分してMビットの第1のデジタル信号を生成するデジタルフィルタと,

前記第1のデジタル信号を入力し,前記第1の制御クロックより高周波の第2の制御クロックに同期して,前記Mビットより少ないNビットの第2のデジタル信号であって前記第1のデジタル信号に対応する第2のデジタル信号を生成するΔΣ変調器と,

前記第2のデジタル信号を電流信号に変換する温度補償チャージポンプと,

前記電流信号により充放電されるキャパシタを有し,前記電流信号を温度補償制御電圧に変換する温度補償ループフィルタとを有し,

前記電圧制御発振器は前記温度補償制御電圧に基づいて前記出力クロックの周波数を制御するPLLシンセサイザ。

【請求項2】

請求項1において,

前記電圧制御発振器は,前記温度補償制御電圧に基づいて,前記出力クロックの周波数が所定の制御周波数範囲から外れることを抑制するPLLシンセサイザ。

【請求項3】

請求項1または2において,

さらに,スリープモードに移行するときに前記デジタルフィルタが生成する第1のデジタル信号を記憶するメモリと,

前記スリープモードから復帰するときに前記メモリに記憶されている第1のデジタル信号に対応する電荷量を前記温度補償ループフィルタ内のキャパシタに供給するプリチャージ回路とを有し,

前記プリチャージ回路は前記スリープモード中は前記温度補償ループフィルタ内のキャパシタへの電荷供給は行わないPLLシンセサイザ。

【請求項4】

請求項1〜3のいずれかにおいて,

前記PLLループフィルタを除いて同じチップ内に形成されているPLLシンセサイザ。

【請求項1】

出力クロックと基準クロックとの位相を比較する位相比較器と,

前記位相比較器の位相比較結果に応じて周波数制御電圧を生成するPLLループフィルタと,

前記周波数制御電圧に応じて制御された周波数を持つ前記出力クロックを生成する電圧制御発振器と,

前記周波数制御電圧が制御電圧範囲から外れたときにそれぞれ第1,第2のレベルを有する比較信号を出力する比較器と,

第1の制御クロックに同期して前記比較信号を積分してMビットの第1のデジタル信号を生成するデジタルフィルタと,

前記第1のデジタル信号を入力し,前記第1の制御クロックより高周波の第2の制御クロックに同期して,前記Mビットより少ないNビットの第2のデジタル信号であって前記第1のデジタル信号に対応する第2のデジタル信号を生成するΔΣ変調器と,

前記第2のデジタル信号を電流信号に変換する温度補償チャージポンプと,

前記電流信号により充放電されるキャパシタを有し,前記電流信号を温度補償制御電圧に変換する温度補償ループフィルタとを有し,

前記電圧制御発振器は前記温度補償制御電圧に基づいて前記出力クロックの周波数を制御するPLLシンセサイザ。

【請求項2】

請求項1において,

前記電圧制御発振器は,前記温度補償制御電圧に基づいて,前記出力クロックの周波数が所定の制御周波数範囲から外れることを抑制するPLLシンセサイザ。

【請求項3】

請求項1または2において,

さらに,スリープモードに移行するときに前記デジタルフィルタが生成する第1のデジタル信号を記憶するメモリと,

前記スリープモードから復帰するときに前記メモリに記憶されている第1のデジタル信号に対応する電荷量を前記温度補償ループフィルタ内のキャパシタに供給するプリチャージ回路とを有し,

前記プリチャージ回路は前記スリープモード中は前記温度補償ループフィルタ内のキャパシタへの電荷供給は行わないPLLシンセサイザ。

【請求項4】

請求項1〜3のいずれかにおいて,

前記PLLループフィルタを除いて同じチップ内に形成されているPLLシンセサイザ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2012−44545(P2012−44545A)

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【出願番号】特願2010−185363(P2010−185363)

【出願日】平成22年8月20日(2010.8.20)

【出願人】(000005223)富士通株式会社 (25,993)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【出願日】平成22年8月20日(2010.8.20)

【出願人】(000005223)富士通株式会社 (25,993)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]