PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、主として半導体集積回路として無線通信装置、無線測定器等で用いられるPLL(Phase-Locked Loop)周波数シンセサイザに関するものである。

【背景技術】

【0002】

近年、半導体の微細化、高速化に伴い、チャージポンプ回路を用いてアナログ電圧で出力周波数を制御するアナログPLL周波数シンセサイザに代わり、デジタル的に電圧制御発振器を制御するデジタルPLL周波数シンセサイザが検討されている(例えば、特許文献1,2、非特許文献1参照)。

【0003】

従来のデジタルPLL周波数シンセサイザの動作について、図を用いて説明する。図17は、従来のデジタルPLL周波数シンセサイザ100の構成を示すブロック図である。同図において、111は累積加算器、112は位相比較器、113はデジタルループフィルタ、114はゲイン調整器、115はデジタル制御発振器、121は正弦波デジタル変換器、116はカウンタ、117及び120はラッチ回路、118はデジタル位相検出器、119はリクロック回路である。

【0004】

デジタルPLL周波数シンセサイザ100には外部の基準水晶発振器からの基準信号FREFと、外部のレジスタ等からの周波数制御ワードFCWとが入力されている。累積加算器111では、基準信号FREFの1周期ごとに周波数制御ワードFCWを累積することによって、基準位相情報Rr[k]が得られる。ここで、[k]は累積加算器111を駆動するクロックの第k番目の遷移に対応して出力される信号を意味する。

【0005】

なお、周波数制御ワードFCWは、基準信号FREFの周波数とデジタル制御発振器115の出力信号の所望周波数との比である。すなわち、デジタル制御発振器115の出力信号の所望周波数をfosc、基準信号FREFの周波数をfrとすると、fosc=FCW×frと表される。また、一般的に、FCWは小数値を含み、foscはfrより高い周波数に設定される。

【0006】

デジタル制御発振器115の出力信号は、正弦波デジタル変換器121で、正弦波からデジタルクロック信号CKVに変換される。カウンタ116では、クロック信号CKVの立ち上がりエッジ(‘0’⇒‘1’のクロック遷移)の数がカウントされ、クロック信号CKVの立ち上がりエッジに同期して変化するカウント値Rv[i]が出力される。ここで、[i]はクロック信号CKVの第i番目の遷移に対応して出力される信号を意味する。ラッチ回路117では、このカウント値Rv[i]が基準信号FREFの1周期ごとにラッチされ、発振信号位相情報Rv[k]として出力される。

【0007】

更に、基準信号FREFとクロック信号CKVとの小さな(クロック信号CKVの周期以下の分解能の)位相差εをデジタル位相検出器118で検出し、基準信号FREFの1周期ごとにラッチ120で蓄積し、ε[k]として出力している。

【0008】

これらの位相情報Rr[k]、Rv[k]、ε[k]を位相比較器112において加減算することにより基準信号FREFとデジタル制御発振器115の出力であるクロック信号CKVとの位相誤差信号PHE[k]が得られる。位相誤差信号PHE[k]は、デジタルループフィルタ113によって高周波成分が取り除かれ、ゲイン調整器114を介して発振器のゲイン調整等の処理が行われた後、発振器115に帰還され、発振器115の周波数が制御される。

【0009】

図18は特許文献2や非特許文献1の図4.13等に開示されているデジタル位相検出器118のブロック図、図19は図18の時間デジタル変換器(TDC)401のブロック図、図20は図18に示したデジタル位相検出器118で位相差εが算出される仕組みを説明するためのタイミング図である。

【0010】

図19によれば、TDC401はL段(Lは2以上の自然数)の直列接続された遅延回路502と、各遅延回路502の出力を入力とするL個のラッチ回路504と、L個のラッチ出力Q(0)〜Q(L−1)を受け取るエッジ検出器とから構成される。

【0011】

図19に示すように、1段目の遅延回路502に発振器115の出力信号から生成されるクロック信号CKVを入力し、ラッチ回路504のクロックに基準信号FREFを用いることで、クロック信号CKVと基準信号FREFとの位相差に関連した情報をデジタル変換した値Q(0)〜Q(L−1)が、各ラッチ回路504より出力される。図19のエッジ検出器は、これらの値からクロック信号CKVの立ち上がりエッジの位相情報(図20のΔTr)とクロック信号CKVの立ち下がりエッジの位相情報(図20のΔTf)とを求めて、図18の正規化回路(NORM)402に出力する。正規化回路(NORM)402では、ΔTfとΔTrの値とをもとに、クロック信号CKVの1周期の時間で正規化された基準信号FREFの立ち上がりエッジとその直後のクロック信号CKVの立ち上がりエッジとの位相差として「ε」を算出する。具体的には、例えば図20(a)及び図20(b)に示すように、ΔTr≦ΔTfの場合にはε=1−ΔTr/2(ΔTf−ΔTr)として、ΔTr>ΔTfの場合にはε=1−ΔTr/2(ΔTr−ΔTf)としてそれぞれ算出される。なお、ΔTf、ΔTrの時間分解能は図19の遅延回路1段分の遅延時間の分解能であるため、位相差εも同じ時間分解能に規定される。

【0012】

一般的に、発振器115の出力信号から生成されるクロック信号CKVと基準信号FREFとは非同期であるため、クロック信号CKVの立ち上がりエッジに同期して変化するラッチ回路117の入力データRv[i]を基準信号FREFでそのままラッチしようとすると、いわゆるメタステーブル状態が発生する危険がある。例えば、図22(a)のように基準信号FREFとクロック信号CKVとの各々の立ち上がりエッジとが近接し、ラッチ回路117の所要のセットアップタイムやホールドタイム以下にΔTrが近づくと、メタステーブル状態が発生しクロック信号CKVの立ち上がりエッジで変化したデータを基準信号FREFで正しくラッチできない場合が生じる。

【0013】

そこで、特許文献1や非特許文献1ではこの危険を回避するため、図17に示すように、基準信号FREFをクロック信号CKVでラッチすることにより、クロック信号CKVに同期した基準信号FREFとほぼ同じ周期のクロック信号CKRをリクロック回路119で生成し、このリクロックされたクロック信号CKRでラッチ回路117、累積加算器111、ラッチ120を駆動するようにしている。

【0014】

図21はリクロック回路119の内部構成例であり、非特許文献1の図4.24にも同様の構成が記載されている。図21において、1190は選択部、1191〜1194はラッチ回路、QP,QN,QNPはラッチ回路1191,1192,1193の各々の出力信号である。

【0015】

上述したようにクロック信号CKRは基準信号FREFを発振器115の出力信号から生成されるクロック信号CKVでラッチすることにより生成されるが、クロック信号CKVの立ち上がりエッジか立ち下がりエッジかのどちらか一方のみで基準信号FREFをラッチしようとすると、リクロックする際にもメタステーブル状態が発生する危険性がある。例えば、基準信号FREFを常にクロック信号CKVの立ち上がりエッジでラッチしてリクロックしようとすると、図22(a)のように基準信号FREFとクロック信号CKVの各々の立ち上がりエッジとが近接し、ラッチ回路の所要のセットアップタイムやホールドタイム以下にΔTrが近づくと、メタステーブル状態が発生する危険が高まる。一方、基準信号FREFを常にクロック信号CKVの立ち下がりエッジでラッチしてリクロックしようとすると、図22(b)のように基準信号FREFの立ち上がりエッジとクロック信号CKVの立ち下がりエッジとが近接し、ラッチ回路の所要のセットアップタイムやホールドタイム以下にΔTfが近づくと、メタステーブル状態が発生する危険が高まる。

【0016】

これらの危険を回避し常に安定したリクロックを行うために、リクロック回路119では、図21に示すように基準信号FREFをクロック信号CKVの立ち上がりエッジ、立ち下がりエッジで各々ラッチするラッチ回路1191,1192を用意し、基準信号FREFとクロック信号CKVとの位相差εの値に応じてデジタル位相検出器118から出力された選択信号SEL_EDGEを用いて、メタステーブル状態になりにくい方のクロック信号CKVのエッジでラッチされた系統の信号を選択し、選択した信号CKを更にクロック信号CKVの立ち上がりエッジでラッチしてクロック信号CKRを生成させている。

【0017】

図23は、FCW=3.5と設定した場合を例に、PLLが所望の周波数に収束した状況における基準信号FREFとクロック信号CKVとのある位相関係時の位相誤差信号PHE[k]が出力されるまでの各信号の変化の様子を示したタイミング図である。

【0018】

図23において、まず、基準信号FREFの第n番目の立ち上がりエッジ付近の信号変化について説明する。基準信号FREFの第n番目の立ち上がりエッジとその直後のクロック信号CKVの立ち上がりエッジとの位相差(時間差)はクロック信号CKVのほぼ1周期近くあり、クロック信号CKVの1周期時間で正規化した位相差(時間差)ε≒1となる。この場合、基準信号FREFとクロック信号CKVとの立ち上がりエッジ同士が図のように近接しており、基準信号FREFの立ち上がりエッジとクロック信号CKVの立ち下がりエッジとの方が離れているので、図21のリクロック回路の選択部1190では信号QNP側が選択され、これを更にラッチ回路1194でラッチしてクロック信号CKRが生成される。そして、このクロック信号CKRの立ち上がりで、図17のカウンタ116の出力Rv[i]、累積加算器111の演算値、デジタル位相検出器118の出力εが各々ラッチされて、Rv[k]、Rr[k]、ε[k]が出力され、位相比較器112より位相誤差PHE[k](=Rr[k]−Rv[k]+ε[k])が出力される。

【0019】

上述したようにFCW=3.5という設定なので、所望の周波数に収束した状況においては、図23のように基準信号FREFの1周期内に約3.5周期分のCKVクロックが存在することになる。したがって、基準信号FREFの次の(第n+1番目の)立ち上がりエッジ付近では、ε≒0.5となる。この場合、基準信号FREFの立ち上がりエッジとクロック信号CKVの立ち下がりエッジとが近接し、基準信号FREFとクロック信号CKVの立ち上がりエッジ同士の方が離れた位相関係になるので、図21のリクロック回路の選択部1190では信号QP側が選択され、これを更にラッチ回路1194でラッチしてクロック信号CKRが生成される。そしてこのクロック信号CKRの立ち上がりで、図17のカウンタ116の出力Rv[i]、累積加算器111の演算値、デジタル位相検出器118の出力εが各々ラッチされて、Rv[k]、Rr[k]、ε[k]が出力され、位相比較器112より位相誤差PHE[k](=Rr[k]−Rv[k]+ε[k])が出力される。

【先行技術文献】

【特許文献】

【0020】

【特許文献1】米国特許第6326851号明細書

【特許文献2】特開2002−76886号公報

【特許文献3】特開2010−21686号公報

【特許文献4】特開2010−119077号公報

【非特許文献】

【0021】

【非特許文献1】R.B.STASZEWSKI and P.T.BALSARA,"ALL-DIGITAL FREQUENCY SYNTHESIZER IN DEEP-SUBMICRON CMOS", Chap.4, John Wiley and Sons,Inc, 2006

【発明の概要】

【発明が解決しようとする課題】

【0022】

上述したように、従来のデジタルPLL周波数シンセサイザ100では、基準信号FREFを発振器115の出力信号から生成されるクロック信号CKVの立ち上がりエッジと立ち下がりエッジとの両方でラッチして、基準信号FREFとクロック信号CKVとの位相差に応じてメタステーブル発生の危険の少ない側のラッチ信号を選択してクロック信号CKRを生成し、クロック信号CKRでラッチ回路117を含め各ブロックのラッチ回路を駆動することにより、クロック信号CKVと基準信号FREFとの非同期によるラッチ回路117におけるメタステーブル状態の発生の危険を回避している。しかしながら、リクロックを安定して行うためには、図21のように、基準信号FREFに比べて高速なクロック信号CKVで駆動する複数のラッチ回路1191〜1194を用いるリクロック回路119が必要となる。そのため、従来のデジタルPLL周波数シンセサイザ100には、ラッチ回路117のメタステーブル状態回避のために、消費電力が増大してしまうという問題がある。

【0023】

本発明は、かかる点に鑑みてなされたものであり、従来に比べて消費電力が少なく、かつ発振器の出力信号CKVと基準信号FREFとの非同期によるメタステーブル状態の発生の問題も回避できるデジタルPLL周波数シンセサイザを提供することを目的とする。

【課題を解決するための手段】

【0024】

上記課題を解決するため、本発明では次のような解決手段を講じた。すなわち、PLL周波数シンセサイザは、デジタル制御コードに応じた発振周波数の発振信号を出力するデジタル制御発振器と、発振信号の波数をカウントしてそのカウント値を出力するカウンタ部と、カウント値を基準信号の1周期毎にラッチしてその値を第1の発振信号位相情報として出力する第1のラッチ部と、第1のラッチ部の出力値を推定し、第2の発振信号位相情報として出力する発振信号位相情報推定部と、基準信号と発振信号との間の位相差値をデジタル値として出力するデジタル位相検出器と、位相差値を基準信号の1周期毎にラッチしてその値を位相差情報として出力する第2のラッチ部と、ロック検出信号に応じて第1の発振信号位相情報から第2の発振信号位相情報に出力信号を切り替える選択部と、選択部の出力を基準信号の1周期毎にラッチしてその値を第3の発振信号位相情報として出力する第3のラッチ部と、発振器の発振周波数を設定するための周波数制御ワードを基準信号の1周期毎に累積加算してその値を基準位相情報として出力する累積加算器と、基準位相情報と位相差情報と第3の発振信号位相情報とから位相誤差を算出して位相誤差信号を出力する位相比較器と、位相比較器の出力信号が与えられ、デジタル制御コードを出力する発振周波数制御部とを備えた構成を採る。

【0025】

これによると、PLL周波数シンセサイザは、通常状態(ロック状態)においてメタステーブル状態の発生の危険を抱えた第1のラッチ部の出力を使用しないため、従来のようなリクロック回路を使用せずとも出力信号と基準信号との非同期によるメタステーブル状態の発生の問題を回避できる。また、リクロックのための高速動作するラッチ回路も不要となるため、従来に比べて消費電力の低減も可能である。

【0026】

また、本発明のPLL周波数シンセサイザは、通常状態(ロック状態)においては、カウンタの出力を使用しないため、選択部が第2の発振信号位相情報を選択するモードに入った場合、カウンタ動作を停止させてもよい。

【0027】

これによると、PLL周波数シンセサイザは、通常状態(ロック状態)においては高速な発振信号クロックで駆動するカウンタ動作を停止させて、更に消費電力の低減ができる。

【0028】

あるいは、PLL周波数シンセサイザは、デジタル制御コードに応じた発振周波数の発振信号を出力するデジタル制御発振器と、発振信号の波数をカウントしてそのカウント値を出力するカウンタ部と、カウント値を第1のクロック信号を用いて基準信号の1周期毎にラッチし、その値を第1の発振信号位相情報として出力する第1のラッチ部と、基準信号と発振信号との間の位相差値をデジタル値として出力するデジタル位相検出器と、位相差値を基準信号の1周期毎にラッチしてその値を位相差情報として出力する第2のラッチ部と、カウント値を第2のクロック信号を用いてラッチし、そのラッチされた値を第1のクロックで基準信号の1周期毎にラッチした値を第2の発振信号位相情報として出力する第3のラッチ部と、位相差情報に応じて、第1の発振信号位相情報、第2の発振信号位相情報、第2の発振信号位相情報に所定値を加えた値のうちいずれかを選択してその値を第3の発振信号位相情報として出力する選択部と、発振器の発振周波数を設定するための周波数制御ワードを基準信号の1周期毎に累積加算してその値を基準位相情報として出力する累積加算器と、基準位相情報と位相差情報と第3の発振信号位相情報とから位相誤差を算出して位相誤差信号を出力する位相比較器と、位相比較器の出力信号が与えられ、デジタル制御コードを出力する発振周波数制御部とを備えた構成を採る。

【0029】

これによると、PLL周波数シンセサイザは、各々異なるクロックでカウント値をラッチする2つのラッチ回路を用いて、位相差情報に応じて、メタステーブル状態の発生の危険性の少ない側のラッチ出力を選択して用いるため、従来のようなリクロック回路を使用せずとも出力信号と基準信号との非同期によるメタステーブル状態の発生の問題を回避できる。また、リクロックのための高速動作するラッチ回路も不要となるため、従来に比べて消費電力の低減も可能である。

【発明の効果】

【0030】

本発明によれば、従来に比べて消費電力が少なく、かつ発振器の出力信号から生成されるクロック信号と基準信号との非同期によるメタステーブル状態の発生の問題も回避できるデジタルPLL周波数シンセサイザを提供することができる。

【図面の簡単な説明】

【0031】

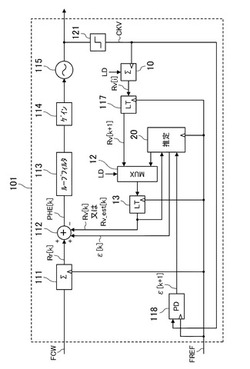

【図1】本発明の第1の実施の形態に係るデジタルPLL周波数シンセサイザの概略構成を示すブロック図である。

【図2】本発明の第1の実施の形態に係る発振信号位相情報推定部の概略構成を示すブロック図である。

【図3】本発明の第1の実施の形態に係る発振信号位相情報推定の原理を説明するためのタイミング図である。

【図4】本発明の第1の実施の形態に係るラッチ判定回路の概略構成を示すブロック図である。

【図5】図4のラッチ判定回路の動作を説明するためのフロー図である。

【図6】デジタルPLL周波数シンセサイザの比較例の構成を示すブロック図である。

【図7】本発明の第1の実施の形態等に係るデジタルPLL周波数シンセサイザの動作のシミュレーション結果を示す図である。

【図8】本発明の第1の実施の形態に係るデジタルPLL周波数シンセサイザの変形例を示すブロック図である。

【図9】本発明の第2の実施の形態に係るデジタルPLL周波数シンセサイザの概略構成を示すブロック図である。

【図10】図9中の発振信号位相情報選択部の概略構成を示すブロック図である。

【図11】本発明の第2の実施の形態に係る発振信号位相情報選択部の選択方法を説明するためのタイミング図である。

【図12】本発明の第2の実施の形態に係るデジタルPLL周波数シンセサイザの変形例を示すブロック図である。

【図13】図12中の発振信号位相情報選択部の概略構成を示すブロック図である。

【図14】本発明の第2の実施の形態に係る変形例の発振信号位相情報選択部の選択方法を説明するためのタイミング図である。

【図15】本発明の応用例に係る無線通信機器の概略構成を示すブロック図である。

【図16】図15の無線通信機器を搭載したテレビの斜視図である。

【図17】従来のデジタルPLL周波数シンセサイザの概略構成を示すブロック図である。

【図18】デジタル位相検出器の概略構成を示すブロック図である。

【図19】デジタル位相検出器に係る時間デジタル変換器(TDC)の概略構成を示すブロック図である。

【図20】(a)及び(b)はデジタル位相検出器で位相差εが算出される仕組みを説明するためのタイミング図である。

【図21】従来のデジタルPLL周波数シンセサイザで使用されるリクロック回路の概略構成を示すブロック図である。

【図22】(a)及び(b)は基準信号FREFと発振器出力から生成されるクロック信号CKVとの位相関係の一例を示すタイミング図である。

【図23】リクロック回路の動作を説明するためのタイミング図である。

【発明を実施するための形態】

【0032】

以下、本発明の実施の形態について図面を参照して詳細に説明する。なお、実施の形態において、従来と同一の構成要素には同一の符号を付し、その説明は背景技術の項で説明したことと重複するので極力省略する。

【0033】

《第1の実施の形態》

図1は、本発明の第1の実施の形態に係るデジタルPLL周波数シンセサイザの概略構成を示すブロック図である。図1において、デジタルPLL周波数シンセサイザ101は、従来のデジタルPLL周波数シンセサイザ100と同じく、累積加算器111、位相比較器112、デジタルループフィルタ113、ゲイン調整器114、デジタル制御発振器115、正弦波デジタル変換器121、ラッチ回路117、時間/デジタル変換器118を有するが、従来用いられてきたリクロック回路を有さない。また、デジタルPLL周波数シンセサイザ101は、イネーブル端子付のカウンタ10と、選択部12と、ラッチ回路13と、発振信号位相情報推定部20とを更に有する。

【0034】

図1に示すように、従来と異なりデジタルPLL周波数シンセサイザ101は、リクロックせずに基準信号FREFそのものを、累積加算器111と、ラッチ回路117,13と、発振信号位相情報推定部20との駆動クロックとして用いる。したがって、ラッチ回路117では、発振器115の出力信号から生成されるクロック信号CKVと基準信号FREFとの非同期によるメタステーブル状態が発生する危険が残る。そのため、メタステーブル状態が発生した場合には、ラッチ回路117は、誤った値を第1の発振信号位相情報として出力する可能性がある。ただし、メタステーブル状態は、図22(a)のように、クロック信号CKVの立ち上がりエッジと基準信号FREFの立ち上がりエッジとが近接し、その間の時間差ΔTrがラッチ回路117の所要のセットアップタイムやホールドタイム以下になる場合に生じるものである。一般的には、図22(a)のΔTrがラッチ回路のセットアップタイムやホールドタイム以下となるケースはそうならないケース、すなわちΔTrがラッチ回路のセットアップタイムやホールドタイムより大きいケースに比べて少ない。そのため、ラッチ回路117が誤った値を出力する頻度は、正しい値を出力する頻度に比べ一般的に低い。

【0035】

図2は、発振信号位相情報推定部20の構成例を示すブロック図である。図2において、201はラッチ回路、202,203,205は減算器、204は丸め回路、206は加算器である。図2の発振信号位相情報推定部20は、基準信号FREFの第k+1番目の遷移(立ち上がりエッジ)とその直後のクロック信号CKVの立ち上がりエッジとのクロック信号CKVの1周期時間で正規化した位相差(時間差)ε[k+1]と、基準信号FREFの1周期前の第k番目の位相差ε[k]との差(ε[k]−ε[k+1])を減算器202で算出し、その算出値から更にFCWの小数部の値FCWFを減算器203で減じた後、その値を丸め回路204で丸めて0又は1の値を減算器205に出力し、その入力値を減算器205でFCWの整数部の値FCWIから減じた後、その値をラッチ回路13の出力に加算器206にて加算した値Rv_est[k+1]を、基準信号FREFの第k+1番目の立ち上がりエッジでラッチ回路117にて正しくラッチした場合の値と推定し、その値を第2の発振信号位相情報として出力する。

【0036】

選択部12は、図示しない外部のロック検出器においてPLLが所定の安定状態(例えばPLLが所望の周波数に収束した状態)であるか否かを判定した結果として出力されるロック検出信号LDを利用して、PLLが安定状態となり所定時間経過するまでは、ラッチ回路117の出力すなわち第1の発振信号位相情報Rvを選択し、PLLが安定状態になって所定時間経過した場合には発振信号位相情報推定部20の出力すなわち第2の発振信号位相情報Rv_estを選択して、ラッチ回路13に出力する。そして、ラッチ回路13はその選択された信号をラッチして、位相比較器112と発振信号位相情報推定部20に出力する。したがって、基準信号FREFの第k+1番目の遷移においてラッチ回路13に選択信号Rv[k+1](又はRv_est[k+1])が入力された時点におけるラッチ回路13の出力は、それより基準信号FREFの1周期前のラッチ回路117(又は発振信号位相情報推定部20)の出力Rv[k](又はRv_est[k)である。

【0037】

図3は、上述のようにして基準信号FREFの第k+1番目の立ち上がりエッジでラッチ回路117を正しくラッチした場合のカウンタ値Rv[k+1]を推定できることを説明するために、FCW=2.5と設定した場合を例に、PLLが所望の周波数に収束した状況における基準信号FREFとクロック信号CKVとのある位相関係時の位相差εや発振信号位相情報RvやRv_est等の変化の様子を示したタイミング図である。

【0038】

図1のカウンタ10はクロック信号CKVの立ち上がりエッジで駆動されカウント値をアップさせる。したがって、基準信号FREFの1周期ごとのカウント値の増分はその基準信号FREFの1周期の区間内に存在するクロック信号CKVの立ち上がりエッジの数に相当する。PLLが所望の周波数に収束した状況においては基準信号FREFの1周期ごとの各区間におけるクロック信号CKVの立ち上がりエッジの数はFCWの整数部の値(FCWI)をNと表すと図3に示すようにNかN+1となる。上述のようにFCW=2.5と設定されているため、図3ではN=2である。

【0039】

図3において基準信号FREFの第m番目の立ち上がりエッジから第m+1番目の立ち上がりエッジまでの区間を区間mと表すことにする。また、区間mから区間m+4までのラッチ回路117の出力Rv[k+1]を各々A0,A1,A2,A3,A4と表す。区間mにおけるカウント値の増分N+1がラッチ回路117において第m+1番目の基準信号FREFの立ち上がりエッジでラッチされるため、第m+1番目の基準信号FREFの立ち上がり直後のラッチ回路117の出力A1はA0+N+1となる。同様にして、図3に示すように、第m+n番目(n=2,3,・・・)の基準信号FREFの立ち上がり直後のラッチ回路117の出力AnはAn−1+(区間m+n−1におけるカウント値の増分)となる。また、図1の選択部12がラッチ回路117の出力を選択している状態におけるラッチ回路13の出力Rv[k]は、ラッチ回路117とラッチ回路13とが同じ基準信号FREFで同期して駆動されているので、図3に示すようにラッチ回路117の出力を基準信号FREFの1周期遅らせたものになる。

【0040】

次に、PLLが収束した状態における基準信号FREFの立ち上がりエッジとその直後のクロック信号CKVの立ち上がりエッジとの位相差εの変動とFCWとの関係について説明する。なお、図3に示すように、基準信号FREFの立ち上がりエッジとその直前のクロック信号CKVの立ち上がりエッジとの時間差をΔTr、クロック信号CKVの1周期の時間をTvとし、基準信号FREFの立ち上がりエッジとその直後のクロック信号CKVの立ち上がりエッジとの位相差εを(Tv−ΔTr)/Tvと定義する。また、FCWの整数部をFCWI、小数部をFCWFと表す。図3の例ではFCW=2.5としているので、FCWI=2、FCWF=0.5である。

【0041】

PLLが所望の周波数に収束した状態においては、基準信号FREFの1周期あたりにほぼFCW個のクロック信号CKVが存在する。したがってFCW=2.5とした場合、ほぼ2.5個のクロック信号CKVが存在するので、図3に示すように、第m番目の基準信号FREFの立ち上がりエッジに対応した位相差ε[m+1]が約0.3だった場合、次の第m+1番目の基準信号FREFの立ち上がりエッジに対応した位相差ε[m+2]は、前回の位相差からほぼFCWF(=0.5)分だけ位相差が変化し、約0.8となる。

【0042】

図3で具体例を示した位相差εの変化とFCWFとの関係を一般式で表すと、

ε[k+1]≒mod(ε[k]−FCWF,1) …(1)

と表される。ここで、mod(A,1)はモジュロ演算(Aを1で割った余り)を意味する。例えば、A=0.3ならmod(A,1)=0.3、A=−0.2ならmod(A,1)=1−0.2=0.8である。よって、ε[k+1]は、

ε[k+1]≒ε[k]−FCWF(ε[k]−FCWF≧0の時) …(2)

ε[k+1]≒1+(ε[k]−FCWF)(ε[k]−FCWF<0の時)…(3)

と表される。

【0043】

図2のラッチ回路201の入力ε[k+1]を出力ε[k]から差し引いた値をΔε[k]とすると、式(1)より、

Δε[k]=ε[k]−ε[k+1]

≒ε[k]−mod(ε[k]−FCWF,1) …(4)

と表される。

【0044】

次に、カウンタ10のカウント値の増分(すなわち、基準信号FREFの1区間内に入るクロック信号CKVの立ち上がりエッジの数)と、εの変動との関係について説明する。

【0045】

図3の第m番目と第m+1番目との基準信号FREFの立ち上がりエッジにおける位相差εの値の変動(約0.3⇒約0.8)と、区間mにおけるカウンタ10のカウント値の増分との関係を見ればわかるように、基準信号FREFのある区間kにおけるカウンタ10のカウント値の増分がFCWI+1となる場合、Δεは負の値を示す。これは言い換えると、Δεの式(4)において、モジュロ演算値がε[k]より大きくなることを意味する。したがって、カウンタ10のカウント値の増分がFCWI+1となる場合、ε[k]−FCWF<0なので、式(3)から、式(4)は、

Δε[k]≒ε[k]−{1+(ε[k]−FCWF)} …(5)

と表される。

【0046】

一方、図3の第m+1番目と第m+2番目との基準信号FREFの立ち上がりエッジにおける位相差εの値の変動(約0.8 ⇒ 約0.3)と、区間m+1におけるカウンタ10のカウント値の増分との関係を見ればわかるように、基準信号FREFのある区間kにおけるカウンタ10のカウント値の増分がFCWIとなる場合、Δεは0以上の値を示す。これは言い換えると、Δεの式(4)において、モジュロ演算値がε[k]以下であることを意味する。したがって、カウンタ10のカウント値の増分がFCWIとなる場合、式(2)から、式(4)は、

Δε[k]≒ε[k]−(ε[k]−FCWF) …(6)

と表される。

【0047】

したがって、キャリーC(C=0又は1)を用いて、第k+1番目の基準信号FREFの立ち上がりエッジでラッチされるラッチ回路117の正しいカウント値Rv[k+1]を、

Rv[k+1]=Rv[k]+FCWI+C …(7)

と表すと、C=1の時、式(5)より、

Δε[k]−FCWF≒−1 …(8)

C=0の時、式(6)より、

Δε[k]−FCWF≒0 …(9)

と表される。

【0048】

式(8)より、C=1の時は、Δε[k]−FCWFを丸めた値Round(Δε[k]−FCWF)が−1となる。また、式(9)より、C=0の時は、Δε[k]−FCWFを丸めた値Round(Δε[k]−FCWF)が0となる。したがって、キャリーCの値は、常に、

C=−Round(Δε[k]−FCWF) …(10)

と表される。よって、式(7)、式(10)より、

Rv[k+1]=Rv[k]+FCWI−Round(Δε[k]−FCWF)

…(11)

という関係が成立する。

【0049】

本発明の第1の実施の形態に係るデジタルPLL周波数シンセサイザは、ラッチ回路117の前回の出力値Rv[k]が正しければ、今回の出力値Rv[k+1]の正しい値と、前回の出力値Rv[k]と、前回と今回との位相差の変動Δε[k]と、FCWとの間に上述した式(11)の関係が成立することを導き出し、図1、図2に示したラッチ回路117と、選択部12と、ラッチ回路13と、発振信号位相情報推定部20とを用いて、式(11)によりラッチ回路117の正しくラッチされた時のカウント値を推定する機能を付加したものである。

【0050】

なお、本実施の形態では、式(7)のキャリーCの値に応じて、ΔεとFCWFとの間に式(8)又は式(9)の関係が成立することから、式(10)のように、丸めを用いてΔεとFCWFでキャリーCを決定した。すなわち、Δε[k]−FCWF≦−0.5ならばC=1、Δε[k]−FCWF>−0.5ならばC=0というように式(7)のキャリーCを決定したが、キャリーCの決定方法はもちろんこれに限らない。例えば、基本的なΔεの変動量(以下、Δεの基準値)はFCWFであるが、図18のTDC401の時間分解能やデジタル制御発振器115自体の位相雑音特性等から推測されるΔεの基準値からの誤差がE(E>0)とすると、すなわち、FCWF−E<Δε<FCWF+Eと想定できる場合には、Δε[k]−FCWF≧−EならばC=0、それ以外の場合はC=1とする等、比較回路を用いて、Δε[k]−FCWFを所定値と比較して、キャリーCを決定することができる。

【0051】

前述したように、ラッチ回路117には、発振器115の出力信号から生成されるクロック信号CKVと基準信号FREFとの非同期によるメタステーブル状態が発生する危険が残るため、ラッチ回路117の前回の出力値Rv[k]が常に正しい値であるとは限らない。そのため、前回の出力値Rv[k]が誤りだった場合、それを用いた推定値も当然誤りとなり、発振信号位相情報推定部20は誤った推定値を出力してしまうことになる。しかしながら、これも前述したように、メタステーブル状態は、図22(a)のように、クロック信号CKVの立ち上がりエッジと基準信号FREFの立ち上がりエッジとが近接し、その間の時間差ΔTrがラッチ回路117の所要のセットアップタイムやホールドタイム以下になる場合に生じるものである。ラッチ回路の性能にもよるが、一般的には、図22(a)のΔTrがラッチ回路のセットアップタイムやホールドタイム以下となるケースは、そうならないケース、すなわちΔTrがラッチ回路のセットアップタイムやホールドタイムより大きいケースに比べて少ない。そのため、ラッチ回路117が誤った値を出力する頻度は、正しい値を出力する頻度に比べ一般的に低い。少なくとも、ラッチ回路117は、常に誤った出力値を出すことはなく、あるタイミングでは必ず正しい値を出力する。

【0052】

一度、ラッチ回路117の正しい出力値Rv[k]から式(11)より、今回のラッチ回路117の正しい出力値を推定して、正しい推定結果Rv_est[k+1]を生成して、その推定結果を、次回の第k+2番目の基準信号FREFの遷移におけるラッチ回路117の出力値Rv[k+1]に代えて使用するようにすることにより、第k番目の基準信号FREFの遷移以降は常に正しい発振信号位相情報を位相比較器112に出力できる。

【0053】

そこで、本発明の第1の実施の形態に係るデジタルPLL周波数シンセサイザは、前回の出力値Rv[k]が正しいかどうかの判定を、ロック検出信号LDを用いて行う。

【0054】

ラッチ回路117の出力Rv[k]が誤った値であり、その値が選択部12で選択されている場合、発振信号位相情報を位相比較器112に出力してしまうので、所望の周波数精度の仕様にもよるが、ある程度所望の周波数精度が厳しければ、PLLは所望の周波数精度に収束しないと考えられる。それ故、ロック検出の条件としては、例えば、発振周波数が所望の周波数精度に所定時間以上収束していることを条件とすればよい。そして上記条件が満たされている場合にロック検出信号LDを図示しないロック検出部から出力(LDの値を1から0に変更)し、選択部12はロック検出信号LDが入力された(LD値が0となった)直後(又はLD値が0の期間が所定時間継続した後)、ラッチ回路13に出力する信号をラッチ回路117の出力信号から発振信号位相情報推定部20の出力信号に切り替えればよい。

【0055】

このようにして、本発明のデジタルPLL周波数シンセサイザは、通常状態(ロック状態)においてメタステーブル状態の発生の危険を抱えたラッチ回路117の出力を使用しないため、従来のようなリクロック回路を使用せずとも出力信号CKVと基準信号FREFとの非同期によるメタステーブル状態の発生の問題を回避できる。また、リクロックのための高速動作するラッチ回路も不要となるため、従来に比べて消費電力の低減も可能である。

【0056】

また、選択部12がその出力信号をラッチ回路117の出力信号から発振信号位相情報推定部20の出力信号に切り替えた後は、それまで使用してきたカウンタ10は不要となるので、ロック検出信号LDあるいはそれに関連した信号をカウンタ10のイネーブル信号として用いて、選択部12の出力信号の切り替えタイミングに応じて、カウンタ動作を停止させてもよい。

【0057】

このように、高速なクロック信号CKVで動作するカウンタ10を停止させることにより、従来のデジタルPLL周波数シンセサイザに比べて、更に消費電力の低減が可能となる。

【0058】

また、上述の説明では、ロック検出の条件を、発振周波数が所望の周波数精度に所定時間以上収束していることとし、この条件を選択部12における信号切り替え条件として用いたが、選択部12における信号切り替えに使用するロック検出の条件はこれに限らず、例えば、ラッチ回路117の出力Rvの変動が所定の範囲内に所定時間以上収束していることとしてもよい。例えば、図3等を用いて説明したようにPLLが所望の発振周波数精度に収束した状態において、Rvの変動(ラッチ回路117の出力値の増分)は、FCWIかFCWI+1かのどちらかの値を取る。つまり、キャリーCは0又は1である。そのため、これらの値以外のRvの変動があった場合、前回又は今回の少なくともどちらか一方の出力Rvの値は誤りであると判断できる。逆にRvの変動がFCWIかFCWI+1かのどちらかであれば、前回の出力Rvの値は正しい可能性が高い。そこで、例えば、ラッチ回路117の出力Rvの変動がFCWIかFCWI+1かのどちらかである区間が所定時間(例えば、基準信号FREFの128周期)継続した場合に、ロック検出信号LDを図示しないロック検出部から出力(例えばLDの値を1から0に変更)するようにしてもよい。

【0059】

あるいはまた、ロック検出の条件を、例えば、ラッチ回路117の出力Rv[k+1]と発振信号位相情報推定部20の出力Rv_est[k+1]とを比較して値が一致した場合(あるいは一致状態が、所定時間継続した場合)に、ロック検出信号LDを図示しないロック検出部から出力(例えばLDの値を1から0に変更)するようにしてもよい。

【0060】

PLL周波数シンセサイザの所望の周波数精度の仕様が甘い場合には、ラッチ回路117の出力Rvが誤っていても所望の周波数精度を満足してしまうことがある。したがって、このようにPLL周波数シンセサイザの所望の周波数精度の仕様が甘い場合には、上述した例のように、ラッチ回路117の出力Rvの値をロック検出条件として用いることが望ましい。

【0061】

なお、上述した例のように、ラッチ回路117の出力Rvの値をロック検出条件として用いた場合には、選択部12の出力信号の切り替えタイミングに応じて、常時カウンタ10を停止してしまうと、何らかの突発的な外乱ノイズ等でPLLの発振周波数が所望値から外れてしまった場合でもロック検出信号LDが出力されたままになってしまう。

【0062】

そのため、ラッチ回路117の出力Rvの値をロック検出条件として用いる場合には、選択部12の出力信号の切り替えタイミングに応じて、カウンタ10を停止させた後、カウンタ10を間欠的に動作させ、PLLの収束状態を確認するようにすればよい。

【0063】

あるいは、上述のように、ラッチ回路117の出力Rvの値を用いたロック検出条件を第1のロック検出条件とし、発振周波数が所望の周波数精度に所定時間以上収束していることを第2のロック検出の条件とし、これら2つのロック検出条件を同時に満たす場合のみロック検出信号LDを選択部12やカウンタ10に出力(例えばLDの値を1から0に変更)するようにして、ロック検出信号LDがロック状態(値0)を示している間はカウンタ10を常時停止するようにしてもよい。

【0064】

例えば、図4のように、ラッチ回路117の出力Rv[k+1]をラッチ回路117と同じく基準信号FREFでラッチしてRv[k]を生成し、Rv[k+1]とRv[k]との差に位相情報推定部20内の丸め回路204の出力を加えた信号ΔRvを生成し、ΔRvとFCWIとの差を示す信号Rv_NGを出力するラッチ判定回路220を設け、図5のフローに従って、選択部12における信号切り替えに使用するロック検出信号LDを切り替えてもよい。

【0065】

第k番目とk+1番目の基準信号FREFの立ち上がりエッジにおけるラッチ回路117の出力Rv[k]、Rv[k+1]が正常な値である場合、式(11)より、

Rv[k+1]−Rv[k]+Round(Δε[k]−FCWF)=FCWI

…(12)

という関係が成立する。したがって、ラッチ判定回路220の出力Rv_NGが0ならば、発振信号位相情報推定部20で推定に使用されたRv[k]の値は正しく、推定値Rv_est[k+1]も正しい値となる。

【0066】

そこで、Rv_NGが0であることを第1のロック検出条件として、図5のフローに示すように、まず初期状態として、第1のロック検出信号LDを1とし(S1)、Rv_NGが0か否かを判定し(S2)、0ならばLDを1から0として選択部12の出力をラッチ回路117側から発振信号位相情報推定部20側に切り替える(S3)。それにあわせてカウンタ10の動作を停止させる。そして、通常良く用いられるロック条件(例えば、発振周波数が所望の周波数精度に所定時間以上収束していること)を第2のロック検出条件として、第2のロック検出条件に対応する第2のロック検出信号NLDがロック状態からロック外れの状態に切り替わった否かを常時判定し(S4)、第2のロック検出条件が外れた場合、第1のロック検出信号LDを1(S1)として、カウンタ10の動作を再開させ、Rv_NGが0か否かの判定をRv_NGが0になるまで繰り返す(S2)。

【0067】

このように、ロック検出条件に関しては、様々なバリエーションが適用可能である。一例として、ラッチ回路117の出力Rvの変動がFCWIかFCWI+1かのどちらかである区間が所定時間(基準信号FREFの128周期)継続した場合に、ロック検出信号LDを出力するようにした場合のデジタルPLL周波数シンセサイザ101の動作のシミュレーション結果(位相雑音特性)を、図7に示す(図7の(3))。なお、図7には比較のために、従来のデジタルPLL周波数シンセサイザ100の動作のシミュレーション結果(図7の(1))と、図6に示したデジタルPLL周波数シンセサイザ99のように、従来のリクロック回路119や本実施の形態の発振信号位相情報推定部20を設けずに、単純にラッチ回路117を基準信号FREFで駆動させた場合の動作のシミュレーション結果結果(図7の(2))を併せて示している。また、図7のシミュレーション結果(2)(3)では、ラッチ回路117におけるメタステーブル状態の発生による出力Rvの値の誤りを、位相差εが0.01以下か0.99以上の場合に1/2の確率でRvの正しい出力値から1小さい値を出力するようにして、擬似的に付加させている。単純にラッチ回路117を基準信号FREFで駆動させた場合(図7の(2))には、メタステーブル状態による誤差発生により位相雑音特性が大幅に劣化してしまうが、本実施の形態のデジタルPLL周波数シンセサイザ101では、ラッチ回路117でメタステーブル状態による誤差が時々生じたとしても、問題なく従来のリクロック回路119を用いたデジタルPLL周波数シンセサイザ100と同等の位相雑音特性を示す。

【0068】

なお、上述した第1の実施形態のデジタルPLL周波数シンセサイザ101では、デジタル位相検出器118の出力信号である位相差εをラッチする回路は、発振信号位相情報推定部20内のラッチ回路201(図17における従来のラッチ回路120に相当)のみであるが、ラッチ回路の段数はこれに限らず、位相比較器112に入力される位相差εと発振信号位相情報Rv(又はRv_est)とのタイミング関係が図3と同様に取れていればよい。

【0069】

例えば、図8のデジタルPLL周波数シンセサイザ1012におけるラッチ回路202,203のように、図1のデジタル位相検出器118−発振信号位相情報推定部20間のパスと、ラッチ回路117−選択部12間のパスとに、複数のラッチ回路を同じ数だけ挿入してもよい。

【0070】

《第2の実施の形態》

図9は、本発明の第2の実施の形態に係るデジタルPLL周波数シンセサイザ102の概略構成を示すブロック図である。図9において、デジタルPLL周波数シンセサイザ102は、第1の実施の形態のデジタルPLL周波数シンセサイザ101と同じく、従来用いられてきたリクロック回路を有さない。また、第1の実施の形態のデジタルPLL周波数シンセサイザ101のイネーブル端子付のカウンタ10に代えて従来と同じカウンタ116を用いる。また、第1の実施の形態のデジタルPLL周波数シンセサイザ101の選択部12と、ラッチ回路13と、発振信号位相情報推定部20とに代えて発振信号位相情報選択部70を有する。

【0071】

図10は、発振信号位相情報選択部70の構成例を示すブロック図である。図10に示すように発振信号位相情報選択部70は、カウンタ116から出力された発振信号位相情報Rv[i]を発振器115の出力信号から生成されるクロック信号CKVの立ち下がりエッジでラッチするラッチ回路801と、基準信号FREFで入力信号をラッチする複数のラッチ回路802〜807と、加算器81と、選択部80とを有する。

【0072】

発振信号位相情報選択部70は、ラッチ回路801の出力Rv_i[i]をラッチ回路802とラッチ回路804とにより基準信号FREFで2回ラッチした後、ラッチ回路804の出力Rv2を加算器81と選択部80とに入力する。加算器81はRv2に1を加えた値Rv3を選択部80に出力する。また、一方、発振信号位相情報Rv[i]をラッチ回路803とラッチ回路805とにより基準信号FREFで2回ラッチした後、ラッチ回路805の出力Rv1を選択部80に入力する。ここで、ラッチ回路802の出力をRv[k+2]aとし、ラッチ回路803の出力をRv[k+2]bとする。

【0073】

従来の課題でも述べたように、クロック信号CKVと基準信号FREFとは非同期であるため、ラッチ回路802及びラッチ回路803においては、メタステーブル状態が発生する危険があり、発生した場合には誤った値を出力してしまう場合がある。ただし、ラッチ回路802に入力されるデータの変化はラッチ回路803に入力されるデータの変化よりクロック信号CKVの半周期分遅れるため、ラッチ回路802とラッチ回路803とが同時にメタステーブル状態になることは通常ない。そこで、選択部80は、クロック信号CKVと基準信号FREFとの位相差ε[k+1]の値に応じて、メタステーブル状態の発生の危険が低い入力データをRv1、Rv2、Rv3のうちから選択して発振信号位相情報Rv[k+1]をラッチ回路806に出力する。ラッチ回路806は基準信号FREFで発振信号位相情報Rv[k+1]をラッチして発振信号位相情報Rv[k]を出力する。

【0074】

図11は、上述のように発振信号位相情報選択部70において位相差εに応じてRv1、Rv2、Rv3のうちから選択することにより、常に正しい発振信号位相情報Rv[k+1]を生成できることを説明するための図である。

【0075】

図11の基準信号FREF(ケース1)のように、クロック信号CKVと基準信号FREFとの立ち上がりエッジの間隔がラッチ回路のセットアップタイムやホールドタイムの規定を十分満たす程度に離れている場合には、ラッチ回路803ではメタステーブル状態が発生する危険はなく、選択部80は入力Rv1、Rv2、Rv3のうちRv1を選択すれば正しい発振信号位相情報Rv[k+1]を出力できる。

【0076】

また、図11の基準信号FREF(ケース2)や基準信号FREF(ケース3)のように、クロック信号CKVと基準信号FREFとの立ち上がりエッジの間隔がラッチ回路のセットアップタイムやホールドタイムの規定を満たせない程近接している場合には、クロック信号CKVの立ち上がりエッジで変化するデータRv[i]を所定の時間ΔT(ここではクロック信号CKVの半周期分)遅延させた入力データをラッチするラッチ回路802ではメタステーブル状態が発生する危険はない。ただし、図11の基準信号FREF(ケース2)のように、位相差εがΔTをクロック信号CKVの1周期の時間で割って正規化した値より大きい場合には、データを遅延させたことにより本来ラッチされるべき値Rv[i]ではなく1少ない値がラッチされることになる。したがって、図11の基準信号FREF(ケース2)のような場合は、選択部80は入力Rv1、Rv2、Rv3のうちRv2に1を加えた値、すなわちRv3を選択すれば正しい発振信号位相情報Rv[k+1]を出力できる。また、図11の基準信号FREF(ケース3)のように、位相差εがΔTをクロック信号CKVの1周期の時間で割って正規化した値より小さい場合には、遅延させたデータをラッチしても本来ラッチされるべき値Rv[i]がラッチされることになる。図11の基準信号FREF(ケース3)のような場合は、選択部80は入力Rv1、Rv2、Rv3のうちRv2を選択すれば正しい発振信号位相情報Rv[k+1]を出力できる。

【0077】

例えば、本実施の形態のようにΔTをクロック信号CKVの半周期とした場合、0≦ε<0.25ならばRv2を選択、0.25≦ε<0.75ならばRv1を選択、0.75≦ε<1ならばRv3を選択とすれば、ラッチ回路のセットアップタイムやホールドタイムの規定値を最大限に緩めることができる。

【0078】

なお、選択部80のεの値に応じた発振信号位相情報(Rv1、Rv2、Rv3)の選択は、上記値に限るものではなく、ラッチ回路のセットアップタイムやホールドタイムの規定値を満足する限り柔軟に定めることができる。

【0079】

また、本実施の形態では、発振信号位相情報Rv[i]の遅延時間ΔTをクロック信号CKVの半周期として、発振信号位相情報Rv[i]をクロック信号CKVの立ち下がりエッジでラッチすることにより半周期分遅延させたが、遅延時間ΔTはこれに限るものではない。例えば、ラッチ回路のセットアップタイムやホールドタイムの規定値がクロック信号CKVの1周期の時間Tvの1/10だとすると、ΔTをTvの2/10より大きい値、例えばTvの3/10程度の時間となるように遅延回路を用いてクロック信号CKVを遅延させたクロックでラッチ回路801をラッチすればよい。また、その場合、選択部80のεの値に応じた発振信号位相情報(Rv1、Rv2、Rv3)の選択は、0≦ε<閾値1ならばRv2を選択、閾値1≦ε<閾値2ならばRv1を選択、閾値2≦ε<1ならばRv3を選択とした場合に、閾値1を0.1より大きく0.2未満の値(例えば0.15)、閾値2を0.8より大きく0.9未満の値(例えば0.85)とすればよい。

【0080】

このように、本発明の実施の形態においては、基準信号FREFに比べ高速なクロック信号CKVで駆動するラッチ回路を多数必要とする従来のリクロック回路119に代えて、低速な基準信号FREFで駆動するラッチ回路を複数用いた発振信号位相情報選択部70を用いて、メタステーブル状態の発生による発振信号位相情報Rv[k]の誤り発生を回避でき、かつ、従来に比べリクロックのための高速動作するラッチ回路の数も少なくできるので、従来に比べて消費電力の低減も可能である。

【0081】

《変形例》

図12は、本発明の第2の実施の形態に係るデジタルPLL周波数シンセサイザ102の変形例を示すブロック図である。図10の発振信号位相情報選択部70では、発振信号位相情報Rv[i]を遅延させたデータRv_i[i]を生成するラッチ回路801と、従来どおりに発振信号位相情報Rv[i]をラッチするラッチ回路803とを用いて、位相差情報に応じて、メタステーブル状態の発生の危険性の少ない側のラッチ出力を選択するものとしたが、図13に示す発振信号位相情報選択部180のように、発振信号位相情報Rv[i]を遅延させるのではなく、バッファ84等により基準信号FREFを所定時間ΔTだけ遅延させたクロック信号FREF_dで駆動するラッチ回路801を設けて、ラッチ回路801から出力されたデータから生成される発振信号位相情報Rv2,Rv3と、従来どおりに基準信号FREFで発振信号位相情報Rv[i]をラッチするラッチ回路803から出力されたデータから生成される発振信号位相情報Rv1とを、位相差情報ε[k+1]に応じて、メタステーブル状態の発生の危険性の少ない側のラッチ出力を選択するものとしてもよい。

【0082】

図14は、上述のように発振信号位相情報選択部180において位相差εに応じてRv1,Rv2,Rv3のうちから選択することにより、常に正しい発振信号位相情報Rv[k+1]を出力できることを説明するための図である。

【0083】

図14の基準信号FREF(ケース1)のように、クロック信号CKVと基準信号FREFとの立ち上がりエッジの間隔がラッチ回路のセットアップタイムやホールドタイムの規定を十分満たす程度に離れている場合には、ラッチ回路803ではメタステーブル状態が発生する危険はなく、選択部80は入力Rv1、Rv2、Rv3のうちRv1を選択すれば正しい発振信号位相情報Rv[k+1]を出力できる。

【0084】

また、図14の基準信号FREF(ケース2)や基準信号FREF(ケース3)のように、クロック信号CKVと基準信号FREFとの立ち上がりエッジの間隔がラッチ回路のセットアップタイムやホールドタイムの規定を満たせない程近接している場合には、基準信号FREFを所定の時間ΔT(ここではクロック信号CKVの半周期分)遅延させたクロック信号FREF_dでラッチするラッチ回路801ではメタステーブル状態が発生する危険はない。ただし、図14の基準信号FREF(ケース3)のように、位相差εがΔTをクロック信号CKVの1周期の時間で割って正規化した値より小さい場合には、駆動クロックを遅延させたことにより本来ラッチされるべき値Rv[i]ではなく1大きい値がラッチされることになる。したがって、図14の基準信号FREF(ケース3)のような場合は、選択部80は入力Rv1、Rv2、Rv3のうちRv2から減算器83にて1を減じた値、すなわちRv3を選択すれば正しい発振信号位相情報Rv[k+1]を出力できる。また、図14の基準信号FREF(ケース2)のように、位相差εがΔTをクロック信号CKVの1周期の時間で割って正規化した値より大きい場合には、遅延させたデータをラッチしても本来ラッチされるべき値Rv[i]がラッチされることになる。図11の基準信号FREF(ケース2)のような場合は、選択部80は入力Rv1、Rv2、Rv3のうちRv2を選択すれば正しい発振信号位相情報Rv[k+1]を出力できる。

【0085】

このように、図10の発振信号位相情報選択部70に代えて図13の発振信号位相情報選択部180を用いても、同様にメタステーブル状態の発生による発振信号位相情報Rv[k]の誤り発生を回避でき、かつ、従来に比べリクロックのための高速動作するラッチ回路の数も少なくできるので、従来に比べて消費電力の低減も可能である。

【0086】

なお、第1、第2の実施形態のデジタルPLL周波数シンセサイザ101,102では、デジタル位相検出器118は、背景技術の項で説明した図18、図19の構成としたが、これに限らず、例えば、特許文献3又は特許文献4に開示されたデジタル位相検出器等に置き換えてもよい。

【0087】

また、第1、第2の実施形態のデジタルPLL周波数シンセサイザ101,102では、発振器115は、ゲイン調整器114から出力されたデジタル値で制御されるデジタル制御発振器(DCO)を想定したが、これに限らず、ゲイン調整器114から出力されたデジタル値をアナログ値に変換するDA変換器と、その変換されたアナログ信号に応じた電圧で制御される電圧制御発振器(VCO)とで構成されるものであってもよい。

【0088】

また、本発明は上記実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。例えば、特許文献3の図4に開示された構成や特許文献4の図11に示された構成のデジタルPLL周波数シンセサイザに対して、本発明の発振信号位相情報推定部20や選択部12等を付加して、発振器の出力信号から生成されるクロックと基準信号との非同期によるメタステーブル状態の発生の問題を回避させることももちろん可能である。

【0089】

《応用例》

図15は、応用例に係る無線通信機器300の構成図である。図15の無線通信機器300は、デジタルPLL周波数シンセサイザ301と、クロック信号CKVに同期して、データ信号Dinを受けてDinを処理し、処理したデータをデータ信号Doutとして外部に送信する送受信装置302とで構成することができる。なお、デジタルPLL周波数シンセサイザ301は、第1、第2の実施形態のいずれかに係るデジタルPLL周波数シンセサイザ101,102である。無線通信機器300は、例えば図16に示すテレビ350等に搭載されるチューナーとして用いることができる。

【産業上の利用可能性】

【0090】

以上のとおり、本発明のPLL周波数シンセサイザは、位相雑音特性の劣化を回避し消費電力を低減するものとして有用である。

【符号の説明】

【0091】

10 イネーブル端子付カウンタ

12,80,1190 選択部

13,117〜120,203,204,1191〜1194 ラッチ回路

20 発振信号位相情報推定部

70,180 発振信号位相情報選択部

99〜102,1012 デジタルPLL周波数シンセサイザ

112 位相比較器

113 ループフィルタ

114 ゲイン調整器

115 デジタル制御発振器

116 カウンタ

118 デジタル位相検出器

119 リクロック回路

121 正弦波デジタル変換器

401 時間デジタル変換器(TDC)

【技術分野】

【0001】

本発明は、主として半導体集積回路として無線通信装置、無線測定器等で用いられるPLL(Phase-Locked Loop)周波数シンセサイザに関するものである。

【背景技術】

【0002】

近年、半導体の微細化、高速化に伴い、チャージポンプ回路を用いてアナログ電圧で出力周波数を制御するアナログPLL周波数シンセサイザに代わり、デジタル的に電圧制御発振器を制御するデジタルPLL周波数シンセサイザが検討されている(例えば、特許文献1,2、非特許文献1参照)。

【0003】

従来のデジタルPLL周波数シンセサイザの動作について、図を用いて説明する。図17は、従来のデジタルPLL周波数シンセサイザ100の構成を示すブロック図である。同図において、111は累積加算器、112は位相比較器、113はデジタルループフィルタ、114はゲイン調整器、115はデジタル制御発振器、121は正弦波デジタル変換器、116はカウンタ、117及び120はラッチ回路、118はデジタル位相検出器、119はリクロック回路である。

【0004】

デジタルPLL周波数シンセサイザ100には外部の基準水晶発振器からの基準信号FREFと、外部のレジスタ等からの周波数制御ワードFCWとが入力されている。累積加算器111では、基準信号FREFの1周期ごとに周波数制御ワードFCWを累積することによって、基準位相情報Rr[k]が得られる。ここで、[k]は累積加算器111を駆動するクロックの第k番目の遷移に対応して出力される信号を意味する。

【0005】

なお、周波数制御ワードFCWは、基準信号FREFの周波数とデジタル制御発振器115の出力信号の所望周波数との比である。すなわち、デジタル制御発振器115の出力信号の所望周波数をfosc、基準信号FREFの周波数をfrとすると、fosc=FCW×frと表される。また、一般的に、FCWは小数値を含み、foscはfrより高い周波数に設定される。

【0006】

デジタル制御発振器115の出力信号は、正弦波デジタル変換器121で、正弦波からデジタルクロック信号CKVに変換される。カウンタ116では、クロック信号CKVの立ち上がりエッジ(‘0’⇒‘1’のクロック遷移)の数がカウントされ、クロック信号CKVの立ち上がりエッジに同期して変化するカウント値Rv[i]が出力される。ここで、[i]はクロック信号CKVの第i番目の遷移に対応して出力される信号を意味する。ラッチ回路117では、このカウント値Rv[i]が基準信号FREFの1周期ごとにラッチされ、発振信号位相情報Rv[k]として出力される。

【0007】

更に、基準信号FREFとクロック信号CKVとの小さな(クロック信号CKVの周期以下の分解能の)位相差εをデジタル位相検出器118で検出し、基準信号FREFの1周期ごとにラッチ120で蓄積し、ε[k]として出力している。

【0008】

これらの位相情報Rr[k]、Rv[k]、ε[k]を位相比較器112において加減算することにより基準信号FREFとデジタル制御発振器115の出力であるクロック信号CKVとの位相誤差信号PHE[k]が得られる。位相誤差信号PHE[k]は、デジタルループフィルタ113によって高周波成分が取り除かれ、ゲイン調整器114を介して発振器のゲイン調整等の処理が行われた後、発振器115に帰還され、発振器115の周波数が制御される。

【0009】

図18は特許文献2や非特許文献1の図4.13等に開示されているデジタル位相検出器118のブロック図、図19は図18の時間デジタル変換器(TDC)401のブロック図、図20は図18に示したデジタル位相検出器118で位相差εが算出される仕組みを説明するためのタイミング図である。

【0010】

図19によれば、TDC401はL段(Lは2以上の自然数)の直列接続された遅延回路502と、各遅延回路502の出力を入力とするL個のラッチ回路504と、L個のラッチ出力Q(0)〜Q(L−1)を受け取るエッジ検出器とから構成される。

【0011】

図19に示すように、1段目の遅延回路502に発振器115の出力信号から生成されるクロック信号CKVを入力し、ラッチ回路504のクロックに基準信号FREFを用いることで、クロック信号CKVと基準信号FREFとの位相差に関連した情報をデジタル変換した値Q(0)〜Q(L−1)が、各ラッチ回路504より出力される。図19のエッジ検出器は、これらの値からクロック信号CKVの立ち上がりエッジの位相情報(図20のΔTr)とクロック信号CKVの立ち下がりエッジの位相情報(図20のΔTf)とを求めて、図18の正規化回路(NORM)402に出力する。正規化回路(NORM)402では、ΔTfとΔTrの値とをもとに、クロック信号CKVの1周期の時間で正規化された基準信号FREFの立ち上がりエッジとその直後のクロック信号CKVの立ち上がりエッジとの位相差として「ε」を算出する。具体的には、例えば図20(a)及び図20(b)に示すように、ΔTr≦ΔTfの場合にはε=1−ΔTr/2(ΔTf−ΔTr)として、ΔTr>ΔTfの場合にはε=1−ΔTr/2(ΔTr−ΔTf)としてそれぞれ算出される。なお、ΔTf、ΔTrの時間分解能は図19の遅延回路1段分の遅延時間の分解能であるため、位相差εも同じ時間分解能に規定される。

【0012】

一般的に、発振器115の出力信号から生成されるクロック信号CKVと基準信号FREFとは非同期であるため、クロック信号CKVの立ち上がりエッジに同期して変化するラッチ回路117の入力データRv[i]を基準信号FREFでそのままラッチしようとすると、いわゆるメタステーブル状態が発生する危険がある。例えば、図22(a)のように基準信号FREFとクロック信号CKVとの各々の立ち上がりエッジとが近接し、ラッチ回路117の所要のセットアップタイムやホールドタイム以下にΔTrが近づくと、メタステーブル状態が発生しクロック信号CKVの立ち上がりエッジで変化したデータを基準信号FREFで正しくラッチできない場合が生じる。

【0013】

そこで、特許文献1や非特許文献1ではこの危険を回避するため、図17に示すように、基準信号FREFをクロック信号CKVでラッチすることにより、クロック信号CKVに同期した基準信号FREFとほぼ同じ周期のクロック信号CKRをリクロック回路119で生成し、このリクロックされたクロック信号CKRでラッチ回路117、累積加算器111、ラッチ120を駆動するようにしている。

【0014】

図21はリクロック回路119の内部構成例であり、非特許文献1の図4.24にも同様の構成が記載されている。図21において、1190は選択部、1191〜1194はラッチ回路、QP,QN,QNPはラッチ回路1191,1192,1193の各々の出力信号である。

【0015】

上述したようにクロック信号CKRは基準信号FREFを発振器115の出力信号から生成されるクロック信号CKVでラッチすることにより生成されるが、クロック信号CKVの立ち上がりエッジか立ち下がりエッジかのどちらか一方のみで基準信号FREFをラッチしようとすると、リクロックする際にもメタステーブル状態が発生する危険性がある。例えば、基準信号FREFを常にクロック信号CKVの立ち上がりエッジでラッチしてリクロックしようとすると、図22(a)のように基準信号FREFとクロック信号CKVの各々の立ち上がりエッジとが近接し、ラッチ回路の所要のセットアップタイムやホールドタイム以下にΔTrが近づくと、メタステーブル状態が発生する危険が高まる。一方、基準信号FREFを常にクロック信号CKVの立ち下がりエッジでラッチしてリクロックしようとすると、図22(b)のように基準信号FREFの立ち上がりエッジとクロック信号CKVの立ち下がりエッジとが近接し、ラッチ回路の所要のセットアップタイムやホールドタイム以下にΔTfが近づくと、メタステーブル状態が発生する危険が高まる。

【0016】

これらの危険を回避し常に安定したリクロックを行うために、リクロック回路119では、図21に示すように基準信号FREFをクロック信号CKVの立ち上がりエッジ、立ち下がりエッジで各々ラッチするラッチ回路1191,1192を用意し、基準信号FREFとクロック信号CKVとの位相差εの値に応じてデジタル位相検出器118から出力された選択信号SEL_EDGEを用いて、メタステーブル状態になりにくい方のクロック信号CKVのエッジでラッチされた系統の信号を選択し、選択した信号CKを更にクロック信号CKVの立ち上がりエッジでラッチしてクロック信号CKRを生成させている。

【0017】

図23は、FCW=3.5と設定した場合を例に、PLLが所望の周波数に収束した状況における基準信号FREFとクロック信号CKVとのある位相関係時の位相誤差信号PHE[k]が出力されるまでの各信号の変化の様子を示したタイミング図である。

【0018】

図23において、まず、基準信号FREFの第n番目の立ち上がりエッジ付近の信号変化について説明する。基準信号FREFの第n番目の立ち上がりエッジとその直後のクロック信号CKVの立ち上がりエッジとの位相差(時間差)はクロック信号CKVのほぼ1周期近くあり、クロック信号CKVの1周期時間で正規化した位相差(時間差)ε≒1となる。この場合、基準信号FREFとクロック信号CKVとの立ち上がりエッジ同士が図のように近接しており、基準信号FREFの立ち上がりエッジとクロック信号CKVの立ち下がりエッジとの方が離れているので、図21のリクロック回路の選択部1190では信号QNP側が選択され、これを更にラッチ回路1194でラッチしてクロック信号CKRが生成される。そして、このクロック信号CKRの立ち上がりで、図17のカウンタ116の出力Rv[i]、累積加算器111の演算値、デジタル位相検出器118の出力εが各々ラッチされて、Rv[k]、Rr[k]、ε[k]が出力され、位相比較器112より位相誤差PHE[k](=Rr[k]−Rv[k]+ε[k])が出力される。

【0019】

上述したようにFCW=3.5という設定なので、所望の周波数に収束した状況においては、図23のように基準信号FREFの1周期内に約3.5周期分のCKVクロックが存在することになる。したがって、基準信号FREFの次の(第n+1番目の)立ち上がりエッジ付近では、ε≒0.5となる。この場合、基準信号FREFの立ち上がりエッジとクロック信号CKVの立ち下がりエッジとが近接し、基準信号FREFとクロック信号CKVの立ち上がりエッジ同士の方が離れた位相関係になるので、図21のリクロック回路の選択部1190では信号QP側が選択され、これを更にラッチ回路1194でラッチしてクロック信号CKRが生成される。そしてこのクロック信号CKRの立ち上がりで、図17のカウンタ116の出力Rv[i]、累積加算器111の演算値、デジタル位相検出器118の出力εが各々ラッチされて、Rv[k]、Rr[k]、ε[k]が出力され、位相比較器112より位相誤差PHE[k](=Rr[k]−Rv[k]+ε[k])が出力される。

【先行技術文献】

【特許文献】

【0020】

【特許文献1】米国特許第6326851号明細書

【特許文献2】特開2002−76886号公報

【特許文献3】特開2010−21686号公報

【特許文献4】特開2010−119077号公報

【非特許文献】

【0021】

【非特許文献1】R.B.STASZEWSKI and P.T.BALSARA,"ALL-DIGITAL FREQUENCY SYNTHESIZER IN DEEP-SUBMICRON CMOS", Chap.4, John Wiley and Sons,Inc, 2006

【発明の概要】

【発明が解決しようとする課題】

【0022】

上述したように、従来のデジタルPLL周波数シンセサイザ100では、基準信号FREFを発振器115の出力信号から生成されるクロック信号CKVの立ち上がりエッジと立ち下がりエッジとの両方でラッチして、基準信号FREFとクロック信号CKVとの位相差に応じてメタステーブル発生の危険の少ない側のラッチ信号を選択してクロック信号CKRを生成し、クロック信号CKRでラッチ回路117を含め各ブロックのラッチ回路を駆動することにより、クロック信号CKVと基準信号FREFとの非同期によるラッチ回路117におけるメタステーブル状態の発生の危険を回避している。しかしながら、リクロックを安定して行うためには、図21のように、基準信号FREFに比べて高速なクロック信号CKVで駆動する複数のラッチ回路1191〜1194を用いるリクロック回路119が必要となる。そのため、従来のデジタルPLL周波数シンセサイザ100には、ラッチ回路117のメタステーブル状態回避のために、消費電力が増大してしまうという問題がある。

【0023】

本発明は、かかる点に鑑みてなされたものであり、従来に比べて消費電力が少なく、かつ発振器の出力信号CKVと基準信号FREFとの非同期によるメタステーブル状態の発生の問題も回避できるデジタルPLL周波数シンセサイザを提供することを目的とする。

【課題を解決するための手段】

【0024】

上記課題を解決するため、本発明では次のような解決手段を講じた。すなわち、PLL周波数シンセサイザは、デジタル制御コードに応じた発振周波数の発振信号を出力するデジタル制御発振器と、発振信号の波数をカウントしてそのカウント値を出力するカウンタ部と、カウント値を基準信号の1周期毎にラッチしてその値を第1の発振信号位相情報として出力する第1のラッチ部と、第1のラッチ部の出力値を推定し、第2の発振信号位相情報として出力する発振信号位相情報推定部と、基準信号と発振信号との間の位相差値をデジタル値として出力するデジタル位相検出器と、位相差値を基準信号の1周期毎にラッチしてその値を位相差情報として出力する第2のラッチ部と、ロック検出信号に応じて第1の発振信号位相情報から第2の発振信号位相情報に出力信号を切り替える選択部と、選択部の出力を基準信号の1周期毎にラッチしてその値を第3の発振信号位相情報として出力する第3のラッチ部と、発振器の発振周波数を設定するための周波数制御ワードを基準信号の1周期毎に累積加算してその値を基準位相情報として出力する累積加算器と、基準位相情報と位相差情報と第3の発振信号位相情報とから位相誤差を算出して位相誤差信号を出力する位相比較器と、位相比較器の出力信号が与えられ、デジタル制御コードを出力する発振周波数制御部とを備えた構成を採る。

【0025】

これによると、PLL周波数シンセサイザは、通常状態(ロック状態)においてメタステーブル状態の発生の危険を抱えた第1のラッチ部の出力を使用しないため、従来のようなリクロック回路を使用せずとも出力信号と基準信号との非同期によるメタステーブル状態の発生の問題を回避できる。また、リクロックのための高速動作するラッチ回路も不要となるため、従来に比べて消費電力の低減も可能である。

【0026】

また、本発明のPLL周波数シンセサイザは、通常状態(ロック状態)においては、カウンタの出力を使用しないため、選択部が第2の発振信号位相情報を選択するモードに入った場合、カウンタ動作を停止させてもよい。

【0027】

これによると、PLL周波数シンセサイザは、通常状態(ロック状態)においては高速な発振信号クロックで駆動するカウンタ動作を停止させて、更に消費電力の低減ができる。

【0028】

あるいは、PLL周波数シンセサイザは、デジタル制御コードに応じた発振周波数の発振信号を出力するデジタル制御発振器と、発振信号の波数をカウントしてそのカウント値を出力するカウンタ部と、カウント値を第1のクロック信号を用いて基準信号の1周期毎にラッチし、その値を第1の発振信号位相情報として出力する第1のラッチ部と、基準信号と発振信号との間の位相差値をデジタル値として出力するデジタル位相検出器と、位相差値を基準信号の1周期毎にラッチしてその値を位相差情報として出力する第2のラッチ部と、カウント値を第2のクロック信号を用いてラッチし、そのラッチされた値を第1のクロックで基準信号の1周期毎にラッチした値を第2の発振信号位相情報として出力する第3のラッチ部と、位相差情報に応じて、第1の発振信号位相情報、第2の発振信号位相情報、第2の発振信号位相情報に所定値を加えた値のうちいずれかを選択してその値を第3の発振信号位相情報として出力する選択部と、発振器の発振周波数を設定するための周波数制御ワードを基準信号の1周期毎に累積加算してその値を基準位相情報として出力する累積加算器と、基準位相情報と位相差情報と第3の発振信号位相情報とから位相誤差を算出して位相誤差信号を出力する位相比較器と、位相比較器の出力信号が与えられ、デジタル制御コードを出力する発振周波数制御部とを備えた構成を採る。

【0029】

これによると、PLL周波数シンセサイザは、各々異なるクロックでカウント値をラッチする2つのラッチ回路を用いて、位相差情報に応じて、メタステーブル状態の発生の危険性の少ない側のラッチ出力を選択して用いるため、従来のようなリクロック回路を使用せずとも出力信号と基準信号との非同期によるメタステーブル状態の発生の問題を回避できる。また、リクロックのための高速動作するラッチ回路も不要となるため、従来に比べて消費電力の低減も可能である。

【発明の効果】

【0030】

本発明によれば、従来に比べて消費電力が少なく、かつ発振器の出力信号から生成されるクロック信号と基準信号との非同期によるメタステーブル状態の発生の問題も回避できるデジタルPLL周波数シンセサイザを提供することができる。

【図面の簡単な説明】

【0031】

【図1】本発明の第1の実施の形態に係るデジタルPLL周波数シンセサイザの概略構成を示すブロック図である。

【図2】本発明の第1の実施の形態に係る発振信号位相情報推定部の概略構成を示すブロック図である。

【図3】本発明の第1の実施の形態に係る発振信号位相情報推定の原理を説明するためのタイミング図である。

【図4】本発明の第1の実施の形態に係るラッチ判定回路の概略構成を示すブロック図である。

【図5】図4のラッチ判定回路の動作を説明するためのフロー図である。

【図6】デジタルPLL周波数シンセサイザの比較例の構成を示すブロック図である。

【図7】本発明の第1の実施の形態等に係るデジタルPLL周波数シンセサイザの動作のシミュレーション結果を示す図である。

【図8】本発明の第1の実施の形態に係るデジタルPLL周波数シンセサイザの変形例を示すブロック図である。

【図9】本発明の第2の実施の形態に係るデジタルPLL周波数シンセサイザの概略構成を示すブロック図である。

【図10】図9中の発振信号位相情報選択部の概略構成を示すブロック図である。

【図11】本発明の第2の実施の形態に係る発振信号位相情報選択部の選択方法を説明するためのタイミング図である。

【図12】本発明の第2の実施の形態に係るデジタルPLL周波数シンセサイザの変形例を示すブロック図である。

【図13】図12中の発振信号位相情報選択部の概略構成を示すブロック図である。

【図14】本発明の第2の実施の形態に係る変形例の発振信号位相情報選択部の選択方法を説明するためのタイミング図である。

【図15】本発明の応用例に係る無線通信機器の概略構成を示すブロック図である。

【図16】図15の無線通信機器を搭載したテレビの斜視図である。

【図17】従来のデジタルPLL周波数シンセサイザの概略構成を示すブロック図である。

【図18】デジタル位相検出器の概略構成を示すブロック図である。

【図19】デジタル位相検出器に係る時間デジタル変換器(TDC)の概略構成を示すブロック図である。

【図20】(a)及び(b)はデジタル位相検出器で位相差εが算出される仕組みを説明するためのタイミング図である。

【図21】従来のデジタルPLL周波数シンセサイザで使用されるリクロック回路の概略構成を示すブロック図である。

【図22】(a)及び(b)は基準信号FREFと発振器出力から生成されるクロック信号CKVとの位相関係の一例を示すタイミング図である。

【図23】リクロック回路の動作を説明するためのタイミング図である。

【発明を実施するための形態】

【0032】

以下、本発明の実施の形態について図面を参照して詳細に説明する。なお、実施の形態において、従来と同一の構成要素には同一の符号を付し、その説明は背景技術の項で説明したことと重複するので極力省略する。

【0033】

《第1の実施の形態》

図1は、本発明の第1の実施の形態に係るデジタルPLL周波数シンセサイザの概略構成を示すブロック図である。図1において、デジタルPLL周波数シンセサイザ101は、従来のデジタルPLL周波数シンセサイザ100と同じく、累積加算器111、位相比較器112、デジタルループフィルタ113、ゲイン調整器114、デジタル制御発振器115、正弦波デジタル変換器121、ラッチ回路117、時間/デジタル変換器118を有するが、従来用いられてきたリクロック回路を有さない。また、デジタルPLL周波数シンセサイザ101は、イネーブル端子付のカウンタ10と、選択部12と、ラッチ回路13と、発振信号位相情報推定部20とを更に有する。

【0034】

図1に示すように、従来と異なりデジタルPLL周波数シンセサイザ101は、リクロックせずに基準信号FREFそのものを、累積加算器111と、ラッチ回路117,13と、発振信号位相情報推定部20との駆動クロックとして用いる。したがって、ラッチ回路117では、発振器115の出力信号から生成されるクロック信号CKVと基準信号FREFとの非同期によるメタステーブル状態が発生する危険が残る。そのため、メタステーブル状態が発生した場合には、ラッチ回路117は、誤った値を第1の発振信号位相情報として出力する可能性がある。ただし、メタステーブル状態は、図22(a)のように、クロック信号CKVの立ち上がりエッジと基準信号FREFの立ち上がりエッジとが近接し、その間の時間差ΔTrがラッチ回路117の所要のセットアップタイムやホールドタイム以下になる場合に生じるものである。一般的には、図22(a)のΔTrがラッチ回路のセットアップタイムやホールドタイム以下となるケースはそうならないケース、すなわちΔTrがラッチ回路のセットアップタイムやホールドタイムより大きいケースに比べて少ない。そのため、ラッチ回路117が誤った値を出力する頻度は、正しい値を出力する頻度に比べ一般的に低い。

【0035】

図2は、発振信号位相情報推定部20の構成例を示すブロック図である。図2において、201はラッチ回路、202,203,205は減算器、204は丸め回路、206は加算器である。図2の発振信号位相情報推定部20は、基準信号FREFの第k+1番目の遷移(立ち上がりエッジ)とその直後のクロック信号CKVの立ち上がりエッジとのクロック信号CKVの1周期時間で正規化した位相差(時間差)ε[k+1]と、基準信号FREFの1周期前の第k番目の位相差ε[k]との差(ε[k]−ε[k+1])を減算器202で算出し、その算出値から更にFCWの小数部の値FCWFを減算器203で減じた後、その値を丸め回路204で丸めて0又は1の値を減算器205に出力し、その入力値を減算器205でFCWの整数部の値FCWIから減じた後、その値をラッチ回路13の出力に加算器206にて加算した値Rv_est[k+1]を、基準信号FREFの第k+1番目の立ち上がりエッジでラッチ回路117にて正しくラッチした場合の値と推定し、その値を第2の発振信号位相情報として出力する。

【0036】

選択部12は、図示しない外部のロック検出器においてPLLが所定の安定状態(例えばPLLが所望の周波数に収束した状態)であるか否かを判定した結果として出力されるロック検出信号LDを利用して、PLLが安定状態となり所定時間経過するまでは、ラッチ回路117の出力すなわち第1の発振信号位相情報Rvを選択し、PLLが安定状態になって所定時間経過した場合には発振信号位相情報推定部20の出力すなわち第2の発振信号位相情報Rv_estを選択して、ラッチ回路13に出力する。そして、ラッチ回路13はその選択された信号をラッチして、位相比較器112と発振信号位相情報推定部20に出力する。したがって、基準信号FREFの第k+1番目の遷移においてラッチ回路13に選択信号Rv[k+1](又はRv_est[k+1])が入力された時点におけるラッチ回路13の出力は、それより基準信号FREFの1周期前のラッチ回路117(又は発振信号位相情報推定部20)の出力Rv[k](又はRv_est[k)である。

【0037】

図3は、上述のようにして基準信号FREFの第k+1番目の立ち上がりエッジでラッチ回路117を正しくラッチした場合のカウンタ値Rv[k+1]を推定できることを説明するために、FCW=2.5と設定した場合を例に、PLLが所望の周波数に収束した状況における基準信号FREFとクロック信号CKVとのある位相関係時の位相差εや発振信号位相情報RvやRv_est等の変化の様子を示したタイミング図である。

【0038】

図1のカウンタ10はクロック信号CKVの立ち上がりエッジで駆動されカウント値をアップさせる。したがって、基準信号FREFの1周期ごとのカウント値の増分はその基準信号FREFの1周期の区間内に存在するクロック信号CKVの立ち上がりエッジの数に相当する。PLLが所望の周波数に収束した状況においては基準信号FREFの1周期ごとの各区間におけるクロック信号CKVの立ち上がりエッジの数はFCWの整数部の値(FCWI)をNと表すと図3に示すようにNかN+1となる。上述のようにFCW=2.5と設定されているため、図3ではN=2である。

【0039】

図3において基準信号FREFの第m番目の立ち上がりエッジから第m+1番目の立ち上がりエッジまでの区間を区間mと表すことにする。また、区間mから区間m+4までのラッチ回路117の出力Rv[k+1]を各々A0,A1,A2,A3,A4と表す。区間mにおけるカウント値の増分N+1がラッチ回路117において第m+1番目の基準信号FREFの立ち上がりエッジでラッチされるため、第m+1番目の基準信号FREFの立ち上がり直後のラッチ回路117の出力A1はA0+N+1となる。同様にして、図3に示すように、第m+n番目(n=2,3,・・・)の基準信号FREFの立ち上がり直後のラッチ回路117の出力AnはAn−1+(区間m+n−1におけるカウント値の増分)となる。また、図1の選択部12がラッチ回路117の出力を選択している状態におけるラッチ回路13の出力Rv[k]は、ラッチ回路117とラッチ回路13とが同じ基準信号FREFで同期して駆動されているので、図3に示すようにラッチ回路117の出力を基準信号FREFの1周期遅らせたものになる。

【0040】

次に、PLLが収束した状態における基準信号FREFの立ち上がりエッジとその直後のクロック信号CKVの立ち上がりエッジとの位相差εの変動とFCWとの関係について説明する。なお、図3に示すように、基準信号FREFの立ち上がりエッジとその直前のクロック信号CKVの立ち上がりエッジとの時間差をΔTr、クロック信号CKVの1周期の時間をTvとし、基準信号FREFの立ち上がりエッジとその直後のクロック信号CKVの立ち上がりエッジとの位相差εを(Tv−ΔTr)/Tvと定義する。また、FCWの整数部をFCWI、小数部をFCWFと表す。図3の例ではFCW=2.5としているので、FCWI=2、FCWF=0.5である。

【0041】

PLLが所望の周波数に収束した状態においては、基準信号FREFの1周期あたりにほぼFCW個のクロック信号CKVが存在する。したがってFCW=2.5とした場合、ほぼ2.5個のクロック信号CKVが存在するので、図3に示すように、第m番目の基準信号FREFの立ち上がりエッジに対応した位相差ε[m+1]が約0.3だった場合、次の第m+1番目の基準信号FREFの立ち上がりエッジに対応した位相差ε[m+2]は、前回の位相差からほぼFCWF(=0.5)分だけ位相差が変化し、約0.8となる。

【0042】

図3で具体例を示した位相差εの変化とFCWFとの関係を一般式で表すと、

ε[k+1]≒mod(ε[k]−FCWF,1) …(1)

と表される。ここで、mod(A,1)はモジュロ演算(Aを1で割った余り)を意味する。例えば、A=0.3ならmod(A,1)=0.3、A=−0.2ならmod(A,1)=1−0.2=0.8である。よって、ε[k+1]は、

ε[k+1]≒ε[k]−FCWF(ε[k]−FCWF≧0の時) …(2)

ε[k+1]≒1+(ε[k]−FCWF)(ε[k]−FCWF<0の時)…(3)

と表される。

【0043】

図2のラッチ回路201の入力ε[k+1]を出力ε[k]から差し引いた値をΔε[k]とすると、式(1)より、

Δε[k]=ε[k]−ε[k+1]

≒ε[k]−mod(ε[k]−FCWF,1) …(4)

と表される。

【0044】

次に、カウンタ10のカウント値の増分(すなわち、基準信号FREFの1区間内に入るクロック信号CKVの立ち上がりエッジの数)と、εの変動との関係について説明する。

【0045】

図3の第m番目と第m+1番目との基準信号FREFの立ち上がりエッジにおける位相差εの値の変動(約0.3⇒約0.8)と、区間mにおけるカウンタ10のカウント値の増分との関係を見ればわかるように、基準信号FREFのある区間kにおけるカウンタ10のカウント値の増分がFCWI+1となる場合、Δεは負の値を示す。これは言い換えると、Δεの式(4)において、モジュロ演算値がε[k]より大きくなることを意味する。したがって、カウンタ10のカウント値の増分がFCWI+1となる場合、ε[k]−FCWF<0なので、式(3)から、式(4)は、

Δε[k]≒ε[k]−{1+(ε[k]−FCWF)} …(5)

と表される。

【0046】

一方、図3の第m+1番目と第m+2番目との基準信号FREFの立ち上がりエッジにおける位相差εの値の変動(約0.8 ⇒ 約0.3)と、区間m+1におけるカウンタ10のカウント値の増分との関係を見ればわかるように、基準信号FREFのある区間kにおけるカウンタ10のカウント値の増分がFCWIとなる場合、Δεは0以上の値を示す。これは言い換えると、Δεの式(4)において、モジュロ演算値がε[k]以下であることを意味する。したがって、カウンタ10のカウント値の増分がFCWIとなる場合、式(2)から、式(4)は、

Δε[k]≒ε[k]−(ε[k]−FCWF) …(6)

と表される。

【0047】

したがって、キャリーC(C=0又は1)を用いて、第k+1番目の基準信号FREFの立ち上がりエッジでラッチされるラッチ回路117の正しいカウント値Rv[k+1]を、

Rv[k+1]=Rv[k]+FCWI+C …(7)

と表すと、C=1の時、式(5)より、

Δε[k]−FCWF≒−1 …(8)

C=0の時、式(6)より、

Δε[k]−FCWF≒0 …(9)

と表される。

【0048】

式(8)より、C=1の時は、Δε[k]−FCWFを丸めた値Round(Δε[k]−FCWF)が−1となる。また、式(9)より、C=0の時は、Δε[k]−FCWFを丸めた値Round(Δε[k]−FCWF)が0となる。したがって、キャリーCの値は、常に、

C=−Round(Δε[k]−FCWF) …(10)

と表される。よって、式(7)、式(10)より、

Rv[k+1]=Rv[k]+FCWI−Round(Δε[k]−FCWF)

…(11)

という関係が成立する。

【0049】

本発明の第1の実施の形態に係るデジタルPLL周波数シンセサイザは、ラッチ回路117の前回の出力値Rv[k]が正しければ、今回の出力値Rv[k+1]の正しい値と、前回の出力値Rv[k]と、前回と今回との位相差の変動Δε[k]と、FCWとの間に上述した式(11)の関係が成立することを導き出し、図1、図2に示したラッチ回路117と、選択部12と、ラッチ回路13と、発振信号位相情報推定部20とを用いて、式(11)によりラッチ回路117の正しくラッチされた時のカウント値を推定する機能を付加したものである。

【0050】

なお、本実施の形態では、式(7)のキャリーCの値に応じて、ΔεとFCWFとの間に式(8)又は式(9)の関係が成立することから、式(10)のように、丸めを用いてΔεとFCWFでキャリーCを決定した。すなわち、Δε[k]−FCWF≦−0.5ならばC=1、Δε[k]−FCWF>−0.5ならばC=0というように式(7)のキャリーCを決定したが、キャリーCの決定方法はもちろんこれに限らない。例えば、基本的なΔεの変動量(以下、Δεの基準値)はFCWFであるが、図18のTDC401の時間分解能やデジタル制御発振器115自体の位相雑音特性等から推測されるΔεの基準値からの誤差がE(E>0)とすると、すなわち、FCWF−E<Δε<FCWF+Eと想定できる場合には、Δε[k]−FCWF≧−EならばC=0、それ以外の場合はC=1とする等、比較回路を用いて、Δε[k]−FCWFを所定値と比較して、キャリーCを決定することができる。

【0051】

前述したように、ラッチ回路117には、発振器115の出力信号から生成されるクロック信号CKVと基準信号FREFとの非同期によるメタステーブル状態が発生する危険が残るため、ラッチ回路117の前回の出力値Rv[k]が常に正しい値であるとは限らない。そのため、前回の出力値Rv[k]が誤りだった場合、それを用いた推定値も当然誤りとなり、発振信号位相情報推定部20は誤った推定値を出力してしまうことになる。しかしながら、これも前述したように、メタステーブル状態は、図22(a)のように、クロック信号CKVの立ち上がりエッジと基準信号FREFの立ち上がりエッジとが近接し、その間の時間差ΔTrがラッチ回路117の所要のセットアップタイムやホールドタイム以下になる場合に生じるものである。ラッチ回路の性能にもよるが、一般的には、図22(a)のΔTrがラッチ回路のセットアップタイムやホールドタイム以下となるケースは、そうならないケース、すなわちΔTrがラッチ回路のセットアップタイムやホールドタイムより大きいケースに比べて少ない。そのため、ラッチ回路117が誤った値を出力する頻度は、正しい値を出力する頻度に比べ一般的に低い。少なくとも、ラッチ回路117は、常に誤った出力値を出すことはなく、あるタイミングでは必ず正しい値を出力する。

【0052】

一度、ラッチ回路117の正しい出力値Rv[k]から式(11)より、今回のラッチ回路117の正しい出力値を推定して、正しい推定結果Rv_est[k+1]を生成して、その推定結果を、次回の第k+2番目の基準信号FREFの遷移におけるラッチ回路117の出力値Rv[k+1]に代えて使用するようにすることにより、第k番目の基準信号FREFの遷移以降は常に正しい発振信号位相情報を位相比較器112に出力できる。

【0053】

そこで、本発明の第1の実施の形態に係るデジタルPLL周波数シンセサイザは、前回の出力値Rv[k]が正しいかどうかの判定を、ロック検出信号LDを用いて行う。

【0054】

ラッチ回路117の出力Rv[k]が誤った値であり、その値が選択部12で選択されている場合、発振信号位相情報を位相比較器112に出力してしまうので、所望の周波数精度の仕様にもよるが、ある程度所望の周波数精度が厳しければ、PLLは所望の周波数精度に収束しないと考えられる。それ故、ロック検出の条件としては、例えば、発振周波数が所望の周波数精度に所定時間以上収束していることを条件とすればよい。そして上記条件が満たされている場合にロック検出信号LDを図示しないロック検出部から出力(LDの値を1から0に変更)し、選択部12はロック検出信号LDが入力された(LD値が0となった)直後(又はLD値が0の期間が所定時間継続した後)、ラッチ回路13に出力する信号をラッチ回路117の出力信号から発振信号位相情報推定部20の出力信号に切り替えればよい。

【0055】

このようにして、本発明のデジタルPLL周波数シンセサイザは、通常状態(ロック状態)においてメタステーブル状態の発生の危険を抱えたラッチ回路117の出力を使用しないため、従来のようなリクロック回路を使用せずとも出力信号CKVと基準信号FREFとの非同期によるメタステーブル状態の発生の問題を回避できる。また、リクロックのための高速動作するラッチ回路も不要となるため、従来に比べて消費電力の低減も可能である。

【0056】

また、選択部12がその出力信号をラッチ回路117の出力信号から発振信号位相情報推定部20の出力信号に切り替えた後は、それまで使用してきたカウンタ10は不要となるので、ロック検出信号LDあるいはそれに関連した信号をカウンタ10のイネーブル信号として用いて、選択部12の出力信号の切り替えタイミングに応じて、カウンタ動作を停止させてもよい。

【0057】

このように、高速なクロック信号CKVで動作するカウンタ10を停止させることにより、従来のデジタルPLL周波数シンセサイザに比べて、更に消費電力の低減が可能となる。

【0058】

また、上述の説明では、ロック検出の条件を、発振周波数が所望の周波数精度に所定時間以上収束していることとし、この条件を選択部12における信号切り替え条件として用いたが、選択部12における信号切り替えに使用するロック検出の条件はこれに限らず、例えば、ラッチ回路117の出力Rvの変動が所定の範囲内に所定時間以上収束していることとしてもよい。例えば、図3等を用いて説明したようにPLLが所望の発振周波数精度に収束した状態において、Rvの変動(ラッチ回路117の出力値の増分)は、FCWIかFCWI+1かのどちらかの値を取る。つまり、キャリーCは0又は1である。そのため、これらの値以外のRvの変動があった場合、前回又は今回の少なくともどちらか一方の出力Rvの値は誤りであると判断できる。逆にRvの変動がFCWIかFCWI+1かのどちらかであれば、前回の出力Rvの値は正しい可能性が高い。そこで、例えば、ラッチ回路117の出力Rvの変動がFCWIかFCWI+1かのどちらかである区間が所定時間(例えば、基準信号FREFの128周期)継続した場合に、ロック検出信号LDを図示しないロック検出部から出力(例えばLDの値を1から0に変更)するようにしてもよい。

【0059】

あるいはまた、ロック検出の条件を、例えば、ラッチ回路117の出力Rv[k+1]と発振信号位相情報推定部20の出力Rv_est[k+1]とを比較して値が一致した場合(あるいは一致状態が、所定時間継続した場合)に、ロック検出信号LDを図示しないロック検出部から出力(例えばLDの値を1から0に変更)するようにしてもよい。

【0060】

PLL周波数シンセサイザの所望の周波数精度の仕様が甘い場合には、ラッチ回路117の出力Rvが誤っていても所望の周波数精度を満足してしまうことがある。したがって、このようにPLL周波数シンセサイザの所望の周波数精度の仕様が甘い場合には、上述した例のように、ラッチ回路117の出力Rvの値をロック検出条件として用いることが望ましい。

【0061】

なお、上述した例のように、ラッチ回路117の出力Rvの値をロック検出条件として用いた場合には、選択部12の出力信号の切り替えタイミングに応じて、常時カウンタ10を停止してしまうと、何らかの突発的な外乱ノイズ等でPLLの発振周波数が所望値から外れてしまった場合でもロック検出信号LDが出力されたままになってしまう。

【0062】

そのため、ラッチ回路117の出力Rvの値をロック検出条件として用いる場合には、選択部12の出力信号の切り替えタイミングに応じて、カウンタ10を停止させた後、カウンタ10を間欠的に動作させ、PLLの収束状態を確認するようにすればよい。

【0063】

あるいは、上述のように、ラッチ回路117の出力Rvの値を用いたロック検出条件を第1のロック検出条件とし、発振周波数が所望の周波数精度に所定時間以上収束していることを第2のロック検出の条件とし、これら2つのロック検出条件を同時に満たす場合のみロック検出信号LDを選択部12やカウンタ10に出力(例えばLDの値を1から0に変更)するようにして、ロック検出信号LDがロック状態(値0)を示している間はカウンタ10を常時停止するようにしてもよい。

【0064】

例えば、図4のように、ラッチ回路117の出力Rv[k+1]をラッチ回路117と同じく基準信号FREFでラッチしてRv[k]を生成し、Rv[k+1]とRv[k]との差に位相情報推定部20内の丸め回路204の出力を加えた信号ΔRvを生成し、ΔRvとFCWIとの差を示す信号Rv_NGを出力するラッチ判定回路220を設け、図5のフローに従って、選択部12における信号切り替えに使用するロック検出信号LDを切り替えてもよい。

【0065】

第k番目とk+1番目の基準信号FREFの立ち上がりエッジにおけるラッチ回路117の出力Rv[k]、Rv[k+1]が正常な値である場合、式(11)より、

Rv[k+1]−Rv[k]+Round(Δε[k]−FCWF)=FCWI

…(12)

という関係が成立する。したがって、ラッチ判定回路220の出力Rv_NGが0ならば、発振信号位相情報推定部20で推定に使用されたRv[k]の値は正しく、推定値Rv_est[k+1]も正しい値となる。

【0066】

そこで、Rv_NGが0であることを第1のロック検出条件として、図5のフローに示すように、まず初期状態として、第1のロック検出信号LDを1とし(S1)、Rv_NGが0か否かを判定し(S2)、0ならばLDを1から0として選択部12の出力をラッチ回路117側から発振信号位相情報推定部20側に切り替える(S3)。それにあわせてカウンタ10の動作を停止させる。そして、通常良く用いられるロック条件(例えば、発振周波数が所望の周波数精度に所定時間以上収束していること)を第2のロック検出条件として、第2のロック検出条件に対応する第2のロック検出信号NLDがロック状態からロック外れの状態に切り替わった否かを常時判定し(S4)、第2のロック検出条件が外れた場合、第1のロック検出信号LDを1(S1)として、カウンタ10の動作を再開させ、Rv_NGが0か否かの判定をRv_NGが0になるまで繰り返す(S2)。

【0067】

このように、ロック検出条件に関しては、様々なバリエーションが適用可能である。一例として、ラッチ回路117の出力Rvの変動がFCWIかFCWI+1かのどちらかである区間が所定時間(基準信号FREFの128周期)継続した場合に、ロック検出信号LDを出力するようにした場合のデジタルPLL周波数シンセサイザ101の動作のシミュレーション結果(位相雑音特性)を、図7に示す(図7の(3))。なお、図7には比較のために、従来のデジタルPLL周波数シンセサイザ100の動作のシミュレーション結果(図7の(1))と、図6に示したデジタルPLL周波数シンセサイザ99のように、従来のリクロック回路119や本実施の形態の発振信号位相情報推定部20を設けずに、単純にラッチ回路117を基準信号FREFで駆動させた場合の動作のシミュレーション結果結果(図7の(2))を併せて示している。また、図7のシミュレーション結果(2)(3)では、ラッチ回路117におけるメタステーブル状態の発生による出力Rvの値の誤りを、位相差εが0.01以下か0.99以上の場合に1/2の確率でRvの正しい出力値から1小さい値を出力するようにして、擬似的に付加させている。単純にラッチ回路117を基準信号FREFで駆動させた場合(図7の(2))には、メタステーブル状態による誤差発生により位相雑音特性が大幅に劣化してしまうが、本実施の形態のデジタルPLL周波数シンセサイザ101では、ラッチ回路117でメタステーブル状態による誤差が時々生じたとしても、問題なく従来のリクロック回路119を用いたデジタルPLL周波数シンセサイザ100と同等の位相雑音特性を示す。

【0068】

なお、上述した第1の実施形態のデジタルPLL周波数シンセサイザ101では、デジタル位相検出器118の出力信号である位相差εをラッチする回路は、発振信号位相情報推定部20内のラッチ回路201(図17における従来のラッチ回路120に相当)のみであるが、ラッチ回路の段数はこれに限らず、位相比較器112に入力される位相差εと発振信号位相情報Rv(又はRv_est)とのタイミング関係が図3と同様に取れていればよい。

【0069】

例えば、図8のデジタルPLL周波数シンセサイザ1012におけるラッチ回路202,203のように、図1のデジタル位相検出器118−発振信号位相情報推定部20間のパスと、ラッチ回路117−選択部12間のパスとに、複数のラッチ回路を同じ数だけ挿入してもよい。

【0070】

《第2の実施の形態》

図9は、本発明の第2の実施の形態に係るデジタルPLL周波数シンセサイザ102の概略構成を示すブロック図である。図9において、デジタルPLL周波数シンセサイザ102は、第1の実施の形態のデジタルPLL周波数シンセサイザ101と同じく、従来用いられてきたリクロック回路を有さない。また、第1の実施の形態のデジタルPLL周波数シンセサイザ101のイネーブル端子付のカウンタ10に代えて従来と同じカウンタ116を用いる。また、第1の実施の形態のデジタルPLL周波数シンセサイザ101の選択部12と、ラッチ回路13と、発振信号位相情報推定部20とに代えて発振信号位相情報選択部70を有する。

【0071】

図10は、発振信号位相情報選択部70の構成例を示すブロック図である。図10に示すように発振信号位相情報選択部70は、カウンタ116から出力された発振信号位相情報Rv[i]を発振器115の出力信号から生成されるクロック信号CKVの立ち下がりエッジでラッチするラッチ回路801と、基準信号FREFで入力信号をラッチする複数のラッチ回路802〜807と、加算器81と、選択部80とを有する。

【0072】

発振信号位相情報選択部70は、ラッチ回路801の出力Rv_i[i]をラッチ回路802とラッチ回路804とにより基準信号FREFで2回ラッチした後、ラッチ回路804の出力Rv2を加算器81と選択部80とに入力する。加算器81はRv2に1を加えた値Rv3を選択部80に出力する。また、一方、発振信号位相情報Rv[i]をラッチ回路803とラッチ回路805とにより基準信号FREFで2回ラッチした後、ラッチ回路805の出力Rv1を選択部80に入力する。ここで、ラッチ回路802の出力をRv[k+2]aとし、ラッチ回路803の出力をRv[k+2]bとする。

【0073】

従来の課題でも述べたように、クロック信号CKVと基準信号FREFとは非同期であるため、ラッチ回路802及びラッチ回路803においては、メタステーブル状態が発生する危険があり、発生した場合には誤った値を出力してしまう場合がある。ただし、ラッチ回路802に入力されるデータの変化はラッチ回路803に入力されるデータの変化よりクロック信号CKVの半周期分遅れるため、ラッチ回路802とラッチ回路803とが同時にメタステーブル状態になることは通常ない。そこで、選択部80は、クロック信号CKVと基準信号FREFとの位相差ε[k+1]の値に応じて、メタステーブル状態の発生の危険が低い入力データをRv1、Rv2、Rv3のうちから選択して発振信号位相情報Rv[k+1]をラッチ回路806に出力する。ラッチ回路806は基準信号FREFで発振信号位相情報Rv[k+1]をラッチして発振信号位相情報Rv[k]を出力する。

【0074】

図11は、上述のように発振信号位相情報選択部70において位相差εに応じてRv1、Rv2、Rv3のうちから選択することにより、常に正しい発振信号位相情報Rv[k+1]を生成できることを説明するための図である。

【0075】

図11の基準信号FREF(ケース1)のように、クロック信号CKVと基準信号FREFとの立ち上がりエッジの間隔がラッチ回路のセットアップタイムやホールドタイムの規定を十分満たす程度に離れている場合には、ラッチ回路803ではメタステーブル状態が発生する危険はなく、選択部80は入力Rv1、Rv2、Rv3のうちRv1を選択すれば正しい発振信号位相情報Rv[k+1]を出力できる。

【0076】

また、図11の基準信号FREF(ケース2)や基準信号FREF(ケース3)のように、クロック信号CKVと基準信号FREFとの立ち上がりエッジの間隔がラッチ回路のセットアップタイムやホールドタイムの規定を満たせない程近接している場合には、クロック信号CKVの立ち上がりエッジで変化するデータRv[i]を所定の時間ΔT(ここではクロック信号CKVの半周期分)遅延させた入力データをラッチするラッチ回路802ではメタステーブル状態が発生する危険はない。ただし、図11の基準信号FREF(ケース2)のように、位相差εがΔTをクロック信号CKVの1周期の時間で割って正規化した値より大きい場合には、データを遅延させたことにより本来ラッチされるべき値Rv[i]ではなく1少ない値がラッチされることになる。したがって、図11の基準信号FREF(ケース2)のような場合は、選択部80は入力Rv1、Rv2、Rv3のうちRv2に1を加えた値、すなわちRv3を選択すれば正しい発振信号位相情報Rv[k+1]を出力できる。また、図11の基準信号FREF(ケース3)のように、位相差εがΔTをクロック信号CKVの1周期の時間で割って正規化した値より小さい場合には、遅延させたデータをラッチしても本来ラッチされるべき値Rv[i]がラッチされることになる。図11の基準信号FREF(ケース3)のような場合は、選択部80は入力Rv1、Rv2、Rv3のうちRv2を選択すれば正しい発振信号位相情報Rv[k+1]を出力できる。

【0077】

例えば、本実施の形態のようにΔTをクロック信号CKVの半周期とした場合、0≦ε<0.25ならばRv2を選択、0.25≦ε<0.75ならばRv1を選択、0.75≦ε<1ならばRv3を選択とすれば、ラッチ回路のセットアップタイムやホールドタイムの規定値を最大限に緩めることができる。

【0078】

なお、選択部80のεの値に応じた発振信号位相情報(Rv1、Rv2、Rv3)の選択は、上記値に限るものではなく、ラッチ回路のセットアップタイムやホールドタイムの規定値を満足する限り柔軟に定めることができる。

【0079】

また、本実施の形態では、発振信号位相情報Rv[i]の遅延時間ΔTをクロック信号CKVの半周期として、発振信号位相情報Rv[i]をクロック信号CKVの立ち下がりエッジでラッチすることにより半周期分遅延させたが、遅延時間ΔTはこれに限るものではない。例えば、ラッチ回路のセットアップタイムやホールドタイムの規定値がクロック信号CKVの1周期の時間Tvの1/10だとすると、ΔTをTvの2/10より大きい値、例えばTvの3/10程度の時間となるように遅延回路を用いてクロック信号CKVを遅延させたクロックでラッチ回路801をラッチすればよい。また、その場合、選択部80のεの値に応じた発振信号位相情報(Rv1、Rv2、Rv3)の選択は、0≦ε<閾値1ならばRv2を選択、閾値1≦ε<閾値2ならばRv1を選択、閾値2≦ε<1ならばRv3を選択とした場合に、閾値1を0.1より大きく0.2未満の値(例えば0.15)、閾値2を0.8より大きく0.9未満の値(例えば0.85)とすればよい。

【0080】

このように、本発明の実施の形態においては、基準信号FREFに比べ高速なクロック信号CKVで駆動するラッチ回路を多数必要とする従来のリクロック回路119に代えて、低速な基準信号FREFで駆動するラッチ回路を複数用いた発振信号位相情報選択部70を用いて、メタステーブル状態の発生による発振信号位相情報Rv[k]の誤り発生を回避でき、かつ、従来に比べリクロックのための高速動作するラッチ回路の数も少なくできるので、従来に比べて消費電力の低減も可能である。

【0081】

《変形例》

図12は、本発明の第2の実施の形態に係るデジタルPLL周波数シンセサイザ102の変形例を示すブロック図である。図10の発振信号位相情報選択部70では、発振信号位相情報Rv[i]を遅延させたデータRv_i[i]を生成するラッチ回路801と、従来どおりに発振信号位相情報Rv[i]をラッチするラッチ回路803とを用いて、位相差情報に応じて、メタステーブル状態の発生の危険性の少ない側のラッチ出力を選択するものとしたが、図13に示す発振信号位相情報選択部180のように、発振信号位相情報Rv[i]を遅延させるのではなく、バッファ84等により基準信号FREFを所定時間ΔTだけ遅延させたクロック信号FREF_dで駆動するラッチ回路801を設けて、ラッチ回路801から出力されたデータから生成される発振信号位相情報Rv2,Rv3と、従来どおりに基準信号FREFで発振信号位相情報Rv[i]をラッチするラッチ回路803から出力されたデータから生成される発振信号位相情報Rv1とを、位相差情報ε[k+1]に応じて、メタステーブル状態の発生の危険性の少ない側のラッチ出力を選択するものとしてもよい。

【0082】

図14は、上述のように発振信号位相情報選択部180において位相差εに応じてRv1,Rv2,Rv3のうちから選択することにより、常に正しい発振信号位相情報Rv[k+1]を出力できることを説明するための図である。

【0083】

図14の基準信号FREF(ケース1)のように、クロック信号CKVと基準信号FREFとの立ち上がりエッジの間隔がラッチ回路のセットアップタイムやホールドタイムの規定を十分満たす程度に離れている場合には、ラッチ回路803ではメタステーブル状態が発生する危険はなく、選択部80は入力Rv1、Rv2、Rv3のうちRv1を選択すれば正しい発振信号位相情報Rv[k+1]を出力できる。

【0084】

また、図14の基準信号FREF(ケース2)や基準信号FREF(ケース3)のように、クロック信号CKVと基準信号FREFとの立ち上がりエッジの間隔がラッチ回路のセットアップタイムやホールドタイムの規定を満たせない程近接している場合には、基準信号FREFを所定の時間ΔT(ここではクロック信号CKVの半周期分)遅延させたクロック信号FREF_dでラッチするラッチ回路801ではメタステーブル状態が発生する危険はない。ただし、図14の基準信号FREF(ケース3)のように、位相差εがΔTをクロック信号CKVの1周期の時間で割って正規化した値より小さい場合には、駆動クロックを遅延させたことにより本来ラッチされるべき値Rv[i]ではなく1大きい値がラッチされることになる。したがって、図14の基準信号FREF(ケース3)のような場合は、選択部80は入力Rv1、Rv2、Rv3のうちRv2から減算器83にて1を減じた値、すなわちRv3を選択すれば正しい発振信号位相情報Rv[k+1]を出力できる。また、図14の基準信号FREF(ケース2)のように、位相差εがΔTをクロック信号CKVの1周期の時間で割って正規化した値より大きい場合には、遅延させたデータをラッチしても本来ラッチされるべき値Rv[i]がラッチされることになる。図11の基準信号FREF(ケース2)のような場合は、選択部80は入力Rv1、Rv2、Rv3のうちRv2を選択すれば正しい発振信号位相情報Rv[k+1]を出力できる。

【0085】

このように、図10の発振信号位相情報選択部70に代えて図13の発振信号位相情報選択部180を用いても、同様にメタステーブル状態の発生による発振信号位相情報Rv[k]の誤り発生を回避でき、かつ、従来に比べリクロックのための高速動作するラッチ回路の数も少なくできるので、従来に比べて消費電力の低減も可能である。

【0086】

なお、第1、第2の実施形態のデジタルPLL周波数シンセサイザ101,102では、デジタル位相検出器118は、背景技術の項で説明した図18、図19の構成としたが、これに限らず、例えば、特許文献3又は特許文献4に開示されたデジタル位相検出器等に置き換えてもよい。

【0087】

また、第1、第2の実施形態のデジタルPLL周波数シンセサイザ101,102では、発振器115は、ゲイン調整器114から出力されたデジタル値で制御されるデジタル制御発振器(DCO)を想定したが、これに限らず、ゲイン調整器114から出力されたデジタル値をアナログ値に変換するDA変換器と、その変換されたアナログ信号に応じた電圧で制御される電圧制御発振器(VCO)とで構成されるものであってもよい。

【0088】

また、本発明は上記実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。例えば、特許文献3の図4に開示された構成や特許文献4の図11に示された構成のデジタルPLL周波数シンセサイザに対して、本発明の発振信号位相情報推定部20や選択部12等を付加して、発振器の出力信号から生成されるクロックと基準信号との非同期によるメタステーブル状態の発生の問題を回避させることももちろん可能である。

【0089】

《応用例》

図15は、応用例に係る無線通信機器300の構成図である。図15の無線通信機器300は、デジタルPLL周波数シンセサイザ301と、クロック信号CKVに同期して、データ信号Dinを受けてDinを処理し、処理したデータをデータ信号Doutとして外部に送信する送受信装置302とで構成することができる。なお、デジタルPLL周波数シンセサイザ301は、第1、第2の実施形態のいずれかに係るデジタルPLL周波数シンセサイザ101,102である。無線通信機器300は、例えば図16に示すテレビ350等に搭載されるチューナーとして用いることができる。

【産業上の利用可能性】

【0090】

以上のとおり、本発明のPLL周波数シンセサイザは、位相雑音特性の劣化を回避し消費電力を低減するものとして有用である。

【符号の説明】

【0091】

10 イネーブル端子付カウンタ

12,80,1190 選択部

13,117〜120,203,204,1191〜1194 ラッチ回路

20 発振信号位相情報推定部

70,180 発振信号位相情報選択部

99〜102,1012 デジタルPLL周波数シンセサイザ

112 位相比較器

113 ループフィルタ

114 ゲイン調整器

115 デジタル制御発振器

116 カウンタ

118 デジタル位相検出器

119 リクロック回路

121 正弦波デジタル変換器

401 時間デジタル変換器(TDC)

【特許請求の範囲】

【請求項1】

デジタル制御コードに応じた発振周波数で発振する発振器と、

前記発振器の出力信号をもとに生成される発振信号の波数をカウントしてそのカウント値を出力するカウンタ部と、

前記カウント値を基準信号でラッチしてその値を第1の発振信号位相情報として出力する第1のラッチ部と、

前記第1のラッチ部の出力値を推定し、第2の発振信号位相情報として出力する発振信号位相情報推定部と、

前記基準信号と前記発振信号との間の位相差値をデジタル値として出力するデジタル位相検出器と、

前記位相差値を前記基準信号でラッチしてその値を位相差情報として出力する第2のラッチ部と、

ロック検出信号に応じて前記第1の発振信号位相情報から前記第2の発振信号位相情報に出力信号を切り替える選択部と、

前記選択部の出力を前記基準信号でラッチしてその値を第3の発振信号位相情報として出力する第3のラッチ部と、

前記発振器の発振周波数を設定するための周波数制御ワードを前記基準信号の所定数の周期毎に累積加算してその値を基準位相情報として出力する累積加算器と、

前記基準位相情報と前記位相差情報と前記第3の発振信号位相情報とから位相誤差を算出して位相誤差信号を出力する位相比較器と、

前記位相比較器の出力信号が与えられ、前記デジタル制御コードを出力する発振周波数制御部とを備えたことを特徴とするPLL周波数シンセサイザ。

【請求項2】

請求項1記載のPLL周波数シンセサイザにおいて、

前記位相比較器と前記発振周波数制御部との間に介在したデジタルループフィルタを更に備えたことを特徴とするPLL周波数シンセサイザ。

【請求項3】

請求項1記載のPLL周波数シンセサイザにおいて、

前記発振信号位相情報推定部は、前記第2のラッチ部の今回の出力値と前記基準信号の所定数の周期前の前回の出力値との差である位相差変化量と、前記周波数制御ワードの整数部の値と、前記周波数制御ワードの小数部の値と、前記第3のラッチ部の出力とから、前記第2の発振信号位相情報を生成することを特徴とするPLL周波数シンセサイザ。

【請求項4】

請求項1記載のPLL周波数シンセサイザにおいて、

前記カウンタ部は、カウンタ動作を停止する機能を有することを特徴とするPLL周波数シンセサイザ。

【請求項5】

請求項4記載のPLL周波数シンセサイザにおいて、

前記カウンタ部は、前記選択部が前記第2の発振信号位相情報を選択するモードに入った場合、カウンタ動作を常時又は間欠的に停止することを特徴とするPLL周波数シンセサイザ。

【請求項6】

請求項1記載のPLL周波数シンセサイザにおいて、

前記第1の発振信号位相情報の変動が所定の範囲内に収束した場合に安定状態と判断されることを特徴とするPLL周波数シンセサイザ。

【請求項7】

請求項1記載のPLL周波数シンセサイザにおいて、

前記第1のラッチ部の出力値をもとに前記発振信号位相情報推定部における推定が正しいか否かを判定するラッチ判定回路を更に備えたことを特徴とするPLL周波数シンセサイザ。

【請求項8】

請求項1記載のPLL周波数シンセサイザにおいて、

前記ラッチ判定回路の判定結果に応じて前記ロック検出信号を切り替えることを特徴とするPLL周波数シンセサイザ。

【請求項9】

デジタル制御コードに応じた発振周波数で発振する発振器と、

前記発振器の出力信号をもとに生成される発振信号の波数をカウントしてそのカウント値を出力するカウンタ部と、

前記カウント値を第1のクロック信号を用いて基準信号でラッチし、その値を第1の発振信号位相情報として出力する第1のラッチ部と、

前記基準信号と前記発振信号との間の位相差値をデジタル値として出力するデジタル位相検出器と、

前記位相差値を前記基準信号でラッチしてその値を位相差情報として出力する第2のラッチ部と、

前記カウント値を第2のクロック信号を用いてラッチし、そのラッチされた値を前記第1のクロックで前記基準信号でラッチした値を第2の発振信号位相情報として出力する第3のラッチ部と、

前記位相差情報に応じて、前記第1の発振信号位相情報、前記第2の発振信号位相情報、前記第2の発振信号位相情報に所定値を加えた値のうちいずれかを選択してその値を第3の発振信号位相情報として出力する選択部と、

前記発振器の発振周波数を設定するための周波数制御ワードを前記基準信号の所定数の周期毎に累積加算してその値を基準位相情報として出力する累積加算器と、

前記基準位相情報と前記位相差情報と前記第3の発振信号位相情報とから位相誤差を算出して位相誤差信号を出力する位相比較器と、

前記位相比較器の出力信号が与えられ、前記デジタル制御コードを出力する発振周波数制御部とを備えたことを特徴とするPLL周波数シンセサイザ。

【請求項10】

請求項9記載のPLL周波数シンセサイザにおいて、

前記位相比較器と前記発振周波数制御部との間に介在したデジタルループフィルタを更に備えたことを特徴とするPLL周波数シンセサイザ。

【請求項11】

請求項9記載のPLL周波数シンセサイザにおいて、

前記第1のクロック信号は、前記基準信号又は前記基準信号に同期し前記基準信号と周期が同じ信号であって、

前記第2のクロック信号は、前記発振信号と同じ周期で前記発振信号と所定の位相差を有する信号であって、

前記位相差情報が第1の所定値未満又は第1の所定値以下の場合には前記第2の発振信号位相情報を選択し、前記位相差情報が第2の所定値以上又は第2の所定値を超える場合には前記第2の発振信号位相情報に1を加えた値を選択し、前記位相差情報が前記第1の所定値以上又は前記第1の所定値を越え、かつ前記第2の所定値未満又は前記第2の所定値以下の場合には前記第1の発振信号位相情報を選択して出力することを特徴とするPLL周波数シンセサイザ。

【請求項12】

請求項11記載のPLL周波数シンセサイザにおいて、

前記第1のクロック信号は前記基準信号であって、

前記第2のクロック信号は、前記発振信号を反転させた信号であって、

前記第1の所定値は、前記基準信号の立ち上がりエッジと前記発振信号の立ち上がりエッジとの時間差を前記発振信号の1周期の時間で正規化した場合に0.25となる値であって、前記第2の所定値は、前記基準信号の立ち上がりエッジと前記発振信号の立ち上がりエッジとの時間差を前記発振信号の1周期の時間で正規化した場合に0.75となる値であるPLL周波数シンセサイザ。

【請求項13】

請求項9記載のPLL周波数シンセサイザにおいて、

前記第1のクロック信号は、前記基準信号又は前記基準信号に同期し前記基準信号と周期が同じ信号であって、

前記第2のクロック信号は、前記第1のクロック信号を所定時間遅延させた信号であって、

前記位相差情報が第1の所定値未満又は第1の所定値以下の場合には前記第2の発振信号位相情報から1を減じた値を選択し、前記位相差情報が第2の所定値以上又は第2の所定値を超える場合には前記第2の発振信号位相情報を選択し、前記位相差情報が前記第1の所定値以上又は前記第1の所定値を越え、かつ前記第2の所定値未満又は前記第2の所定値以下の場合には前記第1の発振信号位相情報を選択して出力することを特徴とするPLL周波数シンセサイザ。

【請求項14】

請求項13記載のPLL周波数シンセサイザにおいて、

前記第1のクロック信号は前記基準信号であって、

前記第2のクロック信号は、前記基準信号を前記発振信号のほぼ半周期時間遅延させた信号であって、

前記第1の所定値は、前記基準信号の立ち上がりエッジと前記発振信号の立ち上がりエッジとの時間差を前記発振信号の1周期の時間で正規化した場合に0.25となる値であって、前記第2の所定値は、前記基準信号の立ち上がりエッジと前記発振信号の立ち上がりエッジとの時間差を前記発振信号の1周期の時間で正規化した場合に0.75となる値であるPLL周波数シンセサイザ。

【請求項15】

請求項1〜14のいずれか1項に記載のPLL周波数シンセサイザを有する受信回路又は送信回路の少なくとも一方を備えた無線通信機器。

【請求項1】

デジタル制御コードに応じた発振周波数で発振する発振器と、

前記発振器の出力信号をもとに生成される発振信号の波数をカウントしてそのカウント値を出力するカウンタ部と、

前記カウント値を基準信号でラッチしてその値を第1の発振信号位相情報として出力する第1のラッチ部と、

前記第1のラッチ部の出力値を推定し、第2の発振信号位相情報として出力する発振信号位相情報推定部と、

前記基準信号と前記発振信号との間の位相差値をデジタル値として出力するデジタル位相検出器と、

前記位相差値を前記基準信号でラッチしてその値を位相差情報として出力する第2のラッチ部と、

ロック検出信号に応じて前記第1の発振信号位相情報から前記第2の発振信号位相情報に出力信号を切り替える選択部と、

前記選択部の出力を前記基準信号でラッチしてその値を第3の発振信号位相情報として出力する第3のラッチ部と、

前記発振器の発振周波数を設定するための周波数制御ワードを前記基準信号の所定数の周期毎に累積加算してその値を基準位相情報として出力する累積加算器と、

前記基準位相情報と前記位相差情報と前記第3の発振信号位相情報とから位相誤差を算出して位相誤差信号を出力する位相比較器と、

前記位相比較器の出力信号が与えられ、前記デジタル制御コードを出力する発振周波数制御部とを備えたことを特徴とするPLL周波数シンセサイザ。

【請求項2】

請求項1記載のPLL周波数シンセサイザにおいて、

前記位相比較器と前記発振周波数制御部との間に介在したデジタルループフィルタを更に備えたことを特徴とするPLL周波数シンセサイザ。

【請求項3】

請求項1記載のPLL周波数シンセサイザにおいて、

前記発振信号位相情報推定部は、前記第2のラッチ部の今回の出力値と前記基準信号の所定数の周期前の前回の出力値との差である位相差変化量と、前記周波数制御ワードの整数部の値と、前記周波数制御ワードの小数部の値と、前記第3のラッチ部の出力とから、前記第2の発振信号位相情報を生成することを特徴とするPLL周波数シンセサイザ。

【請求項4】

請求項1記載のPLL周波数シンセサイザにおいて、

前記カウンタ部は、カウンタ動作を停止する機能を有することを特徴とするPLL周波数シンセサイザ。

【請求項5】

請求項4記載のPLL周波数シンセサイザにおいて、

前記カウンタ部は、前記選択部が前記第2の発振信号位相情報を選択するモードに入った場合、カウンタ動作を常時又は間欠的に停止することを特徴とするPLL周波数シンセサイザ。

【請求項6】

請求項1記載のPLL周波数シンセサイザにおいて、

前記第1の発振信号位相情報の変動が所定の範囲内に収束した場合に安定状態と判断されることを特徴とするPLL周波数シンセサイザ。

【請求項7】

請求項1記載のPLL周波数シンセサイザにおいて、

前記第1のラッチ部の出力値をもとに前記発振信号位相情報推定部における推定が正しいか否かを判定するラッチ判定回路を更に備えたことを特徴とするPLL周波数シンセサイザ。

【請求項8】

請求項1記載のPLL周波数シンセサイザにおいて、

前記ラッチ判定回路の判定結果に応じて前記ロック検出信号を切り替えることを特徴とするPLL周波数シンセサイザ。

【請求項9】

デジタル制御コードに応じた発振周波数で発振する発振器と、

前記発振器の出力信号をもとに生成される発振信号の波数をカウントしてそのカウント値を出力するカウンタ部と、

前記カウント値を第1のクロック信号を用いて基準信号でラッチし、その値を第1の発振信号位相情報として出力する第1のラッチ部と、

前記基準信号と前記発振信号との間の位相差値をデジタル値として出力するデジタル位相検出器と、

前記位相差値を前記基準信号でラッチしてその値を位相差情報として出力する第2のラッチ部と、

前記カウント値を第2のクロック信号を用いてラッチし、そのラッチされた値を前記第1のクロックで前記基準信号でラッチした値を第2の発振信号位相情報として出力する第3のラッチ部と、

前記位相差情報に応じて、前記第1の発振信号位相情報、前記第2の発振信号位相情報、前記第2の発振信号位相情報に所定値を加えた値のうちいずれかを選択してその値を第3の発振信号位相情報として出力する選択部と、

前記発振器の発振周波数を設定するための周波数制御ワードを前記基準信号の所定数の周期毎に累積加算してその値を基準位相情報として出力する累積加算器と、

前記基準位相情報と前記位相差情報と前記第3の発振信号位相情報とから位相誤差を算出して位相誤差信号を出力する位相比較器と、

前記位相比較器の出力信号が与えられ、前記デジタル制御コードを出力する発振周波数制御部とを備えたことを特徴とするPLL周波数シンセサイザ。

【請求項10】

請求項9記載のPLL周波数シンセサイザにおいて、

前記位相比較器と前記発振周波数制御部との間に介在したデジタルループフィルタを更に備えたことを特徴とするPLL周波数シンセサイザ。

【請求項11】

請求項9記載のPLL周波数シンセサイザにおいて、

前記第1のクロック信号は、前記基準信号又は前記基準信号に同期し前記基準信号と周期が同じ信号であって、

前記第2のクロック信号は、前記発振信号と同じ周期で前記発振信号と所定の位相差を有する信号であって、

前記位相差情報が第1の所定値未満又は第1の所定値以下の場合には前記第2の発振信号位相情報を選択し、前記位相差情報が第2の所定値以上又は第2の所定値を超える場合には前記第2の発振信号位相情報に1を加えた値を選択し、前記位相差情報が前記第1の所定値以上又は前記第1の所定値を越え、かつ前記第2の所定値未満又は前記第2の所定値以下の場合には前記第1の発振信号位相情報を選択して出力することを特徴とするPLL周波数シンセサイザ。

【請求項12】

請求項11記載のPLL周波数シンセサイザにおいて、

前記第1のクロック信号は前記基準信号であって、

前記第2のクロック信号は、前記発振信号を反転させた信号であって、

前記第1の所定値は、前記基準信号の立ち上がりエッジと前記発振信号の立ち上がりエッジとの時間差を前記発振信号の1周期の時間で正規化した場合に0.25となる値であって、前記第2の所定値は、前記基準信号の立ち上がりエッジと前記発振信号の立ち上がりエッジとの時間差を前記発振信号の1周期の時間で正規化した場合に0.75となる値であるPLL周波数シンセサイザ。

【請求項13】

請求項9記載のPLL周波数シンセサイザにおいて、

前記第1のクロック信号は、前記基準信号又は前記基準信号に同期し前記基準信号と周期が同じ信号であって、

前記第2のクロック信号は、前記第1のクロック信号を所定時間遅延させた信号であって、

前記位相差情報が第1の所定値未満又は第1の所定値以下の場合には前記第2の発振信号位相情報から1を減じた値を選択し、前記位相差情報が第2の所定値以上又は第2の所定値を超える場合には前記第2の発振信号位相情報を選択し、前記位相差情報が前記第1の所定値以上又は前記第1の所定値を越え、かつ前記第2の所定値未満又は前記第2の所定値以下の場合には前記第1の発振信号位相情報を選択して出力することを特徴とするPLL周波数シンセサイザ。

【請求項14】

請求項13記載のPLL周波数シンセサイザにおいて、

前記第1のクロック信号は前記基準信号であって、

前記第2のクロック信号は、前記基準信号を前記発振信号のほぼ半周期時間遅延させた信号であって、

前記第1の所定値は、前記基準信号の立ち上がりエッジと前記発振信号の立ち上がりエッジとの時間差を前記発振信号の1周期の時間で正規化した場合に0.25となる値であって、前記第2の所定値は、前記基準信号の立ち上がりエッジと前記発振信号の立ち上がりエッジとの時間差を前記発振信号の1周期の時間で正規化した場合に0.75となる値であるPLL周波数シンセサイザ。

【請求項15】

請求項1〜14のいずれか1項に記載のPLL周波数シンセサイザを有する受信回路又は送信回路の少なくとも一方を備えた無線通信機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【公開番号】特開2012−60395(P2012−60395A)

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願番号】特願2010−201307(P2010−201307)

【出願日】平成22年9月8日(2010.9.8)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願日】平成22年9月8日(2010.9.8)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]