PLL回路、及び無線機

【課題】 位相誤差の小さい、発振信号の精度が高いPLL回路及び無線機を提供する。

【解決手段】 第一差動信号を生成する第一発振部と、前記第一差動信号を90度の位相差をもつ第二差動信号を生成する第二発振部と、を有する電圧制御発振器と、前記第一及び第二差動信号に基づく第三差動信号の位相と、基準信号の位相とを比較する位相比較器と、前記位相比較器の比較結果に基づいて、前記電圧制御発振器を制御する制御電圧を生成するループフィルタと、を具備することを特徴とするPLL回路。

【解決手段】 第一差動信号を生成する第一発振部と、前記第一差動信号を90度の位相差をもつ第二差動信号を生成する第二発振部と、を有する電圧制御発振器と、前記第一及び第二差動信号に基づく第三差動信号の位相と、基準信号の位相とを比較する位相比較器と、前記位相比較器の比較結果に基づいて、前記電圧制御発振器を制御する制御電圧を生成するループフィルタと、を具備することを特徴とするPLL回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、PLL回路及び無線機に関する。

【背景技術】

【0002】

無線機における直交変復調器の局部発振器に、PLL(Phase Locked Loop)回路を用いる方法が知られている。一般に、直交変復調器の局部発振器では、移相器を用いることで、PLL回路の出力信号及び該出力信号と90度の位相差をもつ信号を生成する。

【0003】

このように、90度の位相差をもつ局部発振信号を生成する場合、移相器を用いる必要がある。移相器の精度が悪いと局部発振器の位相誤差が大きくなるという問題があった。

【0004】

そこで、一対の電圧制御発振回路をクロスカップリングさせることで1つの電圧制御発振器で4相の発信信号(90度の位相差をもつ差動信号)を出力するQVCO(Quadrature voltage conMolled oscillator)を用いたPLL回路が提案されている(例えば、非特許文献1参照。)。

【0005】

非特許文献1に開示されるPLL回路は、発振器としてQVCOを用いることで、移相器を用いることなく、4相の発信信号を出力することができる。

【非特許文献1】IEEE Biomedical Circuits and Systems Conference, 2007. pp. 63−66

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、上述した非特許文献1に記載されるPLL回路では、QVCOから出力される4相の発振信号のうち1つを分周して、位相周波数比較器へフィードバックしていた。このように4相の出力信号のうちの1つ(ここでは、Q−の発振信号とする。)を分周器へ入力すると、分周器と接続された出力端子、すなわちQ−の発振信号を出力する出力端子Aの負荷条件と、分周器と接続されていない残りの発振信号の出力端子B〜Dの負荷条件が異なってしまう。

【0007】

従って、出力端子Aから出力される発振信号と、出力端子B〜Dから出力される発振信号との位相差、振幅差が大きくなる。すなわち、フィードバックされる信号と、実際の出力信号との差が大きくなることから、PLL回路から出力される発振信号が、所望の位相差とずれてしまうという問題が発生する。

【0008】

そこで、本発明は上記問題点を解決するためになされたものであり、位相誤差の小さい、すなわち発振信号の精度が高いPLL回路及び無線機の提供を目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するために、本発明のPLL回路は、第一差動信号を生成する第一発振部と、前記第一差動信号と90度の位相差をもつ第二差動信号を生成する第二発振部と、を有する電圧制御発振器と、前記第一及び第二差動信号に基づく第三差動信号の位相と、基準信号の位相とを比較する位相比較器と、前記位相比較器の比較結果に基づいて、前記電圧制御発振器を制御する制御電圧を生成するループフィルタと、を具備することを特徴とする。

【0010】

また、本発明の無線機は、無線信号を受信するアンテナと、前記無線信号を増幅し、増幅信号を生成する増幅器と、上述したPLL回路と、前記第一差動信号と前記増幅信号とを乗算し、第一受信信号を生成する第一ミキサ回路と、前記第二差動信号と前期増幅信号とを乗算し、第二受信信号を生成する第二ミキサ回路と、を備えることを特徴とする。

【発明の効果】

【0011】

本発明によると、位相誤差の小さい、すなわち発振信号の精度が高いPLL回路及び無線機を提供することができる。

【発明を実施するための最良の形態】

【0012】

以下、本発明の実施例を、図面を参照して説明する。

【実施例1】

【0013】

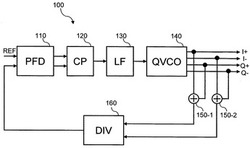

図1乃至図5を用いて本発明の第1の実施例を説明する。図1本実施例に係るPLL回路100のブロック図である。

【0014】

図1に示すPLL回路100は、位相比較器(PFD:Phase Frequency Detector)110と、チャージポンプ(CP:Charge pump)120と、ループフィルタ(LF:LooP Filter)130と、発振器(QVCO:Quadrature voltage conMolled oscillator)140と、加算器150−1,150−2と分周器(DIV:Divider)160と、を有している。

【0015】

位相比較器110は、図示しない基準信号発振器(TCXO)が出力する基準信号(REF)と、分周器160の出力する信号とを比較し、比較結果に基づいて後段のチャージポンプ120を制御するパルス信号を出力する機能を有する。図1に示す例では、位相比較器110は、基準信号(REF)と分周器160により分周された発振器140の発振信号との位相差情報(進みと遅れ・絶対量)に基づいてチャージポンプ120を制御するパルス信号を生成する。

【0016】

図2を用いて、チャージポンプ120の一例を説明する。チャージポンプ120は、電流源IC1,IC2、および各電流源IC1、IC2をオン・オフする電流制御スイッチSW1,SW2を有している。

【0017】

電流源IC1は、一端が電源と接続され、他端が電流源IC2,およびループフィルタ130に接続されており、ループフィルタ130に向けて電流を供給する機能を有する。また、電流源IC2は、一端が電流源IC1の他端およびループフィルタ130に接続され、他端がグランドに接続されており、ループフィルタ130から電流を吸い出す(引き出す)機能を有する。

【0018】

例えば、位相比較器110による位相比較の結果、発振器140の位相が進んでいる場合、位相比較器110は、スイッチSW1をオンとするような制御を行う。また、発振器140の位相が遅れている場合、位相比較器110は、スイッチSW2がオンとなるような制御を行う。すなわち、発振器140の位相が進んでおり、スイッチSW1がオンとなると、電流源IC1が動作し、チャージポンプ120全体としては制御電流を供給する動作を行う。また、発振器140の位相が遅れており、スイッチSW2がオンとなると、電流源IC2が動作し、チャージポンプ120全体としては、制御電流を吸い出す(引き出す)動作を行う。

【0019】

このようにチャージポンプ120は、位相比較器110の位相比較結果に基づき、発振器140に向けて正または負の制御電流信号を供給する(制御電流を供給する/引き出す)作用を有する。

【0020】

次に、図3を用いてループフィルタ130の一例を示す。図3のループフィルタ130は、直列接続された抵抗RおよびキャパシタCを備えており、チャージポンプ120が出力する制御電流信号を平滑化して発振器140の制御電圧信号を生成するローパスフィルタ(LPF)である。

【0021】

抵抗Rの一端はチャージポンプ120の出力と接続され、他端はキャパシタCの一端と接続されている。キャパシタCの他端はグランドと接続されている。

【0022】

ループフィルタ130は、チャージポンプ120から供給された正負の制御電流を制御電圧に変換し制御電圧信号を生成する。また、ループフィルタ130は、チャージポンプ120内のスイッチングノイズ、クロックノイズや熱雑音等を除去する役割も持つ。

【0023】

図4を用いて、発振器140の一例を説明する。図4に示す発振器140は、直角位相信号(I+,I−,Q+,Q−)を生成するQVCO(Quadrature voltage conMolled oscillator)と呼ばれる電圧制御発振器である。具体的には、発振器140は、I+,I−信号を出力する第一発振部I−VCOおよびQ+,Q−信号を出力する第二発振部Q−VCOを有している。

【0024】

第一発振部I−VCOは、第一出力端子P1,第二出力端子P2と、入力端子Vconと、インダクタLI1,LI2と、可変容量CI1,CI2と、nMOSトランジスタMI1〜MI4と、電流源ICIと、を備えている。

【0025】

インダクタLI1,LI2と、可変容量CI1,CI2と、が並列に接続されている。すなわちインダクタLI1は、一端が可変容量CI1の一端と接続されており、他端がインダクタLI2の一端および電源(Vdd)に接続されている。インダクタLI1,LI2と、可変容量CI1,CI2とで第一共振部を構成している。可変容量CI1の他端が、可変容量CI2の一端および入力端子Vconに接続されている。インダクタLI2の他端と可変容量CI2の他端とが接続されている。なお、入力端子Vconは、ループフィルタ130の出力端子に接続される。

【0026】

nMOSトランジスタMI1,MI3は、各ドレイン端子がインダクタLI1の一端および可変容量CI1の一端と接続しており、各ソース端子が電流源ICIの一端と接続されている。またnMOSトランジスタMI3のゲート端子は、後述する第二発振部Q−VCOの第四出力端子P4と接続されている。nMOSトランジスタMI1のゲート端子は、nMOSトランジスタMI2,MI4のドレイン端子、すなわちI−VCOの第二出力端子P2と接続されている。

【0027】

nMOSトランジスタMI2,MI4は、各ドレイン端子がインダクタLI2の一端および可変容量CI2の一端と接続しており、各ソース端子が電流源ICIの一端と接続されている。またnMOSトランジスタMI4のゲート端子は、後述する第二発振部Q−VCOの第三出力端子P3と接続されている。nMOSトランジスタMI2のゲート端子は、nMOSトランジスタMI1,MI3のドレイン端子、すなわちI−VCOの第一出力端子P1と接続されている。

【0028】

また、電流源ICIは、一端がnMOSトランジスタMI1〜MI4に接続されており、他端がグランドに接続されている。

【0029】

発振回路Q−VCOは、第三出力端子P3,第四出力端子P4と、入力端子Vconと、インダクタLQ1,LQ2と、可変容量CQ1,CQ2と、nMOSトランジスタMQ1〜MQ4と、電流源ICQと、を備えている。

【0030】

インダクタLQ1,LQ2と、可変容量CQ1,CQ2と、が並列に接続されている。すなわちインダクタLQ1は、一端が可変容量CQ1の一端と接続されており、他端がインダクタLQ2の一端および電源に接続されている。インダクタLQ1,LQ2と、可変容量CQ1,CQ2とで第二共振部を構成している。可変容量CQ1の他端が、可変容量CQ2の一端および入力端子Vconに接続されている。インダクタLQ2の他端と可変容量CQ2の他端とが接続されている。なお、入力端子Vconは、ループフィルタ130の出力端子に接続される。

【0031】

nMOSトランジスタMQ1,MQ3は、各ドレイン端子がインダクタLQ1の一端および可変容量CQ1の一端と接続しており、各ソース端子が電流源ICQの一端と接続されている。またnMOSトランジスタMQ3のゲート端子は、第一発振部I−VCOの第一出力端子P1と接続されている。nMOSトランジスタMQ1のゲート端子は、nMOSトランジスタMQ2,MQ4のドレイン端子、すなわちQ−VCOの第四出力端子P4と接続されている。

【0032】

nMOSトランジスタMQ2,MQ4は、各ドレイン端子がインダクタLQ2の一端および可変容量CQ2の一端と接続しており、各ソース端子が電流源ICQの一端と接続されている。またnMOSトランジスタMQ4のゲート端子は、第一発振部I−VCOの第二出力端子P2と接続されている。nMOSトランジスタMQ2のゲート端子は、nMOSトランジスタMQ1,MQ3のドレイン端子、すなわちQ−VCOの第三出力端子P3と接続されている。

【0033】

また、電流源ICQは、一端がnMOSトランジスタMQ1〜MQ4に接続されており、他端がグランドに接続されている。

【0034】

以下、第一発振部I−VCOの各構成要素の作用について説明する。第二発振部Q−VCOの各構成要素の作用は、第一発振部I−VCOとほぼ同じであるため説明を省略する。

【0035】

まず、第一発振部I−VCOでは、インダクタLI1,LI2と可変容量CI1,CI2とが並列に接続されており、これらの並列回路は、LC共振回路(第一共振部)として動作する。第一共振部は、インダクタLI1,LI2のインダクタンスや可変容量CI1,CI2の容量値によって決まる共振周波数の交流信号を発振する。この交流信号は、出力端子P1,P2から出力される。出力端子P1,P2から出力される交流信号は、互いに逆相の信号となっている。

【0036】

nMOSトランジスタMI1,MI2は、インダクタLI1,LI2,可変容量CI1,CI2で構成される第一共振部の負性抵抗として動作する。nMOSトランジスタMI1,MI2が、第一共振部での損失を補償することで、第一共振部の発振が継続する。

【0037】

ここで、発振器140では、第一発振部I−VCOの出力端子P1,P2が第二発振部Q−VCOのnMOSトランジスタMQ2,MQ4のゲート端子と接続されている。第二発振部Q−VCOの出力端子P3,P4が第一発振部I−VCOのnMOSトランジスタMI2,MI4のゲート端子と接続されている。すなわち、第一発振部I−VCOのnMOSトランジスタMI2,MI4のゲート端子には、それぞれQ−信号、Q+信号が印加される。第二発振部Q−VCOのnMOSトランジスタMQ2,MQ4のゲート端子には、それぞれI+信号、I−信号が印加される。

【0038】

このように、第一、第二発振部の出力端子及びトランジスタのゲート端子とをクロスカップリングすることで、第一発振部I−VCOの出力信号と第一発振部Q−VCOの出力信号との位相を90度ずらすことができる。すなわち、第一発振部I−VCOから出力される差動の発振信号(第一差動信号)I+、I−と、第二発振部Q−VCOから出力される差動の発振信号(第二差動信号)Q+、Q−との位相差が90度となる。例えば、図5に示すようなI+,I−,Q+,Q−の4相信号が、出力端子P1〜P4からそれぞれ出力される。

【0039】

図1に戻る。加算器150−1は、発振器140の出力端子P1,P3から出力されるI+信号およびQ+信号を加算して、加算信号を分周器へ出力する。加算器150−2は、発振器140の出力端子P2,P4から出力されるI−信号およびQ−信号を加算して、加算信号を分周器160へ出力する。

【0040】

図5に、加算器150−1,150−2の入力信号波形および出力信号波形を示す。図5に示すように、I+信号およびQ+信号を加算した加算信号と、I−信号およびQ−信号を加算した加算信号とは互いに逆相の信号となる。以後、I+信号およびQ+信号の加算結果を正相加算信号と称し、I−信号およびQ−信号を加算した結果を逆相加算信号と称する。

【0041】

分周器160は、加算器150−1,150−2から入力される加算信号を所定の分周比で分周して位相比較器110へ出力する。

【0042】

次に、本実施例にかかるPLL回路の動作を説明する。発振器140から出力される4相の発振信号(I+信号、I−信号、Q+信号、Q−信号)は、I+信号およびQ+信号が加算器150−1で加算され正相加算信号として、分周器160へと送られる。また、I−信号およびQ−信号は、加算器150−2で加算され、逆相加算信号として、分周器160へと送られる。なお、正相加算信号と逆相加算信号とをあわせて第三差動信号と称する。

【0043】

正相および逆相加算信号は、いずれも分周器160にて所定の分周比で分周される。この分周比は、比較対象となるTCXO(図示せず)の周波数に基づいて決定される。分周器160の出力である分周信号は、位相比較器110へと入力される。

【0044】

位相比較器110では、分周信号と、TCXO(図示せず)が出力する基準信号とが比較される。比較結果、分周信号の位相が基準信号より進んでいる、すなわち発振器140の発振信号の位相が所望の位相より進んでいる場合、位相比較器110は、チャージポンプ120のスイッチSW1をオンするための制御信号を出力する。一方、分周信号の位相が基準信号より遅れている、すなわち発振器140の発振信号の位相が所望の位相より遅れている場合、位相比較器110は、チャージポンプ120のスイッチSW2をオンとするための制御信号を出力する。

【0045】

この制御信号によって、チャージポンプ120のスイッチSW1またはスイッチSW2のいずれかがオンとなる。スイッチSW1がオンとなる(発振信号の位相が進んでいる)場合、電流源IC1が動作し、チャージポンプ120は、ループフィルタ130に制御電流を供給する。すなわち、チャージポンプ120は、ループフィルタ130に正の制御電流信号を供給する。スイッチSW2がオンとなる(発振信号の位相が遅れている)場合、電流源IC2が動作し、ループフィルタ130から制御電流を引き出す。すなわち、チャージポンプ120は、ループフィルタ130に負の制御電流信号を供給する。

【0046】

チャージポンプ120から供給される正または負の制御電流信号は、ループフィルタ130にて、平滑化され、制御電圧信号に変換されて、発振器140に供給される。

【0047】

制御電圧信号に応じて、発振器140の可変容量CI1,CI2,CQ1,CQ2の容量値が制御される。これにより、発振器140の発振周波数が制御され、所望の発振信号が得られる。

【0048】

以上のように第1の実施例によれば、発振器140から出力される4相の発振信号のうち、I+信号およびQ+信号を加算し、I−信号およびQ−信号を加算することで、発振器140の出力端子の負荷条件をほぼ同一とすることができ、発振信号の位相誤差、振幅誤差を小さくすることができる。

【0049】

例えば、4相の発振信号のうち、いずれか1つ(例えばI+信号)のみ分周器160にフィードバックする構成とした場合、I+信号の出力端子に発生する寄生容量(または寄生抵抗)の値が他の出力端子に発生する寄生容量(または寄生抵抗)の値と異なってしまう。このため、I+信号の位相・振幅値と、残りの3相の発振信号との位相・振幅値との間に差異が生じる。

【0050】

一方、本実施例にかかるPLL回路100では、4相すべての発振信号を分周器160にフィードバックする構成としている。そのため、発振器140の出力端子に発生する寄生容量(または寄生抵抗)の値を、ほぼ等しくすることができる。これにより、4相の発振信号の各位相・振幅値との間の差異を小さくできるため、発振信号を精度よく出力することができる。

【実施例2】

【0051】

次に、図6乃至図8を用いて本発明の第2の実施例を説明する。本実施例では、発振器240の発振信号(第一差動信号及び第二差動信号)を2乗した2乗信号(第三差動信号)を分周器へ出力している点で第1の実施例と異なる。

【0052】

図6は、本実施例にかかるPLL回路200のブロック図である。図6に示すPLL回路200の構成および動作は、加算器150−1,150−2を有していない点及び発振器240の構成を除き図1に示すPLL回路100と同様であるため、同一符号を付し、説明を省略する。

【0053】

発振器240は、図1の発振器140と同様に4相の発振信号(第一差動信号(I+,I−)、第二差動信号(Q+,Q−))を出力するとともに、I+信号またはI−信号の2乗信号Ic、Q+信号またはQ−の2乗信号Qcを出力する。

【0054】

以下、図7を用いて発振器240の詳細について説明する。図7に示す発振器240は、電流源CIIの一端に第五出力端子P5を、電流源CIQの一端に第六出力端子P6を設けている点を除き、図4に示す発振器140と同じ構成であるため、詳細な説明は省略する。

【0055】

発振器240は、第一発振部I−VCOの第五出力端子P5および第二発振部Q−VCOの出力端子P6を設けることで、発振信号の2倍の周波数をもつ2次高調波信号、すなわち2乗信号Ic,Qcを得る。

【0056】

図8に、各出力端子から出力される信号の波形を示す。第一出力端子P1から出力されるI+信号を正弦波とすると、第二出力端子P2からはI+信号と逆相の信号(I−信号)が出力される。また、第五出力端子P5からは、I+信号の2倍の周波数の信号、すなわちI+信号の2次高調波(2乗信号Ic)が出力される。なお、2乗信号Icは、I−信号の2次高調波信号でもある。

【0057】

第三出力端子P3からは、I+信号と90度位相がずれたQ+信号が出力される。第四出力端子P4からは、Q+信号と逆相の信号(Q−信号)が出力される。また、第五出力端子P6からは、Q+信号の2倍の周波数の信号、すなわちQ+信号の2次高調波(2乗信号Qc)が出力される。なお、2乗信号Qcは、Q−信号の2次高調波信号でもある。

【0058】

第五出力端子P5から出力される2乗信号Icは、第六出力端子P6から出力される2乗信号Qcと逆相の信号となる。従って、2乗信号Icおよび2乗信号Qcを第三差動信号と称する。

【0059】

本実施例では、発振器240の第一発振部I−VCO,第二発振部Q−VCOの電流源ICI,ICQの各一端に出力端子を設け、2乗信号Ic,Qcを分周器160へ入力する。なお、分周器160へ入力する信号の周波数が、図1のPLL回路100と異なるが、この場合は、分周器160の分周比を調整することで、図1のPLL回路100の分周信号と同じ周波数(位相)の分周信号が得られる。

【0060】

本実施例では、第一及び第二発振部が有するトランジスタMI1〜MI4,MQ1〜MQ4のソース端子から2乗信号を取り出す場合について示しているが、インダクタLI1,LI2の接続点から2乗信号Icを、インダクタLQ1,LQ2の接続点から2乗信号Qcを取り出すことができる。

【0061】

以上のように第2の実施例によれば、第1の実施例と同様の効果が得られるとともに、発振器240に新たな出力端子を設けることで、第1の実施例で必要であった加算器を省略することが可能となり、回路面積を削減することができる。また、発振信号の出力端子と加算器を接続していないので、発振信号の出力端子に発生する寄生容量(寄生抵抗)の値を小さくすることができる。

【0062】

なお、本実施例では、分周器へ出力する信号を2次高調波信号である2乗信号Ic、Qcとしたが、高次高調波信号であれば2次高調波信号に限られない。第五出力端子、第六出力端子には、2次高調波信号以外にも高次高調波信号が含まれている。フィルタを用いることで高次高調波信号を取り出すことができるので、2次高調波信号の代わりに2次以外の高次高調波信号を分周器へ出力してもよいが、2次高調波信号の信号振幅は、他の高次高調波信号の信号振幅よりも大きいため、本実施例では、2次高調波信号を分周器へ出力する例を示している。

【実施例3】

【0063】

次に、図9を用いて第3の実施例について説明する。本実施例では、図1に示すPLL回路を用いた無線機300について説明する。本実施例にかかる無線機300は、アンテナ311,312と、バンドパスフィルタ321,322と、低雑音増幅器331と、パワーアンプ332と、ミキサ341〜344と、ローパスフィルタ351〜354とPLL回路100とを有している。

【0064】

本実施例にかかる無線機300の受信回路について説明する。

【0065】

アンテナ311は、無線機300の通信相手が送信する無線信号を受信する。バンドパスフィルタ321は、アンテナ311が受信した無線信号から所望の帯域のRF信号を抽出する。

【0066】

低雑音増幅器331は、バンドパスフィルタ321で抽出されたRF信号を増幅する。ミキサ341は、低雑音僧服器331で増幅された増幅信号と、PLL回路100から出力されるI+信号およびI−信号とを乗算し、BB(ベースバンド)信号(第一受信信号)を生成する。ミキサ342は、低雑音僧服器331で増幅された増幅信号と、PLL回路100から出力されるQ+信号およびQ−信号を乗算し、BB(ベースバンド)信号(第二受信信号)を生成する。

【0067】

ローパスフィルタ351,352は、ミキサ341,342で生成されたBB信号からそれぞれ所望の帯域の信号を抽出し、I−ch信号およびQ−ch信号を生成する。このI−ch信号、Q−ch信号に対して、それぞれA/D変換、復調等の信号処理が行われ、所望の送信データに変換される。この後段の信号処理については、説明を省略する。

【0068】

続いて、無線機300の送信回路について説明する。図示しないが、無線機300の通信相手に送信する送信データは、変調、D/A変換等の信号処理が行われ、I−ch信号(第一送信信号)、Q−ch信号(第二送信信号)に変換される。

【0069】

ローパスフィルタ353,354は、I−ch信号、Q−ch信号から所望帯域の信号を抽出し、後段のミキサ343,344に抽出した信号を出力する。ミキサ343は、ローパスフィルタ353の出力信号と、PLL回路100から出力されるI+,I−信号とを乗算し第一蒸散信号を生成する。ミキサ344は、ローパスフィルタ354の出力信号と、PLL回路100から出力されるQ+,Q−信号とを乗算し第二乗算信号を生成する。

【0070】

パワーアンプ332は、第一及び第二乗算信号を加算した加算信号を増幅し、増幅信号をバンドパスフィルタ322に出力する。バンドパスフィルタ322は、増幅信号から所望の帯域幅の信号を抽出し、抽出した信号をアンテナ312を介して送信する。

【0071】

PLL回路100は、図1に示すPLL回路100と同様の構成であるため、説明を省略する。

【0072】

以上のように第3の実施例によれば、無線機のPLL回路として、図1に示すPLL回路100を用いることで、無線機に必要な移相器を省略するとともに、無線信号を精度よく復調することが可能となる。

【0073】

PLL回路100は、4相の発振信号(I+,I−,Q+,Q−信号)を出力することができるため、発振信号をさらに90度移相させる必要がなく移相器を省略することができる。また、4相の発振信号の各出力端子に発生する負荷条件をほぼ均一とすることができるため、各4相の発振信号の位相誤差、振幅誤差を小さくすることができる。これにより、I−ch信号、Q−ch信号の位相差を90度に近づけることができ、無線信号の復調精度を向上させることができる。

【0074】

なお、ここでは、図1のPLL回路100をダイレクトコンバージョン方式の無線機に応用した例を示したが、スーパーヘテロダイン方式など、ダイレクトコンバージョン方式以外の無線機に応用することも可能である。

【実施例4】

【0075】

次に、図10を用いて第4の実施例について説明する。本実施例では、図6に示すPLL回路200を用いた無線機400について説明する。

【0076】

本実施例にかかる無線機400は、アンテナ410と、バンドパスフィルタ420と、低雑音増幅器430とミキサ440,451,452と、ローパスフィルタ461,462とPLL回路200とを有している。

【0077】

アンテナ410は、無線機400の通信相手が送信する無線信号を受信する。バンドパスフィルタ420は、アンテナ410が受信した無線信号から所望の帯域のRF信号を抽出する。低雑音増幅器430は、バンドパスフィルタ420で抽出されたRF信号を増幅する。

【0078】

ミキサ440は、低雑音僧服器430で増幅された増幅信号と、PLL回路200から出力される2乗信号Ic,Qc(第三差動信号)とを乗算する。これによりミキサ440はIF信号を生成する。

【0079】

ミキサ451は、IF信号と、PLL回路200から出力されるI+信号およびI−信号とを乗算し、BB(ベースバンド)信号(第一受信信号)を生成する。ミキサ452は、IF信号と、PLL回路200から出力されるQ+信号およびQ−信号を乗算し、BB(ベースバンド)信号(第二受信信号)を生成する。

【0080】

ローパスフィルタ461,462は、ミキサ451,452で生成されたBB信号からそれぞれ所望の帯域の信号を抽出し、I−ch信号およびQ−ch信号を生成する。このI−ch信号、Q−ch信号に対して、それぞれA/D変換、復調等の信号処理が行われ、所望の送信データに変換される。この後段の信号処理については、説明を省略する。

【0081】

PLL回路200は、図6に示すPLL回路200とほぼ同様の構成であるが、分周器160に入力する2乗信号Ic,Qcをミキサ440にも出力している点が異なる。図8に示すように、2乗信号Ic,Qcは、I+,I−,Q+,Q−信号(PLL回路の出力である発振信号)の2倍の周波数をもつ差動信号である。したがって、このIc信号およびQc信号をミキサ440へと出力することで、1つのPLL回路で2段階のダウンコンバージョンを実現する。

【0082】

具体的に、60GHzの無線信号を受信する場合の例を説明する。この場合、PLL回路200が、20GHzの発振信号を出力すると、2乗信号Ic,Qcは、40GHzの信号となる。ミキサ440で40GHzの2乗信号Ic,Qcと60GHzの無線信号とを乗算することで、20GHzのIF信号を得る。ミキサ451,452で、20GHzのIF信号と、PLL回路200の出力である20GHzの発振信号(I+,I−,Q+,Q−信号)とを乗算すると1GHzのBB信号が得られる。

【0083】

以上のように、第4の実施例では、無線機のPLL回路として、図6に示すPLL回路100を用いることで、第3の実施例と同様の効果が得られるとともに、2段階のダウンコンバージョンを行う無線方式において、複数の発振器が不要となり、無線機の回路規模を小さくすることができる。また、発振器が1つの無線機も知られているが、この場合、複数の異なる発振信号を得るために、分周器を用いる必要があるが、本実施例の無線機ではこれも不要となる。

【0084】

なお、ここでは、図6のPLL回路200を2段階のダウンコンバージョンを行う無線機の受信回路に応用した例を示したが、2段階のアップコンバージョンを行う送信回路に応用することも可能である。また、図1のPLL回路100の発振器140から、図7に示す発振器240と同様にして2次高調波信号(2乗信号)を取り出すことで、図1のPLL回路を本実施例の無線機に応用することも可能である。

【0085】

なお、本実施例の無線機に限らず、2段階のダウンコンバージョンを行う無線機であれば同様に、第1、第2の実施例にかかるPLL回路を本実施例と同様に応用することも可能である。

【0086】

なお、本発明は上記実施例そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施例に開示されている複数の構成要素の適宜な組み合わせにより、種々の発明を形成できる。例えば、実施例に示される全構成要素から幾つかの構成要素を削除してもよい。さらに、異なる実施例にわたる構成要素を適宜組み合わせてもよい。

【図面の簡単な説明】

【0087】

【図1】本発明の第1の実施例にかかるPLL回路を示すブロック図。

【図2】本発明の第1の実施例にかかるチャージポンプ120を示す図。

【図3】本発明の第1の実施例にかかるループフィルタ130を示す図。

【図4】本発明の第1の実施例にかかる発振器140を示す図。

【図5】本発明の第1の実施例にかかる加算器150−1,150−2の入出力信号の波形を示す図。

【図6】本発明の第2の実施例にかかるPLL回路を示すブロック図。

【図7】本発明の第2の実施例にかかる発振器240を示す図。

【図8】本発明の第2の実施例にかかる発振器240の出力信号波形を示す図。

【図9】本発明の第3の実施例にかかる無線機を示すブロック図。

【図10】本発明の第4の実施例にかかる無線機を示すブロック図。

【符号の説明】

【0088】

100,200・・・PLL回路

110・・・位相比較器(PFD)

120・・・チャージポンプ(CP)

130・・・ループフィルタ(LF)

140,240・・・発振器(QVCO)

150・・・加算器

160・・・分周器(DIV)

311,312,410・・・アンテナ

321,322,420・・・バンドパスフィルタ

331,430・・・低雑音増幅器

332・・・パワーアンプ

341〜344,440,451,452・・・ミキサ

351〜354,461,462・・・ローパスフィルタ

【技術分野】

【0001】

本発明は、PLL回路及び無線機に関する。

【背景技術】

【0002】

無線機における直交変復調器の局部発振器に、PLL(Phase Locked Loop)回路を用いる方法が知られている。一般に、直交変復調器の局部発振器では、移相器を用いることで、PLL回路の出力信号及び該出力信号と90度の位相差をもつ信号を生成する。

【0003】

このように、90度の位相差をもつ局部発振信号を生成する場合、移相器を用いる必要がある。移相器の精度が悪いと局部発振器の位相誤差が大きくなるという問題があった。

【0004】

そこで、一対の電圧制御発振回路をクロスカップリングさせることで1つの電圧制御発振器で4相の発信信号(90度の位相差をもつ差動信号)を出力するQVCO(Quadrature voltage conMolled oscillator)を用いたPLL回路が提案されている(例えば、非特許文献1参照。)。

【0005】

非特許文献1に開示されるPLL回路は、発振器としてQVCOを用いることで、移相器を用いることなく、4相の発信信号を出力することができる。

【非特許文献1】IEEE Biomedical Circuits and Systems Conference, 2007. pp. 63−66

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、上述した非特許文献1に記載されるPLL回路では、QVCOから出力される4相の発振信号のうち1つを分周して、位相周波数比較器へフィードバックしていた。このように4相の出力信号のうちの1つ(ここでは、Q−の発振信号とする。)を分周器へ入力すると、分周器と接続された出力端子、すなわちQ−の発振信号を出力する出力端子Aの負荷条件と、分周器と接続されていない残りの発振信号の出力端子B〜Dの負荷条件が異なってしまう。

【0007】

従って、出力端子Aから出力される発振信号と、出力端子B〜Dから出力される発振信号との位相差、振幅差が大きくなる。すなわち、フィードバックされる信号と、実際の出力信号との差が大きくなることから、PLL回路から出力される発振信号が、所望の位相差とずれてしまうという問題が発生する。

【0008】

そこで、本発明は上記問題点を解決するためになされたものであり、位相誤差の小さい、すなわち発振信号の精度が高いPLL回路及び無線機の提供を目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するために、本発明のPLL回路は、第一差動信号を生成する第一発振部と、前記第一差動信号と90度の位相差をもつ第二差動信号を生成する第二発振部と、を有する電圧制御発振器と、前記第一及び第二差動信号に基づく第三差動信号の位相と、基準信号の位相とを比較する位相比較器と、前記位相比較器の比較結果に基づいて、前記電圧制御発振器を制御する制御電圧を生成するループフィルタと、を具備することを特徴とする。

【0010】

また、本発明の無線機は、無線信号を受信するアンテナと、前記無線信号を増幅し、増幅信号を生成する増幅器と、上述したPLL回路と、前記第一差動信号と前記増幅信号とを乗算し、第一受信信号を生成する第一ミキサ回路と、前記第二差動信号と前期増幅信号とを乗算し、第二受信信号を生成する第二ミキサ回路と、を備えることを特徴とする。

【発明の効果】

【0011】

本発明によると、位相誤差の小さい、すなわち発振信号の精度が高いPLL回路及び無線機を提供することができる。

【発明を実施するための最良の形態】

【0012】

以下、本発明の実施例を、図面を参照して説明する。

【実施例1】

【0013】

図1乃至図5を用いて本発明の第1の実施例を説明する。図1本実施例に係るPLL回路100のブロック図である。

【0014】

図1に示すPLL回路100は、位相比較器(PFD:Phase Frequency Detector)110と、チャージポンプ(CP:Charge pump)120と、ループフィルタ(LF:LooP Filter)130と、発振器(QVCO:Quadrature voltage conMolled oscillator)140と、加算器150−1,150−2と分周器(DIV:Divider)160と、を有している。

【0015】

位相比較器110は、図示しない基準信号発振器(TCXO)が出力する基準信号(REF)と、分周器160の出力する信号とを比較し、比較結果に基づいて後段のチャージポンプ120を制御するパルス信号を出力する機能を有する。図1に示す例では、位相比較器110は、基準信号(REF)と分周器160により分周された発振器140の発振信号との位相差情報(進みと遅れ・絶対量)に基づいてチャージポンプ120を制御するパルス信号を生成する。

【0016】

図2を用いて、チャージポンプ120の一例を説明する。チャージポンプ120は、電流源IC1,IC2、および各電流源IC1、IC2をオン・オフする電流制御スイッチSW1,SW2を有している。

【0017】

電流源IC1は、一端が電源と接続され、他端が電流源IC2,およびループフィルタ130に接続されており、ループフィルタ130に向けて電流を供給する機能を有する。また、電流源IC2は、一端が電流源IC1の他端およびループフィルタ130に接続され、他端がグランドに接続されており、ループフィルタ130から電流を吸い出す(引き出す)機能を有する。

【0018】

例えば、位相比較器110による位相比較の結果、発振器140の位相が進んでいる場合、位相比較器110は、スイッチSW1をオンとするような制御を行う。また、発振器140の位相が遅れている場合、位相比較器110は、スイッチSW2がオンとなるような制御を行う。すなわち、発振器140の位相が進んでおり、スイッチSW1がオンとなると、電流源IC1が動作し、チャージポンプ120全体としては制御電流を供給する動作を行う。また、発振器140の位相が遅れており、スイッチSW2がオンとなると、電流源IC2が動作し、チャージポンプ120全体としては、制御電流を吸い出す(引き出す)動作を行う。

【0019】

このようにチャージポンプ120は、位相比較器110の位相比較結果に基づき、発振器140に向けて正または負の制御電流信号を供給する(制御電流を供給する/引き出す)作用を有する。

【0020】

次に、図3を用いてループフィルタ130の一例を示す。図3のループフィルタ130は、直列接続された抵抗RおよびキャパシタCを備えており、チャージポンプ120が出力する制御電流信号を平滑化して発振器140の制御電圧信号を生成するローパスフィルタ(LPF)である。

【0021】

抵抗Rの一端はチャージポンプ120の出力と接続され、他端はキャパシタCの一端と接続されている。キャパシタCの他端はグランドと接続されている。

【0022】

ループフィルタ130は、チャージポンプ120から供給された正負の制御電流を制御電圧に変換し制御電圧信号を生成する。また、ループフィルタ130は、チャージポンプ120内のスイッチングノイズ、クロックノイズや熱雑音等を除去する役割も持つ。

【0023】

図4を用いて、発振器140の一例を説明する。図4に示す発振器140は、直角位相信号(I+,I−,Q+,Q−)を生成するQVCO(Quadrature voltage conMolled oscillator)と呼ばれる電圧制御発振器である。具体的には、発振器140は、I+,I−信号を出力する第一発振部I−VCOおよびQ+,Q−信号を出力する第二発振部Q−VCOを有している。

【0024】

第一発振部I−VCOは、第一出力端子P1,第二出力端子P2と、入力端子Vconと、インダクタLI1,LI2と、可変容量CI1,CI2と、nMOSトランジスタMI1〜MI4と、電流源ICIと、を備えている。

【0025】

インダクタLI1,LI2と、可変容量CI1,CI2と、が並列に接続されている。すなわちインダクタLI1は、一端が可変容量CI1の一端と接続されており、他端がインダクタLI2の一端および電源(Vdd)に接続されている。インダクタLI1,LI2と、可変容量CI1,CI2とで第一共振部を構成している。可変容量CI1の他端が、可変容量CI2の一端および入力端子Vconに接続されている。インダクタLI2の他端と可変容量CI2の他端とが接続されている。なお、入力端子Vconは、ループフィルタ130の出力端子に接続される。

【0026】

nMOSトランジスタMI1,MI3は、各ドレイン端子がインダクタLI1の一端および可変容量CI1の一端と接続しており、各ソース端子が電流源ICIの一端と接続されている。またnMOSトランジスタMI3のゲート端子は、後述する第二発振部Q−VCOの第四出力端子P4と接続されている。nMOSトランジスタMI1のゲート端子は、nMOSトランジスタMI2,MI4のドレイン端子、すなわちI−VCOの第二出力端子P2と接続されている。

【0027】

nMOSトランジスタMI2,MI4は、各ドレイン端子がインダクタLI2の一端および可変容量CI2の一端と接続しており、各ソース端子が電流源ICIの一端と接続されている。またnMOSトランジスタMI4のゲート端子は、後述する第二発振部Q−VCOの第三出力端子P3と接続されている。nMOSトランジスタMI2のゲート端子は、nMOSトランジスタMI1,MI3のドレイン端子、すなわちI−VCOの第一出力端子P1と接続されている。

【0028】

また、電流源ICIは、一端がnMOSトランジスタMI1〜MI4に接続されており、他端がグランドに接続されている。

【0029】

発振回路Q−VCOは、第三出力端子P3,第四出力端子P4と、入力端子Vconと、インダクタLQ1,LQ2と、可変容量CQ1,CQ2と、nMOSトランジスタMQ1〜MQ4と、電流源ICQと、を備えている。

【0030】

インダクタLQ1,LQ2と、可変容量CQ1,CQ2と、が並列に接続されている。すなわちインダクタLQ1は、一端が可変容量CQ1の一端と接続されており、他端がインダクタLQ2の一端および電源に接続されている。インダクタLQ1,LQ2と、可変容量CQ1,CQ2とで第二共振部を構成している。可変容量CQ1の他端が、可変容量CQ2の一端および入力端子Vconに接続されている。インダクタLQ2の他端と可変容量CQ2の他端とが接続されている。なお、入力端子Vconは、ループフィルタ130の出力端子に接続される。

【0031】

nMOSトランジスタMQ1,MQ3は、各ドレイン端子がインダクタLQ1の一端および可変容量CQ1の一端と接続しており、各ソース端子が電流源ICQの一端と接続されている。またnMOSトランジスタMQ3のゲート端子は、第一発振部I−VCOの第一出力端子P1と接続されている。nMOSトランジスタMQ1のゲート端子は、nMOSトランジスタMQ2,MQ4のドレイン端子、すなわちQ−VCOの第四出力端子P4と接続されている。

【0032】

nMOSトランジスタMQ2,MQ4は、各ドレイン端子がインダクタLQ2の一端および可変容量CQ2の一端と接続しており、各ソース端子が電流源ICQの一端と接続されている。またnMOSトランジスタMQ4のゲート端子は、第一発振部I−VCOの第二出力端子P2と接続されている。nMOSトランジスタMQ2のゲート端子は、nMOSトランジスタMQ1,MQ3のドレイン端子、すなわちQ−VCOの第三出力端子P3と接続されている。

【0033】

また、電流源ICQは、一端がnMOSトランジスタMQ1〜MQ4に接続されており、他端がグランドに接続されている。

【0034】

以下、第一発振部I−VCOの各構成要素の作用について説明する。第二発振部Q−VCOの各構成要素の作用は、第一発振部I−VCOとほぼ同じであるため説明を省略する。

【0035】

まず、第一発振部I−VCOでは、インダクタLI1,LI2と可変容量CI1,CI2とが並列に接続されており、これらの並列回路は、LC共振回路(第一共振部)として動作する。第一共振部は、インダクタLI1,LI2のインダクタンスや可変容量CI1,CI2の容量値によって決まる共振周波数の交流信号を発振する。この交流信号は、出力端子P1,P2から出力される。出力端子P1,P2から出力される交流信号は、互いに逆相の信号となっている。

【0036】

nMOSトランジスタMI1,MI2は、インダクタLI1,LI2,可変容量CI1,CI2で構成される第一共振部の負性抵抗として動作する。nMOSトランジスタMI1,MI2が、第一共振部での損失を補償することで、第一共振部の発振が継続する。

【0037】

ここで、発振器140では、第一発振部I−VCOの出力端子P1,P2が第二発振部Q−VCOのnMOSトランジスタMQ2,MQ4のゲート端子と接続されている。第二発振部Q−VCOの出力端子P3,P4が第一発振部I−VCOのnMOSトランジスタMI2,MI4のゲート端子と接続されている。すなわち、第一発振部I−VCOのnMOSトランジスタMI2,MI4のゲート端子には、それぞれQ−信号、Q+信号が印加される。第二発振部Q−VCOのnMOSトランジスタMQ2,MQ4のゲート端子には、それぞれI+信号、I−信号が印加される。

【0038】

このように、第一、第二発振部の出力端子及びトランジスタのゲート端子とをクロスカップリングすることで、第一発振部I−VCOの出力信号と第一発振部Q−VCOの出力信号との位相を90度ずらすことができる。すなわち、第一発振部I−VCOから出力される差動の発振信号(第一差動信号)I+、I−と、第二発振部Q−VCOから出力される差動の発振信号(第二差動信号)Q+、Q−との位相差が90度となる。例えば、図5に示すようなI+,I−,Q+,Q−の4相信号が、出力端子P1〜P4からそれぞれ出力される。

【0039】

図1に戻る。加算器150−1は、発振器140の出力端子P1,P3から出力されるI+信号およびQ+信号を加算して、加算信号を分周器へ出力する。加算器150−2は、発振器140の出力端子P2,P4から出力されるI−信号およびQ−信号を加算して、加算信号を分周器160へ出力する。

【0040】

図5に、加算器150−1,150−2の入力信号波形および出力信号波形を示す。図5に示すように、I+信号およびQ+信号を加算した加算信号と、I−信号およびQ−信号を加算した加算信号とは互いに逆相の信号となる。以後、I+信号およびQ+信号の加算結果を正相加算信号と称し、I−信号およびQ−信号を加算した結果を逆相加算信号と称する。

【0041】

分周器160は、加算器150−1,150−2から入力される加算信号を所定の分周比で分周して位相比較器110へ出力する。

【0042】

次に、本実施例にかかるPLL回路の動作を説明する。発振器140から出力される4相の発振信号(I+信号、I−信号、Q+信号、Q−信号)は、I+信号およびQ+信号が加算器150−1で加算され正相加算信号として、分周器160へと送られる。また、I−信号およびQ−信号は、加算器150−2で加算され、逆相加算信号として、分周器160へと送られる。なお、正相加算信号と逆相加算信号とをあわせて第三差動信号と称する。

【0043】

正相および逆相加算信号は、いずれも分周器160にて所定の分周比で分周される。この分周比は、比較対象となるTCXO(図示せず)の周波数に基づいて決定される。分周器160の出力である分周信号は、位相比較器110へと入力される。

【0044】

位相比較器110では、分周信号と、TCXO(図示せず)が出力する基準信号とが比較される。比較結果、分周信号の位相が基準信号より進んでいる、すなわち発振器140の発振信号の位相が所望の位相より進んでいる場合、位相比較器110は、チャージポンプ120のスイッチSW1をオンするための制御信号を出力する。一方、分周信号の位相が基準信号より遅れている、すなわち発振器140の発振信号の位相が所望の位相より遅れている場合、位相比較器110は、チャージポンプ120のスイッチSW2をオンとするための制御信号を出力する。

【0045】

この制御信号によって、チャージポンプ120のスイッチSW1またはスイッチSW2のいずれかがオンとなる。スイッチSW1がオンとなる(発振信号の位相が進んでいる)場合、電流源IC1が動作し、チャージポンプ120は、ループフィルタ130に制御電流を供給する。すなわち、チャージポンプ120は、ループフィルタ130に正の制御電流信号を供給する。スイッチSW2がオンとなる(発振信号の位相が遅れている)場合、電流源IC2が動作し、ループフィルタ130から制御電流を引き出す。すなわち、チャージポンプ120は、ループフィルタ130に負の制御電流信号を供給する。

【0046】

チャージポンプ120から供給される正または負の制御電流信号は、ループフィルタ130にて、平滑化され、制御電圧信号に変換されて、発振器140に供給される。

【0047】

制御電圧信号に応じて、発振器140の可変容量CI1,CI2,CQ1,CQ2の容量値が制御される。これにより、発振器140の発振周波数が制御され、所望の発振信号が得られる。

【0048】

以上のように第1の実施例によれば、発振器140から出力される4相の発振信号のうち、I+信号およびQ+信号を加算し、I−信号およびQ−信号を加算することで、発振器140の出力端子の負荷条件をほぼ同一とすることができ、発振信号の位相誤差、振幅誤差を小さくすることができる。

【0049】

例えば、4相の発振信号のうち、いずれか1つ(例えばI+信号)のみ分周器160にフィードバックする構成とした場合、I+信号の出力端子に発生する寄生容量(または寄生抵抗)の値が他の出力端子に発生する寄生容量(または寄生抵抗)の値と異なってしまう。このため、I+信号の位相・振幅値と、残りの3相の発振信号との位相・振幅値との間に差異が生じる。

【0050】

一方、本実施例にかかるPLL回路100では、4相すべての発振信号を分周器160にフィードバックする構成としている。そのため、発振器140の出力端子に発生する寄生容量(または寄生抵抗)の値を、ほぼ等しくすることができる。これにより、4相の発振信号の各位相・振幅値との間の差異を小さくできるため、発振信号を精度よく出力することができる。

【実施例2】

【0051】

次に、図6乃至図8を用いて本発明の第2の実施例を説明する。本実施例では、発振器240の発振信号(第一差動信号及び第二差動信号)を2乗した2乗信号(第三差動信号)を分周器へ出力している点で第1の実施例と異なる。

【0052】

図6は、本実施例にかかるPLL回路200のブロック図である。図6に示すPLL回路200の構成および動作は、加算器150−1,150−2を有していない点及び発振器240の構成を除き図1に示すPLL回路100と同様であるため、同一符号を付し、説明を省略する。

【0053】

発振器240は、図1の発振器140と同様に4相の発振信号(第一差動信号(I+,I−)、第二差動信号(Q+,Q−))を出力するとともに、I+信号またはI−信号の2乗信号Ic、Q+信号またはQ−の2乗信号Qcを出力する。

【0054】

以下、図7を用いて発振器240の詳細について説明する。図7に示す発振器240は、電流源CIIの一端に第五出力端子P5を、電流源CIQの一端に第六出力端子P6を設けている点を除き、図4に示す発振器140と同じ構成であるため、詳細な説明は省略する。

【0055】

発振器240は、第一発振部I−VCOの第五出力端子P5および第二発振部Q−VCOの出力端子P6を設けることで、発振信号の2倍の周波数をもつ2次高調波信号、すなわち2乗信号Ic,Qcを得る。

【0056】

図8に、各出力端子から出力される信号の波形を示す。第一出力端子P1から出力されるI+信号を正弦波とすると、第二出力端子P2からはI+信号と逆相の信号(I−信号)が出力される。また、第五出力端子P5からは、I+信号の2倍の周波数の信号、すなわちI+信号の2次高調波(2乗信号Ic)が出力される。なお、2乗信号Icは、I−信号の2次高調波信号でもある。

【0057】

第三出力端子P3からは、I+信号と90度位相がずれたQ+信号が出力される。第四出力端子P4からは、Q+信号と逆相の信号(Q−信号)が出力される。また、第五出力端子P6からは、Q+信号の2倍の周波数の信号、すなわちQ+信号の2次高調波(2乗信号Qc)が出力される。なお、2乗信号Qcは、Q−信号の2次高調波信号でもある。

【0058】

第五出力端子P5から出力される2乗信号Icは、第六出力端子P6から出力される2乗信号Qcと逆相の信号となる。従って、2乗信号Icおよび2乗信号Qcを第三差動信号と称する。

【0059】

本実施例では、発振器240の第一発振部I−VCO,第二発振部Q−VCOの電流源ICI,ICQの各一端に出力端子を設け、2乗信号Ic,Qcを分周器160へ入力する。なお、分周器160へ入力する信号の周波数が、図1のPLL回路100と異なるが、この場合は、分周器160の分周比を調整することで、図1のPLL回路100の分周信号と同じ周波数(位相)の分周信号が得られる。

【0060】

本実施例では、第一及び第二発振部が有するトランジスタMI1〜MI4,MQ1〜MQ4のソース端子から2乗信号を取り出す場合について示しているが、インダクタLI1,LI2の接続点から2乗信号Icを、インダクタLQ1,LQ2の接続点から2乗信号Qcを取り出すことができる。

【0061】

以上のように第2の実施例によれば、第1の実施例と同様の効果が得られるとともに、発振器240に新たな出力端子を設けることで、第1の実施例で必要であった加算器を省略することが可能となり、回路面積を削減することができる。また、発振信号の出力端子と加算器を接続していないので、発振信号の出力端子に発生する寄生容量(寄生抵抗)の値を小さくすることができる。

【0062】

なお、本実施例では、分周器へ出力する信号を2次高調波信号である2乗信号Ic、Qcとしたが、高次高調波信号であれば2次高調波信号に限られない。第五出力端子、第六出力端子には、2次高調波信号以外にも高次高調波信号が含まれている。フィルタを用いることで高次高調波信号を取り出すことができるので、2次高調波信号の代わりに2次以外の高次高調波信号を分周器へ出力してもよいが、2次高調波信号の信号振幅は、他の高次高調波信号の信号振幅よりも大きいため、本実施例では、2次高調波信号を分周器へ出力する例を示している。

【実施例3】

【0063】

次に、図9を用いて第3の実施例について説明する。本実施例では、図1に示すPLL回路を用いた無線機300について説明する。本実施例にかかる無線機300は、アンテナ311,312と、バンドパスフィルタ321,322と、低雑音増幅器331と、パワーアンプ332と、ミキサ341〜344と、ローパスフィルタ351〜354とPLL回路100とを有している。

【0064】

本実施例にかかる無線機300の受信回路について説明する。

【0065】

アンテナ311は、無線機300の通信相手が送信する無線信号を受信する。バンドパスフィルタ321は、アンテナ311が受信した無線信号から所望の帯域のRF信号を抽出する。

【0066】

低雑音増幅器331は、バンドパスフィルタ321で抽出されたRF信号を増幅する。ミキサ341は、低雑音僧服器331で増幅された増幅信号と、PLL回路100から出力されるI+信号およびI−信号とを乗算し、BB(ベースバンド)信号(第一受信信号)を生成する。ミキサ342は、低雑音僧服器331で増幅された増幅信号と、PLL回路100から出力されるQ+信号およびQ−信号を乗算し、BB(ベースバンド)信号(第二受信信号)を生成する。

【0067】

ローパスフィルタ351,352は、ミキサ341,342で生成されたBB信号からそれぞれ所望の帯域の信号を抽出し、I−ch信号およびQ−ch信号を生成する。このI−ch信号、Q−ch信号に対して、それぞれA/D変換、復調等の信号処理が行われ、所望の送信データに変換される。この後段の信号処理については、説明を省略する。

【0068】

続いて、無線機300の送信回路について説明する。図示しないが、無線機300の通信相手に送信する送信データは、変調、D/A変換等の信号処理が行われ、I−ch信号(第一送信信号)、Q−ch信号(第二送信信号)に変換される。

【0069】

ローパスフィルタ353,354は、I−ch信号、Q−ch信号から所望帯域の信号を抽出し、後段のミキサ343,344に抽出した信号を出力する。ミキサ343は、ローパスフィルタ353の出力信号と、PLL回路100から出力されるI+,I−信号とを乗算し第一蒸散信号を生成する。ミキサ344は、ローパスフィルタ354の出力信号と、PLL回路100から出力されるQ+,Q−信号とを乗算し第二乗算信号を生成する。

【0070】

パワーアンプ332は、第一及び第二乗算信号を加算した加算信号を増幅し、増幅信号をバンドパスフィルタ322に出力する。バンドパスフィルタ322は、増幅信号から所望の帯域幅の信号を抽出し、抽出した信号をアンテナ312を介して送信する。

【0071】

PLL回路100は、図1に示すPLL回路100と同様の構成であるため、説明を省略する。

【0072】

以上のように第3の実施例によれば、無線機のPLL回路として、図1に示すPLL回路100を用いることで、無線機に必要な移相器を省略するとともに、無線信号を精度よく復調することが可能となる。

【0073】

PLL回路100は、4相の発振信号(I+,I−,Q+,Q−信号)を出力することができるため、発振信号をさらに90度移相させる必要がなく移相器を省略することができる。また、4相の発振信号の各出力端子に発生する負荷条件をほぼ均一とすることができるため、各4相の発振信号の位相誤差、振幅誤差を小さくすることができる。これにより、I−ch信号、Q−ch信号の位相差を90度に近づけることができ、無線信号の復調精度を向上させることができる。

【0074】

なお、ここでは、図1のPLL回路100をダイレクトコンバージョン方式の無線機に応用した例を示したが、スーパーヘテロダイン方式など、ダイレクトコンバージョン方式以外の無線機に応用することも可能である。

【実施例4】

【0075】

次に、図10を用いて第4の実施例について説明する。本実施例では、図6に示すPLL回路200を用いた無線機400について説明する。

【0076】

本実施例にかかる無線機400は、アンテナ410と、バンドパスフィルタ420と、低雑音増幅器430とミキサ440,451,452と、ローパスフィルタ461,462とPLL回路200とを有している。

【0077】

アンテナ410は、無線機400の通信相手が送信する無線信号を受信する。バンドパスフィルタ420は、アンテナ410が受信した無線信号から所望の帯域のRF信号を抽出する。低雑音増幅器430は、バンドパスフィルタ420で抽出されたRF信号を増幅する。

【0078】

ミキサ440は、低雑音僧服器430で増幅された増幅信号と、PLL回路200から出力される2乗信号Ic,Qc(第三差動信号)とを乗算する。これによりミキサ440はIF信号を生成する。

【0079】

ミキサ451は、IF信号と、PLL回路200から出力されるI+信号およびI−信号とを乗算し、BB(ベースバンド)信号(第一受信信号)を生成する。ミキサ452は、IF信号と、PLL回路200から出力されるQ+信号およびQ−信号を乗算し、BB(ベースバンド)信号(第二受信信号)を生成する。

【0080】

ローパスフィルタ461,462は、ミキサ451,452で生成されたBB信号からそれぞれ所望の帯域の信号を抽出し、I−ch信号およびQ−ch信号を生成する。このI−ch信号、Q−ch信号に対して、それぞれA/D変換、復調等の信号処理が行われ、所望の送信データに変換される。この後段の信号処理については、説明を省略する。

【0081】

PLL回路200は、図6に示すPLL回路200とほぼ同様の構成であるが、分周器160に入力する2乗信号Ic,Qcをミキサ440にも出力している点が異なる。図8に示すように、2乗信号Ic,Qcは、I+,I−,Q+,Q−信号(PLL回路の出力である発振信号)の2倍の周波数をもつ差動信号である。したがって、このIc信号およびQc信号をミキサ440へと出力することで、1つのPLL回路で2段階のダウンコンバージョンを実現する。

【0082】

具体的に、60GHzの無線信号を受信する場合の例を説明する。この場合、PLL回路200が、20GHzの発振信号を出力すると、2乗信号Ic,Qcは、40GHzの信号となる。ミキサ440で40GHzの2乗信号Ic,Qcと60GHzの無線信号とを乗算することで、20GHzのIF信号を得る。ミキサ451,452で、20GHzのIF信号と、PLL回路200の出力である20GHzの発振信号(I+,I−,Q+,Q−信号)とを乗算すると1GHzのBB信号が得られる。

【0083】

以上のように、第4の実施例では、無線機のPLL回路として、図6に示すPLL回路100を用いることで、第3の実施例と同様の効果が得られるとともに、2段階のダウンコンバージョンを行う無線方式において、複数の発振器が不要となり、無線機の回路規模を小さくすることができる。また、発振器が1つの無線機も知られているが、この場合、複数の異なる発振信号を得るために、分周器を用いる必要があるが、本実施例の無線機ではこれも不要となる。

【0084】

なお、ここでは、図6のPLL回路200を2段階のダウンコンバージョンを行う無線機の受信回路に応用した例を示したが、2段階のアップコンバージョンを行う送信回路に応用することも可能である。また、図1のPLL回路100の発振器140から、図7に示す発振器240と同様にして2次高調波信号(2乗信号)を取り出すことで、図1のPLL回路を本実施例の無線機に応用することも可能である。

【0085】

なお、本実施例の無線機に限らず、2段階のダウンコンバージョンを行う無線機であれば同様に、第1、第2の実施例にかかるPLL回路を本実施例と同様に応用することも可能である。

【0086】

なお、本発明は上記実施例そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施例に開示されている複数の構成要素の適宜な組み合わせにより、種々の発明を形成できる。例えば、実施例に示される全構成要素から幾つかの構成要素を削除してもよい。さらに、異なる実施例にわたる構成要素を適宜組み合わせてもよい。

【図面の簡単な説明】

【0087】

【図1】本発明の第1の実施例にかかるPLL回路を示すブロック図。

【図2】本発明の第1の実施例にかかるチャージポンプ120を示す図。

【図3】本発明の第1の実施例にかかるループフィルタ130を示す図。

【図4】本発明の第1の実施例にかかる発振器140を示す図。

【図5】本発明の第1の実施例にかかる加算器150−1,150−2の入出力信号の波形を示す図。

【図6】本発明の第2の実施例にかかるPLL回路を示すブロック図。

【図7】本発明の第2の実施例にかかる発振器240を示す図。

【図8】本発明の第2の実施例にかかる発振器240の出力信号波形を示す図。

【図9】本発明の第3の実施例にかかる無線機を示すブロック図。

【図10】本発明の第4の実施例にかかる無線機を示すブロック図。

【符号の説明】

【0088】

100,200・・・PLL回路

110・・・位相比較器(PFD)

120・・・チャージポンプ(CP)

130・・・ループフィルタ(LF)

140,240・・・発振器(QVCO)

150・・・加算器

160・・・分周器(DIV)

311,312,410・・・アンテナ

321,322,420・・・バンドパスフィルタ

331,430・・・低雑音増幅器

332・・・パワーアンプ

341〜344,440,451,452・・・ミキサ

351〜354,461,462・・・ローパスフィルタ

【特許請求の範囲】

【請求項1】

第一差動信号を生成する第一発振部と、前記第一差動信号と90度の位相差をもつ第二差動信号を生成する第二発振部と、を有する電圧制御発振器と、

前記第一及び第二差動信号に基づく第三差動信号の位相と、基準信号の位相とを比較する位相比較器と、

前記位相比較器の比較結果に基づいて、前記電圧制御発振器を制御する制御電圧を生成するループフィルタと、

を具備することを特徴とするPLL回路。

【請求項2】

前記第三差動信号は、前記第一差動信号の2乗信号及び第二差動信号の2乗信号であることを特徴とする請求項1に記載するPLL回路。

【請求項3】

前記第三差動信号を分周する分周器をさらに備え、

前記位相比較器は、前記分周器が分周した第三差動信号と前記基準信号とを比較することを特徴とする請求項1に記載のPLL回路。

【請求項4】

前記第一及び第二発振部は、それぞれ複数のトランジスタを有し、前記トランジスタのソース端子から前記2乗信号を生成することを特徴とする請求項2に記載するPLL回路。

【請求項5】

前記第一発振部は、

前記第一差動信号の正相信号を出力する第一出力端子と、

前記第一差動信号の逆相信号を出力する第二出力端子と、

前記第一差動信号の2乗信号を出力する第五出力端子と、

前記第一及び第二出力端子に接続され、インダクタと容量とを有し、前記第一差動信号を生成する第一共振部と、

ドレイン端子が前記第一出力端子に接続され、ゲート端子が前記第二出力端子に接続され、ソース端子が前記第五出力端子に接続される第一MOSトランジスタと、

ドレイン端子が前記第二出力端子に接続され、ゲート端子が前記第一出力端子に接続され、ソース端子が前記第三出力端子に接続される第二MOSトランジスタと、

ゲート端子に前記第二差動信号の逆相信号が印加され、ソース端子が前記第五出力端子に接続される第三MOSトランジスタと、

ゲート端子に前記第二差動信号の正相信号が印加され、ソース端子が前記第五出力端子に接続される第四MOSトランジスタと、

を備え、

前記第二発振部は、

前記第二差動信号の正相信号を出力する第三出力端子と、

前記第二差動信号の逆相信号を出力する第四出力端子と、

前記第二差動信号の2乗信号を出力する第六出力端子と、

前記第三および第四出力端子に接続され、インダクタと容量とを有し、前記第二差動信号を生成する第二共振部と、

ドレイン端子が前記第三出力端子に接続され、ゲート端子が前記第四出力端子に接続され、ソース端子が前記第六出力端子に接続される第五MOSトランジスタと、

ドレイン端子が前記第四出力端子に接続され、ゲート端子が前記第三出力端子に接続され、ソース端子が前記第六出力端子に接続される第六MOSトランジスタと、

ゲート端子に前記第一発振信号の正相信号が印加され、ソース端子が前記第六出力端子に接続される第七MOSトランジスタと、

ゲート端子に前記第二発振信号の逆相信号が印加され、ソース端子が前記第六出力端子に接続される第八MOSトランジスタと、

を備えることを特徴とする請求項2に記載するPLL回路。

【請求項6】

前記第一及び第二差動信号の各正相信号を加算し、前記第一及び第二差動信号の各逆相信号を加算して、前記第三差動信号を生成する加算器をさらに有することを特徴とする請求項1に記載するPLL回路。

【請求項7】

前記第一発振部は、

前記第一差動信号の正相信号を出力する第一出力端子と、

前記第一差動信号の逆相信号を出力する第二出力端子と、

前記第一及び第二出力端子に接続され、インダクタと容量とを有し、前記第一差動信号を生成する第一共振部と、

ドレイン端子が前記第一出力端子に接続され、ゲート端子が前記第二出力端子に接続される第一MOSトランジスタと、

ドレイン端子が前記第二出力端子に接続され、ゲート端子が前記第一出力端子に接続される第二MOSトランジスタと、

ゲート端子に前記第二差動信号の逆相信号が印加される第三MOSトランジスタと、

ゲート端子に前記第二差動信号の正相信号が印加される第四MOSトランジスタと、

を備え、

前記第二発振部は、

前記第二差動信号の正相信号を出力する第三出力端子と、

前記第二作動信号の逆相信号を出力する第四出力端子と、

前記第三出力端子及び前記第四出力端子に接続され、インダクタと容量とを有し、前記第二差動信号を生成する共振部と、

ドレイン端子が前記第三出力端子に接続され、ゲート端子が前記第四出力端子に接続される第五MOSトランジスタと、

ドレイン端子が前記第四出力端子に接続され、ゲート端子が前記第三出力端子に接続される第六MOSトランジスタと、

ゲート端子に前記第一差動信号の正相信号が印加される第七MOSトランジスタと、

ゲート端子に前記第一差動信号の逆相信号が印加される第八MOSトランジスタと、

を備えることを特徴とする請求項5に記載するPLL回路。

【請求項8】

無線信号を受信するアンテナと、

前記無線信号を増幅し、増幅信号を生成する増幅器と、

請求項1に記載のPLL回路と、

前記第一差動信号と前記増幅信号とを乗算し、第一受信信号を生成する第一ミキサ回路と、

前記第二差動信号と前記増幅信号とを乗算し、第二受信信号を生成する第二ミキサ回路と、

を備えることを特徴とする無線機。

【請求項9】

前記PLL回路は、前記第一差動信号の2乗信号及び前記第二差動信号の2乗信号を生成し、

前記第一及び第二差動信号の2乗信号と、前記増幅信号とをそれぞれ乗算し、差動信号である中間周波信号を生成する第三ミキサ回路をさらに有し、

前記第一及び第二ミキサ回路は、前記第一及び第二差動信号と、前記中間周波信号とをそれぞれ乗算し、前記第一及び第二受信信号を生成すること

を特徴とする請求項7に記載する無線機。

【請求項10】

前記PLL回路の前記第一および第二発振部は、それぞれ複数のトランジスタを有し、

前記トランジスタのソース端子から前記2乗信号を生成すること

を特徴とする請求項8に記載する無線機。

【請求項11】

前記第一発振部は、

前記第一差動信号の正相信号を出力する第一出力端子と、

前記第一差動信号の逆相信号を出力する第二出力端子と、

前記2乗信号を出力する第五出力端子と、

前記第一及び第二出力端子に接続され、インダクタと容量とを有し、前記第一差動信号を生成する第一共振部と、

ドレイン端子が前記第一出力端子に接続され、ゲート端子が前記第二出力端子に接続され、ソース端子が前記第五出力端子に接続される第一MOSトランジスタと、

ドレイン端子が前記第二出力端子に接続され、ゲート端子が前記第一出力端子に接続され、ソース端子が前記第三出力端子に接続される第二MOSトランジスタと、

ゲート端子に前記第二差動信号の逆相信号が印加され、ソース端子が前記第五出力端子に接続される第三MOSトランジスタと、

ゲート端子に前記第二差動信号の正相信号が印加され、ソース端子が前記第五出力端子に接続される第四MOSトランジスタと、

を備え、

前記第二発振部は、

前記第二差動信号の正相信号を出力する第三出力端子と、

前記第二差動信号の逆相信号を出力する第四出力端子と、

前記2乗信号を出力する第六出力端子と、

前記第三および第四出力端子に接続され、インダクタと容量とを有し、前記第二差動信号を生成する第二共振部と、

ドレイン端子が前記第三出力端子に接続され、ゲート端子が前記第四出力端子に接続され、ソース端子が前記第六出力端子に接続される第五MOSトランジスタと、

ドレイン端子が前記第四出力端子に接続され、ゲート端子が前記第三出力端子に接続され、ソース端子が前記第六出力端子に接続される第六MOSトランジスタと、

ゲート端子に前記第一発振信号の正相信号が印加され、ソース端子が前記第六出力端子に接続される第七MOSトランジスタと、

ゲート端子に前記第二発振信号の逆相信号が印加され、ソース端子が前記第六出力端子に接続される第八MOSトランジスタと、

を備えることを特徴とする請求項9に記載する無線機。

【請求項1】

第一差動信号を生成する第一発振部と、前記第一差動信号と90度の位相差をもつ第二差動信号を生成する第二発振部と、を有する電圧制御発振器と、

前記第一及び第二差動信号に基づく第三差動信号の位相と、基準信号の位相とを比較する位相比較器と、

前記位相比較器の比較結果に基づいて、前記電圧制御発振器を制御する制御電圧を生成するループフィルタと、

を具備することを特徴とするPLL回路。

【請求項2】

前記第三差動信号は、前記第一差動信号の2乗信号及び第二差動信号の2乗信号であることを特徴とする請求項1に記載するPLL回路。

【請求項3】

前記第三差動信号を分周する分周器をさらに備え、

前記位相比較器は、前記分周器が分周した第三差動信号と前記基準信号とを比較することを特徴とする請求項1に記載のPLL回路。

【請求項4】

前記第一及び第二発振部は、それぞれ複数のトランジスタを有し、前記トランジスタのソース端子から前記2乗信号を生成することを特徴とする請求項2に記載するPLL回路。

【請求項5】

前記第一発振部は、

前記第一差動信号の正相信号を出力する第一出力端子と、

前記第一差動信号の逆相信号を出力する第二出力端子と、

前記第一差動信号の2乗信号を出力する第五出力端子と、

前記第一及び第二出力端子に接続され、インダクタと容量とを有し、前記第一差動信号を生成する第一共振部と、

ドレイン端子が前記第一出力端子に接続され、ゲート端子が前記第二出力端子に接続され、ソース端子が前記第五出力端子に接続される第一MOSトランジスタと、

ドレイン端子が前記第二出力端子に接続され、ゲート端子が前記第一出力端子に接続され、ソース端子が前記第三出力端子に接続される第二MOSトランジスタと、

ゲート端子に前記第二差動信号の逆相信号が印加され、ソース端子が前記第五出力端子に接続される第三MOSトランジスタと、

ゲート端子に前記第二差動信号の正相信号が印加され、ソース端子が前記第五出力端子に接続される第四MOSトランジスタと、

を備え、

前記第二発振部は、

前記第二差動信号の正相信号を出力する第三出力端子と、

前記第二差動信号の逆相信号を出力する第四出力端子と、

前記第二差動信号の2乗信号を出力する第六出力端子と、

前記第三および第四出力端子に接続され、インダクタと容量とを有し、前記第二差動信号を生成する第二共振部と、

ドレイン端子が前記第三出力端子に接続され、ゲート端子が前記第四出力端子に接続され、ソース端子が前記第六出力端子に接続される第五MOSトランジスタと、

ドレイン端子が前記第四出力端子に接続され、ゲート端子が前記第三出力端子に接続され、ソース端子が前記第六出力端子に接続される第六MOSトランジスタと、

ゲート端子に前記第一発振信号の正相信号が印加され、ソース端子が前記第六出力端子に接続される第七MOSトランジスタと、

ゲート端子に前記第二発振信号の逆相信号が印加され、ソース端子が前記第六出力端子に接続される第八MOSトランジスタと、

を備えることを特徴とする請求項2に記載するPLL回路。

【請求項6】

前記第一及び第二差動信号の各正相信号を加算し、前記第一及び第二差動信号の各逆相信号を加算して、前記第三差動信号を生成する加算器をさらに有することを特徴とする請求項1に記載するPLL回路。

【請求項7】

前記第一発振部は、

前記第一差動信号の正相信号を出力する第一出力端子と、

前記第一差動信号の逆相信号を出力する第二出力端子と、

前記第一及び第二出力端子に接続され、インダクタと容量とを有し、前記第一差動信号を生成する第一共振部と、

ドレイン端子が前記第一出力端子に接続され、ゲート端子が前記第二出力端子に接続される第一MOSトランジスタと、

ドレイン端子が前記第二出力端子に接続され、ゲート端子が前記第一出力端子に接続される第二MOSトランジスタと、

ゲート端子に前記第二差動信号の逆相信号が印加される第三MOSトランジスタと、

ゲート端子に前記第二差動信号の正相信号が印加される第四MOSトランジスタと、

を備え、

前記第二発振部は、

前記第二差動信号の正相信号を出力する第三出力端子と、

前記第二作動信号の逆相信号を出力する第四出力端子と、

前記第三出力端子及び前記第四出力端子に接続され、インダクタと容量とを有し、前記第二差動信号を生成する共振部と、

ドレイン端子が前記第三出力端子に接続され、ゲート端子が前記第四出力端子に接続される第五MOSトランジスタと、

ドレイン端子が前記第四出力端子に接続され、ゲート端子が前記第三出力端子に接続される第六MOSトランジスタと、

ゲート端子に前記第一差動信号の正相信号が印加される第七MOSトランジスタと、

ゲート端子に前記第一差動信号の逆相信号が印加される第八MOSトランジスタと、

を備えることを特徴とする請求項5に記載するPLL回路。

【請求項8】

無線信号を受信するアンテナと、

前記無線信号を増幅し、増幅信号を生成する増幅器と、

請求項1に記載のPLL回路と、

前記第一差動信号と前記増幅信号とを乗算し、第一受信信号を生成する第一ミキサ回路と、

前記第二差動信号と前記増幅信号とを乗算し、第二受信信号を生成する第二ミキサ回路と、

を備えることを特徴とする無線機。

【請求項9】

前記PLL回路は、前記第一差動信号の2乗信号及び前記第二差動信号の2乗信号を生成し、

前記第一及び第二差動信号の2乗信号と、前記増幅信号とをそれぞれ乗算し、差動信号である中間周波信号を生成する第三ミキサ回路をさらに有し、

前記第一及び第二ミキサ回路は、前記第一及び第二差動信号と、前記中間周波信号とをそれぞれ乗算し、前記第一及び第二受信信号を生成すること

を特徴とする請求項7に記載する無線機。

【請求項10】

前記PLL回路の前記第一および第二発振部は、それぞれ複数のトランジスタを有し、

前記トランジスタのソース端子から前記2乗信号を生成すること

を特徴とする請求項8に記載する無線機。

【請求項11】

前記第一発振部は、

前記第一差動信号の正相信号を出力する第一出力端子と、

前記第一差動信号の逆相信号を出力する第二出力端子と、

前記2乗信号を出力する第五出力端子と、

前記第一及び第二出力端子に接続され、インダクタと容量とを有し、前記第一差動信号を生成する第一共振部と、

ドレイン端子が前記第一出力端子に接続され、ゲート端子が前記第二出力端子に接続され、ソース端子が前記第五出力端子に接続される第一MOSトランジスタと、

ドレイン端子が前記第二出力端子に接続され、ゲート端子が前記第一出力端子に接続され、ソース端子が前記第三出力端子に接続される第二MOSトランジスタと、

ゲート端子に前記第二差動信号の逆相信号が印加され、ソース端子が前記第五出力端子に接続される第三MOSトランジスタと、

ゲート端子に前記第二差動信号の正相信号が印加され、ソース端子が前記第五出力端子に接続される第四MOSトランジスタと、

を備え、

前記第二発振部は、

前記第二差動信号の正相信号を出力する第三出力端子と、

前記第二差動信号の逆相信号を出力する第四出力端子と、

前記2乗信号を出力する第六出力端子と、

前記第三および第四出力端子に接続され、インダクタと容量とを有し、前記第二差動信号を生成する第二共振部と、

ドレイン端子が前記第三出力端子に接続され、ゲート端子が前記第四出力端子に接続され、ソース端子が前記第六出力端子に接続される第五MOSトランジスタと、

ドレイン端子が前記第四出力端子に接続され、ゲート端子が前記第三出力端子に接続され、ソース端子が前記第六出力端子に接続される第六MOSトランジスタと、

ゲート端子に前記第一発振信号の正相信号が印加され、ソース端子が前記第六出力端子に接続される第七MOSトランジスタと、

ゲート端子に前記第二発振信号の逆相信号が印加され、ソース端子が前記第六出力端子に接続される第八MOSトランジスタと、

を備えることを特徴とする請求項9に記載する無線機。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2010−154270(P2010−154270A)

【公開日】平成22年7月8日(2010.7.8)

【国際特許分類】

【出願番号】特願2008−330652(P2008−330652)

【出願日】平成20年12月25日(2008.12.25)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成22年7月8日(2010.7.8)

【国際特許分類】

【出願日】平成20年12月25日(2008.12.25)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]