PLL回路

【課題】位相比較器の不感帯による位相雑音を低減させるとともに、定常位相誤差とスプリアスレベルをも低減したPLL回路を提供する。

【解決手段】擬似ランダムパターン生成回路4によって擬似ランダムパターンであるM系列信号を生成し、オフセット生成回路3で、上記M系列信号に応じてチャージポンプ2から出力される電流に正及び負のオフセット電流を加える。ここで、オフセット電流は、電圧制御発振器6出力に不感帯幅より大きい位相変化を起こさせるものとする。その結果、位相比較器1の入力信号は常に不感帯幅を超える位相差を持つようになり、位相比較器の不感帯を避けてロックさせることが可能になる。さらに、十分長い周期のM系列を用いることで、定常位相誤差が低減されるとともに、位相オフセットの周期性によって生じるスプリアスが広帯域に拡散され、拡散効果によってスプリアスのレベルが低減される。

【解決手段】擬似ランダムパターン生成回路4によって擬似ランダムパターンであるM系列信号を生成し、オフセット生成回路3で、上記M系列信号に応じてチャージポンプ2から出力される電流に正及び負のオフセット電流を加える。ここで、オフセット電流は、電圧制御発振器6出力に不感帯幅より大きい位相変化を起こさせるものとする。その結果、位相比較器1の入力信号は常に不感帯幅を超える位相差を持つようになり、位相比較器の不感帯を避けてロックさせることが可能になる。さらに、十分長い周期のM系列を用いることで、定常位相誤差が低減されるとともに、位相オフセットの周期性によって生じるスプリアスが広帯域に拡散され、拡散効果によってスプリアスのレベルが低減される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、PLL回路に関し、特にリファレンス信号に位相同期した逓倍信号を出力するPLL回路に関する。

【背景技術】

【0002】

PLL回路はリファレンスクロック信号に位相同期した逓倍クロック信号を得る等のために広く使用されているが、PLL回路で生成されるクロック信号の精度を決めるものの1つとして位相雑音の程度が挙げられ、位相雑音のレベルが大きいほどクロック信号の精度は劣化する。

【0003】

位相雑音を大きくする原因の1つとしては位相比較器の位相比較特性に生じる非線形領域の影響が挙げられる。位相比較器の非線形領域とは、2つの入力信号の間の位相差に対応して適正な位相誤差信号を出力しない領域であり、典型的にはデバイスの伝搬遅延の影響などにより2つの入力信号の位相差ゼロ付近の正負に亘る一定幅の特性領域(以下、「不感帯」という。)である。不感帯では位相差があっても位相誤差信号としてゼロ(0)の出力特性や、位相差に対し線形でない出力特性を示す。また、この不感帯はPLL回路の動作上はリファレンス信号と逓倍信号である発振出力信号の間で位相差があっても適正な位相誤差信号が出力されず位相同期(負帰還制御)が適正にかからない領域である。

【0004】

位相比較器の特性に不感帯が存在するとその領域では位相同期がかからないことから位相変動が生じて位相雑音が大きくなりPLLの特性が劣化する。そのため低位相雑音のPLL回路を構成するためには位相比較器の不感帯の影響を小さくする必要がある。

【0005】

図7は、位相比較器の不感帯の影響を小さくした従来のPLL回路のブロック図を示す図である(特許文献1参照)。

このPLL回路は、位相比較器1、チャージポンプ回路2、ループフィルタ5、電圧制御発振器6、分周回路7及び定常位相誤差生成回路71を備えており、定常位相誤差生成回路71は、遅延回路72、インバータ回路73、AND論理回路74、スイッチ75及び定電流源回路76から構成される。

【0006】

位相比較器1の入力には基準クロック信号REFと、電圧制御発振器6の発振出力を分周回路7で分周した分周信号SIGとが入力され、位相比較器1は両入力信号の位相差に対応して、位相が進んでいるか遅れているかに応じてそれぞれUP信号又はDOWN信号を生成し、チャージポンプ回路2に出力する。チャージポンプ回路2は前記UP信号及びDOWN信号に基づく位相差電流を生成しループフィルタ5に出力する。ループフィルタ5はさらに定常位相誤差生成回路71からの定常的なオフセット電流が加えられる。

【0007】

定常位相誤差生成回路71は、ループフィルタ5に対するオフセット電流をスイッチ75を介して定電流源回路76から加えるように構成され、前記スイッチ75は、基準クロック信号REFを遅延回路72とインバータ回路73を介して時間的に遅延させ反転させた信号と、前記基準クロック信号REFとをAND論理回路74により論理をとることにより、基準クロック信号REFのパルスの前縁部分で発生したパルス信号SWにより開閉(オン/オフ)制御される。

【0008】

ループフィルタ5は位相差電流とオフセット電流を入力し平滑した制御電圧を出力し、帰還信号として電圧制御発振器6の周波数制御部を制御し、電圧制御発振器6からは逓倍クロック信号OUTが発振され、さらに逓倍クロック信号OUTは1/N分周回路7で1/N分周され、その分周信号SIGは位相比較器1の入力の一方としてフィードバックされる。

【0009】

次に、従来のPLL回路の動作をタイミングチャートにより説明する。

図8は従来のPLL回路の動作を示すタイミングチャートである。PLL回路がロック(位相同期)した定常状態でのオフセット電流、UP信号及びDOWN信号の出力の様子を示している。

【0010】

同図において信号(a)は前記基準クロック信号REFであり、信号(d)は前記分周回路7からの分周信号SIG(電圧制御発振器6の発振出力を1/N分周した信号)である。また、信号(b)はAND論理回路74からのパルス信号SWであり、そのハイレベル(“1”)の間でスイッチ75をオン状態とし、定電流源回路76から信号(c)に示すような負のオフセット電流(−Ioff)をループフィルタ5に加える。

【0011】

本例では、パルス状の負のオフセット電流(c)により、ループフィルタ5から平滑した信号として負にオフセットされた制御電圧信号が出力され電圧制御発振器6の発信周波数が制御され、分周信号SIG(d)が基準クロック信号REF(a)より一定位相遅れて位相同期する状態を示しており、位相比較器1からは負帰還信号としてUP信号(e)のパルスのみがチャージポンプ回路2に出力されている。

【0012】

以上により通常のPLL回路では位相がロックした定常状態では基準クロック信号REF(a)と分周信号SIG(d)の位相は揃っており、UP信号、DOWN信号は共に現れないのであるが、このPLL回路では定常位相誤差生成回路71によってオフセット電流がループフィルタ5に流れるように構成されているため、定常状態であっても分周信号SIG(d)は基準クロック信号REFに対して位相差を持った状態となる。

【0013】

具体的にはAND論理回路74の出力が“1”の間は、定電流源回路76によりループフィルタ5からオフセット電流が引き込まれるため、ループフィルタ5の出力電圧は低下する。その結果、分周信号SIGの位相は常に遅れ状態になり、位相比較器1からはUP信号が常に出力される。

【0014】

ここで、オフセット電流による位相変化量を不感帯の幅を超えるように設定すると、位相比較器1の入力信号である基準クロック信号REFと分周信号SIGは、常に不感帯幅以上の位相差を持った状態となる。

【0015】

その結果、分周信号SIGは基準クロック信号REFと位相比較特性の不感帯の範囲外の前記位相差の点にロックさせることができるから不感帯の影響を低減することが可能である。

【0016】

【特許文献1】特開昭62−23620号公報

【発明の開示】

【発明が解決しようとする課題】

【0017】

従来のPLL回路によれば、位相比較特性の不感帯により生じる位相雑音の発生を電圧制御発振器の発振出力に位相オフセットを与えることにより抑制することを可能としているものの、この原理では基準クロック信号REFのパルスのエッジから一定幅の周期的なパルス信号を生成し、一定極性のパルス状のオフセット電流としてループフィルタに加えるものであるから、一方向のオフセットの定常的な加算により定常位相誤差が発生するとともに、周期的なオフセット電流の加算によりループフィルタの出力の制御電圧(帰還信号)に周期的な変動を残留させ電圧制御発振器の発振周波数の変動を引き起こすのでスプリアスのレベルを大きくするという問題がある。

【0018】

従って、従来のPLL回路では位相雑音を抑制できても、定常位相誤差が発生するのに加えスプリアスレベルが大きくなり、PLL回路が生成するクロック信号の精度は充分に向上させることはできない。

【0019】

以上のように従来のPLL回路は位相同期特性の劣化の原因に関連する次のような2つの問題点がある。

第1の問題点は、常に一方向のオフセットを与えるため位相比較器の出力には常に一方向の位相誤差信号が現れ、それが電圧制御発振器の出力信号の定常位相誤差として現れる点である。

【0020】

第2の問題点は、電圧制御発振器の制御電圧がリファレンス信号に同期して周期的に変動するために、周期的な定常位相誤差により電圧制御発振器の出力信号にスプリアスが発生するという点である。

【0021】

(目的)

本発明は、以上の問題を解決するものであり、位相比較器の不感帯による位相雑音を低減させるとともに、定常位相誤差とスプリアスレベルをも低減したPLL回路を提供することにある。

【課題を解決するための手段】

【0022】

本発明のPLL回路は、電圧制御発振器と、入力基準信号と前記電圧制御発振器の分周信号とを位相比較する位相比較器と、前記位相比較器の出力を平滑するループフィルタを介して前記電圧制御発振器を制御するPLL回路に関し、擬似ランダムパターンの2値の論理レベルにより位相比較器の不感帯の幅を超える正及び負の位相オフセット与えるオフセット信号を生成し位相比較器の出力側に供給するオフセット生成回路を備えることを特徴とする。

【0023】

また、前記擬似ランダムパターンは、M系列信号であり、前記M系列信号は、前記位相比較器に入力するリファレンス信号により駆動されるM系列信号発生器により発生され、又は、前記位相比較器に入力する電圧制御発振回路の出力の分周信号により駆動されるM系列信号発生器により発生されることを特徴とする。

【0024】

更に、前記オフセット生成回路は、擬似ランダムパターンにより相補的に開閉動作する2つのスイッチを介してそれぞれ異なる極性のオフセット信号を供給するように構成し、前記オフセット信号は、定電流として供給することを特徴とする。

【0025】

また、前記位相比較器の出力にチャージポンプ回路を備え、前記位相比較器は、リファレンス信号と電圧制御発振器の出力の分周信号の位相とを比較し、リファレンス信号に対し前記分周信号の位相の進み及び遅れに応じたパルス幅を有する位相の遅れ制御パルス及び進み制御パルスを出力することを特徴とする。

【0026】

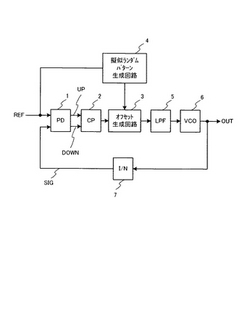

より具体的には本発明のPLL回路は、基準クロック信号REFと分周信号SIGの位相を比較して、分周信号SIGの周波数が低い場合にはパルス状のエッジ位相差をアップ制御信号UPとして出力し、また分周信号SIGの周波数が高い場合にはパルス状のエッジ位相差をダウン制御信号DOWNとして出力する位相比較器1と、これらUP信号、DOWN信号に基づき電流を出力するチャージポンプ回路2と、擬似ランダムパターンであるM系列信号を生成する擬似ランダムパターン生成回路4と、上記M系列信号に応じてチャージポンプ回路2の出力電流に正及び負のオフセット電流を加えるオフセット生成回路3と、オフセット生成回路3から出力される上記オフセット電流が加わった位相差電流に応じて、電圧制御発振器の制御電圧を出力するループフィルタ5と、前記制御電圧が入力され、前記制御電圧に応じた逓倍クロック信号を出力する電圧制御発振器6と、前記逓倍クロック信号が入力されこの逓倍クロック信号を分周した前記分周信号SIGを出力する1/N分周回路7とを備える。(図1)

【0027】

(作用)

本発明によれば、オフセット生成回路によりM系列信号等の擬似ランダムパターンに応じてチャージポンプ等から出力される電流に正及び負のオフセット電流を加えられる。ここで、オフセット電流は、電圧制御発振器出力に不感帯幅より大きい位相変化を起こさせる。ランダムなオフセット電流をPLLの帰還信号に常に発生させることによって、位相比較器の入力信号は常に不感帯幅を超える位相差を持つようになり位相比較器の不感帯を避けてPLLがロックする。

【発明の効果】

【0028】

本発明によれば、電圧制御発振器への帰還信号に、擬似ランダムパターンの2値の論理レベルにより位相比較器の不感帯の幅を超える正及び負の位相オフセット与えることにより、PLL回路の同期動作を位相比較器の不感帯を避けてロックさせることができるから、位相雑音を抑制できるとともに、正負のランダムな位相オフセットにより定常位相誤差の発生を防止することができる。

【0029】

また、擬似ランダムパターンとして十分長い周期のM系列を用いることで、定常位相誤差の低減に加えて、位相オフセットの周期性によって生じるスプリアスが広帯域に拡散させることができるので、拡散効果によってスプリアスのレベルを低減させることができる。

【発明を実施するための最良の形態】

【0030】

(構成の説明)

次に、本発明の実施の形態について図面を参照して詳細に説明する。

図1は、本発明の第1の実施の形態によるPLL回路を示すブロック図である。本実施の形態は位相同期の基準となるリファレンス信号は基準クロック信号とし、電圧制御発振器から逓倍クロック信号を出力する例を示している。1は位相比較器(PD)、2はチャージポンプ回路(CP)、3はオフセット生成回路、4は擬似ランダムパターン生成回路、5はループフィルタ(LPF)、6は電圧制御発振器(VCO)、7は1/N分周回路(1/N)である。

【0031】

位相比較器1には基準クロック信号REFと分周回路7の分周信号SIGが入力され、出力はチャージポンプ回路2に入力される。位相比較器1は基準クロック信号REFと分周信号SIGの位相を比較して、分周信号SIGの周波数が基準クロック信号REFの周波数より低い場合にはパルス状のエッジ位相差(基準クロック信号REFと分周信号SIGのパルスのエッジ間の位相差)をアップ制御信号UP(UP信号)として出力し、また分周信号SIGの周波数が基準クロック信号REFの周波数より高い場合にはパルス状のエッジ位相差をダウン制御信号DOWN(DOWN信号)として出力する。つまり、基準クロック信号REFに対し前記分周信号SIGの位相の進み及び遅れに応じたパルス幅を有する位相の遅れ制御パルス及び進み制御パルスを出力する。

【0032】

チャージポンプ回路2は、これらUP信号、DOWN信号を入力し、UP信号、DOWN信号に基づき位相差電流をオフセット生成回路3に出力する。具体的にはUP信号のパルス幅に応じた時間だけチャージポンプ回路2内の充放電コンデンサ又はループフィルタ側コンデンサに電荷をチャージし、DOWN信号のパルス幅に応じた時間だけ該コンデンサの電荷をディスチャージするように位相差電流を出力する。

【0033】

また、擬似ランダムパターン生成回路4は、基準クロック信号REFを入力クロックとして、オフセット生成回路3に2値の論理レベルでなる擬似ランダムパターンを出力する。

【0034】

オフセット生成回路3は、チャージポンプ回路2と擬似ランダムパターン生成回路4の出力を入力し、チャージポンプ回路2の出力である位相差電流に、擬似ランダムパターン生成回路4で生成する擬似ランダムパターンで制御されたオフセット電流を加え、オフセット電流を加えた位相差電流(位相比較電流)をループフィルタ5に出力する。

【0035】

ループフィルタ5は、ローパスフィルタで構成されオフセット生成回路3からの位相比較電流が入力され、電圧制御発振器6の制御電圧(帰還信号)を出力する。

【0036】

電圧制御発振器6は、ループフィルタ5の出力電圧によって発振周波数が制御され、逓倍クロック信号OUTを出力する。

【0037】

1/N分周回路7は、逓倍クロック信号OUTを入力とし、1/N分周された分周信号SIGを位相比較器1に出力する。

【0038】

図2は、オフセット生成回路3の構成を示す図である。同図により前記位相差電流の生成動作の詳細について説明する。

オフセット生成回路3は、接地及び電源VDDに接続された互いに異なる方向(極性)の電流を出力するの2つの定電流源回路21、22と、各定電流源回路21、22とチャージポンプ回路2とループフィルタ5の接続線との間にそれぞれ接続された2つのスイッチ23、24と、擬似ランダムパターン回路4の出力であるM系列信号SWを2つのスイッチ23、24の制御信号とし、各定電流源回路21、22の何れかを前記接続線へ相補的に接続(オン)、非接続(オフ)させるように設けたインバータ回路25とから構成される。

【0039】

スイッチ23、24は、制御信号が“1”のときにオン(接続)し、制御信号が“0”のときにオフ(非接続)となる。M系列信号SWが“0”であれば定電流源回路22によりオフセット電流をループフィルタ5に流し込み(以下、流し込むオフセット電流を正のオフセット電流+Ioff)、M系列信号SWが“1“であれば定電流源回路21によりオフセット電流をループフィルタ5から引き込む(以下、引き込むオフセット電流を負のオフセット電流−Ioff)ように動作する。ここで、定電流源回路21、22の電流値はともに同一の電流値Ioffであり、位相比較器1のもつ不感帯幅φを超える位相変化を電圧制御発振器に起こさせる大きさの電流値である。

【0040】

次に、擬似ランダムパターン生成回路4の構成及び動作の詳細について説明する。

擬似ランダムパターン生成回路4は、主に、シフトレジスタと、該シフトレジスタの出力をその入力に帰還する1ないし複数の排他的論理和回路(EXOR回路)とで構成されるM系列発生器が利用可能である。このようなM系列発生器の例としては、各種の文献に記載されている(例えば、今井秀樹著「符号理論」、電子情報通信学会、1990年、W.W.Peterson著「Error Correcting Codes」、The M.I.T. Press、1961年、参照)。

【0041】

図3は擬似ランダムパターン生成回路の構成例を示す図である。本実施の形態で使用するM系列発生器の例を示す図である。次数25の原始多項式であるx25+x3+1を用いたM系列発生器を示している。

基準クロック信号REFをクロックとして動作する25段のフリップフロップからなるシフトレジスタ31とEXOR回路32から構成される。少なくとも1つのフリップフロップの初期値を1とすることで所望のM系列を出力する。またこのときのM系列信号の周期は225−1=33,554,431クロックであり、“0”が16,777,215回、“1”が16,777,216回現れる。一般的にM系列は1周期中で生じる“1”の回数が“0”の回数より1回だけ多く現れる性質を持っている。

【0042】

(動作の説明)

次に、本実施の形態のPLL回路の動作をタイミングチャートにより説明する。

図4は、本実施の形態のPLL回路の動作を示すタイミングチャートである。PLL回路がロック(位相同期)した定常状態でのオフセット電流、UP信号及びDOWN信号の変化等を示している。

【0043】

同図において信号(a)は基準クロック信号REFであり、信号(d)は1/N分周回路7からの分周信号SIG(電圧制御発振器6の発振出力を1/N分周した信号)である。また、信号(b)は基準クロック信号REF(a)で動作し該信号REF(a)に同期したM系列信号SWであり、その“1”の論理状態で、図2に示すスイッチ23をオン状態とし、定電流源回路21から信号(c)に示すような負のオフセット電流(−Ioff)をループフィルタ5に加え、“0”の論理状態で、図2に示すスイッチ24をオン状態とし、定電流源回路22から信号(c)に示すような正のオフセット電流(+Ioff)をループフィルタ5に加える。

【0044】

図4ではパルス状の擬似ランダムな正及び負のオフセットを生じさせる信号(c)がチャージポンプ回路2の出力に加算されることにより、ループフィルタ5からの平滑した信号として負及び正にオフセットされた制御電圧が出力され、電圧制御発振器6の周波数制御部が制御される。

【0045】

M系列信号SWが“0”の場合は、ループフィルタ5にオフセット電流+Ioffが加えられるため、ループフィルタ5の出力電圧は上がり分周信号SIGの位相は進み状態になる。M系列信号SWが“1”の場合は、ループフィルタ5にオフセット電流−Ioffが加えられるため、ループフィルタ5の出力電圧は下がり分周信号SIGの位相は遅れ状態になる。

【0046】

ここで、オフセット電流+/−Ioffによる分周信号SIGの位相変化を+/−θとすると、定常状態では位相のバランスをとるために、オフセット電流による位相変動をチャージポンプ2出力の位相差電流で相殺しなければならない。その結果、分周信号SIGは基準クロック信号REFに対して常に−/+θだけの位相差を持った状態でロックすることになる。

【0047】

この例では、位相比較器1からは、正のオフセット電流の加算後にDOWN信号(f)のパルスが出力され、負のオフセット電流の加算後にUP信号(e)のパルスが出力され、分周信号SIG(d)は、基準クロック信号REF(a)に対し正負のオフセット電流に応じて一定位相(θ)の進み(+θ)又は遅れ(−θ)のパルス信号として出力され、PLL回路はランダムな±θのオフセット位相で位相同期状態となる。

【0048】

以上により通常のPLL回路では位相がロックした定常状態では基準クロック信号REF(a)と分周信号SIG(d)の位相は揃っており、UP信号、DOWN信号ともに現れないのであるが、本発明のPLL回路では、M系列信号SWによってオフセット電流が常にループフィルタ5に流れるように構成されているため、定常状態であっても分周信号SIG(d)は基準クロック信号REFに対して位相差を持った状態となり、UP信号、DOWN信号が現れる。

【0049】

図5は、本実施の形態の位相比較器の位相比較特性を示す図である。位相比較器1の入力信号の位相差(横軸)と位相比較器1の制御パルスによって生じるチャージポンプ出力電流(CP電流、縦軸)との関係を示したものである。位相比較器1の位相比較特性としては、位相差0付近において位相比較器1を構成する素子の応答遅延などの理由で非線形特性が現れており、不感帯(不感帯幅φ)が存在する。そのため、図5に示すように、CP電流も位相差0付近で不感帯により非線形な振る舞いを生じる。

【0050】

通常、PLL回路がロックした定常状態は、特性曲線61の位相差0付近での動作となるが、本発明のPLL回路では、常に±θの位相差を持つことになるため、図5に示すように、θ≧φに設定することによりチャージポンプ出力は常に不感帯のない理想的な線形特性をもつ領域で動作を行うことになる。その結果、不感帯の影響による位相雑音を低減することが可能となる。

【0051】

また、前述したように、M系列は1周期中で生じる“1”の回数が“0”の回数より1回だけ多いという性質をもつため、1回だけ余分に負のオフセット電流が生じる。この余分なオフセット電流は定常位相誤差となるが、1周期で平均すれば、この定常位相誤差はM系列の周期に反比例して小さくなる。そのため、十分長い周期のM系列を用いることで定常位相誤差を低減することができる。さらには、十分長い周期のM系列を用いることで位相オフセットの周期性によって生じるスプリアスが広帯域に拡散され、拡散効果によってスプリアスレベルが低減される。

【0052】

(他の実施の形態)

次に、本発明のPLL回路の第2の実施の形態について説明する。

図6は、本発明の第2の実施の形態によるPLL回路を示すブロック図である。第2の実施の形態のPLL回路は、第1の実施の形態と異なり擬似ランダムパターン生成回路4の入力クロックを分周回路7の分周信号SIGとする構成を採用している。

【0053】

本実施の形態の場合は、分周信号SIGは位相オフセット生成回路3により位相変調を受けているが、基本的には、定常状態では基準クロック信号REFと同期した信号である。そのため、分周信号SIGを擬似ランダムパターン生成回路4の入力クロックとしても、基準クロック信号REFを入力クロックとした構成と同様の動作を行うことが可能となり、第1の実施の形態と同様の効果が得られる。なお、リファレンス信号の入力側に設けた1/R分周回路8は、基準信号TCXOの周波数に対し電圧制御発振器6からR/N逓倍クロック信号を出力するためのものである。

【0054】

以上説明した実施の形態では、レファレンス信号等として基準クロック信号等のパルス信号を扱う例を示したが、レファレンス信号(及び/又は分周信号)として交流信号(正弦波信号)を対象とし、位相比較器も少なくとも一方の交流信号を入力する位相比較器を使用することが可能であることは明らかである。

【0055】

また、位相比較器としては必ずしもUP信号及びDOWN信号なる独立した2出力端子を有する回路を使用することは必須とするものではなく、分周信号の遅れ、進みに応じた正負の3値パルス信号、アナログ信号等の位相誤差信号を出力する位相比較器の使用が可能である。従って、チャージポンプ回路自体も位相比較器等に応じて省略することが可能であり、オフセット信号は基本的に位相比較器の出力側に設けることができる。

【産業上の利用可能性】

【0056】

本発明の利用分野として、LSI内部のクロック生成回路、無線通信機器等に使用される周波数シンセサイザなどに適用可能である。

【図面の簡単な説明】

【0057】

【図1】本発明の第1の実施の形態のPLL回路を示すブロック図である。

【図2】オフセット生成回路3の構成を示す図である。

【図3】擬似ランダムパターン生成回路4の構成例を示す図である。

【図4】本実施の形態のPLL回路の動作を示すタイミングチャートである。

【図5】位相比較器1の位相比較特性を示す図である。

【図6】本発明の第2の実施の形態のPLL回路を示すブロック図である。

【図7】位相比較器の不感帯の影響を小さくした従来のPLL回路のブロック図を示す図である

【図8】従来のPLL回路の動作を示すタイミングチャートである。

【符号の説明】

【0058】

1 位相比較器

2 チャージポンプ回路(CP回路)

21、22 定電流源回路

23、24 スイッチ

25 インバータ回路

3 オフセット生成回路

31 シフトレジスタ

32 排他的論理和回路(EXOR回路)

4 擬似ランダムパターン生成回路

5 ループフィルタ

6 電圧制御発振器

7 1/N分周回路

71 常位相誤差生成回路

72 遅延回路

73 インバータ回路

74 AND論理回路

75 スイッチ

76 定電流源回路

【技術分野】

【0001】

本発明は、PLL回路に関し、特にリファレンス信号に位相同期した逓倍信号を出力するPLL回路に関する。

【背景技術】

【0002】

PLL回路はリファレンスクロック信号に位相同期した逓倍クロック信号を得る等のために広く使用されているが、PLL回路で生成されるクロック信号の精度を決めるものの1つとして位相雑音の程度が挙げられ、位相雑音のレベルが大きいほどクロック信号の精度は劣化する。

【0003】

位相雑音を大きくする原因の1つとしては位相比較器の位相比較特性に生じる非線形領域の影響が挙げられる。位相比較器の非線形領域とは、2つの入力信号の間の位相差に対応して適正な位相誤差信号を出力しない領域であり、典型的にはデバイスの伝搬遅延の影響などにより2つの入力信号の位相差ゼロ付近の正負に亘る一定幅の特性領域(以下、「不感帯」という。)である。不感帯では位相差があっても位相誤差信号としてゼロ(0)の出力特性や、位相差に対し線形でない出力特性を示す。また、この不感帯はPLL回路の動作上はリファレンス信号と逓倍信号である発振出力信号の間で位相差があっても適正な位相誤差信号が出力されず位相同期(負帰還制御)が適正にかからない領域である。

【0004】

位相比較器の特性に不感帯が存在するとその領域では位相同期がかからないことから位相変動が生じて位相雑音が大きくなりPLLの特性が劣化する。そのため低位相雑音のPLL回路を構成するためには位相比較器の不感帯の影響を小さくする必要がある。

【0005】

図7は、位相比較器の不感帯の影響を小さくした従来のPLL回路のブロック図を示す図である(特許文献1参照)。

このPLL回路は、位相比較器1、チャージポンプ回路2、ループフィルタ5、電圧制御発振器6、分周回路7及び定常位相誤差生成回路71を備えており、定常位相誤差生成回路71は、遅延回路72、インバータ回路73、AND論理回路74、スイッチ75及び定電流源回路76から構成される。

【0006】

位相比較器1の入力には基準クロック信号REFと、電圧制御発振器6の発振出力を分周回路7で分周した分周信号SIGとが入力され、位相比較器1は両入力信号の位相差に対応して、位相が進んでいるか遅れているかに応じてそれぞれUP信号又はDOWN信号を生成し、チャージポンプ回路2に出力する。チャージポンプ回路2は前記UP信号及びDOWN信号に基づく位相差電流を生成しループフィルタ5に出力する。ループフィルタ5はさらに定常位相誤差生成回路71からの定常的なオフセット電流が加えられる。

【0007】

定常位相誤差生成回路71は、ループフィルタ5に対するオフセット電流をスイッチ75を介して定電流源回路76から加えるように構成され、前記スイッチ75は、基準クロック信号REFを遅延回路72とインバータ回路73を介して時間的に遅延させ反転させた信号と、前記基準クロック信号REFとをAND論理回路74により論理をとることにより、基準クロック信号REFのパルスの前縁部分で発生したパルス信号SWにより開閉(オン/オフ)制御される。

【0008】

ループフィルタ5は位相差電流とオフセット電流を入力し平滑した制御電圧を出力し、帰還信号として電圧制御発振器6の周波数制御部を制御し、電圧制御発振器6からは逓倍クロック信号OUTが発振され、さらに逓倍クロック信号OUTは1/N分周回路7で1/N分周され、その分周信号SIGは位相比較器1の入力の一方としてフィードバックされる。

【0009】

次に、従来のPLL回路の動作をタイミングチャートにより説明する。

図8は従来のPLL回路の動作を示すタイミングチャートである。PLL回路がロック(位相同期)した定常状態でのオフセット電流、UP信号及びDOWN信号の出力の様子を示している。

【0010】

同図において信号(a)は前記基準クロック信号REFであり、信号(d)は前記分周回路7からの分周信号SIG(電圧制御発振器6の発振出力を1/N分周した信号)である。また、信号(b)はAND論理回路74からのパルス信号SWであり、そのハイレベル(“1”)の間でスイッチ75をオン状態とし、定電流源回路76から信号(c)に示すような負のオフセット電流(−Ioff)をループフィルタ5に加える。

【0011】

本例では、パルス状の負のオフセット電流(c)により、ループフィルタ5から平滑した信号として負にオフセットされた制御電圧信号が出力され電圧制御発振器6の発信周波数が制御され、分周信号SIG(d)が基準クロック信号REF(a)より一定位相遅れて位相同期する状態を示しており、位相比較器1からは負帰還信号としてUP信号(e)のパルスのみがチャージポンプ回路2に出力されている。

【0012】

以上により通常のPLL回路では位相がロックした定常状態では基準クロック信号REF(a)と分周信号SIG(d)の位相は揃っており、UP信号、DOWN信号は共に現れないのであるが、このPLL回路では定常位相誤差生成回路71によってオフセット電流がループフィルタ5に流れるように構成されているため、定常状態であっても分周信号SIG(d)は基準クロック信号REFに対して位相差を持った状態となる。

【0013】

具体的にはAND論理回路74の出力が“1”の間は、定電流源回路76によりループフィルタ5からオフセット電流が引き込まれるため、ループフィルタ5の出力電圧は低下する。その結果、分周信号SIGの位相は常に遅れ状態になり、位相比較器1からはUP信号が常に出力される。

【0014】

ここで、オフセット電流による位相変化量を不感帯の幅を超えるように設定すると、位相比較器1の入力信号である基準クロック信号REFと分周信号SIGは、常に不感帯幅以上の位相差を持った状態となる。

【0015】

その結果、分周信号SIGは基準クロック信号REFと位相比較特性の不感帯の範囲外の前記位相差の点にロックさせることができるから不感帯の影響を低減することが可能である。

【0016】

【特許文献1】特開昭62−23620号公報

【発明の開示】

【発明が解決しようとする課題】

【0017】

従来のPLL回路によれば、位相比較特性の不感帯により生じる位相雑音の発生を電圧制御発振器の発振出力に位相オフセットを与えることにより抑制することを可能としているものの、この原理では基準クロック信号REFのパルスのエッジから一定幅の周期的なパルス信号を生成し、一定極性のパルス状のオフセット電流としてループフィルタに加えるものであるから、一方向のオフセットの定常的な加算により定常位相誤差が発生するとともに、周期的なオフセット電流の加算によりループフィルタの出力の制御電圧(帰還信号)に周期的な変動を残留させ電圧制御発振器の発振周波数の変動を引き起こすのでスプリアスのレベルを大きくするという問題がある。

【0018】

従って、従来のPLL回路では位相雑音を抑制できても、定常位相誤差が発生するのに加えスプリアスレベルが大きくなり、PLL回路が生成するクロック信号の精度は充分に向上させることはできない。

【0019】

以上のように従来のPLL回路は位相同期特性の劣化の原因に関連する次のような2つの問題点がある。

第1の問題点は、常に一方向のオフセットを与えるため位相比較器の出力には常に一方向の位相誤差信号が現れ、それが電圧制御発振器の出力信号の定常位相誤差として現れる点である。

【0020】

第2の問題点は、電圧制御発振器の制御電圧がリファレンス信号に同期して周期的に変動するために、周期的な定常位相誤差により電圧制御発振器の出力信号にスプリアスが発生するという点である。

【0021】

(目的)

本発明は、以上の問題を解決するものであり、位相比較器の不感帯による位相雑音を低減させるとともに、定常位相誤差とスプリアスレベルをも低減したPLL回路を提供することにある。

【課題を解決するための手段】

【0022】

本発明のPLL回路は、電圧制御発振器と、入力基準信号と前記電圧制御発振器の分周信号とを位相比較する位相比較器と、前記位相比較器の出力を平滑するループフィルタを介して前記電圧制御発振器を制御するPLL回路に関し、擬似ランダムパターンの2値の論理レベルにより位相比較器の不感帯の幅を超える正及び負の位相オフセット与えるオフセット信号を生成し位相比較器の出力側に供給するオフセット生成回路を備えることを特徴とする。

【0023】

また、前記擬似ランダムパターンは、M系列信号であり、前記M系列信号は、前記位相比較器に入力するリファレンス信号により駆動されるM系列信号発生器により発生され、又は、前記位相比較器に入力する電圧制御発振回路の出力の分周信号により駆動されるM系列信号発生器により発生されることを特徴とする。

【0024】

更に、前記オフセット生成回路は、擬似ランダムパターンにより相補的に開閉動作する2つのスイッチを介してそれぞれ異なる極性のオフセット信号を供給するように構成し、前記オフセット信号は、定電流として供給することを特徴とする。

【0025】

また、前記位相比較器の出力にチャージポンプ回路を備え、前記位相比較器は、リファレンス信号と電圧制御発振器の出力の分周信号の位相とを比較し、リファレンス信号に対し前記分周信号の位相の進み及び遅れに応じたパルス幅を有する位相の遅れ制御パルス及び進み制御パルスを出力することを特徴とする。

【0026】

より具体的には本発明のPLL回路は、基準クロック信号REFと分周信号SIGの位相を比較して、分周信号SIGの周波数が低い場合にはパルス状のエッジ位相差をアップ制御信号UPとして出力し、また分周信号SIGの周波数が高い場合にはパルス状のエッジ位相差をダウン制御信号DOWNとして出力する位相比較器1と、これらUP信号、DOWN信号に基づき電流を出力するチャージポンプ回路2と、擬似ランダムパターンであるM系列信号を生成する擬似ランダムパターン生成回路4と、上記M系列信号に応じてチャージポンプ回路2の出力電流に正及び負のオフセット電流を加えるオフセット生成回路3と、オフセット生成回路3から出力される上記オフセット電流が加わった位相差電流に応じて、電圧制御発振器の制御電圧を出力するループフィルタ5と、前記制御電圧が入力され、前記制御電圧に応じた逓倍クロック信号を出力する電圧制御発振器6と、前記逓倍クロック信号が入力されこの逓倍クロック信号を分周した前記分周信号SIGを出力する1/N分周回路7とを備える。(図1)

【0027】

(作用)

本発明によれば、オフセット生成回路によりM系列信号等の擬似ランダムパターンに応じてチャージポンプ等から出力される電流に正及び負のオフセット電流を加えられる。ここで、オフセット電流は、電圧制御発振器出力に不感帯幅より大きい位相変化を起こさせる。ランダムなオフセット電流をPLLの帰還信号に常に発生させることによって、位相比較器の入力信号は常に不感帯幅を超える位相差を持つようになり位相比較器の不感帯を避けてPLLがロックする。

【発明の効果】

【0028】

本発明によれば、電圧制御発振器への帰還信号に、擬似ランダムパターンの2値の論理レベルにより位相比較器の不感帯の幅を超える正及び負の位相オフセット与えることにより、PLL回路の同期動作を位相比較器の不感帯を避けてロックさせることができるから、位相雑音を抑制できるとともに、正負のランダムな位相オフセットにより定常位相誤差の発生を防止することができる。

【0029】

また、擬似ランダムパターンとして十分長い周期のM系列を用いることで、定常位相誤差の低減に加えて、位相オフセットの周期性によって生じるスプリアスが広帯域に拡散させることができるので、拡散効果によってスプリアスのレベルを低減させることができる。

【発明を実施するための最良の形態】

【0030】

(構成の説明)

次に、本発明の実施の形態について図面を参照して詳細に説明する。

図1は、本発明の第1の実施の形態によるPLL回路を示すブロック図である。本実施の形態は位相同期の基準となるリファレンス信号は基準クロック信号とし、電圧制御発振器から逓倍クロック信号を出力する例を示している。1は位相比較器(PD)、2はチャージポンプ回路(CP)、3はオフセット生成回路、4は擬似ランダムパターン生成回路、5はループフィルタ(LPF)、6は電圧制御発振器(VCO)、7は1/N分周回路(1/N)である。

【0031】

位相比較器1には基準クロック信号REFと分周回路7の分周信号SIGが入力され、出力はチャージポンプ回路2に入力される。位相比較器1は基準クロック信号REFと分周信号SIGの位相を比較して、分周信号SIGの周波数が基準クロック信号REFの周波数より低い場合にはパルス状のエッジ位相差(基準クロック信号REFと分周信号SIGのパルスのエッジ間の位相差)をアップ制御信号UP(UP信号)として出力し、また分周信号SIGの周波数が基準クロック信号REFの周波数より高い場合にはパルス状のエッジ位相差をダウン制御信号DOWN(DOWN信号)として出力する。つまり、基準クロック信号REFに対し前記分周信号SIGの位相の進み及び遅れに応じたパルス幅を有する位相の遅れ制御パルス及び進み制御パルスを出力する。

【0032】

チャージポンプ回路2は、これらUP信号、DOWN信号を入力し、UP信号、DOWN信号に基づき位相差電流をオフセット生成回路3に出力する。具体的にはUP信号のパルス幅に応じた時間だけチャージポンプ回路2内の充放電コンデンサ又はループフィルタ側コンデンサに電荷をチャージし、DOWN信号のパルス幅に応じた時間だけ該コンデンサの電荷をディスチャージするように位相差電流を出力する。

【0033】

また、擬似ランダムパターン生成回路4は、基準クロック信号REFを入力クロックとして、オフセット生成回路3に2値の論理レベルでなる擬似ランダムパターンを出力する。

【0034】

オフセット生成回路3は、チャージポンプ回路2と擬似ランダムパターン生成回路4の出力を入力し、チャージポンプ回路2の出力である位相差電流に、擬似ランダムパターン生成回路4で生成する擬似ランダムパターンで制御されたオフセット電流を加え、オフセット電流を加えた位相差電流(位相比較電流)をループフィルタ5に出力する。

【0035】

ループフィルタ5は、ローパスフィルタで構成されオフセット生成回路3からの位相比較電流が入力され、電圧制御発振器6の制御電圧(帰還信号)を出力する。

【0036】

電圧制御発振器6は、ループフィルタ5の出力電圧によって発振周波数が制御され、逓倍クロック信号OUTを出力する。

【0037】

1/N分周回路7は、逓倍クロック信号OUTを入力とし、1/N分周された分周信号SIGを位相比較器1に出力する。

【0038】

図2は、オフセット生成回路3の構成を示す図である。同図により前記位相差電流の生成動作の詳細について説明する。

オフセット生成回路3は、接地及び電源VDDに接続された互いに異なる方向(極性)の電流を出力するの2つの定電流源回路21、22と、各定電流源回路21、22とチャージポンプ回路2とループフィルタ5の接続線との間にそれぞれ接続された2つのスイッチ23、24と、擬似ランダムパターン回路4の出力であるM系列信号SWを2つのスイッチ23、24の制御信号とし、各定電流源回路21、22の何れかを前記接続線へ相補的に接続(オン)、非接続(オフ)させるように設けたインバータ回路25とから構成される。

【0039】

スイッチ23、24は、制御信号が“1”のときにオン(接続)し、制御信号が“0”のときにオフ(非接続)となる。M系列信号SWが“0”であれば定電流源回路22によりオフセット電流をループフィルタ5に流し込み(以下、流し込むオフセット電流を正のオフセット電流+Ioff)、M系列信号SWが“1“であれば定電流源回路21によりオフセット電流をループフィルタ5から引き込む(以下、引き込むオフセット電流を負のオフセット電流−Ioff)ように動作する。ここで、定電流源回路21、22の電流値はともに同一の電流値Ioffであり、位相比較器1のもつ不感帯幅φを超える位相変化を電圧制御発振器に起こさせる大きさの電流値である。

【0040】

次に、擬似ランダムパターン生成回路4の構成及び動作の詳細について説明する。

擬似ランダムパターン生成回路4は、主に、シフトレジスタと、該シフトレジスタの出力をその入力に帰還する1ないし複数の排他的論理和回路(EXOR回路)とで構成されるM系列発生器が利用可能である。このようなM系列発生器の例としては、各種の文献に記載されている(例えば、今井秀樹著「符号理論」、電子情報通信学会、1990年、W.W.Peterson著「Error Correcting Codes」、The M.I.T. Press、1961年、参照)。

【0041】

図3は擬似ランダムパターン生成回路の構成例を示す図である。本実施の形態で使用するM系列発生器の例を示す図である。次数25の原始多項式であるx25+x3+1を用いたM系列発生器を示している。

基準クロック信号REFをクロックとして動作する25段のフリップフロップからなるシフトレジスタ31とEXOR回路32から構成される。少なくとも1つのフリップフロップの初期値を1とすることで所望のM系列を出力する。またこのときのM系列信号の周期は225−1=33,554,431クロックであり、“0”が16,777,215回、“1”が16,777,216回現れる。一般的にM系列は1周期中で生じる“1”の回数が“0”の回数より1回だけ多く現れる性質を持っている。

【0042】

(動作の説明)

次に、本実施の形態のPLL回路の動作をタイミングチャートにより説明する。

図4は、本実施の形態のPLL回路の動作を示すタイミングチャートである。PLL回路がロック(位相同期)した定常状態でのオフセット電流、UP信号及びDOWN信号の変化等を示している。

【0043】

同図において信号(a)は基準クロック信号REFであり、信号(d)は1/N分周回路7からの分周信号SIG(電圧制御発振器6の発振出力を1/N分周した信号)である。また、信号(b)は基準クロック信号REF(a)で動作し該信号REF(a)に同期したM系列信号SWであり、その“1”の論理状態で、図2に示すスイッチ23をオン状態とし、定電流源回路21から信号(c)に示すような負のオフセット電流(−Ioff)をループフィルタ5に加え、“0”の論理状態で、図2に示すスイッチ24をオン状態とし、定電流源回路22から信号(c)に示すような正のオフセット電流(+Ioff)をループフィルタ5に加える。

【0044】

図4ではパルス状の擬似ランダムな正及び負のオフセットを生じさせる信号(c)がチャージポンプ回路2の出力に加算されることにより、ループフィルタ5からの平滑した信号として負及び正にオフセットされた制御電圧が出力され、電圧制御発振器6の周波数制御部が制御される。

【0045】

M系列信号SWが“0”の場合は、ループフィルタ5にオフセット電流+Ioffが加えられるため、ループフィルタ5の出力電圧は上がり分周信号SIGの位相は進み状態になる。M系列信号SWが“1”の場合は、ループフィルタ5にオフセット電流−Ioffが加えられるため、ループフィルタ5の出力電圧は下がり分周信号SIGの位相は遅れ状態になる。

【0046】

ここで、オフセット電流+/−Ioffによる分周信号SIGの位相変化を+/−θとすると、定常状態では位相のバランスをとるために、オフセット電流による位相変動をチャージポンプ2出力の位相差電流で相殺しなければならない。その結果、分周信号SIGは基準クロック信号REFに対して常に−/+θだけの位相差を持った状態でロックすることになる。

【0047】

この例では、位相比較器1からは、正のオフセット電流の加算後にDOWN信号(f)のパルスが出力され、負のオフセット電流の加算後にUP信号(e)のパルスが出力され、分周信号SIG(d)は、基準クロック信号REF(a)に対し正負のオフセット電流に応じて一定位相(θ)の進み(+θ)又は遅れ(−θ)のパルス信号として出力され、PLL回路はランダムな±θのオフセット位相で位相同期状態となる。

【0048】

以上により通常のPLL回路では位相がロックした定常状態では基準クロック信号REF(a)と分周信号SIG(d)の位相は揃っており、UP信号、DOWN信号ともに現れないのであるが、本発明のPLL回路では、M系列信号SWによってオフセット電流が常にループフィルタ5に流れるように構成されているため、定常状態であっても分周信号SIG(d)は基準クロック信号REFに対して位相差を持った状態となり、UP信号、DOWN信号が現れる。

【0049】

図5は、本実施の形態の位相比較器の位相比較特性を示す図である。位相比較器1の入力信号の位相差(横軸)と位相比較器1の制御パルスによって生じるチャージポンプ出力電流(CP電流、縦軸)との関係を示したものである。位相比較器1の位相比較特性としては、位相差0付近において位相比較器1を構成する素子の応答遅延などの理由で非線形特性が現れており、不感帯(不感帯幅φ)が存在する。そのため、図5に示すように、CP電流も位相差0付近で不感帯により非線形な振る舞いを生じる。

【0050】

通常、PLL回路がロックした定常状態は、特性曲線61の位相差0付近での動作となるが、本発明のPLL回路では、常に±θの位相差を持つことになるため、図5に示すように、θ≧φに設定することによりチャージポンプ出力は常に不感帯のない理想的な線形特性をもつ領域で動作を行うことになる。その結果、不感帯の影響による位相雑音を低減することが可能となる。

【0051】

また、前述したように、M系列は1周期中で生じる“1”の回数が“0”の回数より1回だけ多いという性質をもつため、1回だけ余分に負のオフセット電流が生じる。この余分なオフセット電流は定常位相誤差となるが、1周期で平均すれば、この定常位相誤差はM系列の周期に反比例して小さくなる。そのため、十分長い周期のM系列を用いることで定常位相誤差を低減することができる。さらには、十分長い周期のM系列を用いることで位相オフセットの周期性によって生じるスプリアスが広帯域に拡散され、拡散効果によってスプリアスレベルが低減される。

【0052】

(他の実施の形態)

次に、本発明のPLL回路の第2の実施の形態について説明する。

図6は、本発明の第2の実施の形態によるPLL回路を示すブロック図である。第2の実施の形態のPLL回路は、第1の実施の形態と異なり擬似ランダムパターン生成回路4の入力クロックを分周回路7の分周信号SIGとする構成を採用している。

【0053】

本実施の形態の場合は、分周信号SIGは位相オフセット生成回路3により位相変調を受けているが、基本的には、定常状態では基準クロック信号REFと同期した信号である。そのため、分周信号SIGを擬似ランダムパターン生成回路4の入力クロックとしても、基準クロック信号REFを入力クロックとした構成と同様の動作を行うことが可能となり、第1の実施の形態と同様の効果が得られる。なお、リファレンス信号の入力側に設けた1/R分周回路8は、基準信号TCXOの周波数に対し電圧制御発振器6からR/N逓倍クロック信号を出力するためのものである。

【0054】

以上説明した実施の形態では、レファレンス信号等として基準クロック信号等のパルス信号を扱う例を示したが、レファレンス信号(及び/又は分周信号)として交流信号(正弦波信号)を対象とし、位相比較器も少なくとも一方の交流信号を入力する位相比較器を使用することが可能であることは明らかである。

【0055】

また、位相比較器としては必ずしもUP信号及びDOWN信号なる独立した2出力端子を有する回路を使用することは必須とするものではなく、分周信号の遅れ、進みに応じた正負の3値パルス信号、アナログ信号等の位相誤差信号を出力する位相比較器の使用が可能である。従って、チャージポンプ回路自体も位相比較器等に応じて省略することが可能であり、オフセット信号は基本的に位相比較器の出力側に設けることができる。

【産業上の利用可能性】

【0056】

本発明の利用分野として、LSI内部のクロック生成回路、無線通信機器等に使用される周波数シンセサイザなどに適用可能である。

【図面の簡単な説明】

【0057】

【図1】本発明の第1の実施の形態のPLL回路を示すブロック図である。

【図2】オフセット生成回路3の構成を示す図である。

【図3】擬似ランダムパターン生成回路4の構成例を示す図である。

【図4】本実施の形態のPLL回路の動作を示すタイミングチャートである。

【図5】位相比較器1の位相比較特性を示す図である。

【図6】本発明の第2の実施の形態のPLL回路を示すブロック図である。

【図7】位相比較器の不感帯の影響を小さくした従来のPLL回路のブロック図を示す図である

【図8】従来のPLL回路の動作を示すタイミングチャートである。

【符号の説明】

【0058】

1 位相比較器

2 チャージポンプ回路(CP回路)

21、22 定電流源回路

23、24 スイッチ

25 インバータ回路

3 オフセット生成回路

31 シフトレジスタ

32 排他的論理和回路(EXOR回路)

4 擬似ランダムパターン生成回路

5 ループフィルタ

6 電圧制御発振器

7 1/N分周回路

71 常位相誤差生成回路

72 遅延回路

73 インバータ回路

74 AND論理回路

75 スイッチ

76 定電流源回路

【特許請求の範囲】

【請求項1】

擬似ランダムパターンの2値の論理レベルにより位相比較器の不感帯の幅を超える正及び負の位相オフセット与えるオフセット信号を生成し位相比較器の出力側に供給するオフセット生成回路を備えることを特徴とするPLL回路。

【請求項2】

前記擬似ランダムパターンは、M系列信号であることを特徴とする請求項1記載のPLL回路。

【請求項3】

前記M系列信号は、前記位相比較器に入力するリファレンス信号により駆動されるM系列信号発生器により発生されることを特徴とする請求項2記載のPLL回路。

【請求項4】

前記M系列信号は、前記位相比較器に入力する電圧制御発振回路の出力の分周信号により駆動されるM系列信号発生器により発生されることを特徴とする請求項2記載のPLL回路。

【請求項5】

前記オフセット生成回路は、擬似ランダムパターンにより相補的に開閉動作する2つのスイッチを介してそれぞれ異なる極性のオフセット信号を供給するように構成したことを特徴とする請求項1ないし4の何れかの請求項記載のPLL回路。

【請求項6】

前記オフセット信号は、定電流として供給することを特徴とする請求項5記載のPLL回路。

【請求項7】

前記位相比較器の出力にチャージポンプ回路を備えることを特徴とする請求項1ないし6の何れかの請求項記載のPLL回路。

【請求項8】

前記位相比較器は、リファレンス信号と電圧制御発振器の出力の分周信号の位相とを比較し、リファレンス信号に対し前記分周信号の位相の進み及び遅れに応じたパルス幅を有する位相の遅れ制御パルス及び進み制御パルスを出力することを特徴とする請求項7記載のPLL回路。

【請求項1】

擬似ランダムパターンの2値の論理レベルにより位相比較器の不感帯の幅を超える正及び負の位相オフセット与えるオフセット信号を生成し位相比較器の出力側に供給するオフセット生成回路を備えることを特徴とするPLL回路。

【請求項2】

前記擬似ランダムパターンは、M系列信号であることを特徴とする請求項1記載のPLL回路。

【請求項3】

前記M系列信号は、前記位相比較器に入力するリファレンス信号により駆動されるM系列信号発生器により発生されることを特徴とする請求項2記載のPLL回路。

【請求項4】

前記M系列信号は、前記位相比較器に入力する電圧制御発振回路の出力の分周信号により駆動されるM系列信号発生器により発生されることを特徴とする請求項2記載のPLL回路。

【請求項5】

前記オフセット生成回路は、擬似ランダムパターンにより相補的に開閉動作する2つのスイッチを介してそれぞれ異なる極性のオフセット信号を供給するように構成したことを特徴とする請求項1ないし4の何れかの請求項記載のPLL回路。

【請求項6】

前記オフセット信号は、定電流として供給することを特徴とする請求項5記載のPLL回路。

【請求項7】

前記位相比較器の出力にチャージポンプ回路を備えることを特徴とする請求項1ないし6の何れかの請求項記載のPLL回路。

【請求項8】

前記位相比較器は、リファレンス信号と電圧制御発振器の出力の分周信号の位相とを比較し、リファレンス信号に対し前記分周信号の位相の進み及び遅れに応じたパルス幅を有する位相の遅れ制御パルス及び進み制御パルスを出力することを特徴とする請求項7記載のPLL回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2006−129399(P2006−129399A)

【公開日】平成18年5月18日(2006.5.18)

【国際特許分類】

【出願番号】特願2004−318524(P2004−318524)

【出願日】平成16年11月1日(2004.11.1)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

【公開日】平成18年5月18日(2006.5.18)

【国際特許分類】

【出願日】平成16年11月1日(2004.11.1)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

[ Back to top ]