PLL回路

【課題】 PLL回路において製造ばらつきによらず広い周波数帯域且つ大幅なジッタ低減を簡単な構成で実現する。

【解決手段】 位相比較器と、ローパスフィルタと、電圧制御発振器とからなるPLL回路において、電圧制御発振器は、ローパスフィルタから出力される制御電圧を電流に変換する電圧電流変換回路と、該電流により発振周波数を制御されるリング状に接続された複数の差動インバータ回路より構成する発振回路とからなる。発振回路を構成するトランジスタのゲート長及びゲート幅を制御して位相雑音やジッタノイズを減少させる。

【解決手段】 位相比較器と、ローパスフィルタと、電圧制御発振器とからなるPLL回路において、電圧制御発振器は、ローパスフィルタから出力される制御電圧を電流に変換する電圧電流変換回路と、該電流により発振周波数を制御されるリング状に接続された複数の差動インバータ回路より構成する発振回路とからなる。発振回路を構成するトランジスタのゲート長及びゲート幅を制御して位相雑音やジッタノイズを減少させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、PLL回路に関し、特に低ジッタで広範囲な発振可能周波数範囲を必要とする電圧電流変換回路が使用される電圧制御型発振器を備えたPLL回路に関するものである。

【背景技術】

【0002】

図1はPLL回路の基本構成を示すブロック図である。PLL回路は、位相比較器10、LPF(ループフィルタ)12、電圧制御発振器(VCO)14からなる。PLLブロックの各動作を説明する。基準信号Frと電圧制御発信器の出力信号Fvを位相比較器10に入力して誤差分を出力する。この後LPF12で位相比較より出力された誤差分の信号の直流分を取り出し制御電圧Fvを出力する。これらの構成ループの繰り返しによって電圧制御発振器14の出力信号は基準信号に正確に合わせることができる。PLL回路は、逓倍用PLLや周波数シンセサイザに応用できる。

【0003】

図2は、電圧制御発振器14の基本構成を示すブロック図である。電圧制御発振器14は、LPF12より入力される制御電圧に応じて電流を出力する電圧電流変換回路20と、その電流に応じた発振周波数を出力する電流制御発振器22により構成される。

【0004】

図3は電圧電流変換回路20の従来例を示す。LPF12より入力される制御電圧VCOINをゲートに印加されたNMOSトランジスタM0のソース側は抵抗R0を介してグランドに接地され、そのドレイン側は、PMOSトランジスタM1および抵抗R0と抵抗R1とを並列に介してグランドに接地されている。PMOSトランジスタM1にはNMOSトランジスタM0に流れる電流と抵抗R1に流れる電流の和が流れる。PMOSトランジスタM1のゲートをPMOSトランジスタM2のゲートとドレーンに接続して、PMOSトランジスタM1のゲート電圧をPMOSトランジスタM2に印加する。さらに、トランジスタM2,M3,M4でカレントミラー回路を構成して、トランジスタM2に流れる電流をM3,M4,M5のMOSトランジスタでカレントミラーで折り返して、電流制御型発振回路22の制御ノードNG,PGを形成する。

【0005】

図4は電圧電流変換回路20の他の従来例を示す。反転端子を入力子とする演算増幅回路AMPの出力がPMOSトランジスタM0に与えられており、PMOSトランジスタM0のドレイン側が外付けの抵抗Rを介してグランドに接地され、ゲート側は電源に接続されている。この回路は抵抗Rの両端に入力端子VCOINに印加される電圧と同じ電圧を印加させて出力端子に電流を発生させるものである。PMOSトランジスタM0に流れる電流IoutはIout=VCOIN/Rとなり、入力電圧に比例した電流を取り出すことができる。PMOSトランジスタM1は、PMOSトランジスタM0と等しいゲート電圧を与えることで、PMOSトランジスタM0に流れる電流と等しい電流を流す。

【0006】

図5は、電流制御発振器22における差動インバータの構成例を示す。図5において、M0,M1はPMOS型トランジスタでありM2,M3,M4はNMOS型トランジスタである。トランジスタM0,M1のソースには電源VCCが供給され、トランジスタM0のドレインにはトランジスタM2のドレインが接続され、この接続点から差動出力Vo+が出力される。トランジスタM1のドレインにはトランジスタM3のドレインが接続され、この接続点から差動出力Vo-が出力される。トランジスタM2のゲートには差動入力Vi+が入力され、トランジスタM3のゲートには差動入力Vi-が入力される。トランジスタM2、M3のソースはトランジスタM4のドレインに接続され、トランジスタM4のゲートにはバイアス電圧Vnが印加され、ソースはグランドに接地される。次に動作について説明する。トランジスタM0、M1は、線形領域で動作するようにバイアス電圧VPが加えられ夫々抵抗Rpとして用い、また、トランジスタM4は、飽和領域で動作するようにバイアス電圧Vnが加えられ、電流源として用いられる。

【0007】

PLL回路は、入力の位相差で動作するため位相雑音又はジッタの影響を受けやすいという問題がある。PLL回路設計に際しては、出力周波数の含むジッタ値が重要な電気的特性であり、様々な低ジッタ化が計られている。出力ジッタの原因としては大きく分けて2つ考えられる。1つは外部からPLL回路への雑音の混入、そしてもう1つはPLL回路(特にVCO14)が発生する雑音である。

【0008】

図6に理想的な出力スペクトラム(左側)と実際の出力スペクトラム(右側)を示す。VCO14が発生する位相雑音は、発振器を構成する素子そのものから注入され、出力周波数と出力振幅の両方に影響する。このうち影響が大きいのが出力周波数である。位相雑音は通常周波数領域で扱われる。理想的な発振器の出力スペクトルはインパルスで示されるのに対し、現実的な発振器の出力スペクトルは搬送波周波数の両側に広がるスカート特性を持つ。

【0009】

発振器を構成する素子が持つ雑音のうち、周波数近傍で雑音の影響が大きいのは1/F雑音である。1/F雑音はフリッカ雑音とも呼ばれ、その物理機構は明確化されていない。トランジスタ素子の製造工程において必然的に生じる、酸化膜中における不純物分布の不均一によっておこると概ね考えられている。

【0010】

式(1)は、HSPICE等の回路シミュレーションにおける標準MOSFETモデルであるBSIN3V3における1/F雑音(flicker noise)のモデルである。

【数1】

ここで、Fは発振周波数である。また、KFはフリッカーノイズ係数であり、AFはフリッカーノイズ指数であり、gmはゲート相互コンダクタンスであり、COXはゲート酸化膜キャパシタンスである。いずれもプロセス固有のパラメータである。また、Leffは有効チャネル長、Weffは有効チャネル幅である。

【0011】

図7にMOSFET(トランジスタ)の構造を示す。このMOSトランジスタは四端子デバイスでそれらの端子はドレイン、ゲートソース、基盤と呼ばれる。ソース、ドレイン接合はチャネル領域で反転層とつながっている。ソースとドレインの間にあるチャネルの長さはチャネル長(L)と呼ばれる。チャネル長に垂直な方向となるチャネルの幅は、チャネル幅(W)と呼ばれる。チャネルの電流を担う電荷のタイプによって、MOSFETはNチャネルかPチャネルのいずれかとなる。Nチャンネル型MOSFETでは、P型のSi基板の2ヶ所にn+型の電極を2つ作り、それぞれソース・ドレインとする。また、電極間のSi表面にSiO2の酸化膜を作り、さらにその上に金属を蒸着してゲートとする。チャンネル型の場合は、この説明とはnとp、電子と正孔が逆になるゲート電極に電圧をかけると、絶縁膜の下側で表面電位が変化し、ある程度以上の電圧がかかるとP型のSi基板にN型の反転層(チャンネル)ができる。すると、このチャンネルを通ってソースからドレインへと電子(P型の場合は正孔)が流れるようになり、電流が生じる。ゲート電圧を上げれば反転層は厚くなり、ドレイン電流は増える。逆にゲート電圧を下げると反転層は薄くなり、ドレイン電流は減る。以上が、MOSFETの動作原理である。

【0012】

一方、光ディスク用PLL回路等で必要とされる要件として、高周波発振かつ広いロックレンジの実現がある。高周波かつ広帯域を実現するにはPLL回路のVCO14を高速化する必要がある。CMOS差動インバータリング発振回路方式においては、広帯域なPLL回路を実現するのにもっとも一般的な方法であり、差動インバータ一段あたりのスキュー高速化のために構成トランジスタのゲート長L及びゲート幅Wを最小化する。またリングの差動インバータの段数を減らしリングのスキューを高速化することで、VCOの高速化を実現する。

【0013】

低ジッタ且つ広帯域のPLLに関する発明は従来からなされているが、電源や入力周波数等の外部起因する雑音に対する発明が多数を占める。そのうちPLLが生成するクロック信号に伴って発生する雑音による影響を低減する発明としては、次のようなものがある。

【0014】

特開2001−211055号公報に記載された回路では、中心周波数調整回路とこれによって制御される差動回路からなる遅延回路と加算回路をもち、遅延回路の数を調整することで広い周波数帯域を広げ、電源電圧による雑音を低減する。しかし位相雑音の観点から言えば、上記の回路は既存の回路より構成が複雑になることでVCO自身のジッタに対しては増大する。

また、外部雑音の対策用の回路を考案し、ジッタを低減するための発明には、特開2002−57574号公報に記載された回路があるが、トリプルウェル構造により基盤を通しての外部雑音を遮断する方法が有効である。

【特許文献1】特開2001−211055号公報

【特許文献2】特開2002−57574号公報

【発明の開示】

【発明が解決しようとする課題】

【0015】

位相雑音は、PLL回路のVCOの発振器における雑音の最上位の雑音源であり、ジッタ低減の観点からもこれを低減化することは非常に重要である。加えて、位相雑音は発振周波数の中心付近にあるため、フィルタリングでは完全除去することができない。位相雑音とジッタは、前者が周波数領域で扱われ、後者が時間領域で扱われるが、現象としては同一にとらえられる。したがってジッタ低減のためには、PLL回路の位相雑音を低く抑えることが重要となる。位相雑音はトランジスタの素子数に依存し、位相雑音を低く抑えるためにはPLL回路の構成をできるだけ少ないトランジスタ数で構成することが重要である。従来のジッタ低減技術では、ジッタを低減する機能を搭載するために、PLL回路の構成の複雑化による位相雑音の増大という問題が生じる。この問題を解消するためにはPLL回路をシンプルな構成で実現することが重要である。

【0016】

一方、PLL回路のVCO14の発振周波数は、電圧電流変換回路20及び電流制御発振回路22のプロセスのバラツキ、温度バラツキ、電源のバラツキにより変動する。中でもバラツキによる変動は、VCOの必要とされる発振周波数が高周波になるほど顕著になる。SLOWスピードのワースト条件(プロセスss、温度max,電源min,抵抗min)では仕様に必要なロックレンジを満たすことが難しくなり、一方HIGHスピードのワースト条件(プロセスff、温度min,電源max,抵抗min)ではオーバーレンジによるPLLの帰還ループのデッドロックが生じる場合がある。加えて、光ディスク書き込みクロック発生用PLLではCAV対応のため、広い範囲のロックレンジを満たし低速から高速にかけて一定のVCOゲインを実現することが課題となる。

【0017】

高周波発振かつ広帯域を実現するにはPLL回路のVCOを高速化する必要がある。CMOS差動インバータリング発振回路方式においては広帯域なPLL回路を実現するのにもっとも一般的な方法であり、差動インバータ一段あたりのスキュー高速化のために、構成トランジスタのゲート長L及びゲート幅Wを最小化する。またリングの差動インバータの段数を減らしリングのスキューを高速化することで、VCOの高速化を実現する。しかし、差動インバータ内の構成トランジスタを小面積化することは、発振周波数出力ノードに対する位相雑音への寄与を増大化する。リングの段数を減らすことは、広帯域化という面からは望ましくなく、一段あたりの遅延時間可変領域を増やす必要があり、安定した広範囲のロックレンジ実現は難しい。

【0018】

図3に示す従来例の電圧電流変換回路の課題として、使用する抵抗に内蔵ポリ抵抗を使用した場合、抵抗値がプロセス変動と温度変動をうけ±20%変動し、電圧電流変換特性に影響を及ぼすことがある。内蔵ポリ抵抗使用による抵抗バラツキの解決法としてバラツキの少ない外付抵抗を使用することが考えられるが、部品点数の増加、チップ面積大というデメリットがあるばかりでなく、センシティブなノードを外部に出すことで電圧電流変換回路に外部ノイズの混入のおそれがある。また、図4の電圧電流変換回路のように差動増幅回路の帰還ループで外付け抵抗を使用する回路の場合には、外付抵抗端子の寄生容量により、負帰還回路の帯域が低下し、PLLループ帯域の影響を受ける場合がある。

【0019】

概して広帯域なVCO14を制御する電圧電流変換回路20は、その精度要求から、構成の複雑化が避けられないのであるが、位相雑音を低減化しVCO本体が発生する雑音を低減するという目的のためには、構成回路を簡単化し、トランジスタ素子数を抑え、1/F雑音を取り除くことが重要である。

【0020】

この発明の目的は、以上のような課題を踏まえて、PLL回路において製造ばらつきによらず広い周波数帯域且つ大幅なジッタ低減を簡単な構成で実現することである。

【課題を解決するための手段】

【0021】

本発明に係るPLL回路は、基準信号と出力信号とを入力し誤差分を出力する位相比較器と、位相比較器より出力された信号の直流分を取り出し制御電圧を出力するループフィルタと、ループフィルタから入力される制御電圧に応じて前記出力信号を出力する電圧制御発振器とからなる。電圧制御発振器は、ループフィルタから出力される制御電圧を電流に変換する電圧電流変換回路と、該電流により発振周波数を制御されるリング状に接続された複数の差動インバータ回路より構成する発振回路とからなる。発振回路は、ゲートとドレインに電圧電流変換回路からの電流が入力されソースがグランドに接地される第二の電圧制御トランジスタと、ゲートが第二の電圧トランジスタのゲートに接続されソースがグランドに接地されてカレントミラー回路を構成するトランジスタと、このトランジスタのドレインにドレインとゲートが接続されソースが電源電圧に接続される第一の電圧制御トランジスタを備え、第一及び第二の電圧制御トランジスタは該複数の差動インバータ回路への第一と第二の制御電圧を生成する。各々の差動インバータ回路は、第一の制御電圧がゲートに入力され抵抗素子として動作する第三のトランジスタと、第三のトランジスタに直列に接続されゲートに差動入力が入力される第五のトランジスタとからなり差動出力を出力する一組が2つ並列に配置され、この二組に直列にドレインが接続されゲートに第一の制御電圧が入力され電流源となる第四のトランジスタを備える。第一及び第二の電圧制御トランジスタは、該第一及び第二の電圧制御トランジスタがそれぞれ制御する差動インバータの第三及び第四のトランジスタサイズよりゲート長及びゲート幅を共に等しい倍数だけ大きくしたトランジスタで構成する。

【0022】

好ましくは、前記PLL回路において、前記差動インバータ回路の第四のトランジスタは、第三のトランジスタのサイズよりゲート長及びゲート幅を共に等しい倍数だけ大きくしたトランジスタである。

【0023】

好ましくは、前記PLL回路において、前記電圧電流変換回路は、ゲートにループフィルタから入力される制御電圧が入力され、ソースに電流を決定するための可変抵抗回路が接続されるトランジスタを含み、可変抵抗回路は、直列または並列に接続された複数の抵抗からなる。さらに、可変抵抗回路の抵抗値を校正する校正回路を有する。前記校正回路は、たとえば、校正用の電流が前記可変抵抗回路のレプリカを流れるときの降下電圧を、基準電流が基準抵抗を流れるときの降下電圧を比較するコンパレータを備える。または、前記校正回路は、たとえば、ループフィルタから入力される制御電圧と、基準電流が基準抵抗を流れるときの降下電圧を比較するコンパレータを備える。

【発明の効果】

【0024】

PLL回路において、差動インバータの制御電圧を生成する第一の及び第二の電圧制御トランジスタは該第一及び第二の電圧制御トランジスタが制御する差動インバータの第三及び第四のトランジスタサイズよりゲート長及びゲート幅を等しい倍数だけ大きくしたトランジスタで構成することで、出力発振周波数の位相雑音がきわめて少なく低ジッタのPLLを実現できる。

【0025】

また、差動インバータは抵抗素子をなす第三トランジスタと差動信号が入力されるトランジスタと電流源を成す第四トランジスタとからなる差動回路により構成され、前記定電流源トランジスタは抵抗トランジスタサイズよりゲート長及びゲート幅を等しい倍数だけ大きくしたトランジスタにより構成することで、出力発振周波数の位相雑音がきわめて少なく低ジッタのPLLを実現できる。

【0026】

また、電圧電流変換回路は電流を決定する素子として直列または並列に接続された複数の抵抗を用い抵抗プロセスのばらつきを補正する回路を有し、プロセスバラツキによらずVCOリングが広範囲のロックレンジで一定のゲインを保持する調整機能を有することにより、抵抗のばらつきによらない制御電流を得ることができる。かつ、可変抵抗の制御部をPLL外部デジタル制御回路が持ち、PLL回路内部は簡単な構成ができる。これにより、回路内のトランジスタ数が抑えられることで、雑音成分を少なくし、トランジスタの位相雑音ジッタを抑え、かつ、広範囲なロックレンジを満たすことができる。

【発明を実施するための最良の形態】

【0027】

以下、本発明の実施の形態を添付の図面を参照して説明する。

【0028】

本発明の実施の形態のPLL回路は、図1に示した構成を備える。すなわち、PLL回路は、位相比較器10、LPF(ループフィルタ)12、電圧制御発振器(VCO)14からなる。基準信号FrとVCOの出力信号Fvが位相比較器10に入力されると誤差分が出力される。次に、LPF12は、位相比較器10より出力された信号(誤差分)の直流分を取り出し制御電圧を出力する。VCO14は、この制御電圧に応じて出力信号Fvを出力する。このループの繰り返しによってVCO14の出力信号は基準信号Frに正確に合わせられる。本発明のPLL回路では、以下に説明するVCO14を用いて、製造ばらつきによらず広い周波数帯域かつ大幅なジッタ低減を簡単な構成で実現する。

【0029】

図2に示すように、VCO14において、電圧電流変換回路20は、LPF12より入力される制御電圧に応じて電流を出力し、電流制御発振回路22は、その電流に応じた発振周波数を出力する。電流制御発振回路22は、LPF12からの電流により発振周波数を制御されるリング状に接続された複数の差動インバータ回路より構成する発振回路を含む。

【0030】

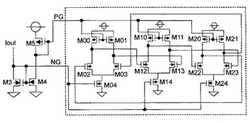

図8は、電流制御発振回路22の1例である。電圧電流変換回路20より入力される電流IoutがNMOSトランジスタM3のドレインとゲートに入力され、NMOSトランジスタM3のソースはグランドに接地される。NMOSトランジスタM3のゲートとドレインに入力されるノードをNGとする。NMOSトランジスタM4はソースをグランドに接地しゲートをNMOSトランジスタM3のゲートに接続して、カレントミラー回路を構成する。さらに、NMOSトランジスタM4のドレインはPMOSトランジスタM5のゲート及びドレインに接続され、このノードをPGとする。PMOSトランジスタM5のソースは電源に接続される。これによって入力電流IoutはM3,M4,M5と折り返され、複数の同一形状の差動増幅回路によって構成される3段のリング発振器(破線で囲まれた部分)にバイアスする。差動増幅回路において抵抗素子として動作するPMOSトランジスタM00,M01,M10,M11,…,MN0,MN1のゲートとノードPGが接続されることにより、PMOSトランジスタM5は第一のリング発振器の電圧制御トランジスタとなり、定電流素子として動作するNMOSトランジスタM04,M14、…,MN4のゲートとノードNGと接続され、よってNMOSトランジスタM5はリング発振器の第二の電圧制御トランジスタとなり、リング発振器の発振周波数を制御する。

【0031】

Ioutの電流を基に各リングに等しい電流値を伝えるには、従来ならばノードPGにて接続された第一の電圧制御トランジスタM5とリング抵抗素子であるPMOSトランジスタM00,M01,M10,M11,…,MN0,MN1のトランジスタサイズW及びLは等しくするものであり、同様にノードNGにて接続された第二の電圧制御トランジスタM3とリング定電流素子であるPMOSトランジスタM04,M14,…MN4のトランジスタサイズW、Lも等しくするものである。

【0032】

式(1)によりトランジスタのWまたはLを大きくすれば1/Fは低減する。すべてのトランジスタを大きくすることはチップ面積の面から現実的ではない。最も効果的な素子は周波数出力の上位に位置するリングの制御トランジスタである。第一の電圧制御トランジスタM5及び第二の電圧制御トランジスタM3はリング構成素子の上流に位置しており、発振周波数出力ノードにおける1/F雑音の影響の大きさからは必ずその影響度が高い。そこで、この素子をゲート幅及びゲート長を2倍以上の等倍にすることで、バイアス部の特性を変更することなく、効果的に位相雑音を低減できる。これにより、出力発振周波数の位相雑音がきわめて少なく低ジッタのPLL回路を実現できる。トランジスタ面積を大きくすることは、電源ノイズ等の外的ノイズに対する耐性強化も期待できる。リング構成素子のうち抵抗素子として動作するPMOSトランジスタM00,M01,M10,M11,…,MN0,MN1についてはVCO全体の位相雑音を減らすためには有効であるが、抵抗素子が大きくなることで寄生容量が増し、高速発振、広帯域のVCO設計の観点からは避けるべきである。

【0033】

たとえば、第一の電圧制御トランジスタM5及び第二の電圧制御トランジスタM3の雑音を小さくし、なおかつIoutの電流を等しく各リングに伝えるために、第一の電圧制御トランジスタM5のサイズ比β5=W5/L5は、リング構成素子であるNMOSトランジスタM04,M14,…,MN4のトランジスタサイズ比をβN=WN/LNとすると、W5=WP*N及びL5=LP*N(N:整数)とし、ゲート幅W、ゲート長Lともリング構成素子に比して等しくN倍とする。また、第二の電圧制御トランジスタM3のサイズ比β3=W3/L3は、リング構成素子であるPMOSトランジスタM00,M01,M10,M11,…,MN0,MN1のトランジスタサイズ比をβP=WP/LPとするとW3=WP*N及びL3=LP*N(N:整数)とし、W,Lともリング構成素子に比して等しくN倍とする。すなわち、差動インバータの制御電圧を生成する第一及び第二の電圧制御トランジスタは、その第一及び第二の電圧制御トランジスタが制御する差動インバータの第三及び第四のトランジスタサイズよりゲート長L及びゲート幅Wを共に等しい倍数だけ大きくしたトランジスタで構成する。

【0034】

また、リング定電流トランジスタM04,M14,…,MN4と抵抗トランジスタM00,M01,M10,M11,…,MN0,MN1のトランジスタサイズ関係はWN=WP*N及びLN=LP*N(N:整数)とする。すなわち、差動インバータは抵抗素子をなす第三トランジスタと差動信号が入力されるトランジスタと電流源を成す第四トランジスタとからなる差動回路により構成されていて、定電流源トランジスタM04,M14,…,MN4は抵抗トランジスタM00,M01,M10,M11,…,MN0,MN1のサイズよりゲート長及びゲート幅を共に等しい倍数だけ大きくしたトランジスタにより構成する。これにより、出力発振周波数の位相雑音がきわめて少なく低ジッタのPLL回路を実現できる。

【0035】

図9は、本発明の電圧電流変換回路20の1例を示す。位相雑音を低減化しVCO本体が発生する雑音を低減するという目的のためには、電圧電流変換回路20の構成を簡単化し、トランジスタ素子数を抑え、1/F雑音を取り除く。電流を決定する素子として可変抵抗回路を用い、抵抗プロセスのばらつきを簡単な校正で補正する。この回路では、VCO14の制御電圧VCOINがNMOSトランジスタM0のゲートに入力され、NMOSトランジスタM0のソースには、破線で囲んで示される可変抵抗回路が接続される。この可変抵抗回路では、N個の固定抵抗R0,R01,R02,…,R0Nの一端がNMOSトランジスタM0のソースに並列に接続され、かつ、それらの固定抵抗R00,R01,R02,…,R0Nの他端はそれぞれスイッチを介してグランドに接地される。夫々のスイッチは信号calsel0, calsel1, calsel2, …, calselNによって制御し、可変抵抗回路の抵抗値を可変とする。また、NMOSトランジスタM0のドレインはPMOSトランジスタM1のドレイン及びゲートに接続され、また、PMOSトランジスタM1のソースは電源に接続される。さらに、NMOSトランジスタM0のドレインはPMOSトランジスタM2,M3,M4,M5,M6のドレインに接続され、PMOSトランジスタM2,M3,M4,M5,M6のソースは電源に接続され、PMOSトランジスタM3,M4,M5,M6のドレインは夫々スイッチを介しM2のドレインと接続される。PMOSトランジスタM3,M4,M5,M6のスイッチを閉じると、出力電流Ioutが増加される。こうして、出力電流Ioutを可変とする。

【0036】

図9の下側に示すように、これらの抵抗値をキャリブレーション(校正)する回路では、固定抵抗R0、R01、R02,…,R0Nと等しい形状の固定抵抗R10,R11,R12,…,R1N(可変抵抗レプリカ)が信号calsel0,calsel1,calsel2,…,calselNによってそれぞれ制御されるスイッチを介してグランドに接地される。これらの抵抗を外付け抵抗R0とキャリブレートするため、定電流源IbiasをNMOSトランジスタM7のドレインとゲートに接続し、NMOSトランジスタM8のゲートと接続し、NMOSトランジスタM7,M8のソースはグランドに接地する。定電流源IbiasとNMOSトランジスタM7,M8は、カレントミラー構成にする。さらに、NMOSトランジスタM8のドレインとPMOSトランジスタM9のドレインとゲート及びPMOSトランジスタM10,M11のゲートを接続し、カレントミラー構成にする。PMOSトランジスタM9,M10,M11のソースは電源に接続する。PMOSトランジスタM10のドレインは、可変抵抗レプリカの固定抵抗R10,R11,R12,…,R1Nとコンパレータの一方の入力段に接続される。PMOSトランジスタM11のドレインは、R0とコンパレータの他方の入力段に接続され、これにより固定抵抗R10,R11,R12,…,R1NにはIbiasを基準とする電流Icalが流れ、外付け抵抗R0には同じくIbiasを基準とする電流Irefが流れる。デジタル制御回路よりスイッチcalsel0〜calsel1に対応したアドレスをインクリメントすることにより、コンパレータに入力される電圧が変動し、他方の入力段の電位と比較した結果をデジタル制御回路に通知してスイッチcalsel0-calsel1を制御することで、一定の抵抗値を得る。図10にキャリブレーションの動作フローを示す。初期設定Calsel0よりスタートしCalsel1,calsel2,…calselFの計16段階のキャリブレーションが行われ、各設定に応じた抵抗値が用意されている。ここで、スイッチごとに、calsel=i(i=0〜F)を設定し、コンパレータの出力が1であると、CAL_CODE=iをデジタル制御回路に出力する。こうして、抵抗値が基準抵抗R0と等しい場合コンパレータに1が出力され、検知したデジタル回路がcal_codeの数値をPLL回路に返し、火炎抵抗回路の抵抗値を決定する。

【0037】

このように、電圧電流変換回路20は、電流を決定する素子として直列または並列に接続された複数の抵抗(可変抵抗回路レプリカ)を用い抵抗プロセスのばらつきを補正する回路を有し、かつ、プロセスのバラツキによらずVCOリングが広範囲のロックレンジで一定のゲインを保持する調整機能を有する。こうして、高速化、広帯域なVCOの実現のために、線形性を保持し、かつ、抵抗とプロセスのばらつきを補正する電圧電流変換回路を簡単な構成で実現できる。これにより抵抗のばらつきによらない制御電流を得ることができる。かつ、可変抵抗の制御部をPLL外部デジタル制御回路が持ちPLL回路内部は簡単な構成ができることにより、回路内のトランジスタ数が抑えられる。このため、雑音成分を少なくし、トランジスタの位相雑音ジッタを抑え、且つ、広範囲なロックレンジを満たすことができる。

【0038】

図11は、本実施形態と従来のVCO回路の位相雑音シミュレーション結果を示す。本発明のVCO回路では、位相雑音がきわめて少ないことがわかる。また、VCO回路の位相雑音の実測結果結果では、RMSジッタは、従来回路では3.09%であったの対し、本発明のVCO回路では1.44%であった。

【0039】

また、図12は、本実施形態のVCO回路における入力電圧VCOINに対する出力周波数FoutのVF特性の実測結果を示す。ここで、SSはSLOWスピードのワースト条件を示し、FFはHIGHスピードのワースト条件を示し、TYPは典型的なスピードの条件を示す。TYPでは広い周波数範囲で線形性が得られている。

【0040】

図13は、電圧電流変換回路20の別の例を示す。図9に示す回路と較べると、抵抗値をキャリブレーション(校正)する回路の構成が異なる。コンパレータCOMPは、その出力電流IcpとコンパレートはVCOIN電圧とCP出力電流と外付け抵抗で行う方式でも実現できる。CP出力電流Icp(Ibias)を流す定電流源は、NMOSトランジスタM7のドレインとゲートおよびNMOSトランジスタM8のゲートに接続し、NMOSトランジスタM7,M8のソースはグランドに接地して、カレントミラー構成とする。さらに、NMOSトランジスタM8のドレインとPMOSトランジスタM9のドレインとゲート及びPMOSトランジスタM11のゲートを接続し、PMOSトランジスタM9、M11のソースは電源に接続して、カレントミラー構成にする。PMOSトランジスタM11のドレインは外付け抵抗R0を介してグランドに接地され、コンパレータ(COMP)の一方の入力段に接続される。コンパレータの他方の入力段にはVCO制御電圧VCOINが入力される。Icp*R0=Vrefを設計時におけるTYP条件の所望の周波数を出力する制御電圧とすると、信号calsel0〜calsel1をインクリメントすることにより変動するVCOINを比較し、コンパレータに入力される電圧が変動し他方の入力段の電位と比較した結果をデジタル制御回路に通知し、スイッチcalsel0-calsel1を制御することで、可変抵抗回路の一定の抵抗値を得ることができる。

【0041】

なお制御電圧VCOINの雑音の対策として、電圧電流変換回路は3.3V系トランジスタで構成し、高速発振を要する発振回路は1.2Vにて構成する。

【図面の簡単な説明】

【0042】

【図1】従来のPLL回路の基本構成を示すブロック図

【図2】電圧制御発振器の基本構成を示すブロック図

【図3】従来の電圧電流変換回路の1例の回路図

【図4】従来の電圧電流変換回路の他の例の回路図

【図5】差動インバータの1例の回路図

【図6】理想的な出力スペクトラムと実際の出力スペクトラムの図

【図7】MOSトランジスタの構造を示す図

【図8】電流制御発振回路の実施例の回路図

【図9】電圧電流回路の実施例の回路図

【図10】キャリブレーション動作のフローチャート

【図11】図9の回路の位相雑音シミュレーション結果のグラフ

【図12】図9の回路のVF特性のグラフ

【図13】電圧電流回路の別の実施例の回路図

【符号の説明】

【0043】

10 位相比較器、 12 LPF、 14 電圧制御発振器(VCO)、 20 電圧電流変換回路、 22 電流制御発振回路。

【技術分野】

【0001】

本発明は、PLL回路に関し、特に低ジッタで広範囲な発振可能周波数範囲を必要とする電圧電流変換回路が使用される電圧制御型発振器を備えたPLL回路に関するものである。

【背景技術】

【0002】

図1はPLL回路の基本構成を示すブロック図である。PLL回路は、位相比較器10、LPF(ループフィルタ)12、電圧制御発振器(VCO)14からなる。PLLブロックの各動作を説明する。基準信号Frと電圧制御発信器の出力信号Fvを位相比較器10に入力して誤差分を出力する。この後LPF12で位相比較より出力された誤差分の信号の直流分を取り出し制御電圧Fvを出力する。これらの構成ループの繰り返しによって電圧制御発振器14の出力信号は基準信号に正確に合わせることができる。PLL回路は、逓倍用PLLや周波数シンセサイザに応用できる。

【0003】

図2は、電圧制御発振器14の基本構成を示すブロック図である。電圧制御発振器14は、LPF12より入力される制御電圧に応じて電流を出力する電圧電流変換回路20と、その電流に応じた発振周波数を出力する電流制御発振器22により構成される。

【0004】

図3は電圧電流変換回路20の従来例を示す。LPF12より入力される制御電圧VCOINをゲートに印加されたNMOSトランジスタM0のソース側は抵抗R0を介してグランドに接地され、そのドレイン側は、PMOSトランジスタM1および抵抗R0と抵抗R1とを並列に介してグランドに接地されている。PMOSトランジスタM1にはNMOSトランジスタM0に流れる電流と抵抗R1に流れる電流の和が流れる。PMOSトランジスタM1のゲートをPMOSトランジスタM2のゲートとドレーンに接続して、PMOSトランジスタM1のゲート電圧をPMOSトランジスタM2に印加する。さらに、トランジスタM2,M3,M4でカレントミラー回路を構成して、トランジスタM2に流れる電流をM3,M4,M5のMOSトランジスタでカレントミラーで折り返して、電流制御型発振回路22の制御ノードNG,PGを形成する。

【0005】

図4は電圧電流変換回路20の他の従来例を示す。反転端子を入力子とする演算増幅回路AMPの出力がPMOSトランジスタM0に与えられており、PMOSトランジスタM0のドレイン側が外付けの抵抗Rを介してグランドに接地され、ゲート側は電源に接続されている。この回路は抵抗Rの両端に入力端子VCOINに印加される電圧と同じ電圧を印加させて出力端子に電流を発生させるものである。PMOSトランジスタM0に流れる電流IoutはIout=VCOIN/Rとなり、入力電圧に比例した電流を取り出すことができる。PMOSトランジスタM1は、PMOSトランジスタM0と等しいゲート電圧を与えることで、PMOSトランジスタM0に流れる電流と等しい電流を流す。

【0006】

図5は、電流制御発振器22における差動インバータの構成例を示す。図5において、M0,M1はPMOS型トランジスタでありM2,M3,M4はNMOS型トランジスタである。トランジスタM0,M1のソースには電源VCCが供給され、トランジスタM0のドレインにはトランジスタM2のドレインが接続され、この接続点から差動出力Vo+が出力される。トランジスタM1のドレインにはトランジスタM3のドレインが接続され、この接続点から差動出力Vo-が出力される。トランジスタM2のゲートには差動入力Vi+が入力され、トランジスタM3のゲートには差動入力Vi-が入力される。トランジスタM2、M3のソースはトランジスタM4のドレインに接続され、トランジスタM4のゲートにはバイアス電圧Vnが印加され、ソースはグランドに接地される。次に動作について説明する。トランジスタM0、M1は、線形領域で動作するようにバイアス電圧VPが加えられ夫々抵抗Rpとして用い、また、トランジスタM4は、飽和領域で動作するようにバイアス電圧Vnが加えられ、電流源として用いられる。

【0007】

PLL回路は、入力の位相差で動作するため位相雑音又はジッタの影響を受けやすいという問題がある。PLL回路設計に際しては、出力周波数の含むジッタ値が重要な電気的特性であり、様々な低ジッタ化が計られている。出力ジッタの原因としては大きく分けて2つ考えられる。1つは外部からPLL回路への雑音の混入、そしてもう1つはPLL回路(特にVCO14)が発生する雑音である。

【0008】

図6に理想的な出力スペクトラム(左側)と実際の出力スペクトラム(右側)を示す。VCO14が発生する位相雑音は、発振器を構成する素子そのものから注入され、出力周波数と出力振幅の両方に影響する。このうち影響が大きいのが出力周波数である。位相雑音は通常周波数領域で扱われる。理想的な発振器の出力スペクトルはインパルスで示されるのに対し、現実的な発振器の出力スペクトルは搬送波周波数の両側に広がるスカート特性を持つ。

【0009】

発振器を構成する素子が持つ雑音のうち、周波数近傍で雑音の影響が大きいのは1/F雑音である。1/F雑音はフリッカ雑音とも呼ばれ、その物理機構は明確化されていない。トランジスタ素子の製造工程において必然的に生じる、酸化膜中における不純物分布の不均一によっておこると概ね考えられている。

【0010】

式(1)は、HSPICE等の回路シミュレーションにおける標準MOSFETモデルであるBSIN3V3における1/F雑音(flicker noise)のモデルである。

【数1】

ここで、Fは発振周波数である。また、KFはフリッカーノイズ係数であり、AFはフリッカーノイズ指数であり、gmはゲート相互コンダクタンスであり、COXはゲート酸化膜キャパシタンスである。いずれもプロセス固有のパラメータである。また、Leffは有効チャネル長、Weffは有効チャネル幅である。

【0011】

図7にMOSFET(トランジスタ)の構造を示す。このMOSトランジスタは四端子デバイスでそれらの端子はドレイン、ゲートソース、基盤と呼ばれる。ソース、ドレイン接合はチャネル領域で反転層とつながっている。ソースとドレインの間にあるチャネルの長さはチャネル長(L)と呼ばれる。チャネル長に垂直な方向となるチャネルの幅は、チャネル幅(W)と呼ばれる。チャネルの電流を担う電荷のタイプによって、MOSFETはNチャネルかPチャネルのいずれかとなる。Nチャンネル型MOSFETでは、P型のSi基板の2ヶ所にn+型の電極を2つ作り、それぞれソース・ドレインとする。また、電極間のSi表面にSiO2の酸化膜を作り、さらにその上に金属を蒸着してゲートとする。チャンネル型の場合は、この説明とはnとp、電子と正孔が逆になるゲート電極に電圧をかけると、絶縁膜の下側で表面電位が変化し、ある程度以上の電圧がかかるとP型のSi基板にN型の反転層(チャンネル)ができる。すると、このチャンネルを通ってソースからドレインへと電子(P型の場合は正孔)が流れるようになり、電流が生じる。ゲート電圧を上げれば反転層は厚くなり、ドレイン電流は増える。逆にゲート電圧を下げると反転層は薄くなり、ドレイン電流は減る。以上が、MOSFETの動作原理である。

【0012】

一方、光ディスク用PLL回路等で必要とされる要件として、高周波発振かつ広いロックレンジの実現がある。高周波かつ広帯域を実現するにはPLL回路のVCO14を高速化する必要がある。CMOS差動インバータリング発振回路方式においては、広帯域なPLL回路を実現するのにもっとも一般的な方法であり、差動インバータ一段あたりのスキュー高速化のために構成トランジスタのゲート長L及びゲート幅Wを最小化する。またリングの差動インバータの段数を減らしリングのスキューを高速化することで、VCOの高速化を実現する。

【0013】

低ジッタ且つ広帯域のPLLに関する発明は従来からなされているが、電源や入力周波数等の外部起因する雑音に対する発明が多数を占める。そのうちPLLが生成するクロック信号に伴って発生する雑音による影響を低減する発明としては、次のようなものがある。

【0014】

特開2001−211055号公報に記載された回路では、中心周波数調整回路とこれによって制御される差動回路からなる遅延回路と加算回路をもち、遅延回路の数を調整することで広い周波数帯域を広げ、電源電圧による雑音を低減する。しかし位相雑音の観点から言えば、上記の回路は既存の回路より構成が複雑になることでVCO自身のジッタに対しては増大する。

また、外部雑音の対策用の回路を考案し、ジッタを低減するための発明には、特開2002−57574号公報に記載された回路があるが、トリプルウェル構造により基盤を通しての外部雑音を遮断する方法が有効である。

【特許文献1】特開2001−211055号公報

【特許文献2】特開2002−57574号公報

【発明の開示】

【発明が解決しようとする課題】

【0015】

位相雑音は、PLL回路のVCOの発振器における雑音の最上位の雑音源であり、ジッタ低減の観点からもこれを低減化することは非常に重要である。加えて、位相雑音は発振周波数の中心付近にあるため、フィルタリングでは完全除去することができない。位相雑音とジッタは、前者が周波数領域で扱われ、後者が時間領域で扱われるが、現象としては同一にとらえられる。したがってジッタ低減のためには、PLL回路の位相雑音を低く抑えることが重要となる。位相雑音はトランジスタの素子数に依存し、位相雑音を低く抑えるためにはPLL回路の構成をできるだけ少ないトランジスタ数で構成することが重要である。従来のジッタ低減技術では、ジッタを低減する機能を搭載するために、PLL回路の構成の複雑化による位相雑音の増大という問題が生じる。この問題を解消するためにはPLL回路をシンプルな構成で実現することが重要である。

【0016】

一方、PLL回路のVCO14の発振周波数は、電圧電流変換回路20及び電流制御発振回路22のプロセスのバラツキ、温度バラツキ、電源のバラツキにより変動する。中でもバラツキによる変動は、VCOの必要とされる発振周波数が高周波になるほど顕著になる。SLOWスピードのワースト条件(プロセスss、温度max,電源min,抵抗min)では仕様に必要なロックレンジを満たすことが難しくなり、一方HIGHスピードのワースト条件(プロセスff、温度min,電源max,抵抗min)ではオーバーレンジによるPLLの帰還ループのデッドロックが生じる場合がある。加えて、光ディスク書き込みクロック発生用PLLではCAV対応のため、広い範囲のロックレンジを満たし低速から高速にかけて一定のVCOゲインを実現することが課題となる。

【0017】

高周波発振かつ広帯域を実現するにはPLL回路のVCOを高速化する必要がある。CMOS差動インバータリング発振回路方式においては広帯域なPLL回路を実現するのにもっとも一般的な方法であり、差動インバータ一段あたりのスキュー高速化のために、構成トランジスタのゲート長L及びゲート幅Wを最小化する。またリングの差動インバータの段数を減らしリングのスキューを高速化することで、VCOの高速化を実現する。しかし、差動インバータ内の構成トランジスタを小面積化することは、発振周波数出力ノードに対する位相雑音への寄与を増大化する。リングの段数を減らすことは、広帯域化という面からは望ましくなく、一段あたりの遅延時間可変領域を増やす必要があり、安定した広範囲のロックレンジ実現は難しい。

【0018】

図3に示す従来例の電圧電流変換回路の課題として、使用する抵抗に内蔵ポリ抵抗を使用した場合、抵抗値がプロセス変動と温度変動をうけ±20%変動し、電圧電流変換特性に影響を及ぼすことがある。内蔵ポリ抵抗使用による抵抗バラツキの解決法としてバラツキの少ない外付抵抗を使用することが考えられるが、部品点数の増加、チップ面積大というデメリットがあるばかりでなく、センシティブなノードを外部に出すことで電圧電流変換回路に外部ノイズの混入のおそれがある。また、図4の電圧電流変換回路のように差動増幅回路の帰還ループで外付け抵抗を使用する回路の場合には、外付抵抗端子の寄生容量により、負帰還回路の帯域が低下し、PLLループ帯域の影響を受ける場合がある。

【0019】

概して広帯域なVCO14を制御する電圧電流変換回路20は、その精度要求から、構成の複雑化が避けられないのであるが、位相雑音を低減化しVCO本体が発生する雑音を低減するという目的のためには、構成回路を簡単化し、トランジスタ素子数を抑え、1/F雑音を取り除くことが重要である。

【0020】

この発明の目的は、以上のような課題を踏まえて、PLL回路において製造ばらつきによらず広い周波数帯域且つ大幅なジッタ低減を簡単な構成で実現することである。

【課題を解決するための手段】

【0021】

本発明に係るPLL回路は、基準信号と出力信号とを入力し誤差分を出力する位相比較器と、位相比較器より出力された信号の直流分を取り出し制御電圧を出力するループフィルタと、ループフィルタから入力される制御電圧に応じて前記出力信号を出力する電圧制御発振器とからなる。電圧制御発振器は、ループフィルタから出力される制御電圧を電流に変換する電圧電流変換回路と、該電流により発振周波数を制御されるリング状に接続された複数の差動インバータ回路より構成する発振回路とからなる。発振回路は、ゲートとドレインに電圧電流変換回路からの電流が入力されソースがグランドに接地される第二の電圧制御トランジスタと、ゲートが第二の電圧トランジスタのゲートに接続されソースがグランドに接地されてカレントミラー回路を構成するトランジスタと、このトランジスタのドレインにドレインとゲートが接続されソースが電源電圧に接続される第一の電圧制御トランジスタを備え、第一及び第二の電圧制御トランジスタは該複数の差動インバータ回路への第一と第二の制御電圧を生成する。各々の差動インバータ回路は、第一の制御電圧がゲートに入力され抵抗素子として動作する第三のトランジスタと、第三のトランジスタに直列に接続されゲートに差動入力が入力される第五のトランジスタとからなり差動出力を出力する一組が2つ並列に配置され、この二組に直列にドレインが接続されゲートに第一の制御電圧が入力され電流源となる第四のトランジスタを備える。第一及び第二の電圧制御トランジスタは、該第一及び第二の電圧制御トランジスタがそれぞれ制御する差動インバータの第三及び第四のトランジスタサイズよりゲート長及びゲート幅を共に等しい倍数だけ大きくしたトランジスタで構成する。

【0022】

好ましくは、前記PLL回路において、前記差動インバータ回路の第四のトランジスタは、第三のトランジスタのサイズよりゲート長及びゲート幅を共に等しい倍数だけ大きくしたトランジスタである。

【0023】

好ましくは、前記PLL回路において、前記電圧電流変換回路は、ゲートにループフィルタから入力される制御電圧が入力され、ソースに電流を決定するための可変抵抗回路が接続されるトランジスタを含み、可変抵抗回路は、直列または並列に接続された複数の抵抗からなる。さらに、可変抵抗回路の抵抗値を校正する校正回路を有する。前記校正回路は、たとえば、校正用の電流が前記可変抵抗回路のレプリカを流れるときの降下電圧を、基準電流が基準抵抗を流れるときの降下電圧を比較するコンパレータを備える。または、前記校正回路は、たとえば、ループフィルタから入力される制御電圧と、基準電流が基準抵抗を流れるときの降下電圧を比較するコンパレータを備える。

【発明の効果】

【0024】

PLL回路において、差動インバータの制御電圧を生成する第一の及び第二の電圧制御トランジスタは該第一及び第二の電圧制御トランジスタが制御する差動インバータの第三及び第四のトランジスタサイズよりゲート長及びゲート幅を等しい倍数だけ大きくしたトランジスタで構成することで、出力発振周波数の位相雑音がきわめて少なく低ジッタのPLLを実現できる。

【0025】

また、差動インバータは抵抗素子をなす第三トランジスタと差動信号が入力されるトランジスタと電流源を成す第四トランジスタとからなる差動回路により構成され、前記定電流源トランジスタは抵抗トランジスタサイズよりゲート長及びゲート幅を等しい倍数だけ大きくしたトランジスタにより構成することで、出力発振周波数の位相雑音がきわめて少なく低ジッタのPLLを実現できる。

【0026】

また、電圧電流変換回路は電流を決定する素子として直列または並列に接続された複数の抵抗を用い抵抗プロセスのばらつきを補正する回路を有し、プロセスバラツキによらずVCOリングが広範囲のロックレンジで一定のゲインを保持する調整機能を有することにより、抵抗のばらつきによらない制御電流を得ることができる。かつ、可変抵抗の制御部をPLL外部デジタル制御回路が持ち、PLL回路内部は簡単な構成ができる。これにより、回路内のトランジスタ数が抑えられることで、雑音成分を少なくし、トランジスタの位相雑音ジッタを抑え、かつ、広範囲なロックレンジを満たすことができる。

【発明を実施するための最良の形態】

【0027】

以下、本発明の実施の形態を添付の図面を参照して説明する。

【0028】

本発明の実施の形態のPLL回路は、図1に示した構成を備える。すなわち、PLL回路は、位相比較器10、LPF(ループフィルタ)12、電圧制御発振器(VCO)14からなる。基準信号FrとVCOの出力信号Fvが位相比較器10に入力されると誤差分が出力される。次に、LPF12は、位相比較器10より出力された信号(誤差分)の直流分を取り出し制御電圧を出力する。VCO14は、この制御電圧に応じて出力信号Fvを出力する。このループの繰り返しによってVCO14の出力信号は基準信号Frに正確に合わせられる。本発明のPLL回路では、以下に説明するVCO14を用いて、製造ばらつきによらず広い周波数帯域かつ大幅なジッタ低減を簡単な構成で実現する。

【0029】

図2に示すように、VCO14において、電圧電流変換回路20は、LPF12より入力される制御電圧に応じて電流を出力し、電流制御発振回路22は、その電流に応じた発振周波数を出力する。電流制御発振回路22は、LPF12からの電流により発振周波数を制御されるリング状に接続された複数の差動インバータ回路より構成する発振回路を含む。

【0030】

図8は、電流制御発振回路22の1例である。電圧電流変換回路20より入力される電流IoutがNMOSトランジスタM3のドレインとゲートに入力され、NMOSトランジスタM3のソースはグランドに接地される。NMOSトランジスタM3のゲートとドレインに入力されるノードをNGとする。NMOSトランジスタM4はソースをグランドに接地しゲートをNMOSトランジスタM3のゲートに接続して、カレントミラー回路を構成する。さらに、NMOSトランジスタM4のドレインはPMOSトランジスタM5のゲート及びドレインに接続され、このノードをPGとする。PMOSトランジスタM5のソースは電源に接続される。これによって入力電流IoutはM3,M4,M5と折り返され、複数の同一形状の差動増幅回路によって構成される3段のリング発振器(破線で囲まれた部分)にバイアスする。差動増幅回路において抵抗素子として動作するPMOSトランジスタM00,M01,M10,M11,…,MN0,MN1のゲートとノードPGが接続されることにより、PMOSトランジスタM5は第一のリング発振器の電圧制御トランジスタとなり、定電流素子として動作するNMOSトランジスタM04,M14、…,MN4のゲートとノードNGと接続され、よってNMOSトランジスタM5はリング発振器の第二の電圧制御トランジスタとなり、リング発振器の発振周波数を制御する。

【0031】

Ioutの電流を基に各リングに等しい電流値を伝えるには、従来ならばノードPGにて接続された第一の電圧制御トランジスタM5とリング抵抗素子であるPMOSトランジスタM00,M01,M10,M11,…,MN0,MN1のトランジスタサイズW及びLは等しくするものであり、同様にノードNGにて接続された第二の電圧制御トランジスタM3とリング定電流素子であるPMOSトランジスタM04,M14,…MN4のトランジスタサイズW、Lも等しくするものである。

【0032】

式(1)によりトランジスタのWまたはLを大きくすれば1/Fは低減する。すべてのトランジスタを大きくすることはチップ面積の面から現実的ではない。最も効果的な素子は周波数出力の上位に位置するリングの制御トランジスタである。第一の電圧制御トランジスタM5及び第二の電圧制御トランジスタM3はリング構成素子の上流に位置しており、発振周波数出力ノードにおける1/F雑音の影響の大きさからは必ずその影響度が高い。そこで、この素子をゲート幅及びゲート長を2倍以上の等倍にすることで、バイアス部の特性を変更することなく、効果的に位相雑音を低減できる。これにより、出力発振周波数の位相雑音がきわめて少なく低ジッタのPLL回路を実現できる。トランジスタ面積を大きくすることは、電源ノイズ等の外的ノイズに対する耐性強化も期待できる。リング構成素子のうち抵抗素子として動作するPMOSトランジスタM00,M01,M10,M11,…,MN0,MN1についてはVCO全体の位相雑音を減らすためには有効であるが、抵抗素子が大きくなることで寄生容量が増し、高速発振、広帯域のVCO設計の観点からは避けるべきである。

【0033】

たとえば、第一の電圧制御トランジスタM5及び第二の電圧制御トランジスタM3の雑音を小さくし、なおかつIoutの電流を等しく各リングに伝えるために、第一の電圧制御トランジスタM5のサイズ比β5=W5/L5は、リング構成素子であるNMOSトランジスタM04,M14,…,MN4のトランジスタサイズ比をβN=WN/LNとすると、W5=WP*N及びL5=LP*N(N:整数)とし、ゲート幅W、ゲート長Lともリング構成素子に比して等しくN倍とする。また、第二の電圧制御トランジスタM3のサイズ比β3=W3/L3は、リング構成素子であるPMOSトランジスタM00,M01,M10,M11,…,MN0,MN1のトランジスタサイズ比をβP=WP/LPとするとW3=WP*N及びL3=LP*N(N:整数)とし、W,Lともリング構成素子に比して等しくN倍とする。すなわち、差動インバータの制御電圧を生成する第一及び第二の電圧制御トランジスタは、その第一及び第二の電圧制御トランジスタが制御する差動インバータの第三及び第四のトランジスタサイズよりゲート長L及びゲート幅Wを共に等しい倍数だけ大きくしたトランジスタで構成する。

【0034】

また、リング定電流トランジスタM04,M14,…,MN4と抵抗トランジスタM00,M01,M10,M11,…,MN0,MN1のトランジスタサイズ関係はWN=WP*N及びLN=LP*N(N:整数)とする。すなわち、差動インバータは抵抗素子をなす第三トランジスタと差動信号が入力されるトランジスタと電流源を成す第四トランジスタとからなる差動回路により構成されていて、定電流源トランジスタM04,M14,…,MN4は抵抗トランジスタM00,M01,M10,M11,…,MN0,MN1のサイズよりゲート長及びゲート幅を共に等しい倍数だけ大きくしたトランジスタにより構成する。これにより、出力発振周波数の位相雑音がきわめて少なく低ジッタのPLL回路を実現できる。

【0035】

図9は、本発明の電圧電流変換回路20の1例を示す。位相雑音を低減化しVCO本体が発生する雑音を低減するという目的のためには、電圧電流変換回路20の構成を簡単化し、トランジスタ素子数を抑え、1/F雑音を取り除く。電流を決定する素子として可変抵抗回路を用い、抵抗プロセスのばらつきを簡単な校正で補正する。この回路では、VCO14の制御電圧VCOINがNMOSトランジスタM0のゲートに入力され、NMOSトランジスタM0のソースには、破線で囲んで示される可変抵抗回路が接続される。この可変抵抗回路では、N個の固定抵抗R0,R01,R02,…,R0Nの一端がNMOSトランジスタM0のソースに並列に接続され、かつ、それらの固定抵抗R00,R01,R02,…,R0Nの他端はそれぞれスイッチを介してグランドに接地される。夫々のスイッチは信号calsel0, calsel1, calsel2, …, calselNによって制御し、可変抵抗回路の抵抗値を可変とする。また、NMOSトランジスタM0のドレインはPMOSトランジスタM1のドレイン及びゲートに接続され、また、PMOSトランジスタM1のソースは電源に接続される。さらに、NMOSトランジスタM0のドレインはPMOSトランジスタM2,M3,M4,M5,M6のドレインに接続され、PMOSトランジスタM2,M3,M4,M5,M6のソースは電源に接続され、PMOSトランジスタM3,M4,M5,M6のドレインは夫々スイッチを介しM2のドレインと接続される。PMOSトランジスタM3,M4,M5,M6のスイッチを閉じると、出力電流Ioutが増加される。こうして、出力電流Ioutを可変とする。

【0036】

図9の下側に示すように、これらの抵抗値をキャリブレーション(校正)する回路では、固定抵抗R0、R01、R02,…,R0Nと等しい形状の固定抵抗R10,R11,R12,…,R1N(可変抵抗レプリカ)が信号calsel0,calsel1,calsel2,…,calselNによってそれぞれ制御されるスイッチを介してグランドに接地される。これらの抵抗を外付け抵抗R0とキャリブレートするため、定電流源IbiasをNMOSトランジスタM7のドレインとゲートに接続し、NMOSトランジスタM8のゲートと接続し、NMOSトランジスタM7,M8のソースはグランドに接地する。定電流源IbiasとNMOSトランジスタM7,M8は、カレントミラー構成にする。さらに、NMOSトランジスタM8のドレインとPMOSトランジスタM9のドレインとゲート及びPMOSトランジスタM10,M11のゲートを接続し、カレントミラー構成にする。PMOSトランジスタM9,M10,M11のソースは電源に接続する。PMOSトランジスタM10のドレインは、可変抵抗レプリカの固定抵抗R10,R11,R12,…,R1Nとコンパレータの一方の入力段に接続される。PMOSトランジスタM11のドレインは、R0とコンパレータの他方の入力段に接続され、これにより固定抵抗R10,R11,R12,…,R1NにはIbiasを基準とする電流Icalが流れ、外付け抵抗R0には同じくIbiasを基準とする電流Irefが流れる。デジタル制御回路よりスイッチcalsel0〜calsel1に対応したアドレスをインクリメントすることにより、コンパレータに入力される電圧が変動し、他方の入力段の電位と比較した結果をデジタル制御回路に通知してスイッチcalsel0-calsel1を制御することで、一定の抵抗値を得る。図10にキャリブレーションの動作フローを示す。初期設定Calsel0よりスタートしCalsel1,calsel2,…calselFの計16段階のキャリブレーションが行われ、各設定に応じた抵抗値が用意されている。ここで、スイッチごとに、calsel=i(i=0〜F)を設定し、コンパレータの出力が1であると、CAL_CODE=iをデジタル制御回路に出力する。こうして、抵抗値が基準抵抗R0と等しい場合コンパレータに1が出力され、検知したデジタル回路がcal_codeの数値をPLL回路に返し、火炎抵抗回路の抵抗値を決定する。

【0037】

このように、電圧電流変換回路20は、電流を決定する素子として直列または並列に接続された複数の抵抗(可変抵抗回路レプリカ)を用い抵抗プロセスのばらつきを補正する回路を有し、かつ、プロセスのバラツキによらずVCOリングが広範囲のロックレンジで一定のゲインを保持する調整機能を有する。こうして、高速化、広帯域なVCOの実現のために、線形性を保持し、かつ、抵抗とプロセスのばらつきを補正する電圧電流変換回路を簡単な構成で実現できる。これにより抵抗のばらつきによらない制御電流を得ることができる。かつ、可変抵抗の制御部をPLL外部デジタル制御回路が持ちPLL回路内部は簡単な構成ができることにより、回路内のトランジスタ数が抑えられる。このため、雑音成分を少なくし、トランジスタの位相雑音ジッタを抑え、且つ、広範囲なロックレンジを満たすことができる。

【0038】

図11は、本実施形態と従来のVCO回路の位相雑音シミュレーション結果を示す。本発明のVCO回路では、位相雑音がきわめて少ないことがわかる。また、VCO回路の位相雑音の実測結果結果では、RMSジッタは、従来回路では3.09%であったの対し、本発明のVCO回路では1.44%であった。

【0039】

また、図12は、本実施形態のVCO回路における入力電圧VCOINに対する出力周波数FoutのVF特性の実測結果を示す。ここで、SSはSLOWスピードのワースト条件を示し、FFはHIGHスピードのワースト条件を示し、TYPは典型的なスピードの条件を示す。TYPでは広い周波数範囲で線形性が得られている。

【0040】

図13は、電圧電流変換回路20の別の例を示す。図9に示す回路と較べると、抵抗値をキャリブレーション(校正)する回路の構成が異なる。コンパレータCOMPは、その出力電流IcpとコンパレートはVCOIN電圧とCP出力電流と外付け抵抗で行う方式でも実現できる。CP出力電流Icp(Ibias)を流す定電流源は、NMOSトランジスタM7のドレインとゲートおよびNMOSトランジスタM8のゲートに接続し、NMOSトランジスタM7,M8のソースはグランドに接地して、カレントミラー構成とする。さらに、NMOSトランジスタM8のドレインとPMOSトランジスタM9のドレインとゲート及びPMOSトランジスタM11のゲートを接続し、PMOSトランジスタM9、M11のソースは電源に接続して、カレントミラー構成にする。PMOSトランジスタM11のドレインは外付け抵抗R0を介してグランドに接地され、コンパレータ(COMP)の一方の入力段に接続される。コンパレータの他方の入力段にはVCO制御電圧VCOINが入力される。Icp*R0=Vrefを設計時におけるTYP条件の所望の周波数を出力する制御電圧とすると、信号calsel0〜calsel1をインクリメントすることにより変動するVCOINを比較し、コンパレータに入力される電圧が変動し他方の入力段の電位と比較した結果をデジタル制御回路に通知し、スイッチcalsel0-calsel1を制御することで、可変抵抗回路の一定の抵抗値を得ることができる。

【0041】

なお制御電圧VCOINの雑音の対策として、電圧電流変換回路は3.3V系トランジスタで構成し、高速発振を要する発振回路は1.2Vにて構成する。

【図面の簡単な説明】

【0042】

【図1】従来のPLL回路の基本構成を示すブロック図

【図2】電圧制御発振器の基本構成を示すブロック図

【図3】従来の電圧電流変換回路の1例の回路図

【図4】従来の電圧電流変換回路の他の例の回路図

【図5】差動インバータの1例の回路図

【図6】理想的な出力スペクトラムと実際の出力スペクトラムの図

【図7】MOSトランジスタの構造を示す図

【図8】電流制御発振回路の実施例の回路図

【図9】電圧電流回路の実施例の回路図

【図10】キャリブレーション動作のフローチャート

【図11】図9の回路の位相雑音シミュレーション結果のグラフ

【図12】図9の回路のVF特性のグラフ

【図13】電圧電流回路の別の実施例の回路図

【符号の説明】

【0043】

10 位相比較器、 12 LPF、 14 電圧制御発振器(VCO)、 20 電圧電流変換回路、 22 電流制御発振回路。

【特許請求の範囲】

【請求項1】

基準信号と出力信号とを入力し誤差分を出力する位相比較器と、位相比較器より出力された信号の直流分を取り出し制御電圧を出力するループフィルタと、ループフィルタから入力される制御電圧に応じて前記出力信号を出力する電圧制御発振器とからなり、

電圧制御発振器は、ループフィルタから出力される制御電圧を電流に変換する電圧電流変換回路と、該電流により発振周波数を制御されるリング状に接続された複数の差動インバータ回路より構成する発振回路とからなり、

発振回路は、ゲートとドレインに電圧電流変換回路からの電流が入力されソースが接地される第二の電圧制御トランジスタと、ゲートが第二の電圧トランジスタのゲートに接続されソースが接地されてカレントミラー回路を構成するトランジスタと、このトランジスタのドレインにドレインとゲートが接続されソースが電源電圧に接続される第一の電圧制御トランジスタを備え、第一及び第二の電圧制御トランジスタは該複数の差動インバータ回路への第一と第二の制御電圧を生成し、

各々の差動インバータ回路は、第一の制御電圧がゲートに入力され抵抗素子として動作する第三のトランジスタと、第三のトランジスタに直列に接続されゲートに差動入力が入力される第五のトランジスタとからなり差動出力を出力する一組が2つ並列に配置され、この二組に直列にドレインが接続されゲートに第一の制御電圧が入力され電流源となる第四のトランジスタを備え、

第一及び第二の電圧制御トランジスタは、該第一及び第二の電圧制御トランジスタがそれぞれ制御する差動インバータの第三及び第四のトランジスタサイズよりゲート長及びゲート幅を共に等しい倍数だけ大きくしたトランジスタで構成したことを特徴とするPLL回路。

【請求項2】

前記差動インバータ回路の第四のトランジスタは、第三のトランジスタのサイズよりゲート長及びゲート幅を共に等しい倍数だけ大きくしたトランジスタであることを特徴とする請求項1記載のPLL回路。

【請求項3】

前記電圧電流変換回路は、ゲートにループフィルタから入力される制御電圧が入力され、ソースに電流を決定するための可変抵抗回路が接続されるトランジスタを含み、

可変抵抗回路は、直列または並列に接続された複数の抵抗からなり、

さらに、可変抵抗回路の抵抗値を校正する校正回路を有することを特徴とする請求項1または請求項2記載のPLL回路。

【請求項4】

前記校正回路は、校正用の電流が前記可変抵抗回路のレプリカを流れるときの降下電圧を、基準電流が基準抵抗を流れるときの降下電圧を比較するコンパレータを備えることを特徴とする請求項3記載のPLL回路。

【請求項5】

前記校正回路は、ループフィルタから入力される制御電圧と、基準電流が基準抵抗を流れるときの降下電圧を比較するコンパレータを備えることを特徴とする請求項3記載のPLL回路。

【請求項1】

基準信号と出力信号とを入力し誤差分を出力する位相比較器と、位相比較器より出力された信号の直流分を取り出し制御電圧を出力するループフィルタと、ループフィルタから入力される制御電圧に応じて前記出力信号を出力する電圧制御発振器とからなり、

電圧制御発振器は、ループフィルタから出力される制御電圧を電流に変換する電圧電流変換回路と、該電流により発振周波数を制御されるリング状に接続された複数の差動インバータ回路より構成する発振回路とからなり、

発振回路は、ゲートとドレインに電圧電流変換回路からの電流が入力されソースが接地される第二の電圧制御トランジスタと、ゲートが第二の電圧トランジスタのゲートに接続されソースが接地されてカレントミラー回路を構成するトランジスタと、このトランジスタのドレインにドレインとゲートが接続されソースが電源電圧に接続される第一の電圧制御トランジスタを備え、第一及び第二の電圧制御トランジスタは該複数の差動インバータ回路への第一と第二の制御電圧を生成し、

各々の差動インバータ回路は、第一の制御電圧がゲートに入力され抵抗素子として動作する第三のトランジスタと、第三のトランジスタに直列に接続されゲートに差動入力が入力される第五のトランジスタとからなり差動出力を出力する一組が2つ並列に配置され、この二組に直列にドレインが接続されゲートに第一の制御電圧が入力され電流源となる第四のトランジスタを備え、

第一及び第二の電圧制御トランジスタは、該第一及び第二の電圧制御トランジスタがそれぞれ制御する差動インバータの第三及び第四のトランジスタサイズよりゲート長及びゲート幅を共に等しい倍数だけ大きくしたトランジスタで構成したことを特徴とするPLL回路。

【請求項2】

前記差動インバータ回路の第四のトランジスタは、第三のトランジスタのサイズよりゲート長及びゲート幅を共に等しい倍数だけ大きくしたトランジスタであることを特徴とする請求項1記載のPLL回路。

【請求項3】

前記電圧電流変換回路は、ゲートにループフィルタから入力される制御電圧が入力され、ソースに電流を決定するための可変抵抗回路が接続されるトランジスタを含み、

可変抵抗回路は、直列または並列に接続された複数の抵抗からなり、

さらに、可変抵抗回路の抵抗値を校正する校正回路を有することを特徴とする請求項1または請求項2記載のPLL回路。

【請求項4】

前記校正回路は、校正用の電流が前記可変抵抗回路のレプリカを流れるときの降下電圧を、基準電流が基準抵抗を流れるときの降下電圧を比較するコンパレータを備えることを特徴とする請求項3記載のPLL回路。

【請求項5】

前記校正回路は、ループフィルタから入力される制御電圧と、基準電流が基準抵抗を流れるときの降下電圧を比較するコンパレータを備えることを特徴とする請求項3記載のPLL回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2006−41810(P2006−41810A)

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願番号】特願2004−217407(P2004−217407)

【出願日】平成16年7月26日(2004.7.26)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願日】平成16年7月26日(2004.7.26)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]